# **INAUGURAL - DISSERTATION**

zur Erlangung der Doktorwürde der Naturwissenschaftlich-Mathematischen Gesamtfakultät der Ruprecht-Karls-Universität Heidelberg

> vorgelegt von Diplom–Physiker Ralf Erich Panse aus Mannheim

Tag der mündlichen Prüfung: 12. Oktober 2009

# CHARM-Card: Hardware Based Cluster Control And Management System

Gutachter: Prof. Dr. Volker Lindenstruth Prof. Dr. Thomas Ludwig

#### CHARM-Card: Hardwarebasiertes Computer-Cluster Kontroll- und Managementsystem

Die Selektion und Analyse von Ereignisdaten des Schwerionen-Experiments ALICE am CERN werden durch sogenannte Triggerstufen vorgenommen. Der High Level Trigger (HLT) ist die letzte Triggerstufe des Experimentes. Er besteht aus einer Rechnerfarm von zur Zeit über 120 Computer, die auf 300 Rechner ausgebaut werden soll. Die manuelle Installation, Konfiguration und Wartung einer Rechnerfarm dieser Größe sind dabei jedoch sehr aufwändig und zeitintensiv.

Die vorliegende Arbeit beschreibt die Implementierung und Funktionsweise einer autonomen Steuereinheit, die in jedem Rechner des HLT Computer Clusters eingebaut wurde. Die Hauptaufgaben der Steuereinheit sind die Fernsteuerung der Knoten und die automatische Installation, Überwachung und Wartung derselben. Ein weiteres erreichtes Ziel ist die universelle Nutzung der Steuereinheit: Denn aufgrund der heterogenen Clusterstruktur durfte es keine Einschränkungen für den Betrieb der Steuereinheit bezüglich des Rechnermodells oder des Betriebssystems der Clusterknoten geben. Dadurch lassen sich auch kostengünstige COTS (commercial-off-the-shelf) Rechner als Knoten einsetzen, ohne dabei auf die Fernwartungsfunktionen zu verzichten, wie sie in teuren Serverrechner zu finden sind.

Die Steuereinheit ist bereits im Einsatz und ermöglicht die Fernwartung aller Rechner des HLT Clusters. Des Weiteren wurde die gesamte HLT Rechnerfarm mit Hilfe der Steuereinheit automatisch installiert, getestet und konfiguriert.

### CHARM-Card: Hardware Based Computer Cluster Control And Management System

The selection and analysis of detector events of the heavy ion collider experiment ALICE at CERN are accomplished by the so-called trigger levels. The High Level Trigger (HLT) is the last trigger level of this experiment. Currently, it consists of up to over 120 computers and it is planned to upgrade the cluster to up to 300 computers. However, the manual installation, configuration and maintenance of such a big computer farm require a large amount of administrative effort.

This thesis describes the implementation and functionality of an autonomous control unit, which was installed to every node of the HLT computing cluster. The main tasks of the control unit are the remote control of the cluster nodes and the automatic installation, monitoring and maintenance of the computers. By the reason of the heterogeneous layout of the target cluster, the control unit was developed to be flexible in use independent of the computer model or operating system of the cluster node. This characteristic enables remote control of cost-efficient COTS (commercial-off-the-shelf) PCs, which do not have integrated remote control capabilities as expensive server boards.

The HLT computing cluster is already remotely controlled by the help of the control unit. Furthermore, this control unit was also used for the automatic setup, testing and configuration of all cluster nodes.

# Contents

| 1 | Intro | oduction                                                  | 17 |

|---|-------|-----------------------------------------------------------|----|

|   | 1.1   | Outline                                                   | 18 |

|   | 1.2   | ALICE Experiment                                          | 18 |

|   | 1.3   | HLT Computer Cluster                                      | 18 |

|   | 1.4   | Remote Management Tools                                   | 20 |

|   |       | 1.4.1 KVM                                                 | 20 |

|   |       | 1.4.2 BIOS Console Redirection                            | 21 |

|   |       | 1.4.3 IPMI                                                | 21 |

|   |       | 1.4.4 Remote Management Cards                             | 21 |

|   | 1.5   | CHARM Card                                                | 23 |

|   |       | 1.5.1 Features of the CHARM                               | 23 |

|   |       | 1.5.2 Usage of the CHARM                                  | 24 |

|   |       |                                                           |    |

| 2 | CHA   | ARM Architecture                                          | 27 |

|   | 2.1   | Overview of the CHARM Board                               | 27 |

|   | 2.2   | Excalibur Chip                                            | 29 |

|   |       | 2.2.1 Embedded Stripe                                     | 29 |

|   |       | 2.2.2 ARM922T CPU                                         | 30 |

|   |       | 2.2.3 FPGA Device                                         | 31 |

|   | 2.3   | FPGA Design of the CHARM                                  | 31 |

| 3 | Sof   | tware of the CHARM                                        | 35 |

| Ū | 3.1   | Boot Loader                                               | 35 |

|   | 3.2   | Operating System                                          | 35 |

|   | 0.2   | 3.2.1 Device Drivers                                      | 35 |

|   | 3.3   | File system of the CHARM                                  | 37 |

|   | 0.0   | 3.3.1 Directory Structure                                 | 37 |

|   | 3.4   | NFS-Directory                                             | 38 |

|   | 0.1   |                                                           | 00 |

| 4 | Gra   | phic Card Implementation                                  | 41 |

|   | 4.1   | VGA Specification                                         | 41 |

|   |       | 4.1.1 VGA Components                                      | 42 |

|   |       | 4.1.2 Video Modes                                         | 43 |

|   |       | 4.1.3 Access to the Video Memory and Register             | 45 |

|   |       | 4.1.4 Addressing of the Video Planes                      | 46 |

|   | 4.2   | Graphic Card Implementation Layout                        | 46 |

|   |       | 4.2.1 VGA address window                                  | 47 |

|   |       | 4.2.2 Hardware Implementation of the PCI Target Interface | 50 |

|   |     | 4.2.3 Software VGA Processing                                                                                                                                           |

|---|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 4.3 | VGA BIOS                                                                                                                                                                |

|   |     | 4.3.1 BIOS Remote Procedure Call                                                                                                                                        |

|   |     | 4.3.2 Host Interface of the RPC                                                                                                                                         |

|   |     | 4.3.3 CHARM Interface of the RPC                                                                                                                                        |

|   |     | 1.3.4 Data Flow of the RPC $\ldots \ldots \ldots$       |

| 5 | Dev | e Emulation 65                                                                                                                                                          |

|   | 5.1 | USB Device Emulation                                                                                                                                                    |

|   |     | 5.1.1 USB Bus System                                                                                                                                                    |

|   |     | 5.1.2 Cypress EZ-Host USB Controller                                                                                                                                    |

|   |     | 5.1.3 Human Interface Device                                                                                                                                            |

|   |     | 5.1.4 Mass Storage Device                                                                                                                                               |

|   | 5.2 | Legacy Device Emulation                                                                                                                                                 |

|   |     | 5.2.1 Keyboard Controller                                                                                                                                               |

|   |     | 5.2.2 BIOS Keyboard Buffer                                                                                                                                              |

|   | 5.3 | Computer Power Control                                                                                                                                                  |

| • |     | •                                                                                                                                                                       |

| 6 |     | vare Monitor Functionality   79                                                                                                                                         |

|   | 6.1 | Power On Self Test                                                                                                                                                      |

|   | 6.2 | Host System Inspector                                                                                                                                                   |

|   |     | $5.2.1  \text{PCI Master Control} \qquad \qquad$ |

|   |     | 5.2.2 Computer Health Analyzer                                                                                                                                          |

|   | 6 9 | 5.2.3 Analog Signal Measurement                                                                                                                                         |

|   | 6.3 | Display Screen Inspector       84         5.3.1       Alphanumerical Representation of the Screen Content       85                                                      |

|   |     | 1 1                                                                                                                                                                     |

|   |     |                                                                                                                                                                         |

|   | 6.4 | 5.3.3       Text Highlighting of the Screen       87         Monitoring Software       89                                                                               |

|   | 0.4 |                                                                                                                                                                         |

| 7 |     | natic Cluster Management 93                                                                                                                                             |

|   | 7.1 | Complex Tasks                                                                                                                                                           |

|   |     | 7.1.1 CHARM Remote Shell                                                                                                                                                |

|   |     | 7.1.2 Setup of the BIOS CMOS Settings                                                                                                                                   |

|   |     | 7.1.3 Automatic Computer Tests                                                                                                                                          |

|   |     | 7.1.4 Automatic Network Setup                                                                                                                                           |

|   |     | 7.1.5 Automatic Operating System Installation                                                                                                                           |

|   |     | 7.1.6 Automatic Repair $\ldots \ldots \ldots$           |

| 8 | Spe | al Implementations 103                                                                                                                                                  |

|   | 8.1 | PCI Bus Analyzer                                                                                                                                                        |

|   |     | $3.1.1  \text{FPGA logic}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                             |

|   |     | $8.1.2  \text{Controller Software}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                    |

|   |     | 8.1.3 GUI of the Analyzer                                                                                                                                               |

|   | 8.2 | Network Card $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $107$                                                                     |

|     |                          | 8.2.1<br>8.2.2                                              | CHARM-Host Network Bridge                                                                                                                                                                                                                                                                     |       |                   |                                       | 108<br>111                                                         |

|-----|--------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------|---------------------------------------|--------------------------------------------------------------------|

| 9   | 9.1<br>9.2<br>9.3<br>9.4 | VGA H<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>USB C<br>USB C | As and Verification         Function Performance         Estimation of the VGA Data Throughput         CHARM PCI Target Throughput         CHARM VGA Processing Performance         CHARM Graphical Output Performance         CD-ROM Performance         Compliance Test         Consumption | · · · | · ·<br>· ·<br>· · | · · · · · · · · · · · · · · · · · · · | <b>113</b><br>113<br>114<br>116<br>116<br>121<br>124<br>126<br>127 |

| 10  | Con                      | clusior                                                     | and Outlook                                                                                                                                                                                                                                                                                   |       |                   |                                       | 129                                                                |

| A   | Abb                      | reviatio                                                    | ons                                                                                                                                                                                                                                                                                           |       |                   |                                       | 131                                                                |

| В   | Cha                      | racteris                                                    | stics of the CHARM System                                                                                                                                                                                                                                                                     |       |                   |                                       | 133                                                                |

| С   | C.1                      | Third                                                       | <b>of the CHARM</b><br>Party Application                                                                                                                                                                                                                                                      |       |                   |                                       | <b>135</b><br>135<br>135                                           |

| D   | СНА                      | RM Re                                                       | gister Map                                                                                                                                                                                                                                                                                    |       |                   |                                       | 137                                                                |

| Е   | СНА                      | RM Int                                                      | ernal Address Map                                                                                                                                                                                                                                                                             |       |                   |                                       | 139                                                                |

| F   | Devi                     | ice Em                                                      | ulation                                                                                                                                                                                                                                                                                       |       |                   |                                       | 143                                                                |

| G   |                          | Setup<br>Suppor                                             | rted Mainboards                                                                                                                                                                                                                                                                               |       |                   |                                       | <b>145</b><br>146                                                  |

| н   |                          | Video                                                       | Modes                                                                                                                                                                                                                                                                                         |       |                   |                                       | <b>147</b><br>147<br>148                                           |

| Bil | bliog                    | raphy                                                       |                                                                                                                                                                                                                                                                                               |       |                   |                                       | 151                                                                |

# **List of Figures**

| $1.1 \\ 1.2$ | Overview of the LHC ring at CERN                                          | $     \begin{array}{c}       19 \\       20     \end{array} $ |

|--------------|---------------------------------------------------------------------------|---------------------------------------------------------------|

| 1.2 1.3      | Remote management of computer systems                                     | $\frac{20}{22}$                                               |

| 1.3<br>1.4   | Screenshot of a VNC session while setup the BIOS settings with the aid of | 22                                                            |

| 1.4          | the CHARM.                                                                | 24                                                            |

| 1.5          | Screenshot of the web page provided by the CHARM.                         | $\frac{24}{25}$                                               |

| 1.0          | Screenshot of the web page provided by the CHARM                          | 20                                                            |

| 2.1          | Layout of the CHARM board.                                                | 27                                                            |

| 2.2          | Structure of the Excalibur Embedded Processor Stripe [1].                 | 30                                                            |

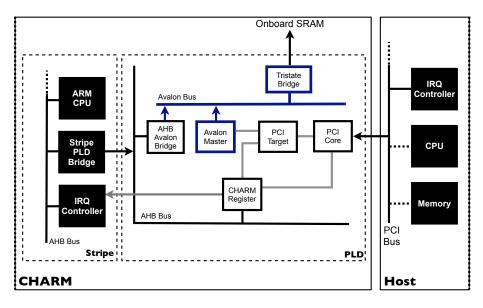

| 2.3          | Structure of the CHARM PLD design.                                        | 32                                                            |

|              |                                                                           |                                                               |

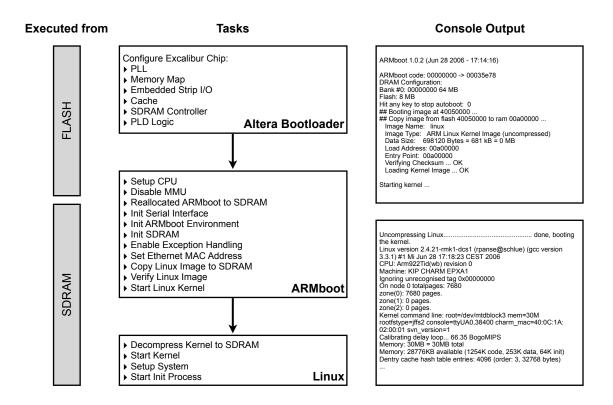

| 3.1          | Boot process of the CHARM. First, the boot loader is executed from flash. |                                                               |

|              | Afterwards, the boot code is copied to the SDRAM and is started from the  |                                                               |

|              | RAM. The console output of the CHARM is shown on the right side of the    |                                                               |

|              | picture.                                                                  | 36                                                            |

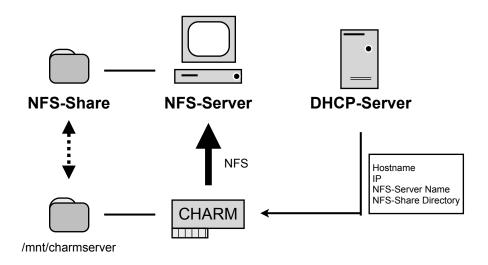

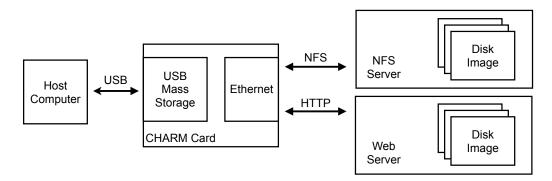

| 3.2          | CHARMs connects to the NFS-Server after boot up                           | 39                                                            |

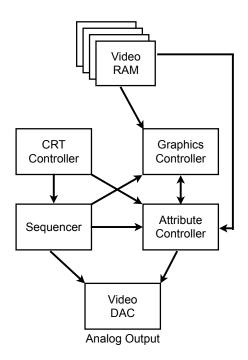

| 4.1          | Diagram of the VGA data processing. The arrows describes the data flow    | 42                                                            |

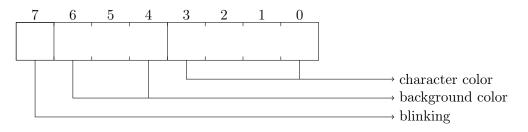

| 4.2          | Layout of the attribute byte                                              | 43                                                            |

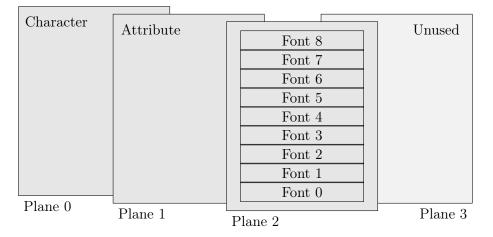

| 4.3          | Organization of the video planes in alphanumeric mode                     | 44                                                            |

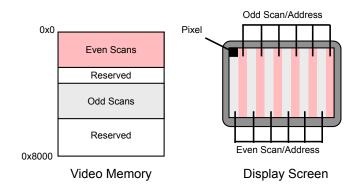

| 4.4          | The screen is divided into odd and even columns                           | 45                                                            |

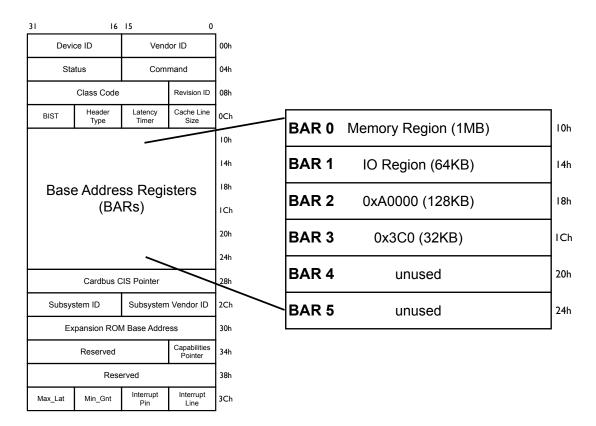

| 4.5          | PCI Configuration Space of the CHARM.                                     | 48                                                            |

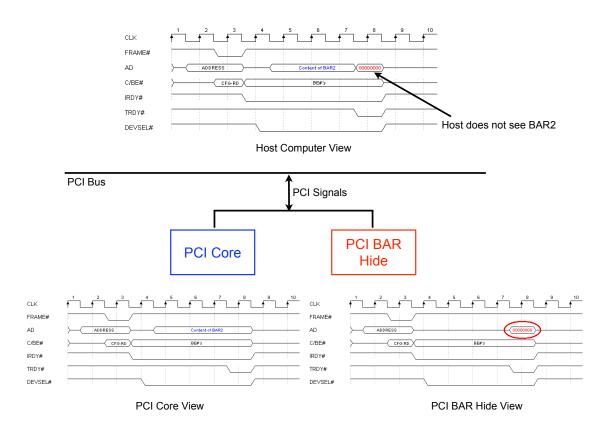

| 4.6          | PCI Configuration Space hiding.                                           | 49                                                            |

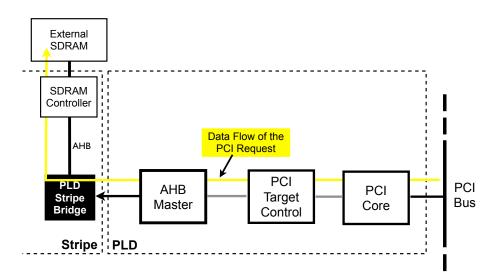

| 4.7          | Layout of the PCI processing units.                                       | 50                                                            |

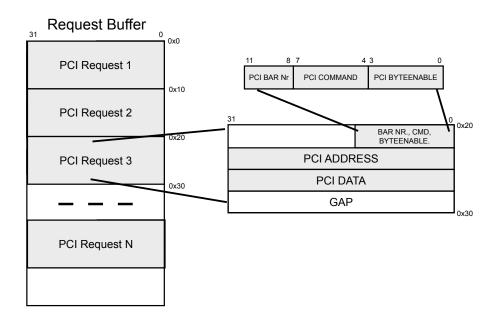

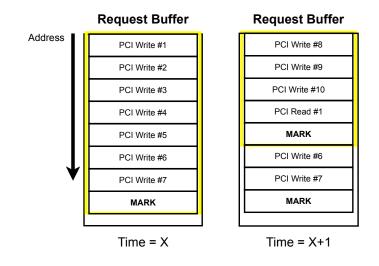

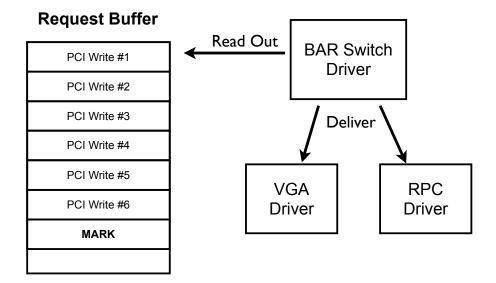

| 4.8          | Structure of the Request Buffer                                           | 51                                                            |

| 4.9          | Two sample Request Buffer contents. The yellow frames mark the valid      |                                                               |

|              | content of the buffer                                                     | 52                                                            |

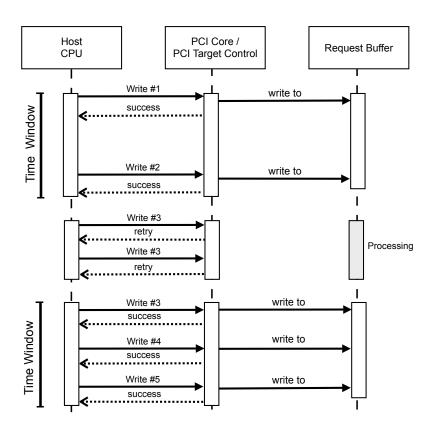

| 4.10         | Timing of the access to the Request Buffer.                               | 53                                                            |

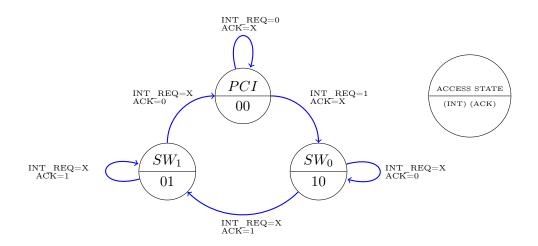

| 4.11         | <b>0</b>                                                                  | 54                                                            |

|              | Request Buffer access synchronization.                                    | 55                                                            |

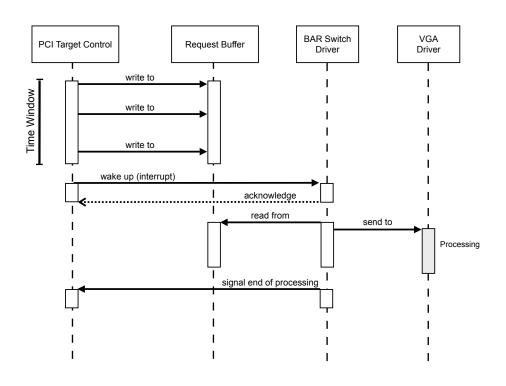

| 4.13         | Processing of the Request Buffer. The BAR Switch driver reads out the     |                                                               |

|              | content and distribute the data to the processing drivers                 | 56                                                            |

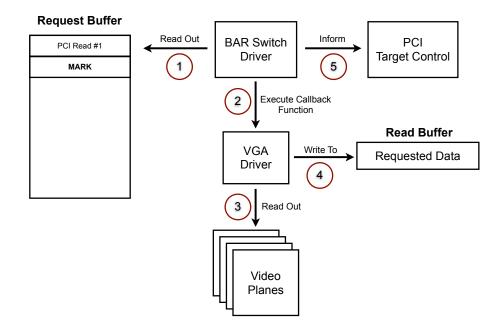

| 4.14         | Processing of read requests.                                              | 59                                                            |

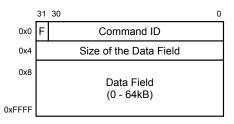

| 4.15         | Data format of a RPC message                                              | 61                                                            |

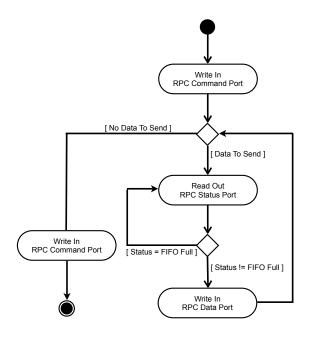

|              | Sending of an RPC message                                                 | 63                                                            |

| 4.17         | Receiving of an RPC message                                               | 63                                                            |

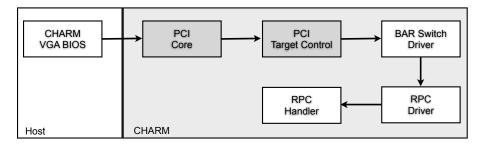

| 4.18         | Data flow of a host initiated RPC command. The dark boxes mark hardware   |                                                               |

|              | components and the white ones software units.                             | 64                                                            |

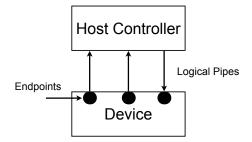

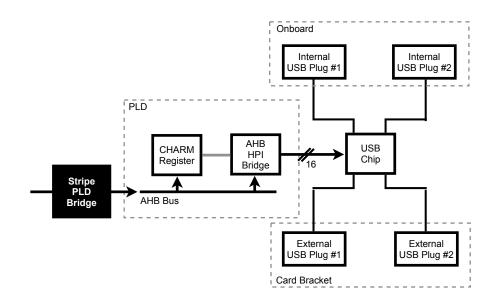

| $5.1 \\ 5.2$ | USB logical pipes                                                                                                                                                                                                                           | 66<br>69   |

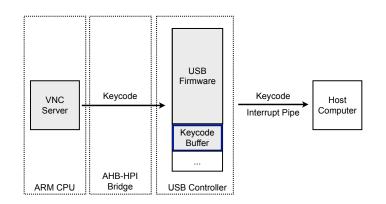

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 5.3          | USB keyboard implementation. The VNC server takes the user interaction<br>and converts it to USB keycodes. These keycodes are written into the keycode                                                                                      | 00         |

|              | buffer inside the USB controller.                                                                                                                                                                                                           | 70         |

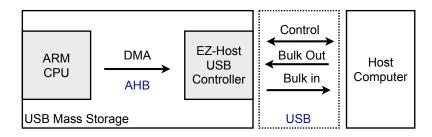

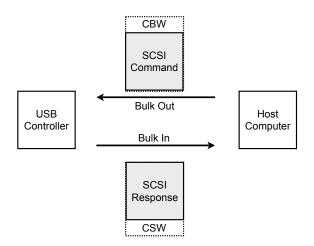

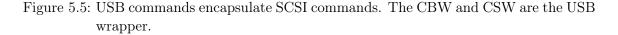

| $5.4 \\ 5.5$ | Overview of the processing units while mass storage emulation USB commands encapsulate SCSI commands. The CBW and CSW are the                                                                                                               | 70         |

| 5.6          | USB wrapper                                                                                                                                                                                                                                 | 71         |

|              | the processing steps.                                                                                                                                                                                                                       | 73         |

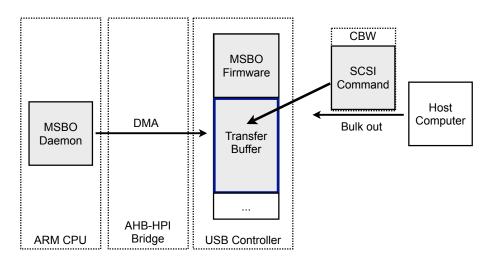

| 5.7          | Usage of the Transfer Buffer. The buffer contains the incoming USB requests.                                                                                                                                                                | 74         |

| 5.8          |                                                                                                                                                                                                                                             | 75         |

| 5.9          | Organization of the keyboard buffer of the BIOS                                                                                                                                                                                             | 77         |

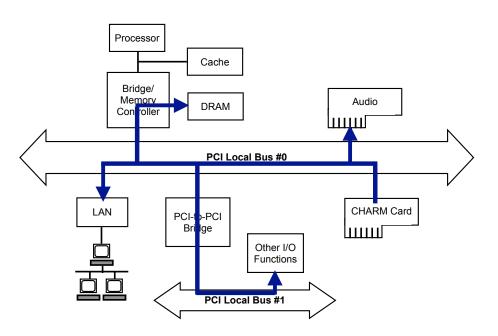

| 6.1          | The PCI bus provides the CHARM card access to the hardware units of the                                                                                                                                                                     | 01         |

|              | host computer.                                                                                                                                                                                                                              | 81         |

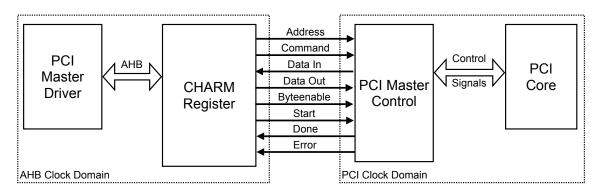

| 6.2          | Communication flow of the PCI Master driver.                                                                                                                                                                                                | 82         |

| 6.3          | Example content of a video plane                                                                                                                                                                                                            | 85         |

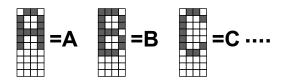

| 6.4          | Look up table of a font set.                                                                                                                                                                                                                | 85         |

| 6.5          | Screenshot of the boot screen of an HLT cluster node                                                                                                                                                                                        | 86         |

| 6.6          | Alphanumerical output of the screen content                                                                                                                                                                                                 | 86         |

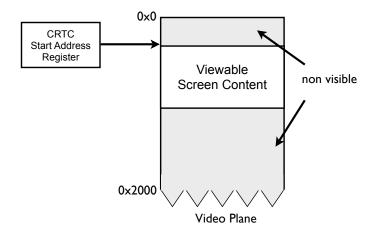

| 6.7          | Diagram of the viewable part of the video plane. Running an alphanumeric mode, the <i>CRTC Start Register</i> defines the start pointer of the current screen                                                                               |            |

|              | content                                                                                                                                                                                                                                     | 87         |

| 6.8          | Actual content of the screen                                                                                                                                                                                                                | 88         |

| 6.9          | Previous content of the screen.                                                                                                                                                                                                             | 88         |

| 6.10         |                                                                                                                                                                                                                                             | 88         |

| 6.11         |                                                                                                                                                                                                                                             | 91         |

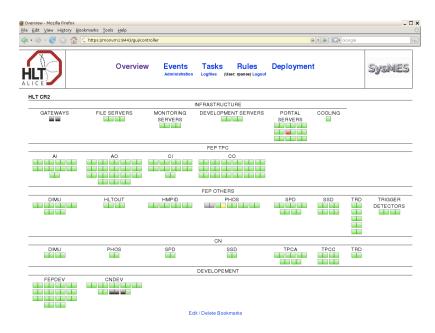

| 6.12         | Screenshot of the HLT SysMES GUI.                                                                                                                                                                                                           | 92         |

|              | Screenshot of the HLT SysMES GUI.                                                                                                                                                                                                           | 92         |

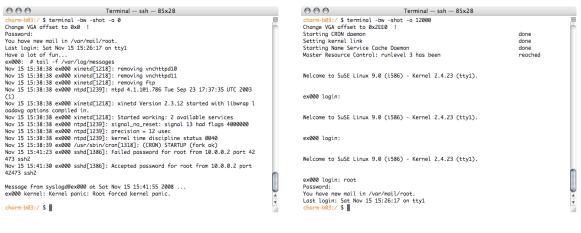

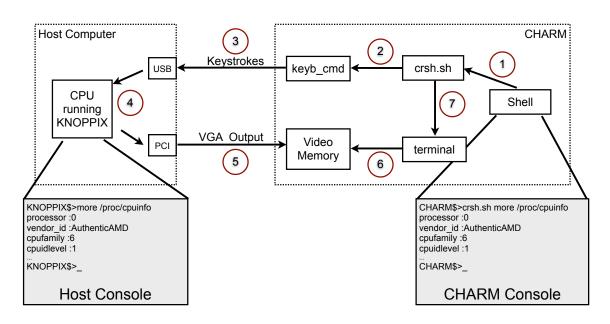

| 7.1          | Functional overview of the crsh.sh program. The red circles define the pro-<br>cessing order of the function units. On the right hand of the picture, a shell<br>console calling the crsh.sh program is shown. The left side of the picture |            |

|              | shows the screen content of the host computer.                                                                                                                                                                                              | 95         |

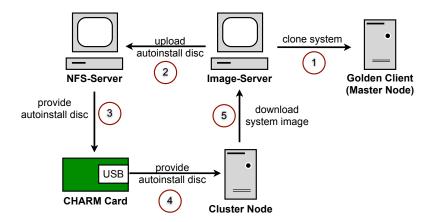

| 7.2          | Functional overview of the system installation of the HLT cluster nodes. The red circles define the process order of the system installation                                                                                                | 100        |

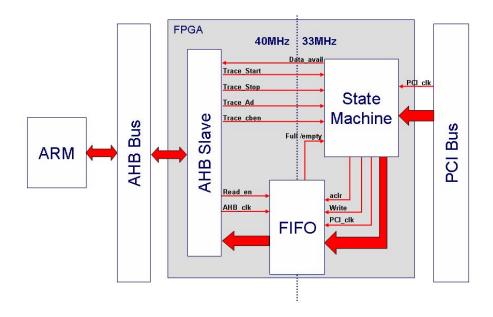

| 8.1          | Layout of the PCI bus analyzer design [2]                                                                                                                                                                                                   | 104        |

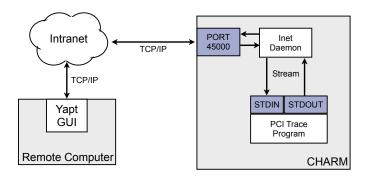

| 8.2<br>8.3   | Data flow of Yapt and the PCI trace program. The Inet daemon builds<br>a bridge between the TCP stream of the Yapt software and the standard                                                                                                | 106        |

| 8.4          |                                                                                                                                                                                                                                             | 107<br>107 |

| 0.4          | Layour of a metwork interface controller (MC)                                                                                                                                                                                               | LUI        |

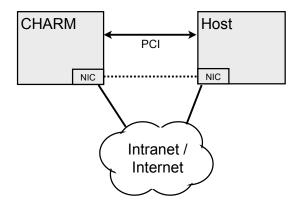

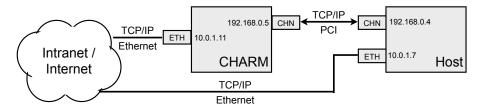

| 8.5        | CHARM-Host network communication. In principle, there is no direct net-<br>work connection between the host and the CHARM. But the PCI bus is used<br>to establish a network bridge between the CHARM and the host computer.                                                                                                                                                                                                                                                                                                                                                    | 108        |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 8.6        | Block diagram of the network function of the CHARM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 109        |

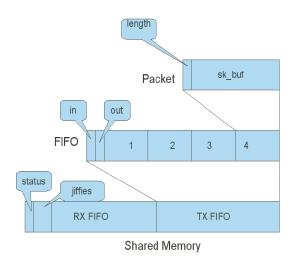

| 8.7        | Layout of the shared SRAM content [3]. The left side represents the lower addresses. The right side marks the end of the SRAM content.                                                                                                                                                                                                                                                                                                                                                                                                                                          | 110        |

| 8.8        | Network connection of the host computer by the aid of the CHARM card.<br>The used IP addresses in the picture are one example of a possible network<br>configuration.                                                                                                                                                                                                                                                                                                                                                                                                           | 111        |

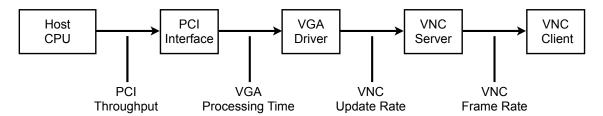

| 9.1        | VGA processing queue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 113        |

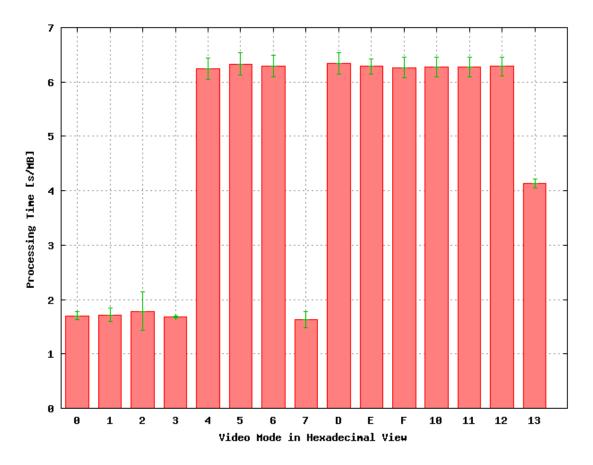

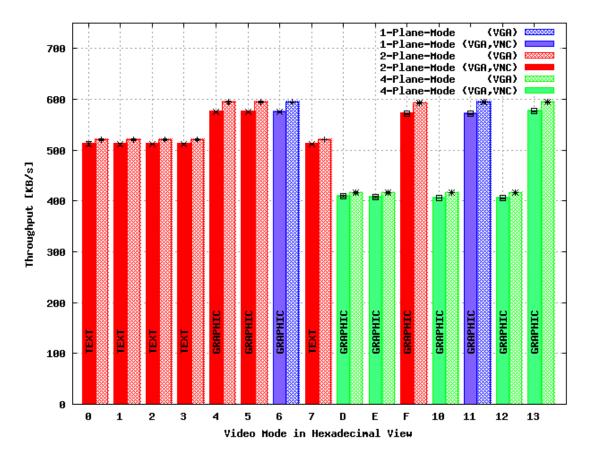

| 9.2<br>9.3 | Processing time of the Request Buffer in relation to the running video mode.<br>Write throughput to the CHARM card in relation to the running video mode.<br>The color of the bars represents the number of provided video planes of the<br>dedicated video mode. The bars filled with a pattern define the throughput of<br>the CHARM card without screen generation. The solid-colored bars represent<br>the throughput with a running VNC server generating the screen content.<br>Additionally, the bars are labeled with the type of video mode: text or graphic           | 118        |

| ~ .        | mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 120        |

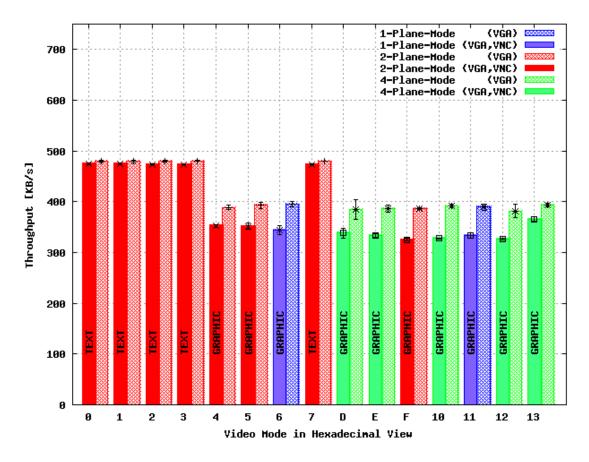

| 9.4        | Write throughput to the CHARM card in relation to the running video mode.<br>In this process, the processing VGA driver use the dirty-region function. The<br>color of the bars represents the number of provided video planes of the ded-<br>icated video mode. The bars filled with a pattern define the throughput of<br>the CHARM card without screen generation. The solid-colored bars rep-<br>resents the throughput with a running VNC server generating the screen<br>content. Additionally, the bars are labeled with the type of video mode: text<br>or graphic mode | 122        |

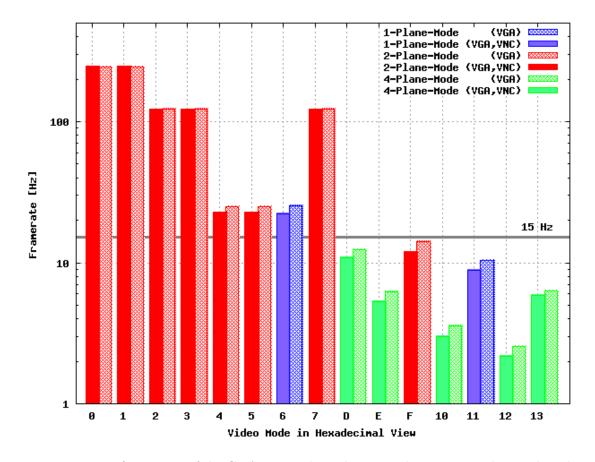

| 9.5        | Input frame rate of the CHARM card in relation to the running video mode.<br>The color of the bars represents the number of video planes used for the<br>dedicated video mode. The bars filled with a pattern define the input frame<br>rate of the CHARM card without screen generation. The solid-colored bars<br>represent the input frame rate with a running VNC server generating the                                                                                                                                                                                     |            |

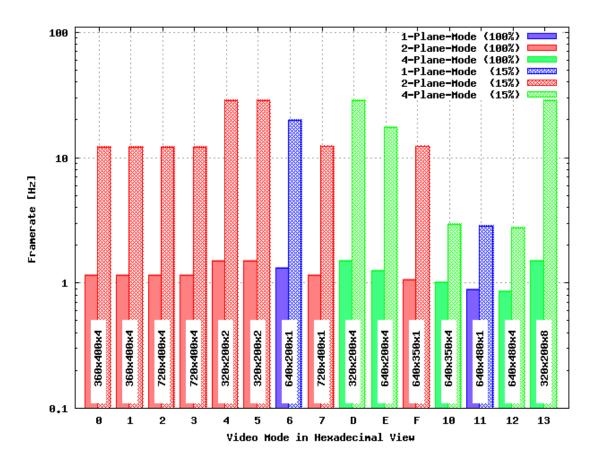

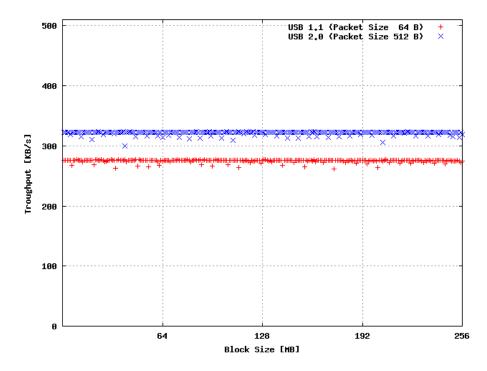

| 9.6        | screen content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 123<br>125 |

| 9.7        | Read throughput to the CHARM USB CD-ROM device corresponding to<br>the block size of the transfer. The color of the bars defines one of the USB                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

|            | packet sizes of the device: USB 1.1 (64 B) or USB 2.0 (512 B). $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 126        |

|     | CHARM card front view (model B)                                          |     |

|-----|--------------------------------------------------------------------------|-----|

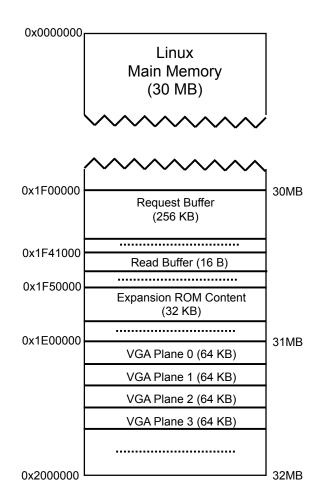

| E.1 | SDRAM address map.                                                       | 141 |

| G.1 | Test system #1 with an installed CHARM card. It is the topmost PCI card. | 145 |

# **List of Tables**

| $2.1 \\ 2.2$                                                   | Features of the FPGA used in the EPXA1 chip where LE means Logic Element.<br>CHARM PCI Base Address Register                                                                                                                                                                                                                                                    | 31<br>33                         |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                         | Device driver of the CHARM                                                                                                                                                                                                                                                                                                                                      | 36<br>37<br>38<br>39<br>40<br>40 |

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \end{array}$ | VGA address window to access the framebuffer                                                                                                                                                                                                                                                                                                                    | 45<br>46<br>57<br>58<br>62       |

| $5.1 \\ 5.2 \\ 5.3 \\ 5.4$                                     | Partitions of the SRAM of the USB controller.                                                                                                                                                                                                                                                                                                                   | 68<br>71<br>72<br>76             |

| 6.1                                                            | Usage of the ADC ports                                                                                                                                                                                                                                                                                                                                          | 84                               |

| $7.1 \\ 7.2$                                                   | Principal tasks of the CHARM card while testing the HLT nodes                                                                                                                                                                                                                                                                                                   | 97<br>101                        |

| 8.1                                                            | Features of the CHARM PCI bus analyzer.                                                                                                                                                                                                                                                                                                                         | 104                              |

| 9.1                                                            | Typical periodical VGA access sequence of the AMI BIOS running a graphic mode. The first I/O write (to 0x3CE) is done once only. It sets up the target register for the I/O writes to port 0x3CF. The next three accesses are repeated periodically, whereas the memory addresses and values are changed. The idle time is the period between two VGA accesses. | 114                              |

| 9.2                                                            | VGA access sequence of a booting Linux kernel running a VGA text mode.                                                                                                                                                                                                                                                                                          |                                  |

| 9.3                                                            | The idle time is the period between two VGA accesses                                                                                                                                                                                                                                                                                                            | 115                              |

|                                                                | requests                                                                                                                                                                                                                                                                                                                                                        | 115                              |

| 9.4 | Performance of the CHARM VGA function. The transfer time is the period<br>of the successful PCI cycle. The CHARM cannot immediately accept data<br>after a data transfer. The dead time defines the period while the CHARM |     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | rejects PCI accesses.                                                                                                                                                                                                      | 116 |

| 9.5 | Power consumption and power limitation of the CHARM card                                                                                                                                                                   |     |

| B.1 | Characteristics of the CHARM                                                                                                                                                                                               | 133 |

| E.1 | AHB address map.                                                                                                                                                                                                           | 139 |

| E.2 | CHARM Register Map                                                                                                                                                                                                         | 140 |

| F.1 | USB controller firmware                                                                                                                                                                                                    | 143 |

| F.2 | USB controller firmware (continued)                                                                                                                                                                                        | 144 |

| G.1 | Test system $\#1$                                                                                                                                                                                                          | 145 |

| G.2 | Test system $#2$                                                                                                                                                                                                           | 145 |

| G.3 | Mainboards which support the CHARM                                                                                                                                                                                         | 146 |

| H.1 | VGA video modes.                                                                                                                                                                                                           | 147 |

| H.2 | VGA I/O Ports.                                                                                                                                                                                                             | 148 |

# **1** Introduction

At present, computer clusters<sup>1</sup> are the predominant construction type of supercomputer installations. They are used in a wide range of applications like web search engines [4], weather forecasts [5], simulation of financial markets [6] and high energy experiments. The data analysis of future high energy experiments like CMS<sup>2</sup> and ALICE<sup>3</sup> are accomplished by computer clusters, for example. A driving force for the usage of computer clusters is the increased need of cheap computing power for computational science and commercial application. The traditional supercomputing platforms cause high costs and have a low availability, whereas clusters can be build up with cheap commodity-off-the-shelf (COTS) components and are readily available.

Clusters can consist of several hundreds of computer nodes. For example, the data center of a government agency in Sweden has a computer cluster of more than 2,000 nodes [9]. Hence, the management of those big computer farms requires a considerable amount of administrative effort: installation, configuration and maintenance. For installing one node and cloning its hard disk provides a fast and easy way to setup the cluster nodes. Afterwards, the files are copied from node to node. This can be done from a distance using the remote boot function of the network card. But in case the booting fails, one needs access to the console of the node to detect the source of the error and repeat the installation. Furthermore, commodity PCs normally do not provide remote access to the system without running an operating system [10]. This is the drawback using COTS instead of expensive server computers, which provide a wide range of remote control functions. There are a couple of remote management tools and devices which enable remote control features on a single computer. The following sections will discuss functions of those and the drawbacks of using them in a computer cluster. But either the existing remote management functions are designed for a specific computer system or they provide only a subset of remote control functions. This thesis describes a remote control and maintenance facility which was developed for the HLT<sup>4</sup> cluster of the ALICE experiment at CERN. The facility is installed to every cluster node and allows the remote control of economic COTS cluster nodes. Furthermore, it provides functions for the automation of the node administration. In addition, this hardware device monitors the computer and takes action when a failure is detected. A specific feature of this device is the possibility to access most of the hardware units of the host computer. Therefore, malfunctioning of computer nodes can be inspected more precisely.

<sup>&</sup>lt;sup>1</sup>Cluster is a collection of interconnected computers working together as a single system.

<sup>&</sup>lt;sup>2</sup>Compact Muon Solenoid [7].

<sup>&</sup>lt;sup>3</sup>A Large Ion Collider Experiment [8].

<sup>&</sup>lt;sup>4</sup>High Level Trigger.

### 1.1 Outline

The following sections give an overview about the target system of this thesis. They also discuss existing remote access tools for computer systems. The heart of the hardware based remote control presented in this thesis is the CHARM<sup>5</sup> PCI card which will be referenced simply as CHARM in the rest of the text. The features of the card are summarized in section 1.5.1. The architecture of the card is illustrated in chapter 2. The CHARM has its own operating system which controls the hardware units of its board. Chapter 3 discusses the operating system of the card. A central feature of the CHARM is the graphic card function. The CHARM replaces the primary graphic card of the computer. The reason of this approach and the implementation of the VGA function is explained in chapter 4. Chapter 5 illustrates the device emulation of the CHARM. It is used for the interaction with the host computer. Besides the remote access feature of the CHARM, the card also monitors the host computer. The monitoring capability of the card is illustrated in chapter 6. The CHARM can also be used for other applications than the remote control of a computer. Chapter 8 explains the other functions which were implemented with the CHARM. Experimental results and experiences with the CHARM are discussed in chapter 9. Chapter 10 summarizes the application of the CHARM and gives an outlook over the CHARM.

# **1.2 ALICE Experiment**

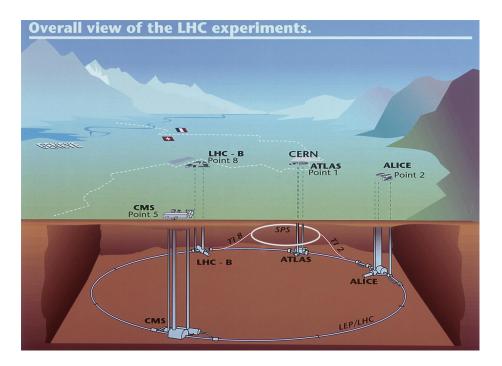

ALICE is one of the four experiments at the Large Hadron Collider (LHC) [11, 12]. The LHC is an accelerator ring which was built for the European Organization for Nuclear Research (CERN). Figure 1.1 shows the LHC ring and the location of the main experiments: CMS, ATLAS<sup>6</sup>, ALICE, LHCb<sup>7</sup>. The aim of ALICE is to study the physics of strongly interacting matter at extreme energy densities, where the formation of a new phase of matter, the quarkgluon plasma, is expected. In the ALICE experiment lead ions collide at a total center of mass energy of 1148.0 TeV [12]. The ALICE setup includes a variety of detectors focusing on different particle properties. The biggest data source of ALICE is the time projection chamber (TPC) which is being readout at a rate of up to 200 Hz [12]. Every such event is about 82 MB in size. The most interesting events are selected by the so-called trigger system. This approach optimizes the usage of the data bandwidth of the detector.

The ALICE trigger system is separated into four levels: Level-0, Level-1, Level-2 and the High-Level Trigger(HLT) [12, 15]. They differ by the amount of data on which the decision is based and by the complexity of the data analysis.

# 1.3 HLT Computer Cluster

The HLT is designed to analyze LHC events produced in the ALICE detector in an online matter [16, 17]. The heart of the HLT consists of a computing cluster of several hundreds of dual-processor nodes [18]. The nodes will be connected via Gigabit Ethernet [19]. Figure

$<sup>^5\</sup>mathrm{Computer}$  Health and Remote Management

<sup>&</sup>lt;sup>6</sup>A Toroidal LHC Apparatus [13].

<sup>&</sup>lt;sup>7</sup>Large Hadron Collider beauty [14].

Figure 1.1: Overview of the LHC ring at CERN.

1.2 shows several HLT cluster nodes in the ALICE counting room. The current setup of the cluster installed at CERN contains approximately a quarter of the foreseen nodes (>100). The installation and administration of such a big computer farm is an extensive task. Therefore, automatization of periodically task is highly recommended. Another issue to be performed on the HLT cluster is the remote control of its nodes. The counting rooms of the HLT are located near the ALICE detector. During beam time, the access to these rooms is restricted and the computer cluster must be controlled remotely. The failed computers have also to be fixed by remote control. Especially the front end processors (FEP) which get the raw data from the detector have to run in any case. Normally, an FEP node cannot be exchanged by a redundant node, because the node is directly connected with the detector via an optical link. A broken FEP node has to be replaced completely with a new computer at the same physical location.

At the beginning planning stage of the HLT, the model or type of PCs for the cluster was not specified. To get a good price-performance ratio, the PCs should be purchase as late as possible. An important aspect of the cluster node was to provided a good throughput and compatibility for the Read Out Receiver Cards (RORC) [20]. These cards connect the detector with the HLT. Unfortunately, the computers which are suited for the RORC do not provide a built-in remote control which fulfills our requirements. To be as flexible as possible the CHARM was developed to provided full remote control of the cluster nodes independent of the final solution adopted for the computer components.

The following section summarizes common remote management facilities. The hardware based remote control tools will be especially discussed whether it can be used for the HLT.

#### 1 Introduction

Figure 1.2: The HLT cluster nodes.

## 1.4 Remote Management Tools

Remote management tools are used to remotely connect and manage a single or multiple computers. There are a couple of software and hardware based remote management and remote control tools on the market. Remote control software are widespread to any operating systems. SSH [21] and Telnet [22] are two of the best known remote access tools. They provide console-based access to a remote computer, whereas graphical access can be obtained with the Remote Desktop Protocol (RDP) [23] from Microsoft or the Remote Framebuffer (RFB) protocol [24] maintained by RealVNC Ltd for example. Therefore, it is not necessary to work in front of a server computer or a computing node in a cluster system. However, if the operating system has failed, the software based remote access tools fail, too. Furthermore, as a general rule the BIOS of a PC does not provide remote control software. Hardware based remote maintenance closes the gap between the remote control software. The following section describes common remote control techniques and components usually used in cluster administration.

### 1.4.1 KVM

The most simple way to provide remote control of a computer system is the use of a KVM<sup>8</sup> over IP<sup>9</sup> devices. It replaces the local monitor and the local keyboard. The KVM device has to be connected to the graphic card and to a serial port. The built-in Ethernet interface

$<sup>^{8}</sup>$ Keyboard/Video/Mouse, a hardware device that allows a user to control multiple computers from a single keyboard, video monitor and mouse.

<sup>&</sup>lt;sup>9</sup>Internet Protocol [25].

of the device provides access to the serial port to emulate keystrokes or mouse movements. The screen content is fetched from the graphic card and provided to remote computers.

### 1.4.2 BIOS Console Redirection

The main-board manufactures equip their products with hardware based remote maintenance units. The remote console is one of the widespread remote access tools for computer systems. Thereby, one of the computer's serial interfaces provides access to the screen of the computer at boot time. However, the serial interface can only redirect text content but cannot send graphical content. The main usage of the console redirection is the remote configuration of the BIOS CMOS. But to use this feature a serial to Ethernet adapter has to be plugged into the serial port of the host computer.

### 1.4.3 IPMI

The Intelligent Platform Management Interface (IPMI) specification defines a set of common interfaces to the platform management subsystem of a computer system [26, 27]. These interfaces are used to monitor the health of a system and manage it. The first IPMI specification was announced in the year 1998 by Dell, HP, Intel Corporation and the NEC Corporation [26]. The key characteristic of the IPMI is that the main control functions are available independently of the main processor. Therefore, the IPMI operates independently of the operating system (OS) and allows administrators to manage a system remotely even in the absence of the OS. The heart of the IPMI architecture is the Baseboard Management Controller (BMC) [27]. It provides the intelligence behind intelligent platform management. The BMC controls the interface between system management software and platform management hardware. Additional management controllers can be connected to the BMC using the IPMB which is a serial bus used for communication to and between management controllers [26].

#### 1.4.4 Remote Management Cards

KVM devices or the console redirection feature do not support the installation of an operating system in a remote way, because they do not provide boot device. As a general rule, critical servers are equipped with a remote management card or an onboard remote management utility. They provide features beyond of KVM function. The most of the remote management cards support a wide variety of management issues as for example a separate network connectivity through a built-in network adapter, a browser (http and https) accessible management interface, hardware event logging, terminal access to system console, providing a boot device, separate power source, restart, power up and power down features. As a general rule, remote management cards are out-of-band management utilities which use a dedicated management channel [28]. It provides remote control of a computer system regardless of whether the machine is powered on. In contrast, an in-band management utility is the use of regular data channels.

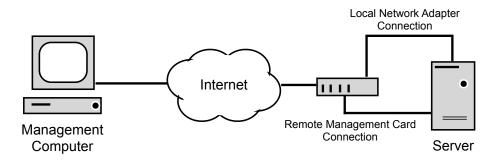

Figure 1.3 depicts a typical setup of a server managed remotely. The remote management card could either share the same network environment as the host system or use a separate

#### 1 Introduction

one. A separate network environment has the advantage to provide a secure remote interface to the Internet, while the servers are only accessible via the local network.

Figure 1.3: Remote management of computer systems.

Currently on the market there are several remote management cards as Peppercon eRIC II [29], AMI MegaRAC<sup>®</sup> G4 [30] and TYAN SMDC M329 [31]. They differ in functionality and functioning. The next paragraphs explain these cards more precisely.

**Peppercon eRIC II** The eRIC II is a KVM-over-IP PCI card that provides browser-based remote access and control to any server [29]. It has an onboard VGA controller which replace the primary graphic card of the host computer. The screen content is accessible via an embedded web server running on the card. However, this card has no POST<sup>10</sup> code analyzer. Furthermore, eRIC II does not provide own monitoring sensors to measure temperature or fan speed.

**AMI MegaRAC® G4** The MegaRAC G4 manufactured by American Megatrends Inc. is a PCI card that can be installed onto regular server platforms or into blade servers [30]. It implements KVM over LAN<sup>11</sup>. The display screen is redirected from the VGA interface of the host computer to a remote PC. The MegaRac G4 has similar features as the eRIC II card, but it differs in that it does not have an onboard VGA chip. All monitoring features of the card requires an IPMI<sup>12</sup> connection to the motherboard.

**TYAN SMDC M3291** In contrast to the MegaRAC and the eRIC express which serve for a wide range of types of mainboards, the SMDC M3291 card was especially developed for TYAN mainboards [31]. TYAN's Server Management Daughter Card (SMDC) is no peripheral card. The connections between the card and the mainboards are established by ribbon cables instead of the card's edge connector [32]. The card has no physical connection to the graphic card. Instead it uses the console redirection feature of the BIOS to provide remote console access. The SMDC provides remote system monitoring and controlling via the IPMI over LAN interface.

$<sup>^{10}\</sup>mathrm{Power}$  On Self Test. It is explained in section 6.1.

<sup>&</sup>lt;sup>11</sup>Local Area Network.

<sup>&</sup>lt;sup>12</sup>Intelligent Platform Management Interface.

# 1.5 CHARM Card

Common remote maintenance devices use existent management facilities of the main-board. For the most part the devices access the BMC of the main-board via an IPMB. The absence of an IPMB limits the features of the device or makes these devices unusable. Furthermore, the most remote control devices provide solely a KVM function. In addition, monitoring features or capabilities to inspect the computer are missing on the remote control cards. The CHARM was developed to archive the required remote access, monitoring and diagnose capabilities of a cluster of computers such as the HLT. The CHARM is a low profile PCI expansion card and it is installed to every node in the cluster (figure B.1 and B.2 of the appendix B shows an image of the card). Thereby, the card can be used independently of the computer model or hardware architecture. The sole requirement for the CHARM is the existence of a Conventional PCI bus. The card combines a number of features needed for the remote control and remote diagnose of computer systems which are introduced in the next paragraphs.

### 1.5.1 Features of the CHARM

The CHARM operates entirely independently of the PC and can remain powered while the PC may even be powered down. In view of the fact that the CHARM runs with its own operating system, it can offer a wide range of automatization features, including automatic installation of the operating system, changing BIOS settings or booting a rescue disk. There is no need for an administrator to process these tasks. Additionally, the card provides monitoring and diagnostic features like temperature measurement and POST code analysis [33]. The board of the CHARM contains several multipurpose interfaces which are adjustable to later requirements. For example, the BIOS setting of the FEPs' mainboards have to be cleared via a jumper after a BIOS update. The mainboard manufacture does not guarantee a runnable system after a BIOS update if the BIOS setting is solely cleared by the BIOS update utility. A cable can be connected from the CHARM to the clear switch in order to reset the BIOS setting by remote control.

The following list gives an overview of the features of the CHARM:

- KVM function.

- Inspecting of the screen content.

- Providing of a boot device via USB.

- Remote power control of the host computer.

- Temperature monitoring with own sensors.

- Fan speed measurement.

- PCI voltage measurement.

- Read out of the CMOS and DMI<sup>13</sup> contents.

<sup>&</sup>lt;sup>13</sup>Desktop Management Interface.

- Detection of the PCI devices via PCI bus scanning.

- PCI master capability to read out the host computer's memory space.

- Reconfiguration to change the function of the card, if needed.

- Operating system Linux.

- Automatic installation and configuration of the host computer.

### 1.5.2 Usage of the CHARM

A couple of standard interfaces provide access to the CHARM and the usage of its functions. The card can be used via SSH, VNC or HTTP. The SSH port provides access to the Linux system of the CHARM. Most of the features of the CHARM can be accessed inside a console. A list of the console applications of the CHARM can be found in the appendix C. The KVM function of the card is established by a VNC server. It provides the screen content of the host computer (see figure 1.4). The way the CHARM obtains the screen content of the host is illustrated in chapter 4. Keyboard or mouse interactions inside a remote VNC session are converted into keystrokes and mouse movements at the host computer system. Chapter 5 explains the method used for device emulation.

Figure 1.4: Screenshot of a VNC session while setup the BIOS settings with the aid of the CHARM.

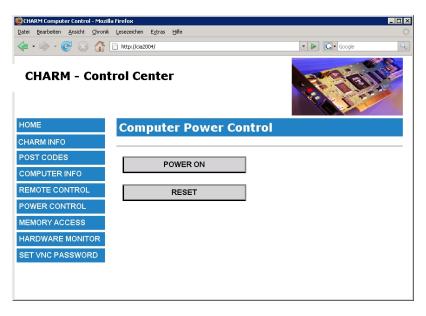

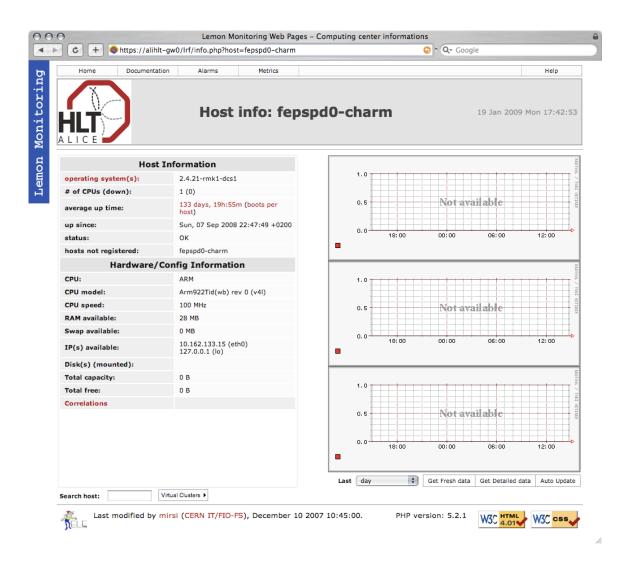

The main function of the CHARM can also be used via a web server which runs on the card (see figure 1.5). It provides information about the CHARM like the  $MAC^{14}$ , the IP,

<sup>&</sup>lt;sup>14</sup>Media Access Control (MAC) is an identifier assigned to most network adapters.

the host name and the revision date of the card. Additionally, the last ten POST codes of the host computer (see section 6.1 to get more information about POST) are shown on a web page. The CHARM can obtain real time information of the host computer like the BIOS CMOS content or the PCI device list. This information is also provided by the web server. Furthermore, an embedded Java VNC applet provides an interactive remote access to the host computer. The sensor information of the CHARM like the PCI voltage, the temperature and the fan speed are also shown on a web page.

Figure 1.5: Screenshot of the web page provided by the CHARM.

# 2 CHARM Architecture

This chapter explains the hardware units and their organization on the CHARM. Section 2.1 gives an overview of the board architecture. Afterwards, the hardware units are explained through section 2.2 to section 2.3.

## 2.1 Overview of the CHARM Board

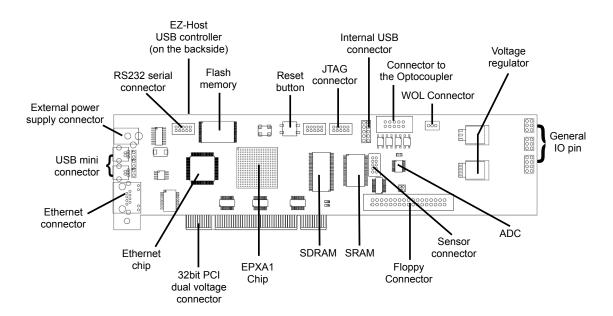

The different hardware components that form the CHARM system are mounted in a multi chip module board which PCB<sup>1</sup> consists of 8 layers. As control policy, controlling the devices, an embedded system is running on the hard-core CPU [34] implemented on the board. Thereby, an FPGA device [35] contains the control logic for the interfaces between the processotar and the hardware of the board. The CPU and the FPGA a part of the Excalibur chip from Altera [1] which is used on the CHARM. Figure 2.1 shows the layout of the CHARM board and the different hardware units which are explained next in the text.

Figure 2.1: Layout of the CHARM board.

<sup>1</sup>Printed Circuit Board.

**RS232 connector** The RS232 connector provides access to the operating system of the card.

**EZ-Host USB Controller** The USB controller is used to emulated peripheral devices to the host computer. It is explained with more detail in section 5.1.2.

**Flash Memory** The flash memory is the sole nonvolatile memory of the CHARM. It contains the kernel of the embedded system, the root file system and a configuration file for the FPGA.

**Reset Button** This button resets the board units and reboots the system.

**JTAG Connector** The card is programmed with the aid of the JTAG connector. It is directly connected to the Excalibur chip which provides write access to the flash memory. Therefore, the flash memory can be written via the JTAG interface.

**Internal USB Connector** To reduce cabling at the backside of the computer, the CHARM contains onboard USB connectors. The USB cable connects the CHARM board directly with the computer's main-board (if the main-board supports internal USB connections).

**Connectors to the Optocoupler** Optocouplers are used for the galvanically separation of electric circuits. The CHARM uses optocoupler for the power and reset switch of the mainboard. The power control of the host system is explained in section 5.3.

**WOL Connector** Wake On LAN (WOL) connector provides a standard interface for a standby power source. Some mainboards are equipped with a WOL connector which is used by network cards. With the aid of the WOL connection, the network card remains powered if the host system is going to be switched off. Additionally, the network card can power on the computer via the WOL connection.

**General I/O Pins** These pins are not used for a special purpose. They can be used for later requirements, like an input for the chassis power button or a connection to the mainboard CMOS reset switch, for example.

**ADC** The onboard analog-digital converter measures the PCI voltage and the temperature. The usage of the ADC is explained in section 6.2.3.

**Floppy Connector** Since the CHARM emulates an USB mass storage device, the floppy connector for floppy drive emulation is not used.

**Sensor Connector** Temperature and additional voltage sensors are connected to the sensor connector. The PCI voltage is measured onboard and does not require an external sensor.

**SRAM** The SRAM is used for fast data storage of the FPGA unit.

**SDRAM** The SDRAM is the main memory of the embedded system.

**Excalibur EPXA1 Chip** The EPXA1 contains the CPU and an FPGA unit. It is illustrated in section 2.2.

**32 bit PCI Connector** The card can be plugged into any PCI or PCI-X slot. Bus switches allow to use the card with 5V and 3.3V PCI slots.

**Ethernet Chip** An 10/100 MBit Ethernet chip provides the network interface of the CHARM.

**USB Mini Connector** The USB mini connectors provide an external USB connection from the CHARM to the host computer. They are used if the host computer does not provide an internal USB interface.

**External Power Connector** Besides PCI and WOL, the CHARM can be powered via a separate power supply.

# 2.2 Excalibur Chip

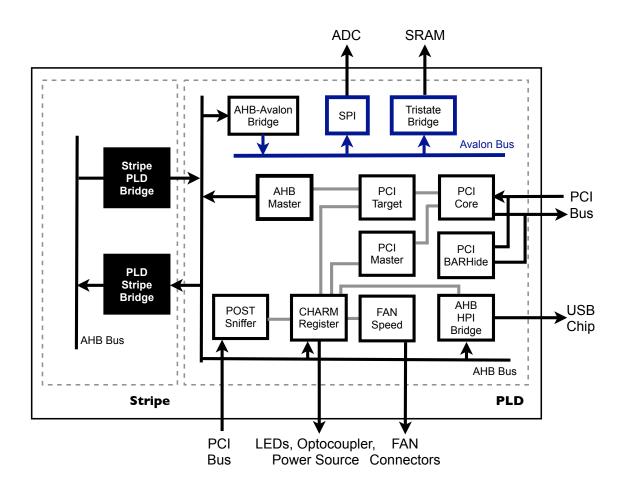

The processing unit of the CHARM is the Excalibur chip [1] of the Altera Corporation [36]. The CHARM uses the EPXA1 chip of the Excalibur family. It contains a hard-core processor and an FPGA unit. The embedded ARM processor operates with a frequency of up to 200 MHz. An AMBA<sup>2</sup> AHB<sup>3</sup> bus combines the processor with the FPGA. Additional you can interconnect SDRAM and flash memories, an Ethernet chip or other external devices to the internal bus system. The Excalibur chip is divided into the *Embedded Stripe* and the PLD array (FPGA).

### 2.2.1 Embedded Stripe

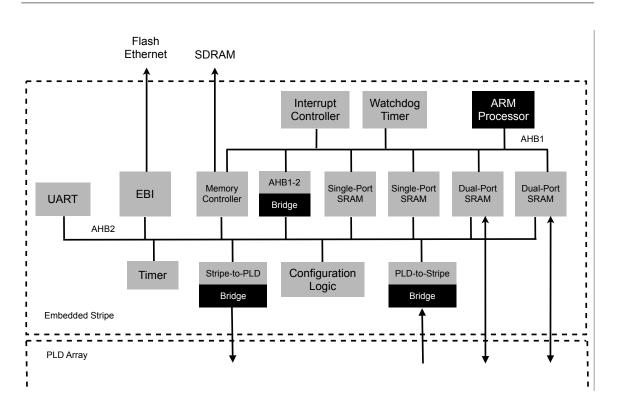

The embedded stripe is the part of the Excalibur chip which contains the peripherals, memory subsystem and the processor core. Figure 2.2 shows the structure and organization of the design components which conform this submodule.

The main system bus of the Excalibur chip is the AHB bus and it is divided into two parts: a fast bus system clocked with the frequency of the ARM processor named AHB1 bus and the AHB2 bus which is clocked with the half of the AHB1 frequency. The AHB system is connected to other bus systems to access the hardware units of the CHARM. The address mapping of the bus systems can be found in the appendix E. The SDRAM module of 32 MB installed on the CHARM is directly connected to the Excalibur device.

<sup>&</sup>lt;sup>2</sup>Advanced Microprocessor Bus Architecture.

<sup>&</sup>lt;sup>3</sup>Advanced High-Performance Bus is a high-performance bus developed by ARM Ltd [37].

Figure 2.2: Structure of the Excalibur Embedded Processor Stripe [1].

The internal SDRAM controller is connected to the AHB bus system. The Ethernet chip and the two 8 MB flash devices are accessible by the EBI<sup>4</sup> bus. The EBI bus is independent of the AHB bus and is synchronized internally with the AHB bus. The FPGA logic is addressable via the AHB-PLD bridge. The internal SRAM entities of the Excalibur device are not used by the CHARM. The FPGA logic is also synchronized with the AHB bus. This is done by the PLD-Stripe-Bridge.

### 2.2.2 ARM922T CPU