#### INAUGURAL-DISSERTATION

ZUR

Erlangung der Doktorwürde

DER

NATURWISSENSCHAFTLICH-MATHEMATISCHEN

GESAMTFAKULTÄT

DER

RUPRECHT-KARLS-UNIVERSITÄT HEIDELBERG

> vorgelegt von Dipl.-Phys. Edgar Sexauer aus Kenzingen

Tag der mündlichen Prüfung: 10.1.2001

## DEVELOPMENT OF RADIATION HARD READOUT ELECTRONICS FOR LHCb

#### Gutachter:

Prof. Dr. Karl-Tasso Knöpfle

Prof. Dr. Volker Lindenstruth

# Dissertation submitted to the Combined Faculties for the Natural Sciences and for Mathematics of the Rupertus Carola University of Heidelberg, Germany for the degree of Doctor of Natural Sciences

## DEVELOPMENT OF RADIATION HARD READOUT ELECTRONICS FOR LHCb

presented by Diplom-Physicist Edgar Sexauer born in Kenzingen, Germany

Heidelberg, 10.1.2001

Referees:

Prof. Dr. Karl-Tasso Knöpfle Prof. Dr. Volker Lindenstruth

#### **Zusammenfassung:**

Das Experiment LHCB am CERN ist zur Zeit in der Entwicklungsphase und hat zum Ziel, CP-Verletzung im System der B-Mesonen mit sehr hoher Präzision zu messen. In dem Experiment wird ein mit Silizium-Mikrostreifenzählern ausgestatteter Vertex-Detektor eingesetzt. Ein Mikrochip, der für die Auslese dieser Detektorkomponente geignet ist, wurde in einer Arbeitsgruppe im ASIC-Labor Heidelberg entwickelt.

Dieser Auslesechip Beetle-1.0 besteht aus 128 analogen Eingangsstufen mit einem ladungsempfindlichen Vorverstärker, einem Pulsformer und einer Treiberstufe. Das analoge Signal wird auf einen Komparator geführt, von dem ein schnelles Triggersignal abgeleitet werden kann. Der darauf folgende Ringspeicher (aufgebaut als Matrix von Gate-Kapazitäten) kann entweder zur Speicherung des analogen Signals der Eingangsstufe oder zur Speicherung des digitalen Ausgangs des Komparators benutzt werden. Ein externes Triggersignal markiert Ereignisse, die ausgelesen werden sollen, wobei die zugehörige Stelle in dem Ringspeicher in einem Derandomizer abgelegt wird. Markierte Ereignisse werden mittels einem rücksetzbaren ladungsempfindlichen Verstärker ausgelesen. Ein analoger Multiplexer, der die Signale abhängig vom Aulesemodus im Verhältniss 32:1, 64:1 oder 128:1 seriell weitergibt, schliest sich daran an. Durch einen Stromtreiber werden die Daten von dem dem Chip ausgegeben.

Beim Einsatz des Beetle im Vertexdetektor von LHCb muss er einer Strahlendosis von insgesamt 10 MRad standhalten. Dies wurde durch den Einsatz einer CMOS-Technology mit Strukturbreiten von  $0.25\,\mu\mathrm{m}$  sowie geschlossener Geometrie von nMOS-Transistoren erreicht.

Im Rahmen dieser Doktorarbeit wurden wesentliche Komponenten der analogen Auslesekette des Beetle-1.0 entworfen und getestet. Dazu wurde auf Ergebnisse von intensiven Messungen an dem Auslesechip HELIX128 zurückgegriffen. Ebenso wurden Teile des SCTA Auslesechips modifiziert, um diesen für das Experiment LHCb einsetzen zu können.

#### **Abstract:**

The experiment LHCb is under development at CERN and aims to measure CP-violation in the B-Meson system at very high precision. The experiment makes use of a vertex detector that is equipped with silicon microstrip detectors. A chip suitable for the readout of this detector has been developed in a working group at the ASIC-laboratory Heidelberg.

This readout chip 'Beetle-1.0' contains 128 analog input stages of a charge sensitive preamplifier, a pulse shaper and a buffer. The analog signal is fed into a comparator, from which a fast trigger signal can be derived. The following pipeline, realized as an array of gate capacitances, can be used to either store the analog output of the input amplifiers or to store the digital comparator output. External trigger signals mark events that have to be read out and the according pipeline location is stored in a derandomizing buffer. Pending events are read out from the pipeline via a charge-sensitive, resetable amplifier and an analog multiplexer, which serializes the signals with a factor of 32:1, 64:1 or 128:1, depending on the readout mode. The data are driven off-chip via a current buffer.

For the use of the Beetle in the vertex detector of LHCb, the chip has to withstand a radiation dose of about 10 MRad. This has been achieved by the use of a deep submicron CMOS with a feature size of  $0.25\mu m$  and an enclosed layout geometry of nMOS transistors.

In the context of this thesis, essential components of the analog readout chain of the Beetle-1.0 have been developed. For that, results of intensive measurements with the HELIX128 readout chip have been used. Also, parts of the SCTA readout chip have been modified to make it usable for the LHCb experiment.

## **Contents**

| 1 | LHO   | Cb: An l             | Experiment to Study CP-Violation in the System of $B$ -Mesons | 19 |

|---|-------|----------------------|---------------------------------------------------------------|----|

|   | 1.1   | Overvi               | ew of the LHCb detector [5]                                   | 19 |

|   | 1.2   | The Ve               | ertex Detector System of LHCb                                 | 21 |

|   |       | 1.2.1                | Layout of the Vertex Detector                                 | 21 |

|   |       | 1.2.2                | Pile-Up Veto Counter                                          | 21 |

|   |       | 1.2.3                | Silicon Detectors                                             | 22 |

|   |       | 1.2.4                | Radiation Fluxes in the Vertex Detector [1]                   | 24 |

|   |       | 1.2.5                | Electronic Readout                                            | 24 |

|   |       | 1.2.6                | Mechanical Support Structure                                  | 27 |

|   | 1.3   | The Tr               | igger System of LHCb                                          | 27 |

| 2 | Rad   | iation D             | Damage in Microelectronic Devices                             | 31 |

|   | 2.1   | Introdu              | action                                                        | 31 |

|   | 2.2   | Radiati              | ion Damage in MOS Field Effect Transistors                    | 32 |

|   |       | 2.2.1                | Total Ionizing Dose Effects                                   | 32 |

|   |       | 2.2.2                | Single Event Effects (SEE)                                    | 39 |

|   | 2.3   | Radiati              | ion Damage in Bipolar Transistors [11, 16]                    | 42 |

|   |       | 2.3.1                | Total Ionizing Dose                                           | 43 |

|   |       | 2.3.2                | Dependency on the Dose Rate [11, 12]                          | 43 |

|   |       | 2.3.3                | Displacement Damage                                           | 44 |

| 3 | Diffe | erent A <sub>l</sub> | pproaches towards Microstrip Readout Chips                    | 49 |

|   | 3.1   | Overvi               | ew                                                            | 49 |

|   | 3.2   | The HI               | ELIX128 Analog Readout Chip for HERA-B                        | 51 |

|   |       | 3.2.1                | Overview                                                      | 51 |

|   |       | 3.2.2                | The Architecture of the HELIX128                              | 51 |

|   |                      | 3.2.3    | Radiation Tolerance of the HELIX128                       | 52 |  |  |  |

|---|----------------------|----------|-----------------------------------------------------------|----|--|--|--|

|   | 3.3                  | The SO   | CTA Analog Readout Chip for ATLAS                         | 52 |  |  |  |

|   |                      | 3.3.1    | The BiCMOS SOI DMILL Process [13]                         | 53 |  |  |  |

|   |                      | 3.3.2    | Architecture and Radiation Hardness of the SCTA           | 54 |  |  |  |

| 4 | Beet                 | le - A R | Readout Chip suitable for LHCb                            | 57 |  |  |  |

|   | 4.1                  | Overvi   | iew                                                       | 57 |  |  |  |

|   | 4.2                  | Compa    | arison with other Readout Chips                           | 60 |  |  |  |

|   | 4.3                  | Radiat   | ion Hardening Methods                                     | 61 |  |  |  |

|   | 4.4                  | Layout   | t and Device Parameter Extraction of Enclosed Transistors | 62 |  |  |  |

|   |                      | 4.4.1    | Extraction of the Aspect Ratio                            | 62 |  |  |  |

|   |                      | 4.4.2    | Output Conductance                                        | 63 |  |  |  |

|   | 4.5                  | Analog   | g Stages                                                  | 63 |  |  |  |

|   |                      | 4.5.1    | Frontend                                                  | 63 |  |  |  |

|   |                      | 4.5.2    | Comparator                                                | 72 |  |  |  |

|   |                      | 4.5.3    | Pipeline                                                  | 74 |  |  |  |

|   |                      | 4.5.4    | Pipeline Readout Amplifier                                | 75 |  |  |  |

|   |                      | 4.5.5    | Multiplexer                                               | 77 |  |  |  |

|   |                      | 4.5.6    | Analog Output Buffer                                      | 79 |  |  |  |

|   | 4.6 Control Circuits |          |                                                           |    |  |  |  |

|   |                      | 4.6.1    | Pipeline Control Logic                                    | 80 |  |  |  |

|   |                      | 4.6.2    | I <sup>2</sup> C Interface                                | 80 |  |  |  |

|   |                      | 4.6.3    | Bias Generators                                           | 81 |  |  |  |

| 5 | Mea                  | sureme   | ent Results                                               | 85 |  |  |  |

|   | 5.1                  | Introdu  | uction                                                    | 85 |  |  |  |

|   | 5.2                  | Fronte   | nd Test Chip                                              | 85 |  |  |  |

|   |                      | 5.2.1    | Introduction                                              | 85 |  |  |  |

|   |                      | 5.2.2    | Transient Behavior                                        | 86 |  |  |  |

|   |                      | 5.2.3    | Frequency Behavior                                        | 87 |  |  |  |

|   |                      | 5.2.4    | Noise Performance                                         | 87 |  |  |  |

|   | 5.3                  | Bias G   | Generator Test Chip                                       | 89 |  |  |  |

|   |                      | 5.3.1    | Introduction                                              | 89 |  |  |  |

|   |                      | 5.3.2    | Current Source                                            | 89 |  |  |  |

|   |                      | 5.3.3    | Voltage DAC                                               | 90 |  |  |  |

|   |                      | 534      | Current DAC                                               | 90 |  |  |  |

#### A Pad Description

## **List of Figures**

| 1.1 | Schematic overview on the LHCb detector seen from above [5]                                                                                                                       | 20 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Schematic showing the strip layout of the $\phi$ - and $r$ -measuring detectors (left) and the arrangement of the detector stations in the vertex detector (right)                | 22 |

| 1.3 | Total particle flux (normalized to 1 interaction in the interaction point) at two stations of the Vertex Detector as a function of the distance to the beam axis [1]              | 25 |

| 1.4 | Side view of the vacuum tank and support structures for the Vertex Detector. The bottom half is omitted                                                                           | 27 |

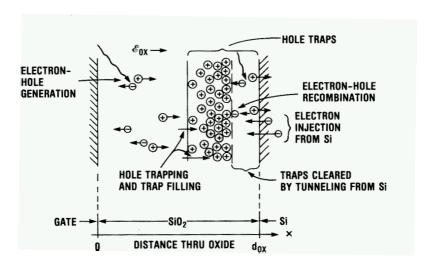

| 2.1 | Charge generation, distribution and trapping due to ionizing radiation in silicon oxide (e.g. in the thin oxide of a MOS transistor) [3]                                          | 33 |

| 2.2 | Schematic of hole trapping and removal in a MOS transistor at a positive gate voltage [3]                                                                                         | 34 |

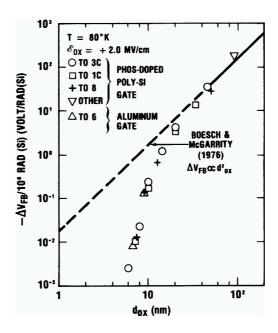

| 2.3 | Shift of the flat-band voltage as function of oxide thickness for various MOS structures. The solid/dashed line shows the expected $d_{ox}^{p}$ dependency for thicker oxides [3] | 35 |

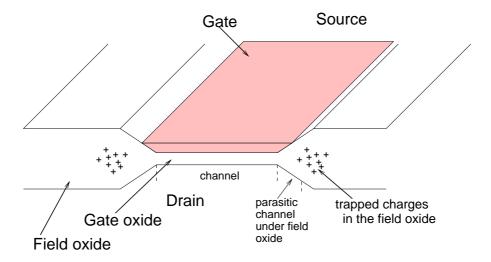

| 2.4 | Schematic view of the parasitic channel due to trapped holes in the field oxide of an nMOS transistor which gives rise to a parasitic leakage current                             | 36 |

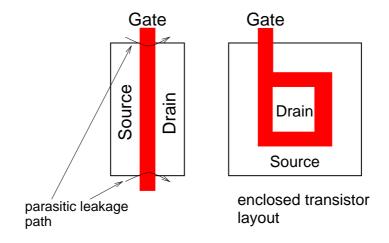

| 2.5 | The parasitic leakage path between source and drain as in a regularly laid out transistor (left) is prevented in an enclosed transistor layout (right)                            | 36 |

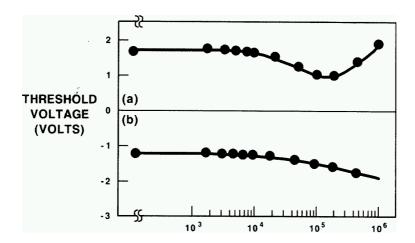

| 2.6 | Threshold voltage of an nMOS transistor (a) and a pMOS transistor (b) as a function of the total ionizing dose [3]                                                                | 37 |

| 2.7 | Normalized channel mobility as function of radiation induced interface trap density [8]                                                                                           | 38 |

| 2.8 | Schematic of the experimental setup for SEU cross section measurements [11]                                                                                                       | 40 |

| 2.9 | Typical result of an SEU cross-section measurement performed on the APV25 [9]                                                                                                     | 41 |

| 2.10 | of the MOS-transistor are not shown for simplicity                                                                                                                                            | 42 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.11 | Measurement of the $\beta$ -degradation with irradiation for different devices [11]                                                                                                           | 43 |

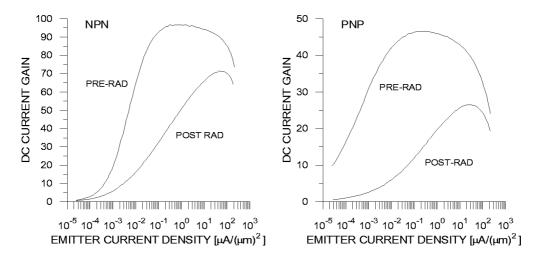

| 2.12 | DC current gain of NPN and PNP transistors before and after irradiation with protons of 800 MeV to a fluence of $1.2\cdot10^{14}cm^{-2}$ [16]                                                 | 45 |

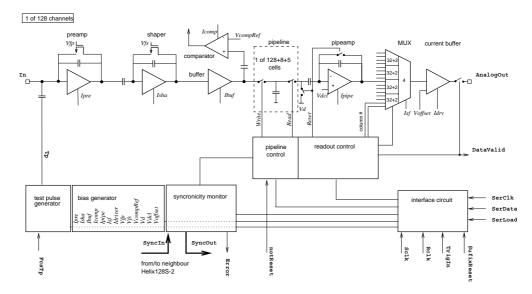

| 3.1  | Schematic overview on the architecture of the HELIX128 analog read-<br>out chip                                                                                                               | 52 |

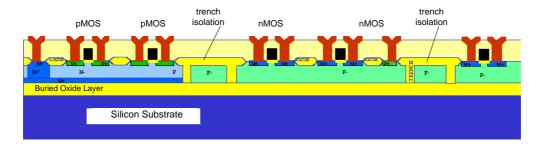

| 3.2  | Cross section of DMILL MOS devices and trench isolations                                                                                                                                      | 53 |

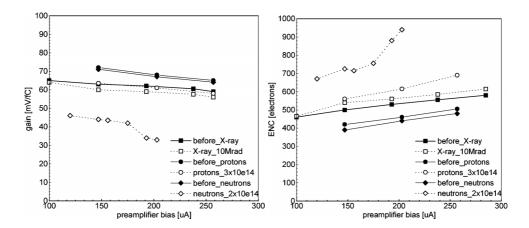

| 3.3  | Gain (left) and noise (right) as a function of the preamplifier current of the ABCD frontend, which is identical to the SCTA frontend [14]                                                    | 54 |

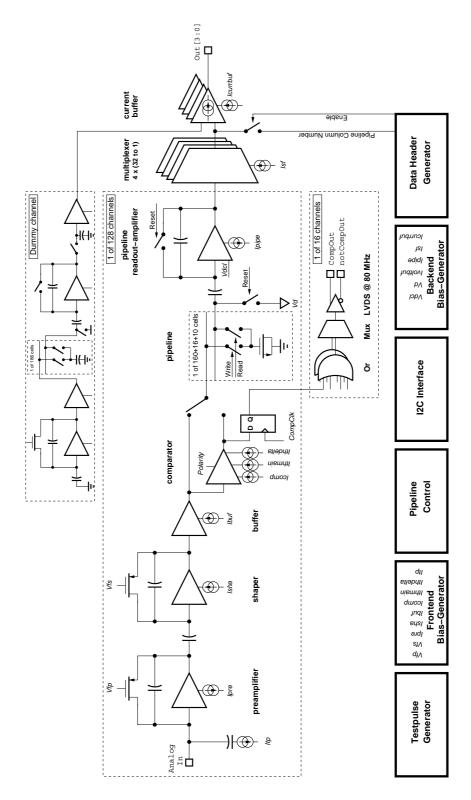

| 4.1  | Block diagram of the Beetle-1.0 readout chip                                                                                                                                                  | 58 |

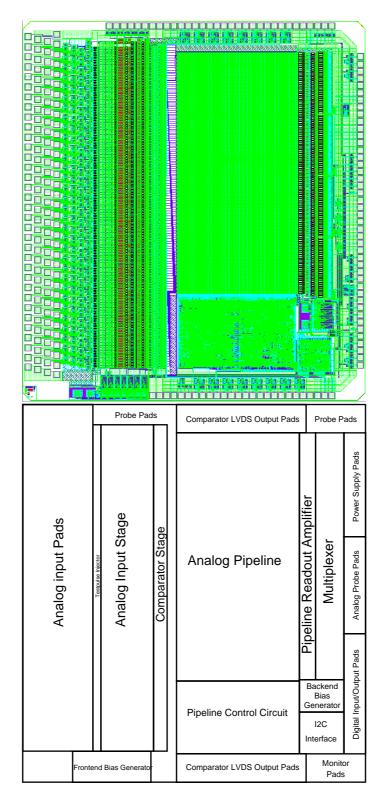

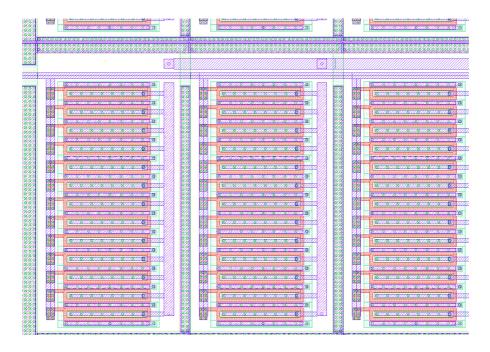

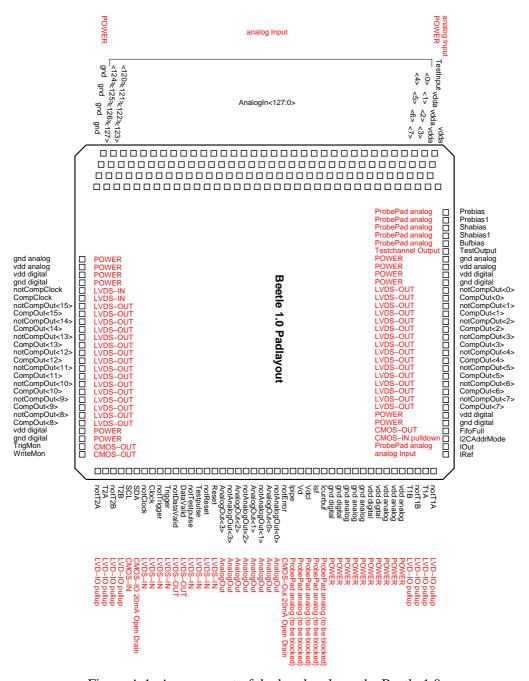

| 4.2  | Layout (top) and floorplan (bottom) of the Beetle-1.0 readout chip                                                                                                                            | 59 |

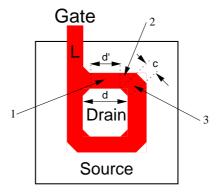

| 4.3  | Geometry of an enclosed transistor. The numbers point to the corresponding parts in eq. 4.1                                                                                                   | 63 |

| 4.4  | Noise sources in the charge sensitive preamplifier                                                                                                                                            | 64 |

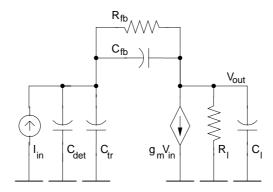

| 4.5  | Small signal model of the preamplifier                                                                                                                                                        | 66 |

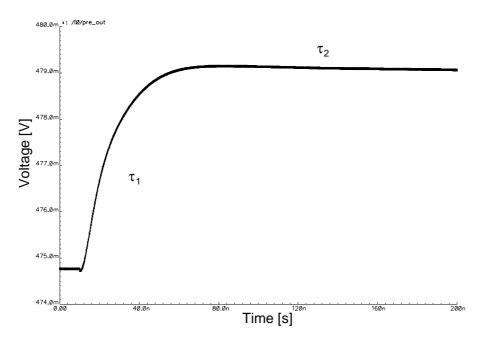

| 4.6  | Simulated output of the preamplifier. The two time constants are represented by $\tau_1$ and $\tau_2$                                                                                         | 67 |

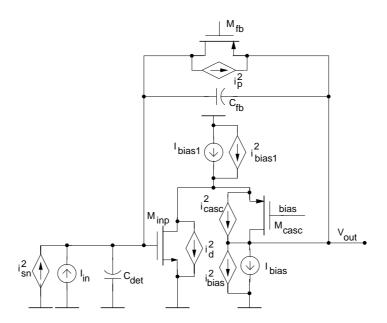

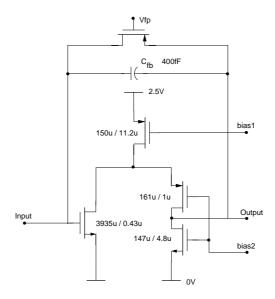

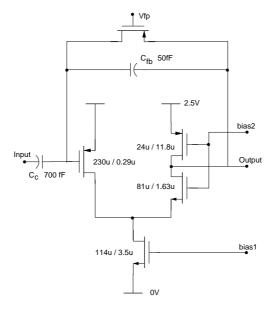

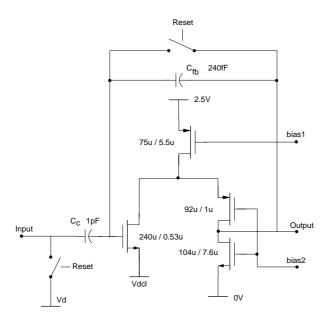

| 4.7  | Detailed schematic of the preamplifier with the according design parameters                                                                                                                   | 68 |

| 4.8  | Layout of the input transistor: The transistor adds up from 12 blocks each consisting of 13 smaller transistors with enclosed gate structure. Three out of 12 blocks are shown for simplicity | 69 |

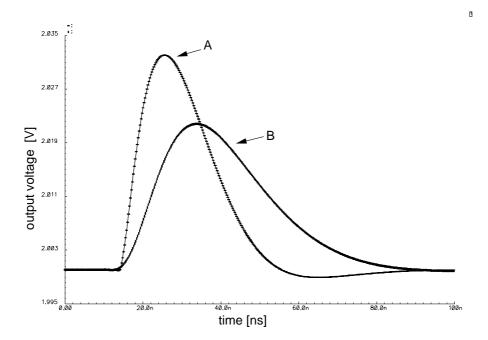

| 4.9  | Simulated output voltage of the pulse shaping stage. Curve A shows the response to an ideal voltage step, curve B the response on the preamplifier output voltage                             | 71 |

| 4.10 | Detailed schematic of the pulse shaper with the according design parameters                                                                                                                   | 71 |

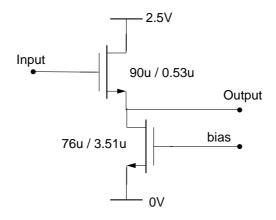

| 4.11 | Schematic of the frontend buffer                                                                                                                                                              | 72 |

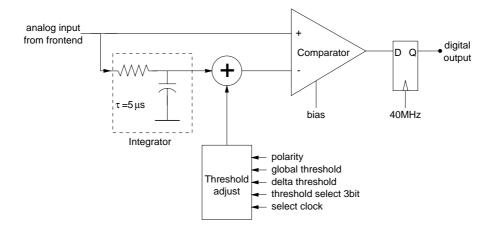

| 4.12 | Schematic blocks of the comparator circuit [8]                                                                                                                                                | 73 |

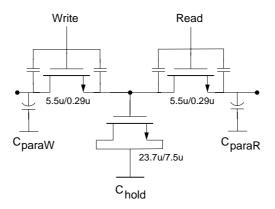

| 4.13 | Schematic of one pipeline cell, including the parasitic capacitances                                                                                                                          | 74 |

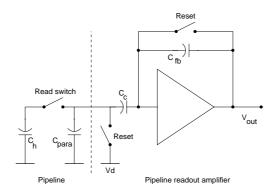

| 4.14 | Schematic of the pipeline readout amplifier                                                                                                                                                   | 75 |

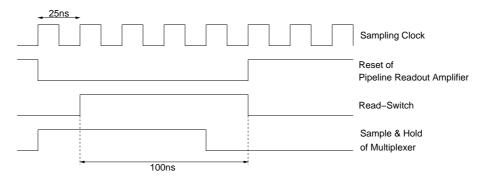

| 4.15 | Control signals of the pipeline readout amplifier during readout of one event                                                                                                                 | 75 |

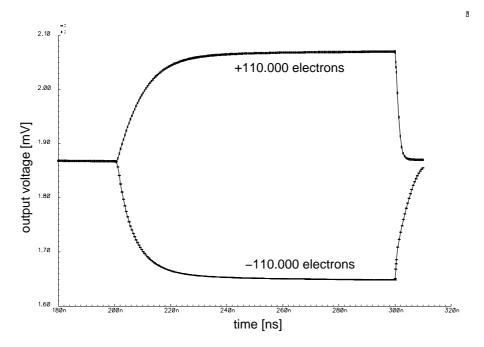

| 4.16 | Simulated output of the pipeline readout amplifier for signals that are equivalent to $-110.000e^-$ to $+110.000e^-$                                                                          | 76 |

| 4.17 | Detailed schematic of the pipeline readout amplifier                                                                                                                                                                    | 77 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

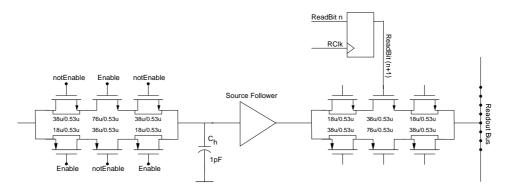

| 4.18 | Schematic of one channel of the multiplexer                                                                                                                                                                             | 77 |

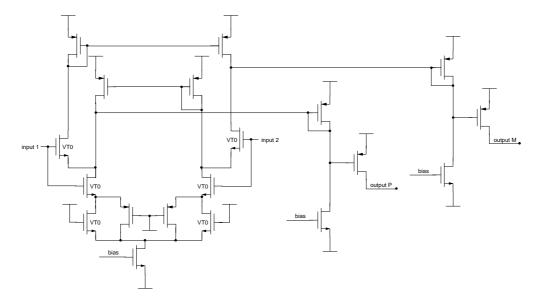

| 4.19 | Schematic of the analog output buffer (dimensions of the transistors are not shown for simplicity). Transistors with the extremely small threshold voltage are labeled 'VT0'                                            | 79 |

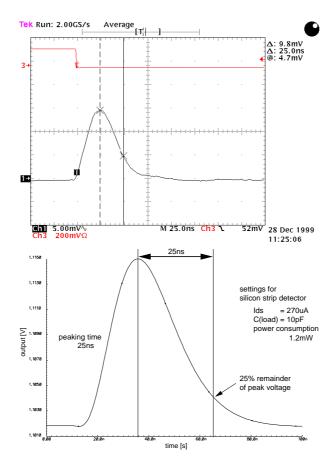

| 5.1  | Transient response of the frontend to a signal of 11.000 electrons: measurement (top) and simulation (bottom)                                                                                                           | 86 |

| 5.2  | Maximum height of the frontend's output versus input charges ranging from -110,000 electrons to +110,000 electrons for three different load capacitances of 5.6 pF, 10 pF and 15.6 pF (highest slope to smallest slope) | 87 |

| 5.3  | Frequency response of the input stage: measurement (top) and simulation (bottom)                                                                                                                                        | 88 |

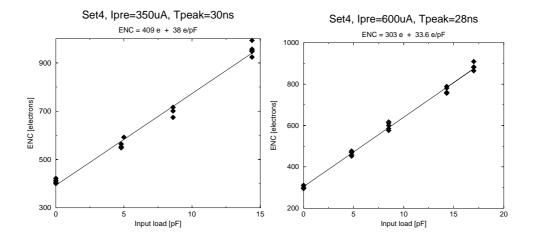

| 5.4  | Noise functions for a preamplifier bias current of 350 $\mu$ A (left) and 600 $\mu$ A (right)                                                                                                                           | 88 |

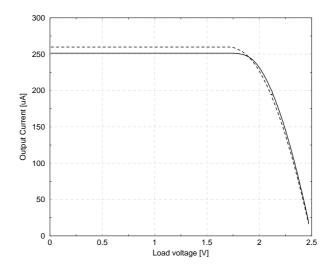

| 5.5  | Measured output current of the current source (dashed line) compared with simulation (solid line) versus load voltage                                                                                                   | 89 |

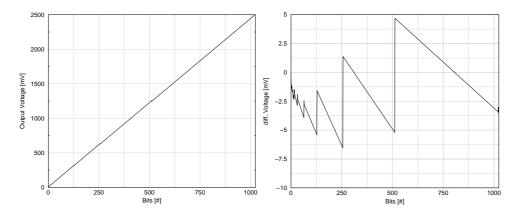

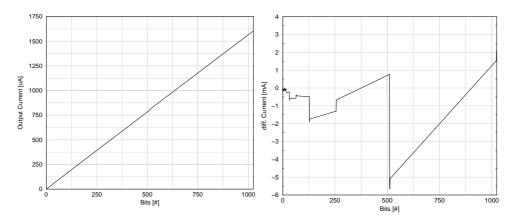

| 5.6  | Output voltage (left) and differential non-linearity (right) of the 10bit voltage DAC as function of the bit number                                                                                                     | 90 |

| 5.7  | Output current (left) and differential non-linearity of the 10bit current DAC as function of the bit number                                                                                                             | 90 |

| A.1  | Arrangement of the bond pads on the Beetle 1.0                                                                                                                                                                          | 94 |

### Introduction

This thesis describes the evolution of the Beetle-1.0 readout chip for LHCb. This VLSI chip has been developed at the ASIC-laboratory Heidelberg in collaboration with the Max-Planck Institute for Nuclear Physics Heidelberg, the University of Heidelberg, NIKHEF Amsterdam and the University of Oxford.

The specification phase of the readout chip started in late 1998, in parallel with the development of prototype components. The first submission of two test chips, containing different variations of analog input stages and bias circuits took place in May 1999. The successful test after their production in November 1999 triggered the assembly of the complete readout chip in one step, which has been submitted in April 2000. Together with the readout chip Beetle-1.0, three test chips containing different subcomponents have been designed and submitted. Table 1 gives an overview on the different chips with their submission dates and functionality.

Chapter 1 describes the basic physics goals of the experiment LHCb, as well as the apparatus and the detector technology. The principle of a silicon microstrip detector is described in more detail to give a picture of the requirements on a silicon microstrip readout chip. Chapter 2 details the important effects of radiation damage in microelectronic circuits, and an overview on existing architectures of microstrip readout chips is given in chapter 3. Chapter 4 describes the design and concepts of the readout chip Beetle-1.0 and in chapter 5 the measurements that have been done so far are reported.

| name       | submission date | size                          | functionality                                 |

|------------|-----------------|-------------------------------|-----------------------------------------------|

| Beetle-FE  | May 1999        | $2\times2~\mathrm{mm}^2$      | 3 different sets of analog input stages       |

|            |                 |                               | with different shaping times/noise behavior   |

| Beetle-BG  | May 1999        | $2\times2~\text{mm}^2$        | 10 bit current and voltage DACs,              |

|            |                 |                               | 3 different types of current sources          |

| Beetle-CO  | April 2000      | $2\times2~\text{mm}^2$        | frontend comparators,                         |

|            |                 |                               | current buffer                                |

| Beetle-PA  | April 2000      | $2\times2~\text{mm}^2$        | pipeline, pipeline readout amplifier          |

|            |                 |                               | I <sup>2</sup> C interface                    |

| Beetle-MA  | April 2000      | $2\times2~\text{mm}^2$        | 3 different sets of analog input stages       |

|            |                 |                               | for the readout of photomultiplier tubes      |

| Beetle-1.0 | April 2000      | $6.1 \times 5.5 \text{ mm}^2$ | complete readout chip with full functionality |

|            |                 |                               | required by LHCb                              |

Table 1: Summary of the chips forming the development steps of the Beetle-1.0

### **Chapter 1**

## LHCb: An Experiment to Study CP-Violation in the System of B-Mesons

Since the first observation of CP-violation in the  $K^0\leftrightarrow \overline{K^0}$ -system in 1964 [1, 2], it has been the aim of physicists to search for this type of symmetry violation in other systems. The  $B^0\leftrightarrow \overline{B^0}$ -system is very attractive for that purpose, since the standard model predicts a large CP-violation for that system. Therefore, the precise examination of CP-violation in the neutral B-mesons is a good test of the standard model and a promising way to find physics beyond the standard model. However, this task is challenging. Typical branching ratios for interesting decay channels of B-mesons are in the order of  $10^{-5}$  and therefore demand a high precision in measuring the interesting effects. Several experiments aim to measure CP-violation in the B-system. The experiments BaBar and BELLE use colliding  $e^+e^-$ -beams to produce about  $10^8$  pairs of B-mesons per year [3, 4]. Another possibility is to use the strong interaction to produce B-mesons. This is done in the experiments HERA-B and LHCb, where accelerated proton beams are used. In LHCb where the center-of-mass energy will be 14 TeV, B-mesons at a rate of 100 kHz can be easily produced and a large statistic of CP-violation data can be gained [5].

#### 1.1 Overview of the LHCb detector [5]

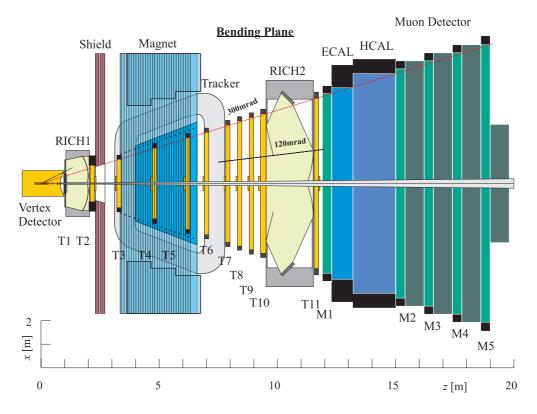

LHCb is a forward spectrometer with an angular coverage from 10 mrad to 250 mrad in the non-bending plane and 300 mrad in the bending plane. A picture of the detector can be seen in fig.1.1. The LHCb features a vertex detector, which is built around the interaction point, a tracking system, two RICH counters, an electromagnetic calorimeter with pre-shower detector, a hadron calorimeter and a muon detector. The interaction point is located in the center of the vertex detector, which also comprises additional detectors to derive a pileup veto.

The vertex detector has to provide precise information on the location of the primary and secondary vertex. Its information is also used in the Level-1 trigger. In order to

Figure 1.1: Schematic overview on the LHCb detector seen from above [5]

suppress events with more than one proton-proton interaction, a pile-up veto detector is integrated into the vertex detector system. A more detailed description of the vertex detector is given in 1.2.

The tracking system is built of two parts, the inner and the outer tracker. The type of detector technology is determined by the requirement of low occupancy to simplify tracking. For the outer tracker, a honeycomb-chamber technology has been chosen with a cell separation of 5 mm. For the inner tracking system, the higher track density requires a smaller granularity. Therefore, a combination of silicon microstrip detectors for the tracking stations close to the vertex detector and microstrip gaseous chambers for the stations far apart from the vertex detector has been chosen.

The RICH detector has to identify charged particles over the momentum range 1-150 GeV/c to provide an efficient kaon tagging facility. The system consists of two parts. RICH1 is located directly behind the vertex detector with a silica aerogel and a  $C_4F_{10}$  gas radiator. RICH2 uses  $CF_4$  as active material. Hybrid photodiodes with pixel readout or multi-anode photomultipliers are foreseen to be used as Cherenkov photon detectors.

The calorimeter consist of three main parts. Its main task is to identify electrons and hadrons for triggering and offline analysis. A pre-shower detector is used to provide an accurate detection of pions. This detector is built from 14 mm thick lead plates followed by square scintillators that are read out by phototubes or photodiodes. The pre-shower detector is followed by an electromagnetic calorimeter (ECAL), which

provides an identification and energy measurement of electrons and photons and a track reconstruction of pions. The ECAL is built from 2 mm thick lead plates, also followed by scintillators. The hadronic calorimeter (HCAL) has to provide a single-particle transverse-energy measurement of high  $p_T$  hadrons and it improves the separation between electrons and hadrons at high energies. The HCAL is constructed from scintillator tiles, that are embedded in an iron structure. The scintillators are read out by photomultipliers.

The muon detector is used for muon identification and to provide Level-0 trigger information. As detecting material, Multigap Resistive Plate Chambers and Cathode Pad Chambers are embedded in an iron filter. The detector uses pad readout instead of strip readout to enable a fast trigger response.

It is planned to start building the detector in autumn 2003 and have it ready for operation together with the operation of LHC in the middle of 2005.

#### 1.2 The Vertex Detector System of LHCb

The important tasks of the vertex detector are the location of the primary interaction point of the colliding protons and the detection of the so-called secondary vertex, which is the decay point of a produced B-Meson, with a resolution in the order of 6  $\mu$ m to 10  $\mu$ m. The efficiency in achieving this goal depends on the performance of the subsystems of the vertex detector as well as on their interaction.

#### 1.2.1 Layout of the Vertex Detector

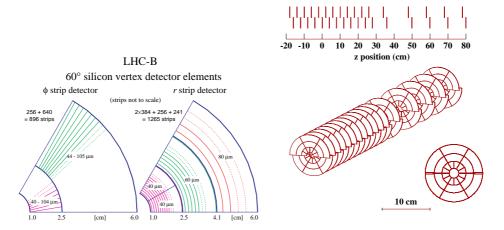

The geometrical layout of the detector arrangement is driven by the need of a precise measurement of the track coordinates close to the interaction region. For that purpose, silicon microstrip detectors have been chosen. In order to achieve an efficient reconstruction of secondary vertices originating from B-mesons in the Level-1 trigger, the layout of the detector strips has been optimized to that task. A strip pattern has been chosen, where detector discs with strips of constant radius alternate with detector discs with radial strips. The layout of the strips for a segment of a detector disc is sketched in fig.1.2 (left). Each disc is divided into six sectors, where the sensitive area of each sector covers  $61^{\circ}$  in  $\phi$ -direction and 1 cm to 6 cm in radius. The arrangement of the detector stations can be seen in fig.1.2 (right). This configuration assures that practically all particles measured in the downstream spectrometer cross at least three stations. The detector modules are split into two halves, so that they can be retracted during beam injection. To allow an overlap of the two detector halves, the upper and lower modules are displaced by 2 cm along the z-direction.

#### 1.2.2 Pile-Up Veto Counter

Two additional stations upstream of the LHCb detector act as a veto counter in the Level-0 trigger (see also sect. 1.3). Their geometrical layout is identical to the vertex

Figure 1.2: Schematic showing the strip layout of the  $\phi$ - and r-measuring detectors (left) and the arrangement of the detector stations in the vertex detector (right)

detector stations, but the requirements on the frontend readout electronics are different. The signals from the veto counter detectors are amplified, discriminated and immediately read out. The discriminated signals are processed and in case of more than one interaction per bunch crossing, a veto for the Level-0 trigger is given. Simulations show that this method rejects 80% of the double interactions while retaining 95% of single interactions.

#### 1.2.3 Silicon Detectors

The use of silicon microstrip detectors in vertex detectors has many advantages. Due to the small amount of energy that is needed to create an electron-hole pair in silicon and the high absorption (compared for example to gases), it is possible to detect ionizing radiation in a very efficient way. Semiconductor processing is a well developed technology for the production of integrated circuits and can be used to produce silicon detectors with high precision at relatively low prices.

#### Creation of the Charge

When a charged particle traverses silicon, the mean energy loss per path length can be described by the Bethe-Bloch formula [6]

$$\frac{dE}{dx} = 0.1535 \frac{MeVc^2}{g} \rho \frac{Z}{A} \frac{z^2}{\beta^2} \left[ \ln \left( \frac{2m_e \gamma^2 v^2 W_{max}}{I^2} \right) - 2\beta^2 - \delta - 2\frac{C}{Z} \right]$$

(1.1)

where

$m_e$  is the electron mass

I is the effective ionization potential averaged over all electrons

Z is the atomic number of the medium

A is the atomic weight of the medium  $\rho$  is the density of the medium z is the charge of a traversing particle  $\beta = v/c$  with v=particle's speed, c=speed of light  $\gamma = \frac{1}{\sqrt{1-\beta^2}}$   $\delta$  is a density correction C is a shell correction  $W_{max}$  is the maximum energy transfer in a single collision

The charged particles scatter inelastically with electrons in the valence band and loose part of their energy, which in turn lifts the electrons into the conduction band. As can be seen from eq 1.1, for low energies, the energy loss rate is proportional to  $\frac{1}{v^2}$ . At a certain energy, a minimum ionization rate is reached and for relativistic energies, the energy loss rate rises logarithmically. In principle, the average energy loss for a sample of silicon of a defined thickness can be obtained by integrating the Bethe-Bloch formula. However, due to statistical fluctuations of the average energy loss, this is not possible in an analytical way. The distribution of the average value for thin targets follows a Landau-distribution, which is an asymmetrical distribution with a long tail for high energies. The high energetic tail is due to occasional energy transfers to single electrons ( $\delta$ -electrons), which then travel several 10  $\mu$ m through the sample, causing further ionization [6]. A phenomenological approach to obtain a value for the mean energy loss is the use of the Fano factor (F). The variance in the number of electrons N that are created by the charged particle passing through the semiconductor is then

$$\left\langle \Delta N^2 \right\rangle = F \cdot N \tag{1.2}$$

For silicon, the Fano factor is about 0.115 [6]. From eq. 1.1 and eq. 1.2, the most likely energy loss for a minimum ionizing particle can be determined, which is about 83 electron/hole pairs per  $\mu$ m or  $295\frac{eV}{\mu m}$ . For a 150  $\mu$ m thick detector material (as planned for the vertex detector of LHCb) the most likely charge signal amounts to 12,500 electrons.

#### **Silicon Strip Detectors**

Position-sensitive particle detectors need to provide information on the position where the particle has passed through the detector. In order to collect the charge created by the particle before electrons and holes recombine, a reverse bias voltage needs to be applied to the detection material. Silicon strip detectors provide an efficient method to obtain a position and energy-loss measurement. In silicon strip detectors, strip-like diodes are used to separate the produced electrons and holes. In principle, the diodes are realized as strip-like arranged  $p^+$  layers (highly doped with donator atoms) on an  $n^-$  substrate (moderately to sparsely doped with acceptor atoms). The strip diodes are reverse biased and the width of the depletion region (which is the insulating region, where the intrinsic charge carriers are swept away due to the presence of an electric field) depends on the voltage applied to the strip diode. In normal operation of the strip diode as a particle detector, it is very desirable to have the complete substrate fully depleted so that a maximum of material is sensitive to ionizing radiation. Traversing

ionizing particles produce an ionization cloud which in turn produces a current pulse on the  $p^+$  strip of typically 3ns width and 30 to 50pA height, depending on the thickness of the detector material [6]. If the amount of charge and the location of the strip is known, this technique provides a means of energy-loss and position measurement. The precision of the position measurement depends on the strip pitch and the method of readout. If only the digital information (strip is hit or not) is used to localize a particle track, the precision of the position measurement is given by

$$\left\langle \Delta x^{2} \right\rangle = \frac{1}{p} \int_{-p/2}^{+p/2} x^{2} dx = \frac{p^{2}}{12}$$

where x is the measured position p is the strip pitch

For a typical strip pitch of  $50\mu m$ , this leads to a resolution of  $\sim 15\mu m$ . The resolution can be improved significantly, if the analog information of the strip signal is used. This allows to measure the height of the charge on more than one strip and therefore the center of gravity of the charge signals gives a more precise position information than in the case of digital readout. In the case of analog readout, the precision only depends on the noise performance of the readout electronics and on the readout pitch p as

$$\Delta x \approx \frac{p}{S/N}$$

where S/N is the signal-to-noise ratio of the readout electronics. In the case of the LHCb vertex detector, where a S/N value of about 12 is targeted, a resolution (neglecting multiple scattering and inclined tracks) of about  $4\mu m$  can be reached. However, in a real detector the resolution is limited by the multiple scattering in the material between the vertex and the points of the track measurements.

#### 1.2.4 Radiation Fluxes in the Vertex Detector [1]

During the operation of the LHCb experiment, the detector modules of the vertex detector are placed 1 cm away from the colliding beams. As a consequence, the detectors and the readout electronics will suffer from radiation damage. The particle fluxes decrease approximately with  $1/r^2$  (qith r being the distance to the beam axis). Figure 1.3 shows the simulated flux of 1 MeV equivalent neutrons/cm² (normalized to 1 interaction in the interaction point) as a function of the distance to the beam axis. The equivalent neutron flux is obtained by using the non-ionizing energy loss (NIEL) of the different particles. It is expected that the NIEL is the major source of radiation damage of the silicon detectors [8].

#### 1.2.5 Electronic Readout

The total number of detector strips of the complete vertex detector amounts to about 220,000. The strip pitch varies between  $40\mu m$  and  $60\mu m$  and the detectors are housed

Figure 1.3: Total particle flux (normalized to 1 interaction in the interaction point) at two stations of the Vertex Detector as a function of the distance to the beam axis [1]

in a vacuum tank, which excludes individual feed-throughs of all channels. Custom made VLSI electronics is needed for an application with such requirements. A chip suitable for readout of the LHCb vertex detector has to be capable of amplifying the detector signals within a time window compatible to the bunch crossing frequency of the LHC of 40 MHz. In order to reduce the number of feedthroughs in the vacuum tank, a certain multiplexing ratio of the signals has to be fulfilled by the readout chip. Due to constrained power consumption (the readout chips are operated in vacuum and have to be cooled), the readout frequency is limited. As a consequence, not all events that are amplified can be read out and only events that are marked by the Level-0 trigger will be sent out of the detector. This requires a ring buffer, which stores the events. This architecture of the readout chip is similar in other experiments, like HERA-B, ATLAS and CMS. A more detailed treatment of several approaches follows in chapter 3. A comparison of analog and binary readout in the vertex detector can be found in [9].

The basic specifications of the LHCb vertex detector are summarized in table 1.1. They determine the requirements on the readout chip given in tab. 1.2. It should be noted that these numbers are a compromise between efficiency in achieving the task of measuring decay vertices, technical limits, reliability of the system and financial limitations.

| Total number of detector channels               | 220.000                                |

|-------------------------------------------------|----------------------------------------|

| Strip pitch at detector                         | $40\mu\mathrm{m}$ to $60\mu\mathrm{m}$ |

| Sampling frequency                              | 40 MHz                                 |

| Level-0 trigger delay                           | $4\mu s$                               |

| Level-0 trigger rate                            | 1 MHz                                  |

| Maximum number of events pending to be read out | 16                                     |

| S/N at a given load capacitance                 | > 14 at 10 pF                          |

| irradiation dose at readout chip position       | 2 Mrad/year                            |

| charge created by 1 minimum ionizing particle   | 11,000 electrons                       |

| required linearity                              | better than 5% for $\pm 10$ MIP        |

| signal remainder at 25 ns after peaking time    | < 30%                                  |

| acceptance of consecutive triggers              | yes                                    |

| operation time                                  | 5 years                                |

Table 1.1: Basic specifications of the LHCb vertex detector, determining the requirements on a readout chip for the LHCb vertex detector.

| Input amplifier                        | preamplifier and pulse shaper            |

|----------------------------------------|------------------------------------------|

|                                        | peaking time 25 ns, signal remainder     |

|                                        | after 25 ns of <30%                      |

| Total noise                            | < 785 electrons at input load of 10 pF   |

| dynamic range                          | -110,000 electrons to +110,000 electrons |

| Number of channels                     | 128                                      |

| Channel pitch                          | $50~\mu\mathrm{m}$                       |

| Sampling frequency                     | 40 MHz                                   |

| Readout time per event                 | < 900 ns                                 |

| Latency                                | 160 clock cycles                         |

| Size of multievent buffer              | 16                                       |

| Total ionizing dose                    | 10 Mrad                                  |

| Acceptance of consecutive triggers     | yes                                      |

| Generation of trigger for pile-up veto | yes                                      |

| Deadtimeless readout                   | yes                                      |

| Power consumption                      | < 4 mW / channel                         |

Table 1.2: Requirements on a readout chip for LHCb

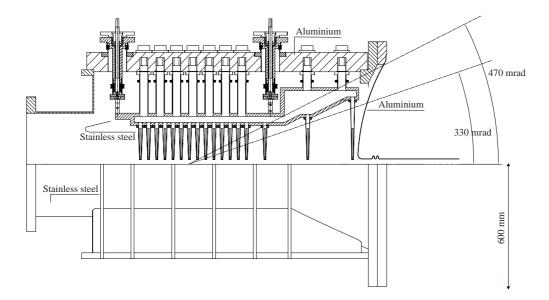

Figure 1.4: Side view of the vacuum tank and support structures for the Vertex Detector. The bottom half is omitted.

#### 1.2.6 Mechanical Support Structure

The mechanical support of the detector modules is an important component in achieving the required performance of the vertex detector system. The detector modules have to be mounted so that they can be retracted from their nominal operating position during beam injection and be aligned to a precision of better than  $50\mu m$ . The detectors also have to be protected from RF-pickup from the proton beams, and in general the total mass in the acceptance region of the detector has to be kept to a minimum. These requirements can be satisfied by a roman pot system. The detector stations are mounted on aluminum support frames via linear actuators. The modules are housed in a secondary vacuum, which is separated from the vacuum of the beam pipe via a  $100\mu m$  thick aluminum foil. The aluminum foil is folded around the detector modules in order to keep the effective thickness for the particles at a minimum. Figure 1.4 shows a preliminary sketch of the mechanical arrangement of the detector modules and their supporting structures [5].

#### 1.3 The Trigger System of LHCb

The task of the trigger system is to reduce the amount of data during the operation of the detector and after the data have been acquired. Different trigger levels allow a very coarse filtering at an early stage of data acquisition with rather simple algorithms and a detailed decision with more complicated algorithms at later stages. In LHCb, the trigger decision is taken in four steps:

**Level-0** trigger uses the information of the muon detector, the electromagnetic and the hadronic calorimeter. It searches for particles with a high transverse momentum

(high  $p_T$ -trigger), which are typical for events with B-Mesons. Events with more than one interaction are suppressed by the pile-up veto counter. The information of the Level-0 calorimeter trigger, the Level-0 muon trigger and the Level-0 pile-up veto trigger are combined by the Level-0 decision unit. The complete Level-0 trigger will be implemented as hardware. The latency of the Level-0 trigger is fixed to  $4\mu s$ . The targeted average trigger rate of Level-0 is 1 MHz, which yields a suppression factor of 40.

**Level-1** trigger uses the information of the vertex detector to select events with one or more secondary vertices (vertex trigger). In addition, the tracks of the high  $p_T$ -trigger are confirmed. The information of the Level-1 vertex trigger and the Level-1 track trigger are combined by the Level-1 decision unit. The complete Level-1 trigger will be implemented as a software solution. The date will be processed on a processor farm consisting of commercial CPUs. The suppression factor of Level-1 is 25 and the latency is variable up to a value of  $256 \mu s$ .

**Level-2** trigger eliminates events with a false secondary vertex. It uses the momentum information of the tracks and correlates the information of the tracking stations with the tracks from the vertex detector. The latency of the Level-2 trigger depends on the installed computing power and it is currently planned to achieve an average latency of 10ms with a suppression factor of 8.

**Level-3** trigger partially and fully reconstructs the final states to select events with specific decay modes. It uses the complete detector information. The suppression factor at Level-3 is about 25 with a latency of about 200 ms. The data output rate is therefore  $\approx 200$  Hz.

### **Bibliography**

- [1] J. H. Christenson et.al, Phys. Rev. Lett. 13 (1964) 138

- [2] B. P. Povh, Teilchen und Kerne, Springer Verlag 1994

- [3] The BaBar Homepage, http://www.slac.stanford.edu/BFROOT

- [4] The Homepage of the BELLE experiment, http://bsunsrv1.kek.jp/

- [5] LHCb Technical Proposal, CERN/LHCC 98-4

- [6] G. Lutz, Semiconductor Radiation Detectors, Springer Heidelberg 1999

- [7] V. Talanov, Radiation Environment at the LHCb Vertex Detector Area, CERN, LHCb 98-019/TRAC

- [8] G. Casse, et.al, Study of Radiation Induced Charge Trapping in Irradiated Silicon Detectors, internal LHCb note

- [9] P. Koppenburg, Comparison of analog and binary readout in the silicon strips vertex detector of LHCb, LHCB/97-020

### **Chapter 2**

## Radiation Damage in Microelectronic Devices

The long-term performance of electronic devices in an environment like the LHCb vertex detector strongly depends on the amount of damage that is caused to the electronic devices by high energy particles. Since no technology or device yet exists that is completely immune to ionizing and non-ionizing radiation, the decision for a certain technology has to keep the radiation defects, failures and the consequences in mind, so as to judge their acceptability. This chapter summarizes most of the known defects due to ionizing and non-ionizing radiation in microelectronic integrated circuits. It shows up consequences and ways to overcome them.

#### 2.1 Introduction

The composition of particle and electromagnetic radiation in a hadron-collider experiment like LHCb can be understood quite well, although the quantitative distributions of the particle types and their energies are difficult to calculate. Detailed distributions of radiative background as seen by electronic devices that are located inside the detector area or inside the detector itself are therefore usually obtained by means of simulations. The simulation takes into account the real distributions of material inside the detector and the distributions and spectra of incident particles. Simulations done for a proposed configuration of the LHCb vertex detector as from 1998 can be found in [1]. Since the configuration of the complete detector system and therefore the exact location of the front-end electronics was not frozen at that time, these calculations can not be regarded as final.

Section 2.2 explains the radiation defects of MOS field effect transistors and describes methods to enhance the radiation tolerance of such devices. In section 2.3, radiation defects of bipolar transistors are presented.

#### 2.2 Radiation Damage in MOS Field Effect Transistors

The use of MOS (metal-oxide-semiconductor) microelectronics in radiation environments recently became popular, mainly due to the wide availability of MOS processes and their low price, compared to bipolar processes. Also, the improvement and development of MOS processes with reduced leakage currents and lower spread of process parameters, yields high performance devices that are available in standard processes. The availability of CMOS processes with structure sizes of less than 0.35  $\mu$ m and the expected radiation tolerance of them has further driven the use of standard CMOS as a basis for the development of radiation hard microelectronics.

#### 2.2.1 Total Ionizing Dose Effects

#### Trapped Charges in Silicon Oxide [12, 3]

Cumulative radiation effects occur during the complete lifetime of a transistor as long as it is exposed to radiation. As long as the dose applied to a transistor is known and the device is characterized completely, the failure or degradation in performance of the device can be predicted.

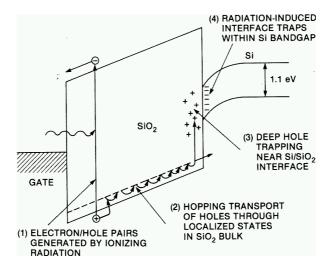

In a radiation environment like in the LHCb detector, the total ionizing dose effects are caused by electrons and by charged hadrons.  $\gamma$ -particles and neutrons do not ionize directly, but they can induce ionization by energy deposition. The most sensitive part of a MOS field effect transistor is the thin gate oxide, which separates the gate from the active channel. If an electron-hole pair is created in the silicon dioxide of the gate oxide, they do not recombine immediately due to the insulation characteristics of the gate oxide. If no electrical field is applied to the gate of the transistor, both the electron and the hole stay in the gate oxide and recombine eventually by diffusion. By application of an electrical field, the electrons can leave the gate oxide faster than the holes due to their higher mobility in silicon dioxide. The result is a growth of the hole concentration in the gate oxide. From this simple consideration, it is already obvious, that total ionizing dose effects on field effect transistors are smaller if there is no electrical field applied to the gate. As a consequence, transistors should always be set under operating condition during irradiation tests to ensure a realistic damage due to total ionizing dose. The effects on the performance of trapped charges in the gate oxide depends on the type of transistor. In an nMOS transistor, the field of the positive trapped charges (holes) adds towards the one, that is generated by supplying a positive voltage to the gate. In a pMOS transistor, the trapped holes 'shield' the electrical field that is generated by a usually, negative voltage applied to the gate.

The mechanism of the generation, distribution and trapping of the holes and electrons in the silicon oxide is visualized in fig.2.1. The amount of charge generated in the oxide depends on the energy that is deposited by the ionizing particle. The energy needed to create one electron/hole pair is about 3.6 eV [2]. The time scale for a recombination process of the electron/hole pair is given by the mobility of the electrons in SiQ, which is much higher than the mobility of holes. At room temperature, the mobility of electrons is about  $20cm^2V^{-1}s^{-1}$  and its velocity saturates at about  $10^7\,cm/s$  for high

Figure 2.1: Charge generation, distribution and trapping due to ionizing radiation in silicon oxide (e.g. in the thin oxide of a MOS transistor) [3]

electrical fields [3]. The mobility of holes is always much lower than the electron mobility and typical values are  $10^{-4} - 10^{-11} cm^2 V^{-1} s^{-1}$ , depending on the temperature and the electrical field. Therefore, if an electrical field is applied to the silicon oxide, the electrons immediately leave the oxide in the order of 1ps. Any recombination process is limited by this time constant. Even without electrical field, any recombination takes places in several picoseconds due to the large difference in mobility of electrons and holes. The remaining holes, that do not initially recombine, follow any electrical field in the  $SiO_2$ -layer towards the negative electrode through a relatively slow transport mechanism, where they are collected or captured in deep trapping sites. The transport mechanism is highly dispersive and the time constants can vary over many decades. A satisfying model for the transport of holes in  $SiO_2$  is given by the CTRW (continuous-time random walk) model [3]. A detailed understanding of this transport mechanism is especially important for the modeling of short-term (order of seconds at room temperature) post-irradiation response of a transistor. The long term radiationinduced behavior of a transistor is dominated by the holes trapped near the SiQ/Siinterface. Figure 2.2 shows a schematic of trapped charges in the gate oxide of a MOS transistor. The shift in the gate bias voltage  $\Delta V_{th}$  originating from the trapped holes in the gate oxide can be written as

$$\Delta V_{th} = -\frac{q}{\varepsilon_{ox}} d_{ox} \Delta N_{ot} \tag{2.1}$$

where  $\Delta N_{ot}$  is the charge density per unit area in the  $SiO_2/Si$  interface and  $d_{ox}$  the thickness of the oxide.  $\Delta N_{ot}$  can be written as

$$\Delta N_{ot} = \frac{1}{d_{ox}} \int_0^{d_{ox}} n_{ht}(x) x dx$$

where  $n_{ht}$  is the local density of trapped holes. An analytical expression for 2.1 can be obtained by simplifying the assumptions on the distribution of the trapped holes. If the

Figure 2.2: Schematic of hole trapping and removal in a MOS transistor at a positive gate voltage [3]

distribution of the holes is assumed to be a single layer with an average density  $\tilde{N}_{ht}$  and a thickness  $\Delta X$  (small compared to  $d_{ox}$ ) and the recombination of trapped holes with electrons is neglected, the fraction of radiation-generated holes that are trapped in the oxide is

$$f_T(E_{ox}) = \sigma_{ht}(E_{ox}) \bar{N}_{ht} \Delta X$$

where  $E_{ox}$  is the effective electrical field in the oxide and  $\sigma_{ht}$  is the local cross-section of the hole traps for capturing holes. The total number of holes trapped in the oxide is then

$$F_h(E_{ox}, E) = d_{ox}[K_g(E)f_y(E_{ox}, E)D(E)]$$

where  $K_g$  denotes the charge generation coefficient,  $f_y$  the fractional free charge yield and D the total dose of ionizing radiation that has passed through the oxide. The energy of the ionizing radiation is E. Using  $\Delta N_{ot}(E_{ox}, E) = F_h f_T$ , one can deduce

$$\Delta V_{th}(E_{ox}, E) = -\frac{q}{\varepsilon_{ox}} K_g(E) f_y(E_{ox}, E) f_T(E_{ox}) d_{ox}^2 D(E)$$

(2.2)

This expression [3] contains the important relationship  $\Delta V_{th} \propto d_{ox}^2$  of the shift in the gate voltage due to trapped charges as a function of the gate oxide thickness for a fixed radiation dose.

The limit of this model can be deduced from fig.2.2 if the thickness is small enough so that the tunneling processes between the gate oxide and the silicon (or the gate, respectively) becomes dominant. Several measurements have shown a much faster decay of the threshold voltage shift with decreasing thickness when  $d_{ox}$  falls below 20 nm. Figure 2.3 shows the shift in the flat-band voltage per unit dose as a function of the oxide thickness for various MOS structures. For thicker oxides, the curve follows the the  $d_{ox}^2$  dependency as shown in 2.2. For a thickness below approximately 20 nm, the shift in the flat-band voltage drops much faster [4, 5]. This effect greatly favors the use of MOS technology with thin gate oxides to prevent a shift in the effective gate voltage.

Figure 2.3: Shift of the flat-band voltage as function of oxide thickness for various MOS structures. The solid/dashed line shows the expected  $d_{ox}^{p}$  dependency for thicker oxides [3].

Another part of transistors, namely nMOS transistors, that is sensitive to trapped charges due to ionizing particles is the so called lateral oxide. Also known as field oxide, this part separates the active channel region from the surrounding bulk material. In an nMOS transistor, trapped holes in the field oxide at the interface to the silicon can create a leakage path from the source to the drain of the transistor. The size of this parasitic leakage current rises with the total amount of holes trapped in the lateral oxide, and therefore with the total ionizing dose. The absolute size of the leakage current depends on the detailed geometrical structure of the lateral oxide and can hardly be predicted. Since the thickness of the field oxide is much larger than 20 nm, a tunneling of trapped holes from the field oxide into the silicon is excluded. Figure 2.4 shows a sketch of an nMOS transistor and the region where this parasitic leakage current occurs. Several methods to prevent the rise in leakage current in nMOS transistors due to ionizing radiation have been reported [6], but most of them use different processing steps and manufacturing techniques to achieve the goal. Only recently, when processes with structure sizes of  $0.35\mu m$  and less became available, the approach of closed gate structures has become an alternative. By using a gate geometry as pointed out in fig. 2.5, any leakage path between source and drain under the field oxide of the transistor is avoided [3]. This method has the price of a larger area for transistors. Also, modeling of the effective behavior of enclosed transistors is not as well established as for standard transistor geometries. A description of models for enclosed transistors is given in chapter 4.

Figure 2.4: Schematic view of the parasitic channel due to trapped holes in the field oxide of an nMOS transistor which gives rise to a parasitic leakage current

Figure 2.5: The parasitic leakage path between source and drain as in a regularly laid out transistor (left) is prevented in an enclosed transistor layout (right)

Figure 2.6: Threshold voltage of an nMOS transistor (a) and a pMOS transistor (b) as a function of the total ionizing dose [3]

#### Interface States at the $Si/SiO_2$ Interface

Defects in the crystal lattice that are formed at the interface of the gate oxide and the silicon are called interface states. These interface states trap charges from the channel of the transistor and therefore cause a shift of the threshold voltage and a degradation of the mobility of the charge carriers in the channel of the transistor. Interface states (also known as interface traps or surface traps) are electronic energy levels between the conduction and the valence band. They arise from lattice mismatch at the interface, disconnected bonds or impurities, and they can be induced by ionizing radiation. As for parasitic leakage currents under the field oxide induced by trapped charges, the total effect of interface states on the behavior of a MOS transistor cannot be predicted. It depends on processing details, gate material and on doping concentrations. The nature of the charge states in the silicon bandgap can be divided into acceptors and donors, where energy levels in the upper half of the bandgap are occupied by acceptors and energy levels in the lower half by donors [3]. The net charge that is captured in the interface states can be positive, negative or zero. However, by applying a voltage to the gate of a MOS transistor, the interface states move along with the valence and conduction band relative to the Fermi level. The effects of interface states on the behavior of transistors are manifest in three important effects:

Shift in the threshold voltage: Due to the additional charges captured in the interface states, the effective gate voltage is shifted which results in a shift of the threshold voltage. For pMOS and nMOS transistors, this effect is different: in pMOS transistors, positively charged donor interface traps reduce the threshold voltage, whereas in nMOS transistors, the threshold voltage is increased due to negatively charged acceptor interface traps. These effects, together with the threshold voltage shift due to trapped charges in the gate oxide, cause the typical shape of the threshold voltage as a function of the total ionizing dose shown in fig. 2.6. Since for pMOS transistors, the threshold voltage is decreased by the trapped charges and the interface states, the overall slope is negative. On the other hand, nMOS transistors show a decrease in th

Figure 2.7: Normalized channel mobility as function of radiation induced interface trap density [8]

threshold voltage for a dose below 100 krad (typically). This decrease is caused by positive trapped charges in the gate oxide, which are dominating at low doses. Above 100krad, the increase of the threshold voltage is caused by negatively charged interface traps. In the literature, this effect is often called "rebound".

**Degradation in the transconductance**  $g_m = \partial I_d/\partial V_g|_{V_d=const}$ : The transconductance of a transistor is reduced by radiation induced interface traps. This can be understood by considering a gate voltage sweep, which empties or fills the interface states at the gate surface. These additional states in turn modify the electrical field, so that more or less respectively, charge is needed on the gate to create the desired electrical field in the channel of the transistor. Also, the voltage needed to bring the transistor into strong inversion is higher. This affects (amongst others) the switching speed in digital circuits.

Change of the mobility: The mobility  $\mu$  of charge carriers in the channel of a transistor is reduced by radiation induced interface traps. A model for the mobility degradation is given in [7, 8]. The mobility of the charge carriers is reduced by an increased amount of lattice and Coulomb scattering due to the interface states. The empirical relationship for the degradation of the channel mobility is

$$\mu = \frac{\mu_0}{1 + \alpha(\Delta N_{it})} \tag{2.3}$$

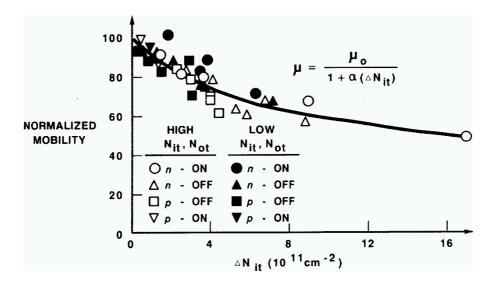

where  $\mu_o$  is the mobility before irradiation,  $N_{it}$  is the concentration of trapped interface charges and the fitting parameter  $\alpha = (8 \pm 2) \times 10^{-13} cm^2$ . Figure 2.7 shows a comparison between measurement values and the empirical model 2.3.

#### **Dynamics of Trapped Charges and Interface States**

The dynamics of the two effects, trapped charges in the gate oxide and interface states, is very different. Trapped charges can easily be removed from the gate oxide by elevated temperatures. The holes are then thermally activated and de-trapped from their locations. In contrast, annealing of interface states has not been observed at normal operating temperatures. Annealing at temperatures above 100° C seems to be very sensitive to the processing of the oxide. An activation energy of 1.4 eV has been reported for the annealing of interface states [10].

#### 2.2.2 Single Event Effects (SEE)

In contrast to the cumulative total ionizing dose effects, single event effects are usually triggered by single particles that cross sensitive regions of the device. The actual effect occurs very localized, but can propagate over the complete system. Single event effects can be classified depending on their impact on the systems behavior:

- Transient effects: yield in asynchronous signals, that propagate through the system. They can appear in analog as well as in digital circuits and can become static if they are latched.

- Static effects: change the content of a memory cell and can be overwritten.

- Permanent effects: are destructive events that cannot be recovered. In some cases, they can be prevented by a fast current limitation.

In the applications of high energy physics experiments, SEE have become a concern during recent years. This is due to the use of deep sub-micron processes, where the intrinsic sensitivity due the smaller gate capacitances is significantly higher than for processes with structure sizes of  $0.8~\mu m$  or larger.

#### **Single Event Upset (SEU)**

If an ionizing particle passes through a semiconductor, it loses its energy by ionization by creating pairs of electrons and positive charged holes. In the semiconductor bulk of a MOS transistor, the electrons and holes recombine immediately. This is not the case in the active region of a transistor and in its surroundings. The electron-hole pairs are separated by the electrical field and therefore give rise to a current spike. This current spike has two components: a fast component (less than a ps) which yields from the electron-hole pairs created directly in the depleted region of the transistor channel, and a second component which is rather slow (in the order of ns) and arises from regions outside of the active area. Depending on the energy loss of the ionizing particle, the current spike can be rather large, and the impact on the circuit, in which the transistor is used, cannot be neglected.

The amount of energy that is deposited in the active region of a transistor by an incident particle is usually expressed by the linear energy transfer (LET). The energy needed to

Figure 2.8: Schematic of the experimental setup for SEU cross section measurements [11]

create an electron/hole pair in silicon is 3.6 eV and that defines the amount of charge that is produced by the absorbed energy. Ions of the same energy have a higher linear energy transfer, the heavier they are. Particles, which do not have enough mass to create enough charge for a SEU to occur (like protons or  $\alpha$ -particles) can initiate nuclear reactions, whose recoil products are heavy enough to produce direct ionization.

The minimum LET needed to change the state of a given device (e.g. a flip-flop) is called critical LET. The critical LET depends strongly on the fabrication process of the device that is considered, since it contains not only the amount of charge that is needed to upset a device, but also the detailed structure of the device, which in turn is responsible for the distribution of the charge.

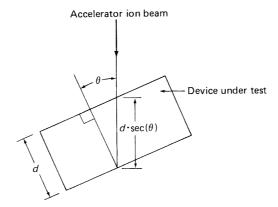

The experimental determination of the critical LET is usually done by exposing the device to a beam of heavy ions (e.g. O, Li, Na). SEUs are then characterized using a beam threshold measure. The threshold is defined as the minimum perturbation that produces an error in the test device, and the upset cross-section is the maximum sensitivity to SEU caused by the ion beam. The upset cross section  $\sigma$  is then calculated as

$$\sigma = \frac{U}{\Phi t \cos \theta} \tag{2.4}$$

where U is the absolute number of upsets during the time interval t and  $\Phi$  the particle fluence of incident ions per  $cm^2$ . The incident angle  $\theta$  is visualized in fig. 2.8. During the measurement, the incident angle of the ion beam is varied across the device. As a result, the charge that is deposited into the sensitive region of the transistor is varied. Assuming the ion tracks inside the material are long compared to the active device geometry, the amount of charge deposited is proportional to  $\frac{1}{\cos\theta}$ . With that method, the LET can be varied over a limited range. By combining these results with results of different types of ions, a larger statistics can be gained. The data of different ions can be combined by assuming that two different ions with the same LET have the same impact on the device. This assumption is not exact, since the radial distribution of the charge that is created by an ion certainly depends on the type of ion. Also, the charge distribution along the track of the ion that penetrates the semiconductor

Figure 2.9: Typical result of an SEU cross-section measurement performed on the APV25 [9]

| Ion Type                                    | Si | Si   | Cl   | Ni | Br   |

|---------------------------------------------|----|------|------|----|------|

| LET [MeV cm <sup>2</sup> mg <sup>-1</sup> ] | 9  | 10.4 | 12.9 | 30 | 39.4 |

Table 2.1: Ion types and according linear energy transfer for the measurement plotted in fig. 2.9

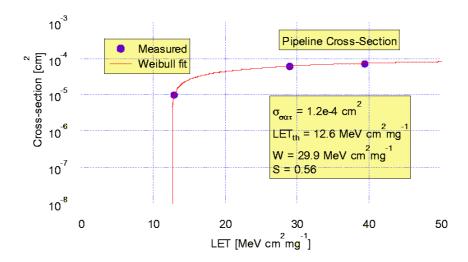

depends on the ion type. Nevertheless, combining results of different ion types is an accepted method to measure the critical LET. Figure 2.9 shows a typical result for a measurement of SEU cross-sections as a function of LET. This measurement was performed with different ion types of an energy of about 100 MeV as listed in tab. 2.1 The curve shows a steep rise in the SEU cross section at the critical LET value of 12.6 MeV cm<sup>2</sup> mg<sup>-1</sup>. This measurement has been performed with the APV25 readout chip for CMS [9], which is manufactured in the same technology as the Beetle readout chip for LHCb (see chapt. 4).

#### **Single Event Latchup (SEL)**

SEL is a well studied phenomenon in CMOS devices since latchups can occur due to high temperatures, large transients on the power supply lines or due to wrong bias cycling of circuits. In a radiative environment, a latchup can also be induced by a heavily ionizing particle.

In general, an SEL occurs in a CMOS structure due to inherently present bipolar transistors, that can be completely turned on. The presence of these parasitic pnp- and npn structures can be seen in fig. 2.10. Of course, this model is only a simplification of the parasitic bipolar structures that are present. A more realistic model would need consideration of the three-dimensional distributions of the p-n junctions.

In this configuration, the collector of the npn-transistor is connected to the base of the pnp-transistor. In the case of an increasing collector current in the pnp-transistor

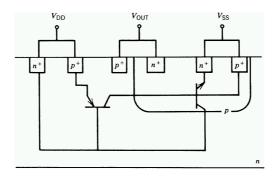

Figure 2.10: Parasitic pnp and npn bipolar structure in a CMOS inverter. The gates of the MOS-transistor are not shown for simplicity.

(which can happen due to a heavily ionizing particle crossing the active region of the device), the base current of the npn-transistor is also increasing, which in turn increases the collector current of it. The rising collector current of the npn-transistor then increases the base current of the pnp-transistor. This positive feedback leads to an almost shorted circuit between the power supplies if the gain of this parasitic pnpn-thyristor is high enough. This case is usually destructive for the adjacent MOS device, unless the current is limited e.g. by the resistance of the supply lines.

Effective methods to decrease the sensitivity of devices to latchup are possible by reducing the gain of the parasitic pnpn thyristor. This can be done by technological solutions, e.g. by using trench isolations between adjacent MOS structures, the gain of the lateral parasitic transistor is strongly reduced. Layout techniques can also reduce the resistance along the parasitic current path. The systematic use of guardrings around the wells of transistors ensures a low-ohmic connection of the lateral bipolar transistors and therefore effectively reduces the latchup sensitivity.

**Single Event Gate Rupture (SEGR), Single Event Burnout (SEBO)** Less often found in literature, SEGR and SEBO have been observed in power MOSFET applications. The threshold for these destructive events is higher than for SEU and therefore requires the presence of very heavily ionizing hadrons [12]. Due to their small likelihood, these effects are not considered to be a problem for the application of CMOS devices in a high energy physics experiment [12].

#### 2.3 Radiation Damage in Bipolar Transistors [11, 16]

In bipolar transistors, radiation damage occurs exclusively in a cumulative way. The effects can be divided by the nature of interaction of the radiation with the devices. Damage caused due to ionizing energy loss is treated in 2.3.1, whereas the effects due to non-ionizing energy loss are described in 2.3.3.

Figure 2.11: Measurement of the  $\beta$ -degradation with irradiation for different devices [11]

#### 2.3.1 Total Ionizing Dose

The cumulative effects of ionizing particles in bipolar transistors are caused by trapped charges in oxide layers and by interface states. They are caused by the creation of a conductive channel under the thick oxide (field oxide) by inversion of the silicon due to trapped charges. There are three main locations where this may occur. First, a conductive channel can be opened between two buried layers. Second, a channel can be opened that creates a current path between collector and emitter at the sidewall oxide. Third, a current can flow under the thick oxide of the surface. These effects result in an increased base current, which in turn reduces the effective gain  $(\beta)$  of the bipolar transistor. The bipolar devices most sensitive to ionizing radiation are lateral PNP transistors, due to their relatively large interface to the field oxide. Figure 2.11 shows a measured  $\beta$ -degradation for different bipolar devices [11].

#### 2.3.2 Dependency on the Dose Rate [11, 12]

For some bipolar processes, a variation of the damage with the dose rate has been reported, e.g. in [13]. In such cases, transistors (both NPN and PNP) show an excess base current by a factor of typically 10 to 20 more at a low dose rate (0.1 rad/s) compared to a high rate (1 krad/s). This effect is due to the formation of trapped charges

|        | Proton | Neutron | Electron |

|--------|--------|---------|----------|

| 1 MeV  |        | 2       | 0.01     |

| 50 MeV | 2      |         |          |

| 1 GeV  | 1      |         | 0.1      |

Table 2.2: Relative displacement damage for various particles and energies [15]

in the oxide that is overlaying the emitter-base junction. The net trapped charge in that oxide is higher at lower dose rates.

A precise prediction on the dose rate behaviour of a bipolar device cannot be given. Therefore, an experimental characterization, usually performed at elevated temeperatures ( $\approx 90^{\circ}$ ) to enhance the damage, is performed.

#### 2.3.3 Displacement Damage

Particles or photons that cross silicon and transfer energy of about 20 eV to a silicon atom, can remove the atom from its lattice location. This displacement damage creates clusters of defects by changing the electronic structure around the displaced atom in the lattice. The total damage due to displacement is proportional to the non-ionizing energy loss (NIEL), which in turn depends on the particle type and its energy. The displacement damage is usually not measured by the absorbed energy, but measured by the effect on the device. For a particle of known energy, the NIEL in silicon can be calculated [14] and these distributions can be used to estimate the relative damage of radiation due to displacement. Table 2.2 shows a comparison for some particle types at different energies.

The damage in silicon due to displacement results in three different effects:

- 1. Mid-gap states are formed between the valence and the conduction band. Since the direct transition of electrons from the valence to the conduction band is rather unlikely, the formation of mid-gap states enables electrons from the valence band to jump to the conduction band via the mid-gap states. Theses electrons would then contribute to the current flow. On the other hand, mid-gap states can capture electrons from the conduction band which then capture holes from the valence band. This process would reduce the current flowing in the conduction band. Whether generation or recombination is dominating depends only on the relative concentration of carriers and empty defect states. Therefore, in a depletion region, where the conduction band is less populated, generation of charge carriers dominates and in a forward biased junction, where the conduction band is filled, recombination is the dominating effect.

- 2. The formation of states close to the conduction band allows trapping of charge carriers for a limited time. This effect reduces the charge carrier concentration in a forward biased region.

- 3. The effective doping characteristics is changed.

Figure 2.12: DC current gain of NPN and PNP transistors before and after irradiation with protons of 800 MeV to a fluence of  $1.2 \cdot 10^{14} cm^{-2}$  [16].