### **Utah State University**

# DigitalCommons@USU

All Graduate Theses and Dissertations

**Graduate Studies**

5-2014

# **Graphics Processing Unit-Based Computer-Aided Design** Algorithms for Electronic Design Automation

Yiding Han Utah State University

Follow this and additional works at: https://digitalcommons.usu.edu/etd

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Han, Yiding, "Graphics Processing Unit-Based Computer-Aided Design Algorithms for Electronic Design Automation" (2014). All Graduate Theses and Dissertations. 3868.

https://digitalcommons.usu.edu/etd/3868

This Dissertation is brought to you for free and open access by the Graduate Studies at DigitalCommons@USU. It has been accepted for inclusion in All Graduate Theses and Dissertations by an authorized administrator of DigitalCommons@USU. For more information, please contact digitalcommons@usu.edu.

# GRAPHICS PROCESSING UNIT-BASED COMPUTER-AIDED DESIGN ALGORITHMS FOR ELECTRONIC DESIGN AUTOMATION

by

### Yiding Han

A dissertation submitted in partial fulfillment of the requirements for the degree

of

#### DOCTOR OF PHILOSOPHY

in

Electrical Engineering

| Approved:               |                                        |

|-------------------------|----------------------------------------|

|                         |                                        |

| Dr. Koushik Chakraborty | Dr. Sanghamitra Roy                    |

| Major Professor         | Committee Member                       |

| Dr. Chris Winstead      | Dr. YangQuan Chen                      |

| Committee Member        | Committee Member                       |

| Dr. Dan Watson          | Dr. Mark R. McLellan                   |

| Committee Member        | Vice President for Research and        |

|                         | Dean of the School of Graduate Studies |

$\begin{array}{c} \text{UTAH STATE UNIVERSITY} \\ \text{Logan, Utah} \end{array}$

Copyright © Yiding Han 2014

All Rights Reserved

iii

Abstract

Graphics Processing Unit-Based Computer-Aided Design Algorithms for Electronic Design

Automation

by

Yiding Han, Doctor of Philosophy

Utah State University, 2014

Major Professor: Dr. Koushik Chakraborty

Department: Electrical and Computer Engineering

This dissertation presents research focusing on reshaping the design paradigm of elec-

tronic design automation (EDA) applications to embrace the computational throughput of

a massively parallel computing architecture. The EDA industry has gone through major

evolution in algorithm designs over the past several decades, delivering improved and more

sophisticated design tools. Today, these tools provide a critical platform for modern inte-

grated circuit (IC) designs composed of multi-billion transistors. However, most of these

algorithms, although showcasing tremendous improvements in their capabilities, are based

on a sequential Von Neumann machine, with limited or no ability to exploit concurrency.

While such limitation did not pose any significant end effect in the past, the advent of

commodity multicores during the beginning of this decade created a need to embrace con-

currency in many fields, including EDA algorithms. This need is now fast gaining urgency

with the recent trends in the emergence of the general purpose computation on graphics

processor units (GPU).

Through algorithmic overhaul, and novel solution space exploration strategies, this

research has shown a concrete path in which inherently sequential problems can benefit

from the massively parallel hardware, and gain higher computation throughput. Broadly,

two important EDA topics are discussed in this dissertation: (1) A floorplanner using a GPU-based simulated annealing algorithm, and (2) a global router framework using GPU architecture and a fast congestion analysis framework. Both topics aim to use GPU as a testbed for high throughput computation. Optimization strategies are studied for the GPU implementations. The GPU-based floorplanning algorithm is able to render 4-166X speedup, while achieving similar or improved solutions compared with the sequential algorithm. The GPU-based global routing algorithm is shown to achieve significant speedup against existing state-of-the-art global routers, while delivering competitive solution quality. The proposed methodology of a design paradigm shift for sequential EDA algorithms has a profound impact on the efficiency and design quality of future IC design flow.

(144 pages)

$\mathbf{V}$

Public Abstract

Graphics Processing Unit-Based Computer-Aided Design Algorithms for Electronic Design

Automation

by

Yiding Han, Doctor of Philosophy

Utah State University, 2014

Major Professor: Dr. Koushik Chakraborty

Department: Electrical and Computer Engineering

The electronic design automation (EDA) tools are a specific set of software that play

important roles in modern integrated circuit (IC) design. These software automate the

design processes of IC with various stages. Among these stages, two important EDA design

tools are the focus of this research: floorplanning and global routing. Specifically, the goal

of this study is to parallelize these two tools such that their execution time can be signifi-

cantly shortened on modern multi-core and graphics processing unit (GPU) architectures.

The GPU hardware is a massively parallel architecture, enabling thousands of independent

threads to execute concurrently. Although a small set of EDA tools can benefit from using

GPU to accelerate their speed, most algorithms in this field are designed with the single-core

paradigm in mind. The floorplanning and global routing algorithms are among the latter,

and difficult to render any speedup on the GPU due to their inherent sequential nature.

This work parallelizes the floorplanning and global routing algorithm through a novel

approach and results in significant speedups for both tools implemented on the GPU hard-

ware. Specifically, with a complete overhaul of solution space and design space exploration,

a GPU-based floorplanning algorithm is able to render 4-166X speedup, while achieving sim-

ilar or improved solutions compared with the sequential algorithm. The GPU-based global

routing algorithm is shown to achieve significant speedup against existing state-of-the-art routers, while delivering competitive solution quality. Importantly, this parallel model for global routing renders a stable solution that is independent from the level of parallelism. In summary, this research has shown that through a design paradigm overhaul, sequential algorithms can also benefit from the massively parallel architecture. The findings of this study have a positive impact on the efficiency and design quality of modern EDA design flow.

This dissertation is lovingly dedicated in memory of my father, Fei Han, and of my grandfather, Zhenyi Chen, who each inspired my life through their strength, faith, and love.

## Acknowledgments

I would like to express my very great appreciation to my adviser, Dr. Chakraborty, for his insightful advice, generous financial support, and patient guidance throughout my entire PhD research. Without his motivation and insights this work would have never been complete. Also, I would like to thank Dr. Roy for assisting me in many publications, her useful critiques of this research, as well as her teachings which helped me tremendously in understanding the EDA algorithms. Also, I would like to express my deep gratitude to all of my committee members, Dr. Chen, Dr. Winstead, and Dr. Waston, for their valuable comments on this research, and the patience to work with me even with the barrier of long distances.

I would like to thank various student members of the Bridge Lab for their constant support, encouragement, as well as making Bridge Lab such a pleasant and rewarding place to work. Specifically, I would like to thank Vilasita for her assistance in the initial work of GPU-based floorplanning; Dean for his valuable contribution and insights for the GPU-based global routing work; and Saurabh for the opportunity to work on the project involving timing analysis of NBTI aging effects. I wish also to acknowledge the help provided by Kshitij Bhardwaj, Jason Allred, Hu Chen, Manzi Dieudonne, Rajesh JS., Harshitha Pulla, Brian Cluff, and Shayan Taheri.

I would like to express my great appreciation to the ECE department and all of the staff members, for offering me this opportunity of PhD research, as well as the financial assistance towards my tuition. I would like to offer my special thanks to Dr. Moon for helping me out in many tough situations. I am particularly grateful for the assistance given by Mary Lee Anderson and Tricia Brandenburg, who have helped me through numerous drafts and formatting of the dissertation. I would also like to extend my thanks to Trent Johnson and Scott Kimber for providing technical support and maintaining the computer laboratory.

Last, but not least, special thanks should be given to my lovely wife, Susanna, and everyone in our families, for their support and encouragement throughout my study.

Yiding Han

# Contents

| Page                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $oldsymbol{	ext{Abstract}}$                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Public Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Acknowledgments                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ist of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ist of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $oxed{Acronyms} \dots \dots$                                                                                                                                                                                                                                                                                                                      |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.1 EDA and Emerging GPU Computing Paradigm 1.1.1 Overview of Modern EDA Design Flow 1.1.2 Physical Design of EDA Flow 1.1.3 GPU in EDA Design Flow 1.1.4 Motivation 1.5 Contributions of this Research 1.6 A Floorplanner Using GPU-Based Simulated Annealing Algorithm 1.7 A GPU-CPU Hybrid Global Router 1.8 A Fine Grain Concurrency Model for Global Router on GPU 1.9 A Congestion Analysis                                                       |

| Literature Survey and Related Work       1         2.1 EDA on GPU       1         2.2 Floorplanning and Parallelization       1         2.3 Global Router: Current Methodology       1         2.3.1 Maze Routing       1         2.3.2 Pattern Routing       1         2.4 Global Routing: Routing Framework       1         2.4.1 Rip-up and Re-route (RRR)       1         2.4.2 Integer Programming       1         2.5 Congestion Analysis       1 |

| General Purpose GPU Computing                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4 | $\mathbf{GP}$ | U-Based Floorplanning                                           | 5 |

|---|---------------|-----------------------------------------------------------------|---|

|   | 4.1           | Floorplanning                                                   | 5 |

|   |               | 4.1.1 B* Tree                                                   | 5 |

|   |               | 4.1.2 Simulated Annealing                                       | 6 |

|   |               | 4.1.3 GPU Design Issues                                         | 7 |

|   | 4.2           | GPU Floorplanning: Algorithm Overview and Specification         | 3 |

|   |               | 4.2.1 Algorithm Specification                                   | 3 |

|   |               | 4.2.2 Implementation: CPU-GPU Dataflow                          | 9 |

|   | 4.3           | Preliminary Results                                             | Э |

|   |               | 4.3.1 Methodology                                               |   |

|   |               | 4.3.2 Results                                                   |   |

|   |               | 4.3.3 Where Does Time Go in a GPU?                              |   |

|   | 4.4           | Performance Optimization                                        |   |

|   |               | 4.4.1 Limiting Data Copy to Shared Memory (OPT1)                |   |

|   |               | 4.4.2 Parallelize Device to Shared Memory Copy (OPT2)           |   |

|   |               | 4.4.3 Memory Access Coalescing (OPT3)                           |   |

|   |               | 4.4.4 Results                                                   |   |

|   |               | 4.4.5 Quality vs. Speedup                                       |   |

|   | 4.5           | Algorithm Restructuring to Improve Solution Quality             |   |

|   | 1.0           | 4.5.1 Algorithm Overview                                        |   |

|   |               | 4.5.2 Implementation                                            |   |

|   |               | 4.5.3 Results                                                   |   |

|   | 4.6           | Adapting Annealing in GPU                                       |   |

|   | 4.7           | Design Space Exploration                                        |   |

|   | 2             | 4.7.1 Solution Selection Through Binary Tree Reduction (BTR) 40 |   |

|   |               | 4.7.2 Annealing Diversity in GPU Threads (ADT)                  |   |

|   |               | 4.7.3 Dynamic Depth (DD)                                        |   |

|   |               | 4.7.4 Results                                                   |   |

|   | 4.8           | Conclusion                                                      |   |

|   |               |                                                                 |   |

| 5 |               | U-Based Global Routing                                          |   |

|   | 5.1           | Global Routing                                                  |   |

|   | 5.2           | Problem Definition                                              |   |

|   | 5.3           | Related Works on Global Routing                                 |   |

|   | 5.4           | Tackling GRP with GPU-CPU Hybrid System                         |   |

|   |               | 5.4.1 Wire Length Distribution of GRP                           |   |

|   |               | 5.4.2 GPU-CPU Hybrid                                            |   |

|   | 5.5           | Overview of GPU-CPU Global Routing                              |   |

|   |               | 5.5.1 Objective                                                 |   |

|   |               | 5.5.2 Design Flow                                               |   |

|   |               | 5.5.3 Global Routing Parallelization                            |   |

|   | 5.6           | Enabling Net Level Parallelism in Global Routing 62             |   |

|   |               | 5.6.1 Challenge in Parallelization of Global Routing 61         |   |

|   |               | 5.6.2 Achieving NLC                                             |   |

|   | 5.7           | Scheduler                                                       |   |

|   |               | 5.7.1 Scheduler Overview                                        | 4 |

|   |              | 5.7.2 Nets Data Dependency                        | 65       |

|---|--------------|---------------------------------------------------|----------|

|   |              | 5.7.3 Net Dependency Construction                 | 66       |

|   |              | 5.7.4 Implementation and Optimization             | 68       |

|   | 5.8          | Implementation                                    | 69       |

|   |              | 5.8.1 Maze Routing Implementation on GPU          | 69       |

|   |              | 5.8.2 GPU Memory Arrangement                      | 72       |

|   |              |                                                   | 74       |

|   |              | 5.8.4 Congested Region Identification (CRI)       | 75       |

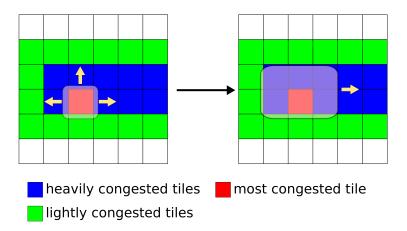

|   |              | 5.8.5 Bounding Box Expansion                      | 76       |

|   |              | 5.8.6 Workload Distribution Between GPU and CPU   | 78       |

|   | 5.9          | Results                                           | 79       |

|   |              | 5.9.1 GPU and CPU Router                          | 80       |

|   |              | 5.9.2 Comparison with NTHU-Route 2.0              | 81       |

|   | 5.10         | Conclusion                                        | 83       |

| 6 | CD           | U-Based Global Router with Fine-Grain Parallelism | 0 =      |

| O |              |                                                   | 85       |

|   | 6.1          |                                                   | 85       |

|   |              |                                                   | 86       |

|   | 6.0          |                                                   | 87       |

|   | 6.2          |                                                   | 89       |

|   |              |                                                   | 89       |

|   | 6.3          |                                                   | 91       |

|   | 0.5          |                                                   | 92       |

|   |              | · · · · · · · · · · · · · · · · · · ·             | 93       |

|   |              | 0                                                 | 93       |

|   |              |                                                   | 94       |

|   | 6.4          | 1 00                                              | 94       |

|   | 0.4          |                                                   | 94       |

|   |              | 8                                                 | 95<br>95 |

|   |              | v e                                               | 96       |

|   | 6 5          |                                                   | 97       |

|   | $6.5 \\ 6.6$ | 1                                                 | .00      |

|   | 0.0          | Conclusion                                        | .UC      |

| 7 | Con          | $_{ m logestion}$ Analysis                        | 02       |

|   | 7.1          | Problem Formulation                               | .03      |

|   | 7.2          | Motivation                                        | 03       |

|   | 7.3          | Orthogonal Congestion Correlation                 | .06      |

|   | 7.4          | Routing Technique                                 | .08      |

|   | 7.5          | Results                                           | .09      |

|   | 7.6          | Conclusion                                        | .11      |

| _ | ~            |                                                   |          |

| 8 |              |                                                   | 13       |

|   | 8.1          |                                                   | .13      |

|   | 8.2          |                                                   | .14      |

|   |              | 9                                                 | .14      |

|   |              | 8.2.2 Tackling Limitations of Bounding Box        | .15      |

|           | ٠ | ٠  | ٠ |  |

|-----------|---|----|---|--|

| v         | 1 | 1  | 1 |  |

| $\Lambda$ | 1 | -1 | 1 |  |

| References | <br> |

|------------|------|

| Vita       | <br> |

# List of Tables

| Table |                                                                                                                                                                | Page |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.1   | Throughput optimized floorplanning algorithm                                                                                                                   | 30   |

| 4.2   | CPU and GPU specs                                                                                                                                              | 31   |

| 4.3   | Preliminary results. Number of modules in a benchmark is indicated in parentheses                                                                              |      |

| 4.4   | Tradeoff in solution quality and speedup (G92). D and B represent the depth and breadth, respectively.                                                         |      |

| 4.5   | Tradeoff in solution quality and speedup (Tesla C1060). D and B represent the depth and breadth, respectively.                                                 |      |

| 4.6   | Comparison of using BTR, BTR+ADT, and BTR+DD. All results are in G92 machine with B=16, D=96, and $\Omega=2.$                                                  |      |

| 4.7   | CPU run time of GSRC hard-block benchmarks                                                                                                                     | 49   |

| 4.8   | Tradeoff in solution quality and speedup. B and D represent the breadth and depth, $\Omega$ represents the time of CPU moves. Results are from G92 GPU.        |      |

| 4.9   | Tradeoff in solution quality and speedup. B and D represent the breadth and depth, $\Omega$ represents the time of CPU moves. Results are from Tesla C1060 GPU |      |

| 5.1   | GPU Lee algorithm notations                                                                                                                                    | 73   |

| 5.2   | Algorithm notations                                                                                                                                            | 78   |

| 5.3   | Wire length and run time comparison with NTHU-Route 2.0 on overflow-free benchmarks                                                                            |      |

| 5.4   | Wire length and overflow comparison with NTHU-Route 2.0 on hard-to-route testcases.                                                                            |      |

| 5.5   | Speedup comparison in RRR stage                                                                                                                                | 83   |

| 6.1   | Routing performance comparison between the CPU and GPU routers. The comparison focuses on solution from the RRR stage                                          |      |

| 6.2 | Routing performance comparison between two state-of-the-art routers. Only RRR stage run time is counted to rule out the effects of pre- and post-routing stages from these routers | 99  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.3 | Normalized speed up and wire length comparison between the GPU router and the other routers. The percentage of wire length increase is denoted as "WL+"                            | 99  |

| 7.1 | ISPD benchmark results.                                                                                                                                                            | 111 |

# List of Figures

| Page |                                                                                                                                                                                                                                                                                       | Figure |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

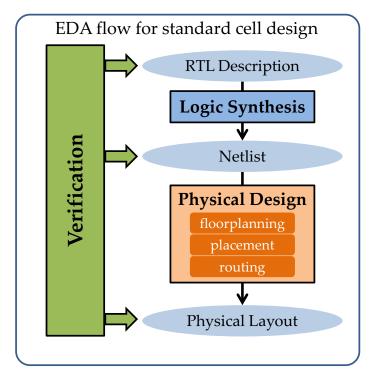

| 3    | The EDA design flow for standard cell consists of many stages, typically including logic synthesis, physical design, and verification tools                                                                                                                                           | 1.1    |

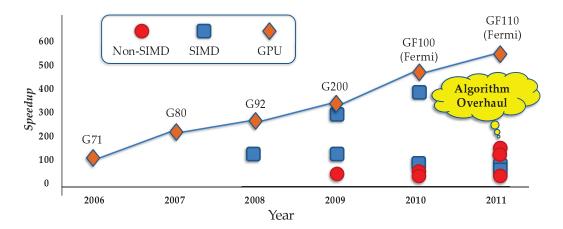

| 6    | Evolution of EDA algorithms in GPU platforms. The figure compares the speedup achieved in NVIDIA GPU architectures relative to a sequential processor (measured in giga-floating point operations), with the reported speedups from the first generation GPU-enabled EDA applications | 1.2    |

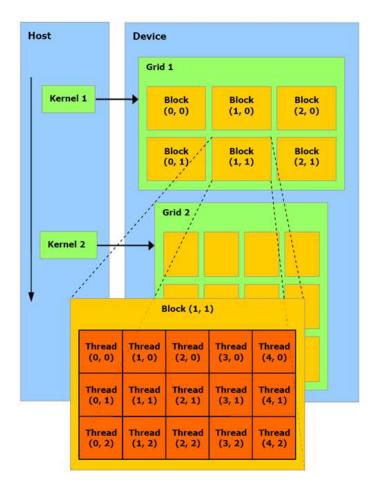

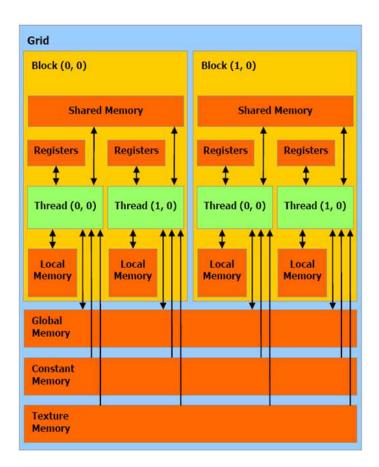

| 21   | CUDA thread hierarchy is configured in a Grid-Block-Thread model to allow programmer managing large quantity of parallel threads                                                                                                                                                      | 3.1    |

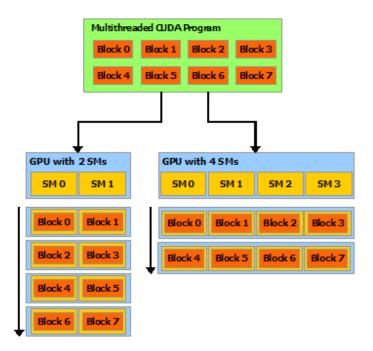

| 22   | CUDA grid can scale across different configurations of GPU hardware, and achieve the best possible workload balancing during runtime                                                                                                                                                  | 3.2    |

|      | CUDA abstracts the GPU memory subsystem in a hierarchical manner. Its different memory components exhibit diverse characteristics, which should be taken into extensive consideration for performance optimization of a GPU application                                               | 3.3    |

| 26   | Floorplanning with CPU                                                                                                                                                                                                                                                                | 4.1    |

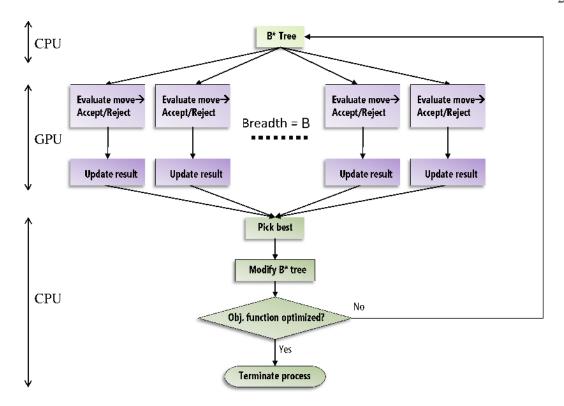

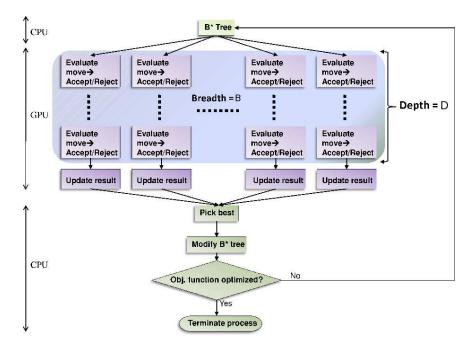

| 29   | Floorplanning in CPU-GPU                                                                                                                                                                                                                                                              | 4.2    |

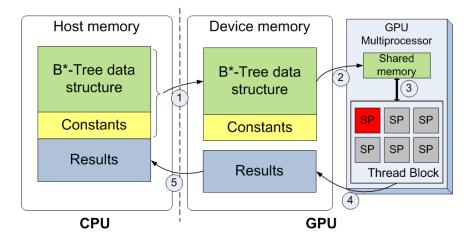

| 31   | Dataflow between CPU and GPU. Active thread is shown with a darker shading within a thread block                                                                                                                                                                                      | 4.3    |

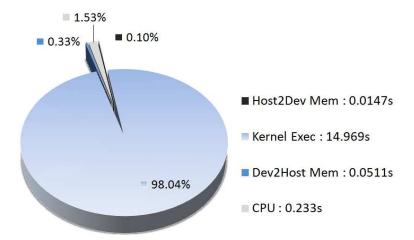

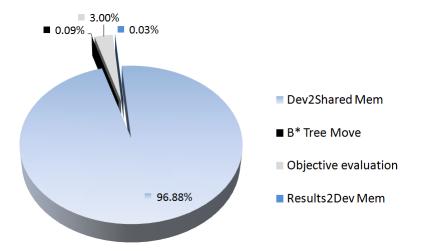

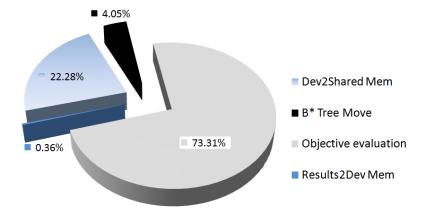

| 33   | Execution time breakdown for ami49                                                                                                                                                                                                                                                    | 4.4    |

| 34   | GPU execution time breakdown for ami49                                                                                                                                                                                                                                                | 4.5    |

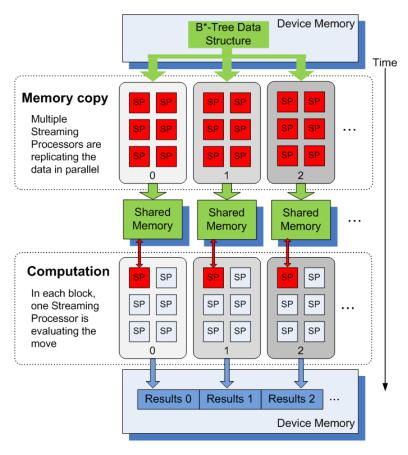

| 36   | Parallelizing data movement between shared memory and device. Active threads on streaming processors (SP) are shown with darker shading within a thread block                                                                                                                         | 4.6    |

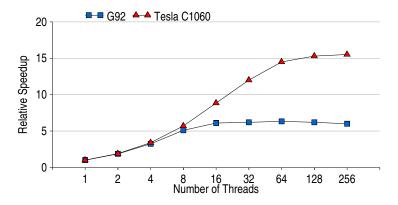

| 36   | Speedup comparison with concurrent threads to copy data                                                                                                                                                                                                                               | 4.7    |

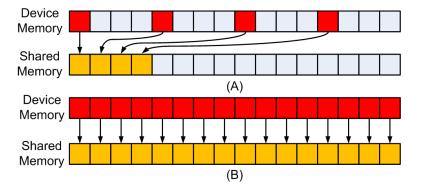

| 37   | (A) Non-coalesced device memory access. Only four threads are active in the transaction. (B) Coalesced device memory access. Sixteen data elements are copied in one transaction                                                                                                      | 4.8    |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | xvii |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.9  | GPU execution time breakdown for $ami49$ after optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38   |

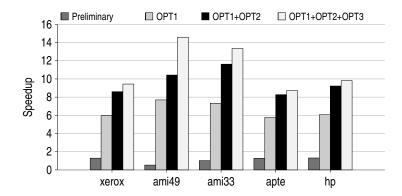

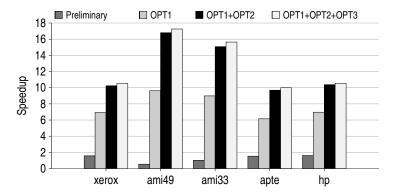

| 4.10 | Speedup achieved using G92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39   |

| 4.11 | Speedup achieved using Tesla C1060                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40   |

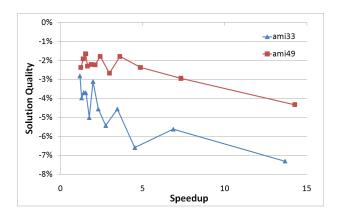

| 4.12 | Solution quality vs. speedup tradeoff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40   |

| 4.13 | New CPU-GPU floorplanning algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 42   |

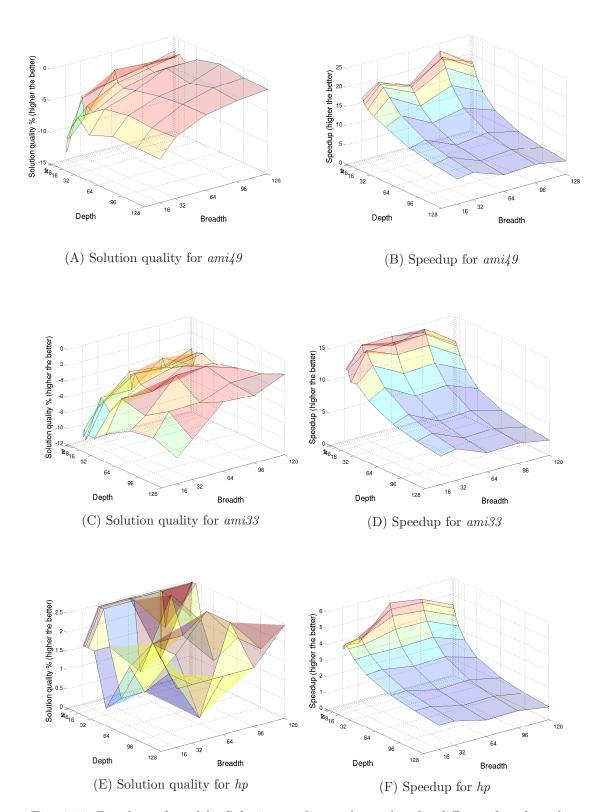

| 4.14 | Depth vs. breadth: Solution quality and speedup for different benchmarks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43   |

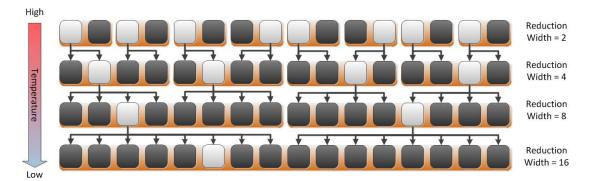

| 4.15 | One iteration of binary tree reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 48   |

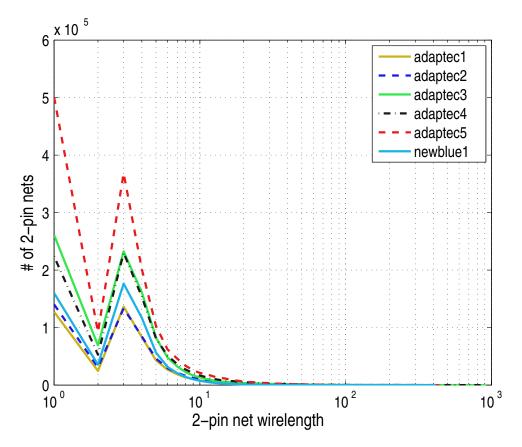

| 5.1  | Wire length distribution indicates co-existence of large number of long and short wires. Wire length is measured in Manhattan distance                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 58   |

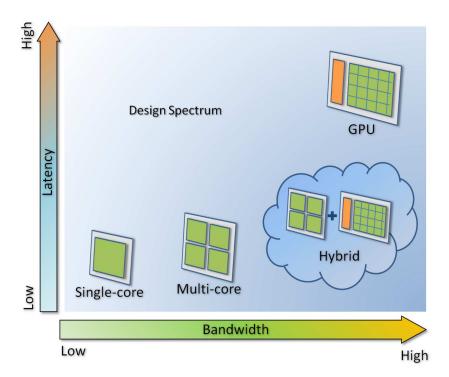

| 5.2  | Conceptual picture of computational bandwidth and latency of existing computing platforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 59   |

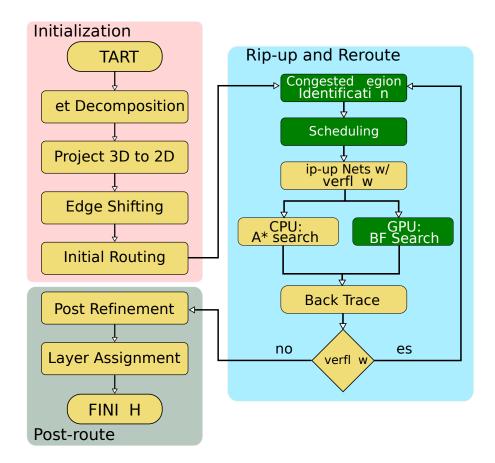

| 5.3  | Global router design flow: The top left section is initialization phase while bottom left is post-routing phase. Steps in these two sections are also present in other CPU-based routers. The right section is RRR. This section is enhanced with a scheduler. The contributions from this work are highlighted in dark shading background                                                                                                                                                                                                                                                                          | 61   |

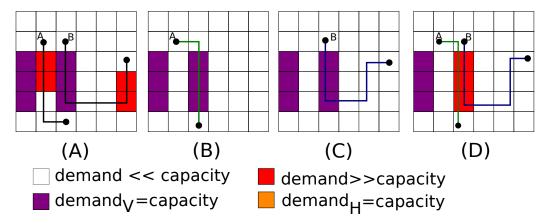

| 5.4  | Parallel router must have consistent view of resources. (A) Routings before RRR. (B) and (C) Viewpoint of each thread, which unknowingly allocates conflicted resources. (D) An overflow is realized at the end of RRR when both threads track back                                                                                                                                                                                                                                                                                                                                                                 | 62   |

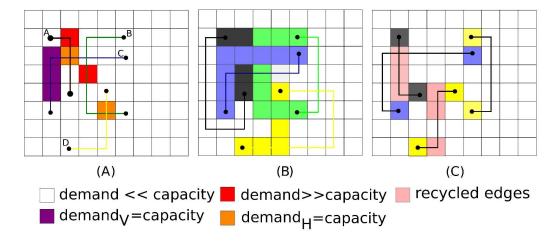

| 5.5  | Collision awareness alone can hurt routing solution: (A) Four-thread router processing a particular congested region, one net per thread. (B) Routing solution generated via collision-aware algorithm. Some resources are wasted due to overhead of collision awareness because threads are discouraged to route on cells (black, green, yellow, and blue cells) that were previously used by another thread. (C) With proper scheduling, only one thread is processing this particular region and some of the resources are recycled. Remaining threads are routing other congested areas on the chip (not shown) | 63   |

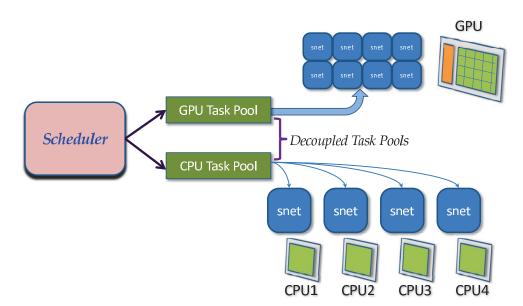

| 5.6  | Overview of GPU-CPU router concurrent subnets (snet) being distributed to GPU and CPU task pools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64   |

| 5.7  | Routing problem with nets overlapping each other                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 67   |

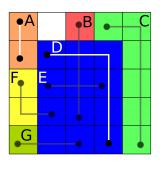

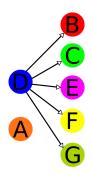

| 5.8  | Results after the 1st iteration: (A) Coloring of tiles: bigger nets dominate ownership over smaller ones. Only $A$ and $D$ can be routed together because other nets are dependent on $D$ . (B) Net dependencies are derived from the colorman                                                                                                                                                                                                                                                                                                                                                                      | 60   |

|      | colormap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 68   |

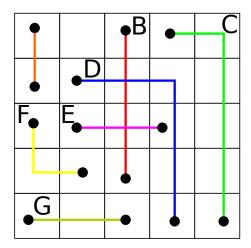

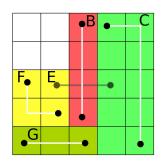

| 5.9  | Results after the 2nd iteration: (A) After $D$ and $A$ are routed, nets $C$ , $B$ , $F$ and $G$ can be routed together because they have no dependencies. (B) More detailed dependencies are revealed in the graph                                                  | 68  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.10 | Pathfinding in a GPU: The propagation starts from the source node. The breadth-first search fills up the entire search region, and continues until all frontiers are exhausted. Then the router back traces from the target node to find the shortest weighted path | 70  |

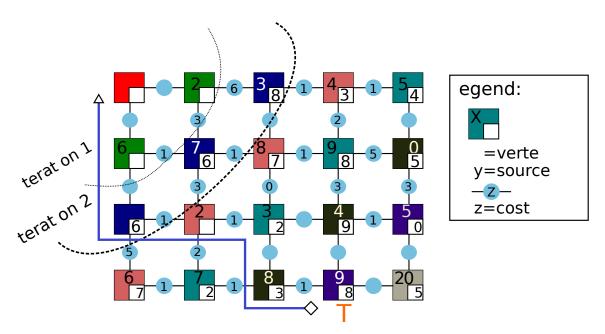

| 5.11 | GPU routing overview: Each thread block finds route for a single set of source and sink. The routing is done locally on the shared memory of each thread block                                                                                                      | 71  |

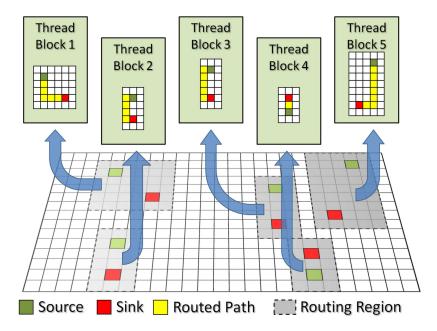

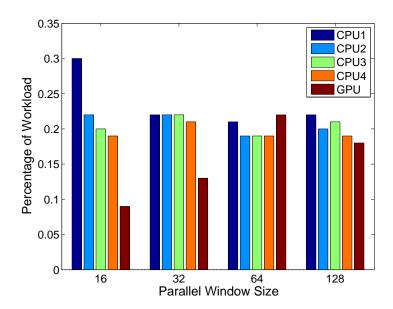

| 5.12 | Workload distribution with different task window. With the increasing size of parallel window, workload is easier to be balanced amongst CPUs and GPU, but it also comes at higher overhead                                                                         | 75  |

| 5.13 | Directional expansion algorithm: Bounding box adaptively expands in the directions with the highest congestion                                                                                                                                                      | 77  |

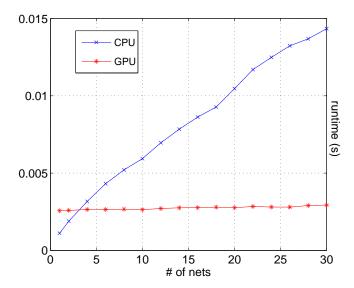

| 5.14 | Runtime comparison between CPU A*Search and GPU BFS                                                                                                                                                                                                                 | 80  |

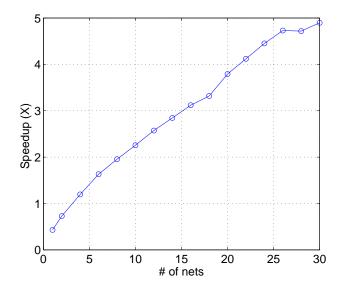

| 5.15 | Speedup of GPU BFS over CPU A*Search                                                                                                                                                                                                                                | 81  |

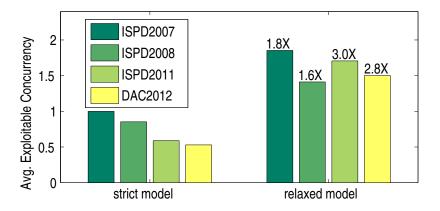

| 6.1  | Exploitable concurrency in ISPD2007, ISPD2008, ISPD2011, and DAC2012 benchmark suites. The y-axis is normalized to the strict model of ISPD2007.                                                                                                                    | 87  |

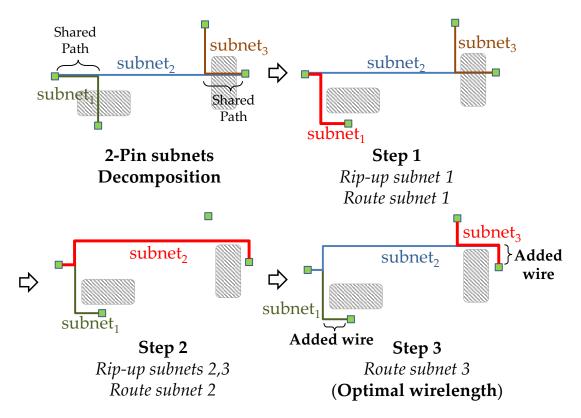

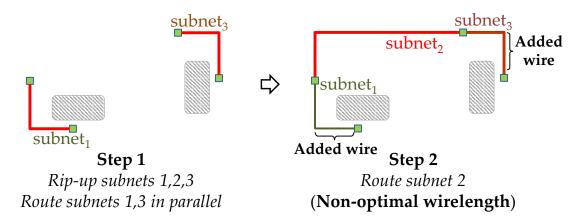

| 6.2  | Net level concurrency serializes the subnets of the same net to rebuild the net topology around obstacles, illustrated by the gray areas                                                                                                                            | 88  |

| 6.3  | Subnet level concurrency promotes concurrency, but relaxes the false data dependency, leading to degradation of solution quality                                                                                                                                    | 89  |

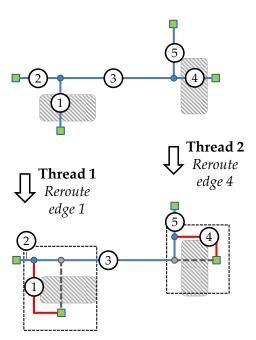

| 6.4  | The net is decomposed into five Steiner edges that do not have any shared path. Steiner edges 1 and 4 are re-routed in parallel in an asynchronous manner                                                                                                           | 90  |

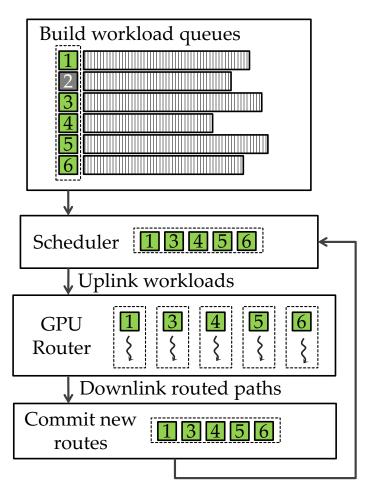

| 6.5  | The main GPU routing framework                                                                                                                                                                                                                                      | 92  |

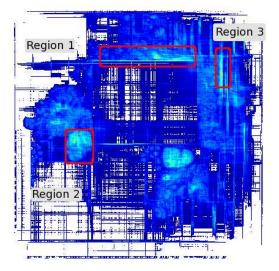

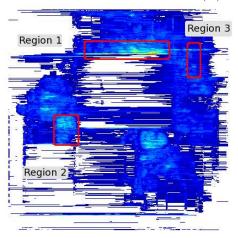

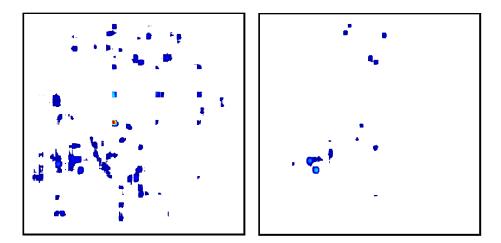

| 7.1  | Comparing congestion heat map and orthogonal congestion heat maps. Benchmark adaptec from ISPD 2007 suite.                                                                                                                                                          | 104 |

| 7.2  | OCC heat map after initial routing. Heat map highlights major hard-to-route areas.                                                                                                                                                                                  | 107 |

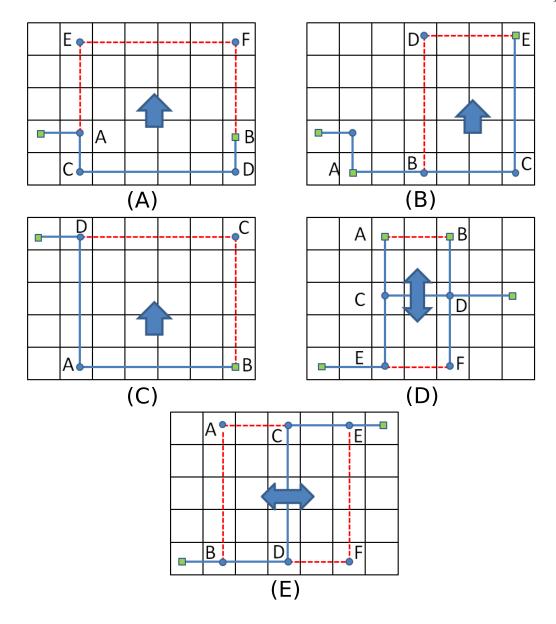

| 7.3  | Different types of moves to be generated on the net topology                                                                                                                                                                                                        | 110 |

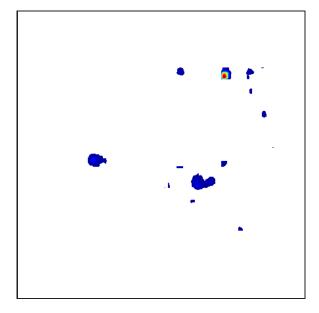

| 7.4  | OCC heat map of newblue7 Benchmark before and after DOC analysis                                                                                                                                                                                                    | 112 |

# Acronyms

EDA electronic design automation

IC integrated circuit

ASICs application-specific integrated circuits

FPGA field-programmable gate array

GPU graphic processing unit

API application programming interface

ILP integer linear programming

IP integer programming

GPGPU general purpose GPU

$\operatorname{SIMD}$  single instruction multiple data

SIMT single instruction multiple thread

SP streaming processor

CAD computer aided design

VLSI very-large-scale integration

CUDA compute unified device architecture

GRP global routing problem

RRR rip-up and re-route

IP integer programming

ILP integer linear programming

NLC net-level concurrency

FGC fine-grain concurrency

RSMT rectilinear Steiner minimal tree

# Chapter 1

### Introduction

As the design complexity of modern integrated circuit (IC) aggregates exponentially, the electronic design automation (EDA) tools, which provide a critical platform for computer-aided design, have become increasingly important. Modern EDA tools designs dedicate considerable efforts to improve the capability of handling complex design constraints and very large size circuits within limited design period. Most of these algorithms, although showcasing tremendous improvements over the past decades, are based on a sequential Von Neumann machine, which have very little ability to exploit concurrency.

Due to the advent of commodity multi-cores during the beginning of this decade, parallel computing has gradually become the major computational paradigm to replace sequential computing. In many data and arithmetic intense fields, including EDA, this shift of paradigm calls for an embrace of concurrency in algorithm designs. Broadly, there are two aspects to this shift: (1) parallelize the application to take advantage of the concurrency provided in modern hardware; (2) understand the performance characteristics of the parallel architectures for algorithmic and implementational optimization. Interestingly, this shift is now fast gaining urgency with the recent trends in the emergence of the general purpose computation on graphics processor units (GPU) [1].

#### 1.1 EDA and Emerging GPU Computing Paradigm

Modern GPUs are inherently concurrent designs, with several thousands of processing units within a single GPU. They not only demonstrate tremendous computation bandwidth (orders of magnitude improvement from commodity multicores), but also the ability to allow non-graphics applications to harness their computing prowess. It is the latter development that will make significant impact in EDA algorithms, as algorithms designed for GPUs in

the next decade are poised to bear little resemblance to the existing body of EDA tools.

This section briefly outlines the design flow of modern EDA tools (Section 1.1.1), draws the emphasis of this research in the physical design category of EDA tools (Section 1.1.2), and presents the current trend of GPU computing in EDA tools (Section 1.1.3).

#### 1.1.1 Overview of Modern EDA Design Flow

The EDA design flow is a combination of computer-aided design tools, which are used to accomplish the design of an integrated circuit (IC). EDA tools are specialized for different IC design methodologies, such as full custom design, application-specific integrated circuits (ASICs) standard cell design, and field-programmable gate array (FPGA) designs, etc.

This work addresses EDA tools that are specific for the ASICs standard cell design flow. During the ASICs flow, several stages of EDA design are used to bring an IC from register-transfer level (RTL) to graphic data system stream format (GDSII). RTL models a synchronous digital circuit with an abstraction of the hardware, while defining the signals, registers, and logical operations performed by the circuit. The EDA tool chain realizes the RTL circuit using components from ASICs standard cell libraries, and generates the output of the IC design in a GDSII format, which plots the physical layout of the circuit ready for chip fabrication.

An ASICs design flow can be further categorized as the following three classes: logic synthesis, physical design, and verification. Figure 1.1 illustrates this classification and the relations among these categories of tools. Starting with the logic synthesis tools, the goal of this stage is to translate the RTL specification into netlist, which consists of IP blocks, gates and interconnects, etc. These components are subsequently arranged and assembled by the physical design tools. The final design output is printed in GDSII format for fabrication. The verification tools are typically interleaved throughout the entire design process to ensure the IC meeting various design specifications. The verification includes many standalone processes, including logic simulation, timing analysis, formal verification, signal integrity check, and design rule checking, etc.

This work will mainly focus on design tools from the physical design family. Specifically,

Fig. 1.1: The EDA design flow for standard cell consists of many stages, typically including logic synthesis, physical design, and verification tools.

it studies tools for floorplanning and global routing of an IC. The following sections will further describe the roles of these physical design tools and address their design challenges.

#### 1.1.2 Physical Design of EDA Flow

The body of this research focuses on the physical design tools of EDA family. A typical physical design flow can be broadly divided into the placement and routing phase. The difference between these two phases is that the placement focuses on finding the physical locations IC components, such as transistors and IP blocks, while the routing phase focuses on the wiring among these components. The design flow starts with placement of the IC components and ends with successful routing of wires that connect the placed components.

The placement phase itself has multiple stages, typically consisting of floorplanning, global placement, and detailed placement. Each stage works with an abstraction of the physical layout in a top-down manner. Floorplanning divides the chip components into

relatively large size blocks and tries to find a close-to-optimal configuration to lay down these blocks within the chip area. Global placement finds general locations for all gates and modules, and detailed placement places them at exact locations on the IC chip.

Similarly, the routing phase is also multi-staged, including global routing and detailed routing. The routing phase is the most complex one throughout the EDA design flow, since it must obey all design and electrical rules of an IC. A multi-staged routing flow alleviates the complexity of the problems. First, global routing phase connects circuits on a coarse-grain level, which identifies and corrects large-scale congestion and routing issues. Then, detail routing takes the coarse-grain solution, and lays down the fine-grain physical interconnect on IC circuits. Typically, the interconnects are built as metal tracks and vias, hence their electrical characteristics must be taken into consideration to avoid problems such as crosstalk, antenna effects, etc. As the complexity of IC design grows, new design constraints are introduced to facilitate features such as multi-layer interconnects, multi-pattern lithography, and make routing extremely difficult.

In modern designs where routability becomes the primary obstacle, the usage of global routing is increasingly critical. To mitigate the routability issue, it is common to utilize congestion analysis tools to reveal routability issues in the early design stages, such as floor-planning and placement. With the early congestion information, designers can rearrange floorplan and massage placement of IC components to avoid a potentially difficult-to-route design. Interestingly, modified global routing engine can be used as a congestion analyzer, leading to a trend of integrating and interleaving global router with other tools in modern physical design flow.

#### 1.1.3 GPU in EDA Design Flow

The advent of GPU computing has successfully rendered improvement in runtime efficiency of many EDA design tools. Compute intensive algorithms like fault simulation, power grid simulation and event-driven logic simulation have been successfully mapped to GPU platforms to obtain significant speedups [2–5]. Recently, Liu and Hu proposed a gate sizing and threshold voltage algorithm optimized for GPUs [6]. Cong and Zou [7] use GPU com-

puting on a force-direct algorithm for global placement, which renders impressive speedup over the CPU sequential implementation. One key similarity in all these previous works is the presence of a fixed common topology/data structure across parallel threads that are fed with separate attributes for concurrent evaluation (e.g. distinct gate sizes and threshold voltages for a single circuit topology, distinct input patterns for a single circuit, distinct localization of components placement). The unmodified topology is highly amenable to the single instruction multiple thread (SIMT) style in GPUs, as it does not require frequent data modification and reuse.

The adaptation of GPU platform for EDA algorithms is, however, at an early stage. The focus of this work is to remodel floorplanning and global routing algorithms for GPU computing, which pioneers the GPU computation research. Specifically, this is the first work in open literature to apply GPU computing for floorplanning and global routing algorithms. Importantly, neither of these algorithms exhibit distinct topology for parallel computing as in the existing paradigm of GPU computing research. This challenge dictates novel context sensitive design space and exploration space explorations to overhaul the paradigm of existing sequential algorithms, formulating the main body of this research.

#### 1.2 Motivation

In contrast to several GPU adapted applications, a great number of EDA algorithms still struggle to keep pace with the performance improvement of GPU hardware platform, as illustrated in Figure 1.2. Typically, unlike applications with abundant data-parallel operations, these EDA applications have limited ability to explore concurrency with their irregular data structures and data dependencies. Even implemented on the GPU platform, the performance boost achieved in such category is considerably lower [7,8].

Among the above mentioned category are some of most computationally intensive EDA applications in the very large scale integrated (VLSI) circuit design flow. Today's aggressive technology scaling introduces many additional constraints in physical designs of VLSI circuits. Such explosion in design rules fundamentally increases the complexity of the problems such as placement and routing, which are two of the most time consuming stages of

Fig. 1.2: Evolution of EDA algorithms in GPU platforms. The figure compares the speedup achieved in NVIDIA GPU architectures relative to a sequential processor (measured in giga-floating point operations), with the reported speedups from the first generation GPU-enabled EDA applications.

VLSI physical design. However, these application typically adopt intrinsically sequential algorithms that are originally designed for a single-core architecture. Without altering the algorithms themselves, these applications can hardly benefit from the extra concurrency created by modern parallel architectures.

These EDA applications face a two-fold challenge. On the one hand, the drastically increased problem size and complexity dictates more complicated algorithms to ensure design quality. But these needs also prolong the design cycle and ultimately lead to delay of time-to-market; on the other hand, with the single-core performance coming at a halt, the performance of the single threaded EDA tools can hardly benefit from the hardware performance progression. As a result, without the ability to scale in parallel environment, these EDA applications can become bottle-neck of the VLSI design flow.

The key research question is whether it is possible to completely overhaul the aforementioned EDA algorithms, and reshape their design space exploration to better utilize the throughput of massively parallel computing platforms. This design philosophy elevates this research from existing general purpose GPU computing works, which mainly focus on inherently parallel applications. Through a design paradigm shift,

this research has shown that intrinsically sequential algorithms and applications can gain higher computational throughput using the massively parallel hardware. Importantly, although GPU is used as a testbed for high throughput computation, the proposed methodologies are developed in a generic manner widely applicable on parallel architectures at large.

### 1.3 Contributions of this Research

This research focuses on reshaping the design paradigm of EDA applications to embrace the computational throughput of a massively parallel computing architecture. Through algorithmic overhaul, and novel solution space exploration strategies, this research has shown a concrete path in which inherently sequential problems can benefit from the massively parallel hardware, and gain higher throughput. The designs of the GPU algorithms are generic for massively parallel architectures, making them applicable to other throughput computing platforms for future EDA applications.

Publications made during the period of this research are listed as follows:

#### Journal Papers

- Exploring High Throughput Computing Paradigm for Global Routing, Yiding Han,

Dean Michael Ancajas, Koushik Chakraborty, and Sanghamitra Roy, IEEE Transactions on Very Large Scale Integration Systems, Accepted

- Design and Implementation of a Throughput Optimized GPU Floorplanning Algorithm, Yiding Han, Koushik Chakraborty, Sanghamitra Roy and Vilasita Kuntamukkala, ACM Transactions on Design Automation of Electronic Systems, Volume 16, Issue 3, No. 23, June 2011, Pages 23:1–23:21

#### Conference Papers

- A Global Router on GPU Architecture, Yiding Han, Koushik Chakraborty, and Sanghamitra Roy, IEEE International Conference on Computer Design, 2013, Pages 74–80

- DOC: Fast and accurate congestion analysis for global routing, Sanghamitra Roy, Yiding Han, Koushik Chakraborty, IEEE 30th International Conference on Computer Design, 2012, pages 508–509

- Exploring High Throughput Computing Paradigm for Global Routing, Yiding Han,

Dean Michael Ancajas, Koushik Chakraborty, Sanghamitra Roy, Proceedings of IEEE/ACM

International Conference on Computer-Aided Design, November 2011, San Jose, Pages

298–305

- Optimizing Simulated Annealing on GPU: A Case Study with IC Floorplanning, Yiding Han, Sanghamitra Roy and Koushik Chakraborty, 12th IEEE International Symposium on Quality Electronic Design (ISQED), March 2011, Pages 1–7

- A GPU Algorithm for IC Floorplanning: Specification, Analysis and Optimization,

Yiding Han, Koushik Chakraborty, Sanghamitra Roy and Vilasita Kuntamukkala,

24th IEEE/ACM International VLSI Design Conference, 2011, Pages 159–164

#### 1.3.1 A Floorplanner Using GPU-Based Simulated Annealing Algorithm

This work proposes a fundamentally different approach of exploring the floorplan solution space. Several performance optimization techniques are demonstrated for this algorithm in GPUs. This research is published in the proceedings of VLSID-11 [9], ISQED-11 conferences [10]. A journal version is published in the TODAES-11 journal [11].

A novel floorplanning algorithm for GPUs is proposed. Floorplanning is an inherently sequential algorithm, far from the typical programs suitable for SIMT style concurrency in a GPU. In this work, a fundamentally different approach of exploring the floorplan solution space is proposed. It illustrate several performance optimization techniques for this algorithm in GPUs. To improve the solution quality, a comprehensive exploration of

the design space is presented, including various techniques to adapt the annealing approach in a GPU. Compared to the sequential algorithm, the proposed techniques achieve 6-188X speedup for a range of MCNC and GSRC benchmarks, while delivering comparable or better solution quality. The contributions of this work are:

- An algorithm to perform floorplanning on a GPU machine. This is the first work on GPU-based floorplanning.

- An in-depth analysis of the profiling in different GPU components, and illustrate several optimizations for the GPU floorplanning algorithm.

- A modified algorithm based on the speedup vs quality analysis to improve the solution quality, and show detailed results of the modified algorithm.

- Based on algorithmic foundation, a comprehensive design space exploration of the solution space is presented. The analysis spans from detailed breadth and depth analysis, adapting the annealing technique for GPU, and dynamic selection and exploration of the solution space.

#### 1.3.2 A GPU-CPU Hybrid Global Router

This is the first work on utilizing GPUs for global routing. It explores a hybrid GPU-CPU high-throughput computing environment as a scalable alternative to the traditional CPU-based router. A novel parallel model is proposed for router algorithms that aims to exploit concurrency at the level of individual nets. This work is published in the proceedings of ICCAD 2011 conference [12]. Its journal version is accepted by the TVLSI-12 journal.

With aggressive technology scaling, the complexity of the global routing problem is poised to rapidly grow. Solving such a large computational problem demands a high throughput hardware platform such as modern GPUs. This work explores a hybrid GPU-CPU high-throughput computing environment as a scalable alternative to the traditional CPU-based router. A *net level concurrency (NLC)* model is introduced. NLC is a novel parallel model for router algorithms that aims to exploit concurrency at the level of individual nets.

To efficiently uncover NLC, a *Scheduler* is designed to create groups of nets that can be routed in parallel. At its core, the Scheduler employs a novel algorithm to dynamically analyze data dependencies between multiple nets. Such an algorithm can lay the foundation for uncovering data-level parallelism in routing: a necessary requirement for employing average of 4X speedup over NTHU-Route 2.0 with negligible loss in solution quality. The contributions of this works are:

- An execution model that allows cooperation of the GPU and the CPU to route multiple nets simultaneously through NLC. The GPU global router uses a breadth first search (BFS) heuristic while the CPU router uses A\* search routing. Together, they provide two distinct classes in the routing spectrum. The high-latency low-bandwidth problems are tackled by the CPU, whereas the low-latency high-bandwidth problems are solved by the GPU. This classification is the key to efficiently tackle the complexity increase of the global routing problem on massively parallel hardware.

- A scheduler algorithm to explore NLC in the global routing problem. The scheduler

produces concurrent routing tasks for the parallel global routers based on net dependencies. The produced concurrent tasks are distributed to the parallel environments

provided by the GPU and multi-core CPU platforms. The scheduler is designed to

dynamically and iteratively analyze the net dependencies, hence limiting it computational overhead.

- A Lee algorithm based on breadth-first search path finding on a GPU. This algorithm

utilizes the massively parallel architecture for routing and back tracing. The approach

is able to find the shortest weighted path, and achieves high computational throughput

by simultaneously routing multiple nets.

#### 1.3.3 A Fine Grain Concurrency Model for Global Router on GPU

This is the first work that utilizes GPU alone for global routing, without offloading any routing workload to the CPU. Based on the net-level concurrency model proposed in the previous GPU-CPU hybrid concept, this work extended the concurrency model to a fine-grain level, which significantly improves the exploitable parallel workloads. A multi-agent GPU routing engine is developed based on A\* search algorithm. This work is published in the proceedings of ICCD 2013 conference [13].

In the modern VLSI design flow, global router is often utilized to provide fast and accurate congestion analysis for upstream processes to improve the design routability. Global routing parallelization is a good candidate to speedup its runtime performance while delivering very competitive solution quality. This work first study the cause of insufficient exploitable concurrency of the existing NLC model, which has become a major bottleneck for parallelizing the emerging design problems. It mitigates this limitation with a novel fine grain parallel model, with which a GPU-based multi-thread global router is designed. Experimental results indicate that the parallel model can effectively support the GPU-based global router, and deliver stable solutions. The contribution of this work includes:

- A concurrency model that exploits parallelism on the Steiner edge level. The main reason of the limited exploitable concurrency is identified to be a false data dependency in the NLC parallel model. The Steiner edge-based net decomposition scheme effectively mitigates this issue, and increases the exploitable concurrency.

- A routing engine on GPU architecture to allow multi thread global routing based on an A\* search multi-source multi-sink maze routing algorithm. This A\* search is designed broadly based on an existing A\* search GPU implementation, but specialized for global routing optimizations.

- The router is designed with the ability to work with the recent routability-driven benchmarks. Experimental results indicate successful parallelization with the GPU-based router, which renders a deterministic solution. Moreover, the run-time of the proposed global router is up to 3.0X faster than that of the NCTUgr2 [14].

#### 1.3.4 Congestion Analysis

This work presents a fast and accurate congestion analysis tool at the global routing stage. It focuses on capturing the difficult-to-solve congestion in global routing designs. The proposed framework identifies the routing congestion using a novel orthogonal congestion correlation (OCC) factor, which identifies the hard-to-route hot-spots. A key contribution of this work is a fast global router to minimize congestion caused by long nets and accurately reveal the distribution of hard-to-route spots due to high density short nets. The global router uses a dynamic representation of net to allow fast topology transformation. The proposed framework can evaluate the routability of a placement solution, and be utilized to aid the placer for a congestion-aware design.

The focuses of this research is in introducing new techniques to improve the accuracy of congested region detection, as well as reducing the runtime overhead of a congestion analyzer. The major contributions are as following:

- An accurate overflow identification approach based on a novel orthogonal congestion

analysis. The analysis uses a new metric to model the difficult-to-route region by

studying the nature of difficult-to-route problems. The proposed metric is shown to

be able to pinpoint problematic regions with high accuracy.

- A set of dynamic edge moves that can efficiently resolve congestion. As the efficiency

of routing engine plays a key role for congestion analysis, complex routing algorithm

is avoided to allow extremely fast analysis. The dynamic edge moves provides a fast

yet accurate routing methods for congestion analysis.

## Chapter 2

# Literature Survey and Related Work

A comprehensive literature survey is undertaken to build the foundation of this research. The relevant areas of this study includes the current adaptation of GPU for EDA tools, the existing body of research for floorplanning and its parallelization, previous works on global routing and its parallel schemes, and the advent of modern congestion analysis tools. To serve the purpose of a literature survey, the following sections are organized as follows: Section 2.1 outlines the previous works that utilize GPU for EDA applications to render speedup; Section 2.2 reviews the current floorplanning technologies and previous parallelization schemes; Section 2.3 lists a collection of existing global routing techniques; Section 2.4 visits the current frameworks used for global routing; Section 2.5 gives a survey on the congestion analysis research.

#### 2.1 EDA on GPU

Some EDA algorithms are able to enjoy the adaption to the GPU platform. Compute intensive algorithms like fault simulation, power grid simulation and event-driven logic simulation have been successfully mapped to GPU platforms to obtain significant speedups [2–5]. Recently, Liu and Hu proposed a gate sizing and threshold voltage algorithm optimized for GPUs [6]. One key advantage in many of these previous works is the *unmodified* topology/data structure across parallel threads, which make them highly amenable to the SIMT style in GPUs. More recently, GPU optimized algorithms for irregular computing patterns like sparse matrix vector product and breadth first graph traversal have been proposed [8]. These algorithms can be applied to certain EDA problems like static timing analysis and force directed placement that use sparse matrix operations. Cong and Zou also optimized the force-directed placement algorithm on GPU platforms [7]. Frishman and Tal used GPUs

to optimize force directed graph layout problem, where certain steps required simulated annealing [15, 16].

In contrast, the floorplanning and global routing algorithms pose severe challenges as they both involve a chain of dependent modifications to the data structures. There is little similarity between existing GPU work and the focus of this research. For example, the layout problem allowed partitioning the graphs, and calculating the desired objective in each partition. In IC floorplanning, no such partitioning is possible during objective calculation as a given move can impact nearly all possible blocks in the floorplan. Due to such fundamental differences in problem structure and resulting restrictions, their proposed algorithm with optimization techniques are not applicable for the GPU-based floorplanning research.

#### 2.2 Floorplanning and Parallelization

The modern fixed-outline floorplanners are typically based on simulated annealing algorithms [17–19]. The simulated annealing is a heuristic that applies random moves to a floorplan to approach for an optimal solution. It is shown recently by Zeng and Chen that searching agents such as random walk for optimal search is fundamentally linked with fractional dynamics [20], which can provide insight for future design and optimization of floorplanning algorithms.

Typically the existing fixed-outline floorplanning problems target to minimize overall area and half-parameter wire length. Cong et al. present a floorplanner to also consider thermal distribution of 3D ICs [21]. To improve the efficiency of modern floorplanner, a fast floorplanner for multilevel design is presented by Chen et al. [22], Chen and Chang present a fast simulated annealing based on B\*-tree representation [19]. However, all of the above floorplanning algorithms are based on sequential architectures.

There has also been some works on parallel simulated annealing, albeit not on floorplanning. Kravitz and Rutenbar [23] presents strategies for implementing simulated annealing-based standard cell placement on shared memory multiprocessors. They propose two orthogonal approaches to exploit parallelism: decomposing single move and compute multiple

moves simultaneously. Done by Rose et al. [24], a SA based standard cell placement algorithm generates and investigates different coarse placements to exploit parallelism. Another parallel simulated annealing is done by Ram et al. [25]. The authors propose to exploit parallelism by expanding the search space. Each processor individually performs SA on a solution space. However, algorithmic exposition for IC floorplanning, with optimization challenges in GPU.

#### 2.3 Global Router: Current Methodology

The global routing problem is NP-hard [26]. Therefore, heuristics are applied to reach the approximate optima of the global routing solution. In general, the algorithms used to solve global routing can be categorized into two classes: (1) sequential; (2) concurrent. The sequential algorithm is typically based on a rip-up and re-route (RRR) scheme, which rips-up the interconnects that cause overuse of routing resources and re-route their paths individually. The routing resources claimed by the previously routed paths have deterministic affects on the decisions made to route the later paths. For this reason, nets in general must be routed in an explicit sequential order.

The concurrent algorithm often utilizes the integer programming approaches, which attempt to route all nets concurrently. The global routing problem is modeled with {0, 1}-integer linear programming (ILP) problem that selects solutions out of candidate paths that optimize the desired global objectives. Such approaches typically possess better global information to the problem, hence can reach a much closer approximation to the optima than the sequential approach. However, in a run time comparison, the concurrent algorithms are generally significantly slower.

Routing techniques solve the fundamental problem in global routing of finding the least costly path to connect two vertices on a rectilinear grid map. Current routing techniques can be roughly categorized into two classes: (1) maze routing; (2) pattern routing.

#### 2.3.1 Maze Routing

Maze routing was first introduced by Moore [27]. The core procedure of maze routing

has two stages: propagation and back-tracing. The propagation phase creates a wave from the source node, and spreads out the wave on a grid map to search for sink node. Once found, the back-tracing stage identifies the least costly path in a reverse direction connecting sink to source node.

Several algorithms have been proposed to realize maze routing for VLSI global routing problem, among these are Lee algorithm [28], Hadlock's algorithm [29], Dijkstra's algorithm [30], and extensions of the Dijkstra's algorithm, such as the A\* search algorithm [31]. These algorithms have significantly enhanced maze routing in memory allocation and run time, although maze routing's main procedure remains intact.