# University of Massachusetts Amherst ScholarWorks@UMass Amherst

**Doctoral Dissertations**

**Dissertations and Theses**

November 2015

# Physically Equivalent Intelligent Systems for Reasoning Under Uncertainty at Nanoscale

Santosh Khasanvis University of Massachusetts - Amherst

Follow this and additional works at: https://scholarworks.umass.edu/dissertations\_2

Part of the Computer and Systems Architecture Commons, Nanoscience and Nanotechnology Commons, Other Computer Engineering Commons, and the VLSI and Circuits, Embedded and Hardware Systems Commons

# **Recommended Citation**

Khasanvis, Santosh, "Physically Equivalent Intelligent Systems for Reasoning Under Uncertainty at Nanoscale" (2015). *Doctoral Dissertations*. 456. https://scholarworks.umass.edu/dissertations\_2/456

This Open Access Dissertation is brought to you for free and open access by the Dissertations and Theses at ScholarWorks@UMass Amherst. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

# PHYSICALLY EQUIVALENT INTELLIGENT SYSTEMS FOR REASONING UNDER UNCERTAINTY AT NANOSCALE

A Dissertation Presented

by

# SANTOSH KHASANVIS

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

September 2015

Department of Electrical and Computer Engineering

© Copyright by Santosh Khasanvis 2015 All Rights Reserved

# PHYSICALLY EQUIVALENT INTELLIGENT SYSTEMS FOR REASONING UNDER UNCERTAINTY AT NANOSCALE

A Dissertation Presented

by

# SANTOSH KHASANVIS

Approved as to style and content by:

Csaba Andras Moritz, Chair

Israel Koren, Member

C. Mani Krishna, Member

Jayasimha Atulasimha, Member

Christopher V. Hollot, Department Head Electrical and Computer Engineering

### ACKNOWLEDGEMENTS

I am forever indebted to my advisor Prof. Csaba Andras Moritz, for his constant encouragement, guidance, and mentorship. This dissertation would not have been possible without his direction. I am grateful to my dissertation committee members Prof. Koren, Prof. Krishna and Prof. Atulasimha for their valuable feedback and suggestions. I would like to acknowledge collaborations with the research group directed by Prof. Atulasimha and Prof. Bandyopadhyay at Virginia Commonwealth University, and thank their students Ayan K. Biswas and Mohammad Salehi Fashami for all their hard work in providing us with data for straintronic magnetic tunneling junctions used extensively in this work.

I have benefited immensely from working with several creative, intelligent and dedicated colleagues. Foremost is Mostafizur Rahman, who has been a close friend and an anchor during my PhD. I would like to thank Dr. Pritish Narayanan, who was a mentor during my initial years and continues to be a close friend. I would also like to express my gratitude to Mingyu Li for his assistance in making this dissertation possible. Finally, I would like to express my sincere gratitude to my entire family for their continued love and support through all these years.

I would like to acknowledge support from Center for Hierarchical Manufacturing at UMass Amherst and National Science Foundation grant no. 1407906 at UMass Amherst.

### ABSTRACT

# PHYSICALLY EQUIVALENT INTELLIGENT SYSTEMS FOR REASONING UNDER UNCERTAINTY AT NANOSCALE

### SEPTEMBER 2015

## SANTOSH KHASANVIS

# B.TECH., VELLORE INSTITUTE OF TECHNOLOGY UNIVERSITY, VELLORE, INDIA

#### M.S., UNIVERSITY OF MASSACHUSETTS AMHERST

## Ph.D., UNIVERSITY OF MASSACHUSETTS AMHERST

# Directed by: Professor Csaba Andras Moritz

Machines today lack the inherent ability to reason and make decisions, or operate in the presence of uncertainty. Machine-learning methods such as Bayesian Networks (BNs) are widely acknowledged for their ability to uncover relationships and generate causal models for complex interactions. However, their massive computational requirement, when implemented on conventional computers, hinders their usefulness in many critical problem areas e.g., genetic basis of diseases, macro finance, text classification, environment monitoring, etc. We propose a new non-von Neumann technology framework purposefully architected across all layers for solving these problems efficiently through *physical equivalence*, enabled by emerging nanotechnology. The architecture builds on a probabilistic information representation and multi-domain mixedsignal circuit style, and is tightly coupled to a nanoscale physical layer that spans magnetic and electrical domains. Based on bottom-up device-circuit-architecture simulations, we show up to four orders of magnitude performance improvement (using computational resolution of 0.1) vs. best-of-breed multi-core machines with 100 processors, for BNs with about a million variables. Smaller problem sizes of  $\sim 100$  variables can be realized at 20 mW power consumption and very low area around a few tenths of a mm<sup>2</sup>. Our vision is to enable solving complex Bayesian problems in real time, as well as enable intelligence capabilities at a small scale everywhere, ushering in a new era of machine intelligence.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS iv                                                                          |

|----------------------------------------------------------------------------------------------|

| ABSTRACTv                                                                                    |

| LIST OF TABLESx                                                                              |

| LIST OF FIGURES xi                                                                           |

| 1. INTRODUCTION1                                                                             |

| 1.1 Notion of Physical Equivalence2                                                          |

| 1.2 Conceptual Framework Overview                                                            |

| 1.3 Limitations of Conventional Implementations4                                             |

| 1.4 Proposed Approach to Overcome Deficiencies in Conventional Implementation5               |

| 2. BAYESIAN NETWORKS9                                                                        |

| 2.1 BN Inference using Pearl's Belief Propagation11                                          |

| 2.2 BN Learning                                                                              |

| 2.3 BN Adaptation14                                                                          |

| 2.4 Summary14                                                                                |

| 3. PHYSICALLY EQUIVALENT DATA REPRESENTATION AND<br>PROBABILITY COMPOSER CIRCUIT FRAMEWORK16 |

| 3.1 Data Representation16                                                                    |

| 3.2 Technology Overview: Straintronic MTJs17                                                 |

| 3.3 Probability Representation using Straintronic MTJs22                                     |

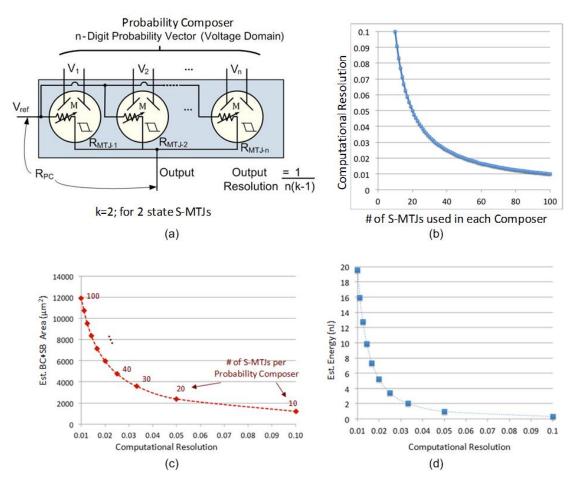

| 3.4 Resolution Scaling with Probability Composer23                                           |

| 3.5 Decomposer Element27                                                                     |

| 3.6 Fault Resilience (Supporting Graceful Degradation)                                       |

| 3.7 Probability Arithmetic Composer Circuit Framework                                                                 |    |

|-----------------------------------------------------------------------------------------------------------------------|----|

| 3.8 Elementary Arithmetic Composers                                                                                   |    |

| 3.9 Summary                                                                                                           | 42 |

| 4. PHYSICALLY EQUIVALENT ARCHITECTURE FOR REASONING UNCERTAINTY                                                       |    |

| 4.1 Bayesian Cell Description                                                                                         | 45 |

| 4.3 Switch Box Description                                                                                            | 53 |

| 4.3 Summary                                                                                                           | 55 |

| 5. EVALUATION AND BENCHMARKING                                                                                        | 56 |

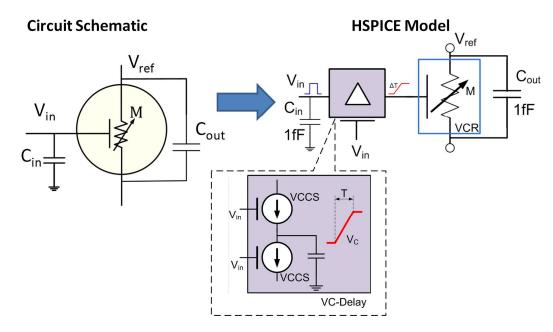

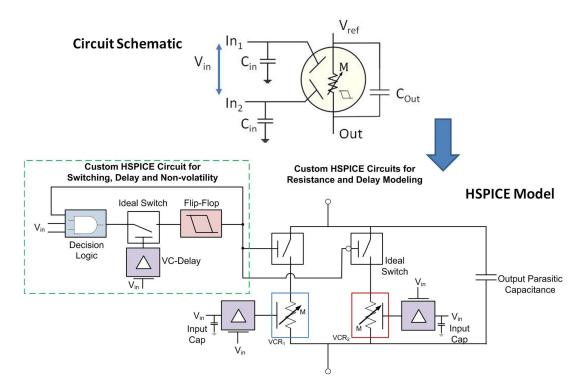

| 5.1 HSPICE Device Models                                                                                              | 56 |

| 5.1.1 Volatile S-MTJ HSPICE Macromodel                                                                                | 56 |

| 5.1.2 Non-volatile S-MTJ HSPICE Macromodel                                                                            | 59 |

| 5.2 Evaluation of Composers used in Bayesian Inference Operations                                                     | 62 |

| 5.3 Comparison of BN Inference on Physically Equivalent Implementation vs.<br>Implementation on Multi-core Processors | 64 |

| 5.3.1 Example Bayesian Network                                                                                        | 66 |

| 5.3.2 Analytical Model for Runtime Estimation of BN Inference on CMOS<br>Multicore Processor                          | 67 |

| 5.3.3 Runtime Estimation of Inference on Proposed Physically Equivalent<br>Architecture                               | 72 |

| 5.4 Benchmarking Results                                                                                              | 73 |

| 5.5 Discussion on BN Accuracy                                                                                         | 75 |

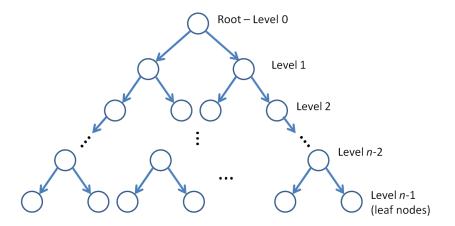

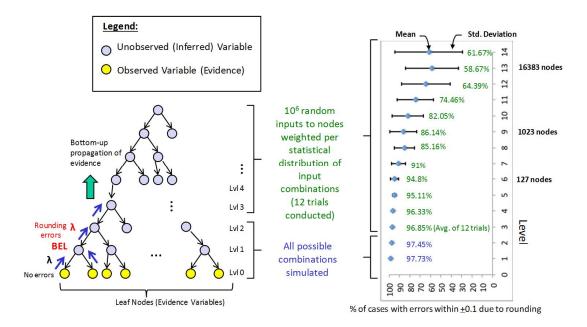

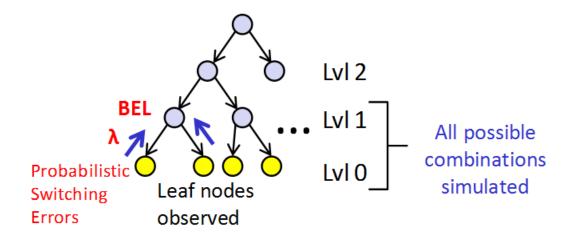

| 5.5.1 Study on Error Propagation due to Rounding in Binary Tree                                                       | 77 |

| 5.5.2 Effect of Errors due to Probabilistic Switching of S-MTJs                                                       | 81 |

| 5.6 Improving Computational Resolution for Probability Composers and Decomposers | 83 |

|----------------------------------------------------------------------------------|----|

| 6. CONCLUSION                                                                    | 87 |

| APPENDIX: LIST OF PUBLICATIONS                                                   | 90 |

| BIBLIOGRAPHY                                                                     |    |

# LIST OF TABLES

| Table 1. Decomposer Element Operation                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------|

| Table 2. Comparison: von Neumann Approach vs. Physical Equivalence Approach43                                                       |

| Table 3. Switching Criteria Encoded in Decision Circuit for HSPICE Macromodeling of Non-Volatile S-MTJ61                            |

| Table 4. Evaluation of Composer Circuits for Bayesian Inference (Resolution is 0.1)63                                               |

| Table 5. Hardware Specifications for CMOS Multi-core Processors*         65                                                         |

| Table 6. Sequence of steps for a BN binary tree with 7 levels (127 nodes)         69                                                |

| Table 7. Impact of S-MTJ switching errors and rounding errors on belief values at Level         1 in the binary tree BN (Figure 39) |

# LIST OF FIGURES

| Figure 1. Part of a BN with showing node x whose child nodes are y, z and p | parent node is         |

|-----------------------------------------------------------------------------|------------------------|

| A. Outcomes of states of child nodes determine likelihood of pare           | nt. All nodes          |

| have four states in this example. Each node maintains likelihoo             | d vector $(\lambda)$ , |

| prior vector $(\pi)$ , belief vector (BEL), and conditional probability     | table (CPT).           |

| The CPT information and messages from child/parent nodes                    | are used to            |

| calculate $\lambda$ , $\pi$ , and BEL vectors during Bayesian inference     | 9                      |

|                                                                             |                        |

Figure 2. Pseudo-code for BN Structure Search with Hill-Climbing Algorithm......13

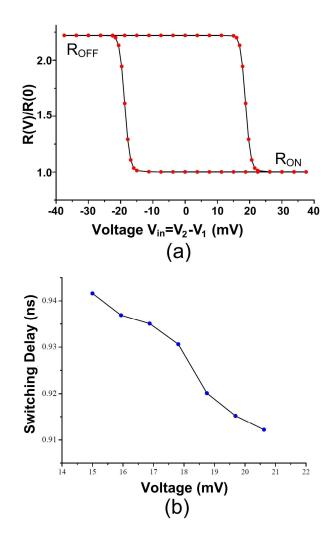

- Figure 5. (a) Volatile S-MTJ circuit schematic; (b) Simulated DC transfer characteristics for volatile S-MTJ showing resistance ratio r(v), as function of input voltage  $V_{in}$ ; (c) Simulated switching delay characteristics for volatile S-MTJ; (d) Nonvolatile S-MTJ circuit schematic; (e) Simulated DC transfer characteristics for non-volatile S-MTJ showing resistance ratio r(v), as function of input voltage  $V_{in}$ . Hysteresis indicates persistence in resistance state; and (c) Simulated switching delay characteristics for non-volatile S-MTJ......21

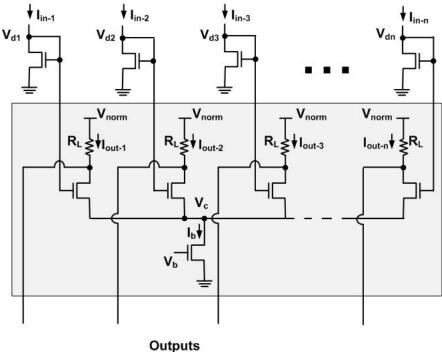

- Figure 19. Normalization circuit for *n* inputs using MOSFETs......41

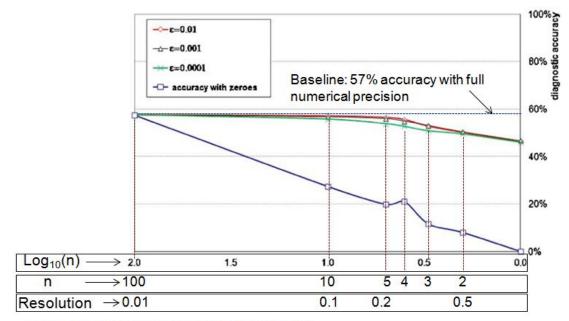

- Figure 35. Diagnostic Accuracy vs. Numerical Precision in HEPAR II Bayesian Network for diagnosis of liver diseases. Here, ε represents an error factor added to prevent rounding to zeroes. This figure is adapted from ref. [31]......76

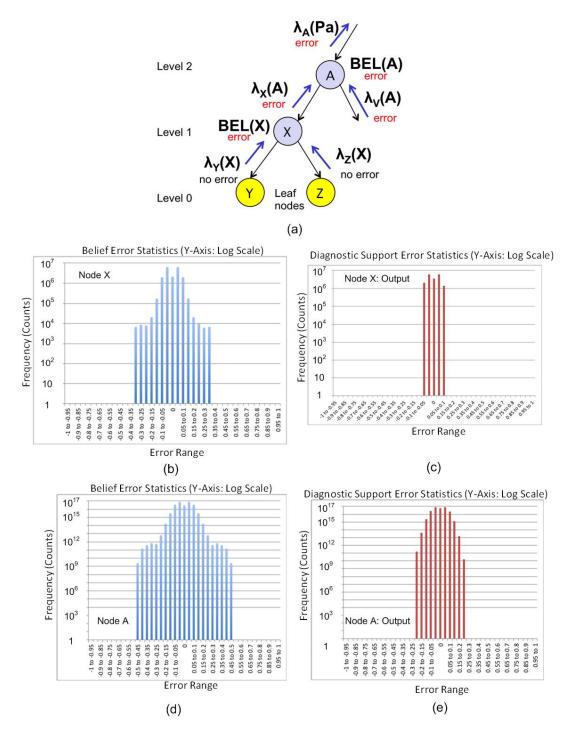

- Figure 37. Methodology for study of propagation of errors due to rounding: (a) Figure showing a part of the binary tree BN. Leaf nodes are evidence variables and are assumed to have no errors in observations. Rounding errors start occurring from level 1 in belief calculations for each node and diagnostic support messages at the output of each node. (b) Rounding error statistics for belief at node X in (a). (c) Error statistics for diagnostic support message from node X to node A. (d), (e) Error statistics for belief and diagnostic support respectively at node A......79

#### **CHAPTER 1**

# **INTRODUCTION**

Machines today lack intelligence, i.e. the inherent ability to reason, make decisions, adapt, and in general operate autonomously in the presence of uncertainty. Today, all computation occurs on microprocessors based on a stored-program von Neumann computing architecture with CMOS technology. This conventional computing paradigm necessitates human intervention to "a priori tell the machine what it needs to do in a given scenario", i.e. program its behavior deterministically. We refer to such conventional computing machines as *abstraction-based engineered systems*; capable of carrying out any procedure expressed algorithmically and implemented through layers of abstraction, and engineered to perform each operation in a procedure as fast as possible given current technology. This conventional mindset of abstracted systems, driven by a desire for convenience in mapping a wide variety of algorithmically expressible problems and to have a reliable machine operation under pre-determined circumstances, has resulted in many discoveries and deterministic tasks to be automated by machines. However, while computers have evolved into fast number-crunching machines today, they are inefficient for supporting machine intelligence that requires operating under nondeterministic scenarios. Handling any new scenario requires explicit instruction by humans for the machine.

Unconventional computation models that draw inspiration from observations in nature such as probabilistic graphical models, neuromorphic computation, hierarchical temporal models using sparse data representation, etc. require immense computing resources and have orders of magnitude inefficiencies when implemented with conventional abstraction-based engineered systems. This inefficiency spans all layers from the Boolean data representation, digital CMOS logic to the underlying microarchitecture. This is one key reason why we do not have intelligence in all things surrounding us, and why machines cannot easily handle complex decision-making problems.

## **1.1 Notion of Physical Equivalence**

We believe that in order to kick-start this evolution in machines and harness the full benefits of unconventional computing paradigms for artificial intelligence, a change in implementation mindset is necessary. We propose a new mindset of architecting intelligent systems with *physical equivalence*; defined as a direct mapping from concept to physical layer, where physical implementation operates on principles defined by the conceptual framework without any abstraction.

A given computational framework can be characterized by:

- quantum of information (or data)

- *interaction* that specifies rules to operate on quantum of information (computation and communication), and

- *organization/architecture*, such as DAG in probabilistic graphical models, that governs the temporal/spatial hierarchy of interactions.

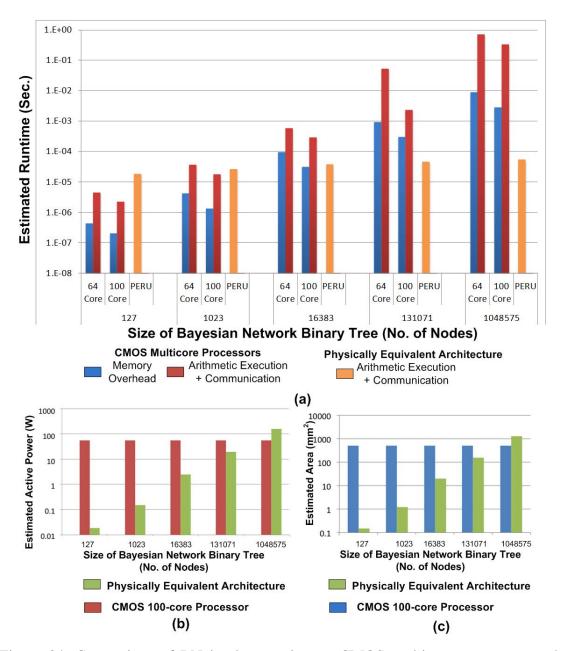

For example, conventional abstraction-based engineered systems operate on symbols represented using binary radix representation (quantum of information), where interactions occur as per rules of binary logic developed through switching theory (interaction), and segregate data storage or memory and computation to enable mapping a wide variety of problems (stored-program von Neumann architecture). In this dissertation, we illustrate our physical equivalence approach through the example of Bayesian Networks, which is a computational framework using probabilistic graphical models for reasoning and decision making under uncertainty. We identify each of the aforementioned characteristics for Bayesian Networks and attempt to find physically equivalent implementation as close as possible to maximize efficiency. We will show that a physically equivalent implementation (with a resolution of 0.1) of Bayesian Networks can yield up to 4 orders of magnitude performance (runtime) benefits compared to conventional software implementations on state-of-the-art CMOS multicore processors, even when considering best-case performance assumptions for conventional approach vs. worst-case evaluation for our proposed approach.

# **1.2 Conceptual Framework Overview**

Bayesian Networks (BNs) [1]-[3] represent a class of widely successful probabilistic formalism capable of modeling causal relationships between random variables in an application domain. A BN can be used for expressing the strength of belief in the state of a system given some observations on its environment. Its structure is a Directed Acyclic Graph (DAG) where every node represents a random variable and every edge is a dependency between nodes. These dependencies are quantified through conditional probabilities (parameters) associated with every node. The belief in the state of a system, specifically the probabilities associated with unobserved variables being in a particular state given the state of observed variables, can be obtained through *inference*. An inference operation is executed following periodic observations on BN variables. Any event (observed variable being assigned a state) triggers the calculation of current belief of a hypothesis, which is an unobservable system variable. Thus Bayesian Networks operate on probabilities (quantum of information), where interactions occur as per rules of probability arithmetic for inference and learning (interaction), and organize knowledge as DAGs (organization/architecture).

Many problems can be mapped into this formalism. For example, gene expression networks are being studied extensively in order to understand the genetic basis of diseases [4][5]. Unfortunately the resulting networks are generally very complex owing to random variables representing gene-gene and gene-environment interactions. Other complex applications [6]-[9] include text classification, situational awareness for cybersecurity, etc.

# **1.3 Limitations of Conventional Implementations**

The high computational complexity in BNs is a result of learning from data; number of candidates is super-exponential in the number of variables. Furthermore, incomplete and limited datasets to learn from mandate a large number of inferences, which further complicates the choice of a candidate network. Additionally, cost and power efficiency aspects make adding BN capabilities impossible in embedded systems. While software implementations representing BNs are highly flexible, several limitations crop up as a consequence of all the layers of abstractions. The underlying conventional von Neumann architectures built with CMOS technology are not well suited to implementing such computational frameworks because:

- (i) their emulation of an inherently non-deterministic, non-logical computing model on a deterministic Boolean logic framework is inefficient,

- (ii) BN's structure and parameter learning is super-exponential in the number of variables,

- (iii) conventional architectures incorporate a limited number of multiplication and division units (due to high complexity of CMOS logic implementation of multipliers and dividers),

- (iv) the use of a rigid separation between logic and memory is undesirable, and

- (v) the use of a radix-based representation of data is inefficient for probabilistic information and incapable of inherently supporting graceful degradation in the presence of errors.

### **1.4 Proposed Approach to Overcome Deficiencies in Conventional Implementation**

Our objective is to architect an efficient machine implementation for causal learning and reasoning framework, given recent developments in nanotechnology. Therefore, our goal is to identify representations across all layers that result in *physical equivalence* with the conceptual probabilistic framework. This mindset, extending from the physical layer to architecture, can potentially address causal inference and learning problems that are computationally infeasible today, and enable such capability at smaller scale in everyday embedded systems. In this dissertation, we design a physically equivalent hardware architecture and nanoscale technology implementation of BNs based on unique magnetoelectric computations that can efficiently address the aforementioned problems, as an illustration of the physical equivalence mindset. It can be extended and applied to other unconventional computation frameworks as well. For physical equivalence at all layers, we explore a technology implementation that operates directly on probabilities (quantum of information) through probability arithmetic without Boolean logic (interactions), and physically realizes a reconfigurable DAG where each node has an equivalent physical entity and communication links representing edges (organization).

At the bottom of the system stack, we use multiferroic straintronic magnetictunneling junctions (S-MTJs) consisting of a single-domain magnetostrictive layer with uniaxial shape anisotropy elastically coupled with a piezoelectric layer. A tiny voltage of 10 - 60 mV applied across the piezoelectric can flip the magnetization in ~1 ns. This is achieved with unprecedented energy-efficiency dissipating only 150 - 200 kT at room temperature [10]-[14] (three to four orders of magnitude reduction in energy dissipated to switch compared to state-of-the-art nanoscale transistors at 1 GHz clock speed). By appropriately "shaping" the voltage pulse, the switching error probability in S-MTJs can be reduced to ~ $10^{-6}$  in the presence of thermal fluctuations at room temperature. In addition, these S-MTJs support non-volatility where the resistance change is persistent, which is unique.

The above-mentioned characteristics of the emerging S-MTJ devices present an opportunity for novel physically equivalent technology frameworks that is not supported by conventional CMOS technology. In this work, we leverage the physical domains that such non-volatile voltage-controlled S-MTJ devices span, for compact and efficient realization of magneto-electric computations with probabilities. They are also capable of sporting multiple magnetization states, which can enable new multi-valued redundant representation of information directly in the physical domain. In this work, we focus on two-state S-MTJs. The synergistic non-Boolean circuit style that we present is non-volatile (enabling no segregation between memory and computation), multi-domain (spanning electrical and magnetic), and mixed-signal (with emphasis on analog for computation without emulation). This leads to circuits that are *self-similar* like fractals when hierarchically composed. Bayesian structure and parameter learning, inference and

adaptation can be supported in a programmable parallel architecture framework that enables for direct mapping and adaptation of BNs.

Key contributions of this dissertation include:

- (i) The idea of physical equivalence for a nanotechnology framework to realize unconventional computing models for causal inference and learning problems, using Bayesian Networks as an example.

- (ii) A data representation for probabilities that has physical equivalence in electrical/magnetic domains and supports graceful degradation in the presence of faults.

- (iii) A new physically equivalent multi-domain mixed-signal Probability Arithmetic Composer circuit framework for computation on probabilities, which supports memory-in-computing through the use of non-volatile devices (S-MTJs).

- (iv) A reconfigurable parallel architecture based on distributed Bayesian Cell framework for implementing any desired Bayesian Network with physical equivalence.

- (v) Methodology to estimate runtime performance of Bayesian inference when implemented on multi-core processors (up to 100 cores) and comparison with the proposed physically equivalent system.

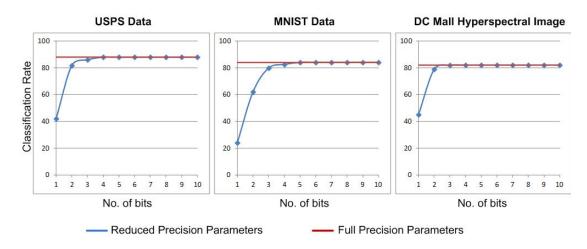

- (vi) A study on the propagation of errors in an example binary tree Bayesian Network due to limited numerical precision (rounding) and impact of probabilistic switching of S-MTJs on BN accuracy.

(vii) Initial projections on impact of improving computational resolution for the proposed framework.

The rest of this dissertation is organized as follows: Chapter 2 presents a brief background on Bayesian Networks. Chapter 3 discusses the S-MTJ device, the proposed data representation and Probability Composer framework for implementing Bayesian Network operations. Chapter 4 presents a reconfigurable architecture that allows implementing any Bayesian Network with the proposed hardware implementation. Chapter 5 presents the evaluation methodologies, benchmarking results against a 100core processor implementation, and studies on error propagation in example BN. Chapter 6 concludes this dissertation.

#### **CHAPTER 2**

### **BAYESIAN NETWORKS**

Bayesian Networks (BN) are probabilistic graphical models [1][2] representing uncertain domains. A BN's *structure* (e.g., a tree) captures qualitative relationships between variables. This is attractive because it is a consistent and complete representation, in addition to being modular and compact. A typical BN is a directed acyclic graph, with individual nodes representing knowledge about variables in a system. Dependencies between the variables are represented as directed links between the nodes. A node is a parent of a child if there exists a directed link from former to the latter. A

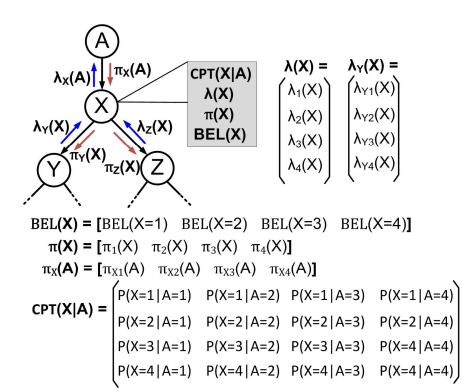

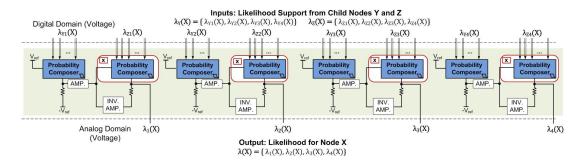

Figure 1. Part of a BN with showing node x whose child nodes are y, z and parent node is A. Outcomes of states of child nodes determine likelihood of parent. All nodes have four states in this example. Each node maintains likelihood vector ( $\lambda$ ), prior vector ( $\pi$ ), belief vector (BEL), and conditional probability table (CPT). The CPT information and messages from child/parent nodes are used to calculate  $\lambda$ ,  $\pi$ , and BEL vectors during Bayesian inference.

node without parents is called a root node, while a node without children is called a leaf node. Each node can have several states for its corresponding variable, and a conditional probability table (CPT) stores conditional probabilities that quantify the relationship with its parents. These CPTs are the *parameters* of a Bayesian Network. The structure and parameters associated with a BN encode a joint probability distribution for all the domain variables in an efficient manner. A part of a typical BN is shown in Figure 1 with one parent node x and two child nodes y, z.

Absence of a link between a pair of variables implies conditional independency between the variables, given other intermediate variables. Due to this independence property, the joint probability distribution can be factorized into local conditional probability distributions of variables given their parent variables, using the chain rule as follows:

$$p(\boldsymbol{x}|\boldsymbol{\theta}) = \prod_{i=1}^{n} p(x_i|pa(x_i), \theta_i), \qquad (1)$$

where  $\mathbf{x} = \{x_1, x_2, ..., x_n\}$  are the variables or nodes in the BN and  $\boldsymbol{\theta} = \{\theta_1, \theta_2, ..., \theta_n\}$  are the associated parameters. These parameters are CPTs, where each element in a CPT for a given node  $x_i$  holds the following data:

$$CPT_{jk}(x_i) = \theta_{ijk} = p(x_i = j | pa(x_i) = k).$$

(2)

The factorization shown in eq. (1) reduces the number of parameters required to specify a full joint probability distribution dramatically.

When constructing a BN for a specific application, hypotheses can be expressed as BN variables and a unique probability is assigned to each hypothesis initially (e.g., based on prior knowledge of the domain from an expert). Alternatively, the BN structure and parameters can be learned from available data on the domain, without explicit elicitation from a domain expert. Given a parameterized BN structure, an inference process requires computation of probability of a hypothesis based on current events observed (state of observed variables) and corresponding conditional probability distributions. Several algorithms exist to perform inference (both exact and approximate) and each algorithm has certain restrictions or trade-offs. We look at one algorithm to illustrate our mindset, which was proposed by Judea Pearl who invented the BN framework. This algorithm, called Belief Propagation [1], is applicable to trees and poly trees, which do not include any loops.

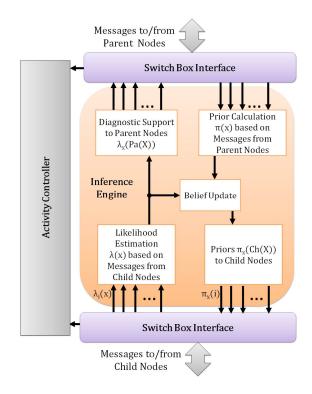

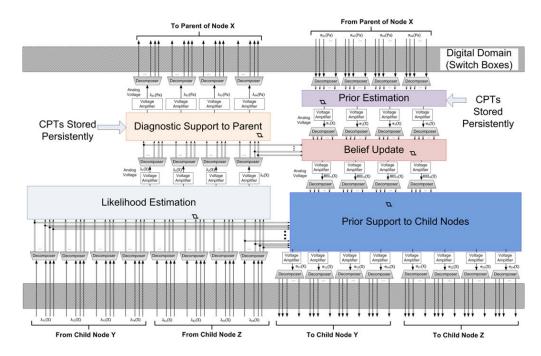

A belief is the probability of an unobserved variable given other observed variables and the BN. Inference is performed via belief update and message propagation through the network. The key operations in this algorithm are likelihood/prior estimation to generate these messages, belief update and diagnostic/prior support message generation. Each of these operations involves arithmetic on probabilities.

### 2.1 BN Inference using Pearl's Belief Propagation

Inference in a BN requires belief updates at all unobserved nodes based on current events observed (evidence), and is performed via message propagation (likelihoods  $\lambda$  and priors  $\pi$  [1] which are essentially probabilities) in the network. Belief update refers to estimating the probability that a node is in a particular state based on the states of its children/parents and current observations. The key operations at each node during inference are likelihood/prior estimation to generate messages and belief update. For

example assuming every node has four states in Figure 1, likelihood messages  $(\lambda_Y(X), \lambda_Z(X))$  from the child nodes are composed at node X to calculate the likelihood vector  $\lambda(X)$  as shown in eq. (3). Here symbols in bold type indicate vectors/matrices, asterisk symbol (\*) represents element-wise multiplication between vectors, and  $\otimes$  operator indicates vector/matrix multiplication.

$$\lambda(\mathbf{X}) = (\lambda_1(X), \lambda_2(X), \lambda_3(X), \lambda_4(X)) = \lambda_{\mathbf{Y}}(\mathbf{X}) * \lambda_{\mathbf{Z}}(\mathbf{X})$$

(3)

where  $\lambda_i(X) = \lambda_{\mathbf{Y}i}(X) \cdot \lambda_{\mathbf{Z}i}(X); i = \{1, 2, 3, 4\}.$

With the likelihood vector being computed, the node then generates messages to send to its parent node as follows:

$$\lambda_{X}(Pa(X)) = (\lambda_{X1}(Pa(X)), \lambda_{X2}(Pa(X)), \lambda_{X3}(Pa(X)), \lambda_{X4}(Pa(X))) \qquad (4)$$

=  $CPT(X|Pa(X)) \otimes \lambda(X).$

Priors computation  $\pi(X)$  is performed at the node X based on prior support messages  $\pi_X(Pa(X))$  received from its parent as follows:

$$\boldsymbol{\pi}(\boldsymbol{X}) = \left(\pi_1(\boldsymbol{X}), \pi_2(\boldsymbol{X}), \pi_3(\boldsymbol{X}), \pi_4(\boldsymbol{X})\right) = \boldsymbol{\pi}_{\boldsymbol{X}}(\boldsymbol{P}\boldsymbol{a}(\boldsymbol{X})) \otimes \boldsymbol{CPT}(\boldsymbol{X} | \boldsymbol{P}\boldsymbol{a}(\boldsymbol{X})).$$

(5)

The current belief at node X **BEL**(X) is updated as follows using computed likelihood  $\lambda(X)$  and prior  $\pi(X)$  vectors:

$$BEL(X) = \alpha \pi(X) * \lambda(X)$$

(6)

where  $BEL_i(X) = \alpha \pi_i(X) \lambda_i(X)$ , ;  $i = \{1, 2, 3, 4\}$ .

Finally, the prior support messages to be sent to its child nodes is computed as follows:

$$\pi_{Y}(X) = \left(\pi_{Y1}(X), \pi_{Y2}(X), \pi_{Y3}(X), \pi_{Y4}(X)\right) = \frac{BEL(X)}{\lambda_{Y}(X)}, and$$

(7)

$$\pi_{Z}(X) = (\pi_{Z1}(X), \pi_{Z2}(X), \pi_{Z3}(X), \pi_{Z4}(X)) = \frac{BEL(X)}{\lambda_{Z}(X)}.$$

#### 2.2 BN Learning

Search-and-score technique [3] is one of the methods used for learning a BN structure and parameters (CPTs) from observed data, even if the dataset is incomplete or has missing values. Since the search space for all possible graphs is super-exponential in the number of variables it is typically narrowed down by using heuristic techniques. Hill-Climbing (HC) algorithm is a typical heuristic approach used where a given structure is perturbed (by adding, removing or reversing edges) and a score is assigned to

#### **Hill-Climbing Algorithm:**

$E \leftarrow \phi$ ; Start with either null set or random network  $T \leftarrow EM_Probability Tables(E,D)$  $B \leftarrow \langle U, E, T \rangle$ *Score*  $\leftarrow -\infty$ **Do:** *Maxscore* ← *Score* For each node pair (X,Y) do For each E'={E  $(X \rightarrow Y), E (X \rightarrow Y), E - (X \rightarrow Y) (Y \rightarrow X)$ T' ← EM\_Probability\_Tables(E',D)  $B' \leftarrow \langle U, E', T' \rangle$ Newscore  $\leftarrow$  AIC(B',D) If *Newscore*> Score then  $B \leftarrow B'$ Score  $\leftarrow$  Newscore WhileScore>Maxscore **Return** B

Figure 2. Pseudo-code for BN Structure Search with Hill-Climbing Algorithm.

#### **Expectation-Maximization Algorithm:**

# **Initialize** T<sup>0</sup>

For t=0 until termination <u>E-step:</u> Compute  $P(X_i, pa(X_i)|D_l, T^t)$  for all  $X_i$  and  $D_l$ Compute the sufficient statistics, for all i, j, k

$$m_{ijk}^{t} = \sum_{l} P(X_{i} = j, pa(X_{i}) = k | D_{l}, T^{t})$$

M-step:

Compute

$$T^{t+1} = \frac{m_{ijk}^t}{\sum_j m_{ijk}^t}$$

for all i, j, k

**Return** $T^{t+1}$

Figure 3. Pseudo-code for BN CPT Estimation with Expectation-Maximization Algorithm.

the new structure (Figure 2). Different scoring metrics (e.g. AIC scoring) are available to determine the quality of the current BN with respect to observed data. At the end of the process, the graph with maximum score is selected.

As a part of the learning algorithm, the conditional probability tables (CPTs) also need to be estimated from data. For the general case of incomplete data, Estimation-Maximization (EM) algorithm is used to learn the CPTs [3] (Figure 3). EM involves performing iterative inference operations, and computation on conditional probabilities to estimate CPTs until convergence.

# 2.3 BN Adaptation

A BN will need to be able to adapt by reinforcing its parameters (CPTs) based on winning hypothesis at the root node. Reinforcement of a single hypothesis (that wins) can be performed by adjusting the corresponding row of the CPT at each child node slightly in the direction of the likelihood ( $\lambda$ ) at that node for current observation. One possible scheme to compute new CPT values (for a child node *j*) is to use the count of number of times a hypothesis (node *i*) was observed as a past weight for the adjustment [7], using eq. (8). This update is performed for every element *j* in the row *i* of the CPT.

$$CPT_{ij}^{new} = \frac{count_i. CPT_{ij} + \lambda_j}{\sum_i (count_i. CPT_{ij} + \lambda_j)}$$

(8)

## 2.4 Summary

In this chapter, we presented a brief overview of the Bayesian Network formalism for representing knowledge, and the operations involved in inference and learning. The next chapter presents our approach towards a physically equivalent implementation of Bayesian Networks using emerging nanotechnology.

#### **CHAPTER 3**

# PHYSICALLY EQUIVALENT DATA REPRESENTATION AND PROBABILITY COMPOSER CIRCUIT FRAMEWORK

Our objective is to architect an efficient machine for the Bayesian Network framework. Therefore, our goal is to identify representations resulting in physical equivalency with the conceptual probabilistic framework, across all layers.

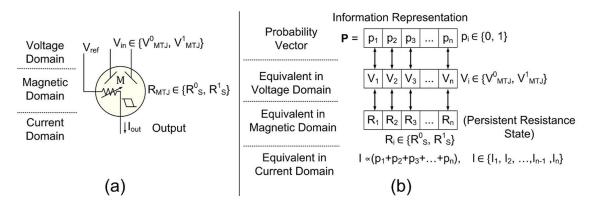

### **3.1 Data Representation**

The first critical element in our approach is the underlying data representation. Since Bayesian Networks (BNs) operate on probabilities, we represent probability as a non-Boolean multi-valued flat probabilistic vector tightly tied to the physical layer. We define n spatially distributed digits  $(p_1, p_2, ..., p_n)$  such that each digit  $p_i$  can take any one of kvalues, where k is the number states supported by the underlying physical device (e.g., for devices with 4-states, k = 4 and a given digit  $p_i \in \{0,1,2,3\}$ ). As opposed to conventional number systems (e.g. binary, HEX etc.), in this representation *all digits carry equal weight irrespective of position*, which implies inherent redundancy and better error resilience through graceful degradation. The probability value P, the basis for our architecture and the inspiration for the physical implementation, represented by an n-digit probability vector is given by:

$$\boldsymbol{P} = \frac{\sum_{i=1}^{n} p_i}{n(k-1)}.$$

(9)

In this representation, the *resolution* is defined as the unit probability at output that can be represented in this format. It is determined by number of digits n and the number

of states of each digit k, and is given by 1/[n(k-1)]. A higher resolution can be achieved either by having more states per device (k) or by increasing the number of digits (n). Here it is to be noted that precision in BNs has a different interpretation: it is the precision of learning and expressing the problem through supporting a large number of variables and relationships, rather than numerical precision alone. This representation also yields fault resilience supporting graceful degradation in case of faults.

# 3.2 Technology Overview: Straintronic MTJs

In this work, we use straintronic MTJs (S-MTJs) as the underlying physical technology for hardware implementation. But the proposed scheme may be implemented with any emerging non-volatile device for physical equivalence.

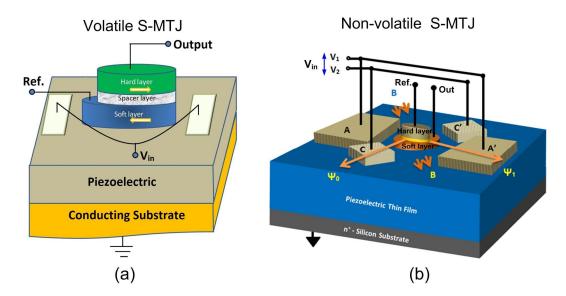

Figure 4. (a) Volatile S-MTJ device configuration: Voltage input induces strain in soft-layer layer adjusting magnetization orientation; a reference terminal (Ref.) is used for resistance readout; and (b) Non-volatile S-MTJ device: The MTJ stack is placed in between two pairs of electrode pads such that the line joining each electrodes subtends an angle of  $15^{0}$  and  $165^{0}$  respectively with the major axis of soft magnetic layer. A magnetic field **B** is applied along the minor axis of the soft magnetic layer. Voltage input persistently changes magnetization.

The concept of straintronics, where the bistable magnetization of a shape anisotropic multiferroic nanomagnet is switched with electrically generated mechanical strain, is attractive due to its extreme low energy of switching. A straintronic MTJ (S-MTJ) device is shown in Figure 4a. It consists of three layers - a "hard" ferromagnetic layer with a fixed magnetization orientation, an ultrathin spacer layer, and a "soft" ferromagnetic layer with variable magnetization orientation. The three-layered stack is fabricated on a thin piezoelectric film grown on an  $n^+$ -Si substrate.

Because of dipole coupling between the hard and soft layers, they tend to have mutually anti-parallel magnetizations (see Figure 4a) and in that configuration, the resistance of the S-MTJ measured between the two ferromagnetic layers is high. Application of an input voltage ( $V_{in}$ ) at the two (shorted) contact pads generates a biaxial strain in the piezoelectric layer underneath the soft magnet (compression along the major axis of the elliptical soft magnet and tension along the minor axis) [22][23], which rotates the magnetization of the soft magnet by an angle  $\Theta$  via the Villari effect, if the soft layer is magnetostrictive and has positive magnetostriction. This reduces the angular separation between the magnetization orientations of the hard and soft layers, which in turn reduces the resistance of the S-MTJ. If the input voltage is withdrawn, the stress in the soft magnetic layer relaxes and hence its magnetization will tend to return to its original orientation because of dipole coupling with the hard magnetic layer. In this case, the operation is volatile. The resistance ratio between the high- and low-resistance states as a function of applied voltage v is roughly given by [24],

$$r(v) = \frac{R_{ON}}{R_{OFF}} = \frac{R(v = V_{ON})}{R(v = 0)} = \frac{1 - \eta_1 \eta_2}{1 - \eta_1 \eta_2 . \cos\left[\Theta(V_{ON})\right]},$$

(10)

where  $\Theta(V_{ON})$  is the angle by which the magnetization of the soft layer rotates under stress generated by input voltage  $V_{ON}$ , assuming it starts from being exactly anti-parallel to the hard layer initially, and  $\eta_1$ ,  $\eta_2$  are the spin-injection/filtering efficiencies at the interfaces between the two ferromagnets and the spacer layer. At room temperature, these quantities are roughly 70% [25]. The maximum value of  $\Theta$  is 90<sup>0</sup> unless the input voltage pulse is timed in a certain way to allow reorientation by 180<sup>0</sup> [26].

The magnetization rotation can be made persistent through a scheme shown in Figure 4b, resulting in non-volatile operation. The electrodes A - A' are shorted to form one input terminal, and C - C' are shorted to form the second terminal. When a voltage is applied between these terminals and the n+-substrate, electric fields are generated underneath the pads, producing a highly localized strain field in the piezoelectric film [22][23]. This results in biaxial strain (compression/tension along the line joining the electrodes and tension/compression along the perpendicular direction) since the distance between the electrode pairs is approximately equal to the PZT film thickness. This strain will then be elastically transferred to the soft layer of the S-MTJ stack despite any substrate clamping. The scheme requires a small in-plane external magnetic field (B) along the minor axis of the soft magnet which brings the two stable magnetization states out of the soft magnet's major axis (easy axis) and aligns them along two in-plane directions that lie between the major and minor axes with an angular separation of  $\sim 132^{\circ}$ . These two stable orientations ( $\Psi_1$  and  $\Psi_0$ ) of magnetization represent the low and high resistance states, respectively. The magnetization of the hard magnetic layer is parallel to  $\Psi_1$ , which is why the low resistance state is visited when the magnetization of the soft magnetic layer is along  $\Psi_1$ . Since Terfenol-D has a positive magnetostriction coefficient, compressive stress along the line joining the electrodes A–A' will stabilize the magnetization at  $\Psi_0$ , while a compressive stress along C–C' electrodes will switch the magnetization back to  $\Psi_1$  [30]. These magnetization orientations are stable, i.e. if the magnetization is left in either state it remains there in perpetuity even after power is switched off, which makes the device non-volatile. The change in resistance of the S-MTJ is read by using a reference voltage, which generates an output current. Thus, conversion between voltage, magnetic and current domains is achieved.

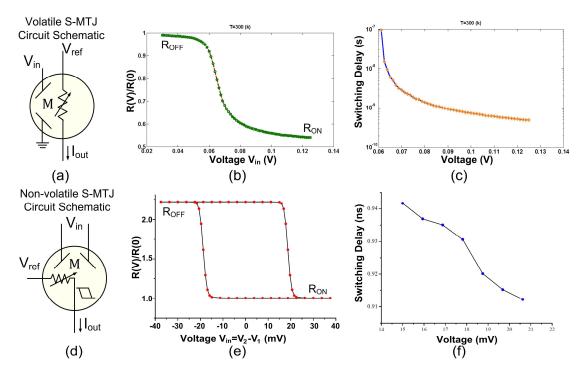

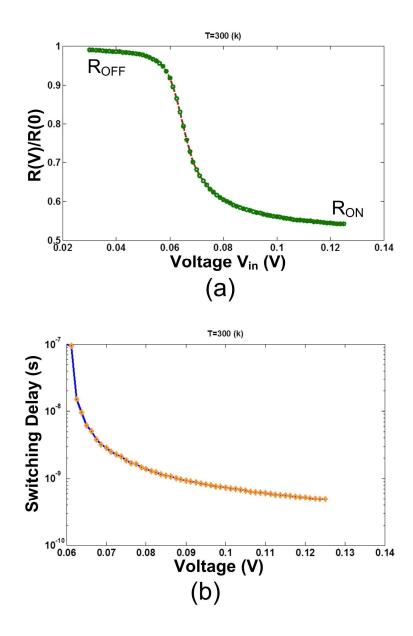

The transfer characteristics of the S-MTJ devices (Figure 5b-c and Figure 5e-f) were extracted from stochastic Landau-Lifshitz-Gilbert (LLG) simulations performed at Virginia Commonwealth University by the research group headed by Prof. Supriyo Bandyopadhyay and Prof. Jayasimha Atulasimha, and are described in refs. [14] [27]-[30]. For the volatile S-MTJ transfer characteristics, a soft layer made of Terfenol-D with dimensions 120nm x 105nm x 6.5nm was used, and 110nm x 90nm x 9 nm for nonvolatile S-MTJ. The piezoelectric layer was assumed to be lead-zirconate-titanate (PZT) of thickness 100nm. The effect of room-temperature thermal noise was taken into account [14] [27]-[30] and the characteristics presented were thermally averaged characteristics. Furthermore, although the strain generated in the magnet was biaxial, it was approximated with uniaxial strain (which overestimated the voltage needed to generate a given strain). This was somewhat compensated by the fact that 100% strain transfer from the piezoelectric film to the magnetostrictive layer was assumed, leading to an underestimation of the voltage needed to generate a given strain. Every data-point in Figure 5b,e was generated by averaging 10,000 simulations. The LLG simulations also

Figure 5. (a) Volatile S-MTJ circuit schematic; (b) Simulated DC transfer characteristics for volatile S-MTJ showing resistance ratio r(v), as function of input voltage  $V_{in}$ ; (c) Simulated switching delay characteristics for volatile S-MTJ; (d) Non-volatile S-MTJ circuit schematic; (e) Simulated DC transfer characteristics for non-volatile S-MTJ showing resistance ratio r(v), as function of input voltage  $V_{in}$ . Hysteresis indicates persistence in resistance state; and (c) Simulated switching delay characteristics for non-volatile S-MTJ.

yielded the switching time needed for  $\Theta(v)$  to stabilize to its final value after input voltage is abruptly switched on, shown in Figure 5c,f.

The S-MTJ device can have a number of stable states depending on the crosssectional shape of the magnet. For example, if the cross-section is an ellipse the magnetization has two stable states. If left in one of those states, the magnetization will remain there indefinitely, making the switch non-volatile. If the cross-section is a different shape, the number of states can be increased. By orienting the hard magnet in a suitable direction, the resistance of the S-MTJ can be made to have as many states as the magnet's orientation. The number of states can be increased further by employing other polygonal cross-sections, but not indefinitely since increasing them reduces the energy barrier between neighboring states, resulting in spontaneous switching and error.

### 3.3 Probability Representation using Straintronic MTJs

Each of the digits in a probability vector is encoded in the resistance state of a nonvolatile S-MTJ (see Figure 6). For example, in the case where S-MTJs are binary with two stable magnetic orientations, the state that leads to a high resistance ( $R_{OFF}$ ) is used to encode probability digit 0, and low resistance ( $R_{ON}$ ) encodes probability digit 1. The probabilistic information from magnetization (and thus resistance) domain is converted to a condensed equivalent representation in the current/voltage domain (Figure 6b) through the S-MTJs for computation. We use an inverse-linear relationship between resistance ( $r_i$ ) and the probability digit ( $p_i$ ) being represented as shown in eq. (11).

$$r_i = \frac{\beta}{(p_i + \varepsilon)}.$$

(11)

Here,  $\beta$  and  $\varepsilon$  are constants chosen such that the above relationship holds. For binary

Figure 6. (a) Non-volatile S-MTJ circuit schematic with 2 states showing multi-domain representation.  $V_{in}$  switches S-MTJ resistance through change in magnetization and  $V_{ref}$  is used during readout; and (b) Spatial probabilistic information representation with S-MTJ with 2 states, and its physical equivalent in resistance, voltage and current domains.

devices with two resistance states ( $r_i = R_{OFF}$  corresponding to  $p_i = 0$  and  $r_i = R_{ON}$  corresponding to  $p_i = 1$ ), by substituting the corresponding  $r_i$  and  $p_i$  values we get

$$\varepsilon = \frac{1}{\left(\frac{R_{OFF}}{R_{ON}} - 1\right)}; \text{ and}$$

$$\beta = \varepsilon. R_{OFF} = \frac{R_{OFF}}{\left(\frac{R_{OFF}}{R_{ON}} - 1\right)}.$$

(12)

Alternative representations may also be used where the resistance is linear with respect to the probability digit. Such alternatives will require changes to the circuit implementations accordingly.

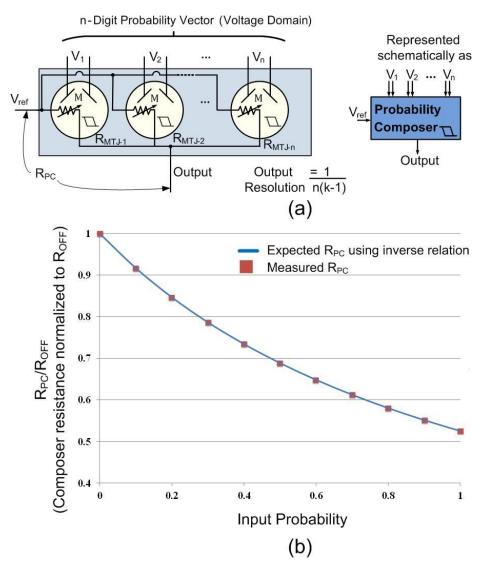

### 3.4 Resolution Scaling with Probability Composer

A single S-MTJ with 2 states is very limited since it can only express probability 0 or 1. In order to increase the resolution, we use a parallel configuration of several S-MTJs to be able to express other probability values between 0 and 1 (see Figure 7a). We call this topology as Probability Composer (for scaling resolution), which accepts inputs represented in probability vector format of *n*-digits. The effective resistance ( $R_{PC}$ ) has *n*+1 discrete states, given by the following expression (see Figure 7b):

$$\frac{1}{R_{PC}} = \sum_{i=1}^{n} \frac{1}{r_i} = \sum_{i=1}^{n} \frac{(p_i + \varepsilon)}{\beta} = \frac{1}{\beta} \left[ \sum_{i=1}^{n} p_i \right] + \left\{ \frac{n\varepsilon}{\beta} \right\}.$$

(13)

In general, if each device in this Probability Composer topology has k states, then the effective resistance of the circuit has n(k-1)+1 distinct states with a resolution of 1/[n(k-1)]. By using a common reference voltage, the probability digits represented by S-MTJ resistance are added up in the Probability Composer via the electrical current flowing

Figure 7. (a) Circuit and schematic representation of Probability Composer element using S-MTJs to increase output resolution; and (b) The effective resistance vs. input probability value (represented using probability digits and stored in each S-MTJ resistance state) of the Probability Composer normalized to its OFF state resistance.

through each device. Thus, the Probability Composer essentially converts the discrete

probability vector to a compressed form in analog electric domain.

When using a load resistance  $R_L$  much smaller than the S-MTJ resistance connected between the output terminal of Probability Composer and ground, the output current flowing through this load resistor is given by:

Figure 8. Read-out schemes for Probability Composer Element. (a) Current read-out with corresponding output values shown in (b); and (c) Voltage read-out with corresponding values shown in (d).

$$I_{out} = \frac{V_{REF}}{(R_{PC} + R_L)} \approx \frac{V_{REF}}{R_{PC}} = \frac{V_{REF}}{\beta} \left[ \sum_{i=1}^n p_i \right] + \left\{ \frac{n \varepsilon V_{REF}}{\beta} \right\}.$$

(14)

The term in {.} represents the additional current that needs to be corrected for output linearity. This can be done with a Compensation Circuit (see Figure 8a), such that the output current is given by:

$$I_{out} \approx \frac{V_{REF}}{\beta} \left[ \sum_{i=1}^{n} p_i \right] + \left\{ \frac{n \varepsilon V_{REF}}{\beta} \right\} + \frac{V_{ADJ}}{R_{ADJ}} = \frac{V_{REF}}{\beta} \left[ \sum_{i=1}^{n} p_i \right] = \frac{n V_{REF} \mathbf{P}}{\beta}.$$

(15)

Here,  $V_{ADJ} = -V_{REF}$ ,  $R_{ADJ} = \beta/(n\epsilon)$  and **P** is the probability value represented by the digital probability vector as defined in eq. (1). Thus for every probability value there is a corresponding current domain output.

However, we are interested in a voltage output since S-MTJs are voltage-controlled. The current signal can be converted to analog voltage domain by using the resultant voltage across the load resistance, given by  $V_{out} = I_{out}.R_L = \frac{V_{REF}.R_L.P}{\beta}$ . However, since the value of  $R_L$  has to be necessarily low relative to S-MTJ resistance for the approximation in eq. (13), the range of output voltages using this scheme needs amplification. But, if the output voltage non-linearity can be tolerated while read-out, then the analog voltage output with a larger range can be obtained by simply eliminating the load resistance  $R_L$  (see Figure 8c). The output voltage is given by the following expression:

$$V_{out} = V_{REF} \cdot \left[ \frac{\frac{1}{R_{PC}} - \frac{1}{R_{ADJ}}}{\frac{1}{R_{PC}} + \frac{1}{R_{ADJ}}} \right] = V_{REF} \cdot \left[ \frac{\sum_{i=1}^{n} p_i}{\sum_{i=1}^{n} p_i + 2n\varepsilon} \right] = V_{REF} \cdot \left[ \frac{\boldsymbol{P}}{\boldsymbol{P} + 2\varepsilon} \right].$$

(16)

Here P is the probability value represented by the digital probability vector, defined in eq. (9). This topology results in a non-linearity in the output; for probability close to 0 the output voltage is proportional to sum of individual probability digits, but degrades for probability close to 1. As long as different output levels can be differentiated, the above topology may be used. This represents a trade-off between using sub-threshold CMOS analog support circuits for amplifying the low output voltage range exhibiting linearity as in the first case, vs. tolerating non-linearity in output for wider voltage range with a potentially simpler circuit implementation.

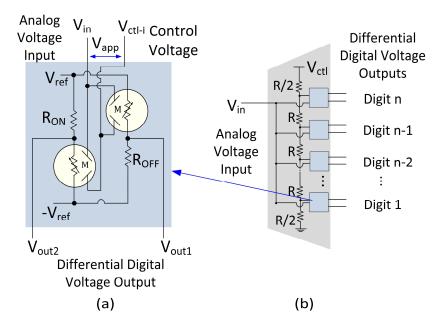

### **3.5 Decomposer Element**

We need a way to convert the analog voltage output back to a digital probability vector representation. To achieve this we design a Decomposer circuit with volatile S-MTJs as follows. The Decomposer has the following requirements:

- i) For converting to an *n*-digit probability vector, it requires *n* decomposer elements;

each decomposer element is designed to trigger at a different input voltage value,

i.e. they have different threshold voltages.

- ii) When triggered, each decomposer element needs to generate a pair of differential output voltage signals, so as to switch a non-volatile S-MTJ in the successive stage.

Drawing inspiration from flash analog-to-digital converters, we use a resistive ladder (tuned for low-power operation since it does not contribute directly to critical path delay after startup) to setup varying threshold voltages for each decomposer element. Alternatively, the S-MTJ device may be designed to have varying thresholds by changing the device parameters (such as PZT thickness, etc.). Here, the volatile S-MTJs in each decomposer element act as a voltage comparator; if the input voltage is below the reference voltage (setup with the resistance ladder) the S-MTJ switches its resistance state, else it remains in its previous state. To generate differential voltage output when triggered, each decomposer element consists of two branches, one with S-MTJ in pull-up

| Operating<br>Condition | S-MTJ<br>Resistance | Voltage<br>Output1 | Voltage<br>Output2  | Probability<br>Digit |

|------------------------|---------------------|--------------------|---------------------|----------------------|

| $V_{app} < V_{th}$     | R <sub>OFF</sub>    | 0                  | V <sub>REF</sub> /3 | 0                    |

| $V_{app} \geq V_{th}$  | R <sub>ON</sub>     | $V_{REF}/3$        | 0                   | 1                    |

Table 1. Decomposer Element Operation

Figure 9. Decomposer Circuit Design: (a) Decomposer Element used to generate differential digital voltages based on analog input voltage for a given threshold voltage; and (b) Full Decomposer circuit consisting of n Decomposer Elements to convert analog voltage signal to n-digit probability vector using discrete voltage representation. Here,  $V_{ctl-i}$  controls the threshold voltage for the *i*-th element and is determined by the resistance ladder network.

and the other with S-MTJ in pull-down (see Figure 9). The possible states of the S-MTJs

and the corresponding output voltages are shown in Table 1 for this configuration.

### **3.6 Fault Resilience (Supporting Graceful Degradation)**

Information representation is inherently fault resilient in both electrical and magnetic domains. Consider two possible single-fault scenarios: (i) an input voltage at any position is shifted by a single level, and (ii) a magnetization vector in an S-MTJ is offset to a neighboring state of the 'intended' value. Given that the representation is redundant with all digits carrying equal weight, either fault would cause the overall value to be erroneous by 1/[n(k-1)], i.e., the resolution of the computation. This is in direct contrast to conventional *m*-digit radix-based representations (e.g., binary, HEX) where a single fault

can cause up to a  $2^{m-1}$  error in the value being stored/computed based on the position. The proposed approach thus supports a graceful degradation, which is linear with increasing number of faults. Furthermore, the number of digits used (*n*) can be adjusted depending on the precision and fault-resilience required by the application.

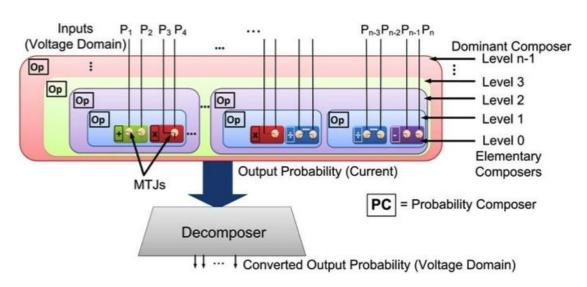

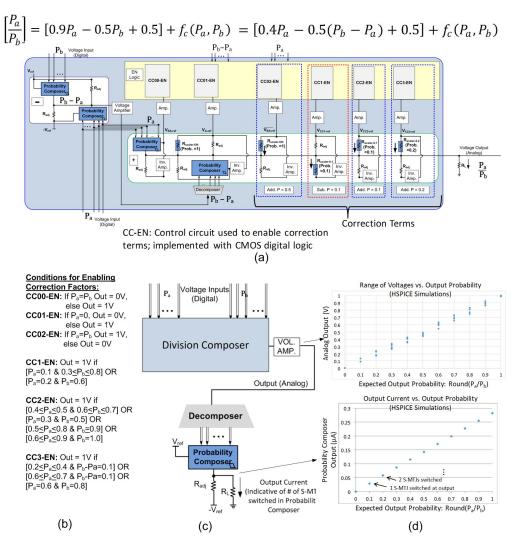

## 3.7 Probability Arithmetic Composer Circuit Framework

The proposed circuit framework achieves physical equivalence by directly implementing arithmetic functions operating on probabilities, rather than emulating with Boolean logic functions. An Arithmetic Composer can be recursively defined as a hierarchical instantiation of other Arithmetic Composer functions until Elementary Arithmetic Composer functions with S-MTJs are reached, as shown in Figure 10. To this end, we defined four Elementary Composers: '+', '-', 'x', '÷'. Details on circuit designs are presented in the subsequent section. Thus, an Arithmetic Composer  $f^n$  consisting of n levels of operations to be performed can be recursively expressed as:

for

$$n > 1$$

,  $f^n = f^{n-1}(f_1^{n-2}, f_2^{n-2}, f_3^{n-2}, \dots, f_j^{n-2})$  (17)

Figure 10. Probability Composer Circuit Framework

for n = 1,  $f^1 = f^0$  (primary inputs); where  $f^0$  is an Elementary Composer.

The top-level operation to be performed ( $f^{n-1}$ ) is called the Dominator Composer since it determines the overall Composer circuit structure, where each node is either another Arithmetic Composer or an Elementary Composer. This approach is easily scalable since any function can be hierarchically built by plugging Arithmetic Composer nodes in a Dominator Composer, without changing the circuit style. For example, a function  $F = (P_a.P_b)+(P_c.P_d)$  can be hierarchically represented as

$$F = f^{2} = f^{1}(f_{1}^{0}, f_{2}^{0}) = SUM[MUL(P_{a}, P_{b}), MUL(P_{c}, P_{d})].$$

(18)

Here n = 2 since there are two levels of operations to be performed,  $f^{1}$ =SUM and  $f^{0}$ =MUL. Thus, at any given level, the Arithmetic Composer is Self-Similar to its corresponding Elementary Composer, exhibiting fractal-like behavior.

### **3.8 Elementary Arithmetic Composers**

The Composers at the lowest level of hierarchy perform fundamental arithmetic operations on probabilities, and are called Elementary Arithmetic Composers. Three of the four fundamental arithmetic operations, viz. multiplication, addition, subtraction, are physically realized based on fundamental laws of circuit physics. While division operation may also be envisioned for physically equivalent implementation, the S-MTJ device limitations (particularly the low  $R_{OFF}/R_{ON}$ ) preclude S-MTJ based direct divider implementation. Hence, we use a physically equivalent circuit based on approximation with addition, subtraction and multiplication with correction techniques to implement a probability divider for our framework. However, a different non-volatile device that does not have S-MTJ limitations may enable a direct physical divider implementation.

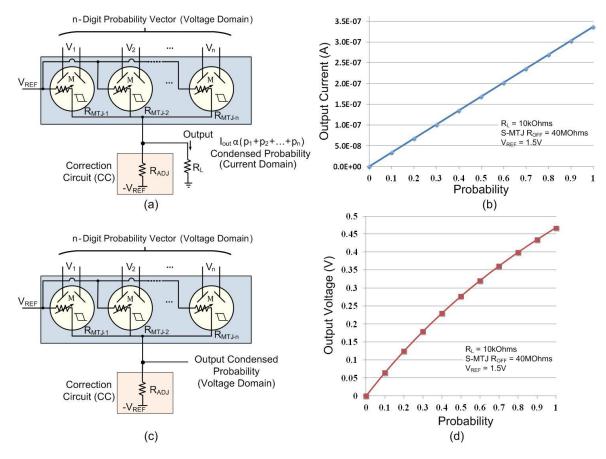

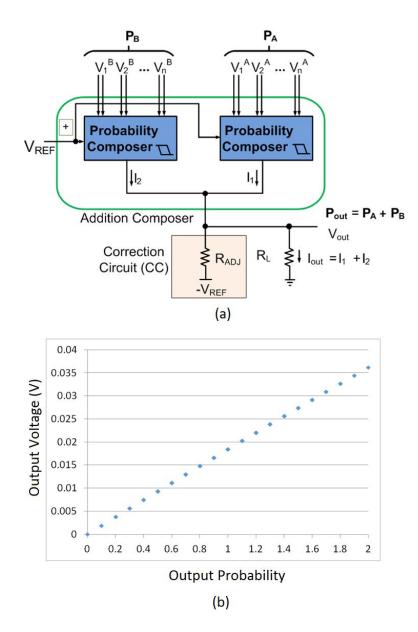

Figure 11. (a) Elementary addition composer using voltage mode read-out; and (b) Corresponding output voltage vs. probability characteristics as calculated by eq. (19) after correction, and validated using HSPICE simulations for all possible input combinations.

Kirchhoff's current law enables elegant physically equivalent implementation for addition and subtraction operations. This is well known in analog CMOS circuits. Here, we illustrate how to implement non-volatile probability adders and subtractors using S-MTJs. Current addition can be implemented by using a parallel configuration of Probability Composer elements, as shown in Figure 11a. This is an extension of the Probability Composer element itself where each S-MTJ was arranged in parallel to be able to sum the probability digits represented using the resistance states. By using a single reference voltage  $V_{REF}$  and load resistor  $R_L$  (of the order of 10-100KOhms) with value much smaller than Probability Composer element resistance (in the order of tens of MOhms), the parallel topology of two *n*-digit Probability Composer elements produces an output current as follows:

$$I_{out} = \frac{V_{REF}}{\left(\frac{R_{PC-A} \cdot R_{PC-B}}{R_{PC-A} + R_{PC-B}} + R_L\right)} \approx V_{REF} \left(\frac{1}{R_{PC-A}} + \frac{1}{R_{PC-B}}\right)$$

$$= \frac{V_{REF}}{\beta} \left[ \left(\sum_{i=1}^n p_i\right)_A + \left(\sum_{i=1}^n p_i\right)_B \right] + \left\{\frac{2n\varepsilon V_{REF}}{\beta}\right\}$$

$$= \frac{nV_{REF}}{\beta} \left[ P_A + P_B \right] + \left\{\frac{2n\varepsilon V_{REF}}{\beta}\right\}.$$

(19)

Correction Circuits (CC) can be used as before in Probability Composer element to extract the current given by the term in  $\{.\}$  in eq. (19). To get a voltage output, we use the voltage across the load resistor (see Figure 11b), which can be amplified using CMOS op-amps. Alternatively, we can simply use the same topology with correction circuits, while removing the resistor  $R_L$  (if the non-linearity in output can be tolerated) for larger voltage range as follows:

$$V_{out} = V_{REF} \cdot \left[ \frac{\frac{1}{R_{PC-A}} + \frac{1}{R_{PC-B}} - \frac{2}{R_{ADJ}}}{\frac{1}{R_{PC-A}} + \frac{1}{R_{PC-B}} + \frac{2}{R_{ADJ}}} \right] = V_{REF} \cdot \left[ \frac{P_A + P_B}{P_A + P_B + 4\varepsilon} \right].$$

(20)

Output Decomposers can be designed to differentiate the voltage levels such that output non-linearity is tolerated.

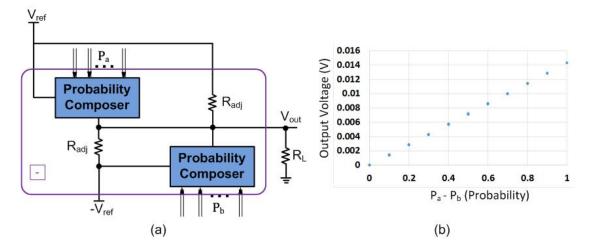

Subtraction is achieved by reversing one of the branches such that it supplies a  $-V_{REF}$  to the Probability Composer Element, as shown in Figure 12. The voltage output is given by:

$$V_{out} = I_{out}R_L = \frac{nV_{REF}}{\beta} [\boldsymbol{P}_a - \boldsymbol{P}_b], \qquad R_L \ll R_{PC}.$$

(21)

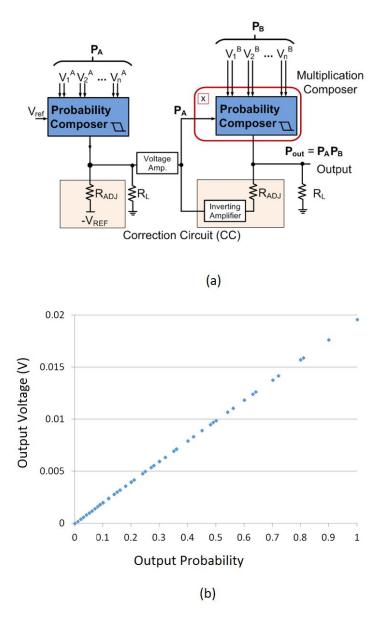

We implement multiplication based on Ohm's law, V = I.R, rewritten as I = V/R. By representing one of the inputs as voltage V, and the other as resistance of Probability Composer Element, we directly implement a multiplication operation. The circuit topology is shown in Figure 13a. The first Probability Composer element converts the digital probability vector from magnetic (resistance) domain to analog voltage domain. This voltage needs to be adjusted so that the loss in the first stage is compensated through

Figure 12. (a) Elementary subtraction composer using voltage mode read-out; and (b) Corresponding output voltage vs. probability characteristics for  $P_a \ge P_b$  as calculated by eq. (21), and validated using HSPICE simulations for all possible input combinations.

Figure 13. (a) Elementary multiplication composer topology; and (b) Output probability vs. voltage characteristics in continuous analog domain validated using HSPICE simulations for all possible input combinations.

amplification using CMOS support circuits (such as op-amps). The amplified voltage is used as an input voltage to the next Probability Composer element, whose resistance is inversely related to the encoded probability value. The current through the second Probability Composer element achieves multiplication of the two probabilities (with Correction Circuits), given by:

$$I_{out} \approx \frac{n}{\beta} [V_A, \boldsymbol{P}_B] = \frac{n^2}{\beta^2} g R_L V_{REF} (\boldsymbol{P}_A \boldsymbol{P}_B), \qquad R_L \ll R_{PC}.$$

(22)

The current output can be converted to voltage mode by simply using the voltage across the load resistance  $R_L$  (see Figure 13a). Alternatively, voltage domain output with larger range can also be obtained by simply removing the load resistance  $R_L$ , given by:

$$V_{out} = g. V_{REF} \left[ \frac{\boldsymbol{P}_{A} \cdot \boldsymbol{P}_{B}}{(\boldsymbol{P}_{A} + 2\varepsilon)(\boldsymbol{P}_{B} + 2\varepsilon)} \right].$$

(23)

Similar to previous case, the denominator causes non-linearity in the output, and is affected when  $P_A$  or  $P_B$  takes a value close to 1. As long as a Decomposer can be designed to tolerate this non-linearity, this topology may be used.

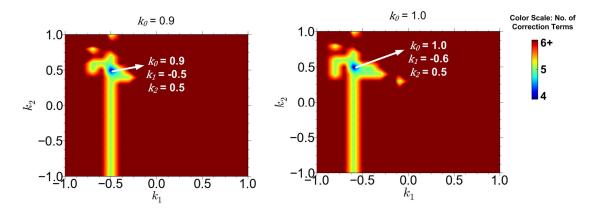

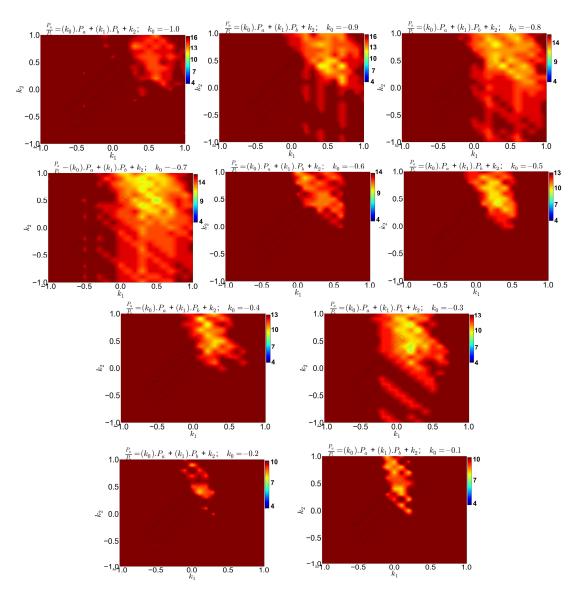

A direct division may be implemented based on the above mindset, through Ohm's law. However, the limited  $R_{OFF}/R_{ON}$  for the S-MTJ devices means that such topologies will have error factors which are difficult to eliminate. A different non-volatile device with a higher  $R_{OFF}/R_{ON}$  may enable such circuit implementations. Hence, in this work we attempt to implement a physically equivalent division through approximation using multiplication, addition and subtraction. We use the following expression using addition, subtraction and multiplication based on assumptions to be stated in the following:

$$\boldsymbol{P_{out}} = \begin{bmatrix} \underline{P_a} \\ \overline{P_b} \end{bmatrix} \approx [k_0 \cdot \boldsymbol{P_a} + k_1 \cdot \boldsymbol{P_b} + k_2] + f_c(\boldsymbol{P_a}, \boldsymbol{P_b}), \quad (24)$$

where  $k_0$ ,  $k_1$ , and  $k_2$  are constants between -1 and 1 with a resolution of 0.1, and  $f_c$  is a correction factor as a function of the two input arguments. The square brackets [.] in eq. (24) indicate rounding function. The assumptions here are:

- i) The output of a division will always result in a valid probability as per the algorithm being used. This implies  $P_a \leq P_b$ .

- ii) The probability  $P_b$  will never take a value 0. Control circuits may be designed to detect a violation of this condition.

- iii) Computational resolution is 0.1.

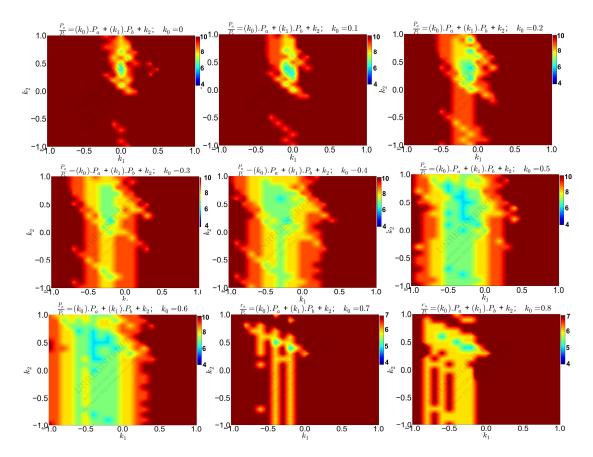

Based on the conditions above, we evaluated all possible combinations of constants  $k_0$ ,  $k_1$  and  $k_2$  that result in the best fit for equation (24) (see Figure 14, Figure 15, Figure 16). Expressions resulting in least number of unique error cases were selected as candidate solutions. We found two expressions that resulted in a minimum of 4 unique error cases to be corrected (see Figure 14). Ideally, the final expression would be chosen based on ease of implementation. In our case, we found that both expressions had similar complexity of implementation and any one of the two expressions could be used. The

Figure 14. Contour plots showing the count of unique error cases, which is equal to the number of correction circuits required, for division implementation through approximation using eq. (24). All possible combinations with resolution of 0.1 for coefficients  $k_0$ ,  $k_1$ , and  $k_2$  were tested and the best results are shown here. The minimum number of correction circuits (indicated by blue color) required were found to be 4, for two expressions with coefficients (a)  $k_0 = 0.9$ ,  $k_1 = -0.5$ ,  $k_2 = 0.5$ ; and (b)  $k_0 = 1.0$ ,  $k_1 = -0.6$ ,  $k_2 = 0.5$ . Here, negative coefficients indicate the use of subtraction.

Figure 15. Contour plots showing the count of unique error cases, which is equal to the number of correction circuits required, for division implementation through approximation using eq. (24). Coefficient  $k_0$  ranges from 0 to 0.8.

values used were  $k_0 = 0.9$ ,  $k_1 = -0.5$  and  $k_2 = 0.5$ .

The correction factor was determined by taking every possible input combination, and hard-wiring the required corrections for cases where the relationship in eq. (24) causes error. For each correction case, we used an enable logic circuit that switched the correction term ON based on the input values. This was a logic-based implementation and used S-MTJs in conjunction with digital CMOS logic circuits in our approach (see Figure 17).

Figure 16. Contour plots showing the count of unique error cases, which is equal to the number of correction circuits required, for division implementation through approximation using eq. (24). Coefficient  $k_0$  ranges from -1.0 to -0.1.

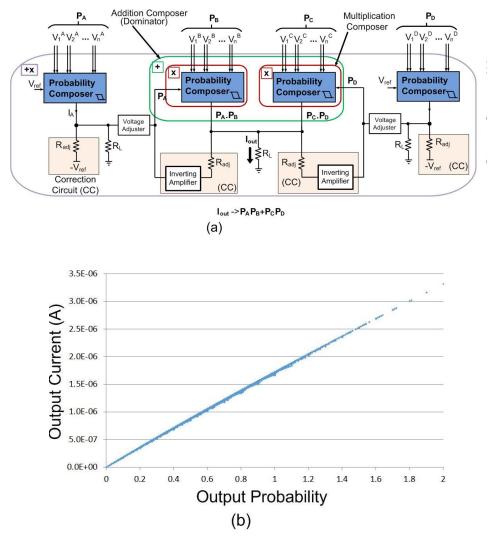

A more complex arithmetic operation such as sum-of-products (used frequently in BN inference) can be composed using these Elementary Addition and Multiplication Composers. We illustrate an example to compose an operation of the form  $(P_A.P_B)+(P_C.P_D)$ . One way to implement it is to use Elementary Addition and Multiplication Composers and connect them serially. However, the Probability

Figure 17. (a) Division schematic (through approximation using addition, multiplication and subtraction Composers and correction circuits); (b) Conditions for enabling correction circuits; (c) Test cascade for functional validation using HSPICE; and (d) HSPICE simulation output.

Arithmetic Composer framework allows us to implement it efficiently for parallel computation by hierarchically composing an Add-Multiply composer as follows.

Each product term implemented with an elementary Multiplication Composer is arranged in a topology of the Addition Composer (see Figure 18a). Thus the Dominator Composer structure is that of the adder, which uses elementary Multiplication Composers

Figure 18. (a) Add-Multiply Composer for calculating sum-of-products on input probabilities. The output is in analog current-domain, and corresponds to the function,  $P_A.P_B+P_C.P_D$ . The voltage adjusters are used to amplify the voltage from first Probability Composer stage, which is then used as input voltage for read-out at the second stage. These adjusters and other support circuits such as the inverting amplifiers can be implemented using CMOS analog circuits (e.g. op-amps); and (b) Output characteristics showing probability output for all possible input combinations and the corresponding output current value, which are obtained using HSPICE simulations.

as the basic building blocks. This topology realizes the add-multiply operation in a single

step (simulated output characteristics in Figure 18b).

In addition to these basic arithmetic operations on probabilities, normalization operation is used after computing updated beliefs at every node to ensure that resulting beliefs are probabilities. This can be implemented using current-mode CMOS analog circuits based on Gilbert normalizer circuit [15], as shown in Figure 19. If the input currents  $I_{in-1}$ ,  $I_{in-2}$ , etc. are in sub-threshold region of the MOSFET, then

$$I_{in-i} = I_0 e^{\kappa \frac{V_{di}}{V_T}}$$

$$I_{out-i} = I_0 e^{\kappa \frac{V_{di}}{V_T} - \frac{V_c}{V_T}}$$

(25)

where *i* is the index of the input cell ( $i \in \{1, 2, ..., n\}$  in this example),  $V_T$  is thermal voltage and  $\kappa$  is the subthreshold slope coefficient of the MOSFETs. Using Kirchhoff's current law at the common node  $V_C$ , we get

$$\sum_{i=1}^{n} I_{out-i} = I_b \tag{26}$$

Analog Domain (Voltage)

Figure 19. Normalization circuit for *n* inputs using MOSFETs.

where  $I_b$  is the constant current set by the reference voltage  $V_b$ . Substituting eq. (26) in (25) gives us the following relation, which is a normalization operation of the input currents. The input currents can be set using S-MTJ based Probability Composers.

$$I_{out-i} = I_b \frac{I_{in-i}}{\sum_{j=1}^{n} I_{in-j}}$$

(27)

# 3.9 Summary

In this chapter, we presented our approach towards using physically equivalent data representation for probabilities in the case of Bayesian Networks computing framework. We also discussed implementing elementary arithmetic operations on probabilities using physical laws in keeping with the mindset of physical equivalence for circuit implementation, through the Probability Arithmetic Composer framework. In the next chapter, we will introduce a physically equivalent architecture for Bayesian Networks.

## **CHAPTER 4**

# PHYSICALLY EQUIVALENT ARCHITECTURE FOR REASONING UNDER UNCERTAINTY

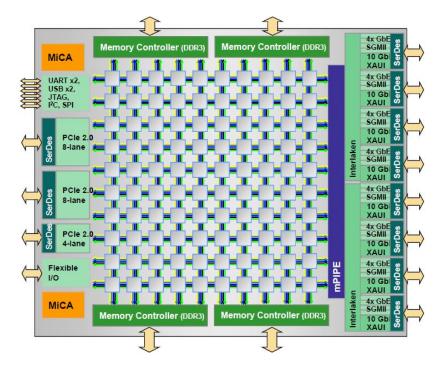

In keeping with the overarching philosophy of physical equivalence, the proposed architecture is designed such that it supports BNs intrinsically; i.e. there is a direct relationship to the structure of a BN graph and its physical implementation. Drawing inspiration from Field-Programmable Gate Arrays (FPGAs) that provide a reconfigurable hardware platform for mapping any digital Boolean logic function, we propose a

|                                | 1                                     |                                                                                                                                                                   |  |

|--------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                | von Neumann Computing                 | Physical Equivalence Paradigm                                                                                                                                     |  |

| Information<br>Representation  | Radix Boolean (Voltage)               | Flat Probability Vectors (Resistance, voltage, current)                                                                                                           |  |

|                                | Digital Logic, Pipelines,             | Non-volatile Probability Arithmetic                                                                                                                               |  |

| Approach                       | Arithmetic, Memory                    | Composer Circuits (memory-in-                                                                                                                                     |  |

|                                | Hierarchy, Multi Core                 | computing), Programmable Switch Boxes                                                                                                                             |  |

| Architectural<br>State         | Registers, Memory                     | Probability Tables, Beliefs, Likelihoods,<br>Priors incorporated into non-volatile<br>Composer Circuits; Network structure in<br>switch-boxes                     |  |

| Operations<br>Defined by       | Instruction Set Architecture<br>(ISA) | Roles – Learning, Inference, Adaptation                                                                                                                           |  |

| Plasticity                     | Explicit software update              | Autonomous learned behavior, reconfigurability                                                                                                                    |  |

| Machine                        | Explicitly timed instruction          | Event-based message propagation in                                                                                                                                |  |

| Execution                      | execution, data sharing               | network                                                                                                                                                           |  |

| Failure<br>Tolerance           | None – Susceptible to<br>single fault | Graceful degradation with faults                                                                                                                                  |  |

| Technology /<br>Primary Device | CMOS (charge-based) /<br>MOSFET       | Hybrid of CMOS and S-MTJs (charge,<br>magnetic)/<br>S-MTJ: Voltage controlled rotation of<br>magnetization; Resistance change is<br>persistent and can be readout |  |

| Target<br>Applications         | High precision arithmetic,            | Applications requiring causal learning                                                                                                                            |  |

|                                | interactive applications,             | and inference in various domains, under                                                                                                                           |  |

|                                | deterministic behavior                | uncertainty                                                                                                                                                       |  |

Table 2. Comparison: von Neumann Approach vs. Physical Equivalence Approach

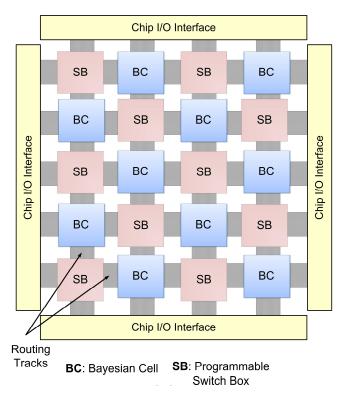

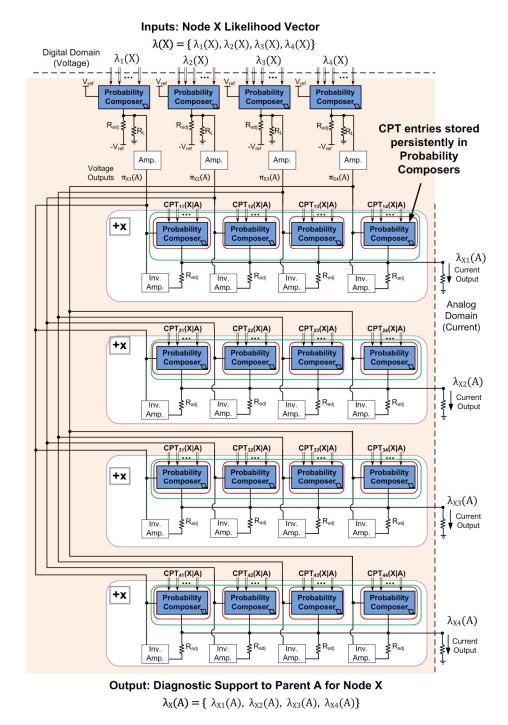

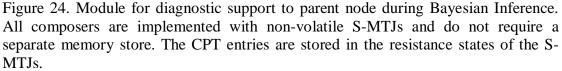

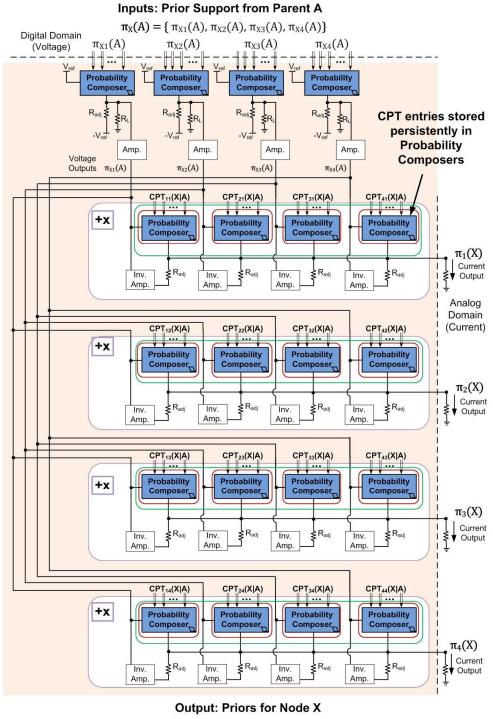

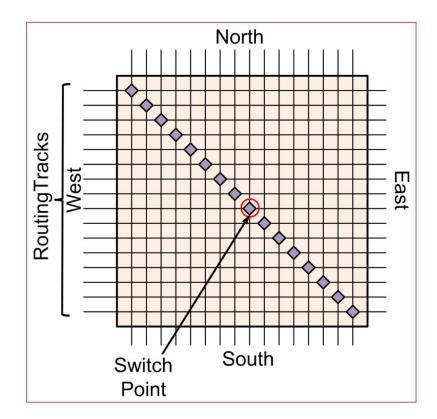

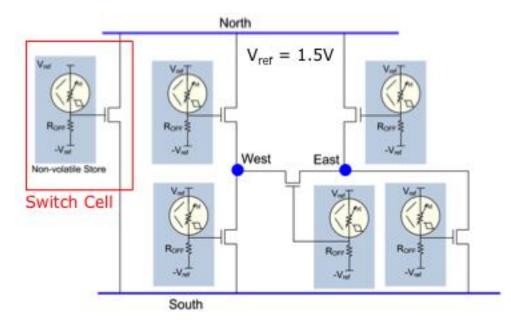

reconfigurable distributed Bayesian Cell architecture to map any given Bayesian Network structure (see Figure 20). This is a significant departure from conventional von Neumann architecture (Table 2). Each Bayesian Cell (or a cluster of multiple Bayesian Cells) implements computation for BN operations in a node. The network consists of several such Bayesian Cells interconnected in a mesh network, through a heterogeneous integration with CMOS metal routing stack for message propagation.

Each Bayesian Cell incorporates state information and conditional probability tables (CPT) intrinsically within non-volatile Probability Composer circuits, for inference and learning operations. Updates to the CPTs can be performed during learning and adaptation, by changing the resistance state of corresponding S-MTJs in the Probability

Figure 20. Proposed Reconfigurable Bayesian-Cell (BC) architecture. Each module in a BC is implemented with non-volatile Probability Composers (no separate memory needed). Routing tracks implemented with CMOS metal stack.