## University of Massachusetts Amherst

# ScholarWorks@UMass Amherst

**Doctoral Dissertations**

Dissertations and Theses

November 2015

# Threat Analysis, Countermeaures and Design Strategies for Secure Computation in Nanometer CMOS Regime

Raghavan Kumar University of Massachusetts - Amherst

Follow this and additional works at: https://scholarworks.umass.edu/dissertations\_2

Part of the Digital Circuits Commons, Hardware Systems Commons, Information Security Commons, Statistical Methodology Commons, and the VLSI and Circuits, Embedded and Hardware Systems Commons

#### **Recommended Citation**

Kumar, Raghavan, "Threat Analysis, Countermeaures and Design Strategies for Secure Computation in Nanometer CMOS Regime" (2015). *Doctoral Dissertations*. 430.

https://scholarworks.umass.edu/dissertations\_2/430

This Open Access Dissertation is brought to you for free and open access by the Dissertations and Theses at ScholarWorks@UMass Amherst. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

# THREAT ANALYSIS, COUNTERMEASURES AND DESIGN STRATEGIES FOR SECURE COMPUTATION IN NANOMETER CMOS REGIME

A Dissertation Presented

by

RAGHAVAN KUMAR

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

September 2015

Electrical and Computer Engineering

© Copyright by Raghavan Kumar 2015 All Rights Reserved

# THREAT ANALYSIS, COUNTERMEASURES AND DESIGN STRATEGIES FOR SECURE COMPUTATION IN NANOMETER CMOS REGIME

A Dissertation Presented by  ${\bf RAGHAVAN~KUMAR}$

| Approved as to style and content by | :                                     |

|-------------------------------------|---------------------------------------|

|                                     |                                       |

| Wayne P. Burleson, Chair            |                                       |

|                                     |                                       |

| Sandip Kundu, Member                |                                       |

|                                     |                                       |

| Christof Paar, Member               |                                       |

|                                     |                                       |

| Hava T. Siegelmann, Member          |                                       |

|                                     | Christopher V Hollot, Department Head |

Electrical and Computer Engineering

## ACKNOWLEDGMENTS

It is really an incredible feeling to think that I have reached this last phase of my graduate life. It is not about writing a chapter for my dissertation or submitting a journal, rather it is about framing the appropriate sentences for the *acknowledgments* section. This section might be *optional*, but it holds the key to how this document and in turn the entire work shaped up during the past few years.

First and foremost, I would like to thank my advisor Prof. Wayne Burleson for his constant guidance and support throughout my doctoral program. I am deeply indebted to him for providing me an opportunity to join his group when I was stuck in a not so noteworthy transition period. I appreciate him for allowing me to explore various research problems of my interest throughout my PhD curriculum. He also inspired me to actively collaborate with other research groups, keeping in mind the significant contribution made by individual authors in a particular project. I am immensely grateful to Prof. Sandip Kundu for supporting my profile to Prof. Wayne Burleson while he was looking for a fresh PhD candidate. He has always been a source of inspiration and knowledge throughout my stint at UMass. He has had a major constructive impact on some of the research projects presented in this dissertation. Special thanks go to Prof. Christof Paar and Prof. Hava Siegelmann for agreeing to serve on my dissertation committee and for their constructive insights and comments. I would also like to thank all the members of VLSI Circuits and Systems Group (VCSG) at UMass for creating a positive work atmosphere and also helping my transition as a PhD student during the initial days. My graduate life would have been utterly boring if not for the amazing friends I have made at Amherst. I will forever cherish the memories I had with the "Dunkin Coffee" group. Those long walks to the various parking lots depending on the commute of the day will be sorely missed.

During my PhD program, I had a unique opportunity to spend five amazing months at University of Passau in the splendid Bavarian region of Germany. I thank Dr. Ilia Polian for accepting to host me as a "Gastwissenschaftler" in his group. A major portion of the work on parametric fault-injection attacks presented in this dissertation was done during my stint at Passau. Special mention goes to Dr. Phillip Jovanovic for being an admirable colleague and contributor/co-author during and after my stay at Passau. Danke Schön. Apart from my stint at Passau, I also spent three highly productive months at Intel Circuits Research Lab (CRL) as an intern. I take this moment to thank everyone at CRL for providing me an opportunity to apply my "academic" skill-sets for solving various state-of-the-art industry oriented research problems.

My entire graduate life wouldn't have been possible, if not for the constant love and support of my wonderful parents. They have absorbed all the immense pressure and troubles created by me when things were not particularly going well during my graduate life. Thanking them alone wouldn't do enough justice. This entire dissertation is dedicated to them.

## ABSTRACT

# THREAT ANALYSIS, COUNTERMEASURES AND DESIGN STRATEGIES FOR SECURE COMPUTATION IN NANOMETER CMOS REGIME

#### SEPTEMBER 2015

#### RAGHAVAN KUMAR

B.E., ANNA UNIVERSITY, CHENNAI, INDIA

M.S., UNIVERSITY OF MASSACHUSETTS AMHERST

Ph.D., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Wayne P. Burleson

Advancements in CMOS technologies have led to an era of *Internet Of Things* (*IOT*), where the devices have the ability to communicate with each other apart from their computational power. As more and more sensitive data is processed by embedded devices, the trend towards lightweight and efficient cryptographic primitives has gained significant momentum. Achieving a perfect security in silicon is extremely difficult, as the traditional cryptographic implementations are vulnerable to various active and passive attacks. There is also a threat in the form of "hardware Trojans" inserted into the supply chain by the untrusted third-party manufacturers for economic incentives. Apart from the threats in various forms, some of the embedded security applications such as random number generators (RNGs) suffer from the impacts of process variations and noise in nanometer CMOS. Despite their dis-

advantages, the random and unique nature of process variations can be exploited for generating unique identifiers and can be of tremendous use in embedded security.

In this dissertation, we explore techniques for precise fault-injection in cryptographic hardware based on voltage/temperature manipulation and hardware Trojan insertion. We demonstrate the effectiveness of these techniques by mounting fault attacks on state-of-the-art ciphers. Physically Unclonable Functions (PUFs) are novel cryptographic primitives for extracting secret keys from complex manufacturing variations in integrated circuits (ICs). We explore the vulnerabilities of some of the popular "strong" PUF architectures to modeling attacks using Machine Learning (ML) algorithms. The attacks use silicon data from a test chip manufactured in IBM 32nm silicon-on-insulator (SOI) technology. Attack results demonstrate that the majority of "strong" PUF architectures can be predicted to very high accuracies using limited training data. We also explore the techniques to exploit unreliable data from "strong" PUF architectures and effectively use them to improve the prediction accuracies of modeling attacks. Motivated by the vulnerabilities of existing PUF architectures, we present a novel modeling attack resistant PUF architecture based on non-linear computing elements. Post-silicon validation results are used to demonstrate the effectiveness of the non-linear PUF architecture against modeling and fault-injection attacks. Apart from the techniques to improve the security of PUF circuits, we also present novel solutions to improve the performance of PUF circuits from the perspectives of IC fabrication and system/protocol design. Finally, we present a statistical benchmark suite to evaluate PUFs in conceptualization phase and also to enable fine-grained security assessments for varying PUF parameters. Data compressibility analyses for validating the statistical benchmark suite are also presented.

# TABLE OF CONTENTS

|    |                   |                |                               |                                | Page       |

|----|-------------------|----------------|-------------------------------|--------------------------------|------------|

| A  | CKN               | OWLI           | EDGME                         | ENTS                           | v          |

| Al | BST               | RACT           |                               |                                | vii        |

| LI | ST (              | OF TA          | BLES                          |                                | <b>xiv</b> |

| LI | ST (              | OF FIG         | GURES.                        |                                | xvii       |

|    |                   |                |                               |                                |            |

| CI | HAP               | TER            |                               |                                |            |

| 1. | INT               | RODI           | UCTION                        | N                              | 1          |

|    | 1.1<br>1.2<br>1.3 | Explo          | iting Proc                    | rity and Vulnerabilities       | 5          |

| 2. | BA                | CKGR           | OUND                          |                                | 11         |

|    | 2.1               | Source         | es of CMC                     | OS Process Variations          | 11         |

|    |                   | 2.1.1          | Manufac                       | cturing Process and Variations | 11         |

|    |                   |                | 2.1.1.1<br>2.1.1.2            | Systematic Variations          |            |

|    |                   | 2.1.2          | Environ                       | nmental Variations and Aging   | 13         |

|    | 2.2               | PUF 7          | Terminolo                     | ogies and Performance Metrics  | 14         |

|    |                   | 2.2.1<br>2.2.2 |                               | ge-Response pairs (CRP)        |            |

|    |                   |                | 2.2.2.1<br>2.2.2.2<br>2.2.2.3 | Uniqueness                     | 16         |

|    |     |        | 2.2.2.4<br>2.2.2.5 | Uniformity                              |    |

|----|-----|--------|--------------------|-----------------------------------------|----|

|    | 2.3 | םוום ו | Dogica Fl          | ow                                      |    |

|    | 2.3 | ГОГІ   | Jesign Fr          | ow                                      | 10 |

|    |     | 2.3.1  | Pre-fabr           | rication phase                          | 20 |

|    |     | 2.3.2  |                    | orication phase                         |    |

| 3. | PAI | RAME   | TRIC F             | AULT INJECTION ATTACKS ON               |    |

|    | (   | CRYP'  | TOGRA              | PHIC HARDWARE                           | 23 |

|    | 3.1 | Backg  | round              |                                         | 24 |

|    |     | 3.1.1  | Fault In           | jection Techniques                      | 24 |

|    |     | 3.1.2  | Hardwa             | re Trojans                              | 27 |

|    | 3.2 | V/T F  | Fault Inje         | ction                                   | 30 |

|    | 3.3 | ,      |                    | n-based Fault Injection                 |    |

|    |     | 3.3.1  | TroianC            | Conc: Doping Concentration Manipulation | 35 |

|    |     | 3.3.2  | -                  | Area: Dopant Area Manipulation          |    |

|    |     | 3.3.3  | •                  | Activation                              |    |

|    |     | 3.3.4  | •                  | Model                                   |    |

|    |     | 3.3.5  |                    | measures and Detection                  |    |

|    |     |        | 3.3.5.1            | Functional testing                      | 42 |

|    |     |        | 3.3.5.2            | Side-channel analysis                   |    |

|    |     |        | 3.3.5.3            | Optical Inspection                      |    |

|    | 3.4 | Result | S                  |                                         | 45 |

|    |     | 3 4 1  | LED-64             |                                         | 46 |

|    |     | 0.1.1  |                    |                                         |    |

|    |     |        | 3.4.1.1            | General Layout                          |    |

|    |     |        | 3.4.1.2            | Circuit implementation                  |    |

|    |     |        | 3.4.1.3            | Fault-based cryptanalysis               |    |

|    |     |        | 3.4.1.4            | Parametric fault injection              |    |

|    |     |        | 3.4.1.5            | V/T fault injection results             |    |

|    |     |        | 3.4.1.6            | Trojan fault injection results          |    |

|    |     |        | 3.4.1.7            | Cryptanalysis results                   | 52 |

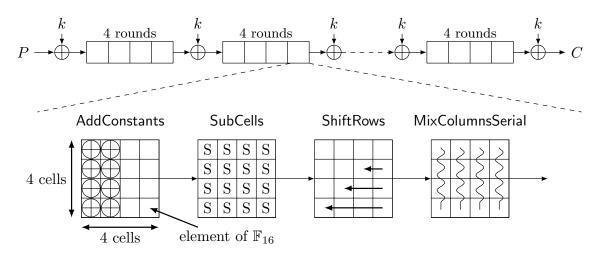

|    |     | 3.4.2  | PRINCI             | E                                       | 54 |

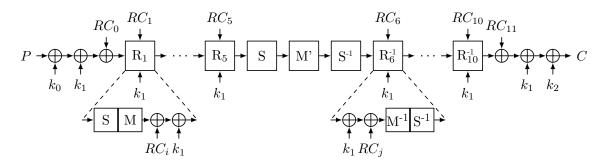

|    |     |        | 3.4.2.1            | General Layout                          | 54 |

|    |     |        | 3.4.2.2            | Circuit implementation                  |    |

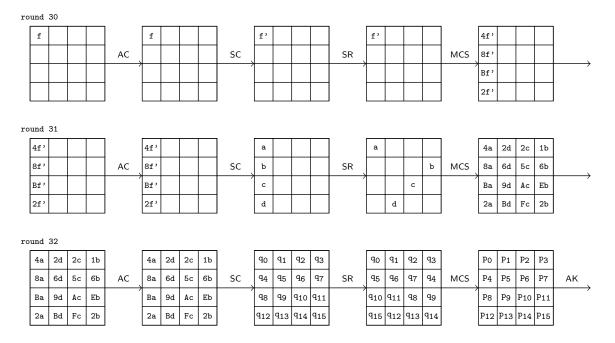

|    |     |        | 3.4.2.3            | Fault-based cryptanalysis               | 55 |

|    |     |        | 3.4.2.4            | Parametric fault injection              |    |

|    |            |                                  | 3.4.2.5<br>3.4.2.6<br>3.4.2.7 |                                               | ection results injection results | ts       | <br>58  |

|----|------------|----------------------------------|-------------------------------|-----------------------------------------------|----------------------------------|----------|---------|

| 4. |            |                                  |                               | CACKS ON P                                    |                                  |          | 63      |

|    | 4.1        | PUF 7                            | Targets                       |                                               |                                  |          | <br>65  |

|    |            | 4.1.1<br>4.1.2                   |                               | PUFsrward Arbiter l                           |                                  |          |         |

|    | 4.2<br>4.3 |                                  |                               | Performance Are<br>eling Attacks .            |                                  |          |         |

|    |            | 4.3.1<br>4.3.2                   |                               | Vector Machir<br>on Strategies                |                                  |          |         |

|    | 4.4<br>4.5 |                                  |                               | r-based PUFs .<br>k Results for Γ             |                                  |          |         |

|    |            | 4.5.1                            | Impact                        | of Error-inflicte                             | ed CRPs                          |          | <br>81  |

|    | 4.6        | Hybrid                           | d attacks                     | on delay-based                                | l PUFs                           |          | <br>86  |

|    |            | 4.6.1<br>4.6.2                   |                               | f Fault Injection<br>jection assisted         |                                  |          |         |

| 5. |            |                                  |                               | TACK RESIS                                    |                                  |          |         |

|    | 5.1<br>5.2 |                                  |                               | PUFssting Current-b                           |                                  |          | <br>96  |

|    |            | 5.2.1<br>5.2.2<br>5.2.3<br>5.2.4 | Attack I<br>Impact o          | Model                                         | ed CRPs                          |          | <br>101 |

|    |            |                                  | 5.2.4.1                       | Performance                                   | of Hybrid atta                   | acks     | <br>108 |

|    | 5.3        | Non-li                           | near Curi                     | rent Mirror bas                               | sed PUF Arch                     | itecture | <br>111 |

|    |            | 5.3.1<br>5.3.2<br>5.3.3<br>5.3.4 | Effect of nlcPUF              | of Non-linearity f Process Varia Architecture | tions                            |          | <br>112 |

|    |     | 5.3.5<br>5.3.6 |                    | con Validation of nlcPUF                       |     |

|----|-----|----------------|--------------------|------------------------------------------------|-----|

|    |     |                | 5.3.6.1            | Modeling attacks validation of nlcPUF          | 118 |

|    |     | 5.3.7          | Hybrid .           | Attacks on nlcPUF                              | 120 |

| 6. |     |                |                    | EGIES FOR PUF CIRCUITS AND                     |     |

|    | ,   | SYSTE          | EMS                |                                                | 124 |

|    | 6.1 | Lithog         | graphy Av          | ware Design of Physically Unclonable Functions | 124 |

|    |     | 6.1.1<br>6.1.2 |                    | work                                           |     |

|    |     |                | 6.1.2.1            | Outline of the Proposed Scheme                 | 129 |

|    |     | 6.1.3          | Lithogra           | aphic Simulation Results                       | 129 |

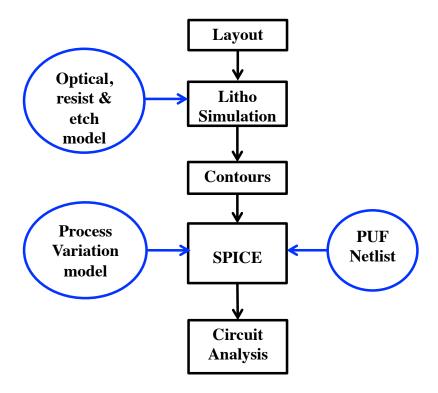

|    |     |                | 6.1.3.1            | Manufacturing Aware Physical Design Framework  | 129 |

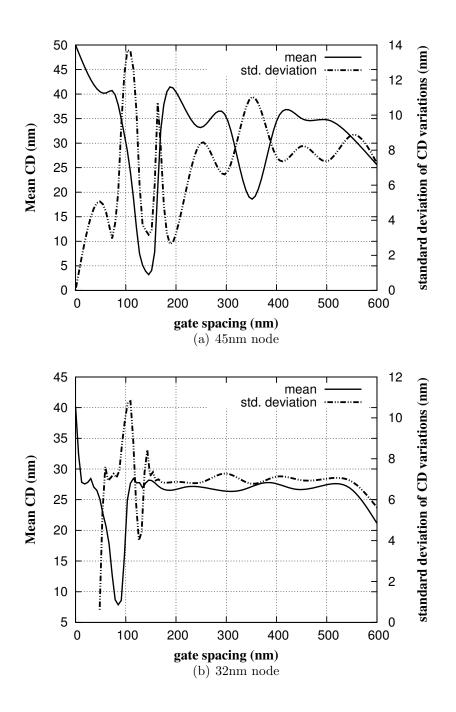

|    |     |                | 6.1.3.2            | Intra-die PV model                             |     |

|    |     |                | 6.1.3.3            | Inter-die PV model                             | 132 |

|    |     |                | 6.1.3.4            | Inter-wafer PV model                           | 133 |

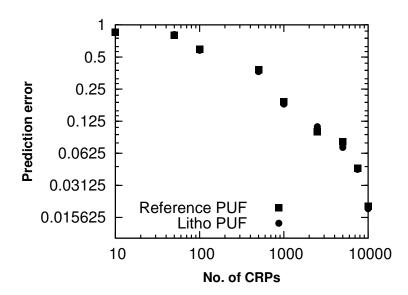

|    |     |                | 6.1.3.5            | Performance metrics computation                | 134 |

|    | 6.2 | PHAF           | P: Passwo          | rd based Authentication System using PUFs      | 137 |

|    |     | 6.2.1          | Backgro            | ound and Related Work for PHAP                 | 139 |

|    |     | 6.2.2          |                    | Systems                                        |     |

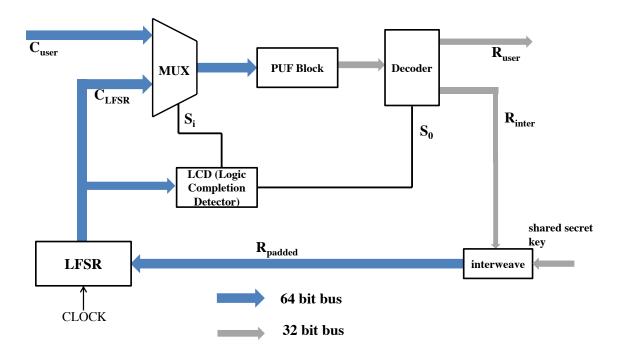

|    |     | 6.2.3          | PHAP A             | Architecture                                   | 141 |

|    |     | 6.2.4          |                    | cication protocol                              |     |

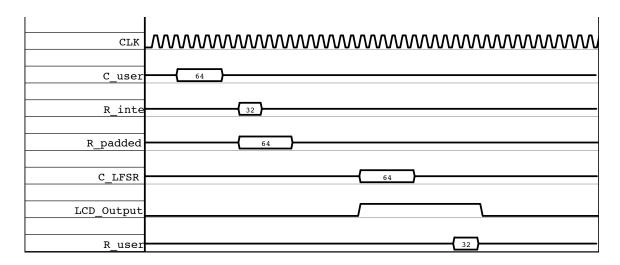

|    |     | 6.2.5          | Simulati           | ion Results                                    | 146 |

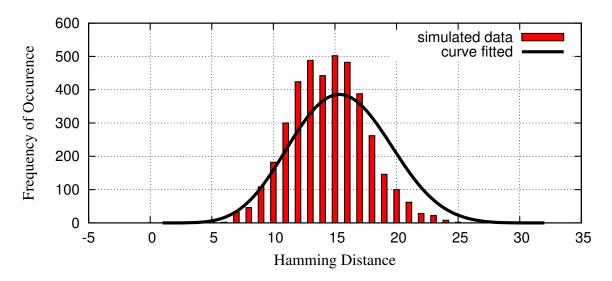

|    |     |                | 6.2.5.1<br>6.2.5.2 | PUF Block                                      |     |

|    |     | 6.2.6          | Security           | Analysis of PHAP                               | 150 |

| 7. | SIL | ICON           | PROTO              | OTYPING                                        | 155 |

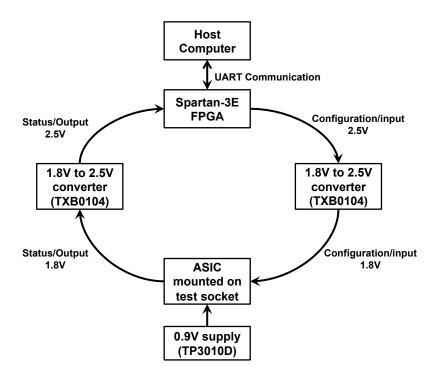

|    | 7.1 | Measu          | rement se          | etup                                           | 158 |

| 8. | STA | ATIST          | ICAL B             | ENCHMARKING FOR PUFS                           | 161 |

|    | 0.1 | т, т           |                    |                                                | 101 |

|    |       |        | Need for Benchmarks                            |       |

|----|-------|--------|------------------------------------------------|-------|

|    | 8.2   | Statis | tical Benchmarking                             | . 163 |

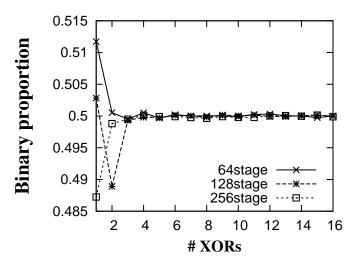

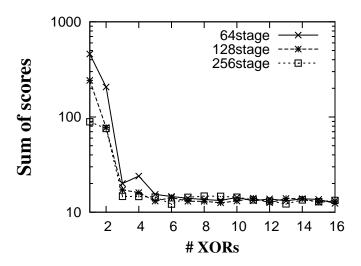

|    |       | 8.2.1  | Impact of varying challenge generation methods | . 165 |

|    | 8.3   | Respo  | onse Compressibility Analysis                  | . 169 |

| 9. | CO    | NCLU   | SION AND FUTURE WORK                           | 173   |

|    | 9.1   | Future | e Work                                         | . 176 |

| DI | m t   | OCD A  | APHY                                           | 150   |

| к  | IBL/I | いっちゃ   | APHY                                           | 179   |

# LIST OF TABLES

| Page                                                                                                                         | Table |

|------------------------------------------------------------------------------------------------------------------------------|-------|

| Comparison of Fault-injection Techniques                                                                                     | 3.1   |

| Detection of Hardware Trojans                                                                                                | 3.2   |

| Best-case $V/T$ Fault Injection percentages for eight random instances of LED-64                                             | 3.3   |

| The PRINCE round constants                                                                                                   | 3.4   |

| Summary of Fault-injection Attacks                                                                                           | 3.5   |

| Overview on the number of required faults                                                                                    | 3.6   |

| Summary of arbiter PUF's performance metrics from statistical circuit simulations and post-silicon measurements 69           | 4.1   |

| Summary of Feed-forward arbiter PUF's performance metrics from statistical circuit simulations and post-silicon measurements | 4.2   |

| Summary of modeling attacks on arbiter PUFs using silicon data81                                                             | 4.3   |

| Summary of modeling attacks on Feed-forward arbiter PUFs using silicon data                                                  | 4.4   |

| Summary of the bit-flips measurements for delay-based PUF designs in 32nm technology                                         | 4.5   |

| Summary of the impacts of error-inflicted CRPs on prediction rates for arbiter PUFs85                                        | 4.6   |

| Summary of the impacts of error-inflicted CRPs on prediction rates for Feed-forward arbiter PUFs86                           | 4.7   |

| Summary of hybrid attack's performance on arbiter and feed-forward arbiter PUFs using silicon data                           | 4.8   |

| 4.9 | Summary of some major results from modeling and hybrid attacks on delay-based PUFs                                                                                                                                        |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1 | Standalone ML attack results on current-based PUFs using stable CRPs from 32nm test chip                                                                                                                                  |

| 5.2 | Bit flip measurements from 32nm Current-based PUFs. Intrinsic bit flips were observed from repeated measurements under optimal conditions, whereas extrinsic bit flips were observed by changing the operating conditions |

| 5.3 | Impact of error-inflicted CRPs on ML prediction rates for current-based PUFs                                                                                                                                              |

| 5.4 | Performance of hybrid attacks on current-based PUFs. The results were averaged over 20 different PUF instances on test chip.  Around, 7% of unreliable CRPs were present in the training set used in hybrid attacks       |

| 5.5 | Area details of a single instance of various nlcPUF circuits                                                                                                                                                              |

| 5.6 | Performance validation of nlcPUF and comparison to other strong PUF architectures                                                                                                                                         |

| 5.7 | Security Validation of nlcPUF and comparison to other strong PUFs                                                                                                                                                         |

| 6.1 | Intra-die PV model                                                                                                                                                                                                        |

| 6.2 | Inter-die MP model                                                                                                                                                                                                        |

| 6.3 | Inter-die and Inter-wafer PV models                                                                                                                                                                                       |

| 6.4 | Uniqueness validation results for litho-aware and conventional arbiter PUFs                                                                                                                                               |

| 6.5 | Uniqueness validation results for litho-aware and conventional current-based PUFs                                                                                                                                         |

| 6.6 | Impact of litho-aware design on other performance metrics for arbiter PUFs                                                                                                                                                |

| 6.7 | Impact of litho-aware design on other performance metrics for current-based PUFs                                                                                                                                          |

| 6.8  | Description of Notations                                  |

|------|-----------------------------------------------------------|

| 6.9  | Password Card (either session or user password)           |

| 6.10 | Trusted Authority's Database                              |

| 6.11 | Authentication Protocol                                   |

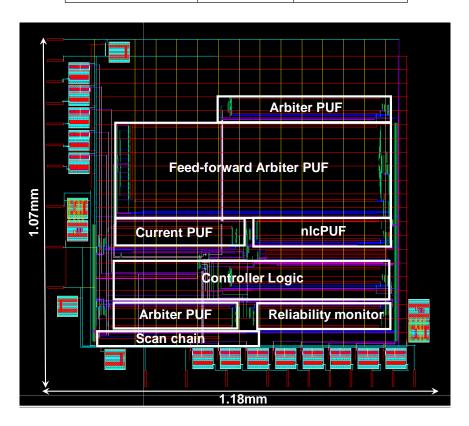

| 7.1  | Available PUF circuits in <i>sugarloaf</i>                |

| 7.2  | Configuration bits description                            |

| 7.3  | Area details of a single instance of various PUF circuits |

# LIST OF FIGURES

| re Pag                                                                                                                             | çe |

|------------------------------------------------------------------------------------------------------------------------------------|----|

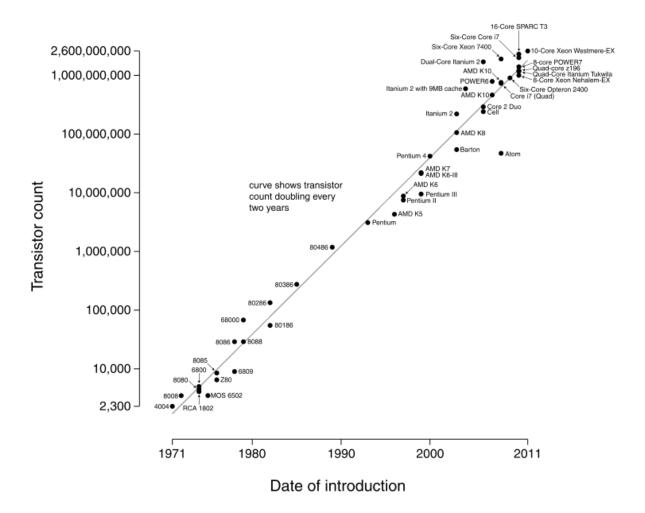

| 1 Moore's law [68]                                                                                                                 | 6  |

| 1 Sources of variations in ICs                                                                                                     | 12 |

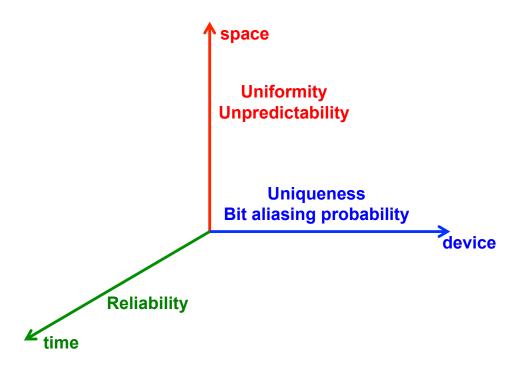

| 2 PUF Performance metrics and dimensions                                                                                           | L5 |

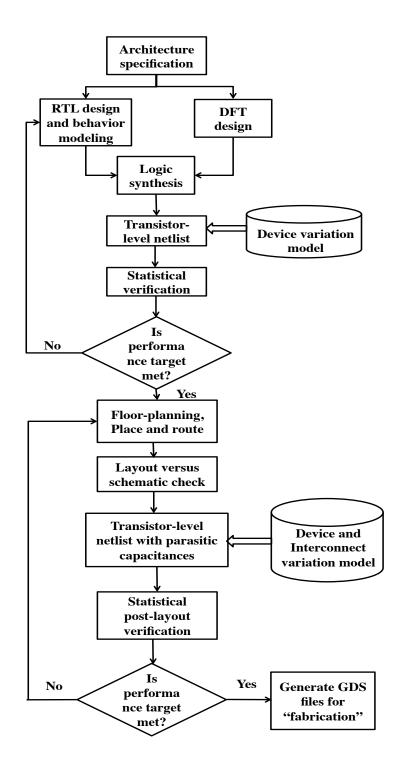

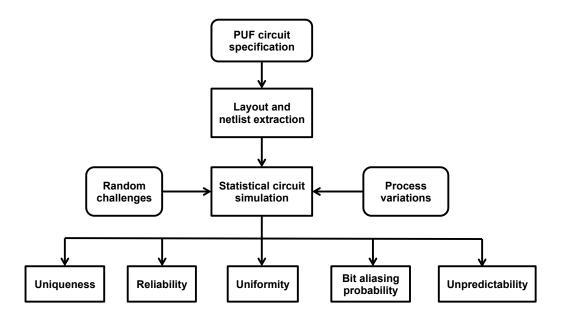

| 3 PUF design flow                                                                                                                  | L9 |

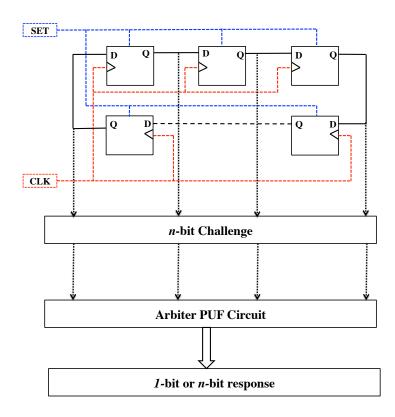

| 4 Arbiter PUF circuit with on-chip LFSR for challenge generation 2                                                                 | 21 |

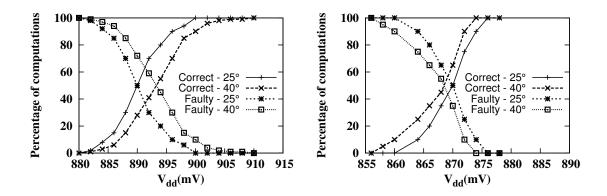

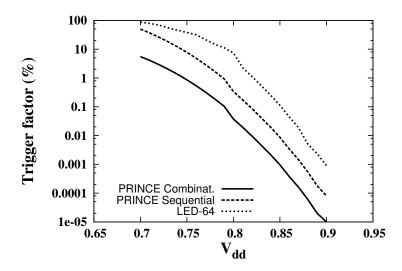

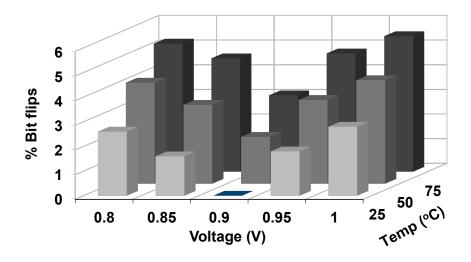

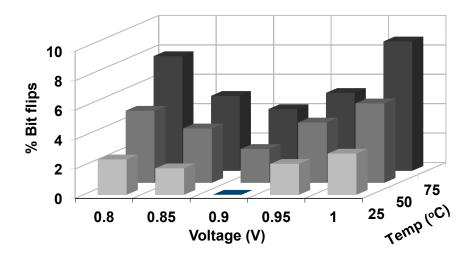

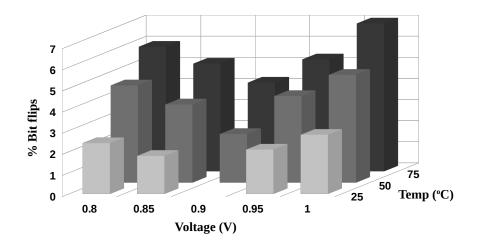

| Percentage of correct and faulty computations as a function of $V_{\rm dd}$ and temperature in PRINCE (left) and LED-64 (right)    | 34 |

| Percentage of injected faults in a single nibble as a function of $V_{\rm dd}$ and temperature in PRINCE (left) and LED-64 (right) | 34 |

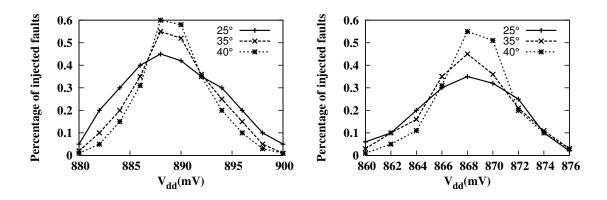

| 3 Cross-sectional view of (a) original inverter and (b) Trojan inverter using doping concentration manipulation                    | 37 |

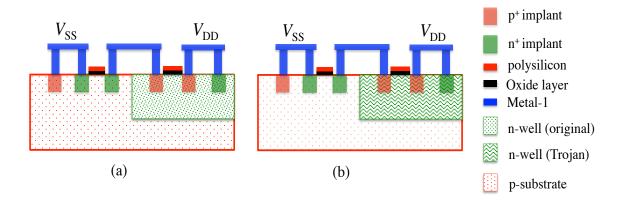

| 4 Layout of (a) original inverter and (b) Trojan inverter using dopant area manipulation                                           | 39 |

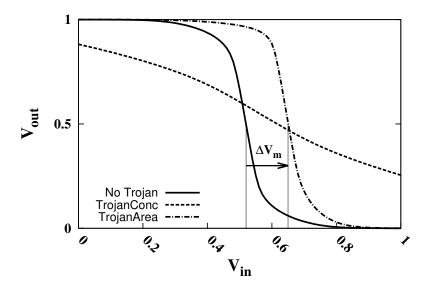

| 5 Electrical characteristics of the unmodified and Trojan inverters                                                                | 39 |

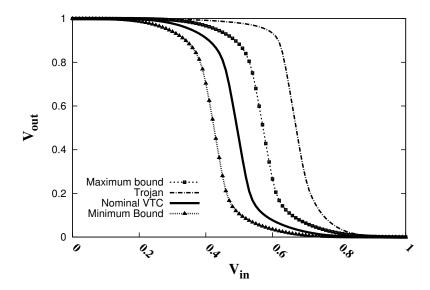

| 6 Impact of process variations on Nominal VTC and the Trojan VTC                                                                   | 10 |

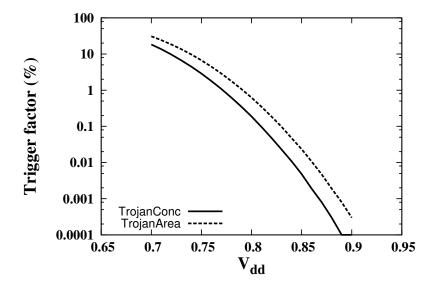

| 7 Triggering factor of the Trojan inverters                                                                                        | 10 |

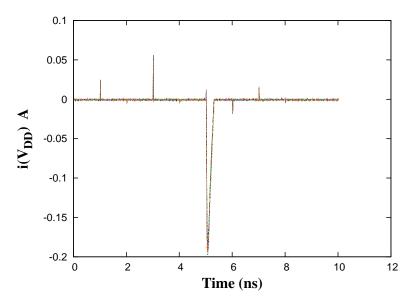

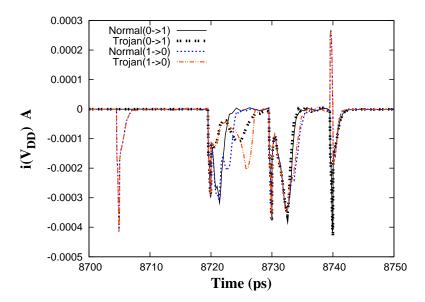

| 8 Supply drawn current for PRINCE                                                                                                  | 14 |

| 9 Supply drawn currents for the original and Trojan inverters                                                                      | 15 |

| 10 Layout of LED-64                                                                                                                | 16 |

| 3.11 | Propagation of the injected fault                                                                                                                                                                                                                                                                                                                                                                     | . 48 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.12 | Equation construction for the attack on LED-64                                                                                                                                                                                                                                                                                                                                                        | . 48 |

| 3.13 | Overview of attack on LED-64 using fault injection                                                                                                                                                                                                                                                                                                                                                    | . 50 |

| 3.14 | LED-64 analysis results                                                                                                                                                                                                                                                                                                                                                                               | . 53 |

| 3.15 | Layout of PRINCE                                                                                                                                                                                                                                                                                                                                                                                      | . 54 |

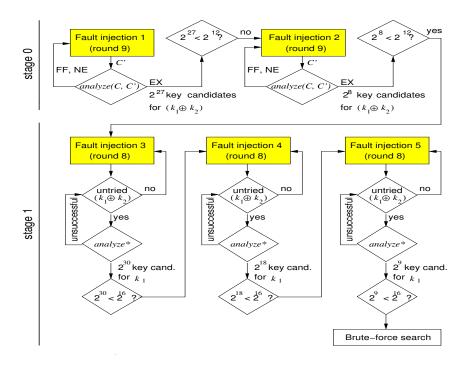

| 3.16 | Overview of attack on PRINCE using 2 EX fault injections in stage 0 and 3 EX injections in stage 1 with $\tau_0 = 2^{12}$ and $\tau_1 = 2^{16}$                                                                                                                                                                                                                                                       | . 56 |

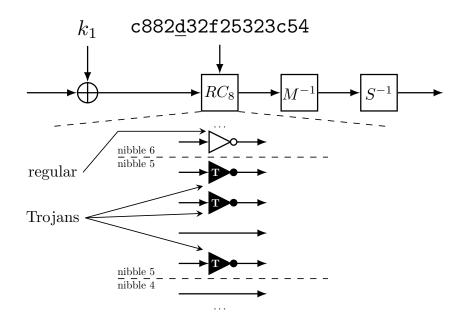

| 3.17 | Schematics of PRINCE MAPLE Trojans                                                                                                                                                                                                                                                                                                                                                                    | . 59 |

| 3.18 | Trigger factor of the Trojan inverters inserted into LED-64 and PRINCE                                                                                                                                                                                                                                                                                                                                | . 60 |

| 3.19 | Percentage of Trojan induced exploitable faults in LED-64 and PRINCE                                                                                                                                                                                                                                                                                                                                  | . 60 |

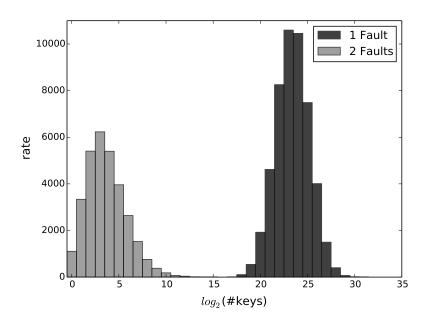

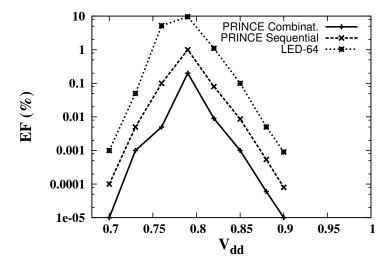

| 3.20 | PRINCE analysis results for stages 0 (upper) and 1 (lower)                                                                                                                                                                                                                                                                                                                                            | . 61 |

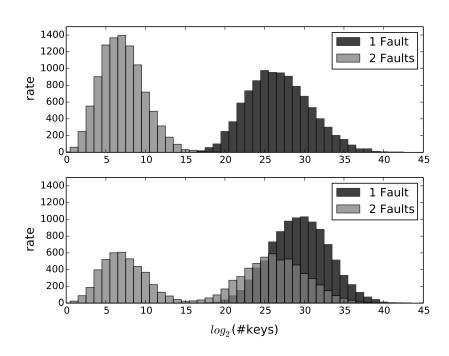

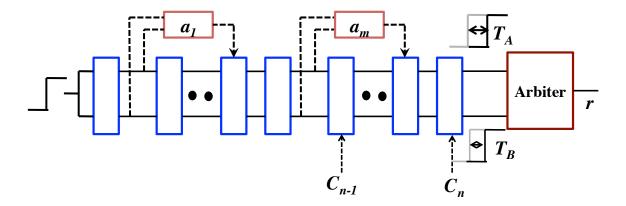

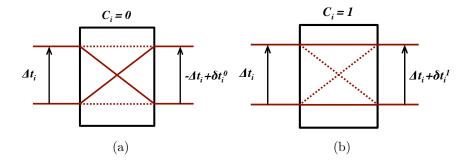

| 4.1  | (a) Arbiter PUF architecture with $n$ stages; (b) NAND gate based implementation of a single MUX/switch stage. The path of propagation of two signals $top_i$ and $bot_i$ is determined by the challenge bit $C_i$ . If $C_i = 1$ , then $top_{i+1} = top_i$ and $bot_{i+1} = bot_i$ . Else, $top_{i+1} = bot_i$ and $bot_{i+1} = top_i$                                                              | . 66 |

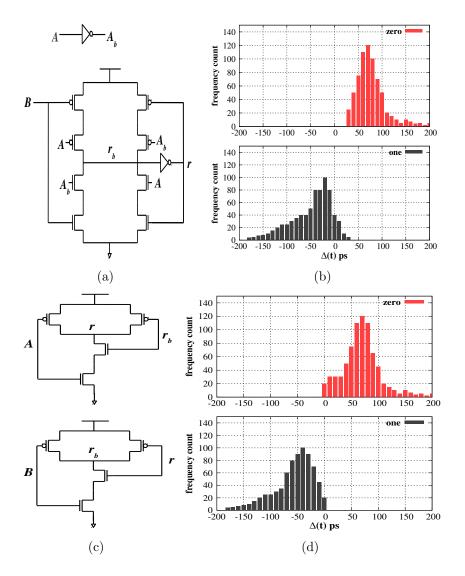

| 4.2  | Fairness evaluation of arbiters based on bias point for choosing $0/1$ output. The bias point is given by $\Delta(t) = T_A - T_B$ (a) A simple D-Type flip-flop arbiter; (b) Plot showing the bias point of d-type flip-flop arbiter for choosing $0/1$ around 30 ps; (c) A simple SR-NAND latch arbiter; (d) Plot showing the bias point of SR NAND arbiter for choosing $0/1$ approximately at 0 ps | . 68 |

| 4.3  | Feed-forward arbiter PUF                                                                                                                                                                                                                                                                                                                                                                              | . 69 |

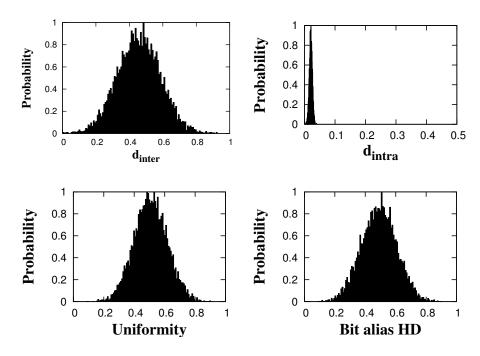

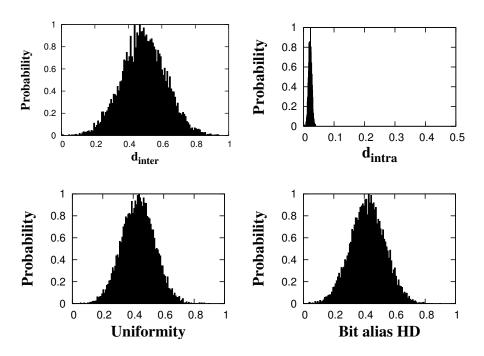

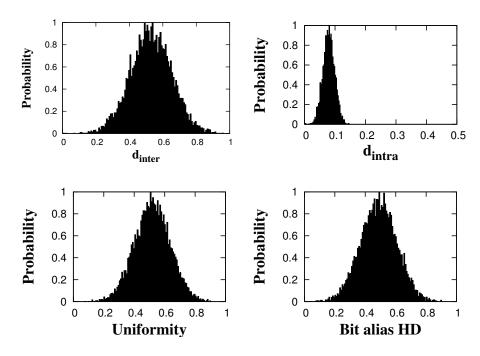

| 4.4  | Arbiter PUF's performance metrics distribution from statistical circuit simulations                                                                                                                                                                                                                                                                                                                   | . 70 |

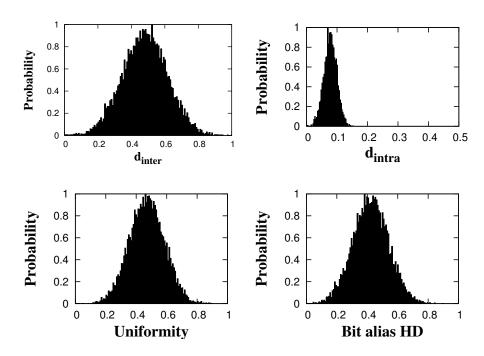

| 4.5  | Arbiter PUF's performance metrics distribution from post-silicon measurements                                                                                                                                                                                                                                                                                                                         | . 71 |

| 4.6  | Methodology for analyzing the performance metrics of PUF circuits                                       |

|------|---------------------------------------------------------------------------------------------------------|

| 4.7  | Feed-forward arbiter PUF's performance metrics distribution from statistical circuit simulations        |

| 4.8  | Feed-forward arbiter PUF's performance metrics distribution from post-silicon measurements              |

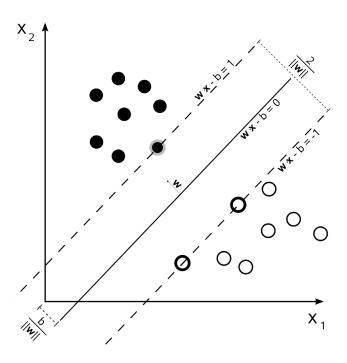

| 4.9  | Data classification in Support Vector Machines                                                          |

| 4.10 | Delay difference parameters for (a) $C_i = 0$ and (b) $C_i = 1 \dots 77$                                |

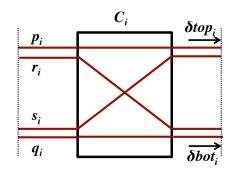

| 4.11 | Individual delay components of a single stage of an arbiter PUF                                         |

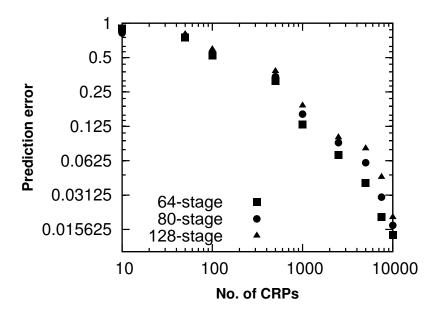

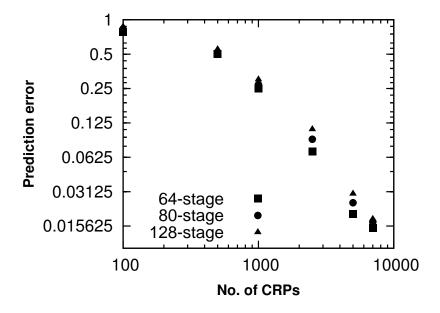

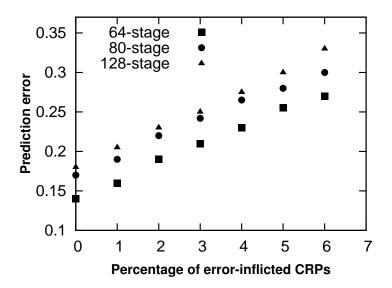

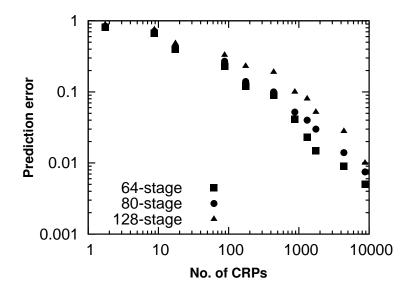

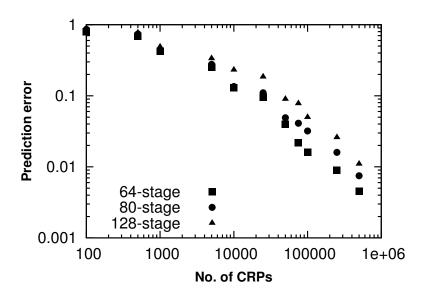

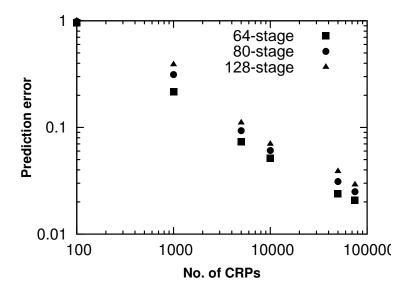

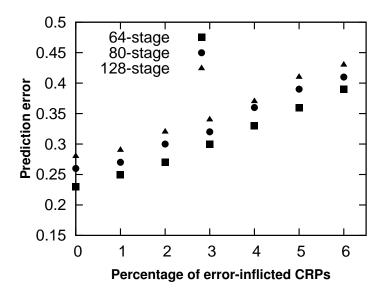

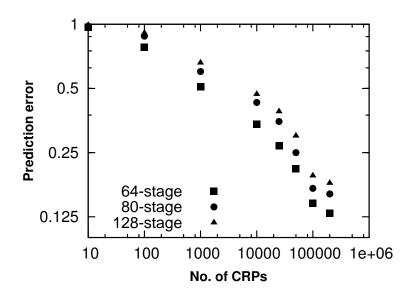

| 4.12 | Prediction errors from SVM attacks on 64, 80 and 128 stage arbiter PUFs                                 |

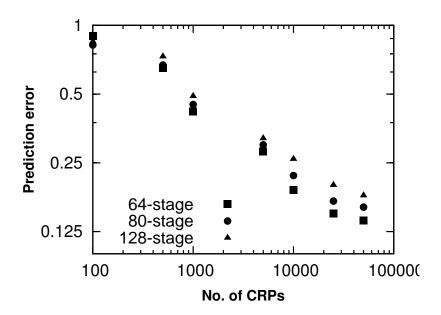

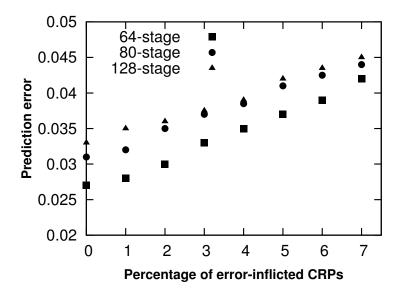

| 4.13 | Prediction errors from SVM attacks on 64, 80 and 128 stage feed-forward arbiter PUFs                    |

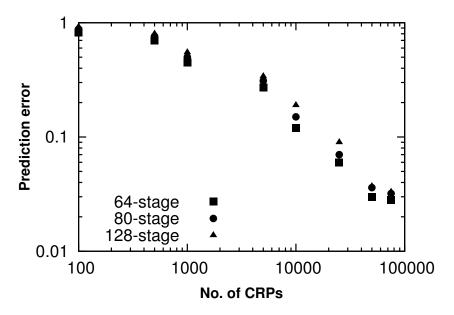

| 4.14 | Prediction errors from ES attacks on 64, 80 and 128 stage arbiter PUFs                                  |

| 4.15 | Prediction errors from ES attacks on 64, 80 and 128 stage feed-forward arbiter PUFs                     |

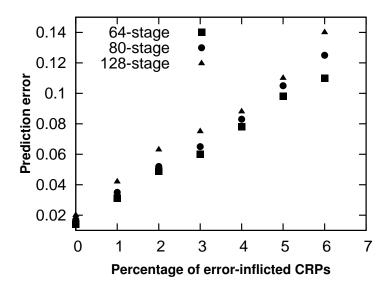

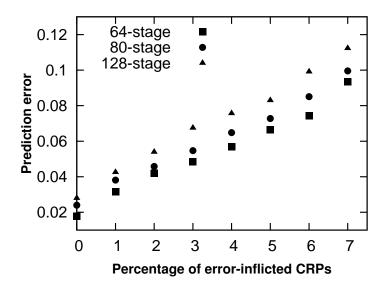

| 4.16 | Impact of the error-inflicted CRPs on the prediction rates of SVM attacks for arbiter PUFs              |

| 4.17 | Impact of the error-inflicted CRPs on the prediction rates of ES attacks for arbiter PUFs               |

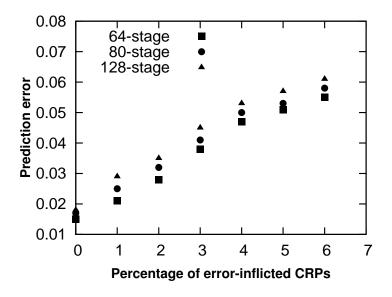

| 4.18 | Impact of the error-inflicted CRPs on the prediction rates of SVM attacks for Feed-forward arbiter PUFs |

| 4.19 | Impact of the error-inflicted CRPs on the prediction rates of ES attacks for Feed-forward arbiter PUFs  |

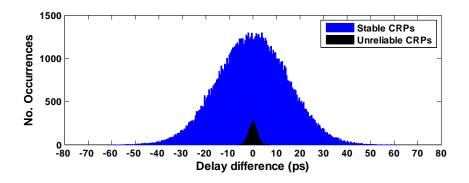

| 4.20 | Delay-difference distributions of error-free and error-inflicted CRPs from arbiter PUFs                 |

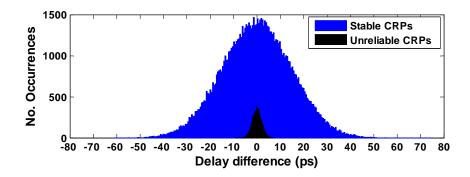

| 4.21 | Delay-difference distributions of error-free and error-inflicted CRPs from feed-forward arbiter PUFs    |

| 4.22 | Amount of bit-flips with $\Delta t_n < \Delta t_{min}$ for arbiter PUFs                                                                                                                                                                        |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.23 | Amount of bit-flips with $\Delta t_n < \Delta t_{min}$ for feed-forward arbiter PUFs                                                                                                                                                           |

| 4.24 | Impact of the number of error-inflicted CRPs on the strength of PUF models                                                                                                                                                                     |

| 4.25 | Performance of hybrid attacks on arbiter PUFs under the presence of 6% error-inflicted CRPs                                                                                                                                                    |

| 4.26 | Performance of hybrid attacks on feed-forward arbiter PUFs under the presence of 7% error-inflicted CRPs92                                                                                                                                     |

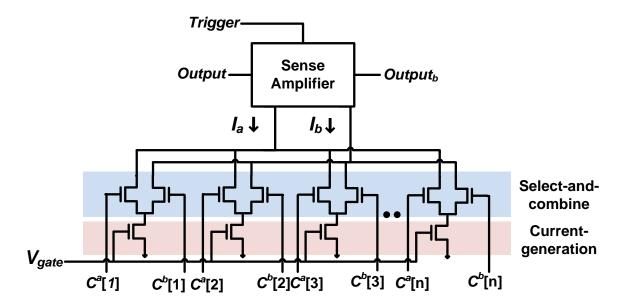

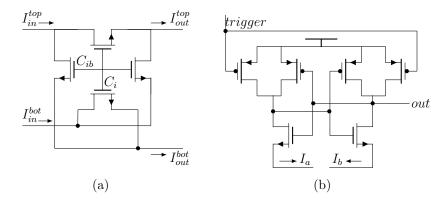

| 5.1  | Current-based PUF architecture [61]. $C^a[i]$ and $C^b[i]$ represents the challenge bits of a single stage. The inputs to the sense amplifier are the currents $I_a$ and $I_b$ . $output_b$ refers to the complimentary form of the output bit |

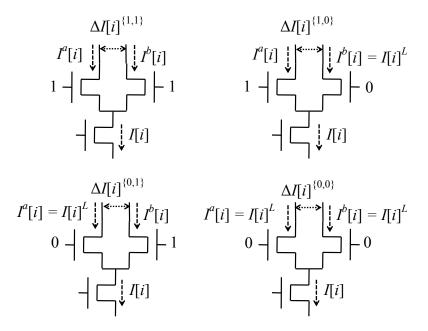

| 5.2  | Current difference modeling parameters for Current-based PUFs 100                                                                                                                                                                              |

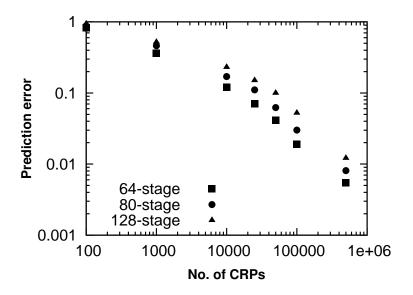

| 5.3  | Prediction errors from SVM attacks for 64, 80 and 128 stage Current-based PUFs                                                                                                                                                                 |

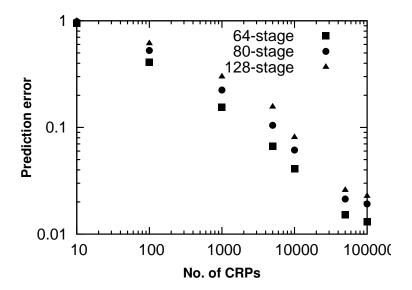

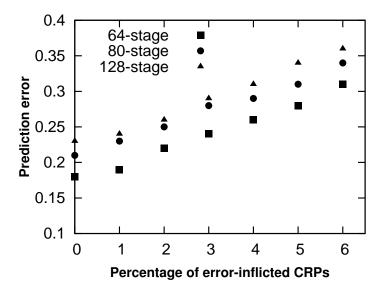

| 5.4  | Prediction errors from ES attacks for 64, 80 and 128 stage Current-based PUFs                                                                                                                                                                  |

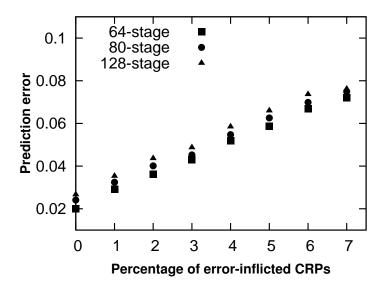

| 5.5  | Performance of SVM attacks on Current-based PUFs with error-inflicted CRPs                                                                                                                                                                     |

| 5.6  | Performance of ES attacks on Current-based PUFs with error-inflicted CRPs                                                                                                                                                                      |

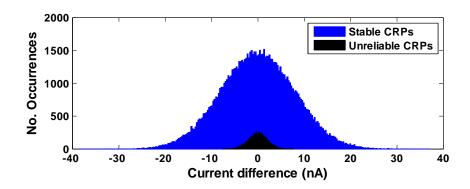

| 5.7  | Current-difference distributions of error-free and error-prone CRPs                                                                                                                                                                            |

| 5.8  | Percentage of unstable CRPs from circuit simulations whose current difference is lower than 5 nA                                                                                                                                               |

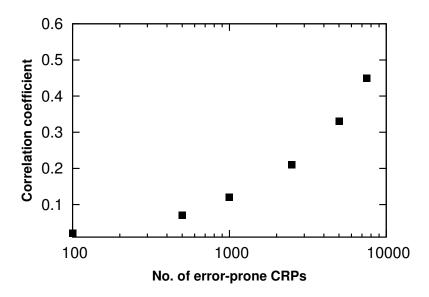

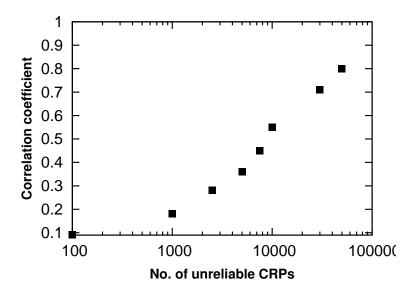

| 5.9  | Correlation coefficient versus the number of unstable CRPs used in hybrid attacks                                                                                                                                                              |

| 5.10 | Performance of hybrid attacks with 7% error-inflicted CRPs                                                                                                                                                                                     |

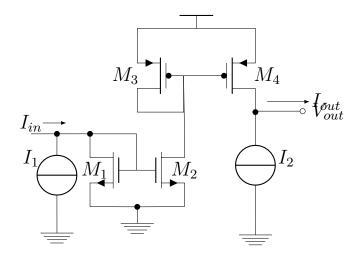

| 5.11 | Non-linear current mirror [91]                                                                                                                                                                                                                 |

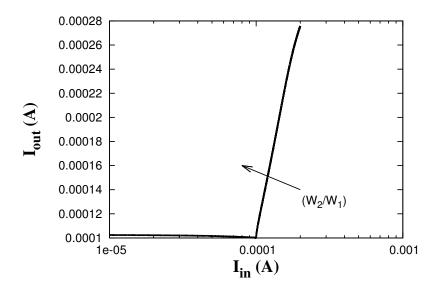

| 5.12 | Non-linear transfer characteristic of the current mirror                                                                                                                                                                                                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

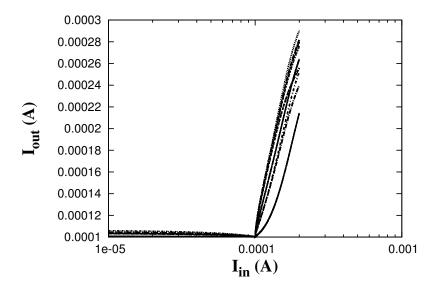

| 5.13 | Impact of process variations on the transfer characteristic of Non-linear current mirror                                                                                                                                                                 |

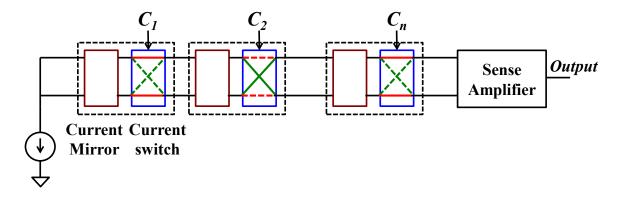

| 5.14 | Proposed PUF Architecture. $I_a$ and $I_b$ are the output currents that are compared to generate the response bit                                                                                                                                        |

| 5.15 | (a) Current switch, (b) Sense amplifier. The input currents to the current switch are $I_{in}^{top}$ , $I_{in}^{bot}$ and the output currents are $I_{out}^{top}$ and $I_{out}^{bot}$ . $C_{ib}$ is the inverted challenge bit $(C_{ib} = \sim C_i)$ 116 |

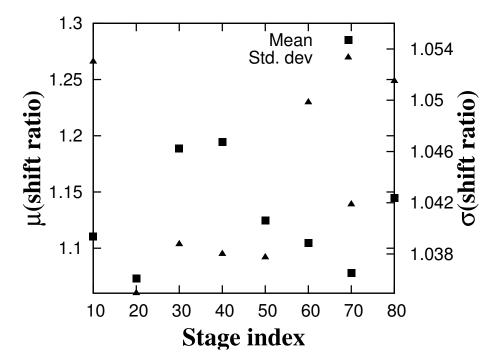

| 5.16 | Mean and standard deviation of current shift ratios in an 80-stage nlcPUF circuit                                                                                                                                                                        |

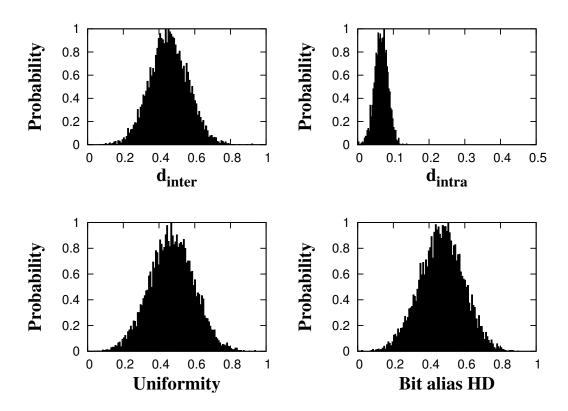

| 5.17 | PUF Performance metrics distributions. (a) Inter-class HD (b) Intra-class HD (c) Uniformity and (d) Bit-aliasing probability 118                                                                                                                         |

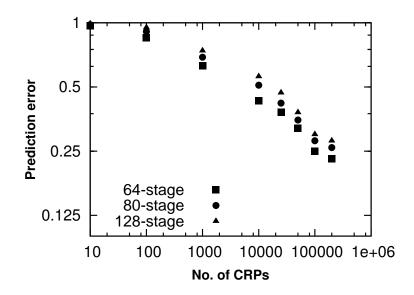

| 5.18 | Prediction errors from SVM attacks for 64, 80 and 128 stage nlcPUF                                                                                                                                                                                       |

| 5.19 | Prediction errors from ES attacks for 64, 80 and 128 stage nlcPUF                                                                                                                                                                                        |

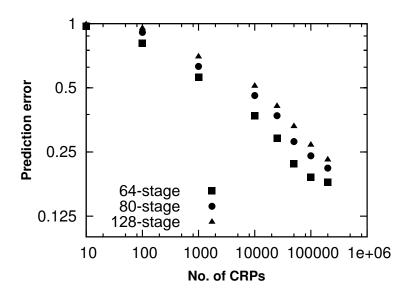

| 5.20 | Impact of error-inflicted CRPs on SVM prediction rates for 64, 80 and 128 stage nlcPUF                                                                                                                                                                   |

| 5.21 | Impact of error-inflicted CRPs on ES prediction rates for 64, 80 and 128 stage nlcPUF121                                                                                                                                                                 |

| 5.22 | Prediction errors from hybrid attacks for 64, 80 and 128 stage  Current-based PUFs                                                                                                                                                                       |

| 6.1  | Forbidden pitches in 45nm and 32nm nodes                                                                                                                                                                                                                 |

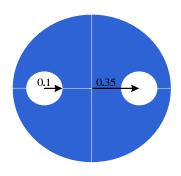

| 6.2  | Dipole light source                                                                                                                                                                                                                                      |

| 6.3  | Simulation methodology to compute uniqueness                                                                                                                                                                                                             |

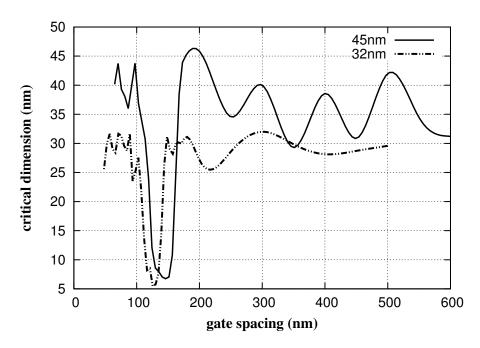

| 6.4  | Sensitivity of CD to gate spacing                                                                                                                                                                                                                        |

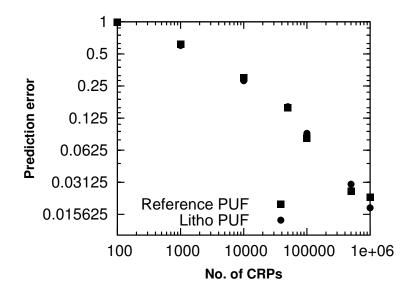

| 6.5  | Prediction errors from SVM attacks on Litho-aware arbiter PUFs 137                                                                                                                                                                                       |

| 6.6  | Prediction errors from SVM attacks on Litho-aware current-based PUFs                                                                                                                                                                                     |

| 6.7  | PHAP Architecture                                                                                                   |

|------|---------------------------------------------------------------------------------------------------------------------|

| 6.8  | Timing diagram for PHAP                                                                                             |

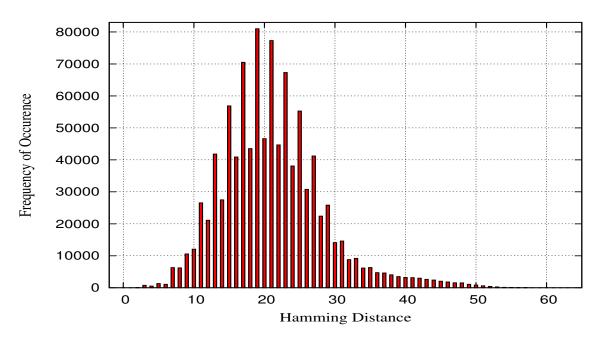

| 6.9  | Hamming Distance distribution of the PUF block                                                                      |

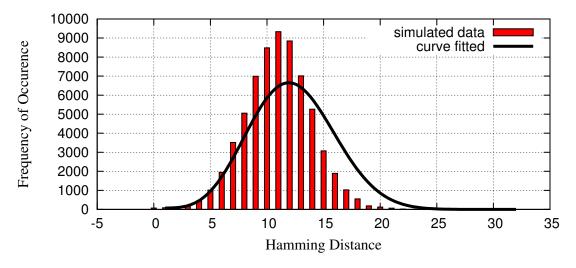

| 6.10 | Hamming distance distribution of the LFSR output                                                                    |

| 6.11 | Hamming distance distribution for various session passwords experiment                                              |

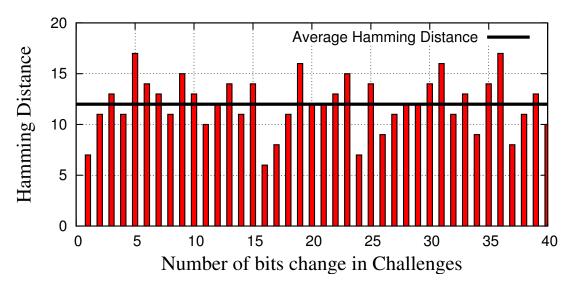

| 6.12 | Hamming distance vs $R_{padded}$ varying from 1 to 40 bits                                                          |

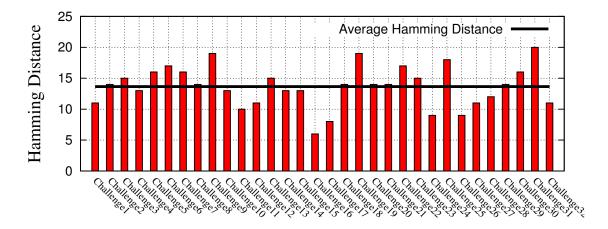

| 6.13 | Hamming distance vs $R_{padded}$ varying by 1 bit                                                                   |

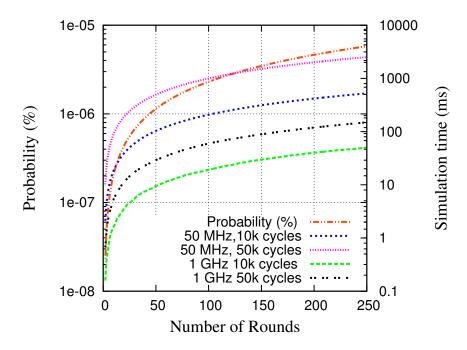

| 6.14 | Simulation time and Probability plot                                                                                |

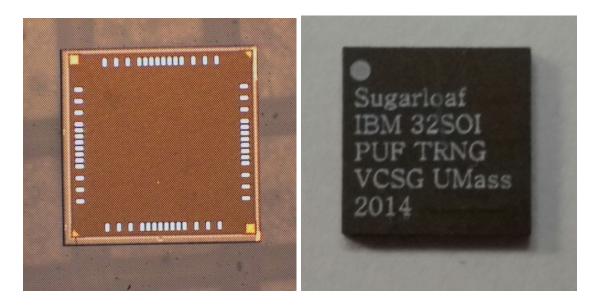

| 7.1  | Unpackaged and Packaged sugarloaf die photos                                                                        |

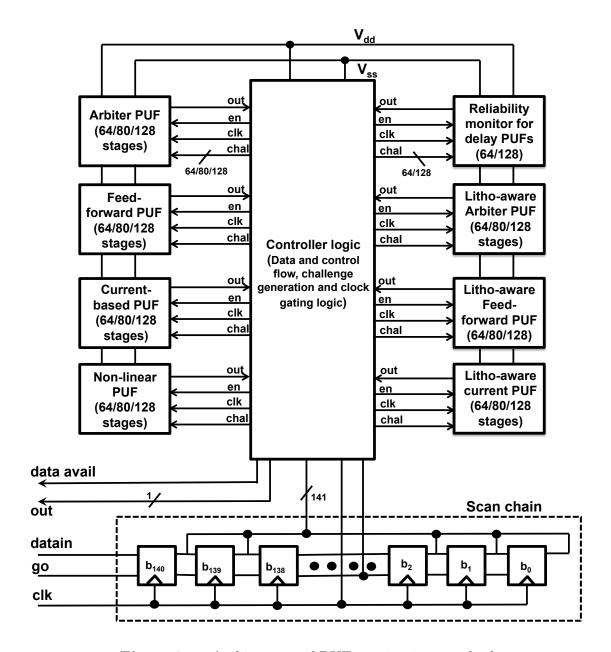

| 7.2  | Architecture of PUF portion in sugarloaf                                                                            |

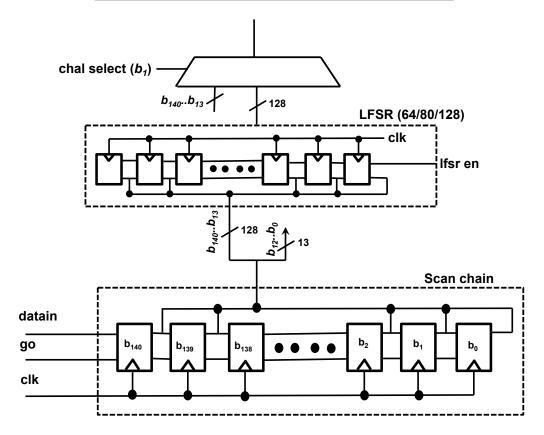

| 7.3  | Challenge generation for PUF circuits in sugarloaf                                                                  |

| 7.4  | Layout snapshot of the PUF banks with controller logic                                                              |

| 7.5  | Post-silicon validation setup                                                                                       |

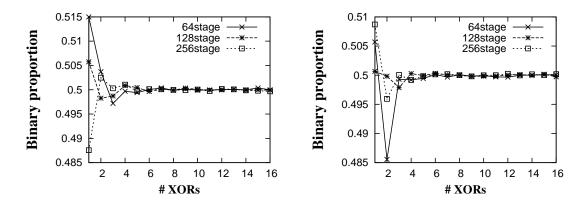

| 8.1  | Proportion of 0's and 1's in XOR arbiter PUFs for Mersenne Twister based challenges                                 |

| 8.2  | NIST scores for XOR arbiter PUFs for Mersenne Twister based challenges                                              |

| 8.3  | Proportion of 0's and 1's in XOR arbiter PUFs for Halton(left) and Sobol(right) based generators with scrambling    |

| 8.4  | NIST sum of scores for XOR arbiter PUFs for Halton(left) and Sobol(right) based generators with scrambling          |

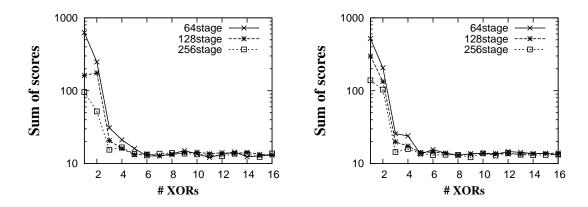

| 8.5  | Proportion of 0's and 1's in XOR arbiter PUFs for Halton(left) and Sobol(right) based generators without scrambling |

| 8.6  | NIST sum of scores for XOR arbiter PUFs for Halton(left) and Sobol(right) based generators without scrambling       |

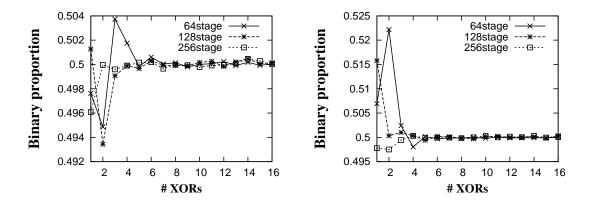

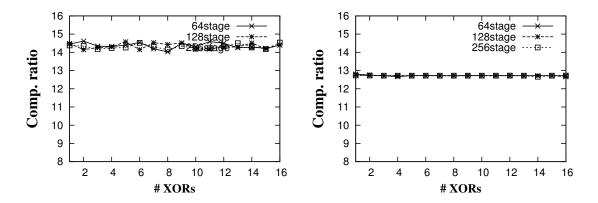

| 8.7 | Compression ratios for MT generator based XOR arbiter PUFs using 7z(left) and Advcomp(right) algorithms170                                      |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|

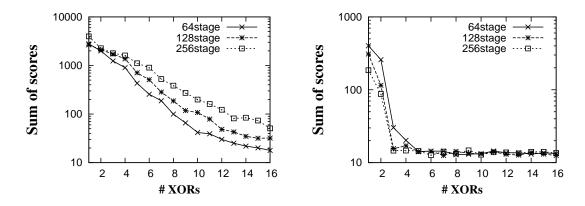

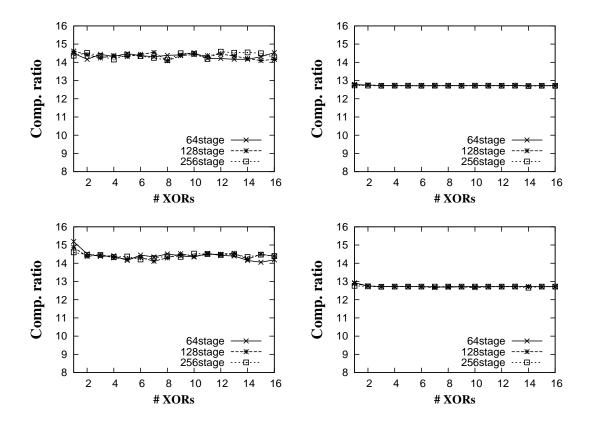

| 8.8 | Compression ratios for scrambled halton(top) and sobol(bottom) generators based XOR arbiter PUFs using 7z(left) and Advcomp(right) algorithms   |

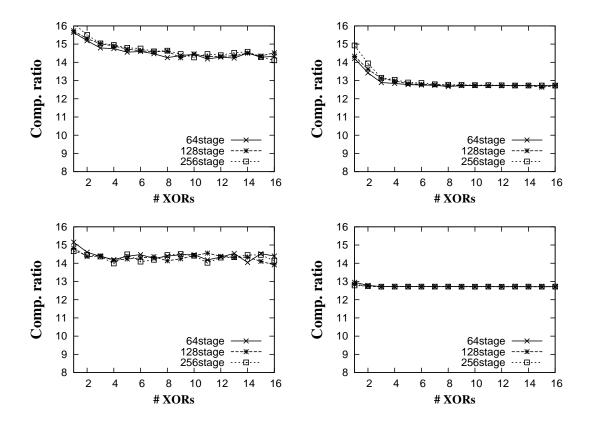

| 8.9 | Compression ratios for unscrambled halton(top) and sobol(bottom) generators based XOR arbiter PUFs using 7z(left) and Advcomp(right) algorithms |

## CHAPTER 1

#### INTRODUCTION

# 1.1 Hardware Security and Vulnerabilities

The role of embedded systems in day-to-day life has improved significantly in the last decade and this trend will likely continue in the forthcoming days. Some major embedded systems include smartphones, tablets, payment systems, smart cards and medical devices. The trend of *ubiquitous computing* has therefore seen a great scope of improvement and has led to an era of *Internet of Things (IoT)*, where the devices have communication ability in addition to computation power. However, because of their ubiquitous nature, they also bring out security and privacy issues as they pose an ideal target for attackers. In particular, protection of sensitive data stored on the devices has brought forth an alarming issue and demands cryptographic protection.

Majority of the embedded systems pose tight constraints on area and energy because of their low cost. So, the trend towards lightweight cryptographic primitives is becoming extremely popular in the design market. Most of the primitives based on classical cryptography are based on the concept of a secret binary key embedded on the device. However, they pose some serious security vulnerabilities especially against physical attacks (invasive, non-invasive and side-channels) and software attacks. The fact that the key has to be stored in a non-volatile memory further aggravates the problem.

As explained above, cryptographic hardware blocks in safety and security critical systems increasingly constitute a target for attackers. Fault-based attacks [6, 10, 12] aim at determining the secret key or other protected data by actively manipulating

the system during operation and thus compromising the system integrity. Such approaches fall into the category of active side-channel cryptanalysis, in order to distinguish them from passive techniques that derive the secret information from measured operational parameters such as power consumption or timing [40,63]. A number of fault-based attacks have been proposed in the recent years and were successful in breaking state-of-the-art ciphers using one or a small number of faults [29,34,37,56]. Consequently, current and emerging cryptographic circuits must be capable of withstanding such attacks. In order to design appropriate countermeasures, it is important to understand the attacks, their limits, and the criteria for their success.

The attacks from the latest generation mentioned above require a very high precision on the fault injection. One part of this requirement is *spatial resolution*: the fault must show up in the desired locations (memory cells, registers or logic gates) while not affecting other locations. The second relevant property is the *temporal resolution*: the fault must be present in a given point of time (e. g., after the end of a specific round of encryption) and absent at other times. For example, the one-fault-injection-attack on AES-128 [56] identifies a set of secret key candidates which is sufficiently small for practical brute-force search under the condition that the fault affects one or multiple bits of one byte of the cipher state after round 8. If multiple bytes of this state or bytes during rounds other than 8 are affected by the fault injection, the mathematical analysis will loose validity and the correct secret key will no longer be found.

The physical techniques to inject faults can be broadly divided into low-cost, low-precision and high-cost, high-precision approaches [6]. Here, the term "cost" refers to the necessary equipment as well as to the qualification of its operator. Low-cost, low-precision fault-injection methods include operating the device under a reduced power supply (underfeeding), tampering with the clock signal (introducing a glitch), overheating the device, irradiating it with X-rays, ion beams, white or ultraviolet

light and may or may not involve de-packaging the circuit in order to expose the active areas of its transistor. These techniques typically do not achieve good spatial and temporal resolutions at the same time. They are suited for attacks such as manipulating the round counter of a cipher in order to reduce the number of rounds applied during encryption, or manipulating the program counter of a microprocessor in order to jump over certain instructions. Methods with high or very high spatial and temporal resolution include laser irradiation, precise application of electromagnetic pulses<sup>1</sup>, and the use of focused-ion beam.

In this work, we suggest two techniques for fault injection that do not require elaborate equipment while providing sufficient precision for attacks of the latest generation. The first technique is based on careful selection of the parameters under which the circuit is operated: power supply voltage  $V_{\rm dd}$  and temperature T. We search for  $V_{\rm dd}/T$  combinations which lead to injection of faults that satisfy the requirements for the cryptanalysis. In contrast, earlier approaches produced faults of low precision and predictability and were not suited for latest-generation attacks. We demonstrate this technique, called V/T fault injection, using a complex two-stage attack on two recent lightweight block ciphers.

The second fault-injection technique employs hardware Trojans to facilitate fault injection. Hardware Trojans [87] are malicious modifications of a circuit unintended by its designer; they can be applied by the untrusted manufacturer or a third-party intellectual property block provider. Here, we introduce a new class of hardware Trojans, called Manufacturing Process LEvel, or MAPLE Trojans. These Trojans are applied to individual logic gates of the circuit and are activated non-deterministically, with a probability (called (triggering factor) being sufficiently high to conduct fault-

<sup>&</sup>lt;sup>1</sup>EM techniques are quoted in [6] under the low-cost category. However, recent results suggest that they can be used for high-precision attacks [93].

based cryptanalysis, but sufficiently low to make their detection extremely challenging or even impossible in practice.

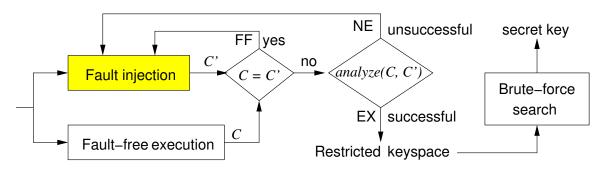

We evaluate both fault-injection methods using the same settings and compare them with each other and with previously introduced fault-injection techniques. In particular, we demonstrate that both methods are applicable for successful fault-based cryptanalysis of state-of-the-art ciphers. We discuss in-depth the effectiveness of known countermeasures against the proposed fault-injection methods and outline the key differences to earlier threats. In particular, we show that the post-manufacturing detection methods that traditionally have been considered as a remedy against hardware Trojans are of little use against MAPLE Trojans. While we have no indication of actual circuits having been manipulated in this way, the theoretical existence of the threats outlined by our work suggests the need to re-think protection of safety-and security-relevant hardware components.

The vulnerabilities of existing cryptographic hardware blocks have been one of the major driving forces behind the search of novel, efficient and secure cryptographic primitives. Moreover, the ever-shrinking transistor sizes has resulted in tiny embedded devices with computing and networking power. Some examples include radio-frequency identifiers, smart cards, PDAs, etc. As these devices store and process sensitive data, they demand efficient and lightweight cryptographic protection. The traditional cryptographic implementations are based on a digital secret key stored in the device. As some of these embedded devices are extremely resource constrained, storing a secret key in a non-volatile memory might be extremely expensive. Motivated by these drawbacks, Physically Unclonable Functions (PUFs) have been proposed in the literature as an efficient way of generating unique and secret identifiers from the complex and unpredictable nature of silicon.

# 1.2 Exploiting Process Variations in Security

The semiconductor industry has been continuously driven by Moore's law, which states that the number of transistors in an integrated circuit doubles approximately every two years. The trend is shown in Figure 1.1. Technology scaling has been the dominant force behind Moore's law. However, aggressive technology scaling is also impacted by variations from process, voltage, temperature and aging to certain extent, also known as PVTA variations. Significant effort is spent by designers to combat the variations, especially in complex systems consisting of billions of transistors. Apart from these variations, the semiconductor industry is also facing non-certainties in the form of scaling limits. It has been predicted that the technology scaling can continue up to around 7nm, below which the number of transistors in the channel region will not be sufficient to generate enough drain current. Researchers are exploring various post-CMOS devices like nano-wires, graphene, carbon nanotubes, etc.

Managing and mitigating process variations in integrated circuits have been extensively explored, especially in sub-nm design era. Random dopant fluctuation (RDF) is one of the major sources of process variations. RDF results in a variation in the number of dopant atoms in the channel region. This in turn changes the threshold voltage of a transistor. Due to the impact of process variations, logic gates suffer from delay variations. Process variations also impact the performance of memory elements such as Static Random Access Memory (SRAM). As the amount of process variations increase with reducing transistor sizes, significant effort is spent on managing them. However, there are also possibilities to utilize increasing process variations in a constructive fashion. Such techniques are gaining popularity in semiconductor industry, where the process variations are used to generate unique signatures in integrated circuits [66,80]. These circuits are often referred to as Physically Unclonable Functions (PUFs). The concept of PUFs were first introduced in [86].

Figure 1.1. Moore's law [68]

A PUF is a partially disordered system that maps a set of external inputs also known as challenges C to a response R. A challenge associated with its response is known as a challenge-response pair (CRP). In silicon PUFs, the mapping function is decided by process variations arising during the manufacturing process. The manufacturing process is extremely complicated especially in sub-45 nm design space and is hard to control even by the manufacturer. This ensures that a manufacturer cannot produce an identical tuple of ICs with the same layout. This behavior is exploited in the design of PUF circuits. PUFs can be employed in several security related applications and the scope is often limited by the number of responses that can be

generated. PUFs can be broadly classified into "strong" and "weak" PUFs based on the number of independent responses that it can generate. Please note that the terms "strong" and "weak" do not have any reference to the security level of a PUF. A strong PUF can produce a large number of responses  $(R_i)$  for different inputs  $C_i$  and can be used in security protocols, key establishment and device authentication. A classical example for a strong PUF is an arbiter PUF [86]. A weak PUF, on the other hand, has a reduced response space and produce only a single response in the worst case scenario. So, the response(s) must be kept secure from the external world and must never be shared with a third party. The weak PUFs can be used in classical crypto-systems for deriving the secret key. One of the typical examples for a weak PUF is an SRAM PUF [30,31].

As PUFs find strong potential for deployment in security systems, they must satisfy some properties. Some of the security properties of a strong PUF as described in [78] are: (i) Cloning a strong PUF is highly impossible. (ii) Entire CRP collection by an attacker within a short amount of time is impossible. (iii) A subset of CRPs should not leak any information to predict the response of a challenge outside the subset. These properties have been exploited in the literature for the development of various security protocols based on PUFs. Some examples include device identification [86], key exchange [73], oblivious transfer [76] etc. The commercial applications employing PUF circuits require that any two responses from two different PUF instances of the same type should have a significant difference. This property of PUFs is referred to as uniqueness. To ensure stable authentication, PUFs are expected to produce the same response for a challenge under any operating condition, which is measured in terms of reliability. Finally, a PUF should be unpredictable such that an attacker possessing a subset of CRP pairs should be unable to predict the response for a challenge outside that subset. More details on performance metrics of PUF circuits can be found in chapter 2.

Although PUFs seem to be a promising alternative to classical cryptography, they must overcome some concerns to be trusted fully secure. One such concern is the robustness of PUF circuits. A PUF is expected to produce the same response whenever queried with a particular challenge. However, due to the presence of on-chip substrate noise, temperature and voltage fluctuations, some of the responses become highly unreliable. Several circuit and system level schemes to improve the reliability of PUF circuits have been proposed in the literature. Prominent examples include error-correction schemes [92], feedback-supply control [45, 49, 89], helper data [14], fuzzy extractors [19], etc. Another major concern for PUFs is their vulnerability to modeling attacks. Moreover, unreliable challenge-response pairs can also be used to improve the performance of modeling attacks. The unreliable challenge-response pairs can leak some side-channel information to extract more data-dependent information from PUF circuits. So, unreliability and security vulnerabilities of PUF circuits are closely related to each other and must be addressed in order to consider them fully secure.

In this work, we study the vulnerabilities of some popular "strong" PUF architectures to various attacks using simulated and silicon data. The PUF circuits were implemented in IBM 32nm Silicon-on-Insulator (SOI) technology and validated using post-silicon measurements. In particular, we study the vulnerabilities of PUF circuits to modeling attacks using Machine Learning (ML) algorithms. The ML algorithms construct a model based on the challenge-response training set. The performance of modeling attacks depends on the robustness of the challenge-response pairs. If there are some unreliable challenge-response pairs in the training set, the learning phase of the ML algorithms is severely impacted and limited prediction accuracies are achieved. To that extent, we propose a hybrid attack that exploits the data-dependent information present in unreliable challenge-response pair and uses it constructively to push the prediction accuracies achieved by ML algorithms. Motivated by the vulnera-

bilities of existing PUF circuits, we also present a modeling attack resistant PUF architecture using non-linear current mirrors. The post-silicon validation results of the proposed non-linear PUF architecture are also presented. Finally, a statistical benchmark suite to evaluate and enable fine-grained security assessments of PUF architectures is presented.

# 1.3 Contributions and Organization

The major contributions of this dissertation include:

- 1. Techniques to extract secret keys from cryptographic hardware through the use of hardware Trojans and precise voltage and temperature manipulation.

- 2. Techniques to attack delay-based PUF designs using modeling attacks.

- 3. Methodologies for exploiting side-channel information to improve the performance of modeling attacks.

- 4. Design and post-silicon validation of a modeling attack resistant PUF design in 32nm SOI process.

- 5. Design strategies to improve the performance of PUF circuits.

- 6. Statistical benchmark suite for analysis of PUF architectures.

The rest of this dissertation is organized as follows. In chapter 2, some background information on various sources of process variations is presented. We also discuss the different performance metrics used to characterize PUF circuits. In chapter 3, we present the different techniques to extract the secret key from cryptographic blocks. Different techniques include voltage and temperature manipulation and hardware Trojan insertion. We also present the performance of fault-injection techniques by using them to extract the secret key from state-of-the-art ciphers. Some of the

countermeasures against fault-injection attacks are also presented. Chapter 4 focuses on modeling and hybrid attacks on popular delay-based PUF designs. Simulation and silicon data from PUF circuits are used to validate the performance of modeling and hybrid attacks. In chapter 5, we present the design and post-silicon measurements of a novel modeling attack resistant PUF design based on non-linear current mirrors. The performance of the proposed PUF is compared against the best-in-class current-based PUF architecture and the results are presented. Chapter 6 discuss the different design strategies to improve the performance metrics of PUF circuits. The different strategies include fabrication-aware design of PUF circuits and a PUF based protocol to improve the authentication capabilities of security systems. In chapter 7, we present the architecture of the 32nm test chip known as sugarloaf and the post-silicon validation setup. Finally, chapter 8 discusses the statistical benchmark suite and data compressibility analysis of PUFs.

## CHAPTER 2

#### BACKGROUND

Some background information related to PUFs are presented in this chapter. Along with some background information, the methodology to compute the performance metrics of a PUF circuit are also presented. The methodology presented is the basis for all performance metrics computation described in the document.

#### 2.1 Sources of CMOS Process Variations

The sources of process variations in ICs are summarized in this section. Some of the sources of variations are shown in Figure 2.1. From the perspective of PUF circuits, the sources of variations can be either desirable or undesirable. The desirable source of variations refers to process manufacturing variations (PMV) as identified in [39]. The environmental variations and aging are undesirable for PUF circuits.

## 2.1.1 Manufacturing Process and Variations

The IC manufacturing process consists of several steps [57]: patterning, etching, doping, film deposition and planarization. A monochromatic light source is focused via a set of optical lenses on a mask containing the desired pattern to be printed onto the silicon wafer. After the wafer is exposed, some parts are etched out through a chemical process and then the surface is planarized using Chemical Mechanical Polishing (CMP) [57]. This process is repeated several times over for printing the patterns. Moreover, diffusion/ion implantation is used to dope certain regions of the wafer. Each of these steps cannot be repeated faithfully from wafer to wafer

# Manufacturing process variations Fluctuations in transistor parameters Variations in device dimensions Aging effects Aging effects

Figure 2.1. Sources of variations in ICs

or even from die to die within the same wafer. Owing to lens material limitations, the wavelength of the light source has not scaled down below 193nm, though the transistor dimensions have scaled down to 22nm. This is also a significant contributor to variations in structures printed on the wafer. Variations occur due to imperfections in:

- Light source exposure intensity (dose)

- Lens system aberration

Limited resolution in IC fabrication

- Mask

- Etching process Line Edge Roughness (LER)

- Doping process

- CMP process

- Alignment defocus

- Optical Proximity Effects

These imperfections result in variations in physical parameters that lead to variations in electrical parameters like threshold voltage and current. This in turn affects timing, power consumption, etc. These variations can be random or systematic [57]. Systematic variations should be suppressed as they affect the uniqueness of PUFs. On the other hand, random variations are unpredictable and improve the performance of a PUF.

### 2.1.1.1 Systematic Variations

Systematic component of process variations includes variations in lithography system, nature of layout and CMP [11]. By performing a detailed analysis of the layout, the systematic sources of variations can be predicted in advance and accounted in design step. If the layout is not available for analysis, the variations can be assigned statistically [11].

#### 2.1.1.2 Random Variations

Random variations refer to non-deterministic sources of variations. Some of the random variations include random dopant fluctuations (RDF), line edge roughness (LER) and oxide thickness variations. The random variations are often modeled using random variables for design and analysis purposes.

### 2.1.2 Environmental Variations and Aging

Environmental variations are detrimental to PUF circuits. Some of the common environmental sources of variations include power supply noise, temperature fluctuations and external noise. These variations must be minimized to improve the reliability of PUF circuits.

Aging is a slow process and it reduces the frequency of operation of circuits by slowing them down. Circuits are also subjected to increased power consumption and functional errors due to aging [90].

## 2.2 PUF Terminologies and Performance Metrics

The terminologies and performance metrics used in the field to evaluate PUF devices are briefly summarized in the following sections.

## 2.2.1 Challenge-Response pairs (CRP)

As the name suggests, PUF circuits can be envisioned as a function mapping a set of inputs to outputs. However, as identified in [58], PUF circuits do not implement a true function as they can produce different outputs for an input under different operating conditions. The inputs to a PUF circuit are known as *challenges* and outputs are referred to as *responses*. A challenge associated with its corresponding response is known as a *Challenge-Response pair (CRP)*. In an application scenario, responses of a PUF circuit are collected and stored in a database. This process is generally known as *enrollment*. Under *verification* or *authentication* process, the PUF circuit is queried with a challenge from the database. The response is then compared against the one stored in the database. If the responses match, the device is authenticated.

#### 2.2.2 Performance Metrics

There are different important metrics used to analyze a PUF circuit, namely uniqueness, reliability, unpredictability, uniformity and bit-aliasing probability [60]. The performance metrics are defined in different measurement dimensions as shown in Figure 2.2. The different measurement dimensions are time, device and space.

Figure 2.2. PUF Performance metrics and dimensions

Uniqueness and bit-aliasing probability are measured across different devices. Reliability is measured across time and uniformity and unpredictability are measured across space.

### 2.2.2.1 Uniqueness

PUF devices are primarily used to generate unique signatures for device authentication. In this application, it is desirable to have a large difference between responses from any two PUF instances. Here, the two PUF instances may be from the same wafer or different wafers. A typical measure used to analyze uniqueness is known as *inter-distance* and is given by [39,60]:

$$d_{inter}(C) = \frac{2}{k(k-1)} \sum_{i=1}^{i=k-1} \sum_{j=i+1}^{j=k} \frac{HD(R_i, R_j)}{m} \times 100\%.$$

(2.1)

In equation 2.1,  $HD(R_i, R_j)$  is the Hamming distance between two responses  $R_i$  and  $R_j$  of m bits long for a particular challenge C and k is the number of PUF

instances under consideration. The desired inter-distance is 50%. By carefully looking at equation 2.1, one can correspond the inter-distance  $d_{inter}(C)$  to the mean of the Hamming distance distribution obtained over k chips for a challenge C. It is also useful to obtain the standard deviation of Hamming distance distribution given by  $\sigma_{inter}(C)$ , which measures the extent of deviation in Hamming distance from the desired inter-distance. Lower  $\sigma_{inter}(C)$  is preferable for PUF design. As uniqueness is measured across devices, it is denoted in the device axis in Figure 2.2.

While designing a PUF circuit, inter-distance is often measured through circuit simulations. A common practice is to perform Monte Carlo simulations over a large population of PUF instances. Though there is no single concrete number for the number of PUF instances to be considered for simulation purposes, it is safe to assume around 1000 samples to obtain a good estimate of uniqueness. In simulations, care must be taken to efficiently model various sources of manufacturing variations in CMOS circuits, as they directly translate into uniqueness. During the simulations, manufacturing variations are modeled using a gaussian distribution. In such cases, mean and standard deviation of the gaussian distribution under consideration must correspond to either inter-die or inter-wafer variations' statistics.

## 2.2.2.2 Reliability

A challenge applied to a PUF operating on an integrated circuit will not necessarily produce the same response under different operating conditions as the circuit is subject to environmental variations. The robustness of PUF's responses is measured in terms of reliability. Reliability of a PUF refers to its ability to produce the same response for a particular challenge under varying operating conditions. Reliability can be measured by looking at the average number of flipped bits in responses for the same challenge under different operating conditions. A common measure of reliability is *intra-distance* given by [24,39,60]:

$$d_{intra}(C) = \frac{1}{s} \sum_{j=1}^{s} \frac{\text{HD}(R_i, R'_{i,j})}{m} \times 100\%.$$

(2.2)

In equation 2.2,  $R_i$  is the response of a PUF to challenge C under nominal conditions, s is the number of samples of response  $R_i$  obtained at different operating conditions,  $R'_{i,j}$  corresponds to  $j^{\text{th}}$  sample of response  $R_i$  for challenge C and m is the number of bits in the response. Intra-distance is expected to be 0% for ideal PUFs, which corresponds to 100% reliability. The terms intra-distance  $(d_{intra})$  and reliability have been used interchangeably further in this chapter. Given  $d_{intra}$ , reliability can always be computed  $(100 - d_{intra}(\%))$ .

### 2.2.2.3 Unpredictability