## University of Massachusetts Amherst

# ScholarWorks@UMass Amherst

**Masters Theses**

Dissertations and Theses

July 2015

# **Function Verification of Combinational Arithmetic Circuits**

Duo Liu University of Massachusetts Amherst

Follow this and additional works at: https://scholarworks.umass.edu/masters\_theses\_2

Part of the Digital Circuits Commons, Other Computer Engineering Commons, and the VLSI and Circuits, Embedded and Hardware Systems Commons

#### **Recommended Citation**

Liu, Duo, "Function Verification of Combinational Arithmetic Circuits" (2015). *Masters Theses*. 235. https://scholarworks.umass.edu/masters\_theses\_2/235

This Open Access Thesis is brought to you for free and open access by the Dissertations and Theses at ScholarWorks@UMass Amherst. It has been accepted for inclusion in Masters Theses by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

# FUNCTION VERIFICATION OF COMBINATIONAL ARITHMETIC CIRCUITS

A Thesis Presented

by

DUO LIU

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN ELECTRICAL AND COMPUTER ENGINEERING

May 2015

Electrical and Computer Engineering

© Copyright by Duo Liu 2015

All Rights Reserved

# FUNCTION VERIFICATION OF COMBINATIONAL ARITHMETIC CIRCUITS

A Thesis Presented

by

DUO LIU

| Approved as to style and content by: |   |

|--------------------------------------|---|

| Maciej Ciesielski, Chair             | _ |

| Sandip Kundu, Member                 |   |

| Eric Polizzi Member                  | _ |

Christopher V. Hollot, Department Head Electrical and Computer Engineering

#### **ACKNOWLEDGMENTS**

I would like to thank Professor. Ciesielski who gives me the opportunity to dedicate myself into this important research and guides me throughout my study in UMASS Amherst. I also would like to thank Walter for developing very useful functions that I used in my software. Special thanks to Cunxi who wrote the benchmark generator BenGen. I have used unsigned multipliers generated by BenGen in the experiments. Thanks to Arun and Sudarshan for answering my questions and friends outside the VLSI CAD lab who help me with my research. Thank you my dear parents, your selfless supports make me understand the meaning of love.

#### **ABSTRACT**

# FUNCTION VERIFICATION OF COMBINATIONAL ARITHMETIC CIRCUIT

#### MAY 2015

#### **DUO LIU**

B.S., JIANGNAN UNIVERSITY, WUXI, JIANGSU, CHINA

M.S.E.C.E., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Maciej Ciesielski

Hardware design verification is the most challenging part in overall hardware design process. It is because design size and complexity are growing very fast while the requirement for performance is ever higher. Conventional simulation-based verification method cannot keep up with the rapid increase in the design size, since it is impossible to exhaustively test all input vectors of a complex design. An important part of hardware verification is combinational arithmetic circuit verification. It draws a lot of attention because flattening the design into bit-level, known as the bit-blasting problem, hinders the efficiency of many current formal techniques. The goal of this thesis is to introduce a robust and efficient formal verification method for combinational integer arithmetic circuit based on an in-depth analysis of recent advances in computer algebra. The method proposed here solves the verification problem at bit level, while avoiding bit-blasting problem. It also avoids the expensive Groebner basis computation, typically employed by

symbolic computer algebra methods.

The proposed method verifies the gate-level implementation of the design by representing the design components (logic gates and arithmetic modules) by polynomials in  $\mathbb{Z}_{2^n}$ . It then transforms the polynomial representing the output bits (called "output signature") into a unique polynomial in input signals (called "input signature") using gate-level information of the design. The computed input signature is then compared with the reference input signature (golden model) to determine whether the circuit behaves as anticipated. If the reference input signature is not given, our method can be used to compute (or extract) the arithmetic function of the design by computing its input signature. Additional tools, based on canonical word-level design representations (such as TED or BMD) can be used to determine the function of the computed input signature represents. We demonstrate the applicability of the proposed method to arithmetic circuit verification on a large number of designs.

# TABLE OF CONTENTS

|                                                                  | Page |

|------------------------------------------------------------------|------|

| ACKNOWLEDGMENTS                                                  | iv   |

| ABSTRACT                                                         | v    |

| LIST OF TABLES.                                                  | ix   |

| LIST OF FIGURES                                                  | x    |

| LIST OF ALGORITHMS                                               | xii  |

| CHAPTER                                                          |      |

| 1. INTRODUCTION                                                  | 1    |

| 1.1 Verification and Its Importance.                             | 1    |

| 1.2 Simulation-Based Verification                                |      |

|                                                                  |      |

| 1.3.1 Equivalence Checking.                                      |      |

| 1.3.2 Model Checking.                                            |      |

| 1.3.3 Symbolic Simulation                                        |      |

| 1.3.4 Theorem Proving                                            |      |

| 1.3.6 *BMD: An Efficient Representation for Word-Level Functions |      |

| 1.3.7 TED: World-Level Compact Canonical Representation          |      |

| 1.4 Inspiration for Current Work                                 | 19   |

| 2. RELATED WORK                                                  | 21   |

| 2.1 Theoretical Background                                       | 21   |

| 2.2 Previous Work                                                |      |

| 3. PROPOSED WORK                                                 | 29   |

| 3.1 Motivation                                                   | 29   |

| 3.2 Implementation.                                              | 30   |

| 4. IMPLEMENTATIONS AND IMPROVEMENTS OF VARIABLE                   |     |

|-------------------------------------------------------------------|-----|

| SUBSTITUTION METHODS                                              | 40  |

|                                                                   | 4.0 |

| 4.1 Preliminary Experiments and Result Analysis                   |     |

| 4.2 Experiments on Improved Algorithm and Result Analysis         |     |

| 4.3 Experiments on Further Improved Algorithm and Result Analysis |     |

| 4.4 Experiments with Improved Algorithm and Result Analysis       | 53  |

| 5. THEOREM                                                        | 61  |

| 6. LEVELIZATION ALGORITHMS                                        | 63  |

| 6.1 Breadth-First Search (BFS) Levelization Algorithm             | 64  |

| 6.2 Modified Levelization Algorithm based on Dijkstra's Algorithm | 71  |

| 6.3 More Experiments and Comparisons with Other Tools             | 75  |

| 6.3.1 Experiments on non-synthesized circuits                     | 75  |

| 6.3.2 Experiments on synthesized circuits                         |     |

| 7. CONCLUSOINS AND FUTURE WORK                                    | 81  |

| 8. CONTRIBUTIONS                                                  | 83  |

| APPENDIX: KEY FUNCTION INPLEMENTATIONS AND SOFTWARE               |     |

| INTERFACE                                                         | 85  |

| RIRLIOGRAPHY                                                      | 94  |

# LIST OF TABLES

| Table                                                                          | Page |

|--------------------------------------------------------------------------------|------|

| 6.1: CPU time comparison of circuits before and after levelization             | 67   |

| 6.2: CPU time comparison of circuits before and after levelization             | 70   |

| 6.3: Example of <i>Dijk_levelization</i> procedure                             | 73   |

| 6.4: CPU time comparison of circuits before and after <i>Dijk_levelization</i> | 74   |

| 6.5: Verification time for signed multipliers.                                 | 75   |

| 6.6: Verification time for unsigned multipliers                                | 76   |

| 6.7: Unsigned multipliers verification CPU time comparison with SMT            | 77   |

| 6.8: Levelization and verification of synthesized unsigned multipliers         | 78   |

| 6.9: Levelization and verification of synthesized signed multipliers           | 79   |

| 6.10: Unsigned multipliers verification CPU time comparison with SMT           | 80   |

# LIST OF FIGURES

| Figure                                                                               | Page |

|--------------------------------------------------------------------------------------|------|

| 1.1: VLSI Design Flow                                                                | 2    |

| 1.2: Simulation-Based Verification.                                                  | 3    |

| 1.3: Model checking example                                                          | 7    |

| 1.4: An example of conventional simulation and symbolic simulations                  | 8    |

| 1.5: Another example of symbolic simulation                                          | 9    |

| 1.6: An example of *BMD representation of function "8-20z+2y+4yz+                    | 15   |

| 1.7: An example of BMD for 2-bit unsigned multiplier                                 | 16   |

| 3.1: An example of gate-level implementation of a 2-bit signed multiplier            | 33   |

| 3.2: An example of keeping variable Boolean                                          | 37   |

| 4.1: Source Verilog file and converted equation file of a 2-bit signed multiplier    | 41   |

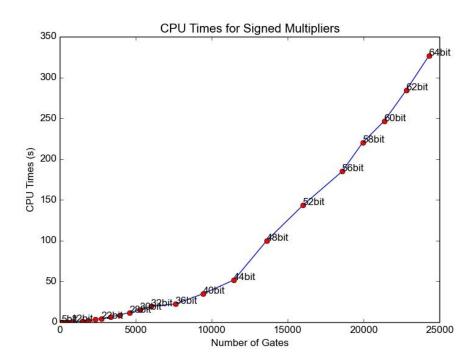

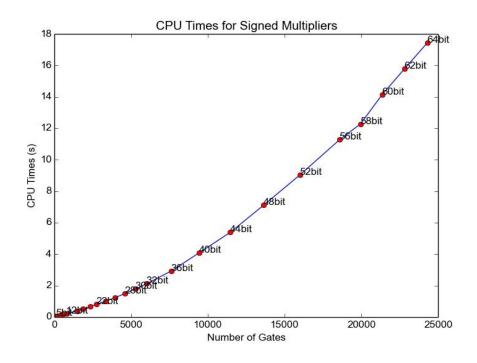

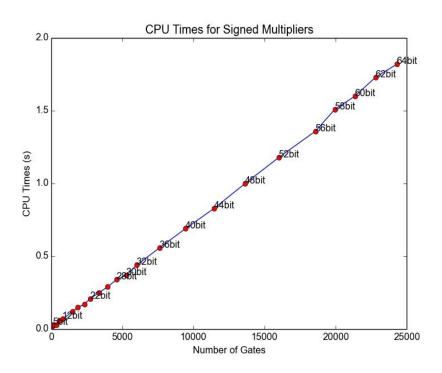

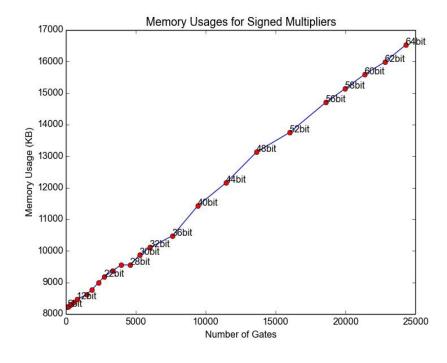

| 4.2: CPU times for verifying signed multipliers using <i>clean_substitute</i>        | 43   |

| 4.3: Memory usage for verifying signed multipliers using <i>clean_substitute</i>     | 43   |

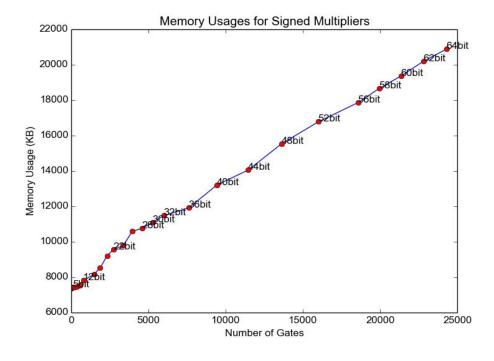

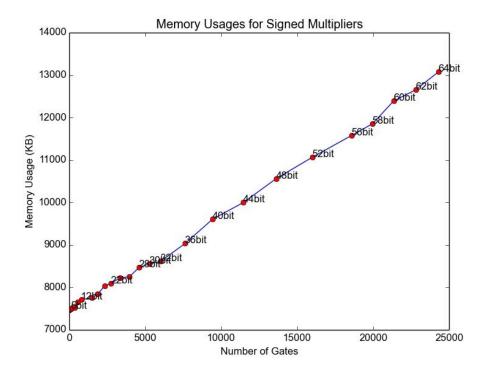

| 4.4: CPU times for verifying signed multipliers using new_clean_substitute           | 47   |

| 4.5: Memory usage for verifying signed multipliers using <i>new_clean_substitute</i> | 47   |

| 4.6: An example of initial dictionary for a 2-bit signed multiplier                  | 49   |

| 4.7: CPU times for verifying signed multipliers using better_clean_substitute        | 51   |

| 4.8: Mem usage for verifying signed multipliers using better_clean_substitute        | 51   |

| 4.9: CPU times for verifying signed multipliers using <i>dict_substitute</i> method  | 58   |

| 4.10: Mem usage for verifying signed multipliers using <i>dict substitute</i> method | 58   |

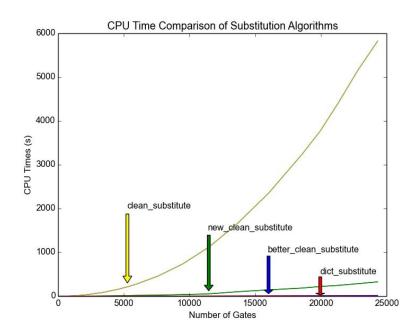

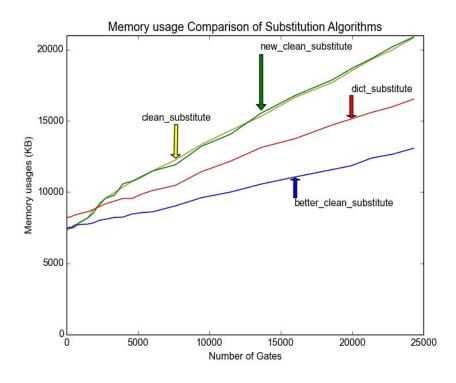

| 4.11: CPU time comparison of four substitution algorithms.    | 59 |

|---------------------------------------------------------------|----|

| 4.12: Memory usage comparison of four substitution algorithms | 59 |

| 6.1: <i>BFS_Levelization</i> methodology                      | 65 |

| 6.2: Level number relaxation example.                         | 66 |

| 6.3 Modified technology mapping library                       | 69 |

| 6.4: <i>Dijk_levelization</i> example                         | 73 |

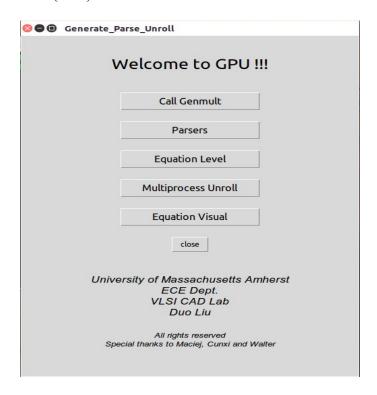

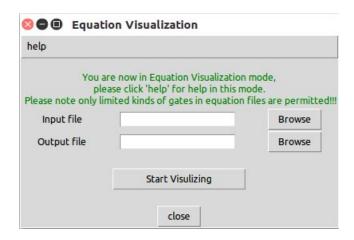

| A.1: GPU main user interface                                  | 87 |

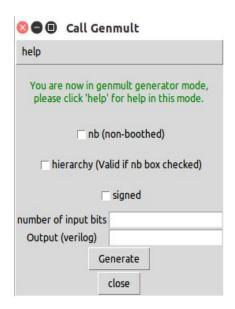

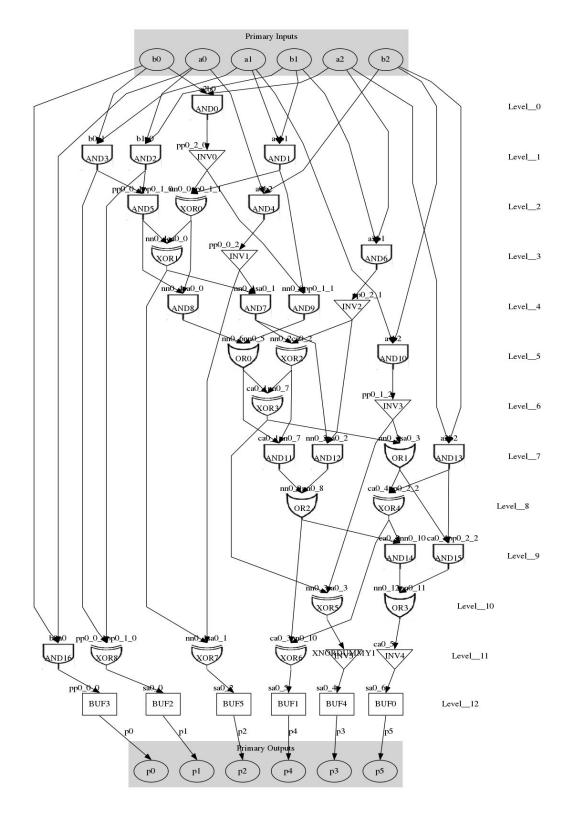

| A.2: Call_Genmult interface.                                  | 88 |

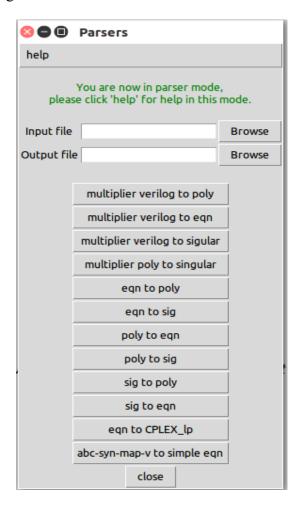

| A.3: Parsers interface                                        | 89 |

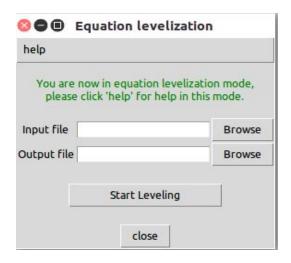

| A.4: Levelization interface                                   | 90 |

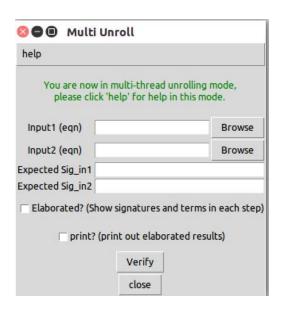

| A.5: Multiprocess Unroll interface.                           | 91 |

| A.6: Equation Visualization interface.                        | 92 |

| A 7: Equation Visualization example                           | 93 |

# LIST OF ALGORITHMS

| Algorithm                              | Page |

|----------------------------------------|------|

| 1: clean_substitute pseudo code        | 42   |

| 2: new_clean_substitute pseudo code    | 45   |

| 3: better_clean_substitute pseudo code | 50   |

| 4: dict_substitute pseudo code         | 54   |

| 5: BFS_Levelization pseudo code        | 64   |

| 6: Dijk levelization algorithm         | 72   |

#### **CHAPTER 1**

#### INTRODUCTION

## 1.1 Verification and Its Importance

Digital hardware verification is becoming more and more challenging. It is because design scale and functionality are growing very fast while the requirement for performance is even higher. It is painful and costly to redesign the circuit if bugs are found very late in the design process. Verification is the one technology for designers to assure the reliance, accuracy and functionality of designs at early stage of work flow.

Validation and verification are two basic techniques to demonstrate that a design is correct. Validation checks if the design's specification meets the market's needs, it is typically done using simulation. Verification checks if the design meets its specifications. We only focus on verification in this thesis.

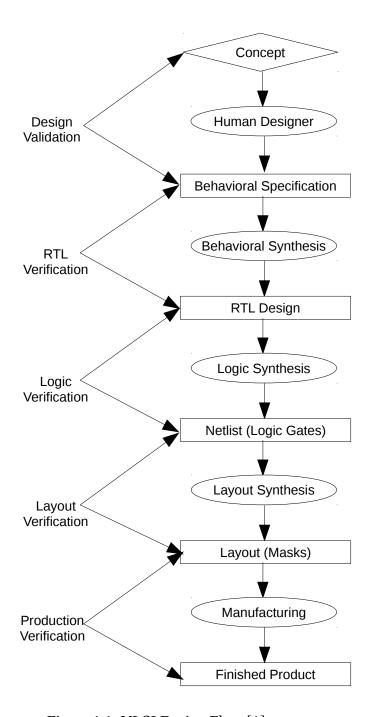

Verification process tries to make sure a design works exactly as the designer anticipated. It is a process that penetrates modern circuit design. Figure 1.1 shows a complete VLSI design flow. This figure shows that most of the total design time, from Register Transfer Level (RTL) to logic level, is consumed by verification. More specifically, more than 70 percent of the design time and resources are spent on functional verification on average [1]. Despite all these efforts, functional bugs still force companies to redesign their products. An important reason for this situation is the

limitations in current verification methods which will be introduced in the following sections.

Figure 1.1: VLSI Design Flow [1].

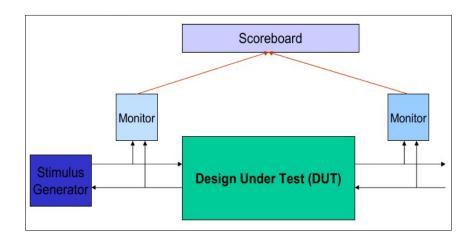

Figure 1.2: Simulation-Based Verification [2].

#### 1.2 Simulation-Based Verification

The traditional way to test design functionality is to simulate the designed circuits function before tape out. To perform simulation of a design, one loads the design into a simulator, assigns a sequence of input vectors and criterion to the simulator and then runs the simulator to check if the circuit behaves as expected the under the given input stimulus. This process is shown in Figure 1.2. In this figure, the scoreboard checks design behavior and the monitors sample interface activity. Through a simulation process, one can design and debug a dynamic model of an actual system either for the purpose of understanding the system behavior or evaluating various strategies (like constraints or optimizations) for the operation of the system [3].

However, with the ever-increasing size and complexity of integrated circuits and systems on chip (SoC) [4], it is becoming harder and harder to simulate the Design Under Test (DUT). The number of problem cases to be examined increase dramatically for

larger and more complex designs. Designers try to put all these cases into a test vector file. Typically this step cannot be done satisfactorily because there are cases that designers may never think of. Without exhausting all possible cases, it is very likely that some corner cases in disguise will be omitted during simulation. Even if all possible cases are considered by designer, it is still impossible to run through all these cases within a reasonable length of time because of the huge quantity of possible test cases. In other words, just as Edsgar W. Dijkstra said, "Program testing can be a very effective way to show the presence of bugs, but is hopelessly inadequate for showing their absence [5]".

#### 1.3 Formal Verification

Taking the above factors into consideration, formal verification can be seen as a good complement for simulation-based verification considering that completeness is the greatest advantage of formal verification. It has already been proved that formal verification methods can be successfully applied to combinational arithmetic circuits [6], [7], [8]. In this section, a series of methods which aim at implementing and improving formal verification methodologies are presented. These works display many important attempts which are pervasively used in formal verification solutions nowadays.

Functional formal verification discussed here is called "formal" because formal methods of mathematics are used to prove that a design implements the correct function. It is a precise technique in the sense of its completeness. Formal verification can guarantee the functional correctness of the design [9] with high confidence, if used correctly, and avoids tremendous cost of fixing bugs that come to surface late in the

whole design chain. Formal verification uses mathematical techniques to ensure that a design conforms to some precisely expressed notion of functional correctness [10]. In the process of implementing formal verification for a design, mathematical models of the system implementation and of the specification must be built first as a formal description of the function of the design. *Specification* in formal verification defines the desired behavior or properties of the system, while *implementation* represents how the circuit is constructed in detail. Then, based on the established mathematical implementation model and specification description, engineers use mathematical reasoning to verify whether design intent (specification) is preserved in the implementation [11]. The current popular formal verification methods include equivalence checking, symbolic simulation, model checking, theorem proving, ATPG (Automatic Test Pattern Generation), and others.

## 1.3.1 Equivalence Checking

Generally speaking, equivalence checking investigates whether two given expressions are functionally identical. In the hardware verification area, equivalence checking plays the role of proving or disproving that a pair of circuit designs behave exactly the same. Typically, the circuit which is known to be correct is called *reference* while the other one is the *implementation* of the DUT. Equivalence checking allows the user to find, analyze and eliminate all the errors introduced during the transfer from one level of abstraction to another [12]. It is often used when engineering changes are made before final manufacturing. Engineering changes are manual corrections made in the implementation process if design errors are found. However, these changes themselves are likely to introduce new errors. Equivalence checking ensures the function of a design after

correction is as intended. Besides, appending optimization and testing circuitry, such as self-scan logic and power-control circuitry, to original designs also may change the design function without being noticed. In this case, the change will require fixing the bugs.

There are many ways to do equivalence checking. Instead of using simulation, which has shortcomings discussed before, people are more inclined to identify similarities between the structures of the designs. Identifying structural similarities means to find functionally equivalent internal nodes in the pair of designs to be compared. Mathematical methods are used frequently to accomplish this identification task. Most of them are based on canonical data structures, such as Binary Decision Diagrams (BDDs) [6], Binary Moment Diagrams (BMDs) [7], Taylor Expansion Diagrams (TEDs) [13] and their extensions [14]. Concrete methods that implement equivalence checking will be illustrated in the following chapter.

# 1.3.2 Model Checking

Model checking, or property checking, has been proposed as a hardware verification method over 30 years ago [15]. It can be a good complement to equivalence checking, specifically for finite state concurrent systems. For example, it can be used to ascertain whether two circuits which are judged to have different functions after equivalence checking are really different. This is useful in practice because in equivalence checking, all too often, designs of different levels need to be compared. Examples include comparing an RTL design with a gate-level design to check their equivalence. In such cases, the lower level design might contain structural details that the higher level design

does not. Due to this, equivalence checking might report a false negative.

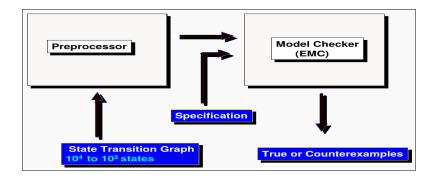

In basic model checking, there are mainly three integral parts: implementation, specification and model checker. The implementation (or system model) is represented as a state-transition graph that shows transition relations between different states. The specification represents the property that must be satisfied. Specifications are expressed in prepositional temporal logic form, a form for time-dependent Boolean functions. The model checker is a module that exhaustively searches the implementation's state space to find as many states that satisfy the specification as possible. Figure 1.3 shows the work flow of a general model checking system.

Figure 1.3: Model checking example [16].

An alternative way to implement model checking is to model both the implementation and the specification as automata. Then, two automata can be compared to test equivalence.

An advantage of model checking is that if the model checker fails to prove the equivalence between implementation and specification, it will generate counterexamples which give clues why the model checking fails and where the errors might be.

The success of the model checker depends on the correct formulation of the

specification and the power of the model checker. The Hardware Model Checking Competition (HWMCC) is held every year to test the efficiency of model checkers. Although model checking is faster than theorem proving (see Section 1.3.4) and is completely automatic, it faces state explosion problem when dealing with larger designs. The difficulty of automata comparison is another factor that limit the pervasive application of model checking.

## 1.3.3 Symbolic Simulation

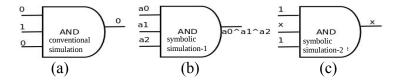

Figure 1.4: An example of conventional simulation and symbolic simulations.

Symbolic simulation "involves introducing an expanded set of signal values and redefining the basic simulation functions to operate over this expanded set", according to [17]. In symbolic simulation, each signal is represented by a symbolic value which can take any value in the symbolic value domain. For example, in Boolean domain, one symbolic value can be regarded as wither binary 0 or binary 1. During symbolic simulation, the symbols are propagated through the design from primary inputs to primary outputs. This content is illustrated in Figure 1.4. The sign " $^{\circ}$ " in Figure 1.4 means logical *AND*. Figure 1.4 (a) represents conventional simulation which guarantees the correctness of only one case in each run. Figure 1.4 (b) represents a complete symbolic simulation. Since a0, a1 and a2 are symbolic binary values, the output of one run actually contains the information provided by 8 conventional simulation runs. Figure

1.4 (c) represents partial symbolic simulation. By assigning symbolic value to one of the inputs and performing constant propagation, the number of total simulation runs can also be reduced. The significant reduction in simulation cases renders symbolic simulation ideal for handling complex and large circuits that otherwise need huge amount of conventional simulation runs. Figure 1.5 shows a more complex example.

Figure 1.5: Another example of symbolic simulation

In Figure 1.5, symbols a, b and c are primary inputs, symbol d is intermediate signal and symbol e is primary output. Signal d can be expressed as  $d = a \wedge b$ . Then e can be represented as  $e = (a \wedge b) \vee c$ . All primary input symbols propagate to the primary output in one simulation run. The primary output bit is represented by a symbolic expression with respect to primary inputs, according to specific circuit.

While performing symbolic simulation, one needs to make sure that the initial state and input variables cover all valid test cases within circuit constraints [18]. BDDs are popular in digital circuit symbolic simulation [17] because they can represent sets of values that signals in circuit may take with reasonable complexity. However, BDDs are not feasible for large designs because certain internal structures, such as XOR, can make BDDs too large to build.

Based on basic symbolic simulation theory, a set of improved works have been proposed for hardware verification, such as ternary simulation [19], quaternary simulation, and symbolic trajectory simulation [20].

### 1.3.4 Theorem Proving

Theorem proving is another important technique used for hardware verification. It is of great importance because of the need for more general-purpose mathematic theorems and tools that can be applied to verification. Designers need more general mathematics because as hardware design improves, the mathematical models for integer and binary areas are not sufficient for solving all verification problems. Some verification problems for certain designs, such as floating-point arithmetic circuits, need mathematical models for more complex fields, such as infinite sets and real numbers.

The first step in theorem proving is to build a collection of formulas derived from the circuit under the proper field. The overall formulation process includes sub-tasks, such as defining semantics and syntax and formulating specification (or conjecture). Then the satisfiability between derived formulas and formulated specification is checked using the selected theory. Some typical formalisms that are common in theorem proving are propositional logic, temporal logic, first-order logic and higher-order logic. The critical factors that determine the selection of formalism type are the formula expressiveness and the difficulty of solving corresponding decision problem. More expressive formalisms will be harder to automate. In practice, it has been found that propositional logic is suitable for modeling a wide range of problems, such as combinational logic equivalence checking problems and finite-state transition problems. First-order logic is also powerful enough for modeling current problems.

After selecting feasible fields, proper theorem proving techniques, such as resolution, tableaux, and others, are applied to check whether the specification theoretically follows

from inferences derived from the circuitry.

There are important differences between model checking and theorem proving. Model checking converts system and specification into certain models (usually state transition graphs) and then check their equivalence. Theorem proving models specification as conjecture and system as axioms, then tries to prove the conjecture using known axioms and theories in the assumed field.

Other works propose a combination of simulation and formal verification. These methods are typically based on Brand's work [21] where a divide and conquer paradigm is introduced. Firstly a small number of simulations are run on both designs to ferret out possible equivalent points. Then techniques, such as comparing ROBDDs or SAT sweeping can be used to prove that these points are indeed equivalent, [22], [23]. Subsequently, the proved true equivalences between subset areas in the designs are used to deduct further equivalences of the circuits until the whole designs are explored. However, approaches that follow such framework also have some problems. The biggest one is the possibility of false negatives [24], and for this reason they can't always claim that two designs which are proved different using this method are indeed different.

## 1.3.5 BDD-Based Techniques

Many of the formal verification methods make use of Binary Decision Diagrams (BDDs) [25], [26]. Being an effective data structure to present Boolean functions, BDDs are popular in formal verification area, where circuit functional verification problems can be described in a Boolean fashion and efficiently solved using BDD-based techniques.

To construct BDDs for boolean functions correctly, some rules must be followed. Firstly, a fixed ordering of variables which appear in the given function specification must be specified. Then the initial decision tree is built from root to leaves according to the predefined ordering. The Boolean-Shannon decomposition rule used while building the decision tree is:

$$F = xF_x + x'F_{x'} \tag{1.1}$$

The decomposition is performed on each node in BDDs with respect to the predefined variable. Finally, all duplicate nodes in the preliminary decision tree are merged and all redundant nodes deleted from the tree, resulting in a general graph.

[24] presents the basic strategy of utilizing BDDs to perform equivalence checking. BDD for each primary output bit of compared circuits needs to be built with respect to the corresponding primary inputs. Such established BDDs are then used to check the function equivalence.

However, as already mentioned in [24], the application of traditional BDD representations is limited by large in BDD size. In the worst case, the complexity of building corresponding BDD increases exponentially with the increase of function size. [24] also shows that BDDs can be used in sequential equivalence checking.

When applied to sequential equivalence checking, BDDs represent sets of states instead of representing internal nodes in circuits. After image computation and reachable state computation, one can decide whether two sequential circuits are functionally equivalent or check if given properties are satisfied. Sequential equivalence checking is beyond the scope of this work and will not be elaborated on in this document.

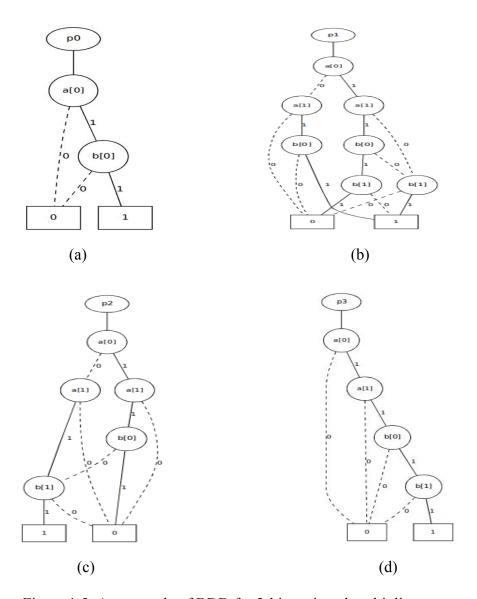

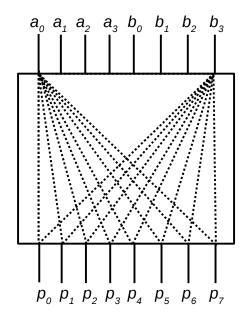

Nevertheless it is known that the application of BDDs in these areas also suffers from size explosion caused by function size and variable order. An example of representing a 2-bit unsigned multiplier with specification  $(2a_1+a_0)(2b_1+b_0)$  in BDD is given in Figure 1.5. In this figure  $p_0$ ,  $p_1$ ,  $p_2$ ,  $p_3$  represent primary output bits of the multiplier.

Figure 1.5: An example of BDD for 2-bit unsigned multiplier.

In [27], Burch used BDDs to verify multipliers by representing the multiplier

specification in a different way (called as fanout splitting) so as to avoid constructing BDDs of exponential size. Although the BDD size can be reduced to  $O(n^3)$ , where n is the number of bits of operands in an  $n \times n$  multiplier, this method requires construction of specifications that are equivalent to the circuit outputs after fanout splitting. Just as evaluated by [28], requirement of Burch's method is hard to apply to synthesized circuits because the logic may be restructured dramatically. [29] proposed a depth-first algorithm to construct BDDs in order to reduce memory overhead, but with poor spatial locality of reference which degrades the overall performance. [30] focused on building large BDDs in a breadth-first way aiming at improving the efficiency by optimizing memory locality. However, the CPU time overhead increases dramatically with the increase of the size of inputs. Currently the best publicly available BDD manipulation tool is CU Decision Diagram Package (CUDD) developed and maintained by University of Colorado at Boulder [31].

## 1.3.6 \*BMD: An Efficient Representation for Word-Level Functions

Multiplicative Binary Moment Diagrams (\*BMDs) [7] enables modeling datapath circuits in word-level data. \*BMDs realize efficient representation for important functions that cannot be efficiently represented by BDDs. In \*BMDs, edges are associated with weights which can be combined multiplicatively. The differences between BDDs and \*BMDs lie in two factors. Firstly, unlike BDDs, \*BMDs don't implement point-wise decomposition. In BDDs, each node has two children representing positive factor and negative cofactor of the expression derived by Shannon decomposition respectively. In contrast, \*BMDs are based on a rearrangement of

Shannon decomposition, called positive Davio decomposition:

$$F = F_{x'} + x(F_x - F_{x'}) \tag{1.2}$$

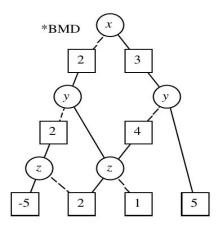

In Equation (1.2) the term  $(F_x - F_{x'})$  is called the linear moment of f with respect to x. The second difference is that each edge in \*BMDs has a specific weight assigned which indicates a multiplicative factor of corresponding node. In BDDs edges just represent the polarity of the decomposing variable (showing if parent node points to a positive cofactor or to a negative cofactor). An example of \*BMD representation of function "8-20z+2y+4yz+12x+24xz+15xy" is shown in Figure 1.6.

Figure 1.6: An example of \*BMD representation of function "8-20z+2y+4yz+12x+24xz+15xy"[7].

\*BMD shows great advantages in representing designs at the word level. The basic algorithms of applying \*BMDs to formal verification area is illustrated are discussed in [7]. The fundamental algorithm uses word-level encoder to encode the bit-level outputs of the circuit while the given specification is also encoded into word level. The \*BMD of world-level output expression is compared with \*BMD of word-level specification to check whether they are equivalent or not. An improved algorithm, which applies \*BMDs

to practical design, is called hierarchical verification. In hierarchical verification, the initial design is first partitioned into subcomponents according to its internal word-level structure. Next, the correctness of subcomponents is verified with respect to the corresponding specification. Finally, based on the correctness of subcomponents, the whole design is verified against its specification.

Although \*BMDs are found to be much more efficient than BDDs in solving verification problems for large and complex circuits, the applicability of \*BMDs is limited by the compulsory requirement of word level representations for the internal structures. This is especially difficult for synthesized or optimized circuits, which often have many irregular structures. Another issue is that, although the \*BMD representation can be linear for circuits which have good word level structure, "a mistake in the implementation of integer multiplication logic can cause an exponential explosion of the resulting graph" [32]. \*BMDs can represent Boolean expressions with complexity comparable to BDDs. An example of representing 2-bit unsigned multiplier with specification  $(2a_1+a_0)(2b_1+b_0)$  using \*BMD is given in Figure 1.7.

Figure 1.7: An example of BMD for 2-bit unsigned multiplier.

Kronecker multiplicative Binary Moment Diagrams (K\*BMDs) [33] as a complement to \*BMDs make the representation of Boolean functions easier. K\*BMDs incorporate the characteristics of ROBDDs and Edge-Values Binary Decision Diagrams (EVBDDs) [34], and allow dynamic switching between the two. In this way, it is possible to represent both word-level and Boolean-level information in circuits in a single flow. However the deficiency of K\*BMDS is that in order to make the diagrams canonical and to make the edges in the diagrams both additive and multiplicative, a set of complex restrictions have to be satisfied.

# 1.3.7 TED: World-Level Compact Canonical Representation

In [13], a canonical graph-based representation, called Taylor Expansion Diagrams (TEDs), has been proposed that provides efficient verification of designs specified on algorithmic and behavioral levels. The authors of TED noticed that BDD-based verification techniques cannot address the verification problem of larger circuits with a hybrid structure of word-level and bit-level representations satisfactorily (including K\*BMDDs mentioned in Section 1.3.6). To address this problem, an entirely different decomposition principle, based on a Taylor series expansion, has been used to decompose the expressions. The circuit is represented as a multi-variate polynomial function. The decomposition is performed on word-level, algebraic variables in the specification, one at a time. For a fixed variable ordering, the resulting TED is canonical.

Given a real, differentiable function f(x, y, ...), the result of decomposing f(x, y, ...) with respect to variable x at an initial point  $x_0 = 0$  is:

$$f(x) = f(0) + xf'(0) + \frac{1}{2!}x^2f''(0) + \frac{1}{3!}x^3f'''(0) + \dots$$

(1.3)

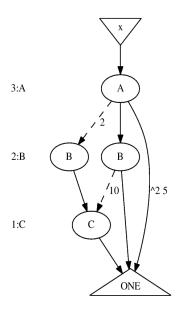

The k-th derivative  $f^{(k)}(x=0)$  in equation 1.3 is a k-children of variable x. Each term in the decomposed equation represents a product of the child-node function and the weight of the edge. Figure 1.8 shows an example of TED result of decomposing expression (5A+B)(A+2C). In Figure 1.8, symbols A, B and C indicate the word-level variables. Each term in the decomposed function is assigned to one of its child node. For example, a dotted line connects the  $\theta$ -child with its parent, a single solid line connects the I-child with its parent, a solid line labeled " $\uparrow i$ " connects the i-child with its parent, etc. The edges can also be labeled with integers that represents the multiplicative coefficient. For instance, the right most edge in Figure 1.8 has label ( $\uparrow 2$  5), where  $\uparrow 2$  denotes the quadratic child (2-child) and constant 5 is the weight of this edge. The reduced TED representation is canonical under fixed variable order.

Figure 1.8: An example of TED for (5A + B)(A + 2C).

Moreover, by constraining the integer range to  $\{0, 1\}$  to support Boolean logic in an algebraic way, TED can be modified to represent Boolean functions. TED of a 2-bit unsigned multiplier with specification  $(2a_I+a_\theta)(2b_I+b_\theta)$  in which all variables are binary is given in Figure 1.9.

Figure 1.9: TED for a 2-bit unsigned multiplier

The known deficiency of TED is that it cannot represent the function of individual bits in output word with respect to word-level input. Similar to \*BMDs, the efficiency of TEDs is affected by the number of variables in the circuit.

## 1.4 Inspiration for Current Work

The different methods and techniques reviewed above cannot address the verification problem of combinational integer arithmetic circuits efficiently. The proposed work aims at solving this problem efficiently at an algebraic level, treating the function specification

(if known) and its implementation as a properly constructed symbolic algebraic system in  $\mathbb{Z}_{2^n}$ . It derives arithmetic function computed by the circuit from its gate-level implementation, which can be compared with a reference signature to determine whether the circuit is correct. It can also be used as a reverse engineering tool, to learn the function performed by the given circuit. Chapter 2 reviews some advanced methods that try to solve the combinational arithmetic circuit verification problem using symbolic computer algebra. Chapter 3 explains the proposed work, how it differs from previous works and shows the preliminary experiment results.

#### **CHAPTER 2**

#### RELATED WORK

The method proposed in this thesis aims at solving the functional verification problem for combinational arithmetic circuits specified on an arithmetic bit level. In this chapter, several formal verification methods that address the similar application are analyzed.

## 2.1 Theoretical Background

The underlying mathematical models of formal verification method discussed here are based mainly on symbolic computer algebra [35]. Symbolic computation manipulates expressions with symbolic variables, which are not given any numerical values. In this way, symbolic computer algebra preserves the advantages of formal verification. Conventional formal verification methods, discussed in Chapter 1, typically try to represent primary outputs with respect to primary inputs using certain data structure. However, formal verification methods that will be investigated here generally utilize another interpretation of symbolic computer algebra. The formal verification problem is modeled in this work as a *membership testing* problem between the circuit specification and its implementation as polynomials, based on a computer algebra model. The final goal is to prove that implementation represented by circuit equations satisfies the specification polynomial. This is accomplished by performing a series of divisions of the

specification polynomial F by the implementation polynomials  $B = \{f_1, ..., f_s\}$ . For example, the specification of a multiplier circuit with word-level inputs X, Y and output Z is  $F = Z - X \cdot Y$ . The implementation polynomials are derived from gate equations, similar to those shown later in Equations 3.1.

To systematically manipulate polynomials, a term ordering ">" is imposed on monomials. The leading term of polynomial g under such ordering is denoted lt(g). Term ordering plays an important role in polynomial reduction used in circuit verification.

Let f, g be polynomials. If a non-zero term t of  $f_i$  is divisible by the leading term of g, we say that f reduces to r modulo g denoted:

$$f \stackrel{g}{\Rightarrow} r$$

, where  $r = f - \frac{lt(f)}{lt(g)} \cdot g$ .

Similarly, f can be reduced with respect to (divided by) a set of polynomials  $B = \{f_l, ..., f_s\}$ . This is known as polynomial division modulo B, denoted symbolically as  $f \stackrel{B}{\Rightarrow}_+ r$  where r is a remainder, with the property that no term in r is divisible by the leading term of any polynomial in B. The sign + refers to the fact that the division process is sequential, using polynomials in B one by one.

Let  $B = \{f_1, ..., f_s\}$  be a set of polynomials representing circuit elements (logic gates, adders, arithmetic modules, etc.) and let R be a polynomial ring,  $R = F\{x_1, ..., x_n\}$ . In fact, in our case R should be defined over integers,  $\mathbb{Z}_{2^n}$ , rather than a field F. Then,  $J = \langle f_1, ..., f_s \rangle$  with  $f_i \in \mathbb{Z}[X]$ , called an ideal, is a set of all polynomials generated by  $\{f_i\}$ .

$$J = \langle f_1, ..., f_s \rangle = h_1 f_1 + ... + h_s f_s : h_i \in R$$

(2.1)

The polynomials  $f_1, ..., f_s$  are called the bases, or generators, of the ideal J. In our case,

each generator is a polynomial model of a circuit module, and the set of generators can be viewed as the implementation of the circuit.

We also need a notion of variety. For a given ideal J, variety V(J) defines a set of all simultaneous solutions to a system of equations  $f_1(x_1, ..., x_n) = 0$ ; ...,  $f_s(x_1, ..., x_n) = 0$ . From the circuit perspective, variety contains all the signal values of the circuit produced by any set of primary inputs, over all possible input combinations.

We define a circuit specification as polynomial  $F \in \mathbb{Z}_{2^n}[X]$ . For example, the specification of a multiplier circuit,  $P = A \cdot B$ , where A, B are word-level variables, is  $F = P - A \cdot B$ .

We can now formulate the arithmetic circuit verification problem as follows [36], [37]. Given a circuit represented by the set of generators,  $B = \{f_1, ..., f_s\}$ , and the specification F, the goal is to prove that the implementation (modeled by B) satisfies the specification F. Mathematically, this can be stated that the solution to F = 0 agrees with V(J), or, equivalently, that that F vanishes on V(J) [37]. We say that F vanishes on V(J) if F evaluates to 0 for all values of V(J) (which also means the remainder F = 0). In computer algebra this problem is known as *ideal membership testing*.

However, if  $r \neq 0$ , such a conclusion cannot be made; B may not be sufficient to reduce F to 0, and yet the circuit may be correct. To check if F is reducible to zero one must use a canonical set of generators,  $G = \{g_1, ..., g_t\}$ , called Groebner basis, which generates the same ideal as the one based on B, i.e.,  $J = \langle g_1, ..., g_t \rangle = \langle f_1, ..., f_s \rangle$ . Without Groebner basis one cannot answer the question whether  $F \in J$ . A number of algorithms have been developed for computing Groebner basis over the field, such as Buchberger

[38], F4 [39], etc., but their computational complexity is prohibitively large for nonlinear arithmetic circuits. Furthermore, these algorithm do not apply directly to rings over integers,  $\mathbb{Z}_{2n}$ , which is considered in this work.

#### 2.2 Previous Work

Work in arithmetic circuit verification based on computer algebra and algebraic geometry was pioneered by [40] and [41].

In [41] an arithmetic circuit is modeled as a network of arithmetic operators, such as half-adders, comparators, product generators, etc., which in principle can be extracted from the gate-level implementation. These operators are modeled using arithmetic bit-level (ABL) equations,  $\{G_j\}$ . Authors of [41] (and also [36]) show that for an arbitrary combinational circuit, if the terms of the gate equations  $\{G_j\}$  are ordered in the reverse topological order,  $\{outputs\} > \{inputs\}$ , then all leading monomials of the polynomials in B are relatively prime. As a result, the corresponding set G constitutes a Grobner basis, obviating the expensive Grobner basis computation. The verification problem is then formulated as a variety subset problem and solved by reducing the specification modulo G to a normal form and testing if it vanishes over  $\mathbb{Z}_T$ . Furthermore, in [42], the solution is restricted to binary variables by imposing Boolean constraints,  $\langle x^2 - x \rangle$ , and solving the problem directly over quotient ring  $Z_T[X]/\langle x^2 - x \rangle : x \in X$ . An important simplification comes from the fact that  $(Lemma\ 1,\ [42])$ : "If some polynomial f vanishes on V(J) then f must be a zero polynomial" and not just a zero function. That is, only the

zero polynomial in  $Q = Z_{2^n}[X]/\langle x^2 - x \rangle$ :  $x \in X$  defines the zero function on  $Q^{|x|}$ , rendering the zero function test superfluous. This makes it possible to replace the expensive zero function test (r = 0?) by checking if r is a zero polynomial. The problem based on this approach was solved using a computer algebra system, Singular [43]. However, this approach is limited to arithmetic bit-level networks composed of half adders and full adders, which need to be extracted from the gate-level implementation. Experimental results show that this is the most expensive part of the process, and such an extraction is not always possible, especially in highly bit-optimized implementations.

In [36], the verification problem is also formulated as ideal membership test but applied to Galois field arithmetic circuits. They have shown that for a special case of Galois Field (GF or  $F_{2^n}$ ), when the specification F and the ideal J of the circuit constraints (implementation) are in  $F_{2^n}$ , then the problem of testing if  $F \in I(V(J))$  can be greatly simplified. Specifically, it can be reduced to the ideal membership testing over a larger ideal,  $F \in (J + J_0)$ , where  $J_0 = \langle x^2 - x \rangle$  is an ideal of vanishing polynomials in  $F_2$ . Adding  $J_0$  basically restricts variety V(J) to solutions in  $F_2$ , i.e., to  $V(J) \cap V(J_0)$ . It is known from the theory of algebraic geometry [35] that intersection of varieties is equivalent to a union (sum) of ideals.

Similarly to [41], Lv, Kalla, et. al [36] derives term ordering from the topological structure of the circuit, which renders the set of polynomials *B* (circuit constraints) a Groebner basis, thus obviating the need to perform expensive *GB* computation. The method uses a customized, F4-style polynomial reduction which is based on a modified Gaussian elimination algorithm [39]. An important feature of this approach is that, by

construction, if the remainder  $r \neq 0$  then it contains only the primary input variables. Consequently, it can be used to provide a counterexample, or a bug trace, to locate the source of the bug.

However, this method also suffers from some problems that limit its application. For example, this approach applies only to Galois Field networks, and it is not clear if the simplification of the general ideal membership problem to testing for  $F \in (J + J_0)$  applies to polynomial rings of integers,  $\mathbb{Z}_{2^n}$ .

In effect, the two approaches, [42] and [36], managed to reduce the problem to an ideal membership problem,  $F \in J$ , instead of solving a more complicated problem of checking if  $F \in I(V(J))$ . Each approach places some limitations on the problem to make it solvable.

Alternative approaches to arithmetic circuit verification were also proposed in [44], [45] and [46]. In [44] an arithmetic bit-level circuit is modeled as a network of half adders, but, in contrast to [42], admits also logic gates. Logic gates are modeled with, or directly derived from, half adders, possibly leaving some of the outputs unused (referred to as floating signals). This model makes it possible to describe an entire network as a system of linear equations. Such a system then represents the implementation of the circuit. The specification is composed of two parts, an input signature,  $Sig_{in}$ , a polynomial in primary inputs (P1); and an output signature,  $Sig_{out}$ , a polynomial representing the circuit result in terms of the primary outputs (PO). The specification is then defined as the difference between the two signatures,  $F_{spec} = Sig_{out} - Sig_{in}$ . For example, for a 2-bit adder with inputs  $a_0$ ,  $a_1$ ,  $b_0$ ,  $b_1$  and outputs  $S_2$ ,  $S_1$ ,  $S_0$ , the

specification is defined as  $F_{spec} = 4S_2 + 2S_1 + S_0 - (a_0 + 2a_1 + b_0 + 2b_1)$ .

The system of linear equations (implementation) is then reduced to a single algebraic expression, called the *circuit signature*, and is compared to  $F_{spec}$ . If the signature polynomial is identical to  $F_{spec}$ , then the circuit operates correctly according to that specification. If not, the difference between the two, called residual expression, RE, determines a possible mismatch between the implementation and the specification. In [44], a Gaussian-like elimination and standard linear algebra techniques were used to compute the signature, and a canonical polynomial representation TED [47] was used to compare the results.

The shortcoming of this method is that it can only handle linear portion of the network, with linear input signature. Extension to nonlinear circuits is also possible, but it requires additional step to translate the input signature of the linear block into a nonlinear signature in terms of the primary inputs. TDS system [48] based on TED can be used for this purpose. It should be noted that such defined  $F_{spec}$  is in fact the same as the specification polynomial F in the works of [36] and [42], and the set of linear equations (or, equivalently, polynomials) forms the basis B of circuit elements (half-adders and logic gates). The resulting RE is then the same as the remainder of the polynomial reduction of  $F_{spec}$  modulo set B. The significant difference between these approaches is that in [44] it was not possible to capture the Boolean nature of the signals, i.e., to impose the quotient ring  $Z_{2^n}[X]/\langle x^2 - x \rangle$ :  $x \in X$  for variables  $x_i \in X$ . The authors suggested that Boolean reasoning combined with topological analysis of the circuit can be used to reduce RE to zero, but in the worst case this task could be as difficult as the original

problem itself.

In [45], a different model was used, whereby the computation performed by the circuit is viewed as a flow of binary data. For the circuit to be correct, the flow must satisfy a suitably modified Flow Conservation Law. Verification problem was solved by transforming the known input signature into a polynomial in primary outputs only, and checking if the resulting expression matches the output signature (binary encoding at primary outputs). The issue of testing if RE = 0 was eliminated by checking the relation between the fanouts and floating signals, that correctly captured the Boolean nature of signal variables. Specifically, the following condition has to be satisfied by the circuit,  $\Delta_{fn} - \Sigma_{fl} = 0$ , where  $\Delta_{fn}$  and  $\Sigma_{fl}$  are polynomials representing fanout variables and the floating (unused) signals, respectively. This condition basically states that any additional flow introduced into the network by fanouts, must be compensated by the flow consumed by the floating signals that do not reach primary outputs. In practice, the method is still applicable only to networks with linear input signatures.

In conclusion, the problem of formally verifying integer arithmetic circuits, over  $\mathbb{Z}_{2^n}$  remains open. This thesis addresses some stated problems and proposes a robust solution in this domain.

#### **CHAPTER 3**

#### PROPOSED WORK

#### 3.1 Motivation

Original works, [41], [36], in computer-algebra based methods showed that, for combinational circuits with proper (reverse topological) ordering of terms in basis B, the constructed basis over the respective ring (in our case  $\mathbb{Z}_{2^n}$ ) constitutes a Groebner basis. This is true for combinational circuits, which are direct acyclic graphs (DAG). In such circuits the leading monomials are single variables and the leading terms are relatively prime. Whether this fact can help solve the problem of proving equivalence of F over  $\mathbb{Z}_{2^n}$  subject to implementation B over  $\mathbb{Z}_2$  remains to be proved. In the meantime, we propose to solve the problem bypassing this theoretical issue, and act as follows.

In our case, the specification polynomial  $F_{spec} = Sig_{out} - Sig_{in}$  is a ring in  $\mathbb{Z}[X]$  with coefficients in  $\mathbb{Z}_{2^n}$  and variables in  $\mathbb{Z}_2$ . In contrast to [45], and work of Kalla et. al, [36] for Galois Fields networks, polynomial F can be nonlinear. This regards the nonlinear circuits, such as multipliers, multiply-accumulator, etc., and any circuit containing logic gates. In this case the input signature and polynomials in B may be nonlinear (see Equations 3.1).

Notice that for polynomials whose terms contain single variables, polynomial division which results in cancellation of terms is equivalent to substitution by the

expression corresponding to the substituted variable. This is true in the case of the HA network (ABL model) and in the case of GF networks, composed entirely of XOR and INV gates. Addition of the OR gates complicates the issue, since the polynomial representation of the OR gates  $(a + b - a \cdot b)$  contains a nonlinear term, and the same variable appears in more than one term. The same is true for XOR in  $\mathbb{Z}_2$ , where XOR is represented as  $(a + b - 2 \cdot a \cdot b)$  while it does not cause the problem in  $GF_2$ , where polynomial for XOR gates are just represented as a + b.

All these investigations can be summarized as follows: polynomial division is equivalent to variable substitution and should be done in a reversed topological order, from the gates outputs to the gates inputs. Examples of polynomials used in polynomial division are Equations 3.1 and Equations 3.2. This applies to both linear and nonlinear case. Because of the potential exponential explosion, the division or substitution should be done in the most efficient manner, the topic which will be explored in the remainder of this thesis. The method proposed here extends our work described in [4] from ABL network to gate-level (or hybrid-level) circuit implementation of arbitrary granularity. It offers a robust solution to integer arithmetic verification by computing (extracting) a unique arithmetic function implemented by the circuit, directly from its low-level circuit implementation. From here on, the terms *rewriting*, *substitution* and *unrolling* will be used equivalently.

## 3.2 Implementation

Our method attempts to solve the functional verification problem of combinational

arithmetic circuits at an algebraic level by formulating it as a function abstraction model, i.e., by deriving a unique bit-level polynomial function computed by the circuit directly from its low-level implementation. It uses an efficient, guided elimination technique while trying to avoid the conventional and expensive process of Groebner basis computation and implementing polynomial division.

In our method, the circuit under study is composed of arbitrary elements, such as logic gates and multiple-output arithmetic components. It will be modeled as a network of interconnected bit-level components (modules), each with a finite set of binary inputs and one or more binary outputs. Specifically, a module represents a single-output Boolean logic gate (AND, OR, XOR, INV) or a bit-level arithmetic circuit (half adder, HA, or a full adder, FA) with two binary outputs, carry C and sum S. In this sense, the proposed model admits a hybrid network, composed of an arbitrary collection of logic gates and bit-level arithmetic components. At one extreme, it can be a purely gate-level circuit; at the other, a network composed of arithmetic components only.

Each module  $m_i$  in the network is modeled as a polynomial with variables  $X = \{x_1, ..., x_n\} \in \mathbb{Z}_2$  (binary) and coefficients in  $\mathbb{Z}_{2^n}$  (integers modulo  $2^n$ ). More precisely,  $f_i$  is a polynomial quotient ring over  $Z_{2^n}[X]/\langle x^2 - x \rangle : x \in X$ . The restriction to  $\langle x^2 - x \rangle$  is dictated by the binary nature of the circuit signals. Sometimes, such a polynomial is referred to as a *pseudo-Boolean* expression, since it represents an algebraic expression, with usual algebraic multiplication and addition operators over Boolean variables. For example, an AND gate  $(a \land b)$ , is expressed by an algebraic equation  $p = a \cdot b$ , or equivalently by a polynomial  $p - a \cdot b$ , etc. The following equations summarize algebraic

representation of Boolean operators:

$$\neg a = 1 - a$$

$$a \wedge b = a \cdot b$$

Equations 3.1

$$a \vee b = a + b - a \cdot b$$

$$a \oplus b = a + b - 2a \cdot b$$

Multiple output modules, such as single-bit adders, with binary inputs can be expressed similarly. For example, a half-adder *HA* and a full-adder *FA*, can be expressed by polynomials:

$$HA: 2C + S = a + b$$

Equations 3.2

$$FA: 2C + S = a + b + c_{in}$$

where a, b, c<sub>in</sub> are binary inputs and C, S are binary outputs.

We define the verification problem by setting  $F_{spec} = Sig_{out}$ . We devise a procedure (based on Gaussian elimination combined with term substitution) to rewrite  $Sig_{out}$  into  $Sig_{in}$  using polynomial representation (shown in Equations 3.1 and 3.2) of the internal circuit elements (gates, adders, etc.). If the resulting  $Sig_{in}$  contains only the primary inputs (PI) then it uniquely determines the arithmetic function computed by the circuit. The designer can then determine if the obtained input signature correctly describes the expected function of the circuit by comparing the computed  $Sig_{in}$  with given specification. In this procedure, the basic requirement is to perform the substitution in a reversed topological order. The reason for this can be clarified using the following

example. In addition, some interesting observations are also found to make the substitution process more efficient.

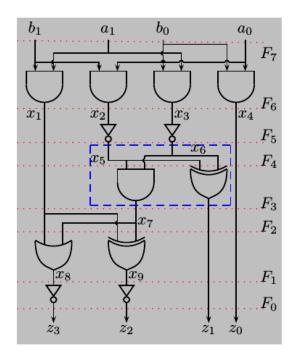

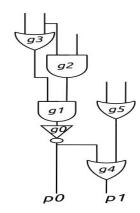

Figure 3.1: An example of gate-level implementation of a 2-bit signed multiplier.

Figure 3.1 shows the gate-level implementation of a 2-bit signed multiplier. This circuit has a hybrid-level structure because because it contains both logic gates and a half adder shown in the dotted box. This circuit is non-linear since its input signature  $Sig_{in} = (-2 a_1 + a_0)(-2 b_1 + b_0) = 4 a_1 b_1 - 2 a_1 b_0 - 2 a_0 b_1 + a_0 b_0$  has non-linear terms.

The first step is to construct the equation set for each component in the circuit. The resulting equation set is as follows:

$$z_3 = 1 - x_8$$

Equation 3.3

$$z_2 = 1 - x_9$$

Equation 3.4

$$z_1 = x_5 + x_6 - 2x_5x_6$$

Equation 3.5

$$z_0 = a_0 b_0$$

Equation 3.6

$$x_8 = x_1 + x_7 - x_1 x_7$$

Equation 3.7

$$x_9 = x_1 + x_7 - 2 x_1 x_7$$

Equation 3.8

$$x_7 = x_5 x_6$$

Equation 3.9

$$x_5 = 1 - x_2$$

Equation 3.10

$$x_6 = 1 - x_3$$

Equation 3.11

$$x_1 = a_1 b_1$$

Equation 3.12

$$x_2 = a_0 b_1$$

Equation 3.13

$$x_3 = a_1 b_0$$

Equation 3.14

By definition, the output signature,  $Sig_{out}$ , of the circuit is a linear polynomial of the primary output signals. It is uniquely determined by the *n*-bit encoding of the output, provided by the designer. In this example,  $Sig_{out} = -8z_3 + 4z_2 + 2z_1 + z_0$ . For more general cases, an output signature of any arithmetic circuit with n output bits  $z_i$  is represented as follows:

$$Sig_{out} = \sum_{i=0}^{n-1} 2^i z_i$$

By substituting variables in  $Sig_{out}$  with their respective expressions, Equation 3.3 to (3.14, we obtain the following sequence of intermediate expressions:

1) By substituting variable  $z_3$  in  $Sig_{out}$  using Equation 3.3,  $Sig_{out}$  is converted to

$$F_1 = 4z_2 + 2z_1 + z_0 + 8x_8 - 8$$

2) By substituting variable  $z_2$  in  $F_1$  using Equation 3.4,  $F_1$  is converted to

$$F_2 = 2z_1 + z_0 + 8x_8 - 4x_9 - 4$$

- 3) By substituting variable  $x_8$  in  $F_2$  using Equation 3.7,  $F_2$  is converted to  $F_2 = 2z_1 + z_0 + 8x_1 + 8x_2 8x_1x_2 4x_0 4$

- 4) By substituting variable  $x_9$  in  $F_3$  using Equation 3.8,  $F_3$  is converted to  $F_4 = 2z_1 + z_0 + 4x_1 + 4x_2 4$

- 5) By substituting variable  $z_1$  in  $F_4$  using Equation 3.5,  $F_4$  is converted to  $F_5 = 2x_5 + 2x_6 4x_5x_6 + z_0 + 4x_4 + 4x_7 4$

- 6) By substituting variable  $x_7$  in  $F_5$  using Equation 3.9,  $F_5$  is converted to  $F_6 = 2x_5 + 2x_6 + z_0 + 4x_1 4$

- 7) By substituting variable  $z_0$  in  $F_6$  using Equation 3.6,  $F_6$  is converted to  $F_7 = 2x_5 + 2x_6 + a_0b_0 + 4x_1 4$

- 8) By substituting variable  $x_1$  in  $F_7$  using Equation 3.12,  $F_7$  is converted to  $F_8 = 2x_5 + 2x_6 + a_0b_0 + 4a_1b_1 4$

- 9) By substituting variable  $x_5$  in  $F_8$  using Equation 3.10,  $F_8$  is converted to  $F_9 = -2x_2 + 2x_6 + a_0b_0 + 4a_1b_1 2$

- 10) By substituting variable  $x_6$  in  $F_9$  using Equation 3.11,  $F_9$  is converted to  $F_{10} = -2x_2 2x_3 + a_0b_0 + 4a_1b_1$

- 11) By substituting variable  $x_2$  in  $F_{10}$  using Equation 3.13,  $F_{10}$  is converted to  $F_{11} = -2a_0b_1 2x_3 + a_0b_0 + 4a_1b_1$

- 12) By substituting variable  $x_3$  in  $F_{II}$  using Equation 3.14,  $F_{II}$  is converted to  $F_{IJ} = -2a_0b_1 2a_1b_0 + a_0b_0 + 4a_1b_1$

After these 12 steps, all equations derived from the circuit have been used. As a result the  $Sig_{out}$  has been converted to  $F_{12} = -2a_0b_1 - 2a_1b_0 + a_0b_0 + 4a_1b_1$  which matches the

given input signature. Furthermore, by analyzing the factored form of  $Sig_{in}$ ,  $Sig_{in} = (-2a_1 + a_0)(-2b_1 + b_0)$ , we conclude that this circuit is a 2-bit signed multiplier. Such a factorized form can be obtained using TDS [47] system based on canonical TED representation.

In the substitution procedure shown above, the equation for  $F_i$  is in Disjunctive Normal Form (DNF). It can be shown that each term in the DNF equation appears only once, and hence  $Sig_{out}$  expression is canonical (This will be formally proved in Chapter 5). Essential of this approach is to improve the efficiency of the substitution process.

First, we must determine which variable to substitute in each step in order to make the cancellation between terms happen as early as possible. This is of great importance for keeping the expression  $F_i$  of the transformed  $Sig_{out}$  expression in each step as simple as possible in terms of the number of its terms. For example, we will identify variables that depend on common fanouts, as this will increase the number of similar expressions and will increase a chance for simplification and elimination of common subexpressions. For instance, variables in subexpression of  $F_2$ ,  $8x_8 - 4x_9$ , depend on common fanout variables  $x_1$ ,  $x_7$ . As a result,  $8x_8 - 4x_9 = 4(2x_8 - x_9)$  after substitution in Equation (3.7) and (3.8) is reduced to  $4(x_1 + x_7)$ , without introducing a nonlinear term  $8x_1x_7$ . Hence, expression  $F_2$  can be directly transformed into  $F_4$ . If the substitution steps are modified, for example by moving step 4 after step 6, then the  $Sig_{out}$  expression after substituting  $x_9$  will be

$$2x_5 + 2x_6 + z_0 + 4x_1 + 4x_5x_6 - 8x_1x_5x_6 - 4x_7 + 8x_1x_7 - 4$$

instead of

$$2x_5 + 2x_6 + z_0 + 4x_1 - 4$$

.

In this hypothetical case, we can see that in order to get rid of  $x_7$ , Equation (3.9) has to be called again. Hence the size of expression, in terms of product terms, in each step is larger and the number of equations used for substitution is also larger. This is obviously more expensive than the order shown in the original procedure.

Second, we try to simultaneously eliminate all outputs of higher level modules such as adders (if present in the design). Consider, for instance, the dotted box in Figure 3.1, which represents a half adder. As shown by Equation (3.2), the weighted sum of the half adder outputs,  $2x_7 + z_1$ , can be replaced directly by its inputs,  $x_5 + x_6$ , thus avoiding unnecessary introduction and elimination of the nonlinear term  $4x_5x_6$ . As a result, cut  $F_4$  can be directly transformed into  $F_6$ . Such nonlinear terms are particularly harmful if their variables continue to be substituted by other variables, potentially leading to an exponential explosion.

Another important heuristic, which is not shown in example of Figure 3.1 explicitly, is to keep all variables Boolean. We will do this by replacing the expensive division by  $\langle x^2 - x \rangle$  (employed by [41] and other symbolic algebra methods) by lowering  $x^k$  to x every time variable x is raised to higher degree during substitution. This may happen in cases such as the one shown below.

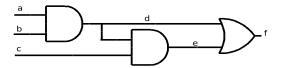

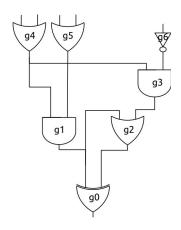

Figure 3.2: An example of keeping variable Boolean.

In Figure 3.2, variable f is the output, and variables a, b and c are the binary inputs. If substitutions are performed using strictly algebraic manipulation (multiplication), the expression for f will be  $ab + abc - a^2b^2c$ . However, by maintaining the Boolean value of variables a, b, f will be represented as

$$ab + abc - abc = ab$$

Other heuristics, noticeably the levelization algorithm, that make the substitution process more efficient are examined in the following chapters. Specifically, these heuristics include:

# Dependency and levelization:

- a) Substitution must follow the reverse-topological order; once a given variable (output of a gate) is substituted by an algebraic expression of the gate inputs, it will be eliminated from the current cut expression and will never be considered again. That is, a variable is substituted for only after substituting all signals in its logical cone. Since the circuit is acyclic, there always exists an ordering of substitutions that satisfies this condition. We refer to this topological constraint informally as "vertical", since it orders variables upwards from primary outputs to primary inputs.

- b) To further increase the efficiency of substitution, another ("horizontal") constraint is imposed on the ordering of the candidate variables at a given transformation step. Specifically, the variables that are at the same logic level (from primary inputs) and have transitive fan-in to common variables should be eliminated together, as this will maximize a chance of the reduction of common

terms. It is these variables that define the best cut at each step of the procedure.

## Complex gates:

Our signature transformation algorithm works on a fabric of basic Boolean gates; this offers high logic granularity and the greatest choice of signals for the selection of the smallest cut. For the design with complex gates (standard cells AOIxx, OAIxx, etc.), algebraic equations are written for each internal signal of the gate, rather than only for its output. As confirmed by our experiments, this offers a richer set of cuts to choose from and increases a chance of an earlier simplification of the cut expression.

## • Binary signals:

During elimination, the expensive division by the ideal  $x^2 - x$ , employed by [42], is replaced by lowering  $x^k$  to x every time variable x is raised to higher degree during the substitution process. For example, if at any point an expression contains a term xyx, it will be replaced by xy. With this, an expression, such as xyx-yxy, will immediately reduce to  $\theta$ .

#### • Efficient data structure:

Our algorithm uses an efficient data structure to support these simplifications and efficiently implement an iterative substitution and elimination process.

#### **CHAPTER 4**

# IMPLEMENTATIONS AND IMPROVEMENTS OF VARIABLE SUBSTITUTION METHODS

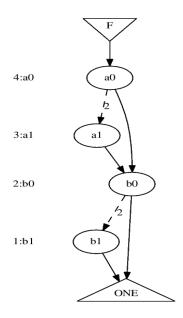

## 4.1 Preliminary Experiments and Result Analysis

To test the basic variable substitution method presented in Chapter 3, we wrote a prototype program in Python that performs such variable elimination. The basic heuristic applied here is to replace each variable only once and to keep each variable binary. The input file to this prototype program is an equation file which is converted from the Verilog description of the circuit. The format of the equation file is predefined as follows the first line in it must be the given output signature, the subsequent lines are gate equations. This format will be the standard input format for all the following algorithms. The order of gate equations in the equation files is the reverse of the order of logic expressions in the Verilog file. The equations are obtained by translating the original Verilog netlist into a netlist of 2-input OR, XOR, AND and INV gate equations. The output signature provided by user is the linear combination of primary output bits defined by the output encoding. An example of the conversion between the Verilog file and the equation file is shown in Figure 4.1. For example, the first equation on line 19 of the Verilog file is converted to the last equation at line 17 of the equation file. Note that the first line in the equation file is the output signature of the multiplier. For each equation in the equation file, the variable on the left side of the equality sign "=" is the variable that needs to be

substituted for in the signature. We refer to this variable as *target variable*. The polynomial on the right side of the equality sign is the substitution for the *target variable*. We refer to this polynomial as *substitution polynomial*.

```

mult2snb-gl-regOR.eqn ×

mult2snb-no-hier.v ×

1 -8*p3+4*p2+2*p1+1*p0

1 // generated by: ./genmult -a 2 -b 2 -s -f ./mult2/mult2PPfiles-nonb -o ./mult2/mult2s-nonb

2 p3=sa0 2

3 p2=sa0_1

3 // signed 2x2 standard non-Booth multiplier (modif. Baugh-Wooley) with primary inputs: a, I

4 p1=sa0_0

4 // primary output: p

5 p0=pp0 0 0

6 sa0_2=1-ca0_1

7 ca0_1=ca0_0+pp0_1_1-ca0_0*pp0_1_1

8 sa0_1=1-XNORDUMMY1

7 module mult_sn_2x2(p, a, b);

9 XNORDUMMY1=ca0_0+pp0_1_1-2*ca0_0*pp0_1_1

9 // The input-vectors of the circuit #0:

10 ca0_0=nn0_0*nn0_1

10 input [1:0] a;

11 sa0 0=nn0 1+nn0 0-2*nn0 0*nn0 1

11 input [1:0] b;

12 nn0_1=1-pp0_0_1

13 nn0_0=1-pp0_1_0

13 // The only output-vector:

14 pp0_1_1=a1*b1

15 pp0_0_1=a0*b1

14 output [3:0] p;

15 wire pp0_0_0,pp0_1_0,nn0_0,pp0_0_1,nn0_1,pp0_1_1,sa0_0,ca0_0,sa0_1,ca0_1,sa0_2;

16 pp0_1_0=a1*b0

17 pp0_0_0=a0*b0

18 // ***** Partial products *****

19 assign pp0_0_0 = a[0] & b[0];

20 assign pp0_1_0 = a[1] & b[0];

21 assign nn0_0 = ~pp0_1_0;

22 assign pp0_0_1 = a[0] & b[1];

23 assign nn0_1 = ~pp0_0_1;

24 assign pp0_1_1 = a[1] & b[1];

25 // ***** Partial products *****

28 assign sa0_0 = nn0_1 ^ nn0_0;

29 assign ca0_0 = nn0_1 & nn0_0;

30 assign sa0_1 = ~( ca0_0 ^ pp0_1_1 );

31 assign ca0_1 = ca0_0 | pp0_1_1;

32 assign sa0_2 = ~ca0_1;

34 // *** outputs ***

35 assign p[0] = pp0_0_0;

36 assign p[1] = sa0_0;

37 assign p[2] = sa0_1;

38 assign p[3] = sa0_2;

40 endmodule

```

Figure 4.1: Source Verilog file and converted equation file of a 2-bit signed multiplier

After the equation file is read in, substitutions start from  $Sig_{out}$ . The substitution and elimination approach implemented in the prototype program is straightforward. The program repeatedly calls the *clean\_substitute* function. This function takes the current intermediate signature and one gate equation encountered as input parameters. After a *target variable* is completely substituted, it will return a new simplified intermediate

signature to the next call. After all gate equations in the equation file are exhausted, the returned signature will be the computed input signature for the given output signature and gate equations. The pseudo code for the *clean substitute* function is shown below.

```

Input: one intermediate signature, one gate equation

Output: a new signature after substitution and proper cancellation

// Preparation step:

1 simplify given signature to DNF: // make signature canonical

// Substitution steps:

2 recognize the target variable targVar to be substituted;

3 get the polynomial needed to substitute the tarqVar;

4 for each literal in signature do

if literal == tarqVar then

substitute targVar by (polynomial);

6

end

continue to next literal;

9 end

10 simplify substituted signature and get new signature newSig;

11 return newSig;

```

Algorithm 1: *clean substitute* pseudo code.

In Algorithm 1, the *simplify* method is used to perform the term cancellation task by combining terms that have the same monomial. It is very efficiently implemented in the following fashion. In the *simplify* method, each term in the signature is stored in a dictionary with a monomial string as the key and its integer coefficient as corresponding containment. If the monomial of a term already exists in the dictionary, the coefficients are combined. For cases when monomial keys are not stored yet, a new monomial-coefficient pair will be added into the existing dictionary.

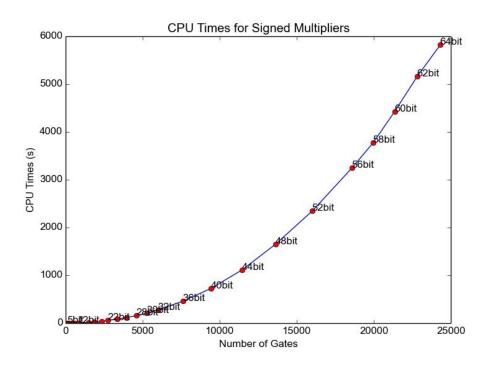

Figure 4.2: CPU times for verifying signed multipliers using *clean\_substitute*.

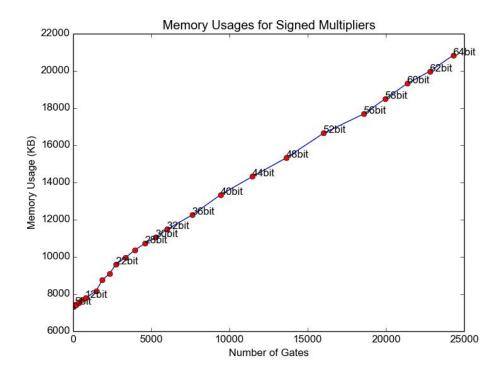

Figure 4.3: Memory usage for verifying signed multipliers using *clean\_substitute*.

We performed initial experiments on gate-level arithmetic circuits, such as multipliers. The multipliers were generated by a program Genmult [49]. The tests were run on a PC with an Intel® Core<sup>TM</sup> i5-3470 CPU @ 3.20GHz × 4 processor, 15.6 GB of memory and a 229.2 GB disk. Our preliminary experiment results are shown in Figure 4.3 and Figure 4.4.

The CPU time results for verifying the signed multipliers, shown in Figure 4.3, demonstrate quadratic dependency on the number of gates. The rudimentary implementation is able to verify signed multipliers up to 64 bits in a reasonable time. Note that the memory usages for our method is very small, less than 15MB for verifying 64-bit signed multiplier, as shown in Figure 4.4, and the main limitation is the CPU time.

Analyzing the preliminary implementation, it is obvious that the *clean\_substitute* function consumes most of the CPU time, because it will be called as many times as the number of gates in the circuit. Also it is the most complex function in the program. Since the *simplify* method in the *clean\_substitute* function is hard to be further optimized, the chance of improving the efficiency lies in modifying the overall substitution process. As shown in Algorithm 1, the substitution is achieved by comparing each literal in the signature with the *target variable*. If a match is found, the literal will be replaced by the polynomial that algebraically matches the *target variable*. Once all matches are found, the resulting signature will be simplified and returned to next step.

# 4.2 Experiments on Improved Algorithm and Result Analysis

One of the heuristics (and the only heuristic implemented up to now) described in

Section 3.2 is to keep variables binary. This means that after simplification, it is not possible to have a term like " $a \cdot a \cdot b$ ", given that a and b are both binary variables. The term  $a^k$  of a binary variable a evaluates always to a itself, so each literal in a term appears exactly once. That is, for each term in the simplified DNF expressions, it is enough to check whether the *target variable* is in the expression or not, instead of checking what every single literal is. Algorithm 2 shows the *new\_clean\_substitute* procedure obtained by modifying the substitution process in *clean substitute* function is as follows.

```

Input: one intermediate signature, one gate equation

Output: a new signature after substitution and proper cancellation

// Preparation step:

1 simplify given signature to DNF;

// make signature canonical

// Substitution steps:

2 recognize the target variable targVar to be substituted;

3 get the polynomial needed to substitute the tarqVar;

4 term_list = split_signature_to_terms;

5 for each term in term_list do

multiplier\_list = term.monomial.split(*);