## THE DEVELOPMENT OF A HIGH-PERFORMANCE DISTRIBUTED BATTERY MANAGEMENT SYSTEM FOR LARGE LITHIUM ION PACKS

A thesis presented to the Faculty of California Polytechnic State University, San Luis Obispo

In Partial Fulfillment of the Requirements for the Degree Master of Science in Electrical Engineering

> by Christopher Grasberger June 2015

© 2015 Christopher Grasberger ALL RIGHTS RESERVED

# COMMITTEE MEMBERSHIP

| TITLE:            | The Development of a High-Performance Distributed<br>Battery Management System for Large Lithium Ion Packs |

|-------------------|------------------------------------------------------------------------------------------------------------|

| AUTHOR:           | Christopher Grasberger                                                                                     |

| DATE SUBMITTED:   | June 2015                                                                                                  |

| COMMITTEE CHAIR:  | Dr. Dale Dolan, Ph.D<br>Associate Professor<br>Dept. of Electrical Engineering                             |

| COMMITTEE MEMBER: | Dr. Taufik, Ph.D<br>Professor, Director of Electric Power Institute<br>Dept. of Electrical Engineering     |

| COMMITTEE MEMBER: | Dr. Ali Shaban, Ph.D<br>Professor<br>Dept. of Electrical Engineering                                       |

### ABSTRACT

### The Development of a High-Performance Distributed Battery Management System for Large Lithium Ion Packs

### Christopher Grasberger

A high performance battery management system (BMS) for large capacity cells was designed, built, and tested in a cycle of three revisions. The BMS was designed for use in applications where the battery pack configuration is unknown: parallel, series, or any combination. Each of the cells is equipped with its own battery management system to allow a peer-to-peer mesh network to monitor the safety of the cell. The BMS attached to each cell also is equipped with a 25A DC/DC converter to perform active balancing between cells in a string. This converter can transfer charge to (or from) a cell of higher potential and a cell of lower potential at the same time. The balancing circuit has a peak efficiency of 85.3%. The system draws only 53mA while balancing at 25A helping to increase low current performance. The system draws just under 5mA over all while active. Each BMS is equipped with one current sensor, which can measure  $\pm 800A$  with a second  $\pm 120A$  current range. Additionally, the board is equipped with coulomb counting to provide a better understanding of each cell.

While this design has many great features, lack of full software support makes many of the subsystems dependent on user interaction to use. As a result, the design is not fully complete. Additionally, last minute design changes on the final revision resulted in detrimental effects to the accuracy of many of the analog circuits including the current sensing features.

## ACKNOWLEDGMENTS

I would like to acknowledge the support that everyone gave me while working on this project. Additionally, I thank everyone for not dashing my hopes of completing something much larger than I was capable of completing; it was an enjoyable challenge to try and complete it all.

| LIST OF TABLESx                                  |

|--------------------------------------------------|

| LIST OF FIGURESxi                                |

| LIST OF EQUATIONSxix                             |

| CHAPTER 1 - INTRODUCTION1                        |

| 1.1 BATTERY MANAGEMENT2                          |

| 1.2 GOALS                                        |

| CHAPTER 2 - LITERATURE REVIEW7                   |

| CHAPTER 3 - DESIGN                               |

| 3.1 ELECTRICAL HARDWARE12                        |

| 3.1.1 SYSTEM VOLTAGE AND POWER14                 |

| 3.1.2 ANALOG SUPPLIES                            |

| 3.1.3 MEASUREMENT19                              |

| 3.1.3.A BATTERY VOLTAGE                          |

| 3.1.3.B BATTERY CURRENT                          |

| 3.1.3.C COULOMB COUNTING                         |

| 3.1.3.D OVER-CHARGE AND OVER DISCHARGE DETECTION |

| 3.1.3.E CURRENT PULSE                            |

| 3.1.3.F EXTERNAL TEMPERATURE SENSOR              |

| 3.1.4 ACTIVE BALANCER DC/DC DESIGN               |

| 3.1.4.A DC/DC DESIGN EQUATION DEVELOPMENT        |

| 3.1.4.B DC/DC CURRENT MEASUREMENT                |

| 3.1.5 SAFETY                                     |

# TABLE OF CONTENTS

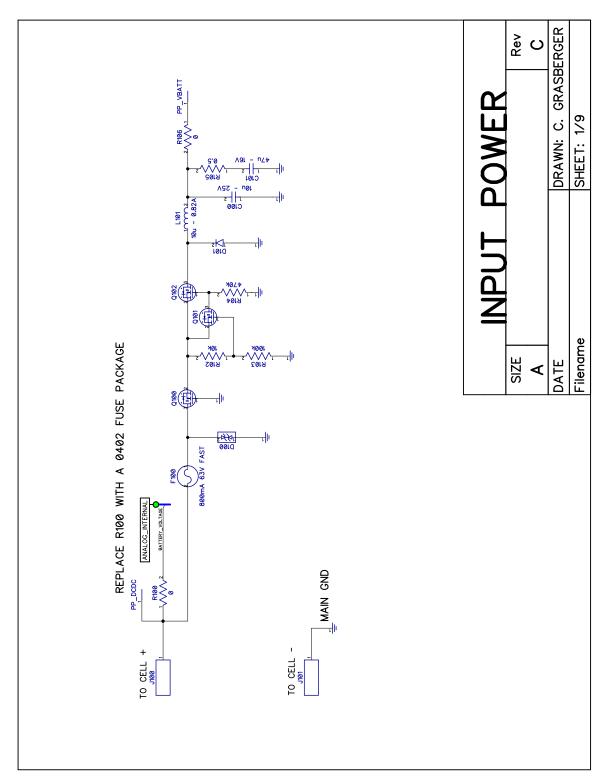

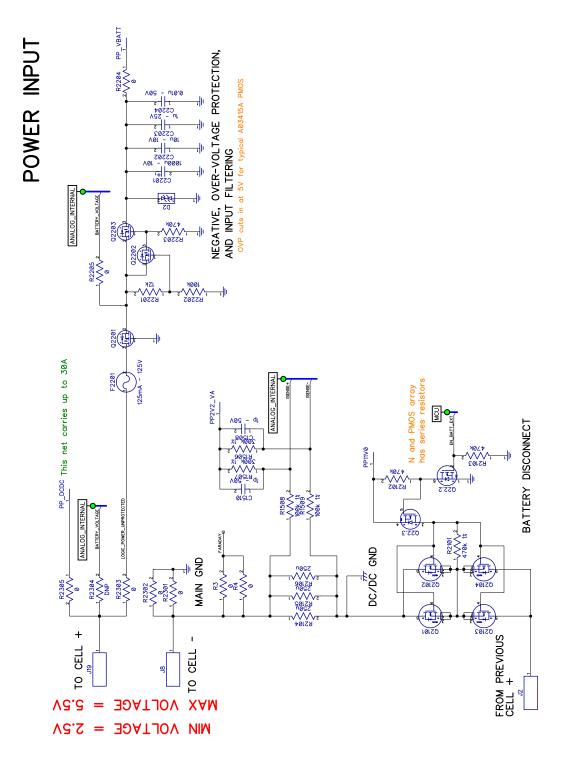

| 3.1.6 INPUT POWER                               | 54  |

|-------------------------------------------------|-----|

| 3.1.7 OTHER ELECTRICAL DESIGN CONSIDERATIONS    | 56  |

| 3.1.7.A INPUT VOLTAGE RANGE                     | 56  |

| 3.1.7.B COMMUNICATION                           | 57  |

| 3.1.7.C PCB                                     | 59  |

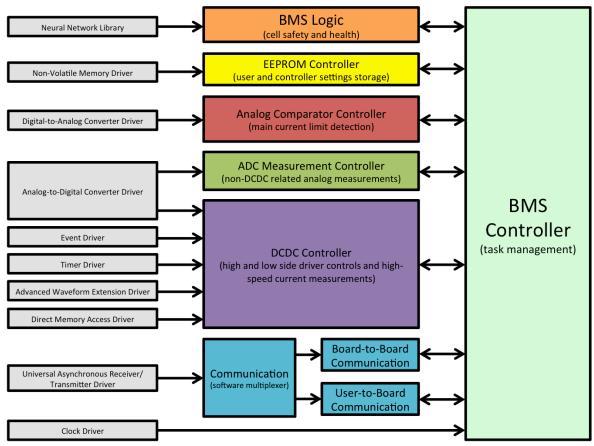

| 3.2 SOFTWARE                                    | 63  |

| 3.2.1 TASK MANAGEMENT                           | 65  |

| 3.2.2 LOGIC CONTROLLER                          | 66  |

| 3.2.3 DC/DC CONTROLLER                          | 67  |

| 3.2.4 ADC CONTROLLER                            | 69  |

| 3.2.5 ANALOG COMPARATOR CONTROLLER              | 69  |

| 3.2.6 COMMUNICATION CONTROLLER                  | 70  |

| 3.2.6.A EXTERNAL COMMUNICATION (USER INTERFACE) | 73  |

| 3.3 MECHANICAL                                  | 77  |

| CHAPTER 4 – RESULTS AND VERIFICATION            | 83  |

| 4.1 MEASUREMENT CIRCUITS                        | 83  |

| 4.1.1 BATTERY VOLTAGE                           | 83  |

| 4.1.2 CURRENT MEASUREMENT                       | 85  |

| 4.1.3 COULOMB COUNTING                          | 94  |

| 4.1.4 CURRENT PULSE                             | 95  |

| 4.1.5 TEMPERATURE SENSOR                        | 97  |

| 4.2 ACTIVE BALANCING DC/DC CONVERTER            | 99  |

| 4.3 INPUT POWER AND SUPPLIES                    | 104 |

| 4.3.1 SYSTEM POWER MEASUREMENTS        | 104 |

|----------------------------------------|-----|

| 4.3.2 INPUT FILTER                     | 107 |

| 4.3.3 INPUT PROTECTION                 | 108 |

| 4.3.4 BOOST EFFICIENCY                 | 109 |

| 4.3.5 ANALOG POWER FILTER              | 111 |

| 4.4 COMMUNICATIONS                     | 113 |

| CHAPTER 5 – CONCLUSION AND FUTURE WORK | 116 |

| 5.1 HARDWARE                           | 118 |

| 5.2 SOFTWARE                           | 120 |

| REFERENCES                             | 121 |

| APPENDICES                             |     |

| A. SYSTEM OVERVIEW                     | 123 |

| A.1 POWER DISTRIBUTION                 |     |

| B. SCHEMATIC (REVISION C)              | 124 |

| C. PRINTED CIRCUIT BOARD (REVISION C)  | 134 |

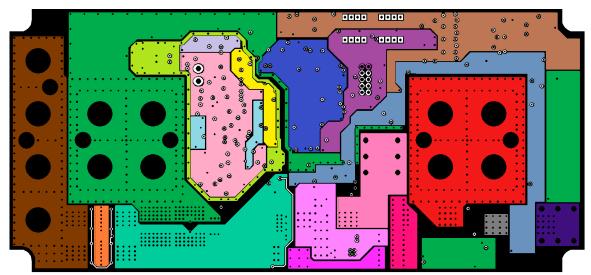

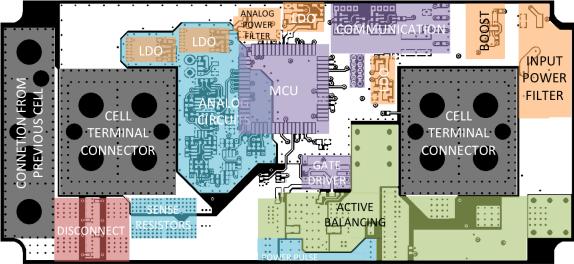

| C.1 HIGHLIGHTED AREAS                  | 134 |

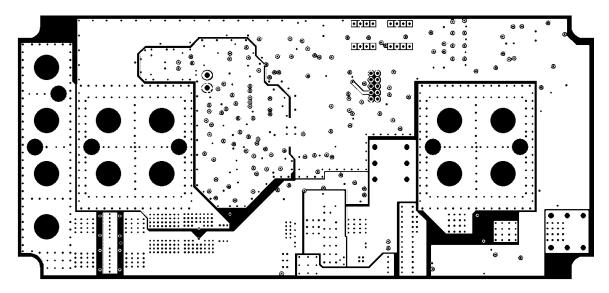

| C.1.1 TOP LAYER                        | 134 |

| C.1.2 BOTTOM LAYER                     | 134 |

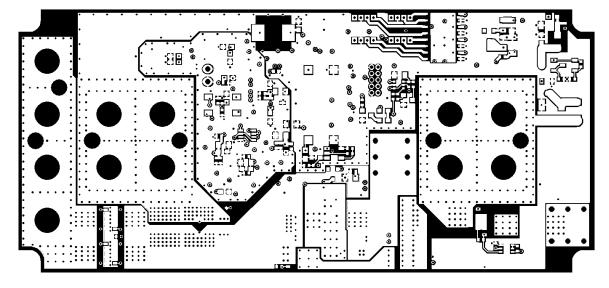

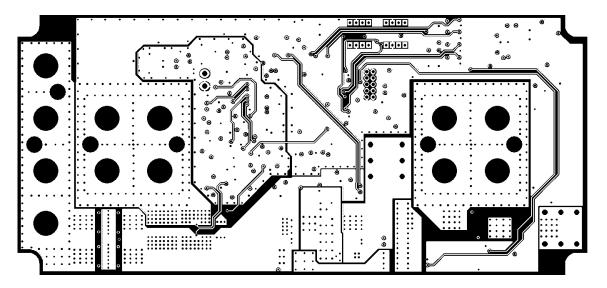

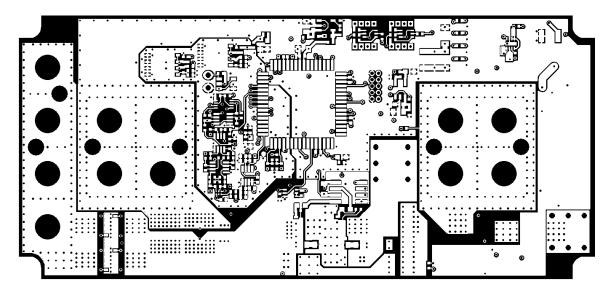

| C.2 PLAIN GERBER                       | 135 |

| C.2.1 TOP – SIGNAL & COMPONENTS        | 135 |

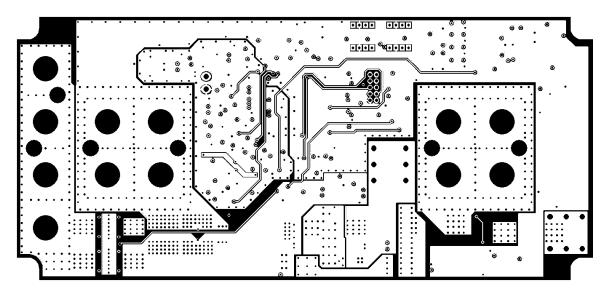

| C.2.2 ISL2 – SIGNAL                    | 135 |

| C.2.3 ISL3 – POWER                     | 136 |

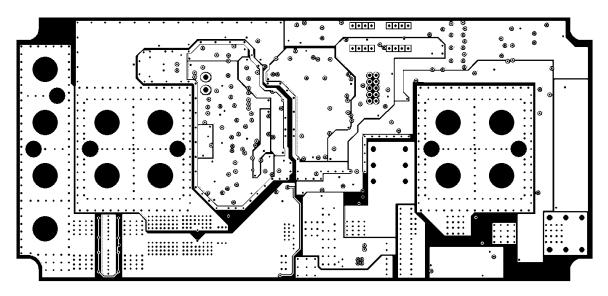

| C.2.4 ISL4 – GROUND                    |     |

| C.2.5 ISL5 – SIGNAL                               | 137 |

|---------------------------------------------------|-----|

| C.2.6 BOTTOM – SIGNAL & COMPONENTS                | 137 |

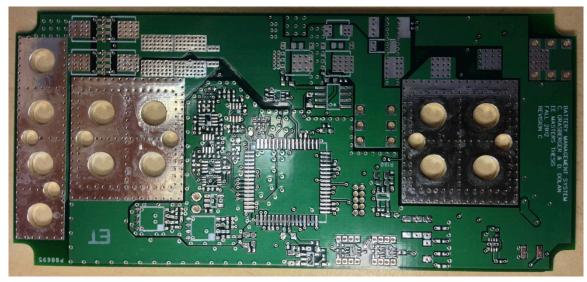

| C.3 REVISION C PCB PHOTOS                         | 138 |

| D. BILL OF MATERIALS (REVISION C)                 | 140 |

| E. SUB SYSTEM RAW DATA                            | 142 |

| E.1 CURRENT SENSE AMPLIFIER                       | 142 |

| E.2 POWER MEASUREMENTS                            | 144 |

| E.3 DC/DC CONVERTER MEASUREMENTS                  | 145 |

| F. COMMUNICATION                                  | 146 |

| F.1 EXTERNAL COMMANDS (USER INTERFACE)            | 146 |

| F.2 INTERNAL COMMANDS                             | 147 |

| G. REVISION B                                     | 148 |

| G.1 SCHEMATIC                                     | 149 |

| G.2 BILL OF MATERIALS                             | 156 |

| H. REVISION A                                     | 158 |

| H.1 SCHEMATIC                                     | 159 |

| H.2 BILL OF MATERIALS                             | 164 |

| I. CALCULATION                                    | 165 |

| I.1 DC/DC CONVERTER'S MODES OF OPERATION          | 165 |

| I.2 GAINS AND OFFSETS OF CURRENT MEASUREMENT PATH | 170 |

| LIST | OF | TAI | BLES |

|------|----|-----|------|

|------|----|-----|------|

| TABLE 4.1 – SENSE RESISTOR MEASUREMENTS                                                          | 87  |

|--------------------------------------------------------------------------------------------------|-----|

| TABLE 4.2 – SUMMARY OF CURRENT SENSE AMPLIFIER OFFSETS AND GAINS.                                | 89  |

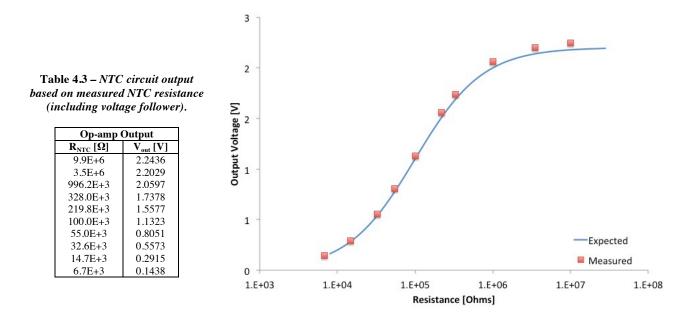

| TABLE 4.3 – NTC CIRCUIT OUTPUT BASED ON MEASURED NTC<br>RESISTANCE (INCLUDING VOLTAGE FOLLOWER)  | 98  |

| TABLE 4.4 – SUMMARY OF POWER CONSUMPTION                                                         | 105 |

| TABLE 4.5 – BREAKDOWN OF ANALOG CURRENT SINKS BASED OFF OF<br>IC DATA SHEETS.                    | 106 |

| TABLE 5.1 – THIS TABLE OUTLINES THE GOALS AND THEIR<br>CURRENTLY MEASURED VALUES IN REVISION C   | 117 |

| TABLE 7.1 – REVISION C BILL OF MATERIALS                                                         | 140 |

| TABLE 7.2 – DC RESPONSE FROM ±800 AND ±120A CURRENT RANGES                                       | 142 |

| TABLE 7.3 – RANDOM SAMPLES FROM ±120A CURRENT RANGE AFTER<br>CALIBRATION. ALL UNITS ARE IN AMPS. | 143 |

| TABLE 7.4 – FREQUENCY RESPONSE OF INPUT POWER FILTER                                             | 144 |

| TABLE 7.5 – FREQUENCY RESPONSE OF ANALOG CIRCUIT POWER<br>FILTER                                 | 144 |

| TABLE 7.6 – BOOST VOLTAGE AND CURRENT MEASUREMENTS                                               | 144 |

| TABLE 7.7 – BOOST VOLTAGE MEASUREMENTS FOR LINE<br>REGULATION CALCULATION                        | 144 |

| TABLE 7.8 – MEASUREMENTS FROM REVISION C BALANCING DC/DC CONVERTER.                              | 145 |

| TABLE 7.9 – TABLE OF BASIC COMMANDS TO CONTROL THE BMS                                           | 146 |

| TABLE 7.10 – REVISION B BILL OF MATERIALS                                                        | 156 |

| TABLE 7.11 – REVISION A BILL OF MATERIALS                                                        | 164 |

# LIST OF FIGURES

| FIGURE 1.1 – PICTURES OF A RUDIMENTARY BATTERY MANAGEMENT<br>SYSTEM ATTACHED TO LARGE CAPACITY CELLS                             | 4  |

|----------------------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 1.2 – A BATTERY PACK WITH FOUR 100AH CELLS                                                                                | 4  |

| FIGURE 2.1 – IMAGE SHOWING THE USEABLE CAPACITY OF A<br>BALANCED AND UNBALANCED BATTERY PACKED, BOTH OF THE<br>SAME CAPACITY.    | 9  |

| FIGURE 2.2 – IMAGE SHOWING THE USEABLE CAPACITY OF A<br>BALANCED AND UNBALANCED BATTERY PACKED, BOTH OF<br>DIFFERENT CAPACITIES  | 10 |

| FIGURE 2.3 – THIS FIGURE SHOWS HOW THE CURRENT FLOWS TO-<br>AND-FROM THE CELLS IN ORDER TO BALANCE THE BATTERY<br>PACK           | 11 |

| FIGURE 3.1 – PICTURE OF THE TOPSIDE OF THE DESIGNED BMS<br>MOUNTED TO A CELL.                                                    | 12 |

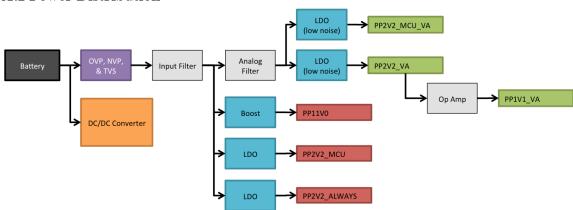

| FIGURE 3.2 - ELECTRICAL SYSTEM OVERVIEW                                                                                          | 13 |

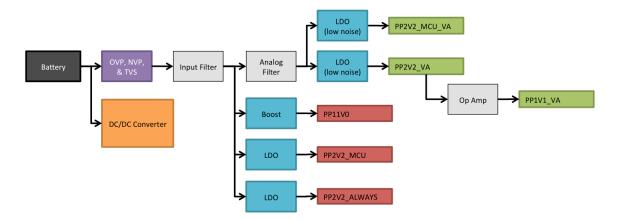

| FIGURE 3.3 - OVERVIEW OF SYSTEM SUPPLY VOLTAGES.                                                                                 | 16 |

| FIGURE 3.4 - BATTERY VOLTAGE MEASUREMENT CIRCUIT                                                                                 | 20 |

| FIGURE 3.5 – INSTRUMENTATION AMPLIFIER CIRCUIT USED TO<br>AMPLIFY VOLTAGE FROM SENSE RESISTOR.                                   | 25 |

| FIGURE 3.6 - AMPLIFIER STAGE TO ARCHIVE ±120A CURRENT RANGE                                                                      | 26 |

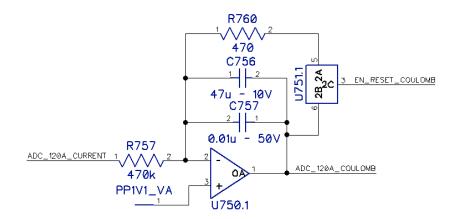

| FIGURE 3.7 - CIRCUIT DIAGRAM OF THE ±120A CURRENT RANGE'S<br>COULOMB COUNTER. THERE IS A SIMILAR CIRCUIT FOR THE<br>±800A RANGE. | 30 |

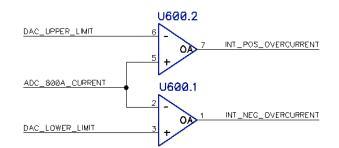

| FIGURE 3.8 – OVER DISCHARGE AND OVER CHARGE CURRENT<br>DETECTION CIRCUIT                                                         | 31 |

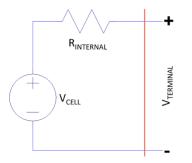

| FIGURE 3.9 – SIMPLIFIED DIAGRAM SHOWING INTERNAL CELL<br>VOLTAGE VERSUS TERMINAL VOLTAGE                                         | 32 |

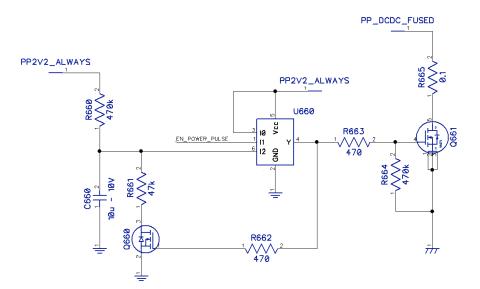

| FIGURE 3.10 – POWER PULSE CIRCUIT WITH TIMEOUT TO PREVENT<br>DAMAGE TO POWER RESISTOR.                                           | 33 |

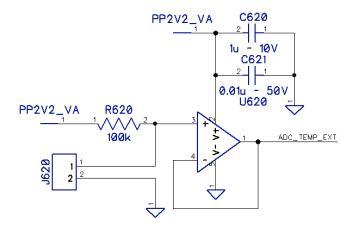

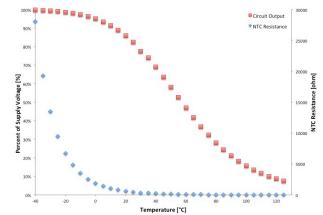

| FIGURE 3.11 – SCHEMATIC VOLTAGE FOLLOWER USED TO BUFFER<br>VOLTAGE DIVIDER WITH THERMISTOR                                                                                                                             | 35 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 3.12 – PLOT OF THERMISTOR (NTC RESISTOR) VERSUS<br>TEMPERATURE AND PERCENT OF VOLTAGE SUPPLY FROM<br>DIVIDED VOLTAGE                                                                                            | 35 |

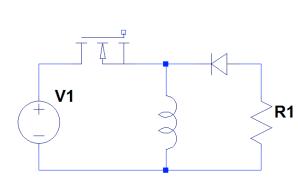

| FIGURE 3.13 – SCHEMATIC OF A BASIC BUCK-BOOST DC/DC<br>CONVERTER.                                                                                                                                                      | 36 |

| FIGURE 3.14 – BASIC SCHEMATIC OF SYNCHRONOUS BUCK-BOOST<br>USED TO TRANSFER CHARGE FROM CELL TO CELL                                                                                                                   | 36 |

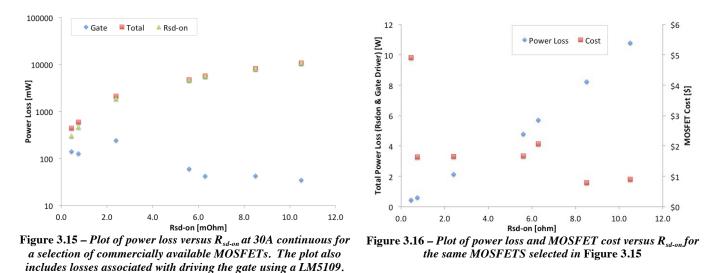

| FIGURE 3.15 – PLOT OF POWER LOSS VERSUS R <sub>SD-ON</sub> AT 30A<br>CONTINUOUS FOR A SELECTION OF COMMERCIALLY AVAILABLE<br>MOSFETS. THE PLOT ALSO INCLUDES LOSSES ASSOCIATED WITH<br>DRIVING THE GATE USING A LM5109 | 38 |

| FIGURE 3.16 – PLOT OF POWER LOSS AND MOSFET COST VERSUS R <sub>SD-ON</sub><br>FOR THE SAME MOSFETS SELECTED IN FIGURE 3-15                                                                                             | 38 |

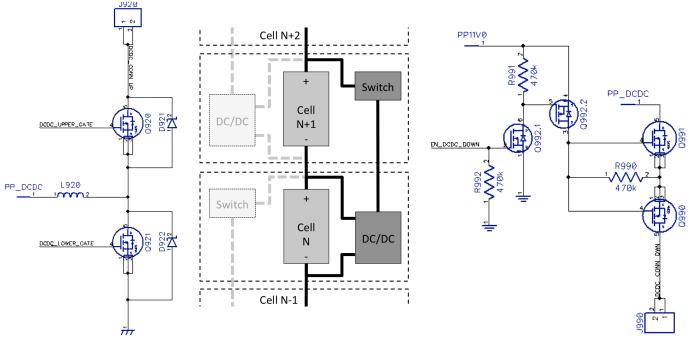

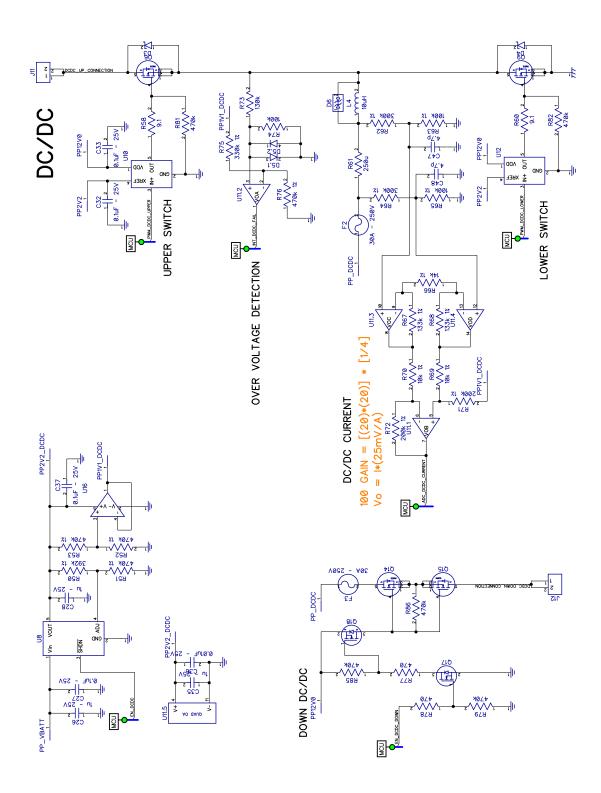

| FIGURE 3.17 – THIS FIGURE SHOWS THE SUB CIRCUITS THAT CONNECT<br>TOGETHER TO MAKE THE ACTIVE BALANCING DC/DC<br>CONVERTER.                                                                                             | 40 |

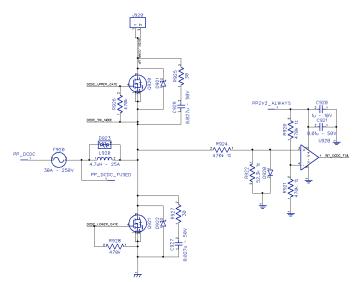

| FIGURE 3.18 – COMPLETE SCHEMATIC OF THE BUCK-BOOST<br>SWITCHES, SNUBBERS, AND DISCONNECT PROTECTION                                                                                                                    | 42 |

| FIGURE 3.19 - CIRCUIT OF SYNCHRONOUS BUCK-BOOST                                                                                                                                                                        | 43 |

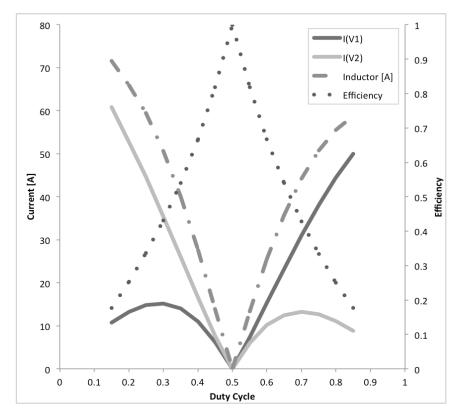

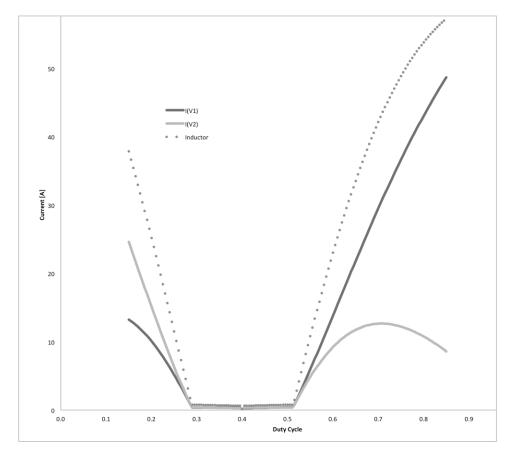

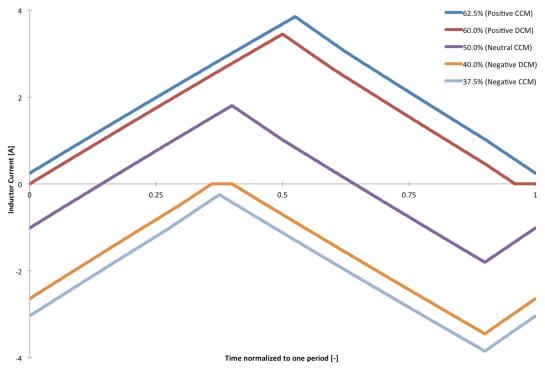

| FIGURE 3.20 – PLOT OF INDUCTOR CURRENT, V1 AND V2 CURRENT,<br>AND EFFICIENCY VERSUS DUTY CYCLE. ALL VALUES ARE<br>ABSOLUTE VALUES. V1 = V2 = $3.3$ V. R1 = $53$ M $\Omega$ , R2 = $43$ M $\Omega$                      | 45 |

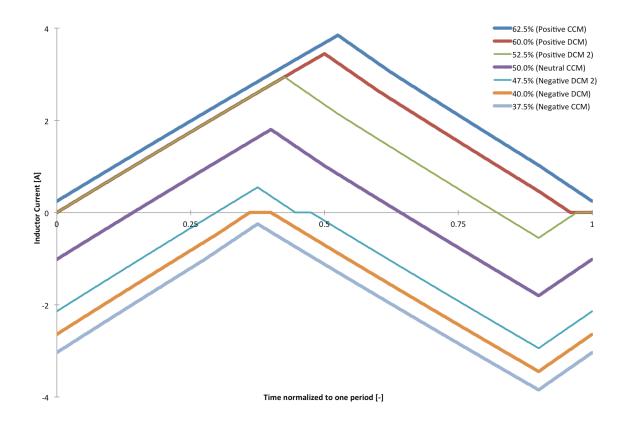

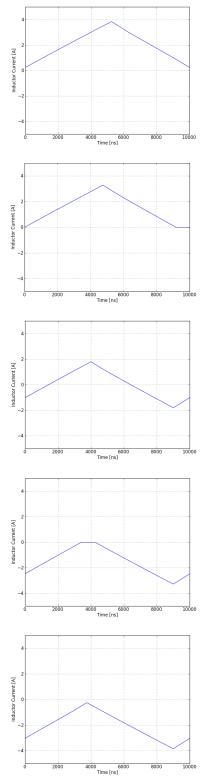

| FIGURE 3.21 – PLOT OF ALL SEVEN MODES OF OPERATION OF THE DC/DC CONVERTER.                                                                                                                                             | 47 |

| FIGURE 3.22 – FIVE MODES THAT THE SYNCHRONOUS BI-<br>DIRECTIONAL BUCK-BOOST CAN OPERATE IN                                                                                                                             | 48 |

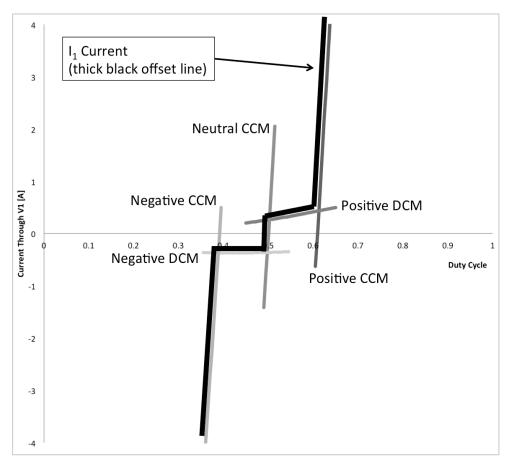

| FIGURE 3.23 – PLOT OF AVERAGE CURRENT THROUGH SUPPLY 1<br>VERSUS DUTY CYCLE THROUGH ALL FIVE MODES OF OPERATION<br>SHOWN IN FIGURE 3-22. THE BOLD LINE IS OFFSET TO MAKE IT<br>EASIER TO SEE.                          | 49 |

| FIGURE 3.24 – PLOT OF INDUCTOR CURRENT, V1, AND V2 CURRENT<br>VERSUS DUTY CYCLE. ALL VALUES ARE ABSOLUTE VALUES. V1<br>= V2 = 3.3V. R1 = 53 M $\Omega$ , R2 = 43 M $\Omega$ , A = 10%, L = 10MH, F = 100KHZ            | 50 |

| FIGURE 3.25 – SCHEMATIC OF THE EMERGENCY DISCONNECT SWITCH53                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

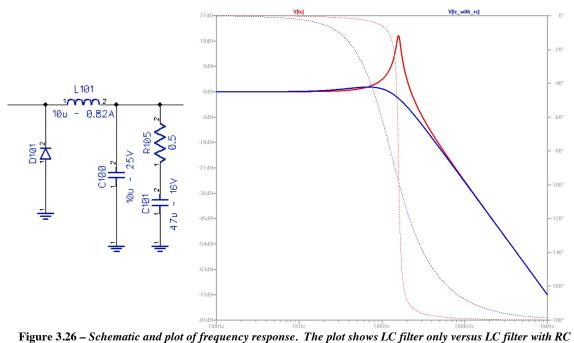

| FIGURE 3.26 – SCHEMATIC AND PLOT OF FREQUENCY RESPONSE. THE<br>PLOT SHOWS LC FILTER ONLY VERSUS LC FILTER WITH RC<br>DAMPING                                                                                                                            |

| FIGURE 3.27 – SCHEMATIC OF OVER-VOLTAGE AND NEGATIVE<br>VOLTAGE PROTECTION ON INPUT                                                                                                                                                                     |

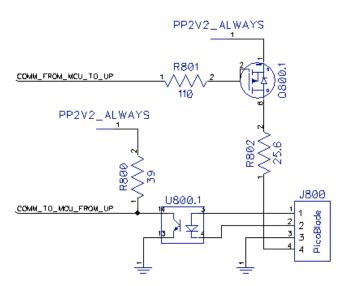

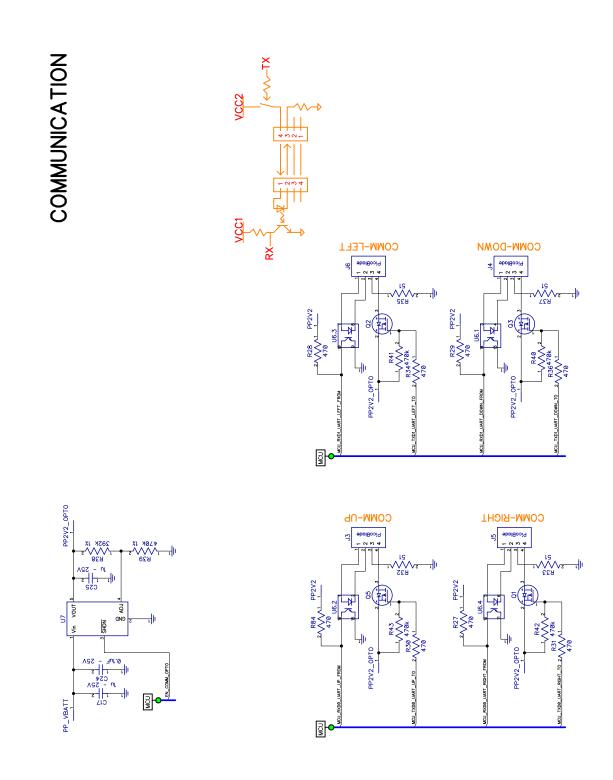

| FIGURE 3.28 – SCHEMATIC OF SINGLE CHANNEL TRANSMITTER AND<br>RECEIVER FOR ISOLATED COMMUNICATION                                                                                                                                                        |

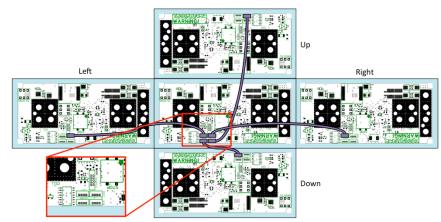

| FIGURE 3.29 – MULTIPLE BOARD COMMUNICATION WIRING DIAGRAM59                                                                                                                                                                                             |

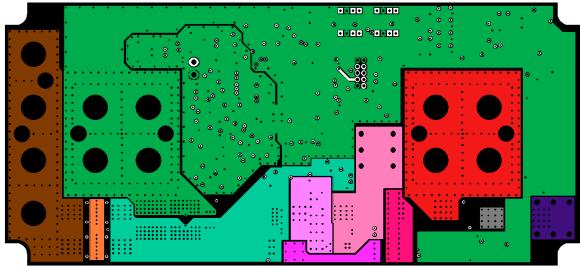

| FIGURE 3.30 – A SCREEN CAPTURE OF THE GROUND PLANE LAYER<br>(ISL4). THE ANALOG AND DIGITAL GROUNDS ARE MERGED ON<br>THIS PLANE. GREEN SHOWS GROUND. THE HIGH CURRENT<br>AREAS DID NOT HAVE GROUND FILL, HOWEVER THE TEAL AREA<br>IS SIMILAR TO A GROUND |

| FIGURE 3.31 – A SCREEN CAPTURE OF THE POWER PLAY LAYER (ISL3).<br>DARK GREEN IS DIGITAL GROUND. PALE GREEN IS ANALOG<br>GROUND                                                                                                                          |

| FIGURE 3.32 – BLOCK DIAGRAM OF SOFTWARE DESIGN                                                                                                                                                                                                          |

| FIGURE 3.33 – EXAMPLE OF COMMUNICATION BETWEEN TWO<br>BOARDS                                                                                                                                                                                            |

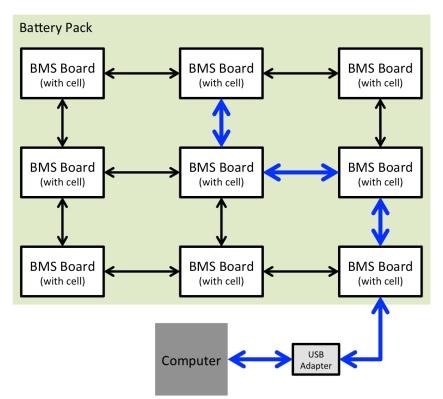

| FIGURE 3.34 – DIAGRAM OF SHOWING HOW THE COMMUNICATION<br>NETWORK CAN TRANSFER DATA                                                                                                                                                                     |

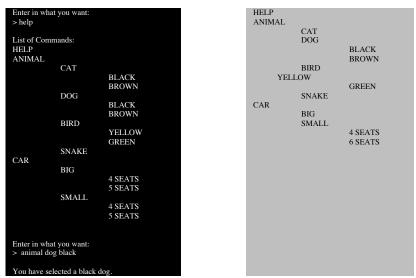

| FIGURE 3.35 – EXAMPLE SHOWING HOW THE USER INTERFACE TREE-<br>STRUCTURE IS SET UP                                                                                                                                                                       |

| FIGURE 3.36 – A SECTION OF THE CONFIGURATION CODE SHOWING<br>THE TREE-STRUCTURE THAT WAS DESCRIBED IN FIGURE 3-3575                                                                                                                                     |

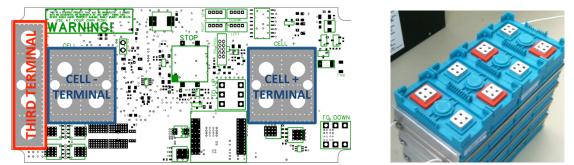

| FIGURE 3.37 – IMAGE SHOWING WHERE THE CELL TERMINAL<br>CONNECTS TO THE BOARD AND WHERE THE THIRD TERMINAL IS<br>TO UTILIZE THE EMERGENCY DISCONNECT SWITCH                                                                                              |

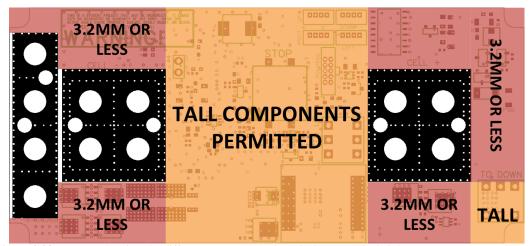

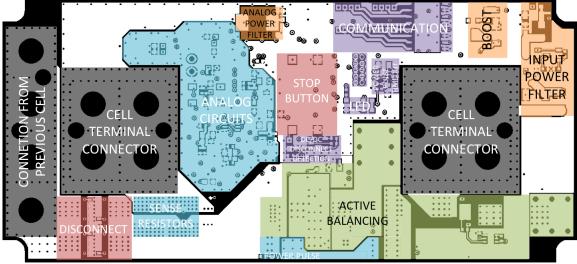

| FIGURE 3.38 – IMAGE SHOWING THE DIFFERENT ZONES ON THE<br>BOARD WHERE CERTAIN HEIGHT COMPONENTS WERE ALLOWED80                                                                                                                                          |

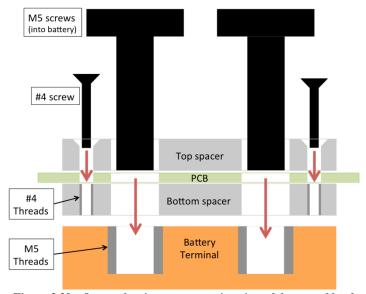

| FIGURE 3.39 – IMAGE SHOWING A CROSS-SECTION VIEW OF THE<br>ASSEMBLY OF SPACERS, PCB, AND BATTERY TO REACH THE<br>CORRECT HEIGHT                                                                                                                         |

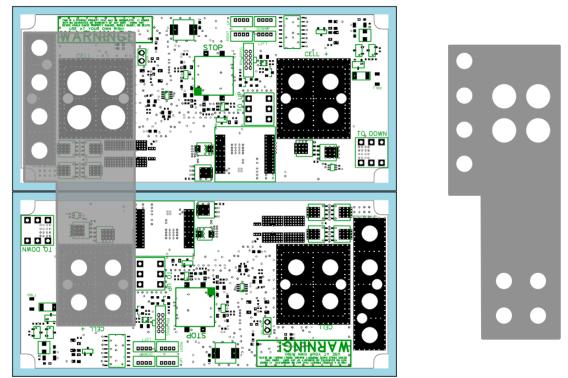

| FIGURE 3.40 – IMAGE SHOWING HOW A BUSBAR CONNECTS THE<br>THIRD TERMINAL OF ONE CELL AND THE POSITIVE TERMINAL OF<br>THE OTHER CELL. | 82 |

|-------------------------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 4.1 – BATTERY CELL MEASUREMENT CIRCUIT (SAME AS FIGURE 3-4).                                                                 | 83 |

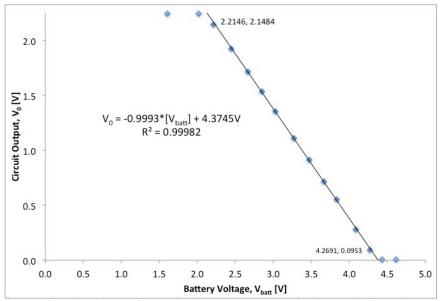

| FIGURE 4.2 – PLOT OF OUTPUT FROM CELL VOLTAGE MEASUREMENT<br>CIRCUIT AS CELL VOLTAGE CHANGES.                                       | 84 |

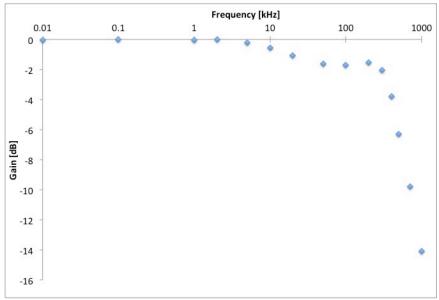

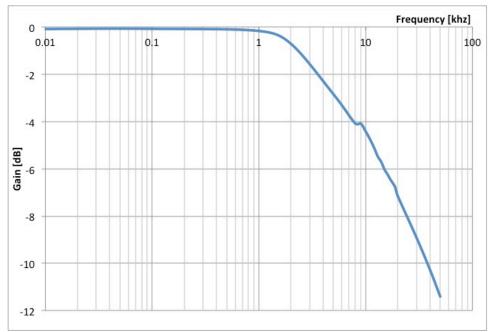

| FIGURE 4.3 – PLOT OF THE FREQUENCY RESPONSE OF CELL VOLTAGE<br>MEASUREMENT CIRCUIT                                                  | 85 |

| FIGURE 4.4 – 250MΩ SENSE RESISTOR (SIZE 2725) ON A PENNY                                                                            | 86 |

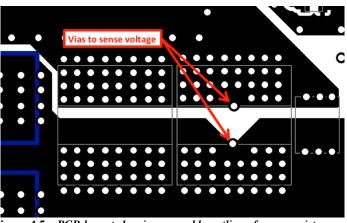

| FIGURE 4.5 – PCB LAYOUT SHOWING ASSEMBLY OUTLINE OF SENSE<br>RESISTORS AND SENSING VIAS                                             | 86 |

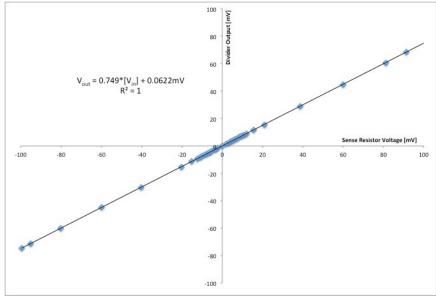

| FIGURE 4.6 – OUTPUT OF VOLTAGE DIVIDER FOR CURRENT SENSE<br>RESISTOR.                                                               | 87 |

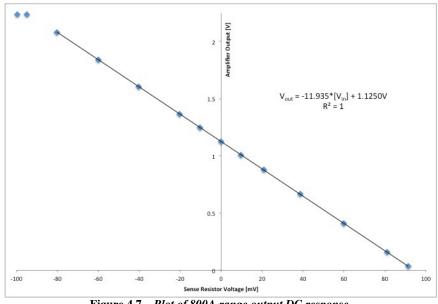

| FIGURE 4.7 – PLOT OF 800A RANGE OUTPUT DC RESPONSE                                                                                  | 88 |

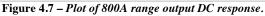

| FIGURE 4.8 – PLOT OF 120A RANGE OUTPUT DC RESPONSE                                                                                  | 89 |

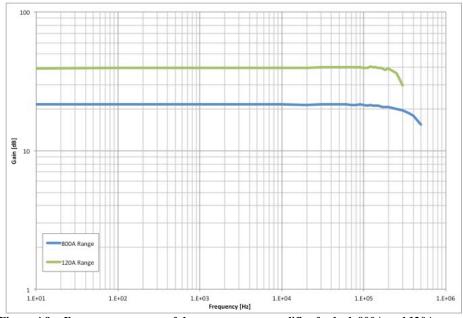

| FIGURE 4.9 – FREQUENCY RESPONSE OF THE CURRENT SENSE<br>AMPLIFIER FOR BOTH 800A AND 120A RANGE                                      | 91 |

| FIGURE 4.10 – SCREEN CAPTURE OF RIPPLE ON PP2V2_VA SUPPLY<br>OUTPUT.                                                                | 91 |

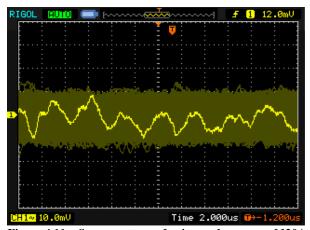

| FIGURE 4.11 – SCREEN CAPTURE OF NOISE ON THE OUTPUT OF 120A<br>RANGE FROM 0A INPUT CURRENT. AC COUPLING IS ON                       | 92 |

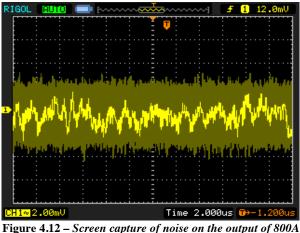

| FIGURE 4.12 – SCREEN CAPTURE OF NOISE ON THE OUTPUT OF 800A<br>RANGE FROM 0A INPUT CURRENT. AC COUPLING IS ON                       | 92 |

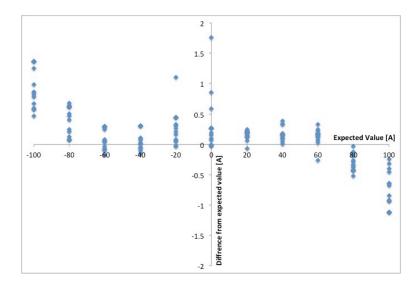

| FIGURE 4.13 – PLOT OF DIFFERENCE FROM MEASURED VALUE AND<br>EXPECTED VALUE FOR THE CALIBRATED ±120A CURRENT RANGE                   | 93 |

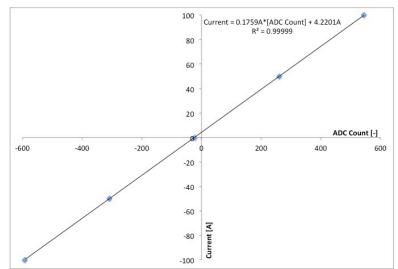

| FIGURE 4.14 – PLOT OF RANDOMLY SAMPLED DATA'S LINEAR<br>REGRESSION FOR COMPARISON WITH BMS'S CALCULATED<br>REGRESSION               | 94 |

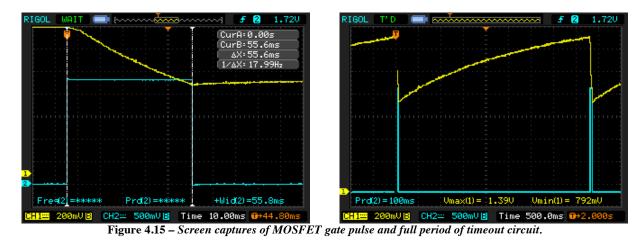

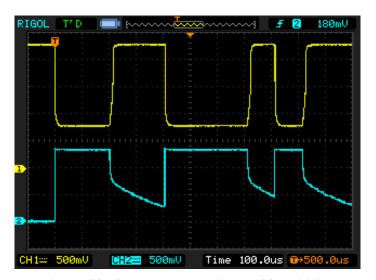

| FIGURE 4.15 – SCREEN CAPTURES OF MOSFET GATE PULSE AND FULL<br>PERIOD OF TIMEOUT CIRCUIT                                            | 96 |

| FIGURE 4.16 – PLOT OF OUTPUT VOLTAGE FROM NTC CIRCUIT VERSUS<br>NTC RESISTANCE.                                                                        | 98  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

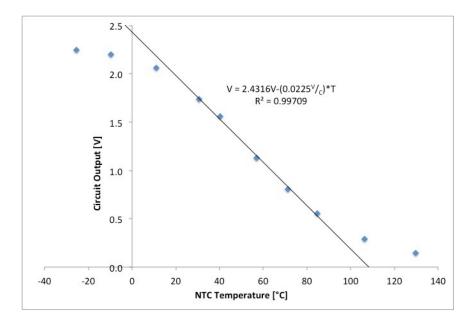

| FIGURE 4.17 – PLOT OF OUTPUT VOLTAGE FROM NTC CIRCUIT VERSUS<br>TEMPERATURE.                                                                           | 99  |

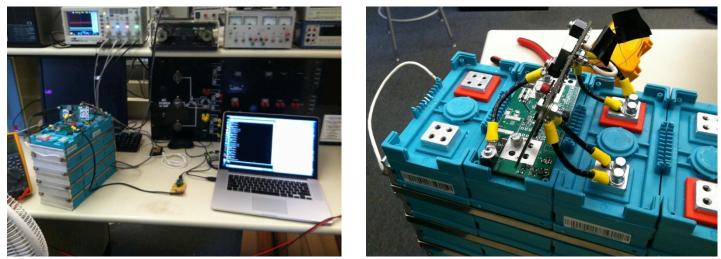

| FIGURE 4.18 – TEST SETUP TO MEASURE DC/DC CONVERTER<br>EFFICIENCY.                                                                                     | 100 |

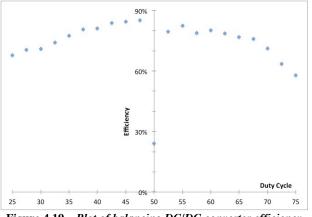

| FIGURE 4.19 – PLOT OF BALANCING DC/DC CONVERTER EFFICIENCY<br>VERSUS SET DUTY CYCLE                                                                    | 101 |

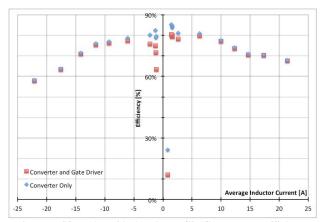

| FIGURE 4.20 – PLOT OF BALANCING DC/DC CONVERTER EFFICIENCY<br>VERSUS AVERAGE INDUCTOR CURRENT                                                          | 101 |

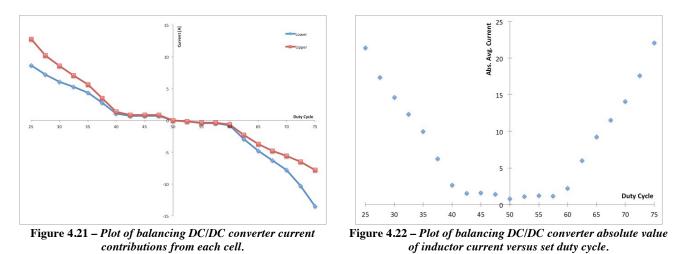

| FIGURE 4.21 – PLOT OF BALANCING DC/DC CONVERTER CURRENT<br>CONTRIBUTIONS FROM EACH CELL                                                                | 102 |

| FIGURE 4.22 – PLOT OF BALANCING DC/DC CONVERTER ABSOLUTE<br>VALUE OF INDUCTOR CURRENT VERSUS SET DUTY CYCLE                                            | 102 |

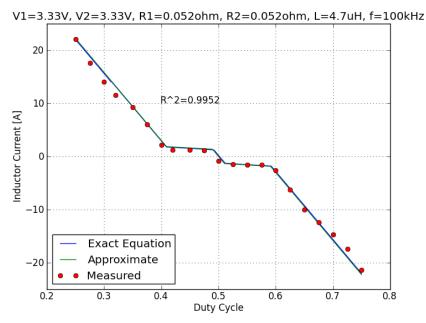

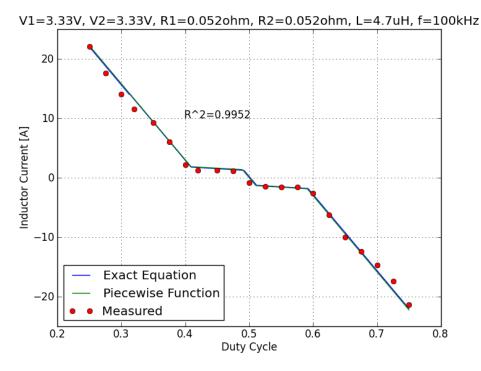

| FIGURE 4.23 – PLOT OF MEASURED DATA COMPARED WITH EXACT<br>EQUATIONS AND APPROXIMATE EQUATIONS                                                         | 103 |

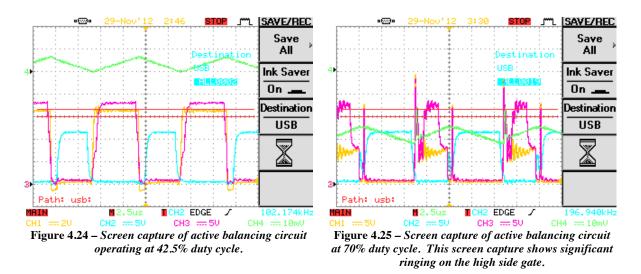

| FIGURE 4.24 – SCREEN CAPTURE OF ACTIVE BALANCING CIRCUIT<br>OPERATING AT 42.5% DUTY CYCLE                                                              | 103 |

| FIGURE 4.25 – SCREEN CAPTURE OF ACTIVE BALANCING CIRCUIT AT<br>70% DUTY CYCLE. THIS SCREEN CAPTURE SHOWS SIGNIFICANT<br>RINGING ON THE HIGH SIDE GATE. | 103 |

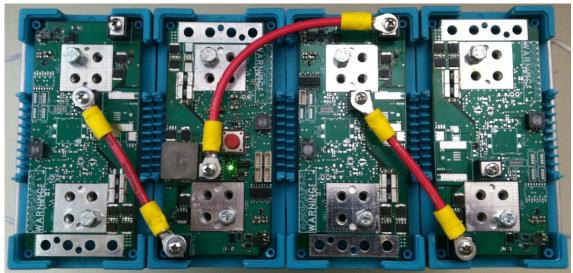

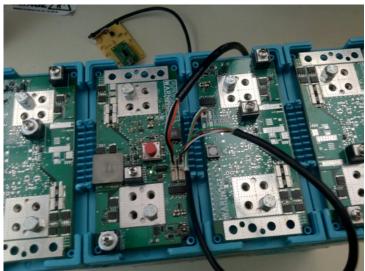

| FIGURE 4.26 – PICTURE OF FOUR PCBS MOUNTED ON TOP OF THE<br>BATTERY PACK. NOT ALL COMPONENTS ARE POPULATED                                             | 104 |

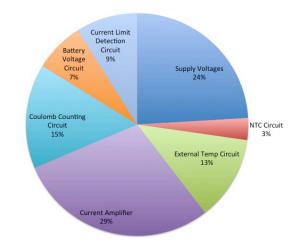

| FIGURE 4.27 – PIE CHART SHOWING SINKS OF ANALOG SUPPLY<br>(PP2V2_VA) CURRENT CONSUMPTION                                                               | 106 |

| FIGURE 4.28 – PLOT OF FREQUENCY RESPONSE OF INPUT POWER<br>FILTER                                                                                      | 107 |

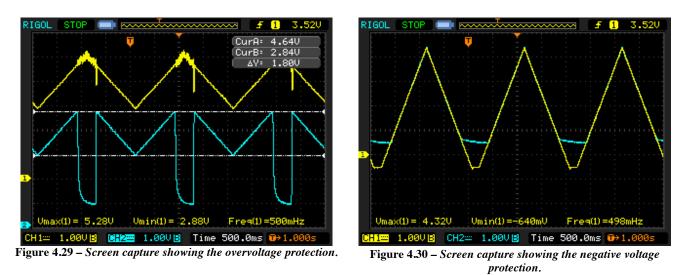

| FIGURE 4.29 – SCREEN CAPTURE SHOWING THE OVERVOLTAGE<br>PROTECTION.                                                                                    | 109 |

| FIGURE 4.30 – SCREEN CAPTURE SHOWING THE NEGATIVE VOLTAGE<br>PROTECTION.                                                                               | 109 |

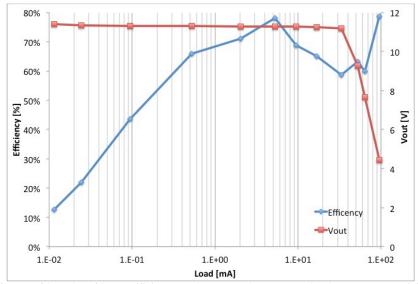

| FIGURE 4.31 – PLOT OF BOOST EFFICIENCY AND OUTPUT VOLTAGE VERSUS LOAD CURRENT. $V_{IN} = 3.3V$                                                         | 111 |

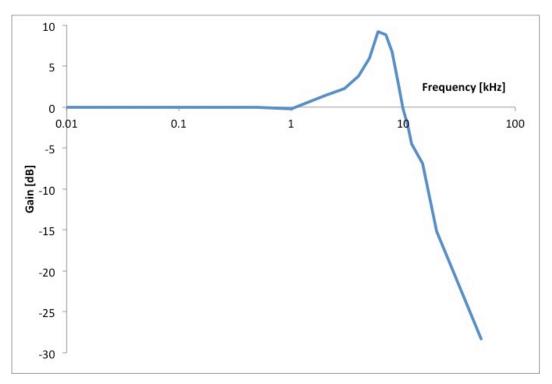

| FIGURE 4.32 – PLOT OF FREQUENCY RESPONSE OF ANALOG CIRCUIT<br>POWER FILTER                                                                                                                   | 112 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

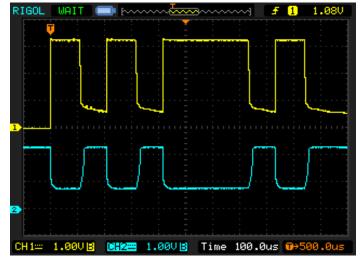

| FIGURE 4.33 – SCREEN CAPTURE SHOWING AN ASCII 'F' BEING<br>COMMUNICATED FROM BOARD TO BOARD. CHANNEL 1 IS THE<br>OUTPUT PHOTOTRANSISTOR VOLTAGE AND CHANNEL 2 IS THE<br>INPUT DIODE VOLTAGE. | 114 |

| FIGURE 4.34 – SCREEN CAPTURE SHOWING AN ASCII 'E' BEING<br>COMMUNICATED FROM COMPUTER TO BOARD. CHANNEL 1 IS<br>INPUT DIODE VOLTAGE AND CHANNEL 2 IS THE OUTPUT<br>PHOTOTRANSISTOR VOLTAGE.  | 114 |

| FIGURE 4.35 – PICTURE OF A BMS BOARD CONNECTED TO COMPUTER<br>AND TO ADJACENT BMS BOARD.                                                                                                     | 115 |

| FIGURE 4.36 – PICTURE OF THE COMPUTER-TO-BMS INTERFACE<br>BOARD.                                                                                                                             | 115 |

| FIGURE 7.1 – SYSTEM OVERVIEW OF THE DESIGN. SHOWS<br>CONNECTIONS TO ADJACENT CELLS                                                                                                           | 123 |

| FIGURE 7.2 – OVERVIEW OF SUPPLY VOLTAGE GENERATION                                                                                                                                           | 123 |

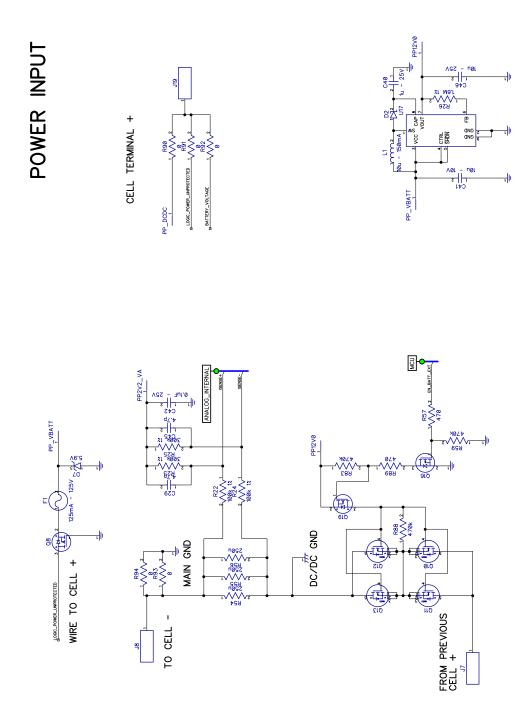

| FIGURE 7.3 – REVISION C SCHEMATIC – PAGE 1 – INPUT POWER                                                                                                                                     | 124 |

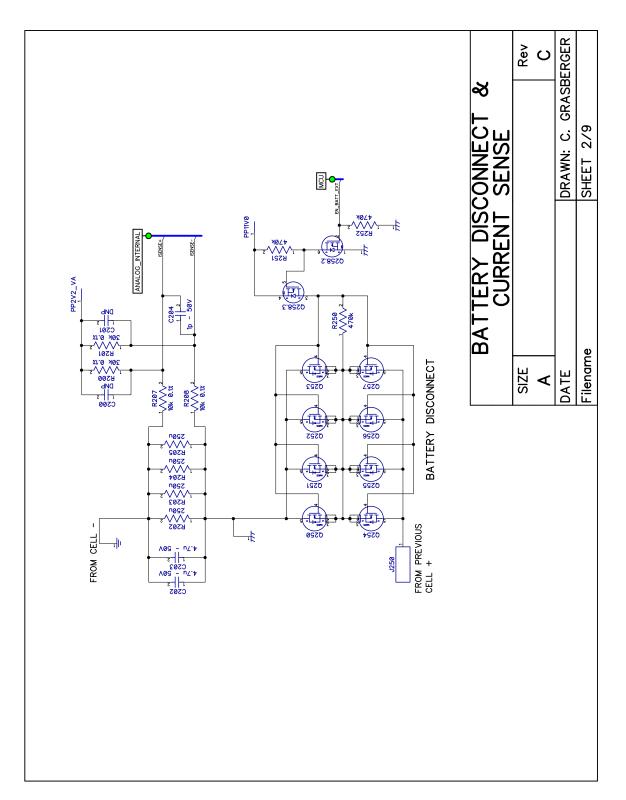

| FIGURE 7.4 – REVISION C SCHEMATIC – PAGE 2 – DISCONNECT                                                                                                                                      | 125 |

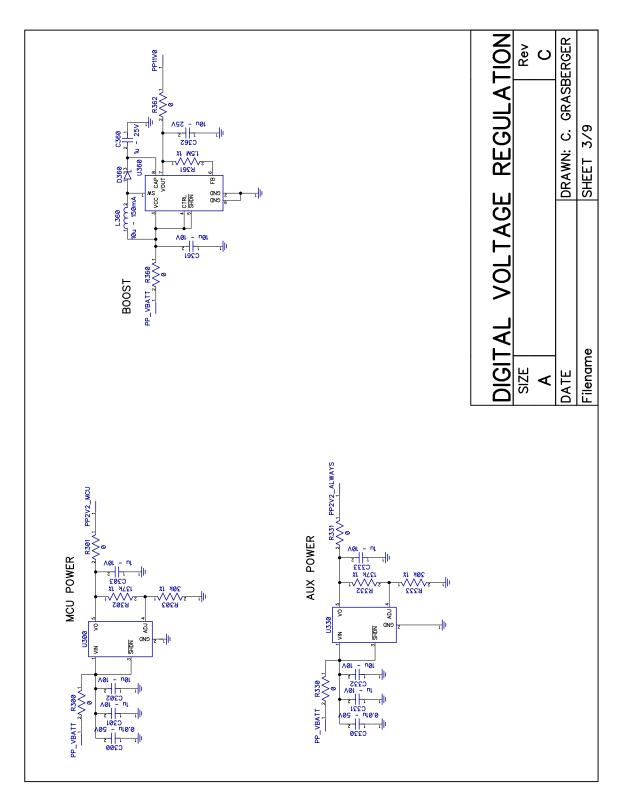

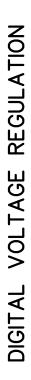

| FIGURE 7.5 – REVISION C SCHEMATIC – PAGE 3 – DIGITAL VOLTAGE<br>REGULATION                                                                                                                   | 126 |

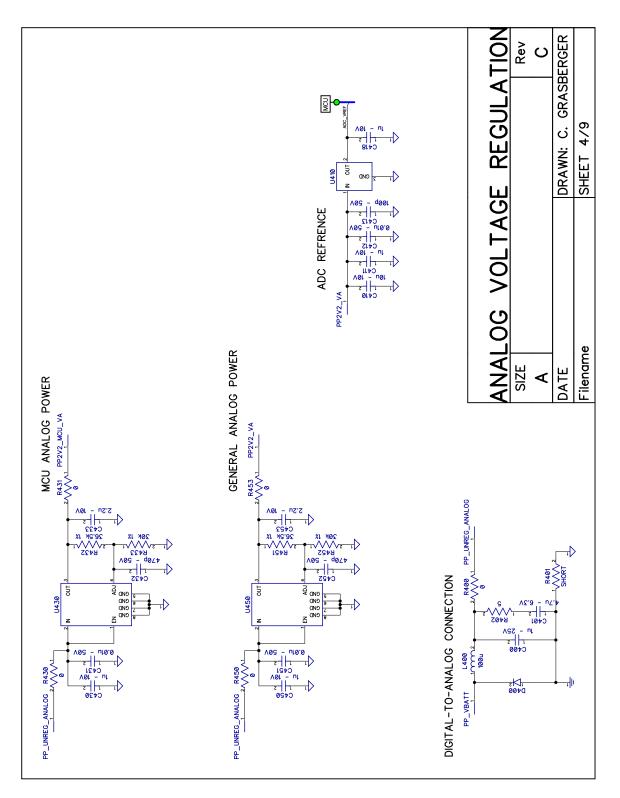

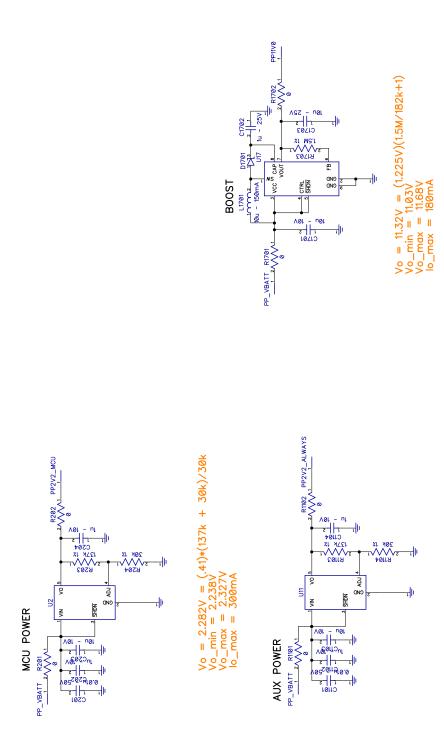

| FIGURE 7.6 – REVISION C SCHEMATIC – PAGE 4 – ANALOG VOLTAGE<br>REGULATION                                                                                                                    | 127 |

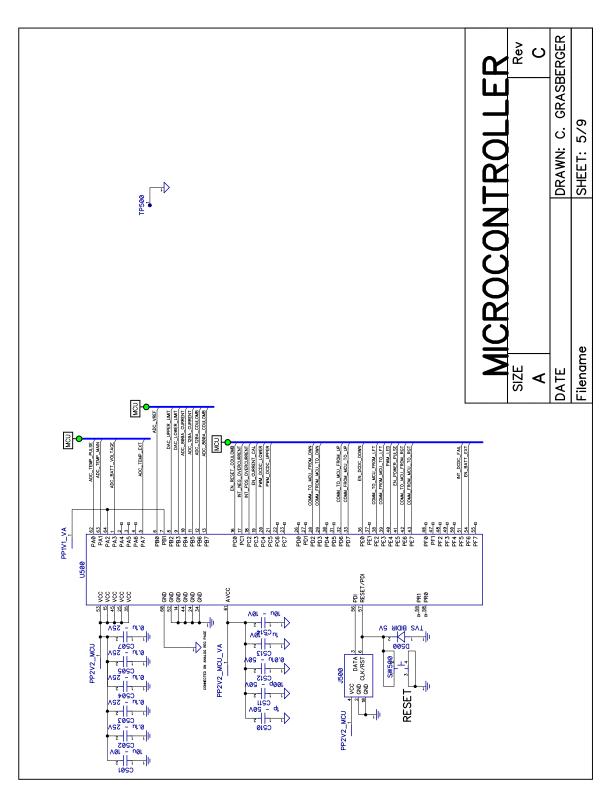

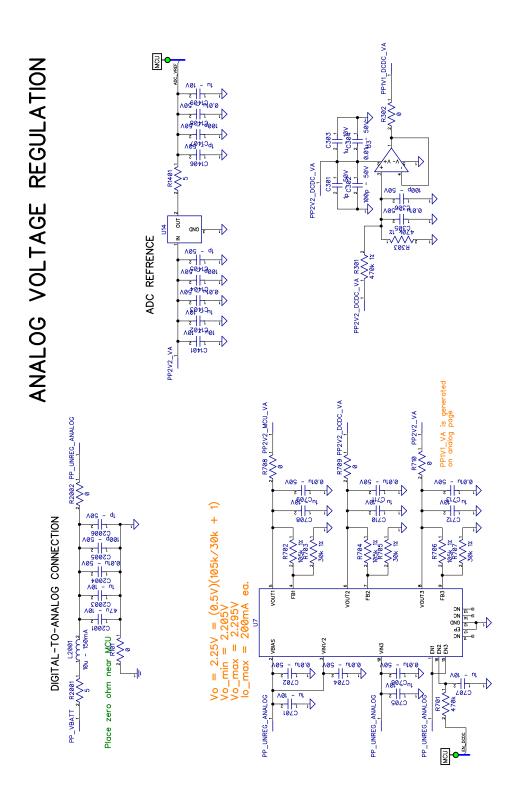

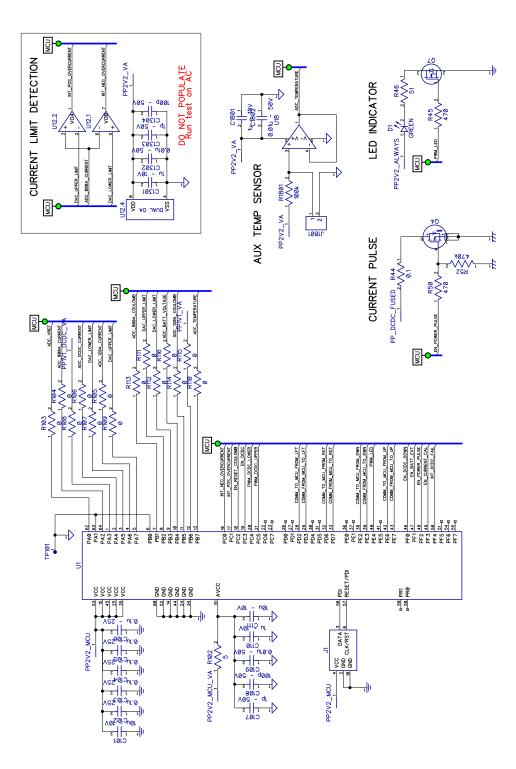

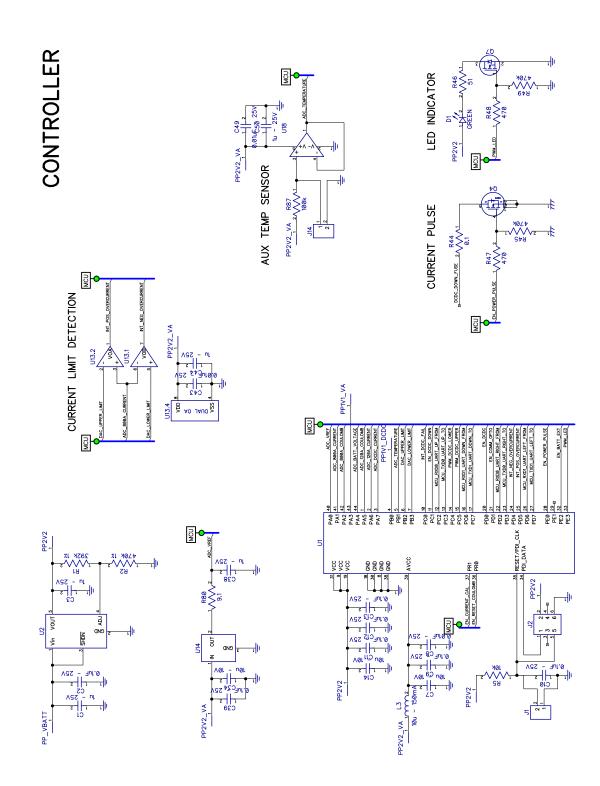

| FIGURE 7.7 – REVISION C SCHEMATIC – PAGE 5 – MICROCONTROLLER                                                                                                                                 | 128 |

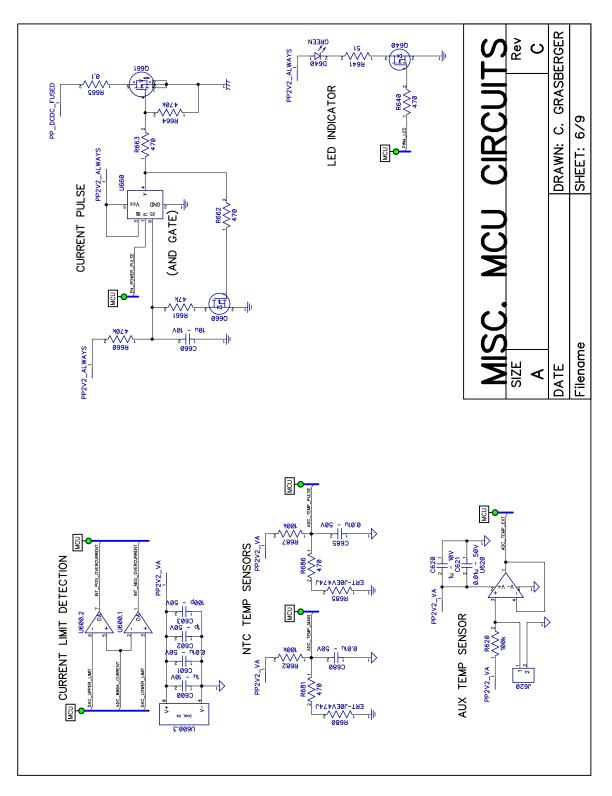

| FIGURE 7.8 – REVISION C SCHEMATIC – PAGE 6 – MISCELLANEOUS<br>MCU CIRCUITS                                                                                                                   | 129 |

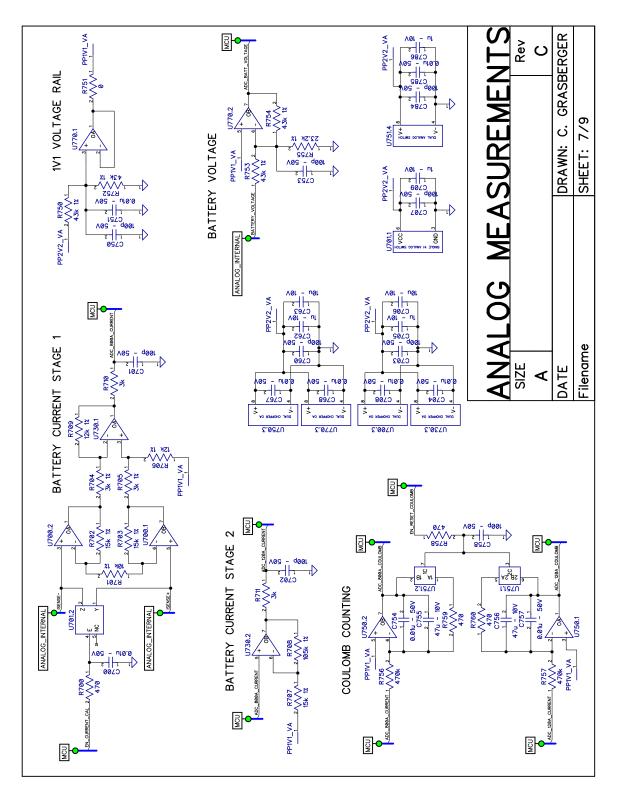

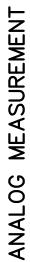

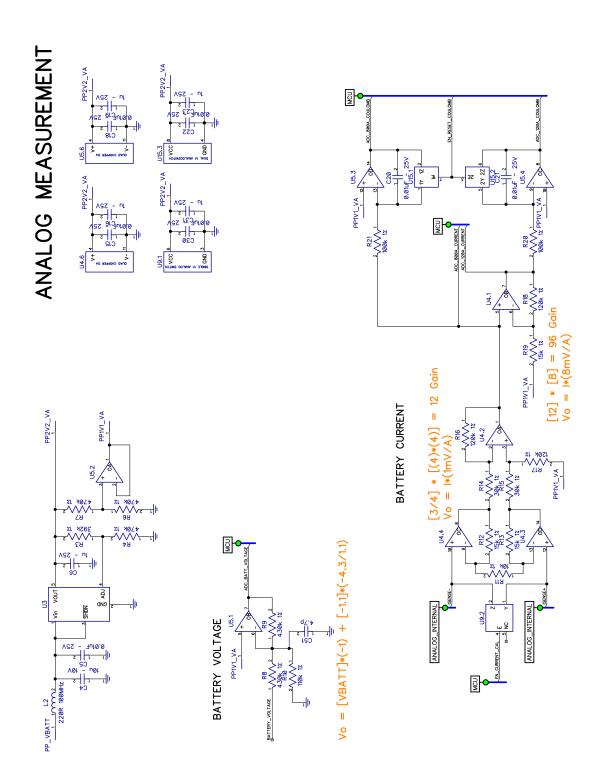

| FIGURE 7.9 – REVISION C SCHEMATIC – PAGE 7 – ANALOG<br>MEASUREMENT                                                                                                                           | 130 |

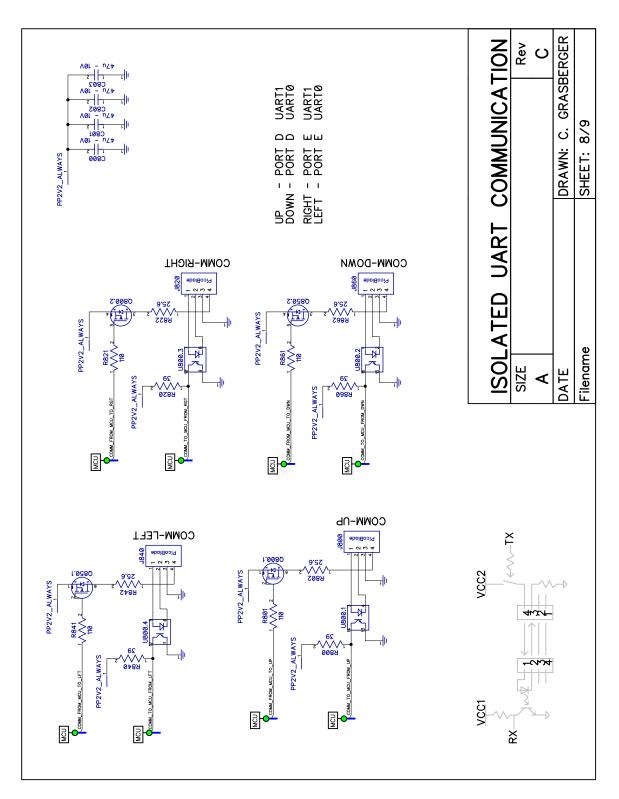

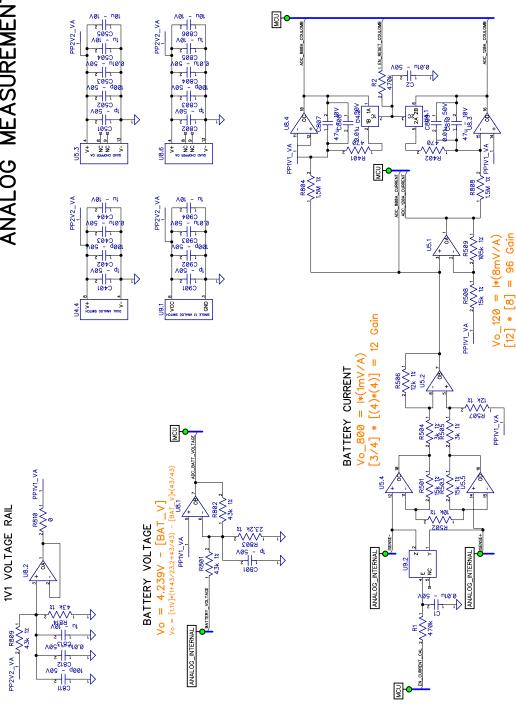

| FIGURE 7.10 - REVISION C SCHEMATIC - PAGE 8 - COMMUNICATION                                                                                                                                  | 131 |

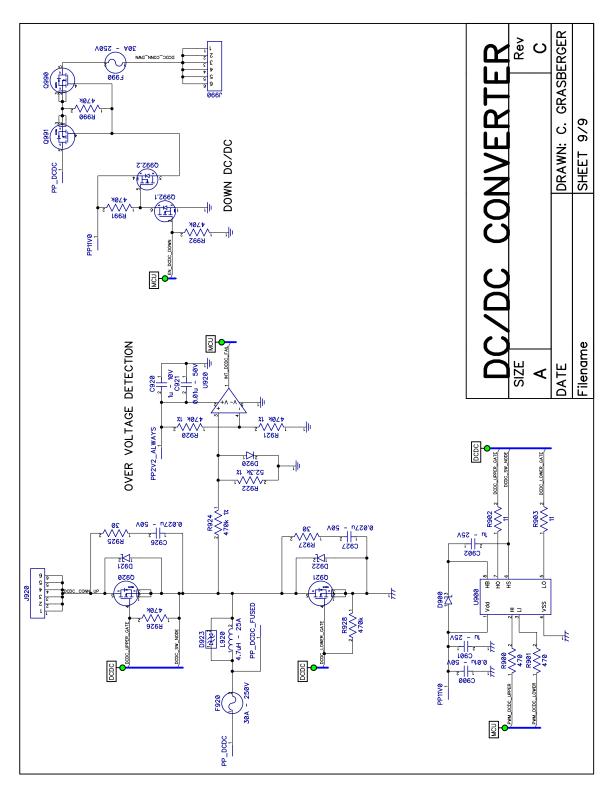

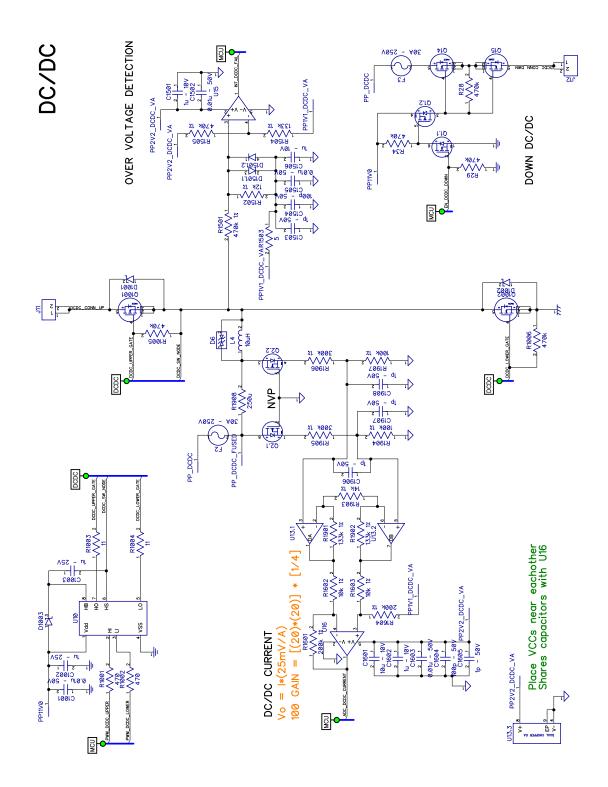

| FIGURE 7.11 – REVISION C SCHEMATIC – PAGE 9 – DC/DC CONVERTER                                                                                                                                | 132 |

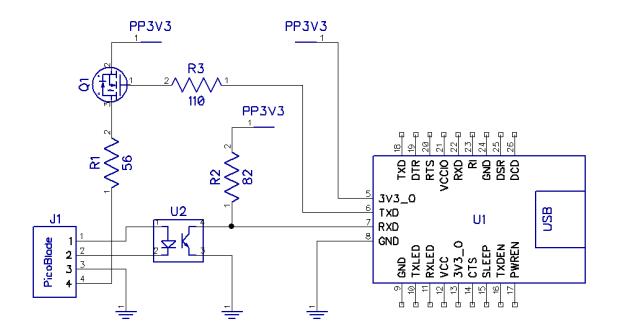

| FIGURE 7.12 – SCHEMATIC FOR UART-TO-USB ADAPTER BOARD                                                                                                                                        | 133 |

| FIGURE 7.13 – TOP SIDE OF REVISION C BOARD WITH IMPORTANT<br>ZONES HIGHLIGHTED.                        | 134 |

|--------------------------------------------------------------------------------------------------------|-----|

| FIGURE 7.14 BOTTOM SIDE OF REVISION C BOARD WITH IMPORTANT<br>ZONES HIGHLIGHTED                        | 134 |

| FIGURE 7.15 – SCREEN CAPTURE OF TOP LAYER FROM PCB GERBER<br>FILE.                                     | 135 |

| FIGURE 7.16 – SCREEN CAPTURE OF INNER LAYER 2 (SIGNAL LAYERS)<br>FROM PCB GERBER FILE.                 | 135 |

| FIGURE 7.17 – SCREEN CAPTURE OF INNER LAYER 3 (POWER PLANES)<br>FROM PCB GERBER FILE.                  | 136 |

| FIGURE 7.18 – SCREEN CAPTURE OF INNER LAYER 4 (GROUND<br>PLANES) FROM PCB GERBER FILE                  | 136 |

| FIGURE 7.19 – SCREEN CAPTURE OF INNER LAYER 5 (SIGNALS) FROM<br>PCB GERBER FILE.                       | 137 |

| FIGURE 7.20 – SCREEN CAPTURE OF THE BOTTOM SIDE (LAYER 6)<br>FROM PCB GERBER FILE.                     | 137 |

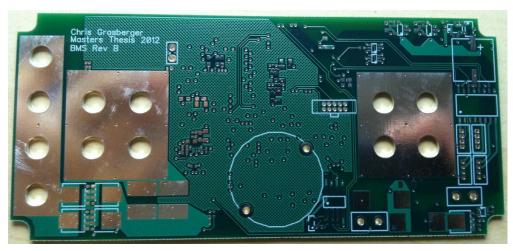

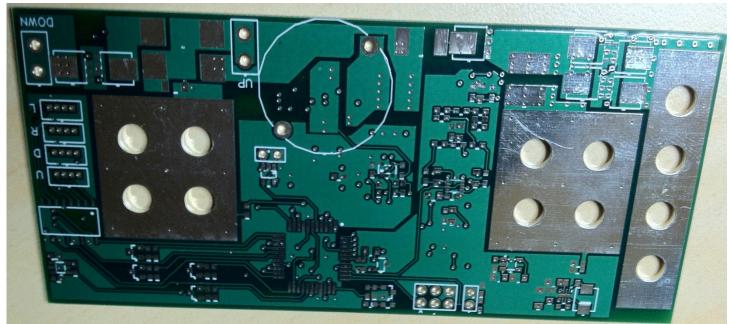

| FIGURE 7.21 – PICTURE OF A BLANK REVISION C PCB TOPSIDE                                                | 138 |

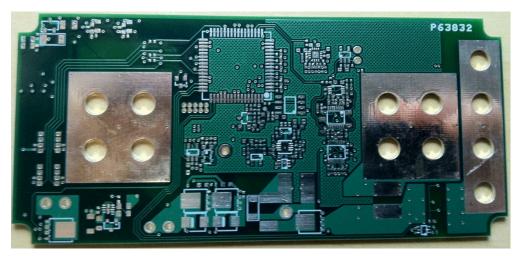

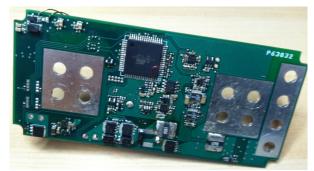

| FIGURE 7.22 – PICTURE OF NEARLY FULLY POPULATED REVISION C<br>PCB TOPSIDE.                             | 138 |

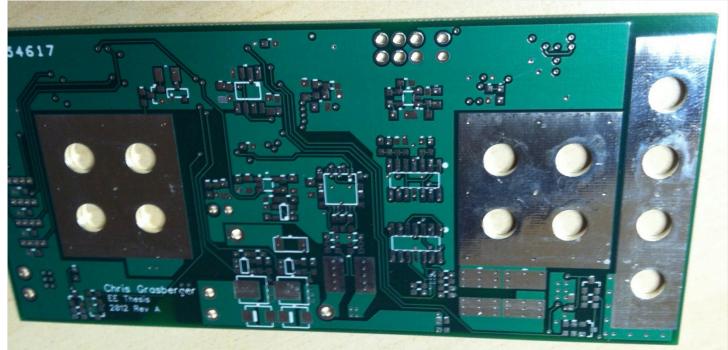

| FIGURE 7.23 – PICTURE OF A BLANK REVISION C PCB BOTTOM SIDE                                            | 139 |

| FIGURE 7.24 – PICTURE OF A NEARLY FULLY POPULATED REVISION C<br>PCB BOTTOM SIDE.                       | 139 |

| FIGURE 7.25 – PICTURE OF A NEARLY FULLY POPULATED REVISION C<br>PCB EDGE VIEW SHOWING COMPONENT HEIGHT | 139 |

| FIGURE 7.26 – PICTURE OF BLANK REVISION B PCB TOPSIDE                                                  | 148 |

| FIGURE 7.27 – PICTURE OF BLANK REVISION B PCB BOTTOM SIDE                                              | 148 |

| FIGURE 7.28 – PICTURE OF REVISION B PCB TOPSIDE NEARLY FULLY<br>POPULATED                              | 148 |

| FIGURE 7.29 – PICTURE OF REVISION B PCB BOTTOM SIDE NEARLY<br>FULLY POPULATED.                         | 148 |

| FIGURE 7.30 – REVISION B SCHEMATIC – PAGE 1 – POWER INPUT                                              | 149 |

| FIGURE 7.31 – REVISION B SCHEMATIC – PAGE 2 – DIGITAL VOLTAGE<br>REGULATION     | 150 |

|---------------------------------------------------------------------------------|-----|

| FIGURE 7.32 – REVISION B SCHEMATIC – PAGE 3 – ANALOG VOLTAGE<br>REGULATION      | 151 |

| FIGURE 7.33 – REVISION B SCHEMATIC – PAGE 4 – CONTROLLER                        | 152 |

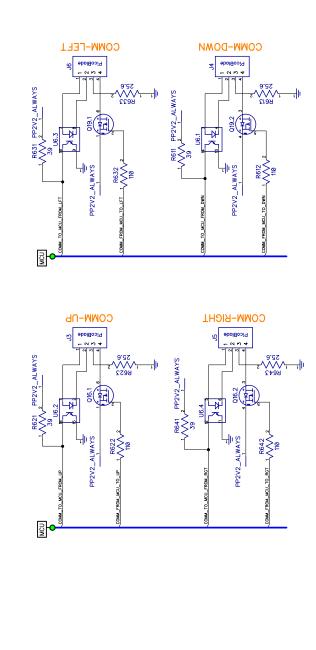

| FIGURE 7.34 – REVISION B SCHEMATIC – PAGE 5 – ANALOG<br>MEASUREMENT             | 153 |

| FIGURE 7.35 – REVISION B SCHEMATIC – PAGE 6 – COMMUNICATION                     | 154 |

| FIGURE 7.36 – REVISION B SCHEMATIC – PAGE 7 – DC/DC                             | 155 |

| FIGURE 7.37 – PICTURE OF BLANK REVISION A PCB TOPSIDE                           | 158 |

| FIGURE 7.38 – PICTURE OF BLANK REVISION A PCB BOTTOM SIDE                       | 158 |

| FIGURE 7.39 – REVISION A SCHEMATIC – PAGE 1 – POWER INPUT                       | 159 |

| FIGURE 7.40 – REVISION A SCHEMATIC – PAGE 2 – CONTROLLER                        | 160 |

| FIGURE 7.41 – REVISION A SCHEMATIC – PAGE 3 – ANALOG<br>MEASUREMENT             | 161 |

| FIGURE 7.42 – REVISION A SCHEMATIC – PAGE 4 – COMMUNICATION                     | 162 |

| FIGURE 7.43 – REVISION A SCHEMATIC – PAGE 5 – DC/DC                             | 163 |

| FIGURE 7.44 – PLOT SHOWING FIVE MODES OF OPERATION OF THE DC/DC CONVERTER.      | 166 |

| FIGURE 7.45 – EXACT EQUATION, PIECEWISE EQUATION, AND<br>MEASURED DATA PLOTTED. | 169 |

| EQUATION 3.1 – DESIGN EQUATION FOR BATTERY VOLTAGE SCALING<br>AND SHIFTING.                                                        | 20 |

|------------------------------------------------------------------------------------------------------------------------------------|----|

| EQUATION 3.2 – DESIGN EQUATION TO CALCULATED DESIRED<br>OUTPUT FROM AN INSTRUMENTATION AMPLIFIER MADE FROM<br>THREE OP-AMPS        | 25 |

| EQUATION 3.3 – DESIGN EQUATION FOR ±120A CURRENT<br>MEASUREMENT GAIN STAGE.                                                        | 26 |

| EQUATION 3.4 – EQUATION TO DETERMINE THE INTERNAL CELL<br>RESISTANCE.                                                              | 32 |

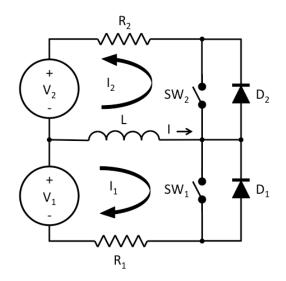

| EQUATION 3.5 – BUCK-BOOST OUTPUT FUNCTION.                                                                                         | 43 |

| EQUATION 3.6 – DUTY CYCLE                                                                                                          | 44 |

| EQUATION 3.7 – CURRENT THROUGH SWITCH 1                                                                                            | 44 |

| EQUATION 3.8 – CURRENT THROUGH SWITCH 2.                                                                                           | 44 |

| EQUATION 3.9 – EQUATION TO DETERMINE EFFICIENCY                                                                                    | 44 |

| EQUATION 3.10 – EQUATION FOR CONVERTER EFFICIENCY WHEN<br>TRANSFER IS FROM SOURCE 1 TO 2. THIS IS FOR THE CASE OF NO<br>DEAD TIME. | 45 |

| EQUATION 3.11 – EQUATION FOR CONVERTER EFFICIENCY WHEN<br>TRANSFER IS FROM SOURCE 2 TO 1. THIS IS FOR THE CASE OF NO<br>DEAD TIME. | 45 |

| EQUATION 3.12 – EQUATION TO ESTIMATE SERIES RESISTANCE IF<br>SNUBBER                                                               | 54 |

| EQUATION 4.1 – OUTPUT RELATIONSHIP FROM THE BATTERY<br>VOLTAGE CIRCUIT.                                                            | 84 |

# LIST OF EQUATIONS

#### **Chapter 1 - Introduction**

Batteries are used in everything from inexpensive toys to high performance cars. While an inexpensive toy most likely will use a non-rechargeable (primary) battery and a car will use some sort of rechargeable (secondary) battery, both devices would be of little use without a battery. Though batteries have evolved over the years, from the "Baghdad Batteries"<sup>1</sup> to Alessandro Volta 1800's first battery to modern day cells using carbon nano-tubes <sup>[1]</sup>, the technology remains fundamentally the same.

In both primary and secondary batteries, chemical potential energy is converted into electrical energy. However, secondary batteries are capable of reversing this process by applying current to the cell. Primary batteries are typically used in low drain or intermittent use products <sup>[2]</sup>. Primary cells typically have a higher energy density than secondary cells. Secondary cells on the other hand can output more current, which is required when starting a car or accelerating in an electric car. While secondary cells can be recharged, there usually is a limit to the number of recharges because not 100% of the chemical process is reversible

In a low cost application, a simple circuit that connects a battery to a motor is all that needed: for example a toy car. However, in a more expensive or sensitive product, a warning of low battery may be required. How obnoxious would it be to have a cell phone just simply turn off without a warning of low battery? What if a pacemaker gave no warning of low battery? In both of these cases, some sort of battery management system is needed to monitors of the remaining charge.

<sup>&</sup>lt;sup>1</sup> Baghdad batteries are speculated to be an ancient cell.

#### **1.1 Battery Management**

A battery management system can be used to estimate remaining capacity in a cell. This capability is just one of the many tasks battery management systems (BMS) perform. The most important job for a BMS is to ensure the safety of the cell and the users. For example in Boston in 2013, a Boeing Dreamliner's auxiliary battery overheated and caught fire <sup>[3]</sup>. Fortunately no one was onboard the plane. Had this occurred in the air instead of on land, the results could have been much worse. While the source of the exact failure is not known at the time of writing, potentially a better battery management system could had prevented this failure.

Battery management systems come in a variety of forms and typically change from application to application. A common measurement for a BMS to take is voltage measurements. The voltage of the cell is one of the critical measurements as it can monitor if the cell is within a safe operating region (SOR). Over discharging or over charging, can cause damage. Damaging the cell could potentially lead to damage to the device the cell is powering. Attempting to charge a primary cell could cause it to overheat and catch fire. Similarly, secondary cells are sensitive to abuse; their capacity can be degraded or they may be destroyed. A battery management system is able to monitor if an unsafe condition is occurring and potentially disable the device to protect the cell.

Another common thing for a battery management system to do is to monitor the current into and/or out of the cell. This measurement may be of the entire battery pack (multiple cells). Measuring the current, especially of each individual cell, will allow the system to watch for any situations that may cause the device to be damaged. For example,

a 100Ah may be able to source 1000A for a short period <sup>[4]</sup>, but extended period may cause the cell to overheat and become damaged. Accelerating from a stop in an electric car may require 1000A for a few seconds. Similarly, charging the same 100Ah cell with 100A is not recommended as it will decrease the capacity or, again, overheat it.

Using a combination of data collected from current measurements and voltage measurements, other aspects of the cell can be estimated. For example, the internal resistance of the cell can be estimated. As a cell ages, the internal resistance tends to increase <sup>[5]</sup>. As the cell ages, it decreases its capacity <sup>[6]</sup>. The capacity can be estimated by tracking the amount of charge that leaves and enters the cell, also referred to as coulomb counting. Other things like state-of-health or depth-of-discharge can be calculated from these measurements as well <sup>[7]</sup>.

Many of the examples listed are concerns about overheating. Using the same cell as in the previous example, with only  $100\mu\Omega$  of internal resistance, continuous sourcing at 100A will result in only 1W of self-heating. This is not a big concern assuming the cell can dissipate heat somehow. At 400A, the cell is dissipating 16W. At 1000A, it is dissipating 100W. These wattages are relatively low compared to the total output of the cell. However consider the case of an electric car with 16 cells performing time trials in the Mohave Desert. The ambient air is warm and the cells are all being utilized very heavily. Internal heat generation could be several hundred watts to further heat up the battery compartment. Since the voltage and current do not tell the BMS how warm the cell is, the BMS may also need to measure the temperature of individual cells or packs to remain in the SOR.

Another task that may be part of a BMS is charge management. In some cases, a separate controller handles this. Each cell's chemistry has a different preferred charge profile. For example, lithium ion typically uses a constant current charge until a certain point near maximum charge then a constant voltage charge <sup>[8]</sup>. Even if there is a separate charge module, the BMS may be required to perform balancing.

Balancing is used in systems with more than one cell. As the pack charges and discharges many times, differences in cells (even with the same model or same manufacturing lot) cause one cell to be more charged than another. This results in an unbalanced state that can reduce the effective capacity. Balancing can be as simple as using a resistor to discharge a cell or utilize a more complicated method of balancing.

There are many things a BMS may do, and some may not do. Typically this results in each system being tailor for a specific application. Many commercial systems are available, especially for handheld devices where an IC can handle the management without having to deal with significant current loads. Figure 1.1, shows a very basic BMS system attached to a battery pack consisting of four 100Ah cells. Figure 1.2, shows the cell without the BMS.

Figure 1.1 – Pictures of a rudimentary battery management system attached to large capacity cells.

Figure 1.2 – A battery pack with four 100Ah cells.

#### 1.2 Goals

This project is more product development than a research project. Also the goals are somewhat general because the customer did not have a desired solution to solve the problem. The goal of the project from the customer (thesis advisor) was that the system was to handle battery management for multiple large capacity lithium ion cells. Each cell is to be at least 60Ah or larger. Additionally there was no predetermined cell configuration of the cells in the pack: all in series, all in parallel, or a combination of both.

Further discussion of the project indicated the direction of using a microcontroller to control the system. An additional requirement was to use an Atmel AVR processor was requested. This requirement was added so future work could be accomplished on the design since many students are familiar with this family of chips. Additionally, there was one more obvious goal: the design must be safe.

After determining the four primary goals: safety, unknown number of cells, 60Ah or larger capacity per cell, and the use of an AVR processor, secondary goals were added. The author added six secondary goals to make a better product instead of making the easiest to design and build. First, the product should be durable since it is designed to go into somewhat harsh environments: a car for example. Second, the design should fit within the outline of the cell so that the pack density is not affected by the addition of the board. Third, the design should be low profile so that it does not protrude from the top of the cell so far that the compartment where the batteries are stored must be retrofitted. Fourth, there should be minimal hardware setup required to install the system. There are many designs that require running hundreds (possibly thousands) of sense wires to a

central measurement system. Fifth, the system should be high performance so that its measurements and capabilities can be trusted. Finally, the system should be low cost.

## **Primary Goals**

- 1. Safe

- 2. Unknown number of cells in pack

- 3. 60Ah or more per cell

- 4. Use AVR MCU

## **Secondary Goals**

- 1. Durable design

- 2. Fits within cell outline

- 3. Low profile

- 4. Minimal setup

- 5. High performance

- 6. Low cost

#### **Chapter 2 - Literature Review**

This project is more product-oriented so a significant amount of literature review that is covered in the design sections as research was done to resolve or fix problems. Describing all of the research before explaining the design might result in confusion. To assist with clarity in the research and design, this section will cover the preliminary research that builds up to the basic design of the system.

Battery management systems come in a variety of forms. Ideally the solution is low cost yet high performance. However, most of the time these are mutually exclusive. Typically buying off-the-shelf systems is less expensive than the ground up design <sup>[7]</sup>. Many prefabbed designs exist which could be utilized. A quick search on Digikey reveals that nearly 9,788 (1,892 stocked) BMS related products were available. For example, a full-featured integrated circuit that includes charging controls, capacity, state of health, and many other great tools is available for \$3.88/ea in volumes of 2K <sup>[9]</sup>. However, nearly every one of these prefabricated ICs is aimed at one market: mobile electronics. Unfortunately, mobile electronics typically have 1-40Wh packs while the design for this project has 1200Wh battery pack.

While Digikey and its competitors focus on small capacity cells, large cells are not without prefabricated battery management systems. For example, Orion BMS and Elithion are two companies making battery management systems for large capacity packs. Orion's design is a centralized BMS, where Elithion is distributed BMS. There is a litany of other designs including a variety of custom circuit boards made by no-name companies and hobbyist available for purchase online. Centralized or distributed BMS: which is better? Like many choices, there is not one correct answer. Centralized systems work by connecting all cells (or possibly only packs of cells) to one large processor to monitor the voltage of the cells (or pack). These systems tend to be less expensive than distributed designs because typically only one controller box is required. Centralized designs tend to be limiting in that each box can only handle a specific amount of units. An additional down side is that each cell has to be connected to the central box, which can result in very large bundles of sense wires to manage and maintain. Also, a centralized system tends to be physically further away from the cells and passive cell balancing is typically used. This may result in longer charge times. Finally, a possibly larger cooling system may be required to cool the passive balancing circuit.

Distributed BMS come in a variety of forms. Some have one BMS per cell, while others use one BMS per several cells. The latter has some similarities to a centralized system as it monitors multiple cells. Distributed systems tend to have many more control units, and as a result there is a much higher cost associated with this design since there are more controllers. Each controller also tends to be smaller because it no does not has hundreds of wires connected to the board. Since each controller is closer (or on) each cell, active or passive balancing can be used.

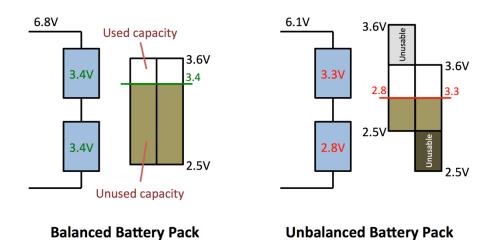

Cell balancing is critical to utilizing the maximum capacity of all cells in the pack. Unbalanced packs will be unable to fully discharge or fully charge. Figure 2.1 shows an example of a battery pack with balanced cells. In this scenario, both cells charge and discharge at the same rate and will reach the empty point at the exact same time leaving no unused charge. Similarly when charged, they will reach their maximum capacity at the same time. Figure 2.1 also shows a battery pack with unbalanced cells. While both of the cells are the same capacity, the pack's capacity is reduced. When charging, one cell reaches its maximum voltage and cannot be charged anymore preventing the partially charged cell (2.8V cell in Figure 2.1) from being fully charged. A similar thing happens when the cells discharge. The partially charged cell reaches an empty state before the fully charged cell which prevents the previously fully charged cell from completely discharging because further discharge would cause damage to the now empty cell.

Figure 2.1 – Image showing the useable capacity of a balanced and unbalanced battery packed, both of the same capacity.

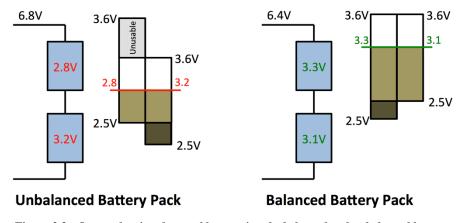

Cells with different capacities further exacerbate the problems from an unbalanced pack. While using a 60Ah cell with a 100Ah cell would make this problem very noticeable, fabrication of two identical cells will result in different capacities and internal properties. These slight differences will cause the cells to become unbalanced over a few charge cycles. Figure 2.2 shows two cells of different capacities in both unbalanced and balanced states. In the case of balanced cells, there is still an unusable region. The smaller cell is fully used and the larger cell is used as much as possible. In the case of unbalanced cells, there is limited usage because of charge and discharge limits.

Figure 2.2 – Image showing the useable capacity of a balanced and unbalanced battery packed, both of different capacities.

To balance unbalanced cells, passive or active balancing techniques are typically used. Passive balancing is an excellent choice as it is very simple to implement and exceptionally inexpensive. Typically implementations of a passive balancing system are a power resistor or MOSFET across the terminals of the cell to discharge the most charged cell. Doing this permits the rest of the pack to charge more. Unfortunately, this solution has two large drawbacks. First, since it is dissipating the stored charge into heat, the power resistor or MOSFET will heat up. Depending on how the solution is implemented, there may be little or no room available to add a heat sink or a fan. As a result, the current through the dissipative element most likely will be fairly small which may result in extremely long balancing periods. Depending on capacity and how unbalanced the pack is, balancing may take anywhere from a few minutes to several hours. This can easily add a large amount of extra charge time. The second problem is that the charged capacity is being wasted. If efficiency is important, wasting energy is not an acceptable solution.

In contrast to passive systems, there are active balancing systems. These systems come in a variety of forms. A simple but improved method from the passive system is to continuously discharge the most charged cell (as in the passive system) as the pack is being charged. This requires a better voltage monitoring system than a simple passive method, however it decreases charge and balance time. A significantly more complicated and expensive, but efficient, faster balancing, and charge, is to use a DC/DC converter. Using a DC/DC converter can potentially allow the system to transfer charge from the most charged cell to the least charged cell.

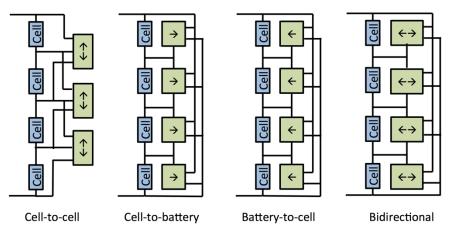

There are four basic varieties of a DC/DC converter based balancers. Each has multiple implementations. There is cell-to-cell, cell-to-battery, battery-to-cell, and bidirectional. See Figure 2.3. Each design has its own benefits but many of them require a very large storage element, typically an inductor or transformer, which would potentially require the system to be designed around a set cell configuration.

Figure 2.3 - This figure shows how the current flows to-and-from the cells in order to balance the battery pack.

### Chapter 3 - Design

This part of the project was the longest phase of the project. A lot of early design was spent trying to optimize every aspect as much as possible before the first revision of hardware was fabricated. In total three revisions of the hardware were fabricated. For each he first two revisions, there were only two boards fabricated to test features. The final, revision had four boards fabricated to permit testing on a pack of four cells. This section will only discuss the final design, however earlier designs can be reviewed in the appendices.

Figure 3.1 – Picture of the topside of the designed BMS mounted to a cell.

### **3.1 Electrical Hardware**

Most of the goals relate to the electrical hardware. Unlike software, a simple change in the hardware design requires that a new PCB (printed circuit board) be fabricated. To prevent fabricating too many boards, the design started with a high-level

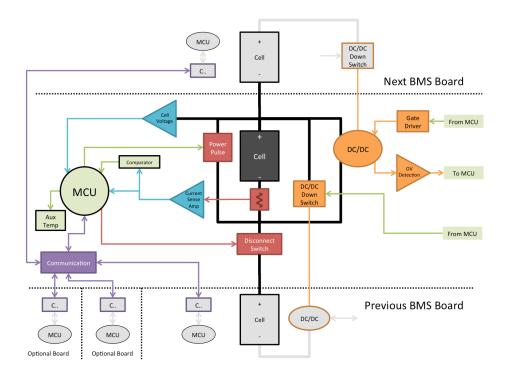

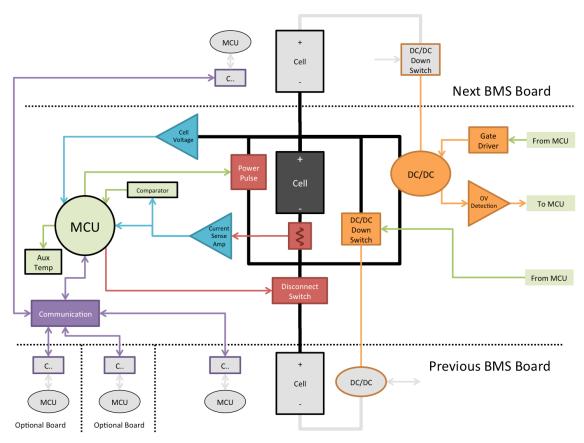

block diagram to achieve the goals. An overview of the system is shown in Figure 3.2. The image details the major features of the PCB. The image also includes connections to circuit boards of higher and lower potentials via communication and DC/DC connections. A circuit to greatly increase the current momentarily, shown in red, shorts the terminals across a small resistor to generate a measurable change in current. A sense resistor is connected to the negative terminal of the cell to measure. Connected to the sense resistor is a disconnect switch to break the connection to the outside world to protect the cell. Operational amplifier circuits to measure cell voltage and current are shown in blue. DC/DC related components for transferring charge from one cell to the next are shown highlighted in orange. Finally, things that are associated with the microcontroller (MCU) are in green. Finally, communication connections from board-to-board are shown in purple.

Figure 3.2 - Electrical System Overview

#### **3.1.1** System voltage and power

With all battery-operated systems, the system voltage can be low. 1V or less is common for computer processors these days. Other circuit components, such as operational amplifiers, are difficult to find in these voltage ranges. Additionally, using nearly any LED would be difficult. As a result, some time was put into what the voltage the logic of the circuit should operate from.

Knowing that lithium ion batteries can vary in safe operating region (more on this covered in a later section), a logic level of 2.2V was selected. More common logic voltage of 3.3V was rejected as the cell voltage can operate below 3V in many cases. Utilizing a boost or SEPIC DC/DC converter would reduce the challenges associated with component selection; but these solutions create a larger, more expensive, more complicated solution, and a less efficient one. Additionally, there are exceptionally sensitive analog components within the design. By using a DC/DC converter supply voltage would be potentially too noisy and a second stage linear-drop-out regulator (LDO) would be required to clean up the signal. This means that the voltage would have to be boosted even higher meaning additional losses beyond the DC/DC converter's own losses. These losses are further exacerbated by the quiescent current required the drive the DC/DC converter as the target set for total system current is less than 1mA. However, the biggest motivation was noise on the analog system. Using another common voltage of 1.8V was also rejected because of lack of operational amplifiers selection and gate drivers for MOSFETs. As a result, 2.2V was selected using adjustable LDOs. This allowed for a 200mV drop out from the LDO (with a 2.4V cell). None of the LDOs should ever see a high enough current load to incur a 200mV drop. 2.2V also gave an acceptable selection of components to use on the system.

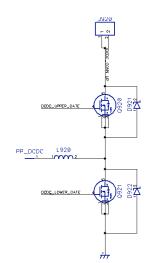

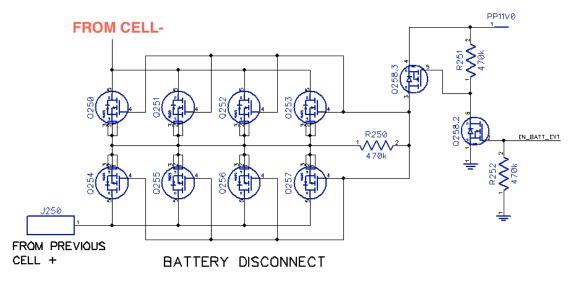

The board was designed for batteries that can output very large currents (100-1000A). A fuse alone would not sufficiently ensure the battery remains at a safe operating point so MOSFETs were used to protect the cell. However, losses in the MOSFET could reduce the output performance of the cell, over-heat, or cause damage to the board. To prevent losses, very low  $R_{SD-on}$  MOSFETs were selected: NXP's PSMN0R9-25YLC <sup>[10]</sup>. Unfortunately to benefit from the low  $R_{SD-on}$ , the gate voltage needs to be 5 volts higher than the drain to ensure the MOSFET was completely on. The cell voltage alone could not supply this. As a result, a boost DC/DC converter had to be used.

As pointed out before using a boost converter adds more current draw. However, most of the MOSFETs in this design are simply in an on or off state and not driven hard with the exception of the balancing circuit which is covered later. Holding a MOSFET gate in an on state does not require much current: therefore a very low output current boost could be used, provided it does not have high losses or high quiescent current. A boost was found that required only 400µA quiescent current and had conversion efficiency at near no-load of approximately 50%. While increasing the load does improve efficiency, this boost typically only holds MOSFET gates high or low, thus it does not see higher loads often.

Figure 3.3 shows an outline of all of the voltages and supplies in the design. PP2V2 means 2.2 volts. Any label with MCU is for the microcontroller and anything with VA is an analog supply. PP2V2\_ALWAYS is a legacy name from early n the

15

project indicating it was always on. In revision A, some of the power supplies would be disabled to conserve power. All power supplies stay on in revisions B and C.

Figure 3.3 - Overview of system supply voltages.

#### **3.1.2 Analog supplies**

Separating analog supplies from the digital supply is a common and necessary practice because digital components tend to inject noise back onto the power lines supplying them. In revision A, both the digital and analog supplies were identical common LDOs. Unfortunately, as mentioned previously, the analog components are susceptible to noise. The analog circuitry was exceptionally sensitive as it attempted to amplify a signal that could be as small as  $15\mu$ V. Despite careful layout and selection of amplifiers, revision A suffered from noise on the analog supplies resulting in an unreliable amplifier output.

Some debugging of the circuit uncovered that the linear regulators (LDOs) used in the design were taking in a clean signal and outputting a signal with more noise than the input. To resolve this issue, revision B of the hardware used ultra-low noise LDOs. This particular kind of LDO was very hard to find. The design required low input voltage, very low quiescent current, and a package that could be hand soldered with a reasonable yield. One IC was found that was a triple output ultra-low noise LDO: the Analog Device's ADP323ACPZ. There were a few other ICs available, however the cost to get the same number outputs was more than 2 times the cost.

The next step to noise suppression was to add a very wide range of input capacitors. Revision A used  $0.01\mu$ F and  $1\mu$ F capacitors in parallel to suppress noise. Both of these caps were rated for 25V so capacitor de-rating was not the problem. Revision B used 1pF, 100pF,  $0.01\mu$ F,  $1\mu$ F, and  $10\mu$ F. Using a wide range suppresses a wider range of frequencies, but it added the risk of self-oscillation between the larger and smaller capacitors. Fortunately, testing showed no oscillations during operation.

The noise on the output was no longer detectable and the amplifiers generated a usable signal after adding nearly fifty more capacitors, using better capacitors (X5R vs. X7R and Y5R), and changing to a more expensive regulator. This improvement came at an expense more than just the cost. Adding more capacitors required more space. Revision A used 0603 capacitors and resistors. However, adding fifty more capacitors to a small area required that the design use 0402 whenever possible. To be consistent the whole design moved to 0402 components. Some 0603s and 0805s remained as the capacitance values reached higher values. There was another difficulty added by the design change. Since the quantity of boards being fabricated was very small, paying for a factory to assemble 2-6 boards was cost prohibitive. As a result all boards were hand soldered. As expected, some packages were more challenging to solder than others. The DFN package for the triple regulator was more challenging than any of the other DFNs

17

on the board. In fact, of the five attempts to solder the IC to a board, only one succeeded. This meant that only one of the two prototype boards could measure analog signals. For reference, the other DFNs could be soldered down with no issues.

In the final revision, revision C, the circuit was modified one more time to make assembly slightly easier since four complete boards were desired. The regulator was changed. This was a high-risk action as the new regulator was untested, however with such a low yield in assembly it was necessary. The new LDO selected was Micrel's MIC5209YM. This is an adjustable LDO with an ultra-low noise option by changing the feedback circuit <sup>[11]</sup>. Another change to the circuit was to reduce the number of capacitors to a more reasonable quantity. All of the 1pF caps in the analog section were removed and several of the 10µF capacitors were removed as well. This was done for three reasons.

First, the filter between the unregulated digital main and the unregulated analog main was improved from a simple RC filter to an LC filter damped with an RC filter. This filter used 100 $\mu$ H inductor and a 1 $\mu$ F capacitor resulting in a cut off at 16kHz. At such a low frequency, linear regulators are able to suppress any noise and output a clean supply. Second, 1pF capacitors filter out extremely high frequencies. It is possible for a high frequency to get into the circuit, however the PCB design should shield against external noise. Third, having more capacitors around reduces the options of how to route all of the signals. Less components makes routing easier and having a clean routing will most likely have more of an impact on signal integrity than a 1pF in this design. Unfortunately, the new regulator was significantly noisier than the previous regulator. The impact of the noise is covered in Chapter 4.

Finally, there is a high precision voltage reference IC. This regulator outputs a  $2.048V \pm 0.2\%$  reference. Another option would have been to connect the ADC reference to one of the analog supplies. While the LDOs regulate the output to less than  $\pm 1\%$ , the tolerance of the resistors and the internal reference can vary the output's set point by several hundred millivolts. Accounting for this variability in software is not too challenging, but if the voltage drifts or dips at all, any calibration is useless. Additionally the reference IC is nearly insensitive to temperature and aging effects unlike the LDOs. By using a 2.048V reference, each least significant bit (LSB), of the 12-bit ADC, is equivalent to 0.5mV.

#### 3.1.3 Measurement

One of the primary tasks for the battery management system is to monitor the cell. The following sections describe the design for measuring battery voltage, current, and cell capacity as well as measuring other important values.

#### **3.1.3.A Battery voltage**

One of the first things designed was a way to measure the battery voltage. Since the cell voltage is direct indication of remaining capacity and health, it is very important to monitor this voltage accurately. The lithium iron phosphate (LiFePO<sub>4</sub>) cells were selected for testing the BMS. These cells have a working voltage between 3.1 to 3.3V,and an absolute max range of 2.8V to 3.6V. Since the system voltage is 2.2V, a simple voltage divider would be an exceptionally inexpensive and reasonably accurate solution. However, the lowest part of the Analog-to-Digital Converter's (ADC) range is unreachable and this reduces the usefulness of the divider<sup>2</sup>. Also, since the divider would probably need a voltage follower to buffer the divider from an ADC, a better circuit was added for nearly no additional cost.

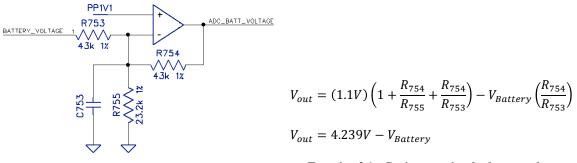

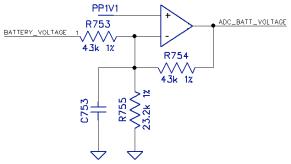

Figure 3.4 - Battery voltage measurement circuit

Equation 3.1 – Design equation for battery voltage scaling and shifting.

The circuit shown in Figure 3.4 was designed. This circuit scales and shifts the battery voltage to fit the ADC measurement range. To make the design useful on more than LiFePO<sub>4</sub> batteries, an input voltage range of 2.4 to 4.2V was used. This range was shifted and scaled to fit within the range of just slightly above 0V and slightly below 2.048V. The circuit is an inverting summing amplifier using 1.1V as the reference instead of ground. This means 4.2V would be nearly 0V at the ADC and 2.2V would be 2.048V. Since 1.1V is "ground" in this circuit, tying one of the summed inputs to real ground results in a -1.1V being summed. The resulting equation is shown as Equation 3.1. Adjusting  $R_{755}$  will scale how large the voltage shift down affects the input and adjusting  $R_{753}$  will adjust the scaling of the input. The current design includes a -1

$<sup>^{2}</sup>$  A voltage divider could be designed so that the divided voltage is just at the top of the ADC's range at full charge. However, there is no way that the voltage divider's divided voltage can ever reach zero, thus wasting a section of the ADC's measurement range.

scaling factor and a voltage shift down of 4.2V.  $C_{753}$  was added as an optional low-pass filter.

#### **3.1.3.B** Battery current

Measuring the battery current is one of the most important features and also one of the most challenging to design. Accurately measuring the current is important for the system to count coulombs, log usage, and detect abnormal operation. One challenge associated with accurately measuring the current is that the selected 100Ah batteries can source peak currents of 1000A for 10 seconds. Measuring  $\pm 1000A$  (for over-current detection) is possible to do accurately, but also measuring a more typical range of  $\pm 30A$  accurately is a challenge using the same hardware.

Initial research indicated that the best way to measure a  $\pm 1000$ A current range is to use a magnetic sensor to minimize power loss.<sup>[12]</sup> There were a number of problems with this design. Nearly every commercially available design using a magnetic sensor used one single current sensor on the output of the entire array of battery packs. This yielded a lower cost solution, however it gave very little insight into the charge in an individual cell. The design proposed in this paper uses a current sensor for each cell.

Another option was to use a current loop sensor. Several of the current loop sensors were rated for the required range: for example, a  $\pm 200$ A current sensor could measure 800A for short duration. However this current loop sensor was accurate to  $\pm 2$ A near 0A through sensor and  $\pm 10$ A closer to 200A<sup>[13]</sup>. Using these values to coulomb count would possibly result in an unacceptable error in cell capacity estimations.

Another issue this device presented was that its bandwidth was limited to 50kHz. In addition to the inaccuracies, most of the current loop systems needed 5-12V with currents ranging from 15-30mA. A current of 15mA exceeds the entire budget for current before considering the current required to boost from 2.2V up to 5-12V. Finally, these devices required that typically a wire or bus bar be placed through the sensor. While a solution could have been designed, this posed a problem when considering two of the goals of the project: low profile and durable. Regardless of the bulkiness of this design, the power consumption was enough to completely remove it from consideration.

A lower cost system that does not directly require contact with the trace is to use a giant magnetoresistance (GMR) IC. These ICs are essentially resistors that are sensitive to magnetic fields <sup>[14]</sup>. These devices need to be in near proximity to the current carrying trace. Unfortunately these sensors also could be thrown off by other magnetic sources such as an electric motor. Since these sensors would be unreliable in this application, they were rejected.

Overall, the magnetic solutions posed too many problems for high accuracy measurement. Many commercial designs use one large magnetic sensor to determine the output current but this limits feedback for the BMS. The design used in this thesis measures the current for each individual battery to better control and monitor battery usage. Ultimately, the final solution was to use a current sensing resistor.

Research into the resistive sensors indicated that there are two options: use power resistors or calibrate a small copper trace length. Using a copper trace length is appealing because it is an inexpensive solution. The major issue with using a copper trace is the temperature dependence of copper's resistance is very significant (~3930ppm/K<sup>[15]</sup>),

which would add an error into the measurement. The change in the resistance can be accounted for by using a temperature sensor. The second option is to use power sense resistors, which typically have much lower thermal coefficient (<20ppm/C<sup>[15]</sup>).

To minimize the effect of temperature dependence, this project uses four power sense resistors in parallel. Each resistor is 4W  $250\mu\Omega \pm 1\%$ . Four power resistors were chosen since it was easier to purchase four resistors than a single 16W  $62.5\mu\Omega$  resistor. The resistor network allows for 506A to continuously go through the sensor. This would require external cooling because the board cannot dissipate 16W on its own. A more typical continuous operating current of 100A will only dissipate 5/8W. Additionally, the resistors can only handle short transients above 500A.

One of the many design problems was that a 1A measurement would only output a 62.5 $\mu$ V signal. Another problem was that a failsafe feature (this is covered in a later section) required that the sense resistors be connected to ground. This is a problem because the signal to measure is potentially outside the range of operation for most ICs. A set of voltage dividers was used to remedy this problem. The voltage dividers are connected from the analog supply of 2.2V to both terminals of the sensor resistor. The signal is shifted up to a more optimal operating condition for the amplifiers, however it reduced the amplitude of the signal to 3/4<sup>th</sup> of what it was before. So now a 1A signal results in a 46.875 $\mu$ V output signal. An additional problem that was caused by using voltage dividers was the tolerance of the resistors.

Initially the voltage divider used  $10k\Omega \pm 1\%$  and  $30k\Omega \pm 1\%$  resistors. However, when two circuits are connected in parallel (to exactly the same supply and ground) the difference between the two center nodes can be as large as 16.5mV with a 2.2V source.

This is an exceptionally large error. It can be removed in calibration (covered in a later section) but this adds a large offset to the signal that will be multiplied by 120 possibly causing saturation at a very low current measurement. To resolve this problem, more expensive  $\pm 0.1\%$  resistors were used for the voltage divider. Using 0.1% resistors, the maximum difference became only 1.65mV, which is still a significant error. The total offset after amplification is 198mV instead of 1.98V with 1% tolerance resistors.

The next step to processing the differential signal was to amplify it. A logical choice would be to use an instrumentation amplifier (IA). Three problems immediately arose. The first problem was that most IA ICs require too large of a quiescent current: typically 1mA or more. The second problem was that many of the IA ICs bandwidth was low. Some of the better commercial IA's bandwidth was in the range of 50kHz with a gain of 1 (the final design of this circuit uses a gain of 120). Finally, the input voltage offset of many IAs are anywhere from 1mV to 500mV. An input offset of  $\pm$ 1mV would be seen as  $\pm$ 1.33mV more on the current sense resistor, adding the equivalent of  $\pm$ 21A to the measured value. While 1mV is less than the error of the voltage divider, the voltage divider is a worst-case scenario where the input offset is the best case. Additionally, the resistors are much less dependent on temperature and age than the input offset of an amplifier. When combining all of these problems, commercially available IA ICs were not sufficient for the design. As a result, a discrete IA circuit was designed.

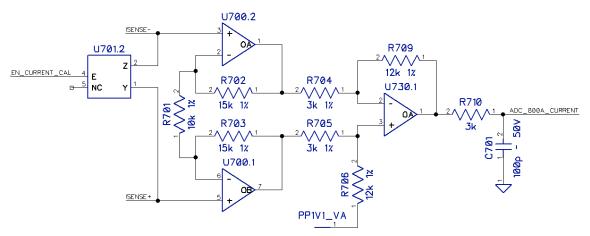

The selected operational amplifiers were LTC6256, which is a dual chopper OA. A chopper op-amp was selected because they constantly calibrate themselves to minimize the input voltage offset. The LTC6256 has a typical input voltage offset of  $\pm 9\mu V$  (with a maximum of  $\pm 100\mu V$ ). The circuit that was designed is a basic three OA instrumentation

amplifier. The first stage (two OAs, U700.1 and U700.2) had a gain of 4 and the second stage (one OA, U730.1) also has a gain of 4. By splitting the gain into two stages of 4, the bandwidth of the OAs was maximized. The total gain of the IA from input to output was a gain of 16 with a bandwidth of more than 200kHz. Additionally, the circuit has an optional low-pass filter on the output using  $R_{710}$  and  $C_{701}$  to attenuate undesirable signals.

Figure 3.5 – Instrumentation amplifier circuit used to amplify voltage from sense resistor.

$V_{ADC\_800A\_CURRENT} = (V_{ISENSE+} - V_{ISENSE-}) \left(1 + 2\frac{R_{702}}{R_{701}}\right) \left(\frac{R_{709}}{R_{704}}\right)$  Equation 3.2 – Design equation to calculated desired output from an instrumentation amplifier made from three op-amps.

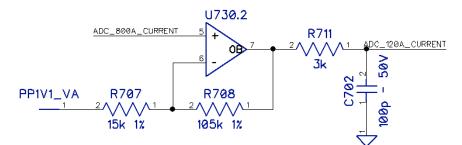

The output of the IA is used to measure the current through the sense resistors for a range of  $\pm 800$ A with a sensitivity of 187.5 $\mu$ V/A. A second measurement range of  $\pm 120$ A, with a sensitivity of 1.5mV/A, was added by adding a third amplification stage. The third amplification stage is a simple non-inverting op-amplifier circuit (U730.2) with a gain of 8. The circuit also has an optional low-pass filter R<sub>711</sub> and C<sub>702</sub>.

As mentioned before, there was an accumulation of errors that are part of the signal. To remedy this, two calibrations were used to mitigate most of the error. First, there is an analog switch that shorts the inputs of the IA. Shorting the inputs allows for

the errors from the input of the op-amps to the input of the ADC to be measured. Some of the errors are temperature dependent such as the input offset. As a result, the analog switch is used before every measurement to calibrate out many of the variable errors. To sample the current, the inputs of the IA are shorted first. After shorting the inputs, a measurement is made on the ADC. This measurement is all of the accumulated errors in the IA circuit. After that measurement is completed, the inputs are no longer shorted and a second sample is taken. The first measurement is subtracted from the second measurement to remove the offsets and errors. This does not account for the tolerance of the sense resistor or the errors associated with the voltage dividers since they are before the analog switch.

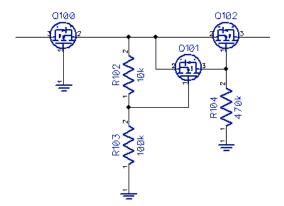

Figure 3.6 - Amplifier stage to archive ±120A current range.

$$V_{ADC\_120A\_CURRENT} = -V_{ADC\_800A\_CURRENT} \left(1 + \frac{R_{708}}{R_{707}}\right) \qquad \begin{array}{l} \text{Equation 3.3 - Design equation for $\pm$120A current} \\ measurement gain stage. \end{array}$$

To adjust for the errors not covered by shorting the inputs, a calibration is done using software tools. The software measures multiple known currents and fits a line using linear regression. This removes most of the errors, however some of the parameters may have a weak relationship with temperature and aging that is only corrected by recalibration using software. This calibration would be done at the "factory," however it is possible for the user to do it as well.

#### Software Steps to Sample:

- 1. Enable analog switch (short inputs)

- 2. Sample ADC channel desired (120A or 800A range signal)

- 3. Disable analog switch (no longer shorting inputs)

- 4. Sample same ADC channel as in step 2

- 5. Subtract the first sample (step 2) from the second sample (step 4)

- 6. Apply gains and offsets determined by software calibration

Ignoring all of the offsets and errors associated with this measurement circuit, there are two additional sources of error that are not directly associated with the circuit. The first one is the noise from the power supplies. The initial linear regulators (LDO) used on revision A added about  $20mV_{pp}$  of noise on to the input signal of the amplifier. This caused unpredictable errors at the output of the amplifier. The impact of the power supply noise was reduced by using ultra-low noise regulators, a large range of input capacitors to suppress a wide range of frequencies, and a low-pass filter to isolate digital power from analog power.

The second problem was that this highly sensitive amplifier is unavoidably close to the active balancing circuit, which may be switching up to 25A. This problem was one of the most challenging and mitigated in multiple ways. First the analog signals were buried as much as possible to protect against electronic noise. A magnetically shielded inductor was used to protect the circuit from magnetic noise. The balancing circuit was pushed as far away as possible from the analog circuit. Finally, the layout of the ground planes was designated to prevent currents from circulating through the analog area.

# **3.1.3.C** Coulomb Counting

Measuring the capacity of the cell is an important feature of a battery management system. A very inexpensive way to estimate the capacity of the cell is to use the cell voltage. This can be an accurate measurement if the profile of the cell charge to voltage is well known. However, age, usage, temperature, discharge rate, and other parameters affect the profile of the voltage vs. charge <sup>[16]</sup>. Additionally, the internal resistance of the cell is required parameter to accurately estimate the cell's voltage. Ignoring the internal resistance may make the cell appear to be at a higher voltage, which would give a higher estimation of remaining charge.

A more accurate measurement of the remaining capacity is to count the charge that enter and leave the cell. This can be achieved by first carefully discharging the cell down to a state of near zero capacity. Then charge the cell back to full capacity and integrate the current going into the cell.<sup>[17]</sup>