JOURNAL OF NANO- AND ELECTRONIC PHYSICS Vol. 8 No 1, 01041(4pp) (2016) ЖУРНАЛ НАНО- ТА ЕЛЕКТРОННОЇ ФІЗИКИ

Tom 8 № 1, 01041(4cc) (2016)

# Comparison of Three Dimensional Partially and Fully Depleted SOI MOSFET Characteristics Using Mathcad

Neha Goel<sup>1,\*</sup>, Manoj Kumar Pandey<sup>2,†</sup>

Department of ECE, RKGIT Ghaziabad, India

Department of ECE, SRM University NCR Campus Ghaziabad, India

(Received 23 October 2015; published online 15 March 2016)

In this Paper, comparison of three Dimensional characteristics between partially and fully depleted Silicon-On-Insulator (SOI MOSFET) is presented, this is done through 3D device modeling using mathcad, based on the numerical solution of three dimensional Poisson's equation. Behavior of Various Parameters like Surface Potential, Threshold Voltage, Electric field and Drain current are presented in this paper.

**Keywords:** Silicon on insulator (SOI), Poisson's Equation, Front surface potential, Threshold voltage, Electric field, Drain Current.

DOI: 10.21272/jnep.8(1).01041 PACS numbers: 85.30.tv

## 1. INTRODUCTION

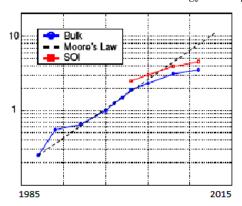

High performance and digital circuits are the current need of electronics industries, Earlier Bulk MOSFET was considered fit for the electronics industry and to satisfy the Moore's law [15], which states that performance of transistors in a dense integrated circuit doubles approximately every two years. Primary method to increase productivity and performance is scaling, But due to Short channel effects and junction leakage current with scaling, it is difficult to follow moore's law with bulk CMOS. So the need to SOI technology arises [17].

Fig. 1 - Evolution of CMOS Technology with moors Law

# 2. NEED OF SILICON ON INSULATOR (SOI) MOSFET

SOI Technology is the solution to the limitation of the CMOS bulk technology against various impacts due to Scale down the device.

There are various characteristics of SOI MOSFET due to which it would be beneficial to switch to SOI MOSFET technology. The main advantages of SOI technology are the following.

- Latch can be eliminated as there are no parasitic bipolar devices because of SOI Layer.

- Due to the insulation layer above the substrate,

- these devices have smaller leakage current.

- High speed of operation due to the very low capacitance between device and substrate.

- Power dissipation of SOI MOSFET is small, because operated at lower voltages and current levels [2].

## 3. SILICON ON INSULATOR (SOI) MOSFET

Structure of SOI MOSFET is almost similar to that Bulk CMOS, But an insulation layer is inserted underneath the device on the silicon substrate.

On the Basis of the thickness of the SOI layer, there are Two types of SOI MOSFETS [17]:

- 1. Partially Depleted SOI MOSFET;

- 2. Fully Depleted SOI MOSFET.

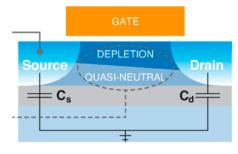

In Partially Depleted SOI MOSFET, SOI layer Thickness is kept more than the Maximum depletion width of the gate. A technology based on this principle is called a partially depleted SOI Technology. PD SOI Structure is as shown in Fig 2.

Top Silicon Layer is Approximately  $50 \sim 200 \text{ nm}$  Thick, as per the requirement of the design, Following four parameters Make PDSOI Technology as an essential IC Technology for industry compare to Bulk CMOS. (1) Low Power, Can operate at low power with the same performance. (2) High performance, Provides Performance gain of 20-40 % [16]. (3) Easy Process (4) Technology mixing. But the major problem with PD SOI is floating body effect.

Fig. 2 - Partially Depleted SOI MOSFET Structure [14]

<sup>\*</sup> nehagoel@rkgit.edu.in

<sup>†</sup> mkspandey@gmail.com

Table 1 - PD and FD SOI Structure at a Glance

|                      | Structural differences                                                                                                   | Advantages                                                                                                                                             |

|----------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Partial<br>Depletion | 1. Doped Channel 2. Top Silicon 50 ~ 90 nm thick 3. Insulating Box Layer is typically 100 to 200 nm thick                | 1. Well Under- stood 2. Industrial Proven 3. Easy to Manufacture. 4. Can leverage floating body for performance gain or memory applications.           |

| Fully Depletion      | 1. Un doped or lightly doped Channel 2. Top Silicon 5 ~ 20 nm thick 3. Insulating Box Layer may be ultra thin 5 to 50 nm | 1. Leakage and power consumptions are very low 2. for undoped channel, random voltage fluctuations can be minimized 3. free from floating body effects |

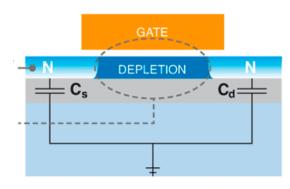

Fig. 3 – Fully Depleted SOI MOSFET Structure [14]

In fully depleted SOI MOSFET silicon thickness is very less hence channel is fully depleted from the majority carriers. ie SOI layer is thinner than the depletion width of the device [14].

Top silicon layer is approximately  $5 \sim 20$  nm. Thick, as per the requirement of the design silicon under the gate is very thin so, fully depleted by mobile carriers.

In FD SOI technology, floating point effect can be eliminated as there is no Neutral region of MOSFET for charge [14]. FD SOI Structure is shown in Fig 3 and Comparison points between PD SOI and FD SOI are given in Table 1.

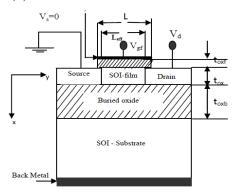

# 4. DEVICE MODELING

Fig. 4 illustrates a three-dimensional view of a typical MOSFET structure with corresponding device dimensions. The source-SOI film and drain-SOI film junctions are located at y = 0 and y = Leff, respectively, where, *Leff* is the effective channel length. The front and back Si-SiO interfaces are located at x = 0 and  $x = t_s$ , where  $t_s$  is the SOI film thickness.  $t_{oxf}$  and  $t_{oxb}$  are

the front and the back gate oxide thicknesses, respectively, where the applied potential to the front and back gates are  $V_{gf}$  and  $V_{gb}$ . The vertical and the lateral directions are defined as x and y, respectively, while the direction along the width of the transistor is defined as z. The sidewall Si-SiO interfaces are located at z=0 and z=W

In general, in order to analyze this structure, we have Poisson's equation, which is as below.

$$\frac{d^2}{dx^2}\psi(x,y,z) + \frac{d^2}{dy^2}\psi(x,y,z) + \frac{d^2}{dz^2}\psi(x,y,z) = \frac{q\cdot N_a}{\varepsilon_{si}} \ (1)$$

In order to solve equation (1), it is separated into 1D Poisson's equation, 2-&3-D Laplace equation as:

$$\frac{d^2}{dx^2}\psi 1(x) = \frac{q \cdot N_a(x)}{\varepsilon_{si}}$$

(2)

$$\frac{d^2}{dx^2}\psi(x,y) + \frac{d^2}{dy^2}\psi_s(x,y) = 0$$

(3)

$$\frac{d^{2}}{dx^{2}}\psi_{v}(x,y,z) + \frac{d^{2}}{dy^{2}}\psi_{v}(x,y,z) + \frac{d^{2}}{dz^{2}}\psi_{v}(x,y,z) = 0$$

(4)

Where,

$$\Psi i = \Psi l(x) + \Psi s(x, y) + \Psi v(x, y, z)$$

(A)

Main Equation can be obtained by finding separate solutions for  $\Psi l$ ,  $\Psi s$  and  $\Psi v$  and finally putting in Equation (A).

$\label{eq:fig.4-Cross} \textbf{Fig. 4} - \textbf{Cross sectional view of double gate SOI MOSFET} \\ \textbf{along channel length}$

#### 5. RESULT AND DISCUSSION

Modeling has been done for Both PD and FD SOI MOSFET and comparison between the PD and FD SOI MOSFET'S for Surface Potential, Threshold Voltage, Electric Field with respect to Channel Length is given here, Variation Comparison for Drain current with respect to Drain voltage, gate source voltage are also presented as below.

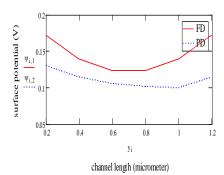

# 5.1 Surface Potential

The variation of front surface potential at the front  $Si-SiO_2$  interface (i.e., x=0) of a PD and FD SOI MOSFETS for different values of channel length is shown in Fig. 5. which shows that FD SOI MOSFET follows better surface potential characteristic as com-

COMPARISON OF THREE DIMENSIONAL PARTIALLY...

pare to PD SOI MOSFET.

In the Fig. 5, we determine the variation of front surface potential for n-channel SOI MOSFETs along the different values of channel length at the front Si-SiO<sub>2</sub> interface and z=w/2. The values we have taken here are:  $t_{oxf}=3$  nm,  $t_{oxb}=400$  nm,  $N_A=1\times 10^{17}$ /cm³ at  $V_{gf}=V_{gb}=0$  &  $V_{ds}=1.5$  V.

Fig. 5 – Variation of the front Surface Potential along channel length for PD and FD SOI at the front Si-SiO $_2$  interface

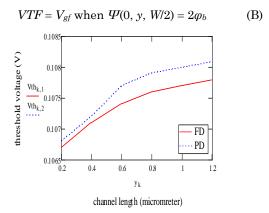

#### 5.2 Threshold Voltage

The Threshold voltage of the short channel MOSFET [5, 11] is defined as the gate voltage at which the minimum surface potential in the channel is the same as the channel potential at threshold for a long channel device, i.e., at threshold.

The variation of threshold voltage with respect to Channel length for PD and FD SOI MOSFET is shown in Fig. 6.

${\bf Fig.~6}-{\rm Variation}$  of threshold voltage with respect to channel length in PD and FD SOI MOSFET

From Fig. 6, It is evident that FD SOI MOSFET is having Lower threshold voltage characteristic as compare to PD SOI MOSFET along with the channel length. Hence FD SOI will be less affected by short channel effects.

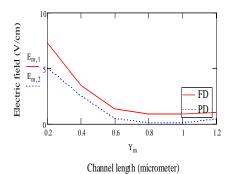

## 5.3 Elctric Field

The electric field distribution along the channel length for PD and FD SOI MOSFET is given as below, which shows that FD SOI MOSFET follows higher electric field characteristic as compare to PD SOI MOSFET.

${\bf Fig.7}-{\rm Variation}$  of electric field along the length of channel for PD and FD SOI MOSFET

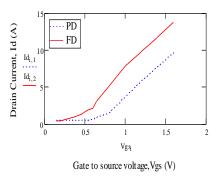

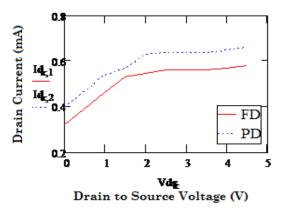

#### 5.4 Drain Current

Drain Current is a very important parameter to determine the current capacity of any device, this can be considered as a output characteristics of a device. Drain Current Characteristics comparison along with the Drain voltage for PD and FD SOI MOSFET can be shown as below in Fig. 8, This Shows that PD SOI MOSFET is having Kink Effect whereas FDSOI MOSFET is free from any kind of Kinking effect

${\bf Fig.\,8}-{\rm Variation}$  of Dain Current with respect to drain to source voltage in PD and FD SOI MOSFET

Drain Current variation along with gate to source voltage for PD and FD SOI MOSFET, which can also be assumed as input characteristic are shown in Fig. 9. It can be seen here that PD SOI MOSFET shows less Drain Current as compare to FDSOI MOSFET for same value of  $V_{gs}$ .

${\bf Fig.~9}-{\bf Variation}$  of Dain Current with respect to gate to source voltage in PD and FD SOI MOSFET

#### 6. CONCLUSION

A 3D modeling and comparison for PD and FD SOI MOSFET has been shown in the paper, this is based on the solution of the Poisson equation. Surface potential, threshold voltage, electric field along with the channel length & Drain Current variations with drain voltage & gate source voltage are given which shows that FD

SOI Performance is giving better Performance results as compare to PD SOI MOSFET.

#### ACKNOWLEDGMENT

This Research Work is recognized by SRM University, Chennai.

#### REFERENCES

- C. Fiegna, H. Iwai, T. Wada, T. Saito, E. Sangiorgi, B. Ricco, VLSI Technol. Dig. Tech. Papers 33 (1993).

- Guruprasad Katti, Nandita Das Gupta, Amitava Das Gupta, IEEE T. Electron Dev. 51 No 7, 1169 (2004).

- C. Mallikarjun, K.N. Bhat, *IEEE T. Electron Dev.* 37 No 9, 2039 (1990).

- Hans van Meer, Kristin De Meyer, IEEE T. Electron Dev. 48 No 10, 2292 (2001).

- H.K. Lim, J.G. Fossum, *IEEE T. Electron Dev.* 30 No 6, 713 (1983).

- Z.H. Liu, C.H. Hu, J.H. Huang, T.Y. Chan, M.C. Jeng, P.K. Ko, Y.C. Cheng, *IEEE T. Electron Dev.* 40 No 1, 86 (1993)

- Jason C.S. Woo, Kyle W. Terrill, Prahalad K. Vasudev, *IEEE T. Electron Dev.* 37 No 9, 1999 (1990).

- 8. Takeshi Shima, Hisashi Yamada, Ryo Luong MoDang, IEEE T. Computer Aided Design of Integrated Circuits and Systems CAD.2, No 2, (1983).

- 9. David Esseni, Antonio Abramo, Luca Selmi, Enrico Sangiorgi, *IEEE T. Electron Dev.* **50** No 12, 2445 (2003).

- S. Veeraraghavan, J.G. Fossum, *IEEE T. Electron Dev.* 36 No 3, 522 (1989).

- Francis Balestra, Mohcine Benachir, Jean Brini, Gerard Ghibaudo, *IEEE T. Electron Dev.* 37 No 11, 2303 (1990).

- Y.A. El Mansy, A.R. Boothroyd, *IEEE T. Electron Dev.* 24 No 3, 254 (1977).

- T.Y. Chan, P.K. Ko, C. Hu, *IEEE Electron Dev. Lett.* 6 No 10, 551 (1985).

- Neha Goel, Ankit Tripathi, Int. J. Computer Appl. 42 No 21, 975 (2012).

- 15. https://en.wikipedia.org/wiki/Moore%27s\_law.

- G.G. Shahidi, et al., IEEE Int. Solid- State Circuit Conference 426 (1999).

- F.Z. Rahou, A. Guen-Bouazza, M. Rahou, Global J. Res. Eng. Electrical Electron. Eng. 13 No 1, Version 1.0 (2013).

- K.W. Temll, C. Hu, P.K. Ko, *IEEE Electron Dev. Lett.* 5, 440 (1984).

- 19. Neha Goel, Manoj Pandey, Bhawna Agarwal, Int. J. Electron. Electrical Computational System 3, No 9 (2014).