## Washington University in St. Louis Washington University Open Scholarship

Engineering and Applied Science Theses & Dissertations

McKelvey School of Engineering

Summer 8-2020

# Investigating Single Precision Floating General Matrix Multiply in Heterogeneous

Steven Harris

Follow this and additional works at: https://openscholarship.wustl.edu/eng\_etds

Part of the Computer and Systems Architecture Commons, Hardware Systems Commons, Numerical Analysis and Scientific Computing Commons, Software Engineering Commons, Systems Architecture Commons, Theory and Algorithms Commons, and the VLSI and Circuits, Embedded and Hardware Systems Commons

#### **Recommended Citation**

Harris, Steven, "Investigating Single Precision Floating General Matrix Multiply in Heterogeneous" (2020). *Engineering and Applied Science Theses & Dissertations*. 536. https://openscholarship.wustl.edu/eng\_etds/536

This Thesis is brought to you for free and open access by the McKelvey School of Engineering at Washington University Open Scholarship. It has been accepted for inclusion in Engineering and Applied Science Theses & Dissertations by an authorized administrator of Washington University Open Scholarship. For more information, please contact digital@wumail.wustl.edu.

Washington University in St. Louis School of Engineering and Applied Science Department of Computer Science and Engineering

> Thesis Examination Committee: Professor Roger Chamberlain, Professor Christopher Gill, Professor Ning Zhang

Investigating Single Precision Floating General Matrix Multiply in Heterogeneous

Hardware

by

Steven D. Harris

A thesis presented to the McKelvey School of Engineering of Washington University in partial fulfillment of the requirements for the degree of

Master of Science

May 2020 Saint Louis, Missouri copyright by Steven D. Harris

2020

# Contents

| Li       | st of           | Tables                                        | v        |  |  |  |  |  |  |  |  |  |  |

|----------|-----------------|-----------------------------------------------|----------|--|--|--|--|--|--|--|--|--|--|

| Li       | List of Figures |                                               |          |  |  |  |  |  |  |  |  |  |  |

| A        | cknov           | ${ m wledgments}$                             | ii       |  |  |  |  |  |  |  |  |  |  |

| Abstract |                 |                                               |          |  |  |  |  |  |  |  |  |  |  |

| 1        | 21st            | Century Challenges in Matrix Multiplication   | 1        |  |  |  |  |  |  |  |  |  |  |

|          | 1.1             | Introduction                                  | 1        |  |  |  |  |  |  |  |  |  |  |

|          | 1.2             | The Current State of the Art                  | 3        |  |  |  |  |  |  |  |  |  |  |

|          | 1.3             | Innovation under Compliance Constraints       | 4        |  |  |  |  |  |  |  |  |  |  |

| <b>2</b> | Mo              | dern Architecture                             | 7        |  |  |  |  |  |  |  |  |  |  |

|          | 2.1             | Parallelism and Concurrency                   | 8        |  |  |  |  |  |  |  |  |  |  |

|          |                 | 2.1.1 Single Data Stream Architectures        | 9        |  |  |  |  |  |  |  |  |  |  |

|          |                 | 2.1.2 Multiple Data Stream Architectures      | 0        |  |  |  |  |  |  |  |  |  |  |

|          | 2.2             | Single-Core to Multi-Core Evolution 1         | 2        |  |  |  |  |  |  |  |  |  |  |

|          |                 | 2.2.1 Von Neumann Architecture                | 2        |  |  |  |  |  |  |  |  |  |  |

|          |                 | 2.2.2 Computing at Scale                      | 3        |  |  |  |  |  |  |  |  |  |  |

|          | 2.3             | Multicore to Heterogeneous Architectures      | 6        |  |  |  |  |  |  |  |  |  |  |

|          |                 | 2.3.1 Alternative Accelerators                | 7        |  |  |  |  |  |  |  |  |  |  |

|          |                 | 2.3.2 Modern GPU Architecture                 | 21       |  |  |  |  |  |  |  |  |  |  |

|          |                 | 2.3.3 GPUs as Accelerators                    | 3        |  |  |  |  |  |  |  |  |  |  |

|          |                 | 2.3.4 GPUs are not the solution               | 25       |  |  |  |  |  |  |  |  |  |  |

|          | 2.4             | Alternative Hardware Accelerators             | 6        |  |  |  |  |  |  |  |  |  |  |

|          |                 | 2.4.1 Application-Speciic Integrated Circuits | 6        |  |  |  |  |  |  |  |  |  |  |

|          |                 | 2.4.2 Field-Programmable Gate Array           | 9        |  |  |  |  |  |  |  |  |  |  |

|          |                 |                                               | 0        |  |  |  |  |  |  |  |  |  |  |

|          | 2.5             | Hardware Agnostic Programming                 | <b>2</b> |  |  |  |  |  |  |  |  |  |  |

|          |                 | 2.5.1 OpenCL Overview                         | <b>2</b> |  |  |  |  |  |  |  |  |  |  |

|          |                 | 2.5.2 Platform Model                          | 3        |  |  |  |  |  |  |  |  |  |  |

|          |                 | 2.5.3 Memory Model                            | 4        |  |  |  |  |  |  |  |  |  |  |

|          |                 | 2.5.4 Execution Model                         | 5        |  |  |  |  |  |  |  |  |  |  |

| 3  | Mat                  | $\operatorname{trix}$ Multiplication                                                                                        | 9 |  |  |  |  |  |  |

|----|----------------------|-----------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|--|--|

|    | 3.1                  | Theory                                                                                                                      | 9 |  |  |  |  |  |  |

|    | 3.2                  | Optimizations                                                                                                               | 2 |  |  |  |  |  |  |

|    |                      | 3.2.1 Naïve                                                                                                                 | 3 |  |  |  |  |  |  |

|    |                      | $3.2.2$ Transposition $\ldots \ldots 4$ | 4 |  |  |  |  |  |  |

|    |                      | 3.2.3 2 Dimensional Block                                                                                                   | 6 |  |  |  |  |  |  |

|    |                      | 3.2.4 Loop Unrolling 5                                                                                                      | 0 |  |  |  |  |  |  |

| 4  | Experimental Results |                                                                                                                             |   |  |  |  |  |  |  |

|    | 4.1                  | Experimental Setup                                                                                                          | 2 |  |  |  |  |  |  |

|    | 4.2                  | Experimental Levels                                                                                                         | 3 |  |  |  |  |  |  |

|    | 4.3                  | Performance                                                                                                                 | 5 |  |  |  |  |  |  |

|    | 4.4                  | Insights                                                                                                                    | 4 |  |  |  |  |  |  |

|    | 4.5                  | Discussion                                                                                                                  | 9 |  |  |  |  |  |  |

| Re | efere                | nces                                                                                                                        | 3 |  |  |  |  |  |  |

| Vi | ita .                |                                                                                                                             | 8 |  |  |  |  |  |  |

# List of Tables

| 2.1 | ASIC Design Flow         | 27 |

|-----|--------------------------|----|

| 2.2 | OpenCL Consistency Model | 34 |

| 2.3 | OpenCL Memory Hierarchy  | 35 |

# List of Figures

| 2.1  | Parallelism vs Concurrency                                                                 |

|------|--------------------------------------------------------------------------------------------|

| 2.2  | Single Instruction Stream, Single Data Stream (SISD)                                       |

| 2.3  | Multiple Instruction Streams, Single Data Stream (MISD)                                    |

| 2.4  | Single Instruction Stream, Multiple Data Streams (SIMD)                                    |

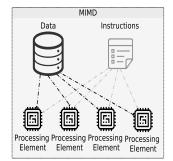

| 2.5  | Multiple Instruction Streams, Multiple Data Streams (MIMD) 11                              |

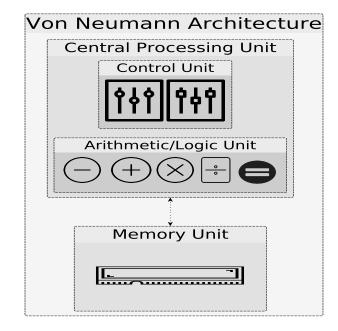

| 2.6  | Von Neumann Architecture                                                                   |

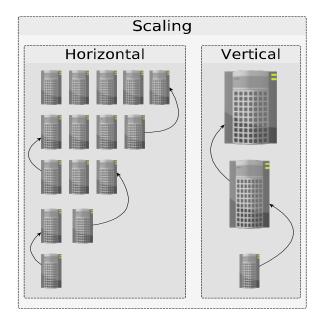

| 2.7  | Horizontal vs Vertical Scaling 13                                                          |

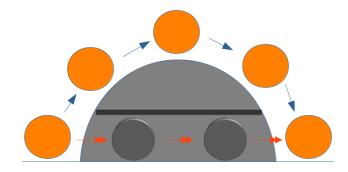

| 2.8  | Quantum Tunneling 15                                                                       |

| 2.9  | Modern Compute Devices                                                                     |

| 2.10 | General Purpose CPU Architecture                                                           |

| 2.11 | CPU vs GPU Architecture                                                                    |

| 2.12 | Streaming Multiprocessor Architecture                                                      |

| 2.13 | FPGA Architecture                                                                          |

| 2.14 | Intel HARP Version 2 CPU+FPGA Architecture                                                 |

| 2.15 | Execution Behavior                                                                         |

| 2.16 | Branching Behavior                                                                         |

| 3.1  | Naïve Algorithm - Matrix Multiplication                                                    |

| 3.2  | Naïve Algorithm - Cache Behavior                                                           |

| 3.3  | Transposition Algorithm - Matrix Multiplication                                            |

| 3.4  | Transposition Algorithm - Cache Behavior                                                   |

| 3.5  | Naïve Algorithm - Blocking 49                                                              |

| 3.6  | Transposition Algorithm - Blocking                                                         |

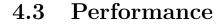

| 4.1  | Performance Results – Execution Time vs Matrix Size                                        |

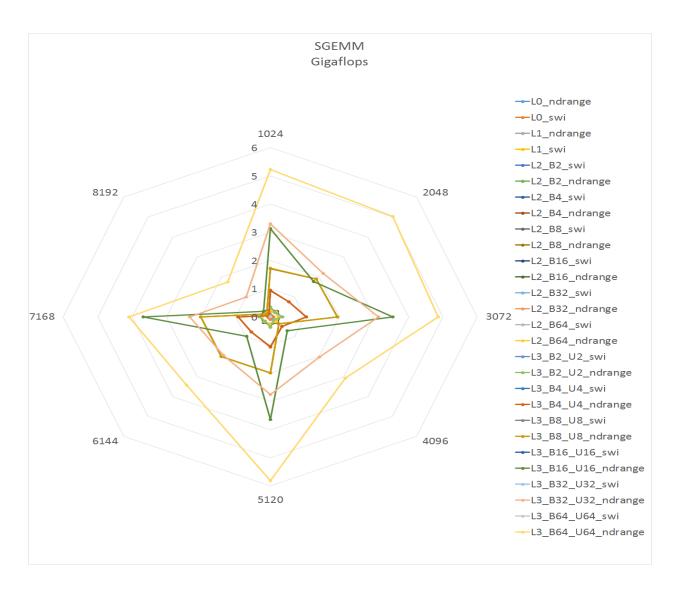

| 4.2  | Gigaflop Performance - Overall                                                             |

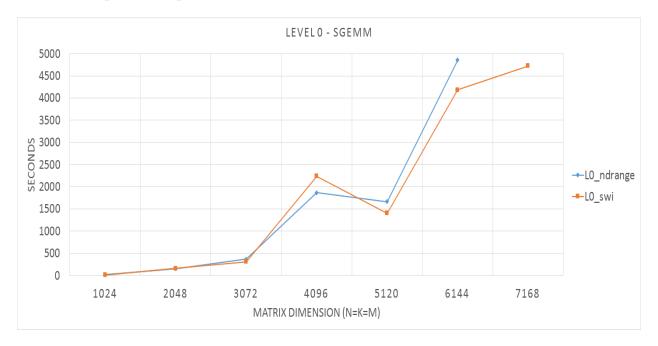

| 4.3  | Performance results – Level 0 (Naïve) Implementation                                       |

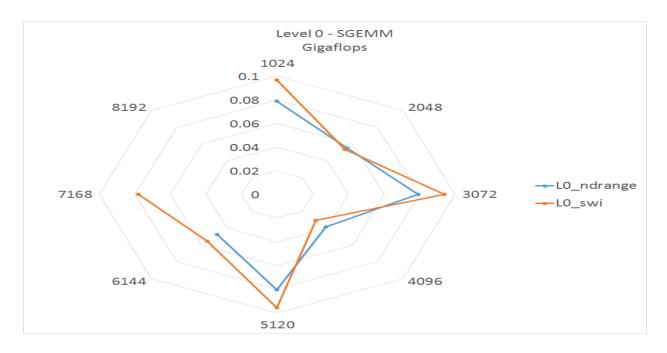

| 4.4  | Gigaflop Performance - Level 0                                                             |

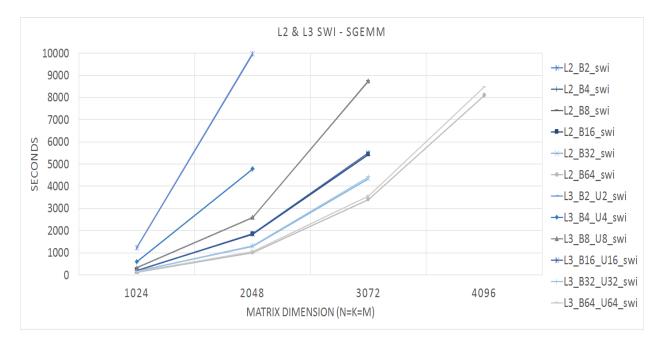

| 4.5  | Performance Results - Optimized SWI Kernels                                                |

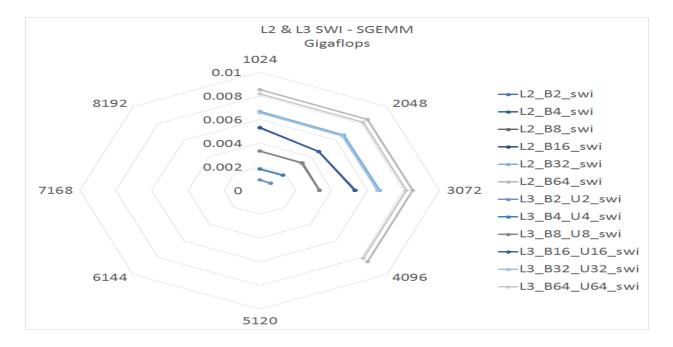

| 4.6  | Gigaflop Performance - Optimized SWI Kernels                                               |

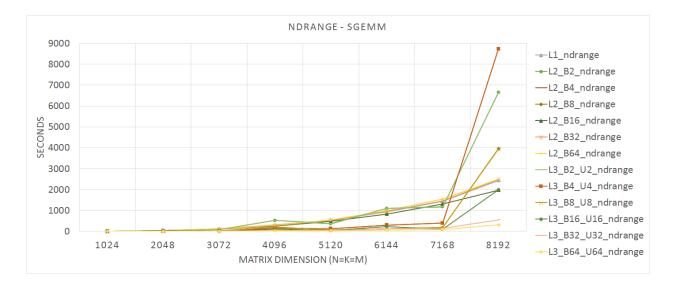

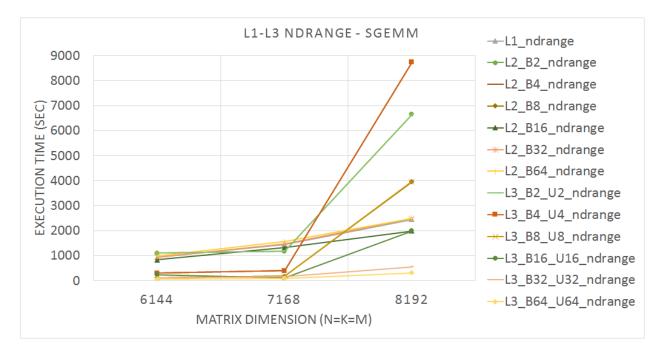

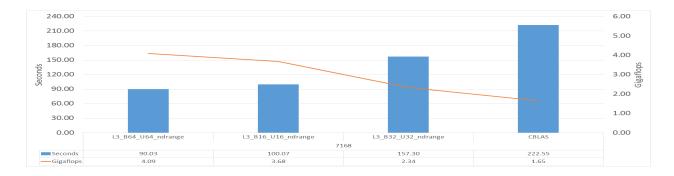

| 4.7  | Performance Results – Optimized NDRange Kernels                                            |

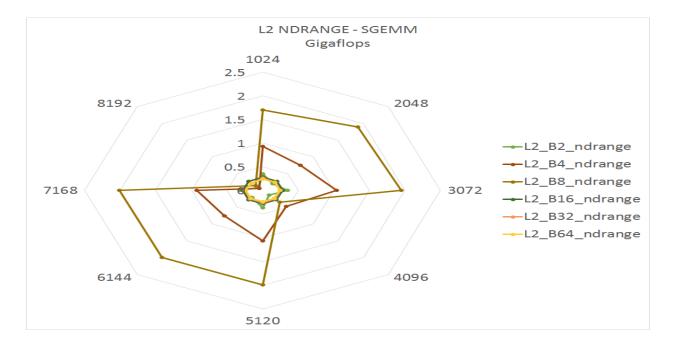

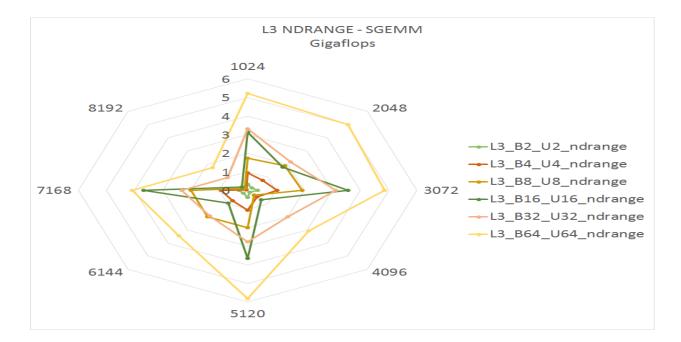

| 4.8  | Gigaflop Performance – NDRange Level 2                                                     |

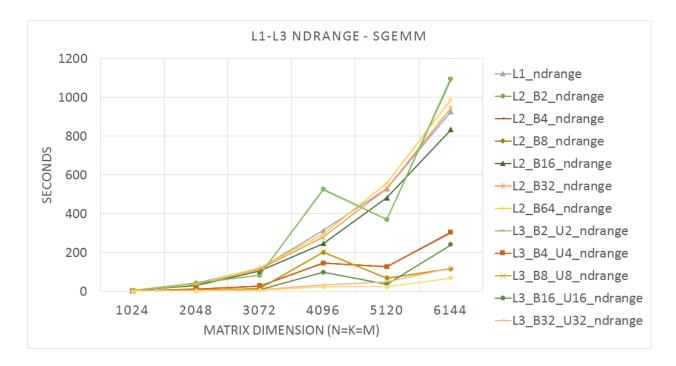

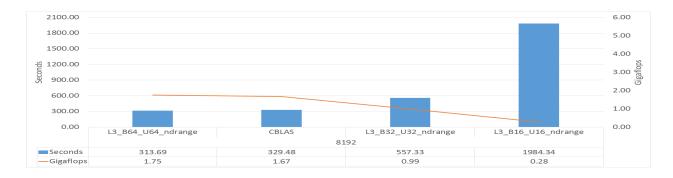

| 4.9  | Performance Results – NDRange Small Matrices $(6144 \times 6144 \text{ and smaller})$ . 62 |

| 4.10 | Performance Results – NDRange Matrices (larger than $6144 \times 6144$ inclusive) 63       |

| 4.11 |                                                                                            |

|      |                                                                                            |

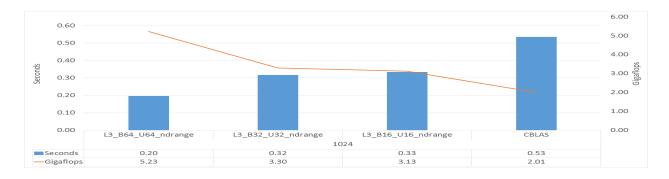

| 4.12 | Top 3 Highest | Performance   | -1024   | x 1024     |  | • |       |  |   |   |   |   | 65 |

|------|---------------|---------------|---------|------------|--|---|-------|--|---|---|---|---|----|

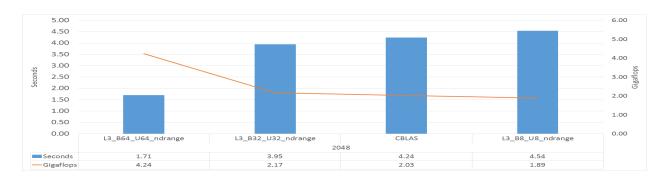

| 4.13 | Top 3 Highest | Performance   | -2048   | x 2048     |  |   |       |  |   |   |   |   | 65 |

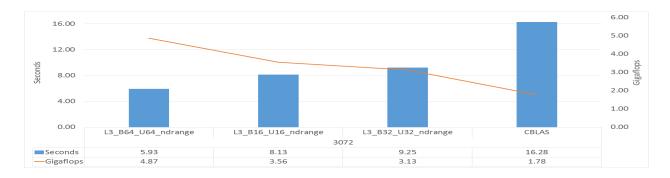

| 4.14 | Top 3 Highest | Performance   | -3072   | x 3072     |  |   |       |  |   |   |   |   | 65 |

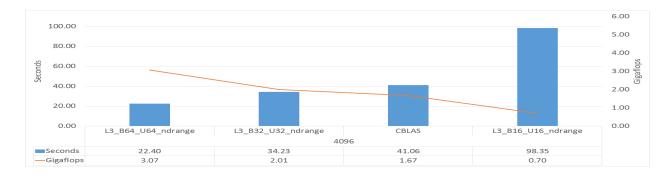

| 4.15 | Top 3 Highest | Performance   | - 4096  | x 4096     |  | • |       |  |   | • | • |   | 66 |

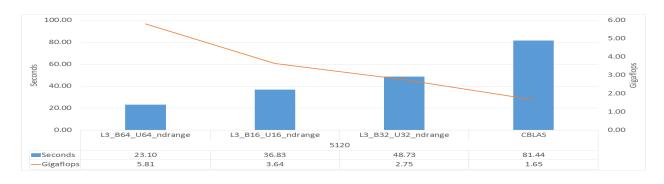

| 4.16 | Top 3 Highest | Performance   | -5120   | $\ge 5120$ |  | • |       |  |   | • | • |   | 66 |

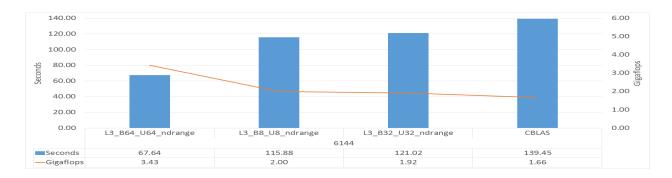

| 4.17 | Top 3 Highest | Performance   | - 6144  | x 6144     |  | • |       |  |   | • | • |   | 66 |

| 4.18 | Top 3 Highest | Performance   | -7168   | x 7168     |  | • |       |  |   | • | • |   | 67 |

| 4.19 | Top 3 Highest | Performance   | -8192   | x 8192     |  | • | <br>• |  | • |   |   | • | 67 |

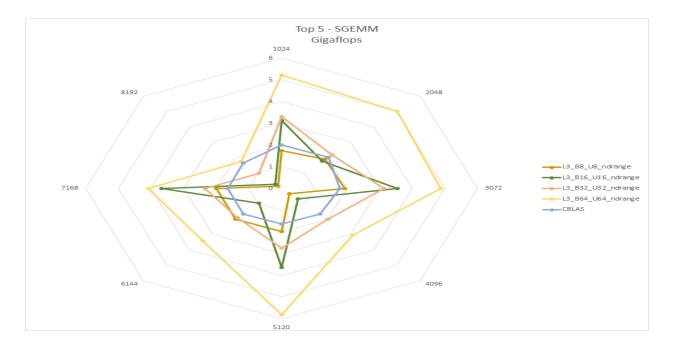

| 4.20 | Top 5 Highest | Performance   | - Gigat | flops      |  | • |       |  |   | • |   |   | 68 |

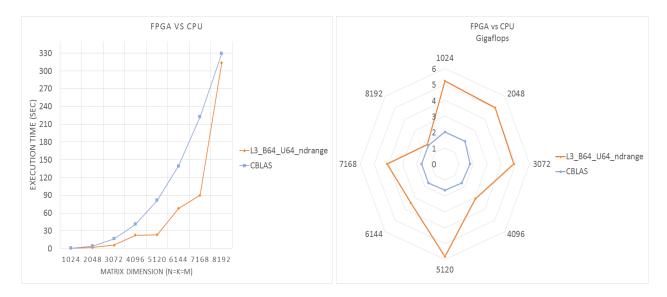

| 4.21 | FPGA vs CP    | U Execution 7 | Гime.   |            |  | • | <br>• |  |   |   |   | • | 68 |

| 4.22 | FPGA vs CP    | U Gigaflops   |         |            |  | • |       |  |   |   |   | • | 68 |

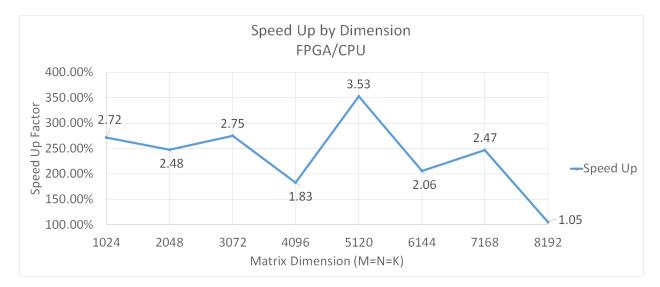

| 4.23 | FPGA/CPU S    | speed Up      |         |            |  |   |       |  |   |   |   |   | 69 |

## Acknowledgments

I would like to thank the Washington University Department of Computer Science & Engineering and the Department of Mathematics and Statistics. These departments have been my home for a very long time and within its walls, I have had the opportunity to work with luminaries that for all their brilliance had equal measures of modesty and patience. I would like to give a very sincere acknowledgement to Dr. Roger Chamberlain, Dr. Chris Gill, Dr. Ning Zhang, and Dr. Mladen Wickerhauser for all of their time, energy, and insights. There support has been invaluable to my progress and the development of this manuscript. I would like to thank the Texas Advanced Computing Center (TACC) at The University of Texas at Austin for providing HPC resources that have contributed to the research results reported within this paper. I would also like to thank the National Science Foundation for supporting my work through NSF CCF1337218 XPS:FP: Real-Time Scheduling of Parallel Tasks, NSF CNS1527510 CSR: Small: Concurrent Accelerated Data Integration, NSF CNS1814739 CSR: Small: Dynamically Customizable Safety-Critical Embedded Systems, and NSF CNS1763503 CSR: Performant Architecturally Diverse Systems via Aspect Oriented Programming.

Steven D. Harris

Washington University in Saint Louis May 2020

#### To My Companions

As I think about all the people, events, and perfectly timed synchronicities that have occurred in order to create this work, the metaphor of standing on the shoulders of giants comes to mind and I chuckle to myself. Instead of being so high that I can see the full landscape above the trees and know where I am headed, this work required a mad dash through a dense rain forest. There were twists, turns, and many holes. There were times when I dodged the branches and when I did not, I was either looking up at the clouds or face to face with flowers, vines, and a few startled eyes. I have reached a small clearing and as I look back, all the thrashing through the forest makes a clear path that very few could miss. I would like to thank my mother and teacher, Maria DeShields, who home-schooled my sister and I, enabling all three of us to graduate from Washington University. She told me to keep running but don't miss all the marvelous sights as I race by. I would like to thank my father, Alvin Harris, who gave me my very first computer, unassembled, in a box filled with components and told me to tuck in my chin, stop flailing like a bird, and read the manual. My sister, Salina Greene, who dragged me into the forest but told me to stop using my head to clear branches. My Rebbe, Randy Fleisher, who told me to always bring Tikkun Olam, even in the wilderness. These teachers are the giants that chuckled and cheered as I raced headlong through the tropics at breakneck speed. I had one other companion on this trip as well, my son Yochanan. Tucked in a tactical baby carrier, reaching for every berry, branch, and thorn; I hope that he can one day walk further down a well-trodden path. To them and all the others, along with the ancestors shaking their heads but patiently watching our travels through this forest, I say thank you.

### ABSTRACT OF THE THESIS

## Investigating Single Precision Floating General Matrix Multiply in Heterogeneous Hardware

by

Steven D. Harris

Master of Science in Computer Science

Washington University in St. Louis, May 2020

Research Advisors: Professor Roger Chamberlain & Professor Christopher Gill

The matrix, a rectangular array of numbers, expressions, or symbols, has become ubiquitous across many genres of science, industry, and business. It is fundamental to mathematics, physics, computer science, and engineering disciplines including cyber-physical systems in which precise simulation and control of safety-critical physical behavior must be managed computationally. By delineating data sets into neatly arranged rows and columns, these arrays can be manipulated to identify and exploit underlying relationships and correspondences between elements. For example, the structure provided by a matrix allows one to perform one of the most fundamental matrix operations: multiplication.

The form, function, and behavior of matrix multiplication has been studied consistently over the years and its properties are well-known. However, the standard matrix multiplication computation performed on modern computer system runs in cubic time  $O(n^3)$ . As modern data sets become ever larger, matrix multiplication becomes ever more time-consuming. Therefore, with each new central processor unit (CPU) or graphics processing unit (GPU), and with the introduction of accelerators such as Field Programmable Gate Arrays (FPGAs), researchers continue to investigate new optimizations to improve the performance of matrix multiplication on modern hardware.

Many optimizations are moving beyond the scope of general-purpose CPUs in order to target emerging architectures. To support this effort, the Khronos Group, a non-profit technology consortium, has developed an open framework called the Open Computing Language (OpenCL). OpenCL allows rapid development of programs, typically called kernels, that can execute across a wide range of heterogeneous platforms including but not limited to CPUs, GPUs, and FPGAs.

In the last few decades, CPU speeds have rapidly diverged from projections given by Moore's law as we approach the limitations of Dennard scaling. Consequently, researchers have put increasing efforts into optimizing GPUs for computationally intensive tasks such as matrix multiplication. The rapid adoption of GPUs for a wide range of computationally intensive tasks has infused the spheres of academia, industry, and engineering with a wealth of literature, implementations, and guidelines for developing performant kernels for matrix multiplication on the GPU.

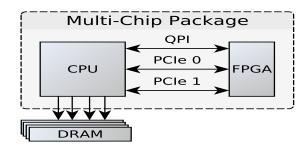

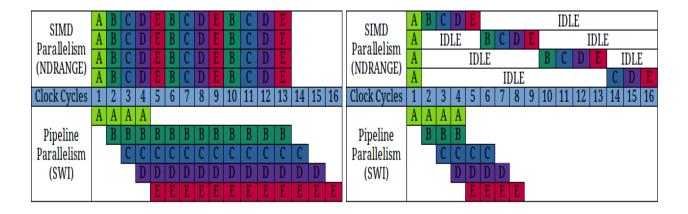

While GPUs excel at most parallel workloads, these devices are not a panacea for complex workloads including computations which may require branching for data dependent conditions. Such workloads must be completed independently by the CPU. Yet, one of the newest emerging technologies attempts to combine the benefits of the CPU and other accelerators into a dynamic, hybrid, reconfigurable processing unit. One realization of this effort comes by way of the Heterogeneous Architecture Research Platform (HARP). This system consists of an Intel Broadwell Xeon CPU combined with an Intel Arria 10 GX1150 FPGA into a Multi-Chip Package (MCP) that enables shared DRAM memory through a single Intel QuickPath Interconnect (QPI) and two Peripheral Component Interconnect Express (PCIe) channels.

With the advent of such hybrid architectures, one of the benefits of OpenCL is the ability to write code for a given task, once, and have it execute across a range of devices in a heterogeneous environment. With a suitable implementation in hand, one should be able to perform complex computations efficiently in any OpenCL compliant environment. As better hardware becomes available, one should be able to execute these kernels on new infrastructures with little, if any, modification to the existing kernels. Using the OpenCL framework as a vehicle of exploration, we have investigated the efficacy of using the current wealth of knowledge and best practices pertaining to matrix multiplication for OpenCL compliant devices on the HARP system and the implications of such methodologies for future heterogeneous architectures.

## Chapter 1

# 21st Century Challenges in Matrix Multiplication

## 1.1 Introduction

Matrix multiplication is a well-known mathematical operation that is critical in numerous disciplines. Even with the nearly exponential increases in computer performance, matrix multiplication remains a persistent challenge and the advent of accelerators (both FPGA and GPU) reopens questions of both expression and optimization. In decades past, users could scale up simply by purchasing the next generation of higher performance processors, but with the breakdown of Dennard scaling, along with thermal and memory barriers, there has been a divergence from the performance predictions previously driven by Moore's law and CPU clock rates have reached a plateau around 4-5 GHz. Under these constraints, both users and manufacturers have elected to scale horizontally. Manufacturers increase the core counts on processors and users aggregate more of these processors into individual servers, and by extension into data center clusters. However, vertical and horizontal scaling of CPU resources has not been enough to keep up with the demands of modern workloads. This performance gap has motivated alternative architectures such as GPU, ASIC, and FPGA solutions.

Some users have bypassed CPU and GPU architectures entirely by adapting their workloads to Application-Specific Integrated Circuits (ASICs), which tend to be more performant than general purpose CPU/GPU devices for specific applications. However, these devices require significant overhead and cannot be modified once created. For devices with strict timing and performance constraints, and requiring application modification in the future, the Field-Programmable Gate Array (FPGA) has become the option of choice. Although it has considerably less cost and development overhead than an ASIC, developing a comparable FPGA based solution may involve a steep learning curve that has traditionally only been accessible to those with knowledge of Hardware Description Languages (HDLs) and digital system design techniques.

That learning curve may be exacerbated in heterogeneous environments due to additional challenges, two of the most prominent being orchestration and data migration. With each device having different architectures, languages, and computational units, it can be challenging to wrangle all the disparate tools and functionalities to create a suitable implementation of an application. This may be further complicated by data migration, wherein pertinent data must shuttle from one device to another in a pipeline or streaming fashion, particularly, across memory hierarchies.

To alleviate these challenges, the Khronos Group, a non-profit technology consortium, has developed an open framework called the Open Computing Language (OpenCL). OpenCL allows rapid development of programs that can execute across a wide range of heterogeneous platforms, including but not limited to, CPUs, GPUs, and FPGAs. The OpenCL framework enables computation orchestration on existing systems and its compatibility with the Intel High Level Synthesis compiler allows users to architect new designs for reconfigurable hardware using C/C++.

As the world shifts toward more application-specific accelerators for modern workloads, Intel has developed an alternative accelerator in the form of a unified hybrid CPU+FPGA. One realization of this effort is the Heterogeneous Architecture Research Platform (HARP). Version 2 of this system consists of an Intel Broadwell Xeon CPU combined with an Intel Arria 10 GX1150 FPGA into a Multi-Chip Package (MCP) that enables shared DRAM memory through a single Intel QuickPath Interconnect (QPI) and two Peripheral Component Interconnect Express (PCIe) channels. Using the HARPv2 as a vehicle for exploration, we investigate the design space of matrix multiplication, using several existing cache-oriented optimizations to better understand the performance portability of OpenCL and the implications for such optimizations on this and future heterogeneous architectures. Across a range of matrix sizes, we show that several classic optimizations designed for traditional caches are also effective on the HARP system. This includes transposition, blocking, and loop unrolling. When all optimizations are included, our implementations consistently outperform the optimized standard library implementation (CBLAS). However, there are still considerable variations in performance, across both matrix size and various tuning parameters, that are not yet well understood and that warrant further investigation.

## **1.2** The Current State of the Art

Over the past decade, heterogeneous computing has typically implied a computation that is partitioned across one or more devices containing a combination of CPUs and GPUs. For CPU computations, there are a wealth of libraries and tools, such as Open Multi-Processing (OpenMP) and the Basic Linear Algebra System (BLAS) that facilitate the rapid development of high-performance computations. For GPUs, the dominant solutions come from industry leaders such as NVIDIA who manufactures the most popular GPUs as well as being the author of CUDA, the well-known parallel computing platform [1, 27, 38, 21, 14].

In a general sense, these solutions simplify development. Developers have invested considerable time and effort into understand the underlying hardware architectures, identifying optimal execution methods, and generalizing these operations. Instead of investigating the myriad of hardware specifications, developers have identified generalities between target architectures to use across various classes of devices. By having a solid grasp of the computational architectures, developers provide users with extensions, application programming interfaces, and tools that organize the data, computation, and communication efficiently across these devices. Yet, developers also share the burden of the revision process: particularly, as hardware evolves, users and developers alike are required to pivot to new hardware, frameworks, and specifications to take advantage of additional features incorporated into next-generation GPUs. Developers perform the heavy-lifting for users that may not have the time or background to understand how an algorithm may augment performance or the resources to create interfaces to operate these devices.

While users have the flexibility to perform tasks that may actually degrade performance, developers typically provide users with best-practices for a given class of tasks [19]. Instead

of having to reinvent the wheel, users with these tools can rapidly develop solutions that fully utilize these devices with little effort. However, even with such tools many challenges arise when users want to use multiple devices for a given computation. With different computational units, memory hierarchies, and communication methods, users can spend considerable time on data manipulation, coordination, and orchestration. Irrespective of the sophisticated programmatic solutions developed for a given computation, data migration also can have significant impacts on overall performance.

These challenges bring out new questions concerning algorithms, architectures, and computational workflows. For example, are there tools that allow user to orchestrate a computation and reconfigure all available resources in the most efficient manner? This is one goal that researchers are working towards with solutions such as OpenCL for orchestration and hybrid accelerators for reconfigurable architectures. However, such question pose a more fundamental question: Are we developing solutions that target the computation or the hardware?

## **1.3** Innovation under Compliance Constraints

Mathematical concepts such as systems of equations, linear transformations, and scalar products are prevalent in many areas of science. One of the most pertinent of these concepts is that of matrix multiplication. Matrix multiplication has been studied, analyzed, and established for decades. It sits at the core of many numerical algorithms, scientific computations, and big data workloads.

Much like fundamental arithmetic operations, many would consider the "problem" of matrix multiplication to be solved: we do not often consider the efficiency of arithmetic operations or review new developments in their optimizations, assuming suitable performance of such arithmetic operations. That is, we assume that these operations can be performed as fast as the hardware (i.e. silicon switching) will allow. When we consider multiplication and division, we often focus more on precision than on efficiency. We would like to think that the operations may run slightly slower than addition or subtraction, but that ultimately the main challenge is one of precision. However, this comparison could not be farther from the truth: the performance of matrix multiplication remains an open problem. The challenge of optimizing the performance of matrix multiplication has been investigated by Strassen [18], Bini [4], and Coppersmith & Winograd [8], among others [55]. Many resulting algorithms have been implemented on computer systems since the 1970s, and yet each year the scientific communities of the world still try to find more efficient ways to perform this well-known mathematical operation [22, 5, 7, 2, 50, 23, 16, 34, 33, 36, 45]. Given that the efficiency of matrix multiplication on modern computer systems is still in a state of flux, what does it mean when a new method arrives that is touted to be more efficient, simpler, faster, or offering more calculations per unit of time? These definitions are all suitable classifications for efficiency. However, efficiency in the context of matrix multiplication has a particular metric that complements any other measurement of efficiency: utilization. The algorithm with the highest level of efficiency is often tightly coupled with the utilization of the underlying hardware resources. Because of the relationship between efficiency and utilization, each matrix multiplication algorithm has to be specifically tailored to the underlying architecture.

Given the multitude of computer systems on the market and the likely new architectures of the future, it thus seems necessary to continue refactoring implementations indefinitely. There are many reasons why we cannot now simply write a program once and (without further modification) see improvements in precision, performance, and efficiency as better technology on which to run the program becomes available: we write our programs to a specific architecture as opposed to writing code solely to address the computational problem; our primitive data types may be selected from predefined capacities; our algorithms reflect the parallelism of our compute units; and our function calls, methods, and tools are often selected *a priori* based on available languages, operating systems, or architectures.

To overcome those limitations of the current state of the art, it is appropriate to consider what computations would look like if we could simply write a sufficient algorithm and the system then could dynamically orchestrate the underlying architecture to fulfill the algorithmic requirements.

The experiments presented in this work offer a preliminary step towards that vision, with a particular emphasis on domain specific architectures and heterogeneous solutions, by examining performance of matrix multiplication across different relevant design and architectural factors. By investigating state of the art techniques for a subset of matrix multiplication challenges, we have identified some areas where new ideas about architectures and assumptions affecting matrix multiplication may prove useful.

## Chapter 2

## Modern Architecture

In 1972, Intel released the first commercial 8-bit processor called the 8008. This processor was formed from 3,500 transistors that ran at speeds up to 800 kHz. Using the (then advanced) 8-bit architecture, this processor was capable of accessing up to 16 KB of RAM. In stark contrast, today's modern processors are comprised of over 8,000,000,000 transistors and can reach speeds of up to 4,400,000 kHz (4.4 GHz). Using modern 64-bit architectures, these processors can access over 2,000,000,000 KB (2TB) of RAM. Since the inception of the 8008, the performance of microprocessors has increased dramatically. A well-known predictor of processor performance has been Moore's law which proposed that the number of transistors on microprocessors would double every 18 months. For a time, this prediction held true and society reaped the benefit of increased performance year after year. However, since about the mid-2000s processor speeds have plateaued due to constraints imposed by physics and the laws of thermodynamics. While many would argue that Moore's law is dead, each time this argument arises engineers and scientists develop new ways to bring its predictive power back to life. In this incarnation, Moore's law is reborn again via multi-core processors.

## 2.1 Parallelism and Concurrency

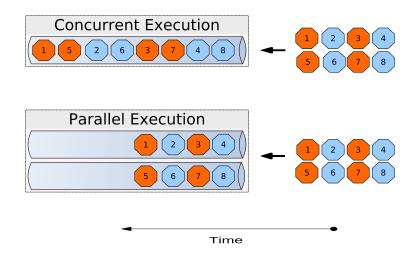

Figure 2.1: Parallelism vs Concurrency

While many programs have segments of sequential code, there are often opportunities to take advantage of parallelism in code segments. An important part of computer processing involve the concepts of *parallelism* and *concurrency*. While these two terms are often used interchangeably, parallelism and concurrency are not equivalent. Parallelism is an execution model wherein two or more tasks can be executed simultaneously. However, the concurrent task model allows tasks to progress at the same rate even if executed at different times. Concurrent tasks are typically executed in an interleaved fashion which allows two or more programs to execute in lock-step with each other. These execution models are shown in figure 2.1. In the most general sense, a computer consists of a combination of CPU, Memory, Storage, and various input and output devices which utilize a communication system (a.k.a. a bus) that is used to transfer data between components inside the computer system.

Traditionally, all computer processing units consist of control, arithmetic logic, and memory management units. The control unit orchestrates all the processes occurring inside the CPU. From execution of program instructions to the ALU and memory management, all processes are governed by the control unit. The ALU performs all arithmetic and bitwise logic operations. The memory management unit controls access and communication with memory. CPUs are typically synchronous circuits which utilize a clock signal to synchronize their operations. Each and every operation occurs on a "tick" of a clock cycle. This clock signal arises from external oscillator circuits that generate a fixed number of pulses per second in the form of periodic square waves. The frequency of these pulses is how we derive the speed of the processor and the number of instructions that the CPU can perform per second. To simplify things, we will define a processor as containing a Processing Element (PE) which manages the execution of instructions, an Instruction Pool which stores those instructions, and a Data Pool which stores the data which the instructions will act upon. Over time, processors have improved to take advantage of parallelism using different methods to control both data and execution within the CPU.

In 1966, Dr. Flynn proposed a method for classifying digital computers, which is now referred to as Flynn's Taxonomy [13]. The primary classifications can be subdivided into two groups: Single Data Stream (SISD, MISD) and Multiple Data Stream (SIMD, MIMD) architectures.

### 2.1.1 Single Data Stream Architectures

Single Instruction Stream, Single Data Stream (SISD)

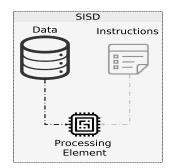

Figure 2.2: Single Instruction Stream, Single Data Stream (SISD)

As is shown in figure 2.2, a traditional single-core processor would fall into the Single Instruction Stream, Single Data Stream (SISD) category. This specific architecture processes a single stream of data in sequential order. To process large amounts of data, the user would be limited to using recursive techniques or loops in order to iterate through the data. This architecture has no parallelism.

#### Multiple Instruction Streams, Single Data Stream (MISD)

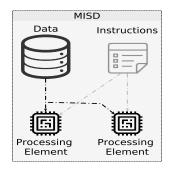

Figure 2.3: Multiple Instruction Streams, Single Data Stream (MISD)

In contrast to this is the Multiple Instruction Streams, Single Data Stream (MISD) architecture, a type of parallelism akin to pipe-lining. Multiple processing units perform separate operations on the same data set. This method is fault-tolerant as the same instruction can be executed by different PEs in order to ensure reliability. However, this architecture has been superseded by multiple data stream architectures.

## 2.1.2 Multiple Data Stream Architectures

Single Instruction Stream, Multiple Data Streams (SIMD)

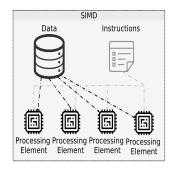

Figure 2.4: Single Instruction Stream, Multiple Data Streams (SIMD)

In terms of modern CPUs, one would be hard-pressed to find a system which did not contain more than one core. That is to say, most modern CPUs are multi-core processors. These processors have a Single Instruction Stream, Multiple Data Streams (SIMD) architecture, shown in figure 2.4, which allows them to perform the same instruction on multiple data sets simultaneously. This architecture exploits *data level parallelism*.

#### Multiple Instruction Streams, Multiple Data Streams (MIMD)

Figure 2.5: Multiple Instruction Streams, Multiple Data Streams (MIMD)

SIMD was expanded to take advantage of multiple instructions as well as data. CPUs of this type employ Multiple Instruction, Multiple Data architectures (MIMD) as shown in figure 2.5. These processors contain multiple PEs which work independently and asynchronously allowing the execution of various instruction on unique data sets simultaneously. This is typically referred to as *task level parallelism* according to Flynn's taxonomy. A subcategory of MIMD is Single Program, Multiple Data (SPMD) wherein a single program is executed across all PEs.

## 2.2 Single-Core to Multi-Core Evolution

### 2.2.1 Von Neumann Architecture

Figure 2.6: Von Neumann Architecture

General purpose CPUs have advanced significantly with the advent of additional cores, low power usage, and additional extensions. As shown in figure 2.6, the CPU consists of a Control Unit and Arithmetic Logic Unit (ALU) connected via data bus to the Memory Unit. The Control Unit manages communication with the ALU and interprets program instructions. The ALU receives data/commands from the Control Unit in order to execute arithmetic and logic instructions on the received data. This design is known as the Von Neumann architecture. Data and instructions are stored in the memory subsystem in the same format. This allows the contents of memory to be defined by the system interpreting the memory location. For instance, a program compiler can translate user-defined programming pragmas into machine language that is stored as ordinary data but can also be executed by the CPU directly as instruction directives. This makes Von Neumann architecture flexible and versatile but it has one glaring disadvantage, a phenomenon known as the Von Neumann bottleneck which will be discussed later. This architecture places specific limits on the programmatic solutions as the execution of instructions are inherently sequential. Fundamentally, modern general purpose CPUs have not diverged from the original Von Neumann architecture since its inception which shows both the longevity of this architecture as well as the legacy of persistence computational constraints.

#### 2.2.2 Computing at Scale

Figure 2.7: Horizontal vs Vertical Scaling

General-purpose architectures have developed over the years and are deployed in many industries based on the workload targets. However, a little over a decade ago, in an era dominated by the seemingly ever-increasing CPU frequencies, many industries found that if their computer systems could not keep up with the computational demands, they would defer to the old adage of "wait until next year", in order to upgrade to a faster CPU by utilizing vertical scaling. Some industries would take a slightly different approach by taking advantage of horizontal scaling which would incorporate additional CPUs in networked servers to increase processing power, as is often found in High Performance Computing (HPC) environments. However, horizontal scaling in this fashion is expensive and cost prohibitive for many industries. Such vertical and horizontal scaling, shown in figure 2.7, were not limited to the industries which adopted the processors, but were also adopted in processor fabrication as well.

The rapid advances in processing power were due to the ability to take advantage of transistor scaling that enabled the minimization of transistors. Consequentially, the semiconductor industry took advantage of horizontal scaling afforded by transistor minimization in order to pack more transistors into integrated circuits (ICs) and thereby improve performance. For several decades, the number of transistors per square inch on an integrated circuit (IC) doubled nearly every two years, corresponding roughly to the projections by Dr. Moore. Such rapid increases in transistor scaling elicited an unparalleled effervescence of computational power and processor diversity. As the size of transistors became smaller, transistor density and switching frequency increased. Coupling the transistor improvement with significantly cheaper manufacturing costs created a perfect storm of events that led to rapid expansion in computer technology to such an extent that system integrators were barely able to assemble existing hardware before newer and more powerful integrated circuits (ICs) were introduced to the market.

Dr. Moor's projections seemed likely to extend far into the future, but two challenges emerged that caused actual results to diverge from the long held predictions: thermal runaway and quantum effects. As subsequent chips incorporated smaller and more tightly packed transistors, it was determined that these chips could maintain the same amount of power while operating at higher frequency while consuming less voltage. That is, as transistor feature size decreased, the power density remained relatively constant. This idea is commonly referred to as *Dennard Scaling*. However, the tremendous benefit of Dennard Scaling overlooked a major component: leakage current. Dennard scaling did not take into account leakage current which serves as a baseline for power per transistor. Consequently, the tightly packed chips with electrons moving at increasing speeds through smaller and smaller silicon circuits, contributed to higher and higher power densities. Given that power density does not scale with size, this generated substantial amounts of heat that would become impossible to dissipate with common airflow cooling methods. The only option for manufacturers was to limit either the number of transistors or the frequency of the processor. Due to Dennard Scaling, processor frequencies have not exceeded roughly 5 GHz. With further transistor scaling, further challenges emerged which are related to smaller feature sizes. Transistors lie at the heart of a processor and are comprised of electrical leads called the emitter, collector, and base. In computer systems, these transistors are responsible for switching: that is, moving between on and off states to encode ones and zeroes. In switching implementations, the electrical leads take on additional terminology with the emitter referred to as the source, the collector as the drain, and the base as the gate. These terms evoke a notion of current or fluid flow. The most critical component that enables the action of switching revolves around the gate, which controls the flow of electrons through the transistor. As transistors are scaled to smaller and smaller feature sizes, the thickness of the gates decreases as well.

Figure 2.8: Quantum Tunneling

Thinner gates can lead to a phenomenon known as quantum mechanical tunneling wherein electrons can pass through the gate medium of a closed gate. In Classical Mechanics, if an electron has enough energy to overcome the potential energy at the top of the barrier, the electron will be able to traverse the barrier. Even if the electron does not have enough kinetic energy to overcome the barrier, however, quantum effects may allow the electron to tunnel through the barrier. Figure 2.8 shows an example of quantum tunneling with the blue arrows indicating the Classical Mechanics trajectory and the red arrows indicating the Quantum Mechanical trajectory.

Quantum tunneling effects can contribute to a significant gate leak current that increases exponentially as the gate thickness decreases. The break down in Dennard scaling, undesirable quantum effects, and limitations on clock frequencies led many researchers to assume that Moore's Law was coming to an end. However, innovation would breathe new life into Moore's Law through the introduction of multi-core systems.

## 2.3 Multicore to Heterogeneous Architectures

Horizontal scaling, it would seem, has developed a lasting permanence in the computer industry. As noted previously, when computations required additional computing power, one could either scale vertically through the purchase of faster processors (if available) or scale horizontally with the acquisition of additional servers. The semiconductor industry took the horizontal approach and with transistor miniaturization, more processors could fill the same horizontal space on a microscopic level. With limitations curtailing transistor minimization, the semiconductor industry developed a new approach to the challenges which threatened to end Moore's Law. Instead of creating dense high frequency single core processors, they began to develop additional cores which ran at comparable frequencies as single core processors and the era of multi-core processing began. The increasing numbers of processor cores benefited many workloads but did little to help with sequential tasks.

Nevertheless, multi-core processing enabled the partitioning of workloads onto several processors and also introduced the notion of *dark silicon* [52]. The semiconductor industry designed the multi-core processors so that only a fraction of the processors was actually operating on a workload at any given time which greatly reduced the power constrains that were leading to thermal runaway and other complications. With many processors cores working on a subset of a given workload, some processors were running while other processors were idle or "dark". The dark silicon paradigm increased the industry's ability to improve power efficiency in computer systems. Yet, the growth of multi-core systems has lagged far behind architectural needs for massive computationally intensive workloads which in turn has opened the door to alternative architectures.

### 2.3.1 Alternative Accelerators

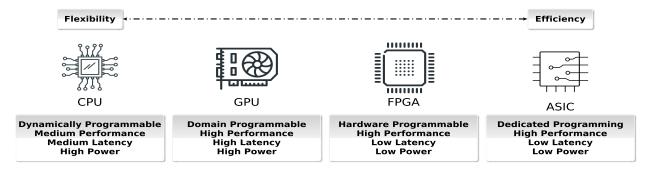

Figure 2.9: Modern Compute Devices

Given the demand for viable solutions to support computationally intensive workloads many industries have attempted to scale horizontally by adding additional CPUs in networked servers to increase processing power. However, scaling in this fashion is expensive and cost prohibitive for many industries. Not to mention, since about 2006, processor speeds have shifted from what appeared to be exponential growth to logarithmic growth and we find ourselves close to a plateau in processor frequency. Increases in the number of transistors per square inch for general purpose CPUs according to Moore's law predictions has declined in recent years. The International Technology Roadmap for Semiconductors (ITRS) has warned that transistor minimization may reach its limit in 2021 [52]. While there has been a steady increase in processing power of general-purpose CPUs, the doubling of performance according to Moore's law projections no longer holds. In light of this, there is a need for new technologies and programming paradigms to offset some of the deficiencies in performance scaling.

In recent years, many have turned towards heterogeneous computing to satisfy computational demands. The most prominent technologies in terms of hardware have been GPUs, FPGAs, and ASIC. Of the three, GPUs offer a readily available option. They are commonly found in most modern desktops and laptops, offering competitive raw processing power as compared to their CPU counterparts [26]. GPUs are capable of processing computationally intensive workloads that would typically be performed by the CPUs. The underlying hardware features of GPUs have been exposed by manufacturers to support parallelism in processing that can be orchestrated by the programmer. While traditional superscalar processors support

many hardware features such as branch prediction, instruction pipelining, and out-of-order execution, GPUs do not. However, what GPUs lack in terms of execution model versatility, they compensate for with exceptional performance.

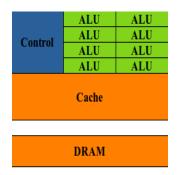

For the past few decades, general purpose CPUs have been tailored almost exclusively towards serialized workloads. Examples of such workloads include compilation, network communication, and user interactions. There have been advances in recent years towards parallel workloads with the inclusion of multi-core architecture for such purposes. However, CPU cores continue to be optimized for single-threaded performance. Consider an arbitrary x86 CPU with 8 cores, hierarchical shared memory caches, with a max frequency of 4-5 GHz. If this example CPU is made with a 14 nm process, each chip will have approximately 2 billion+ transistors consuming around 35W of power. This example processor is shown in figure 2.10 (notice the portion of the die area used for the ALUs of the processor).

Figure 2.10: General Purpose CPU Architecture

With so little of the die area committed to arithmetic computations, it is evident why additional CPUs are required for intensive computations. The remaining space of the die and the main contribution to heat comes from multiple caches, decoders, and additional extensions while not visible on the die, contribute significantly to the increase in single thread performance. One of the primary contributors to increasing single thread performance is the concept of speculation. Speculation optimizations go far beyond speculative execution (the execution of instructions prior to determining if the resulting output will be needed for future operations) into such areas as data caches, branch predictions, and out-of-order processing. Speculation allows the system to anticipate with a given probability the need for data. This in some sense could be thought of as a bet that a certain portion of the data will be in high demand in the near future.

These speculative optimizations may work well depending on the workload, particularly in cases where the data has high locality, significant branching, and a variety of operations. However, these optimizations come at the expense of precious die space which could otherwise be used for additional processing units. If the workloads tend to be of a scientific nature such as similar sequential operations, then these optimizations remain underutilized, merely hoarding precious die space and consuming countless watts of thermal design power.

Many companies elect to use advanced process technologies to achieve higher operating speeds, but increasing the clock rate comes at a price. Particularly, transistors operating at higher speeds lead to higher operating temperatures. Overclocking processors requires significant adjustments in heat dissipation techniques beyond air cooling. Water or nitrogen cooling is unfeasible for most users and companies for that matter. In addition to thermal issues, high speed processors also contribute to increased power leakage and are cost prohibitive to develop. In light of these issues, processor speeds have leveled off around 4 GHz to date but other methods have been employed to increase the performance of these processors up to a maximum of 5 GHz.

It should come as no surprise that micro-architecture optimizations can contribute significantly to performance of these chips. The typical methods used fall into two class: *dual-issue core* and *multi-issue core* [43]. The dual-issue core is a superscalar architecture which allows the processor to execute up to two instructions per clock cycle. In many cases, there is a set of specifications which define which instructions can be executed together. Those rules often define explicitly what operations can be performed simultaneously on particular data types. For instance, two integer operations or one integer operation and one floating-point but not two floating-points can be executed simultaneously. Most modern programs typically execute in sequential order and because of this, the dual-issue core can often exploit the intrinsic instruction-level parallelism (ILP) found in many programs for a significant performance gain. While the processor cannot always exploit ILP in every program, there is typical enough ILP in most programs to take advantage of this functionality. Multi-issue cores follow the same principles but have more execution units to utilize simultaneously. Modern processors often utilize the multi-issue architecture and advanced features of an x86 processor such as multi-branch prediction, speculative execution, and simultaneous multi-threading among others. Most of these performance enhancements are used to optimize single-threaded performance of the device. New methods are being used to squeeze as much performance out of these processors as possible given that manufacturers have been hitting the wall or limitations for Von Neumann architecture. There are actually three particular types of "walls" that manufacturers encounter for this architecture:

#### 1. Power

- Increased frequency leads to increased power density.

- Difficult to mitigate dynamic and static power dissipation.

- Diminishing return on performance for higher power density.

#### 2. Memory

- Compute bandwidth continues to outpace memory bandwidth.

- Data migration can become the limiting factor on performance.

- Exacerbated by increasing data set sizes.

#### 3. Instruction-level parallelism

- Increasingly difficult to find parallelism in single instruction streams.

- Diminishing returns on additional ILP hardware.

- Functional Units remain idle waiting for memory access.

Many programs have sequential execution which allows the CPU to exploit the natural ILP of these programs but the performance is program specific. In terms of the *power wall*, adding more and more transistors to the processor and running them at high speeds has increased the power dissipation of the processors far beyond the capacity of inexpensive cooling techniques. This *memory wall* also has another name, the Von Neumann Bottleneck. In the past few decades, processor speed has increased dramatically but the performance of memory has not kept pace. Much of the improvements in memory have been attributed to increased density (i.e. higher memory capacity). With the advent of faster processors, the CPU spends an increasing amount of time waiting for data to be fetched from memory. Irrespective of the processor, its speed is in effect limited by the rate of transfer from memory for most operations. A faster processor would simply mean increased idle time. Thus, memory has secured its place as the primary bottleneck in Von Neumann architectures.

Several solutions are used to alleviate the intensity of the bottleneck. The most prominent ones are Larger Caches, Hardware Prefetching, Software Prefetching, and Multi-Threading [12]. Increasing the cache size can be prohibitively slow and only efficient if data has both temporal locality and fits into the cache. Hardware Prefetching cannot be optimized for each application and its functionality is based on the behavior of the program execution at runtime. Software Prefetching typically excels for iterative loops with regular array access, but it requires source code and manual programmer intervention which is not often feasible, especially in the case of precompiled programs and closed source. Finally, Multi-threading solves the problem of throughput but ultimately does not contribute to decreases in memory latency.

The present solutions can only take this so far but in order to traverse these walls, many have chosen to look to a paradigm shift in terms of hardware architecture. The Von Neumann architecture has securely reserved itself a place in computing. However, as researchers look to move beyond the inherently sequential processing paradigm for demanding applications, they look to incorporate modern GPUs.

### 2.3.2 Modern GPU Architecture

The Graphics Processing Unit (GPU) has changed dramatically since its inception. It began as a specialized device used to accelerate the rendering of computer graphics for visual displays. To output images to the screen via the frame buffer, the GPU used fixed-function 3D graphics pipelines to quickly process pixel data independently and in parallel from vertex, texture, and lighting data. This data needed to be processed quickly but unlike CPUs, there was less necessity for minimal latency and more of an emphasis on high throughput, as the visual acuity of humans is less sensitive and can operate on longer time scales than other critical systems. The effort to have maximum throughput was necessary as the images required the GPU to process millions of pixels at a time and in the case of real-time rendering, billions of pixels per second. The process of image rendering has a fundamental level of parallelism.

Data input to the GPU goes through a series of pipeline tasks. The output of each pipeline stage is used as an input to the next stage of the pipeline. Operating on data simultaneously in consecutive tasks, the pipeline reveals the task parallelism of the GPU architecture. As each stage of the pipeline operates on multiple data inputs simultaneously, this exposes the intrinsic data parallelism capability of the GPU. The first programs written for GPUs were geared towards graphics processing and utilized languages similar to assembly that mapped user specified input data to particular operations. Researchers began investigating alternative computational methods for their parallelized workloads and began to re-purpose GPUs for such endeavors. Using GPUs for such tasks required researchers to reorganize their programs into a graphics processing format [25, 28, 41]. Writing programs for scientific computations as a graphics processing tasks proved difficult. The resulting programs were riddled with bugs that were hard to isolate and the code was challenging to debug, optimize, and develop.

However, research began to indicate that GPUs offered better performance for certain algorithms compared to their CPU counterparts, and the adoption of GPUs for computations increased [6, 35, 9]. With this new found interest in GPUs came the development of high level languages which simplified programming tasks and decreased the burden of dependence on knowledge of the underlying graphics systems in order to create programs. While these graphics programming languages allowed many researchers to show performance improvements of GPUs over CPUs for particular workloads, they were ultimately deprecated when hardware vendors released their own implementations for their hardware. The GPUs first conceived as simple graphics processing devices have evolved into indispensable tools for deep learning, artificial intelligence, bioinformatics, and essentially any computationally intensive process which requires a high level of parallelism [40, 1, 27, 51, 38, 21].

Figure 2.11: CPU vs GPU Architecture

Before the advent of GPU computations, mathematical libraries were used to create performant computations on general purpose CPUs. Developers spent considerable time analyzing CPU architectures and memory hierarchies to develop optimizations for general purpose hardware [10]. However, CPUs lack the necessary computational units to process large data sets in parallel given their high frequency but low core counts. GPUs on the other hand have low frequency but high core counts that are specifically designed to perform floating point computations for 32 and 64 bit data types. A comparison of the two architectures can be seen in figure 2.11. Developers have analyzed GPUs to create specialized libraries that take advantage of GPU architecture [3, 11, 39]. The computational power and specialized architectures leveraged by GPUs over CPUs for parallel workloads explains the rapid adoption of GPUs for ML and Big Data workloads today [38].

### 2.3.3 GPUs as Accelerators

The modern GPU has moved far beyond the display of graphics for visual applications. While some GPUs continue to display graphics, specialized GPU cards have been developed (sans graphics port) to utilize the GPU solely for the purpose of intensive computations. Many manufacturing companies create GPU devices, with the top manufacturing companies being Intel, AMD, and NVIDIA. Though Intel is the largest manufacturer, their graphics focus has been toward integrated and low-performance cards found in laptops and economy workstations and servers. The remaining two suppliers, AMD and NVIDIA, are well known for their high performance cards. Of the two, NVIDIA appears to be the dominant supplier of cards for academic and industrial environments. NVIDIA also happens to be the maker of CUDA, a programming language developed for their line of GPUs. Newer GPUs are composed of multiple GPU processing Clusters (GPCs), Texture Processing Clusters (TPCs), Streaming Multiprocessors (SMs), and memory controllers. Differing from standard server architecture, advanced GPUs utilize High Bandwidth Stacked DRAM memory which has significant advances over standard GDDR5 server memory. A GPC combines multiple TPCs into individual units. Each GPC contains the characteristics of a standalone GPU and each one can be dedicated to an individual workload or used in conjunction with one another. The TPC is a cluster of SMs with a texture unit and logic controls. Similar to the GPC, the TPC can be grouped into higher level configurations known as a Streaming Processor Array. The highlight of the TPC is the ability to utilize texture memory functions. Texture memory found in the texture unit is a cache memory, entirely separate from the global, shared, and register memory. It can be used to improve both latency and bandwidth for certain workloads. The texture memory cache is geared towards 2D graphics processing but for computational workloads the optimization of the cache allows for 2D spatial data locality. With the data bound to pitch linear memory, a running kernel can update this data allowing for increased performance in caching behavior and minimize superfluous data duplication computations, in calculations that require two-pass updating.

| L0 Instruction Cache |           |           |           |           |                      |            |   |   |    |  |   |

|----------------------|-----------|-----------|-----------|-----------|----------------------|------------|---|---|----|--|---|

| Warp Scheduler       |           |           |           |           |                      |            |   |   |    |  |   |

|                      |           |           | D         | ispatch   | Unit                 |            |   |   |    |  |   |

| Register File        |           |           |           |           |                      |            |   |   |    |  |   |

| FP64                 | INT       | INT       | FP32      | FP32      |                      | NSO<br>ORE | R | 1 | CO |  | ~ |

| FP64                 | INT       | INT       | FP32      | FP32      |                      |            |   |   |    |  |   |

| FP64                 | INT       | INT       | FP32      | FP32      |                      |            |   |   |    |  |   |

| FP64                 | INT       | INT       | FP32      | FP32      |                      |            |   |   |    |  |   |

| FP64                 | INT       | INT       | FP32      | FP32      |                      |            |   |   |    |  |   |

| FP64                 | INT       | INT       | FP32      | FP32      |                      |            |   |   |    |  |   |

| FP64                 | INT       | INT       | FP32      | FP32      |                      |            |   |   |    |  |   |

| FP64                 | INT       | INT       | FP32      | FP32      |                      |            |   |   |    |  |   |

| LD/<br>ST            | LD/<br>ST | LD/<br>ST | LD/<br>ST | LD/<br>ST | LD/ LD/<br>ST ST SFU |            | U |   |    |  |   |

Figure 2.12: Streaming Multiprocessor Architecture

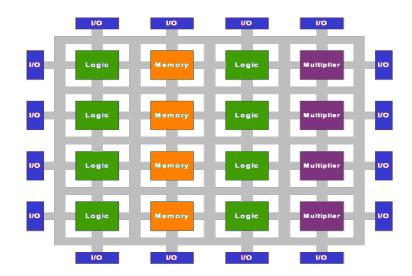

The primary workhorse of computations is the SM shown in figure 2.12. The SM contains several cores and Special Function Units (SFU). The collection of SMs are multithreaded SIMD processors. At a high level, the GPU is a MIMD composed of a grouping of multithreaded SIMD processors. The SM are optimized for high throughput floating point operations. The SM is equivalent to the Processing Element as seen in CPUs. The floating point and integer cores allow for faster throughput in computations. The SFU supports high throughput intrinsic functions (sin,cos,etc). The Tensor cores are high throughput mixedprecision FP16/FP32 cores optimized for deep learning applications. Multiple Tensor cores per SM are capable of performing multiple floating point operations per clock cycle. Proactively placing these specialized Tensor cores on the GPU allows for specialized machine learning tasks and emerging applications.

To process data GPUs uses two different architectures. For global execution across the TPCs, the MIMD architecture is used. To execute across the SMs, the Single Instruction Multiple Thread (SIMT) architecture, a subset of the SIMD classification, is used. Unlike traditional Von Neumann processors, the SIMT architecture allows a substantial number of parallel computations to execute across thousands of hardware threads each with different data sets. SIMT advances the SIMD design pattern not only in performance but in ease of use for programmers. Given that SIMT is scalar, it has no predefined set vector width which allows SIMT to perform at maximum speed regardless of the vector width. By comparison, the SIMD architecture experiences a capacity reduction when the input size is smaller than the SIMD/MIMD width. SIMT guarantees that the processing cores operate at full capacity consistently. Demanding workloads with substantial parallelism can benefit from the massively parallel computational abilities of GPUs.

### 2.3.4 GPUs are not the solution

GPU adoption has increased over the past few decades and has become the go-to device for parallel workloads, but have we really solved the challenges faced by the modern CPU? GPU architecture with its own caches, memory hierarchy, and PCI bus communication exploits embarrassingly parallel workloads by design but the primary bottleneck for Von Neumann processors is inherent to GPUs as well and significant performance degradation in data migration continues to persist. We have seen that CPUs lacked sufficient compute units to process massively parallel workloads and researchers have scaled horizontally to increase computational power. As we look at the landscape of GPU computing are we not doing the same thing? That is, densely packing servers with more and more GPUs and linking them over high bandwidth technologies such as RDMA and infiniband. Have we not simply shifted the problem to a different (albeit more capable) device? As new cards emerge with additional features, compute units, and extensions, we find ourselves refactoring code again. Another challenge that is faced by GPUs which is often overlooked is the notion of code branching. GPUs perform very badly, in fact worse than CPUs, when they encounter code with conditional branches. To circumvent this problem, many tools recommend executing branching code on the CPU and strictly parallel code with no branching on the GPU. This can bring other challenges as some data is on the CPU and in system memory while other portions are traveling across the bus to the internal GPU memory. Such synchronization, aggregation, and coherence can severely affect computational performance. The constant refactoring continues as new revisions of GPUs arrive to market and data migration challenges persist across device specific memory hierarchies. In a sense, we have not solved the problem but have simply shifted the issue to another architecture.

## 2.4 Alternative Hardware Accelerators

### 2.4.1 Application-Speciic Integrated Circuits

Industries with specific computational demands have diverged from standard CPU and GPU adoption in favor of Application Specific Integrated Circuits (ASIC). These devices differ from other hardware solutions in that they are not targeted for general purpose applications. These application specific integrated circuits, or chips, are targeted for very specific use cases. Such chips are often used in embedded device or single purpose applications in fields such as networking, bitcoin mining, and automotive industries just to name a few. As discussed previously, by adopting general purpose processing solutions, one has to tailor computations to the underlying hardware which may have drawbacks that limit computational performance. ASICs on the other hand, tailor the underlying hardware architecture to the computational demands. This makes for hardware with very precise architecture that ensure certifiable execution times and can take full advantage of the resources in order to complete the computation or function. However, developing such chips require a significant amount of time in terms of design, development, and fabrication. Traditionally, an industry

| System Specifications             | Identify the non-formal functionality specifications of  |

|-----------------------------------|----------------------------------------------------------|

|                                   | the ASIC.                                                |

| Architectural Design              | Layout development taking into account area, power,      |

|                                   | and size considerations.                                 |

| Functional and Logic Design       | An electronic components description used to capture     |

|                                   | functional requirements of the integrated circuit logic. |

| Circuit Design                    | The physical description of ASIC circuitry that achieves |

|                                   | the system specification using a hardware description    |

|                                   | language.                                                |

| Physical Design                   | Partitioning, floor-planning, placement, Clock Tree Syn- |

|                                   | thesis, Signal Routing, and Timing.                      |

| Physical Verification and Signoff | Formal circuit, timing, power testing, evaluation, and   |

|                                   | verification.                                            |

| Fabrication                       | Physical device creation.                                |

| Packaging and Testing             | Device packaging and final testing to ensure that ASIC   |

|                                   | operates within specified tolerances.                    |

| Completed Chip                    | Ready for use by the industry.                           |

Table 2.1: ASIC Design Flow

with interest in using ASICs would need a large team including several designers that would come up with an architectural layout using hardware description languages (HDL). Once the design was completed, the developer would need to engage an ASIC manufacturer to fabricate the design. Initially, designers would normally be constrained to using the available design tools of a manufacturer based on Verilog or VHDL. Over time third parties began developing design tools to provide features comparable to those found in manufacturer-specific tools, and today there are many options to choose from. These modern tools assist with logic synthesis and are able to compile HDL design descriptions into gate-level netlist which gives a description of the connectivity of all electronic components to one another. Creating ASICs follows a very specific design flow as shown in Table 2.1.

One of the most intensive processes of ASIC development is Functional Verification. Such verification may include techniques such as logic simulation, emulation, and formal verification. Unlike FPGAs, ASICs cannot be reprogrammed once they complete the fabrication phase. If errors are found after the fabrication phase, the redesign and re-fabrication of the device can be cost prohibitive. To eliminate errors, designers may elect to use full coverage

testing wherein the device is tested through all of the possible permutations of its functionality. However, given the volume of potential permutations or test-cases, even for a simple design, functional verification tests could exceed a Vigintillion  $(10^{63})$  test cases in order to verify a design. The functional verification process is often compared to program verification, both of which are NP-hard and may have zero possible solutions in all test cases. Solutions such as simulation, emulation, and intelligent verification can assist with the process in most cases to ensure the correctness of the design to a given margin of error.

Design and fabrication of ASICs can fall into two categories: Fully Custom and Semi-Custom designs. Many circuit designs have common components that fulfill basic logic or functional requirements. These common components are often packaged into cells and comprise a library of circuitry that may be offered by a vendor in order to speed up development and limit not only re-inventing common functionality but also required Functional Verification for a portion of the design. Designers are free to choose such libraries or create new ones for their applications. In the case of fully custom designs, the designer has the flexibility to create a complete layout of the circuitry on the device whereas semi-custom designs are slightly more constrained given that the design may use one or more of the pre-designed cell libraries provided by the manufacturer.

Clearly, ASICs provide the best performance given that the architecture is completely tailored to the computation, but this flexibility comes at a considerable price in terms of cost, price, and effort. Some of the time expense can be reclaimed by taking advantage of semicustom designs but ultimately, one has to create a new hardware architecture which is certainly more time consuming than merely refactoring source code for the CPU or GPU. The multi-factor expense of ASIC development seems larger than the effort required to refactor code for other architectures. Have ASICs solved the refactoring problem or is there another solution that will enable professionals to take advantage of architectural flexibility without reinventing the wheel?

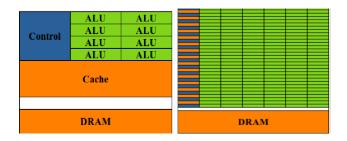

### 2.4.2 Field-Programmable Gate Array

Figure 2.13: FPGA Architecture

While ASICs have a long development time, a solution that is seeing a lot of adoption lately is that of the Field Programmable Gate Array (FPGA) shown in Figure 2.13. These devices have a lot in common with ASICs and when compared to the ASICs fully customizable design abilities, FPGAs fall into the semi-customizable category. FPGAs are integrated circuits that provide re-programability which is something that ASICs lack. They also can be configured using the hardware description languages as used for ASIC development. FPGAs are comprised of arrays of programmable logic blocks and a nested hierarchy of reconfigurable interconnects that allow designers to connect available circuitry at will. The logic blocks support simple or complicated functions and most FPGAs include complete memory blocks. With an ever growing amount of resources at the disposal of the FPGA, designers can build ASIC like circuity with competitive I/O rates to that of modern computer systems and can be used in mission critical areas where timing constraints must be fulfilled.

FPGAs provide an unparalleled level of flexibility and enable designers to create dynamic architectures with considerably less effort and costs than ASIC development. Yet, why have FPGAs not been adopted in all industries with demanding computational needs? One major factor is the steep learning curve required to master hardware description languages such as VHDL and Verilog. Even with the growth in programmers' workforce there has always been a limited number of professionals with an understanding of low-level architecture development.