# Rocket Cam Low Frequency Analog Transmission of Digital Video

by

Thomas J. Higdon

Advisor: Wayne Pilkington

Senior Project

# ELECTRICAL ENGINEERING DEPARTMENT

California Polytechnic State University

San Luis Obispo

2015

| <i>Section</i> Page                                                 |

|---------------------------------------------------------------------|

| Abstract4                                                           |

| I. Introduction                                                     |

| II. Product Design Engineering Requirements 5                       |

| IV. System Design - Functional Decomposition (Level 1)              |

| V. Technology Choices and Design Approach Alternatives Considered12 |

| VI. Project Design Discretion14                                     |

| VII. Physical Construction and Integration19                        |

| VIII. Integrated System Tests and Results                           |

| IX. Conclusions                                                     |

| References                                                          |

| Appendices                                                          |

| A. Senior Project Analysis                                          |

| B. Parts List and Costs                                             |

| C. Project Schedule - Time Estimates & Actuals43                    |

| D. Program Listings                                                 |

# TABLE OF CONTENTS

# LIST OF TABLES AND FIGURES

| Tables I                                                 | Page |

|----------------------------------------------------------|------|

| I. Requirements and Specifications                       | 6    |

| II. Level 0 Functional Requirements                      | 7    |

| III. Level 1 Functional Requirements                     | 9    |

| IV. Level 1 Data Flow Signals                            | 11   |

| V. Actual and Reconstruct Video                          | 22   |

| A1. Estimated Expected Parts and Equipment Costs         | 27   |

| A2. Estimated Expected Labor Costs                       | 27   |

| A3. Actual Parts and Equipment Costs                     | 28   |

| A4. Actual (Approximate) Labor Costs                     | 28   |

| A5. Planning Gantt Charts                                |      |

| (a) Fall Quarter and Winter Break                        | 29   |

| (b) Winter Quarter 2015                                  | 30   |

| (c) Spring Quarter 2015                                  | 31   |

| A6. Actual Development Gantt Charts                      |      |

| (a) Fall Quarter and Winter Break                        | 32   |

| (b) Winter Quarter 2015                                  | 33   |

| (c) Spring Quarter 2015                                  | 34   |

| B1: Actual Parts and Equipment Costs                     | 42   |

| B2: Estimated Production Model Parts and Equipment Costs | 42   |

| C1: Estimated Planned Development Time                   | 43   |

| C2: Approximant Actual Development Time                  | 43   |

| C3. Planning Gantt Charts                                |      |

|         | (a) Fall Quarter and Winter Break                        | 44 |

|---------|----------------------------------------------------------|----|

|         | (b) Winter Quarter 2015                                  | 45 |

|         | (c) Spring Quarter 2015                                  | 46 |

| C       | C4. Actual Development Gantt Charts                      |    |

|         | (a) Fall Quarter and Winter Break                        | 47 |

|         | (b) Winter Quarter 2015                                  | 48 |

|         | (c) Spring Quarter 2015                                  | 49 |

| Figures |                                                          |    |

| I.      | . Level 0 Block Diagram                                  | 7  |

| I       | I. Level 1 Hierarchical Decomposition                    | 8  |

| I       | II. Level 1 Block Diagram                                | 8  |

| Г       | V. Level 1 Implementation Concept Block Diagram          | 10 |

| V       | V. Level 2 Implementation Concept Block Diagram          | 16 |

| V       | VI. AD7245A Pinout and Wiring Schematic                  | 17 |

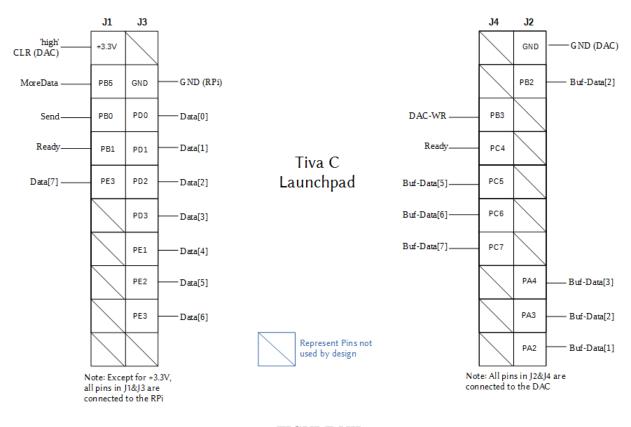

| V       | VII. Tiva C Launchpad Pinout and Wiring Schematic        | 18 |

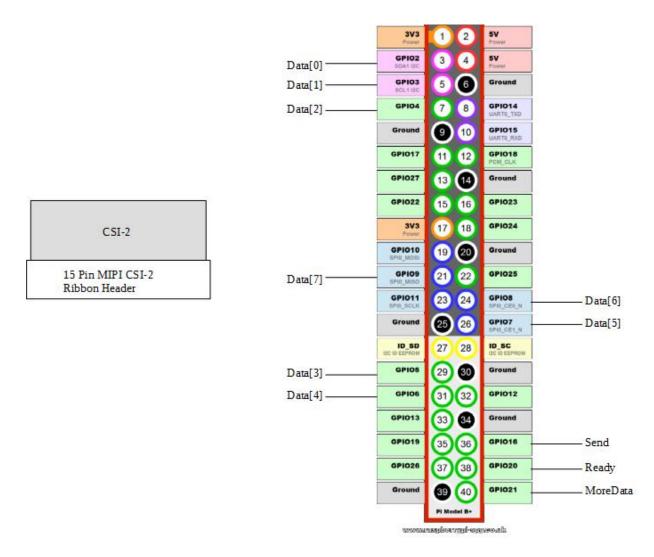

| V       | VIII. Raspberry Pi B+ Pinout and Wiring Schematic        | 19 |

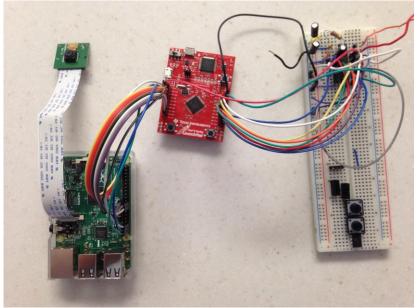

| Ľ       | X. Rocket Cam: Final Prototype                           | 21 |

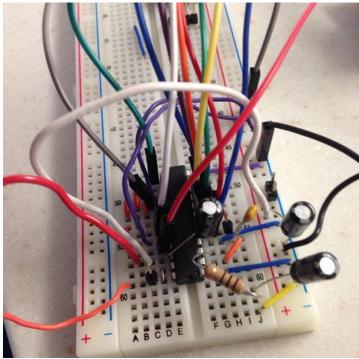

| Х       | X. Rocket Cam: Final Prototype DAC                       | 21 |

| Х       | XI. Difference Between Reconstructed & Actual Bytes      | 23 |

| Х       | XI. Test Data Used to Determine Settling Error Threshold | 23 |

|         |                                                          |    |

# Abstract

The camera module provides data for improving models of dynamic events on Orbital ATK Corp. rockets and aids in troubleshooting, if necessary. Video images provide a valuable addition to the strain, vibration, shock, and acoustic data used for modeling dynamic events, such as stage separations. The cameras can record a duration of video data suitable for capturing a dynamic event and of high enough quality to aid in its modeling. The module readily integrates into the rocket's current analog data collection systems. The project has further relevance to any other application that necessitates video data transmission over similar limited-bandwidth, analog data channels.

Though errorless data transmission was not achieve, over 99% of the digital by bytes transmitted where recovered to within 99% accuracy. This level of error is not suitable for compressed data. However, the primary sources of error can potentially be resolved by adaption to a more permanent prototype platform.

# I. Introduction

The camera module records dynamic events on Orbital ATK Incorporated rockets. Examples of dynamic events include stage separations and payload (satellite) deployments. Video data provides a valuable addition to previously existing sensors such as strain gages, accelerometers (vibration and shock), and microphones (for acoustic information). Teams then use the information from these sensors to improve models of the events, and to troubleshoot any undesired outcomes [1].

Groups internal to Orbital ATK have done some work on developing an inexpensive camera module for this task, however, their versions do not currently satisfy all of the needs of other departments in the corporation. Unfortunately, Orbital ATK has not approved for public release the details of the status of current development. However, this project focuses on the need to utilize an existing data channel that has minimal impact on the resources of the larger rocket system (the same type of data channel which the accelerometers use) [2]. The data channel consists of an analog data line, with relatively low bandwidth when compared to typical video data channels. The primary constraint to the bandwidth comes from the receiver unit consisting of an ADC with a maximum sampling rate of 10 kilo-samples per second, with a maximum of 12 bits of resolution [2]. Fortunately, the video data utilizes buffering before transmission and does not need to achieve real time transmission. However, the severely limited bandwidth still places significant limitations and consequences on the design. Though no need exists for real time transmission, the module must still transmit the video sample within a widow constrained by the minimum flight time of the rocket after the dynamic event. Other groups have done some work on "low-bandwidth" video data transmission [3]. But it remains an under-developed area, because of the limited number of applications that necessitate it.

Because of the data bandwidth limitations, effective compression before its transmission must also occur, in order to minimize the necessary transmission time. In contrast to the "low-bandwidth" concerns, video compression remains an area of significant and active development. The MPEG-4 AVC/H.264 lossy compression standard illustrates a method with widespread use [4]. In addition, groups have also researched the implementation of compression algorithms in embedded applications, both using microprocessors [5] and using FPGAs [6].

However, the author believes that this project typifies one of very few that require the compression of video data, and its transmission through such a narrow bandwidth analog data channel.

# **II. Production Design Engineering Requirements**

#### **Customer Needs Assessment**

Orbital ATK Incorporated needs a low-cost module to provide video data for improving models of dynamic events and for troubleshooting. It needs to be relatively stand-alone, and require minimal effort to integrate into their existing rocket system; and it should have minimal impact on their existing resources [1, 2].

#### **Requirements and Specifications**

The marketing requirements and engineering specifications listed in Table I below, primarily come from the need to integrate the module into the existing systems of the rocket. However, marketing requirements 1 & 2 and the first three specifications relate to the need to obtain sufficient data for useful study of dynamic events.

Orbital ATK deems that 0.5 to 3 seconds of video, with a resolution of 640x480 pixels, with 8-bit depth grayscale pixels, and a rate of 30 frames per second, is sufficient for aiding in their modeling and troubleshooting of typical dynamic events [1, 2]. The module must be able to transmit the data through of the previously existing data channel (the analog data line), and the data must be recoverable after receipt by their previously existing hardware (the ADC). In order to make better use of the limited bandwidth, the data must be compressed before transmission. The

transmission of the video sample must take less than 10 minutes. The module must also store the original, followed by the compressed, data, before being ordered by a dedicated 1-bit "Transmit Command" line send it. Recording and compression should start after the receipt of a signal from a dedicated 1-bit "Record Command" line. The device's addition to the larger rocket system should not constitute a significant increase to the cost of the overall system [1, 2]. The module must be safe and minimize its environmental impacts.

| Marketing     | Engineering                                   | Justification                                     |

|---------------|-----------------------------------------------|---------------------------------------------------|

| Requirements  | Specifications                                | Justification                                     |

| [1], [2]      | Capable of recording at between 0.5 and 3     | Sufficient time to observe event (i.e. stage      |

|               | seconds of video                              | separation)                                       |

| [4]           | At least 640x480 pixel image resolution, at 8 | Sufficient for useful image of event.             |

|               | bits per pixel                                |                                                   |

| [1], [2], [3] | Captures at between 30 and 60 frames per      | Fast enough to track dynamics, but slow           |

|               | second                                        | enough to not produce excessive data.             |

| [2], [3], [6] | Sufficient memory to store captured data and  | Necessary to hold data and send it only when      |

|               | to perform compression operations on the      | requested.                                        |

|               | data                                          |                                                   |

| [4]           | Output data over analog line                  | Existing data interface that has the minimum      |

|               |                                               | system impact.                                    |

| [4]           | Data recoverable after analog signal is       | This describes the existing system that           |

|               | sampled by an ADC with 12 bit maximum         | receives the transmitted data.                    |

|               | resolution, at 10,000 samples per second      |                                                   |

| [5]           | Inputs 2 separate, 1-bit command lines. One   | Minimal interfacing between an otherwise          |

|               | signals the module to begin recording; the    | stand-alone module and the larger system.         |

|               | other to transmit recorded data.              |                                                   |

| [6]           | Sufficient video data compression such that   | Due to the limited bandwidth of the necessary     |

|               | sample transmission requires less than 10     | data channel, it's critical to reduce the size of |

|               | minutes (minimum compression factor of 2      | the data, so that transmission fits within        |

|               | to 1)                                         | available time                                    |

| [7]           | Finished production units should cost no      | Desire a relatively inexpensive module to         |

|               | more than \$200.                              | complement existing sensors.                      |

| [8]           | Use at least 70% ROHS compliant               | ROHS provides a good general standard for         |

|               | components.                                   | minimizing health and environmental impacts       |

|               |                                               | of component materials                            |

#### TABLE I

#### ROCKET CAM MODULE REQUIREMENTS AND SPECIFICATIONS

#### **Marketing Requirements**

- 1. Provide short duration video data of dynamic events

- 2. Video data has sufficient quality to aid in event modeling and troubleshooting

- 3. Internally store the captured data until transmission

- 4. Use existing data interfaces on the rocket

- 5. Require minimal command interfacing

- 6. Transmit data in less than 10 minutes

- 7. Be "low-cost"

- 8. Be safe and relatively environmentally-friendly

#### Black Box Diagram (Level 0)

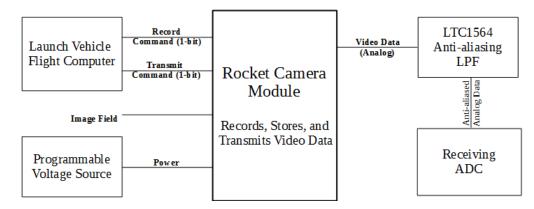

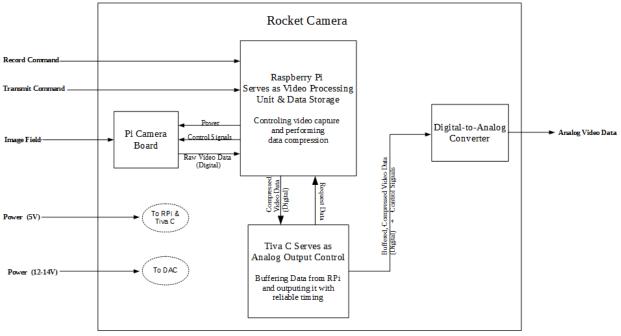

As its overall function, the design inputs light data, and then outputs an analog voltage representation of that data. The module also accepts two 1-bit command signals, the record and transmit commands, and it inputs power. Figure 1 shows this overall Level 0 functionality within the context of the larger rocket system, and Table III elaborates on each facet of it.

FIGURE I Rocket Cam – Level 0 Block Diagram

| TABLE II                             |

|--------------------------------------|

| ROCKET CAM – FUNCTIONAL REQUIREMENTS |

| Module          | Rocket Camera                                                                             |  |

|-----------------|-------------------------------------------------------------------------------------------|--|

| Inputs –        | Record Command: Bi-level optical signal or 1-bit TTL level signal                         |  |

|                 | Transmit Command: Bi-level optical signal or 1-bit TTL level signal                       |  |

|                 | Image Field: Incident light from the surrounding environment                              |  |

|                 | Power: Sufficient power for the module to function on                                     |  |

| Outputs –       | Video Data: Analog signal, 8 to 12 bit resolution, sampled at 10,000 samples per second   |  |

| Functionality – | Upon receipt of the Record Command, it records and stores 0.5 to 3 seconds of video data. |  |

| Functionality – |                                                                                           |  |

|                 | Then, upon receipt of the Transmit Command, it outputs the analog Video Data              |  |

Bi-level optical signal and 1-bit TTL level signals represent the existing command line infrastructure available in the rocket system. The bi-level optical signals have the advantage of providing optical isolation between the camera module, and rockets more critical control systems. The 1-bit TTL signals have the advantage of being faster, cheaper, and easier to implement and integrate. The analog data line represents the available, and lowest impact, data channel [1,2].

# **IV: System Design – Functional Decomposition (Level 1)**

### **Functional Block Diagrams**

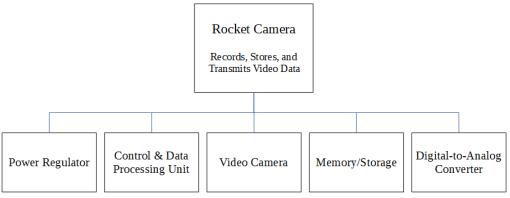

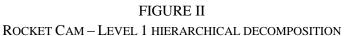

Figure II illustrates the primary subcomponents of the module in hierarchical decomposition format. Figure III shows them in function structure format. In words, the control unit receives the Record and Transmit Commands from the outside world and controls the other sub-modules' operations so that the device performs these tasks. Upon receipt of the Record Command, the video camera activates, takes in visual data and outputs an uncompressed digital representation of this data, which the memory access peripheral routes into memory. The control & data processing unit then communicates with memory, in order to perform compression and encoding operations on the video data. The compressed and encoded version of the data gets stored back in memory. Upon receipt of the Transmit Command, the compressed and encoded data gets read from memory, routed by the peripheral, and sent to the digital-to-analog converter, which converts it to its final analog form and outputs it to the outside world. During all of these operations, the power regulation unit provides appropriate power to all of the other sub-modules. The Control Unit contains the Memory Access Peripheral shown in the functional structure diagram, however, the peripheral can operate largely autonomously from the rest of the Control Unit, and is functionally distinct and significant enough to warrant separate mention at this level.

FIGURE III Rocket Cam – Level 1 Block Diagram

Table IV provides a breakdown of the inputs, outputs, and functional requirements of each sub-module.

| Module          | Power Regulator                                                                              |

|-----------------|----------------------------------------------------------------------------------------------|

| Inputs –        | External Power: 3 to 13V, constant voltage source at up to 100mA [1]                         |

|                 | Or programmable 28V (max) voltage source, with unspecified current capability                |

| Outputs –       | Regulated Power: Power at voltage levels acceptable to all of the other components           |

| Functionality – | Regulates externally supplied power to a level safe and usable by the other sub-modules      |

| Module          | Video Camera                                                                                 |

| Inputs –        | Camera Control Lines: Digital. Controls operation and settings.                              |

|                 | Image Field: Optical. Incident light from the surrounding environment.                       |

|                 | Regulated Power: DC voltage source.                                                          |

| Outputs –       | Raw Image Data: Digital. Uncompressed (raw) video image data.                                |

| Functionality – | After receiving instruction from the Control Unit, it inputs optical information from the    |

|                 | surroundings and converts it into an uncompressed digital representation, which it outputs.  |

| Module          | Control & Data Processing Unit                                                               |

|                 |                                                                                              |

| Inputs –        | Record Command: 1-Bit external control signal                                                |

|                 | Transmit Command: 1-Bit external control signal                                              |

|                 | Memory Data Bus: Digital. Accesses data stored in the Memory sub-module.                     |

|                 | Regulated Power: DC voltage source.                                                          |

| Outputs –       | Camera Control Lines: Digital. Instructs the Video Camera sub-module when to activate and    |

|                 | controls its settings.                                                                       |

|                 | DAC Control Lines: Digital. Controls settings of the DAC sub-module.                         |

|                 | Memory Control Lines: Digital. Control setting of the Memory sub-module.                     |

|                 | Memory Data Bus: Digital. Send data to the Memory sub-module for storage.                    |

| Functionality – | Inputs the Transmit and Receive Commands from the outside world. Controls the other sub-     |

|                 | modules and overall behavior of the device. Takes raw video data from memory, compresses and |

|                 | encodes it, then stores it back in memory.                                                   |

| Module          | Memory Access Peripheral                                                                     |

| Wiodule         | Memory Access T empheral                                                                     |

| Inputs –        | Address Information: Digital. From the main part of the Control Unit module.                 |

|                 | Data In: Digital.                                                                            |

|                 | Regulated Power: DC voltage source.                                                          |

| Outputs –       | Memory Control Lines: Digital. Controls address access and settings of Memory sub-module.    |

|                 | Memory Data Bus: Digital. Sends data to the Memory sub-module for storage.                   |

| Functionality - | Controls and formats data access from and storage in the Memory Sub-module. Physically       |

|                 | integrated into the Control Unit sub-module, but can operate largely autonomously and        |

|                 | considered functionally distinct and significant enough to warrant separate mention.         |

TABLE III

ROCKET CAM – LEVEL 1 FUNCTIONAL REQUIREMENTS

| TABLE III (continued)                        |  |

|----------------------------------------------|--|

| ROCKET CAM – LEVEL 1 FUNCTIONAL REQUIREMENTS |  |

| Module          | Memory                                                                                           |

|-----------------|--------------------------------------------------------------------------------------------------|

| Inputs –        | Control Lines: Controls operation and settings.                                                  |

|                 | Address Line: Controls accessed address for read or write operations.                            |

|                 | Data Bus In: Digital.                                                                            |

|                 | Regulated Power: DC voltage source.                                                              |

| Outputs –       | Data Bus Out: Digital.                                                                           |

|                 |                                                                                                  |

| Functionality - | Stores values placed in it by the Control Unit or the Memory Access Peripheral. Allows retrieval |

|                 | of these stored values.                                                                          |

|                 |                                                                                                  |

| Module          | Digital-to-Analog Converter                                                                      |

| Inputs –        | Control Lines: Controls operation and settings.                                                  |

|                 | Data Bus: Digital.                                                                               |

|                 | Regulated Power: DC voltage source.                                                              |

| Outputs –       | Analog Data Line: Analog. Transmitted to outside world. Converted at a resolution of higher      |

|                 | than 8-bits, and a rate of 10,000 samples per second.                                            |

| Functionality - | Takes digital data sent to it and converts it into an analog representation.                     |

# **Implementation Concept Block Diagram**

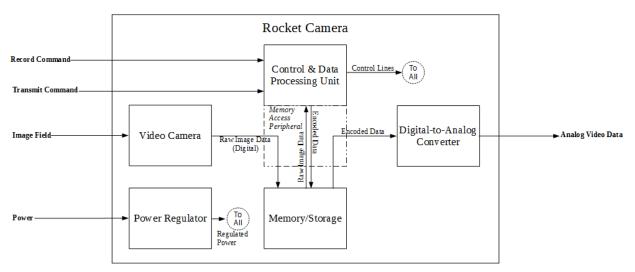

Figure IV below displays the implementation concept block diagram, indicating the physical component breakdown of the system. The control/processing unit consists of two processors, one which primarily controls the video capture and processing, and one which primarily controls the analog data transmission. The video data is captured by a digital camera unit. The non-volatile memory consists of a microSD card inserteded into the video processors board (on which the video processor's operating system is also stored). The digital-to-analog converter also exists on a separate chip, and steps are taken to reduce the effect of noise generated by the digital circuitry it. The power regulation system is actually comprised of multiple regulators associated with each submodule in order to provide the voltage levels necessary for all of the components and subcomponents.

| FIGURE IV                                         |

|---------------------------------------------------|

| ROCKET CAM – IMPLEMENTATION CONCEPT BLOCK DIAGRAM |

Table IV describes in greater detail, important data flow signals shown in Figure IV.

| ROCKET CAM – DATA FLOW SIGNALS |                       |                                                                          |

|--------------------------------|-----------------------|--------------------------------------------------------------------------|

| Source                         | Signal                | Format/Function                                                          |

| Outside                        | Record Command –      | 1-Bit external control signal                                            |

| World                          | Transmit Command –    | 1-Bit external control signal                                            |

|                                | Image Field –         | Physical light striking the sensor                                       |

|                                | Power –               | DC 3 to 13V, constant voltage source at up to 100mA                      |

|                                |                       | or programmable 28V (max) voltage source, with unspecified current       |

|                                |                       | capability (higher than 100mA)                                           |

| Image                          | Raw Image Data –      | Camera Serial Interface (CSI-2), 15 pin interface [7]                    |

| Sensor                         |                       |                                                                          |

| Rasp. Pi                       | Raw Image             | Camera Serial Interface (CSI-2), 15 pin interface                        |

| w/ Cam                         | Data/Camera Control – |                                                                          |

| Rasp. Pi                       | Compressed Data –     | 8-pins parallel data + 2-pins control (data ready & more data available) |

|                                |                       |                                                                          |

| Tiva C.                        | Buffered Data –       | 8-pins parallel data + 1-pins control (write enable)                     |

|                                | Request Data –        | 1-pin control                                                            |

1-pin. 0-10 V analog value with minimum of 8-bit accuracy.

# TABLE IV

Additional, parameters necessary for functional components in the design are summarized below.

Control/Processing Unit -

Analog Video Data -

DAC

Capable of inputting image data at real time video speeds •

- $\circ \geq 27.648 * 10^6 \text{ Bps} \left( 640 * 480 \frac{pixels}{frame} * 3 \frac{Byte}{pixel} * 30 \text{ fps} \right) \text{ [YCbCr format]}$

- Capable of storing image data to memory at real time video speeds

$$\circ \geq 9.216 * 10^{6} \text{ Bps} \quad \left(640 * 480 \frac{pixels}{frame} * 1 \frac{Byte}{pixel} * 30 \text{ fps}\right) \quad [\text{Grayscale format}]$$

- Capable of outputting a byte to the DAC at consistent frequencies up to 5 kHz

- Maximum hypothetical unsynchronized transmission rate, the Nyquist Rate

- $\circ$  Maximum allowable timing deviation, 20 µs (10%)

- Compression takes less than 2 minutes to complete

- Any processing time beyond this mark must either be more than compensated in reduced transmission time, or must occur concurrently with transmission of earlier data

- Cost less than \$60

Image Sensor -

- Capable of VGA quality resolution at 30 frames per second

- o 640x480 pixels @ 30 fps

- Minimum of 8-bit luma depth

- 8-bit grayscale can be extracted

#### Memory -

• Capable of inputting image data at real time video speeds

$$\circ \geq 9.216 * 10^{6} \text{ Bps} \quad \left(640 * 480 \frac{pixels}{frame} * 1 \frac{Byte}{pixel} * 30 \text{ fps}\right) \quad [\text{Grayscale format}]$$

• Sufficient memory to store both raw and compressed video data

$$\circ \geq 9.216 * 10^{6} \text{ Bytes} \qquad 2 * \left( 640 * 480 \frac{pixels}{frame} * 1 \frac{Byte}{pixel} * 30 \text{ fps} * 0.5 \text{ s} \right)$$

Digital-to-analog converter -

- Output levels of 0-10 V (unipolar operation)

- The values read by the existing ADC

- Slew + settling time (to within 10/256 V) should be less than  $100 \ \mu s$

- Operating at 3.33 kHz this means that at least 2/3 of the period should be at the correct level, and with the external ADC sampling 3 times for each period, two out of three samples should contain the correct value.

- Monotonic

- An increase in value always equates to an increase in voltage

- Total Unadjusted Error should be less than 10/256 V and INL < the 8<sup>th</sup> bit (1 LSB if a 8-bit DAC) [8]

- The importance of these requirement can be reduced by sending a calibration signal over the line, prior to any data transmission, and accounting for existing offsets.

#### V. Technology Choices and Design Approach Alternatives Considered

The primary technology choice central to this design, was how to implement the control/processing unit. Several possibilities were investigated. The two primary alternatives categories were: a low-cost ARM microcontroller with direct C programing and real time operation (typically targeted at controls applications), or a more expensive ARM microprocessor built for mobile applications and running a full operating system. Below are listed some of the pros and cons of each option.

ARM "Controls" family -

Pros:

• Low-cost (with development boards as low as \$13) [9]

- C environment gives designer a large degree of control over the behavior of the processor

- Interrupt driven, real time operation is possible

- Existing code for serial interfaces available for specific devices

- Existing C code for video compression could potentially be adapted for device

Cons:

- Small on-chip memory means video data must be stored off-chip

- Clock speeds and data transfer rates are on the edge of not being able to handle the live video data, especially with the need to immediately send it to external memory (though DMA's could help with this, that removes the possibility of performing any processing to the data before storage (i.e. convert to grayscale to save memory space))

- Compression algorithms would likely take significant time, and could be challenging to run simultaneously with data transmission

#### ARM "Mobile" family -

Pros:

- Sufficient data rates to handle video

- Active and helpful development communities and documentation (esp. for BeagleBone and Raspberry Pi)

- Existing projects and software for camera integration and video compression

- Either larger on chip memory, or relatively inexpensive development board with memory onboard

#### Cons:

• Non-real time operating systems make timings unreliable

#### FPGA -

Pros:

- Can be designed to handle capturing and moving video data into memory in real time, even with some preprocessing

- Various operations can be performed in parallel

- Hardware based compression algorithms could potentially run very fast

- Open source hobbyist community [10]

- Most flexible option

Cons:

- Most expensive option

- Requires external memory (or very large, and expense chip)

- HDL coding and implementation are potentially more challenging than software implementation

In the end, I choose a hybrid approach, utilizing both a low-cost "controls" ARM and a higher performance "mobile" ARM. This solution takes advantage of the benefits of both families. The higher performance processor can handle video capture and storage, and perform the computationally intensive compression operations; and it can make use of the large development communities, a higher level of abstraction, and available open source software, to streamline the development process. While the lower-performance controls ARM can control the analog data output with consistent, reliable timing, for little additional cost. This solution is still significantly less expensive than using an FPGA, and is also less expensive than high performance, real-time operation (single) ARM processors. The approach does have higher complexity than a single processor and requires the two to communicate with each other, but it also allows a greater degree of design flexibility.

A color image sensor was chosen, despite only needing grayscale data, because color image sensors are more prevalent, more supported, and actually cheaper. In specific an image sensor already supported by the "mobile" ARM processor was chosen.

A digital-to-analog converter that met all of the performance parameters discussed above was chosen.

Specifically the Raspberry Pi Model B+ development platform serves as the video capture, processing, and storage control role. The Raspberry Pi's low cost, large open-source development community, specifically supported low-cost camera unit, and existing software for performing H.264 video compression (included with the Raspbian operating system), caused its selection platform. The Raspberry Pi features a Broadcom BCM2835 system-on-a-chip, containing an ARM11 floating point CPU and Videocore 4 GPU [11]. For the analog data output control, the design uses the Tiva C Launchpad development platform, which features a Texas Instruments TM4C123GH6PM microcontroller with an ARM Cortex-M4 processor core and 32 KB of on-chip SRAM [12]. The Tiva C was chosen for its sufficient memory to buffer the video data, sufficient processing capabilities to control the data output and retrieval from the Raspberry Pi, and low-cost. The Raspberry Pi Camera Module's compatibility and support with Raspberry Pi determined its selection. The AD7245A digital-to-analog converter's compliance with the minimum static and dynamic performance parameters determined in the previous section, and its 0-10V unipolar operating mode allowed its consideration [13]. Its relatively simple parallel digital interface, and its availability in a PDIP package conducive to early prototyping furthered its selection.

# **VI. Project Design Description**

#### **Component Integration**

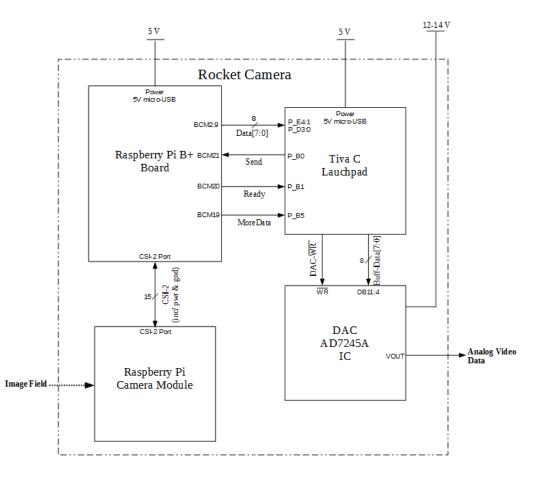

The Level 2 Block Diagram of the final design with additional signal and interconnection detail is shown in Figure V. It contains all functional submodule connections.

#### FIGURE V

### ROCKET CAM – IMPLEMENTATION CONCEPT BLOCK DIAGRAM LEVEL 2

The connection between the Raspberry Pi B+ and the Raspberry Pi Camera Module follows the MIPI standard and is controlled using existing drivers. The communication between the Raspberry Pi and the Tiva C consists of a custom parallel data interface (coded by the project designer). The Tiva C controls the AD7245A via a single-latched, parallel data loading structure (the AD7245A contains a double latched input, however, the design is configure so that one latch is left transparent).

For simplicity the schematic wiring diagrams showing specific pinouts are broken into 3 diagrams, centered around the 3 main subcomponents. This prevents crossing wires in the diagrams. Signal names correspond to those shown in Figure V.

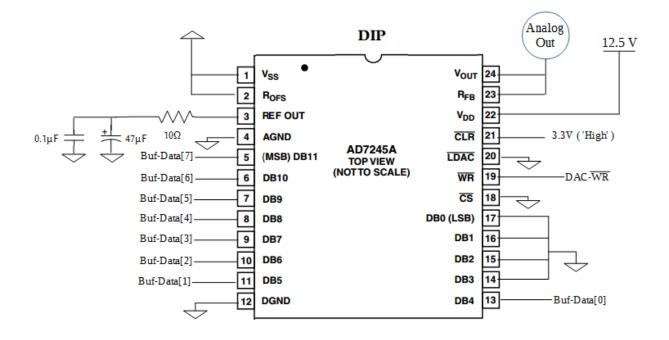

Figure VI shows the pin connections for the AD7245A DAC. The DAC is configured in unipolar-mode, with the LDAC latch held transparent, the chip select engage, and latch clearing disabled. The design only makes use the upper 8 data bits and the lower 4 are tied to ground; this allows the design to make use of the higher precision the AD7245A has over most 8-bit DACs, without pushing the resolution to its limit and incurring less noise and drift resilience. The device configuration is primarily based on the unipolar configuration and microprocessor interfacing application notes contained within its datasheet [13].

Figure VII shows the pin connections for the Tiva C Launchpad evaluation board. In the design, the Tiva C serves the function of controlling the analog data output with reliable timing. After being informed that the Raspberry Pi has data ready for it, it buffers data from the RPi and sends it to the DAC at consistent time intervals. When the amount of data stored in the buffer falls below a minimum value, it requests the next byte from the RPi.

FIGURE VII TIVA C LAUNCHPAD PINOUT AND WIRING SCHEMATIC

Figure VIII shows the pin connections on the Raspberry Pi B+. The RPi's function is to receive record and transmit commands, control video data collection, perform video compression, store the video data, and send it to the Tiva C when requested. For the purposes of testing and debugging, the receive and transmit commands are instructions sent over an SSH connection from the designer's computer, rather than the specified 1-bit lines. However, switching to 1-bit TTL-level commands takes minimal effort (the RPi's gpio ports are already compliant with TTL-levels).

# FIGURE VIII RASPBERRY PI B+ PINOUT AND WIRING SCHEMATIC (IMAGE BASED ON RASPBERRYPI-SPY.CO.UK IMAGE [14])

# **Design Operation**

The final analog output of the design is at 256 discrete levels, corresponding to one full byte of data. Because of the inability to synchronize transmission and reception, the design faces Nyquist rate limitations. The DAC outputs the next byte at intervals of 300  $\mu$ s (or slightly longer), so that the receiving end will have at least 3 samples for every new voltage level (every new byte). If transition (slew) and settling times are below 100  $\mu$ s total, then (assuming negligible noise) there will be 2 settled samples with voltages correctly representing the byte of data, for each byte sent. Thus the analog data decoding algorithms on the receiving end can look for two consecutive readings at the same voltage level, to determine the byte value. The output interval is controlled by the Tiva C's timers, which are set to trigger at 3330 Hz. This necessity for settling in under 100  $\mu$ s, was a primary reason behind the choice of the AD7245A, as mentioned in Section V. Before actual data is sent, a calibration signal containing 2 full 300  $\mu$ s periods of every voltage level (byte value) is output, so that the decoding algorithm can adjust and calibrate for any offsets and persistent non-idealities of the DAC's output levels.

The Tiva C uses a 512-byte array as a circular type buffer. A byte received from the Raspberry Pi is stored into the array at one index location, while bytes sent to the DAC are read from a different index location. The program attempts to keep the receive index 500 elements in the lead of the send index, with the indices wrapping around when they reach the end of the array. The 500 element buffer length was chosen, because, during a test of the impact of the Linux's background multithreading on gpio output performance, the largest undesired delay (during a 3 minute measurement period) was approximately 5.3 ms with multiple others on the order of 4 ms. The 500 element buffering length, combined with the output interval of 300 µs, means that the buffer stores enough information for 150 ms, or roughly 30 times the maximum observed delay. This better than order of magnitude safety margin, which is desirable to protect against the possible danger if multiple delays are stacked before the buffer can be fully replenished. In the Tiva C's code, the receive and store process is run in the main program, while the read and send process occurs within an interrupt service routine (triggered by the timers).

The communication between the Raspberry Pi and the Tiva C uses the following pattern:

Begin: RPi: MoreData = 1; //To tell the TC there is data available

Repeat: TC: If the buffer is not full, set Send=1, else wait; //TC requests next byte from RP

RPi: Load the byte onto the Data[7:0] pins;

RPi: Set Ready=1; //Tell TC that the byte is ready

TC: Read byte

TC: Send = 0; //Acknowledge receipt of data

RPi: If no more data (file end reached), MoreData = 0;

RPi: Ready=0; //Prepare for the next loop iteration

TC: If MoreData==1, repeat, else break loop.

This communication method was specifically designed to be resilient to interrupts, both from the Tiva C's timers and from background threads in the Raspberry Pi's non-real time operating system (Raspbian Linux), and to neither lose its place in the process nor miss data that was sent, due to timing errors. Thus its asynchronous nature. This provides a reliable communication scheme, which can still be quite fast when compared to the 300 µs per byte that it must exceed, because (when not interrupted) the next step runs as soon as the previous step is completed (and the outputs are stable), at the clock speeds the two processors are configured for.

The code for the Tiva C was rewritten in C using Texas Instruments' Code Composer Studio IDE. During compiling, the optimization level for set to 1, while optimize-for-speed was set 5 (maximum), because sufficiently fast operation is critical to the buffer's reliability. The gpio interactions of the Raspberry Pi were written in C in a simple text editor, before being compiled in Linux terminal commands using the GCC compiler with standard compilation and optimization options. The code made use of the WiringPi library for gpio control [15]. Running the exiting video capture and compression code, as well as higher level program flow control, takes place in Linux shell scripts. The compressed H.264 video data is wrapped in .mp4 format using the MP4Box application [16]. The analog data capture for testing purposes used an Analog Discovery's oscilloscope, which was being controlled by a Python script provided with the beta 2.8.13 Version of its software development kit (WaveformsSDK)[17][18]. Decoding of analog data and reconstruction into a digital file is performed in Matlab. Samples of all the source code developed for the project are included in Appendix D.

#### **VII. Physical Construction and Integration**

For prototyping purposes the design consists of the Tiva C Launchpad and Raspberry Pi B+ development boards, and an AD7245A in a PDIP package on a breadboard, all interconnected via wire-leads and jumpers, as shown in Figure IX.

FIGURE IX Rocket Cam: Final Prototype

On the breadboard, all ground connections (especially for analog references) are made as physically close together as practical, and capacitive coupling is added between all nodes that are supposed to have fixed DC values. Figure X is a closer image of the bread board section.

FIGURE X Rocket Cam: Final Prototype - DAC

For the prototype, power for the AD7245A is provided by a voltage source set to 12.5 V. Power (5V) for the Tiva C Launchpad is provided over a micro-USB connection. When debugging this is typically connected to the designer's computer. Power (5V) for the Raspberry Pi B+ is also provided via a micro-USB connection. This connection is typically to a wall outlet adapter.

# **VIII. Integrated System Tests and Results**

For testing purposes the recovered, processed, and reconstructed video data from the analog output of the module is compared with the raw video data stored in the modules memory (accessed via an Ethernet connection). The reconstructed byte-array in Matlab is compared to the original file viewed as a byte-array. The following numbers are based off of a specific test of the video capture and transmission.

The first statistic to consider is the number of times the Matlab code detected that it had failed to read a byte, these points are stored in the byte array as NaN's (Not-a-Number's). This occurs when Matlab does not detect a settled value within 4 samples of the previous byte. The resulting count was:

NaN Count: 1025

The next relevant statistic is the length of the reconstructed data array, vs the actual data array. This gives a general starting point for comparison of the too samples.

| Actual Video Data Length:  | 959038 bytes |

|----------------------------|--------------|

| Reconstructed Data Length: | 959034 bytes |

Which means that the decoding algorithm failed to read at least 4 bytes, which it did not explicitly detect as failed reads and use a NaN as a placeholder for. Also note that this also allows the calculation of the percentage of detected unreadable bytes, 1025/959038 = 0.107%.

Table V shows a comparison of the first 12 and the last 12 bytes of the actual and the reconstructed data. The sets clearly correlate, however there are several single bit errors present, most likely due either to inaccurate calibration of the decoding, or to noise on the analog line.

|               | -      |        |       | ·     | -     |       |       |       |       |       |       |     |

|---------------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-----|

| Index         | 1      | 2      | 3     | 4     | 5     | 6     | 7     | 8     | 9     | 10    | 11    | 12  |

| Actual        | 0      | 0      | 0     | 24    | 102   | 116   | 121   | 112   | 105   | 115   | 111   | 109 |

| Reconstructed | 0      | 0      | 0     | 24    | 102   | 116   | 121   | 112   | 104   | 115   | 111   | 109 |

|               |        |        |       |       |       |       |       |       |       |       |       |     |

| Index         | end-11 | end-10 | end-9 | end-8 | end-7 | end-6 | end-5 | end-4 | end-3 | end-2 | end-1 | end |

| Actual        | 67     | 32     | 48    | 46    | 53    | 46    | 48    | 45    | 114   | 101   | 118   | 0   |

| Reconstructed | 68     | 32     | 48    | 47    | 53    | 47    | 48    | 45    | 114   | 101   | 119   | 0   |

TABLE V

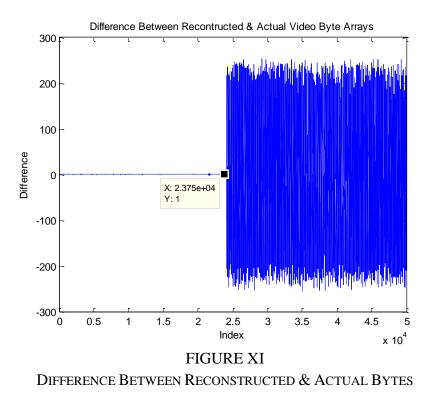

A plot of the between the first 50,000 bytes of the two arrays shows that up to the 24,138th byte, there was at most single, least significant bit errors. Figure XI shows this.

The 24,139th byte represents the appearance of an index offset, after which the array values no longer match up.

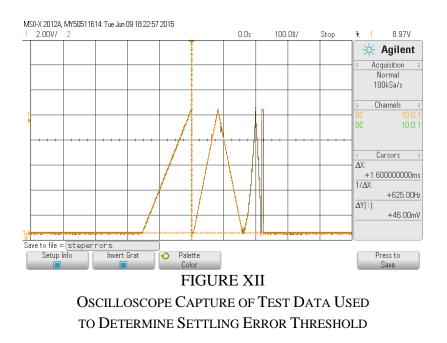

The primary cause of unreadable bytes is parasitic RC delays that increase the settling time of large code transitions to the point that two settled sample values are not detected before the output transition to a new value. Using the test file whose analog output is shown in Figure XII, it was determined that at code transitions of greater than about 50, byte detection became unreliable.

Because of the various errors present, the reconstructed file could not be opened by normal .mp4 players.

Summarizing, over 99% of the digital by bytes transmitted were recovered to within 99% accuracy; however, this is not sufficient for corruption free transmission of .mp4 files.

# **IX.** Conclusions

The complete specifications were not met. Because of the noise and delay errors, the reconstructed, compressed video data file was corrupted and unreadable. In part this is due to the unforgiving nature of H264 compression, and compression in general, to errors. Compression involves the reduction of statistical redundancy in data, and reduction of redundancy also means a reduction in resilience to errors [19]. In its current state, the channel and reconstruction likely has sufficient accuracy for uncompressed video data to be sent and recovered with adequate quality. However, uncompressed video cannot have the specified video duration and resolution and still be transmitted in the specified time. In addition, although documentation to the contrary exists, the drivers for the Raspberry Pi Camera Module do not currently support 30 frames per second capture, the videos are actually captured at 25 fps (83% the specified speed) [20].

Despite its inability (in its current form) to meet all of the specifications simultaneously, this project serves as a solid proof of concept for the technology. In the trials discussed above, less than 0.2% of all bytes transmitted were unreadable, and of those that were readable almost all were within one least significant bit of the correct value. Moving forward with this project to a PCB design would most likely resolve the primary issues preventing the project from fully meeting all of the specifications. A well designed PCB will have significantly lower parasitic capacitances than a breadboard circuit, allowing the time until a settled value, to be decreased, potentially to less than 100 µs for a full 10 V swing. Furthermore, implementation of noise suppression techniques and methods for isolating analog components from digital noise, should greatly reduce the number of least significant bit errors. This combined with improved reconstruction algorithms could potentially remove them altogether, allowing for complete, uncorrupted reconstruction of the compressed video data and achievement of all of the specifications.

Specifications that the design currently fully meets are: capable of recording at between 0.5 and 3 seconds of video; at least 640x480 pixel image resolution, at 8 bits per pixel; sufficient memory to store captured data and to perform compression operations on the data; output data over analog line; sufficient video data compression such that sample transmission requires less than 10 minutes (minimum compression factor of 2 to 1); finished production units should cost no more than \$200 (Note: the component costs of the final prototype are at less than \$100); and use at least 70% ROHS compliant components. The 1-bit TTL-level record and transmit were not implemented in the final design for debug and testing reasons, but would be trivial to add to it.

Overall the project meets the majority of its specifications, and meets each of the remaining specifications by better than 80%, and there are clear routes that can improve the design until all of the specifications are met.

#### References

[1] Orbital Sciences Corporation, "Rocket Camera Proposal," *Orbital Sciences Corporation*, Unknown Date. [Online]. Available: Cal Poly Polylearn: EE460. [Accessed: Aug. 27, 2014].

[2] Orbital Sciences Corporation, "Rocket Camera Proposal – Revised 10/21/14," *Orbital Sciences Corporation*, Oct. 2014. Unpublished.

[3] M. Noonen, K. Deierling, K. Barraclough, and B. Martin, "Video compression and decompression arrangement having reconfigurable camera and low-bandwidth transmission capability," U.S. Patent 5 926 208, July 20, 1999.

[4] G.J. Sullivan and T. Wiegand, "Video Compression - From Concepts to the H.264/AVC Standard," Proceedings of the IEEE, vol.93, no.1, pp.18,31, Jan. 2005. Available: IEEE Xplore, <u>http://www.ieee.org</u> [Accessed: 10/20/14]

[5] Kyusam Lim; Jeonghun Kim; Hwangyoung So; Sejin Kang; Suki Kim, "A Low Power QXGA Camera Signal Processor for Mobile Camera Applications," International Conference on Consumer Electronics, 2007. ICCE 2007. Digest of Technical Papers., vol., no., pp.1,2, 10-14 Jan. 2007. Available: IEEE Xplore, <u>http://www.ieee.org</u> [Accessed: 10/20/14]

[6] M.L. Kaddachi, L. Makkaoui, A. Soudani, V. Lecuire, and J. Moureaux, "FPGA-based image compression for low-power Wireless Camera Sensor Networks," 3rd International Conference on Next Generation Networks and Services (NGNS), 2011, vol., no., pp.68,71, 18-20 Dec. 2011. Available: IEEE Xplore, <u>http://www.ieee.org</u> [Accessed: 10/20/14]

[7] D. Braun, "EE 460 Gantt Chart – Fall 2014," Cal Poly Courseware – EE. [Online]. Available: https://courseware.ee.calpoly.edu/~dbraun/courses/ee460/EE460Gantt.html. [Acessed: 10/27/14]

[8] I. Wahidah, A.B. Suksmono, Hendrawan, and T.L.R. Mengko, "Compressive sampling for digital video signal compression involving dynamic sparsity," 7th International Conference on Telecommunication Systems, Services, and Applications (TSSA), 2012, vol., no., pp.46,50, 30-31 Oct. 2012. Available: IEEE Xplore, <u>http://www.ieee.org</u> [Accessed: 10/20/14]

[9] Aptina Imaging, "1/4-Inch VGA Digital Sensor - MT9V011 Data Sheet," Aptina Imaging. [Online]. Available: Aptina, www.aptina.com . [Accessed: 11/15/14]

[10] Cypress Perform, "4-Mbit (256 K x 16) Static Ram - CY7C1041DV33 Data Sheet," Cypress Perform. [Online]. Available: Cypress, <u>www.cypress.com</u>. [Accessed: 11/15/14]

[11] Cypress Perform, "4-Mbit (256 K x 16) Static Ram," CY7C1041DV33 datasheet [Online]. Available: Cypress, www.cypress.com. [Accessed: 11/15/14]

[12] Analog Devices, "LC2MOS 12-Bit DACPORTs," AD7245A/AD7248A datasheet [Online] Available: Analog, www.analog.com. [Accessed: 6/12/15]

[13] Analog Devices, "LC2MOS 12-Bit Serial DACPORTs," AD7243 datasheet [Online] Available: Analog, <u>www.analog.com</u>. [Accessed: 6/12/15]

[14] Analog Devices, "12-Bit 100 kSPS A/D Converter," AD7243 datasheet [Online] Available: Analog, <u>www.analog.com</u>. [Accessed: 6/12/15]

[15] Linear Technology, "10kHz to 150kHz Digitally Controlled Antialiasing Filter and 4-Bit P.G.A," LTC1564 datasheet [Online] Available: Linear, <u>www.linear.com</u>. [Accessed: 6/12/15]

[16] Digilent, "PmodSF2 Reference Manual," [Online] Available http://www.digilentinc.com. [Accessed: 6/12/15]

[17] Numonyx, "Numonyx® OmneoTM P5Q PCM," P5Q PCM datasheet, [Online] Available, Digilent Inc, <u>http://www.digilentinc.com</u>. [Accessed: 6/12/15]

[18] E2e.ti.com, "SPI Speed on ARM microprocessors (Tiva for example) - TM4C Microcontrollers Forum - TM4C Microcontrollers - TI E2E Community," 2015. [Online]. Available: http://e2e.ti.com/support/microcontrollers/tiva\_arm/f/908/p/274452/958695. [Accessed: 6/12/15].

[19] Elinux.org, "RPi Low-level peripherals - eLinux.org," 2015. [Online]. Available: <u>http://elinux.org/RPi Low-level peripherals#GPIO Code examples</u>. [Accessed: 6/12/15].

[20] Wiringpi.com, 'WiringPi', 2015. [Online]. Available: http://wiringpi.com/. [Accessed: 6/12/15].

[21] Raspberrypi.org, "Raspberry Pi Forums - DMA and SPI and Interrupts - cant get it to work," 2015. [Online]. Available: <u>https://www.raspberrypi.org/forums/viewtopic.php?f=71&t=19797</u>. [Accessed: 6/12/15].

[22] Raspberrypi.org, "Raspberry Pi Forums - DMA on GPIO," 2015. [Online]. Available: https://www.raspberrypi.org/forums/viewtopic.php?f=44&t=8376. [Accessed: 6/12/15].

[23] Wallacoloo, "Wallacoloo/Raspberry-Pi-DMA-Example," GitHub, 2014. [Online]. Available: https://github.com/Wallacoloo/Raspberry-Pi-DMA-Example/blob/master/dma-gpio.c. [Accessed: 6/12/15].

[24] J. Pihlajamaa, 'Benchmarking Raspberry Pi GPIO Speed | Code and Life', Codeandlife.com, 2012. [Online]. Available: http://codeandlife.com/2012/07/03/benchmarking-raspberry-pi-gpio-speed/. [Accessed: 6/12/15].

[25] Raspberrypi.stackexchange.com, 'How to compile C files in terminal', 2015. [Online]. Available: http://raspberrypi.stackexchange.com/questions/5599/how-to-compile-c-files-in-terminal. [Accessed: 6/12/15].

[26] Raspberrypi.org, "Raspberry Pi Camera Module -Applications," Raspberry Pi Documentation 2015. [Online]. Available: https://www.raspberrypi.org/documentation/raspbian/applications/camera.md. [Accessed: 6/12/15].

[27] Raspberrypi.org, "Camera - Hardware," Raspberry Pi Documentation 2015. [Online]. Available: https://www.raspberrypi.org/documentation/hardware/camera.md. [Accessed: 6/12/15].

[28]A. Allain, "C File I/O Tutorial - Cprogramming.com." Cprogramming.com, 2015. [Online]. Available: http://www.cprogramming.com/. [Accessed: 6/12/15].

[29] Codingunit.com, "C Tutorial – Binary File I/O | CodingUnit Programming Tutorials," 2015. [Online]. Available: <u>http://www.codingunit.com/c-tutorial-binary-file-io</u>. [Accessed: 6/12/15].

[30] M. Samek, "Are We Shooting Ourselves in the Foot with Stack Overflow?", Embeddedgurus.com, 2015. [Online]. Available: <u>http://embeddedgurus.com/state-space/2014/02/are-we-shooting-ourselves-in-the-foot-with-stack-overflow</u>. [Accessed: 6/12/15].

[31] N. Jones, "Efficient C Tip #13 – use the modulus (%) operator with caution," Embeddedgurus.com, 2015. [Online]. Available: <u>http://embeddedgurus.com/stack-overflow/2011/02/efficient-c-tip-13-use-the-modulus-operator-with-caution/</u>. [Accessed: 6/12/15].

[32] Oshpark, "OSH Park ~ Pricing and Specifications," 2015. [Online]. Available: <u>https://oshpark.com/pricing</u>. [Accessed: 6/12/15].

[33] R. Gonzalez, and R Woods, Digital Image Processing, 3rd ed. Upper Saddle River: Prentice Hall, 2007.

# Appendix A – Analysis of Senior Project Design

Project Title: Rocket Cam: Low Frequency Analog Transmission of Digital Video

Student's Name: Thomas Higdon

Advisor's Name: Professor Wayne Pilkington

#### **1. Summary of Functional Requirements**

The design's overall function inputs visible light video image data, and then to outputs an analog voltage representation of that data. The module also accepts two commands, record and transmit. Upon receipt of the record command, the module captures and stores 3 seconds of video data. Upon receipt of the transmit command, the module sends that data over the analog data line [1],[2].

#### 2. Primary Constraints

The primary challenges came from the need to transmit the video data over a narrow bandwidth analog data channel. The available channel is sampled at 10,000 samples per second (at most), with 12 bit resolution. Thus, the primary challenges to overcome in order to meet product specifications involved: devising an effective analog encoding scheme within this bandwidth; compressing the data so that it takes a short enough duration to transmit (sending entire sample within mean flight time; keeping the noise from the module components off of the analog channel; maximizing the signals resilience to noise; and handling bit errors that occur. A supplemental challenge was establishing reliable communications between components.

#### 3. Economic

The product's design and creation utilized multiple forms of capital. In human terms, a variety of individuals have contributed to the project's success (discussed further in terms of direct and indirect stakeholders in the Social and Political section). In addition, the project made use of third party services such as major components vendors, component manufacturers, and delivery infrastructure. In this way, the project utilizes the existing infrastructure of these organizations, rather than necessitating the construction of entirely new facilities. Lastly, the materials used to manufacture the product come from the planet itself, as does the energy used in the manufacturing process and in operation.

The direct monetary investment in the project, for physical component and equipment purchases, rounds to approximately \$200. However, the equivalent monetary value of the labor provided in the development process approaches \$8,000 dollars. Tables A1 and A2 below, detail the preliminary planning estimates of costs for components and labor (estimated using \$30/hour). The formula, *estimated* = (min + 4\*typical + max)/6, yields the PERT values listed. Further below, Tables A3 and A4 detail the actual final costs for part and labor.

| LSTIMA          |      | AKIS    | AND EQU     | IPMENT CO  | 212 |       |

|-----------------|------|---------|-------------|------------|-----|-------|

| Estimated Dev   | velo | pmer    | nt Costs    | (Equipme   | nt) |       |

| Final Prototype |      |         |             |            |     |       |

| System          | Min  |         | Тур         | Max        | PE  | RT    |

| Camera          |      | \$5     | \$10        | \$40       | \$  | 14.17 |

| Controller      |      | \$10    | \$25        | \$80       | \$  | 31.67 |

| Data Storage    |      | \$2     | \$8         | \$30       | \$  | 10.67 |

| DAC             |      | \$2     | \$10        | \$20       | \$  | 10.33 |

| Misc. Passive   |      | \$1     | \$5         | \$20       | \$  | 6.83  |

| Power Systems   |      | \$4     | \$6         | \$25       | \$  | 8.83  |

| PCB             |      | \$40    | \$75        | \$150      | \$  | 81.67 |

| Total -         |      | \$64    | \$139       | \$365      |     | \$164 |

|                 |      |         |             |            |     |       |

| Development C   | ycle | 's 1 ar | nd 2 (Not I | PCB Versic | n)  |       |

| System          | Min  |         | Тур         | Max        | PE  | RT    |

| Total           |      | \$24    | \$64        | \$215      | \$  | 82.50 |

|                 |      |         |             |            |     |       |

| Development a   | nd T | est Eq  | uipment     |            |     |       |

| System          | Min  |         | Тур         | Max        | PE  | RT    |

| Total           |      | \$20    | \$35        | \$120      | \$  | 82.50 |

|                 |      |         |             |            |     |       |

| Equip. Total    | Min  |         | Тур         | Max        | PE  | RT    |

|                 |      | \$108   | \$238       | \$700      |     | \$329 |

# TABLE A1

# ESTIMATED PARTS AND EQUIPMENT COSTS

# TABLE A2

## ESTIMATED LABOR COSTS

| Estimated Dev  | velopmer  | nt Costs ( | Labor)    |           |

|----------------|-----------|------------|-----------|-----------|

| Labor (Weekly) |           |            |           |           |

| Person         | Min       | Тур        | Max       | PERT      |

| Myself (hrs)   | 8         | 18         | 30        | 18.3      |

| Myself (\$)    | \$ 240.00 | \$ 540.00  | \$ 900.00 | \$ 550.00 |

|                |           |            |           |           |

| Labor (Total)  |           |            |           |           |

| Person         | Min       | Тур        | Max       | PERT      |

| Myself (hrs)   | 160       | 360        | 600       | 366.7     |

| Myself (\$)    | \$4,800   | \$10,800   | \$18,000  | \$11,000  |

| Others (hrs)   | 10        | 15         | 40        | 18.3      |

| Myself (\$)    | \$300     | \$450      | \$1,200   | \$549     |

|                |           |            |           |           |

| Grand Total    | Min       | Тур        | Max       | PERT      |

|                | \$5,100   | \$11,250   | \$19,200  | \$11,549  |

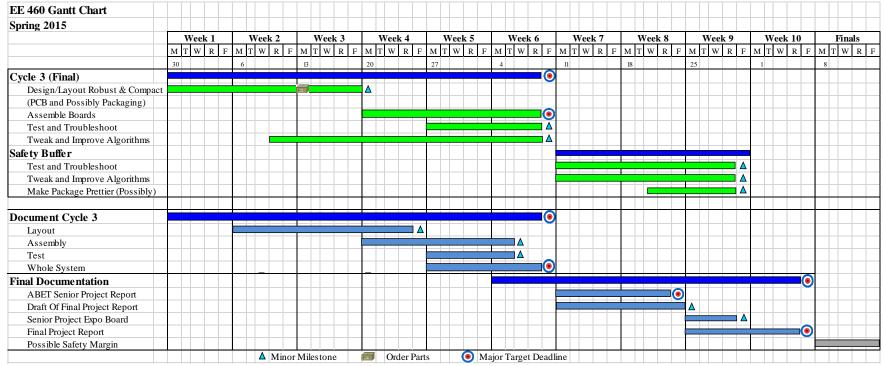

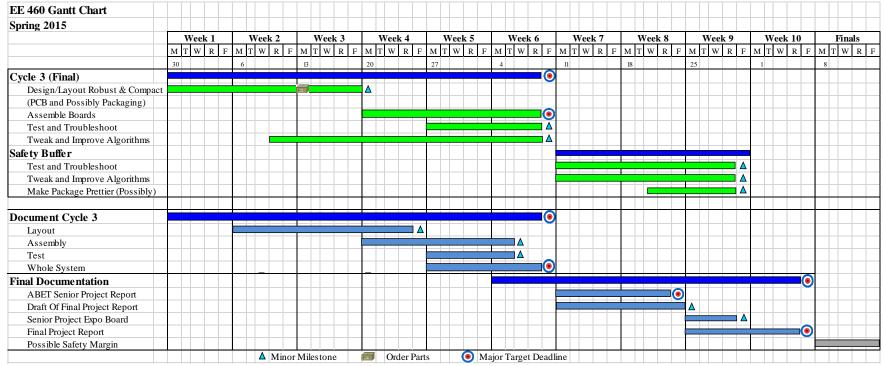

These estimated costs corresponded to the planned development cycle illustrated in the Gantt charts in Tables A5 (a), A5 (b), & A5 (c).

Tables A3 and A4 detail the actual final costs for part and labor (approximated using an updated \$35/hour) for the project. The parts whose costs are listed at N/A, are ones which were already owned before the start of the project, but are important enough to the final prototype, to warrant explicit mentioning in the table. Components and devices used for early prototyping, and for development and testing, but not purchased specifically for the project are not listed.

#### TABLE A3

| ACTUAL PARTS AND EQUIPMENT COSTS |  |

|----------------------------------|--|

| Actual Developmen    | nt Costs (Equipment)     |           |                     |      |         |       |          |

|----------------------|--------------------------|-----------|---------------------|------|---------|-------|----------|

| Final Prototype      |                          |           |                     |      |         |       |          |

| System               | Part Name/Number         | Vender    | Manufacturer        | Base | e Price | Cost  | (w∕ Tax) |

| Camera               | Raspeberry Pi 5MP Camera | Amazon    | Raspberry Pi Foun.  | \$   | 26.95   | \$    | 29.38    |

| Video Data Processor | Raspberry Pi - Model B+  | MCM Elec. | Raspberry Pi Foun.  | \$   | 25.00   | N/A   |          |

| Memory               | 16 GB Micro SD Card      | Amazon    | Kingston Digital    | \$   | 6.95    | N/A   |          |

| DAC                  | AD7245AANZ               | DigiKey   | Analog Devices      | \$   | 19.37   | \$    | 20.92    |

| D/A Control Unit     | Tiva C TM4C123GXL Eval   | DigiKey   | Texas Instruments   | \$   | 16.68   | \$    | 18.01    |

| Misc. Passive        | Caps/Resistors/Leads     | N/A       | N/A                 | \$   | 2.00    | N/A   |          |

|                      |                          |           | Total -             | \$   | 96.95   |       | \$68     |

| Early Prototype      |                          |           |                     |      |         |       |          |

| System               | Part Name                | Vender    | Manufacturer        | Base | e Price | Cost  | (w/ Tax) |

| Camera               | OV7670 300KP VGA Module  | Amazon    | Atomic Market       | \$   | 10.99   | \$    | 10.99    |

| Memory               | PmodSF2 - Serial PCM     | Amazon    | Digilent            | \$   | 14.95   | \$    | 14.95    |

| DAC                  | AD7243ANZ                | DigiKey   | Analog Devices      | \$   | 16.68   | \$    | 16.68    |

|                      |                          |           | Total:              | \$   | 42.62   | \$    | 42.62    |

| Development and Te   | st Equipment             |           |                     |      |         |       |          |

| Function             | Part Name                | Vender    | Manufacturer        | Base | e Price | Cost  | (w/ Tax) |

| ADC                  | AD1674JNZ                | DigiKey   | Analog Devices      | \$   | 29.17   | \$    | 31.50    |

| USB-UART Cable       | 768-1204                 | DigiKey   | FTDI                | \$   | 15.00   | \$    | 16.20    |

| Antialiasing Filter  | LTC1564IG#PBF            | DigiKey   | Linear Technologies | \$   | 17.59   | \$    | 19.00    |

| Breakout BNC         | FEMALE-20AWG LEADS       | DigiKey   | Pomona Electronics  | \$   | 17.10   | \$    | 18.47    |

|                      |                          |           | Total:              | \$   | 78.86   | \$    | 85.17    |

|                      | Shipping and Handing:    |           |                     |      |         |       |          |

| Total                | \$16.50                  |           | Equip. Total        | Base | e Price | Actua | l Cost   |

|                      |                          |           | S&H: \$16.50        | \$   | 218.43  | \$    | 196.10   |

# TABLE A4Actual (Approx.) Labor Costs

| Approximant I | Developn  | nent Cost | s (Labor) |           |

|---------------|-----------|-----------|-----------|-----------|

| Labor (Weekly | Averaged) |           |           |           |

| Person        | Min       | Тур       | Max       | PERT      |

| Myself (hrs)  | 8         | 10        | 15        | 10.5      |

| Myself (\$)   | \$ 280.00 | \$ 350.00 | \$ 525.00 | \$ 367.50 |

|               |           |           |           |           |

| Labor (Total) |           |           |           |           |

| Person        | Min       | Тур       | Max       | PERT      |

| Myself (hrs)  | 160       | 200       | 300       | 210.0     |

| Myself (\$)   | \$5,600   | \$7,000   | \$10,500  | \$7,350   |

| Others (hrs)  | 12        | 18        | 25        | 18.2      |

| Others (\$)   | \$420     | \$630     | \$875     | \$636     |

|               |           |           |           |           |

| Grand Total   | Min       | Тур       | Max       | PERT      |

|               | \$6,020   | \$7,630   | \$11,375  | \$7,986   |

The initial planning timeline for project development is shown in Tables A5 (a), A5 (b), & A5 (c) below.

# TABLE A5 (a)

# PLANNING GANTT CHART – FALL QUARTER AND WINTER BREAK 2014 [21]

| EE 460 Gantt Chart                |          |          |        |        |          |    |        |         |         |          |     |       |          |     |     |       |            |       |        |       |        |          |       |        |               |        |          |      |     |         |         |      |   |          |    |      |

|-----------------------------------|----------|----------|--------|--------|----------|----|--------|---------|---------|----------|-----|-------|----------|-----|-----|-------|------------|-------|--------|-------|--------|----------|-------|--------|---------------|--------|----------|------|-----|---------|---------|------|---|----------|----|------|

| Fall 2014                         |          |          |        |        |          |    |        |         |         |          |     |       |          |     |     |       |            |       |        |       |        |          |       |        |               |        |          |      |     |         |         |      |   |          |    |      |

|                                   |          | eek 1    |        |        | eek 2    |    | Week   |         |         | Week 4   |     |       | eek 5/   |     |     | eek 6 |            |       | Veek ' |       |        | Wee      |       |        |               | eek 9  |          |      | eek |         |         | Weel |   |          |    | nals |

|                                   |          | WR       |        |        | W R I    | _  |        | R F     |         | T W F    | t F |       | WR       | _   |     | W R   | F          | _     | WI     | ιF    |        |          | R     |        |               | WR     | t F      |      | W   | R F     | Μ       | ΤW   | R | F M      | ΤV | W R  |

| Project Plan                      | 22       |          |        | 29     |          | 6  |        |         | 13      |          | _   | 20    |          | _   | 27  | _     |            | 3     |        | _     | 10     | _        |       | 1      | 17            |        | _        | 24   |     |         | 1       |      |   | 8        | _  | _    |

| Abstract (Proposal) V1            |          |          |        |        |          |    |        |         |         |          |     |       |          |     |     |       |            |       |        |       | _      |          |       |        |               |        |          |      |     |         |         |      |   | T        |    |      |

| Requirements and Specifications   |          |          |        |        |          |    | 0      | -       |         |          | -   |       |          | -   |     | _     | _          |       | _      |       | _      |          |       | -      | _             |        |          | _    | _   | _       |         | -    |   |          | _  |      |

| Block Diagram                     |          |          |        |        |          |    |        |         | h . /   | <b>)</b> |     |       |          | -   |     | NO    | <b>)TE</b> | Du    | ıe d   | late  | es /   | AND      | ) fe  | ed     | ba            | ck ı   | req      | uire | d   |         |         |      |   |          |    |      |

| Literature search                 |          |          |        |        |          |    |        |         |         | J        |     | ▲     |          | -   |     |       |            |       |        |       |        |          |       |        |               |        |          |      |     |         | -       |      |   |          |    |      |

| Gantt Chart                       |          |          |        |        |          |    |        |         |         |          |     |       | 2        |     | A - | -     |            | -     |        | -     | _      |          |       |        |               |        | -        |      |     |         |         |      |   |          |    |      |

| Cost Estimates                    |          |          |        |        |          | _  |        |         |         |          |     |       |          |     |     | _     |            | _     |        |       | _      |          |       |        |               |        | -        |      |     | _       | -       | _    |   |          | _  |      |

| ABET Sr. Project Analysis         |          |          |        |        |          | _  |        | _       |         |          |     |       |          |     |     |       |            | ▲     |        |       | _      | _        |       |        |               |        | -        |      |     |         | -       |      |   |          |    |      |

| Requirements and Specifications V | )   In++ | ~        |        |        |          | _  |        | _       |         |          |     |       |          | T   |     |       |            | - U   | 1      |       |        |          |       |        |               |        |          |      |     |         |         |      |   |          |    |      |

| Report VI                         | 2 + 1111 | 0        |        |        |          |    |        |         |         |          |     |       |          |     |     |       |            |       |        |       | 1-     | Ŷ        |       | ^      |               |        | ·        |      |     | _       | -       |      |   |          |    |      |

| Advisor Feedback Due              |          |          |        |        |          |    |        |         |         |          |     |       | 2        |     |     |       |            |       |        |       |        |          | ,     | _      |               | -      |          |      |     | 2       | -       | -    |   |          | _  |      |

| Report V2                         |          |          |        |        |          | _  |        |         |         |          |     |       | <b>4</b> | -   |     | _     |            | _     |        |       | _      |          |       |        |               |        |          |      |     | 4       | ,       |      |   | <u> </u> |    | _    |

| Report V2                         |          |          |        | _      |          | -  |        | _       |         |          |     |       |          | -   |     | _     |            | _     |        |       | -      | -        |       |        | _             |        |          |      |     |         |         |      |   | ┭≏       |    |      |

| Presentations                     |          |          |        |        |          | _  |        |         |         |          |     |       |          |     |     |       |            |       |        |       |        | -        |       |        |               |        | -        |      |     |         |         |      |   |          |    |      |

| Requirements and Specifications   |          |          |        |        |          | _  |        |         | $\odot$ |          |     |       |          |     |     |       |            |       |        |       |        |          |       |        |               |        |          |      |     |         |         | _    |   |          |    |      |

| Report V1                         |          |          |        |        |          | _  |        | _       |         |          |     |       |          | -   |     | _     |            | _     |        |       | _      |          |       |        |               |        |          |      |     |         | <u></u> |      |   |          |    |      |

| Report VI                         |          |          | -      |        |          | -  |        |         |         |          | -   |       |          |     |     | -     |            | -     |        | -     | -      | -        |       |        |               |        | -        |      |     | -       | 9       | -    |   | _        |    |      |

| HW1 Resume & Cover Lette          |          |          |        |        | -        | -  |        | -       |         |          |     |       |          |     |     |       |            |       |        | -     |        | -        |       | +      |               |        | -        |      |     |         |         |      |   |          |    |      |