# Study of High-k Dielectrics and their Interfaces on Semiconductors for Device Applications

Thesis submitted in accordance with the requirements of the University of Liverpool for the degree of Doctor in Philosophy in the Faculty of Science and Engineering by

### SITI NURBAYA SUPARDAN

November 2019

Department of Electrical Engineering and Electronics

#### Abstract

# Study of High-k Dielectrics and their Interfaces on Semiconductors for Device Applications

#### Siti Nurbaya Supardan

This thesis has focused on two emerging applications of high-k dielectrics in Metal-Oxide-Semiconductor Field Effect Transistors (MOSFETs) and in Metal-Insulator-Semiconductor High Electron Mobility Transistors (MIS-HEMTs). The key aim has been to propose the best routes for passivation of semiconductor/high-k oxide interfaces by investigating the band alignments and interface properties of several oxides, such as  $Tm_2O_3$ ,  $Ta_2O_5$ ,  $ZrO_2$ ,  $Al_2O_3$  and MgO, deposited on different semiconductors: Si, Ge, GaN, InGaAs and InGaSb. The electrical characterisation of fabricated MIS capacitor and (MIS)-HEMT devices have also been performed.

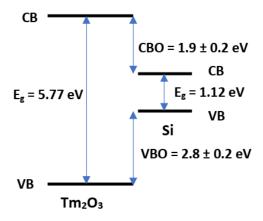

Thulium silicate (TmSiO) has been identified as a promising candidate for integration as interfacial layer (IL) in HfO<sub>2</sub>/TiN MOSFETs. The physical properties of  $Tm_2O_3/IL/Si$  interface have been elucidated, where IL (TmSiO) has been formed using different post-deposition annealing (PDA) temperatures, from 550 to 750 °C. It has been found that the best-scaled stack (sub-nm IL) is formed at 550 °C PDA with a graded interface layer and a strong  $SiO_x$  (Si 3+) component. A large valence band offset (VBO) of 2.8 eV and a large conduction band offset (CBO) of 1.9 eV have been derived for  $Tm_2O_3/Si$  by X-ray photoelectron spectroscopy (XPS) and variable angle spectroscopic ellipsometry.

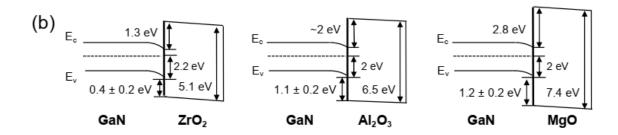

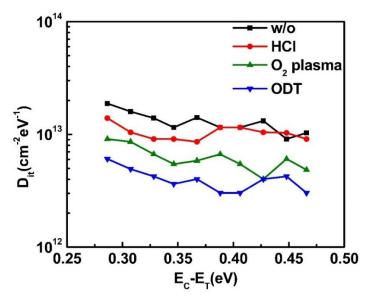

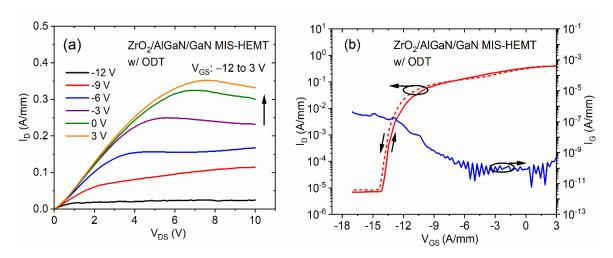

Further increase of device performance can be achieved by replacing Si with GaN for high frequency, high power and high-temperature operation. In this thesis, several GaN cleaning procedures have been considered: 30% NH<sub>4</sub>OH, 20% (NH<sub>4</sub>)<sub>2</sub>S, and 37% HCl. It has been found that the HCl treatment shows the lowest oxygen contamination and Garich surface, and hence has been used prior sputtering of Ta<sub>2</sub>O<sub>5</sub>, Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub> and MgO on GaN. The large VBOs of 1.1 eV and 1.2 eV have been derived for Al<sub>2</sub>O<sub>3</sub> and MgO on GaN respectively, using XPS and Kraut's method; the corresponding CBOs are 2.0 eV and 2.8 eV respectively, taking into account the band gaps of Al<sub>2</sub>O<sub>3</sub> (6.5 eV) and MgO (7.4 eV) determined from XPS O 1s electron energy spectra. The lowest leakage currents were obtained for devices with  $Al_2O_3$  and MgO, i.e.  $5.3 \times 10^{-6}$  A/cm<sup>2</sup> and  $3.2 \times 10^{-6}$  A/cm<sup>2</sup> at 1 V, respectively in agreement with high band offsets (> 1 eV). Furthermore, the effect of different surface treatments (HCl, O2 plasma and 1-Octadecanethiol (ODT)) prior to atomic layer deposition of Al<sub>2</sub>O<sub>3</sub> on the GaN/AlGaN/GaN heterostructure has been investigated. The MIS-HEMTs fabricated using the low-cost ODT GaN surface treatment have been found to exhibit superior performance for power switching applications such as a low threshold voltage,  $V_T$  of -12.3 V, hysteresis of 0.12 V, a small subthreshold voltage slope (SS) of 73 mV/dec, and a low density of interface states,  $D_{it}$  of  $3.0 \times 10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup>.

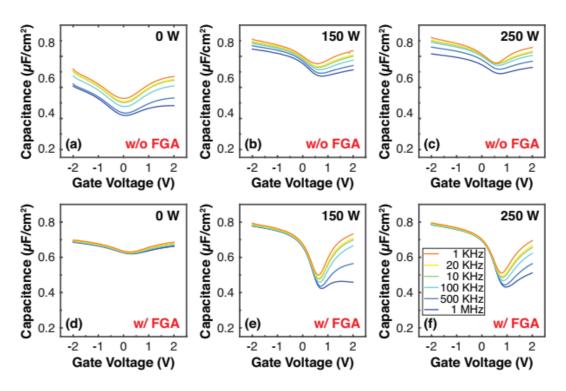

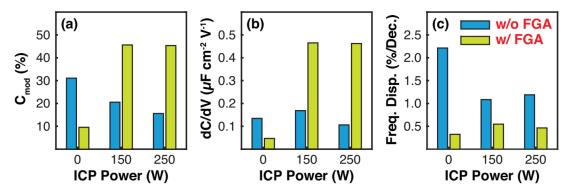

A comprehensive novel study of HfO<sub>2</sub>/InGaAs and Al<sub>2</sub>O<sub>3</sub>/InGaSb interfaces have also been conducted for use in III-V based MOSFETs. The addition of the plasma H<sub>2</sub>/TMA/H<sub>2</sub> pre-cleaning has been found to be very effective in recovering etch damage on InGaAs, especially for (110) orientation, and led to the improvement of electrical characteristics. Furthermore, the combination of H<sub>2</sub> plasma exposure and forming gas anneal yielded significantly improved metrics for Al<sub>2</sub>O<sub>3</sub>/InGaSb over the control HCl-treated sample, with the 150 W plasma treatment giving both the highest capacitance and the lowest stretch out.

#### Acknowledgement

All Praise to ALLAH S.W.T the Almighty, for giving me the blessing, the strength, the chance and endurance to complete this thesis.

I want to express my utmost gratitude and thanks to my primary supervisor, Associate Professor Dr Ivona Z. Mitrovic for giving me the golden opportunity to work as a full-time PhD student under her supervision. Without her guidance and persistent help, this PhD work would not have been possible.

I am also deeply indebted to my secondary supervisor, Professor Dr Vin Dhanak, for all his guidance and advice, especially for XPS measurements and analysis. My special thanks to my respected PhD assessors, Professor Steve Hall and Dr Ian Sandall, for the good assessment and constructive comments of my research work.

Special thanks to all collaborators for great contributions: Partha Das from National Institute of Technology Durgapur, India; Laura and Professor Per-Erik Hellström from KTH Royal Institute of Technology, Sweden; David Millar, Yen Chun and Professor Iain Thayne from University of Glasgow, UK; Dr Zaffar Zaidi, Dr Kean Boon Lee and Professor Peter Houston from University of Sheffield, UK; Dr Adrian Hannah and Dr Reza Valizadeh from STFC Daresbury Laboratory, UK; and Yutao Cai and Miao Ciu from Xi'an Jiaotong-Liverpool University, China.

My appreciation also extends to my colleagues, Dr Naser Sedghi, Dr Ayendra Weerakkody, Dr Andy Shaw, Dr Jidong, Sawangsri Kriangkamon, Dr David Donaghy, Serdar, Zhongming, Siriny, Ulfa, Afnida, Fatirah and Saidatul from Electrical Engineering and Electronics department, University of Liverpool for their support and help during my PhD work. Also, not to forget to Dr David Hesp, Dr Tom Whittles, Dr Mohammed Althobaiti, Dr James and Leanne Jones from Stephenson Institute Renewable Energy (SIRE), the University of Liverpool for their help in the lab.

I want to acknowledge Malaysia's Ministry of Education and Universiti Teknologi MARA (UiTM), Malaysia for financial support.

Finally, and most importantly, I would like to thank my family especially my beloved husband Mohd Hilmi for his continuous supports and love, to my beautiful kids Hannan, Isyraf, Hannah and Ishaq thanks for sacrifice your time while I was busy with my lab and to my parents Supardan and Sarah, my siblings, family in-laws who have been always pray for my success.

Indeed, this work would never be possible without the hands from so many amazing people and friends who have been encouraging my PhD journey.

Many thanks.

### **Table of Content**

| Abstract                                  | 1     |

|-------------------------------------------|-------|

| Acknowledgement                           | ii    |

| Table of Content                          | iii   |

| List of Figures                           | viii  |

| List of tables                            | xx    |

| Contribution from this work               | xxiii |

| Abbreviations                             | xxv   |

| CHAPTER 1 Introduction                    | 1     |

| 1.1 CMOS technology                       | 1     |

| 1.1.1 High-k dielectric material          | 4     |

| 1.1.2 MOSFET operation                    | 7     |

| 1.1.2.1 Current-Voltage characteristics   | 10    |

| 1.1.2.2 MOSFET device metrices            | 13    |

| 1.1.3 State of the art Si CMOS technology | 15    |

| 1.1.4 Ge-based MOSFETs                    | 17    |

| 1.1.5 Other III-V MOSFETs                 | 19    |

| 1.2 GaN MIS-HEMTs                         | 21    |

| 1.2.1 Basic structure of HEMT             | 23    |

| 1.2.2 GaN issues                          | 25    |

| 1.2.3 Several oxides on GaN               | 26    |

| 1.3 Research aims and objectives          | 27    |

| 1.4 Thesis outlines                       | 28    |

| CHAPTER 2 Experimental Techniques                                                               | 30 |

|-------------------------------------------------------------------------------------------------|----|

| 2.1 Material deposition methods                                                                 | 30 |

| 2.1.1 Sputtering                                                                                | 30 |

| 2.1.2 Atomic layer deposition                                                                   | 33 |

| 2.2 X-ray photoelectron spectroscopy (XPS)                                                      | 36 |

| 2.2.1 Basic principles of XPS                                                                   | 36 |

| 2.2.2 Ultra-high vacuum                                                                         | 38 |

| 2.2.3 X-ray source                                                                              | 42 |

| 2.2.4 Electron energy analyser                                                                  | 45 |

| 2.2.5 Detector                                                                                  | 47 |

| 2.2.6 XPS resolution                                                                            | 48 |

| 2.2.7 Inelastic mean free path (IMFP)                                                           | 50 |

| 2.3 Variable angle spectroscopic ellipsometry (VASE)                                            | 51 |

| 2.3.1 Basic principle of VASE                                                                   | 51 |

| 2.3.2 Data analysis                                                                             | 52 |

| 2.4 Atomic force microscopy (AFM)                                                               | 54 |

| 2.5 High-resolution transmission electron microscopy (HR-TEM)                                   | 56 |

| 2.6 Electrical measurement                                                                      | 58 |

| 2.6.1 Current-Voltage measurements                                                              | 58 |

| 2.6.2 Capacitance-Voltage measurements                                                          | 64 |

| 2.7 Conclusion                                                                                  | 67 |

| CHAPTER 3 High-k Dielectrics on Si and Ge                                                       | 68 |

| 3.1 Introduction                                                                                | 68 |

| 3.2 Band alignment of Tm <sub>2</sub> O <sub>3</sub> /Si                                        | 74 |

| 3.2.1 Experimental                                                                              | 75 |

| 3.2.2 Estimation of VBO for Tm <sub>2</sub> O <sub>3</sub> /Si gate stacks using Kraut's method | 77 |

| 3.2.3 Properties of TmSiO interfacial layer fabricated using different PDAs of Tm <sub>2</sub>                                |       |

|-------------------------------------------------------------------------------------------------------------------------------|-------|

| 3.2.4 High-resolution transmission electron microscopy and electron energy spectroscopy studies of HfO <sub>2</sub> /TmSiO/Si | loss  |

| 3.3 XPS study of Tm <sub>2</sub> O <sub>3</sub> /Ge interfaces                                                                | _ 98  |

| 3.3.1 Experimental work                                                                                                       | 98    |

| 3.3.2 Results and Discussion                                                                                                  | _ 99  |

| 3.4 Conclusion                                                                                                                | _ 109 |

| CHAPTER 4 Band Alignment of Sputtered Dielectrics on GaN                                                                      | _111  |

| 4.1 Introduction                                                                                                              | _ 111 |

| 4.2 Band alignment of Ta <sub>2</sub> O <sub>5</sub> /GaN                                                                     | _ 114 |

| 4.2.1 Experimental                                                                                                            | _ 114 |

| 4.2.2 Thickness and band gap estimation using VASE                                                                            | _ 119 |

| 4.2.3 Band offsets estimation                                                                                                 | _ 123 |

| 4.3 Band alignment of ZrO <sub>2</sub> /GaN, Al <sub>2</sub> O <sub>3</sub> /GaN and MgO/GaN                                  | _ 127 |

| 4.3.1 Experimental                                                                                                            | _ 131 |

| 4.3.1.1 Sputtering procedure                                                                                                  | _ 131 |

| 4.3.1.2 GaN samples                                                                                                           | _ 134 |

| 4.3.2 Band gap estimation of oxides using XPS O 1s energy loss spectra                                                        | _ 138 |

| 4.3.3 Band offsets of ZrO <sub>2</sub> , Al <sub>2</sub> O <sub>3</sub> and MgO on GaN                                        | _ 139 |

| 4.3.3.1 The effect of differential charging                                                                                   | _ 144 |

| 4.3.3.2 The effect of band bending                                                                                            | _ 147 |

| 4.4 Conclusion                                                                                                                | _ 152 |

| CHAPTER 5 GaN-Based Devices                                                                                                   | _154  |

| 5.1 Introduction                                                                                                              | _ 154 |

| 5.2 GaN-based MIS-capacitors                                                                                                  | _ 158 |

| 5.2.1 Device fabrication                                                                                                      | _ 158 |

| 5.2.2 Oxide thickness estimation using VASE                                                                                   | _ 160 |

| 5.2.3 IV measurements                                                                                     | 162   |

|-----------------------------------------------------------------------------------------------------------|-------|

| 5.2.4 Conduction mechanisms                                                                               | 170   |

| 5.2.4.1 Fowler-Nordheim tunnelling                                                                        | 171   |

| 5.2.4.2 Poole-Frenkel emission                                                                            | 183   |

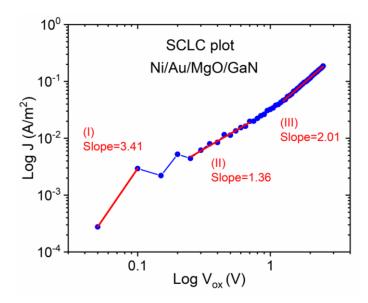

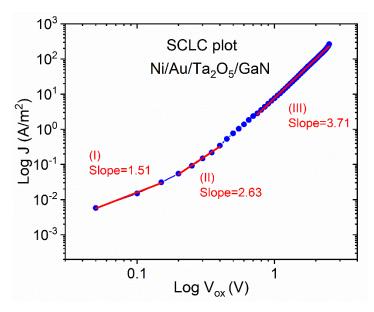

| 5.2.4.3 Space-charge-limited current                                                                      | 187   |

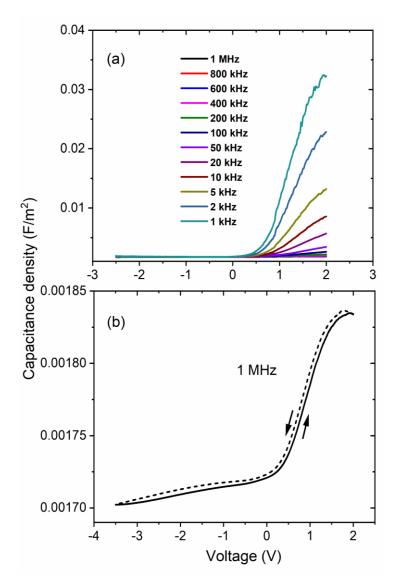

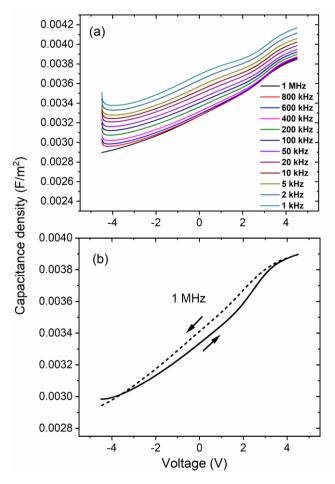

| 5.2.5 CV measurements                                                                                     | 190   |

| 5.3 Al <sub>2</sub> O <sub>3</sub> -based MIS-HEMTs                                                       | 195   |

| 5.3.1 Device fabrication                                                                                  | 195   |

| 5.3.1.1 Fabrication process of HEMTs and MIS-HEMTs (D-mode and E-mode)                                    | 196   |

| 5.3.1.2 Fabrication of Al <sub>2</sub> O <sub>3</sub> -MIS-HEMTs with different surface treatments (with  | hout, |

| HCl, O <sub>2</sub> plasma and ODT)                                                                       | 198   |

| 5.3.2 XPS measurements of Al <sub>2</sub> O <sub>3</sub> /AlGaN/GaN with different GaN surface treatments | nents |

|                                                                                                           | 200   |

| 5.3.3 Electrical measurements                                                                             | 202   |

| 5.3.3.1 AlGaN/GaN HEMTs and capacitors                                                                    | 202   |

| 5.3.3.2 D-mode and E-mode MIS-HEMTs and MIS-capacitors with Al <sub>2</sub> O <sub>3</sub> as gat         | te    |

| dielectric                                                                                                | 204   |

| 5.3.3.3 Effect of different GaN surface treatments on Al <sub>2</sub> O <sub>3</sub> based AlGaN/GaN I    | MIS-  |

| HEMTs properties                                                                                          | 214   |

| 5.4 ZrO <sub>2</sub> -based MIS-HEMTs                                                                     | 221   |

| 5.4.1 Device fabrication                                                                                  | 221   |

| 5.4.2 Effect of ODT GaN surface treatment on ZrO <sub>2</sub> -based AlGaN/GaN MIS-HE                     | EMTs  |

| properties                                                                                                | 222   |

| 5.5 Conclusion                                                                                            | 226   |

| CHAPTER 6 Study of surface treatments on III-V compound semiconductor                                     | rs    |

|                                                                                                           | 228   |

|                                                                                                           | 220   |

| 6.1 Introduction                                                                                          | . 228 |

| 6.2 InGaAs orientation and surface treatments effect on electrical properties of                          |       |

| HfO <sub>2</sub> /InGaAs based MOS capacitors                                                             | 231   |

| 6.2.1 Process flow of the HfO <sub>2</sub> /InGaAs samples                                                | 231   |

| 6.2.2 XPS studies of HfO <sub>2</sub> /InGaAs interface                                                   | 234   |

| 6.2.2.1 XPS analysis of InGaAs blanket samples                                                                   | 234 |

|------------------------------------------------------------------------------------------------------------------|-----|

| 6.2.2.2 XPS analysis of HfO <sub>2</sub> /InGaAs samples after H <sub>2</sub> /TMA/H <sub>2</sub> plasma exposur | e   |

| and forming gas anneal                                                                                           | 236 |

| 6.2.3 The correlation between XPS analysis and electrical results                                                | 240 |

| 6.3 InGaSb surface treatments                                                                                    | 244 |

| 6.3.1 Experimental details on surface and sample preparation                                                     | 245 |

| 6.3.2 Experimental details on XPS measurements                                                                   | 247 |

| 6.3.2.1 Effect of HCl surface treatment on n- and p-InGaSb                                                       | 248 |

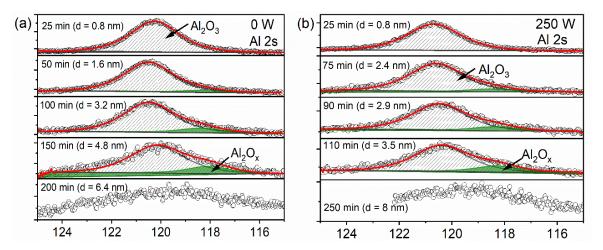

| 6.3.2.2 Effect of HCl and H <sub>2</sub> plasma exposure on Al <sub>2</sub> O <sub>3</sub> /n-InGaSb interface   | 251 |

| 6.3.3 The correlation between XPS analysis and STEM, EDX and electrical results                                  | 257 |

| 6.4 Conclusion                                                                                                   | 261 |

| CHAPTER 7 Conclusion and future work                                                                             | 263 |

| References                                                                                                       | 270 |

## **List of Figures**

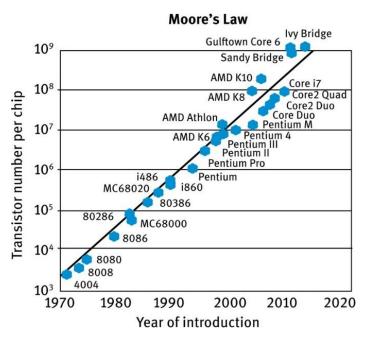

| Figu | re 1.1: The number of transistors per chip increases exponentially as predicte by Moore's law [2]                                                                                                                                                                                                                   | d<br>2    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

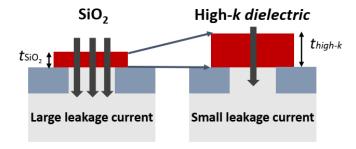

| Figu | re 1.2: Reduction of the tunnel leakage current by replacing $SiO_2$ with a high- $k$ gate dielectric.                                                                                                                                                                                                              | k<br>_3   |

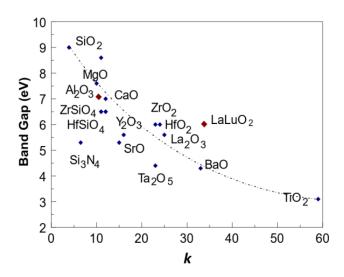

| Figu | re 1.3: The trade-off between the dielectric constant and band gap, which lim the choice of gate oxides [8].                                                                                                                                                                                                        |           |

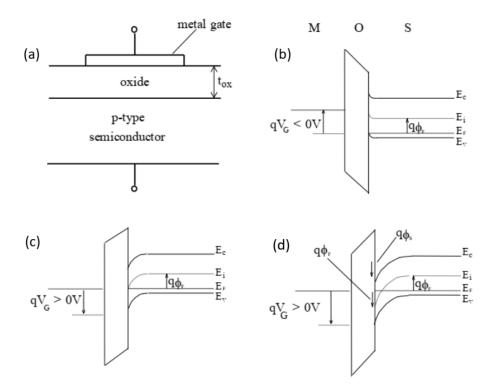

| Figu | re 1.4: (a) p-type MOS-capacitor, (b) accumulation condition, (c) depletion condition and (d) depletion and inversion condition (electron channel formin [18].                                                                                                                                                      | g)<br>_ 9 |

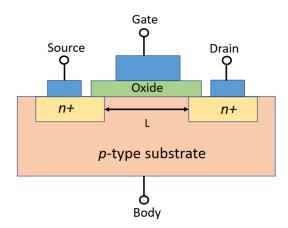

| Figu | re 1.5: A schematic of an $n$ -MOSFET structure. The current in the MOSFET is d to the flow of charge from the source terminal to drain terminal through the inversion-layer-induced (or referred to the channel region with a channel length $L$ ) adjacent to the metal-oxide-semiconductor interface.            |           |

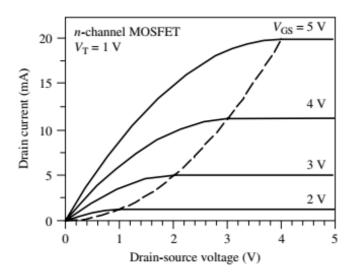

| Figu | re 1.6: The current-voltage output characteristics of an $n$ -channel MOSFET (long-channel device) with current saturation caused by pinch-off. The intersections with the dotted line indicate the onset of saturation for each characteristic. The threshold voltage is assumed to be $V_T = 1 \text{ V } [19]$ . | 11        |

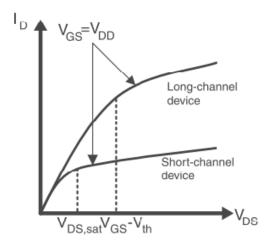

| Figu | re 1.7: Short channel device expected behaviour due to velocity saturation [20                                                                                                                                                                                                                                      | 0].<br>12 |

| Figu | re 1.8: The common source output characteristics of an n-channel MOSFET (a with four device metrics: on-current, on-resistance, output resistance, and transconductance; and (b) with two additional device metrics: subthreshold swing and drain-induced barrier lowering [22].                                    |           |

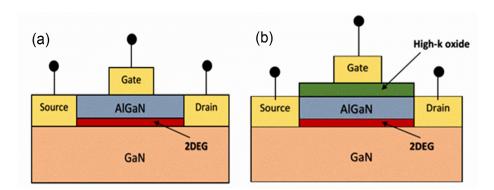

| Figu | re 1.9: Structure of (a) AlGaN/GaN HEMT, (b) AlGaN/GaN MIS-HEMT.                                                                                                                                                                                                                                                    | 24        |

| Figu | re 1.10: The 2DEG formation (a) before heterojunction, (b) the formed heterojunction produces tensile stress, (c) the polarization dipole occurs, (d) the 2DEG is formed [137], [138].                                                                                                                              | 25        |

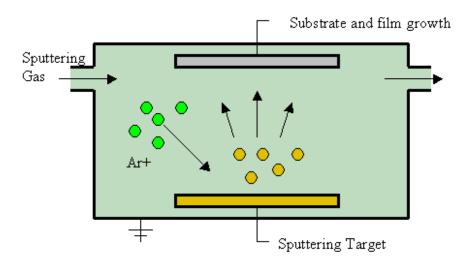

| Figu | re 2.1: The schematic illustration of the sputtering system [164].                                                                                                                                                                                                                                                  | 32        |

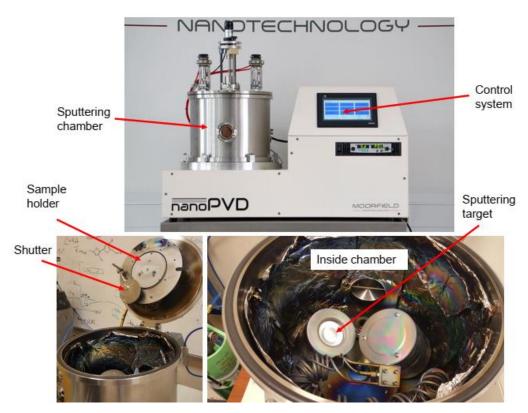

| Figu | re 2.2: The RF magnetron sputtering system used in this work at the Universit of Liverpool, UK.                                                                                                                                                                                                                     | З3        |

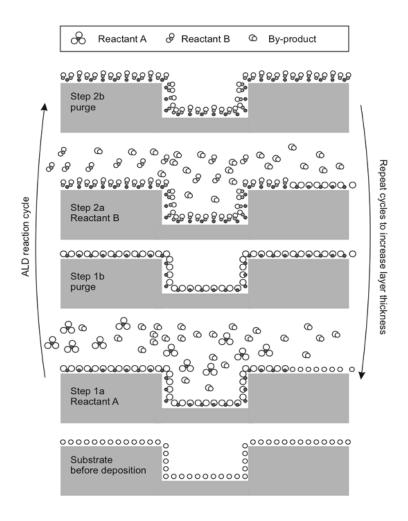

| Figu | re 2.3: The schematic diagram of one ALD cycle [167].                                                                                                                                                                                                                                                               | 35        |

| Technology, Sweden.                                                                                                                                                                                                                                                                                                                                | _36        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

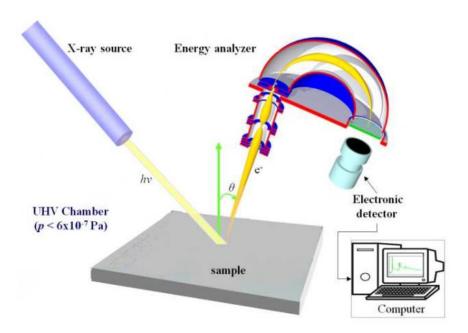

| Figure 2.5: The schematic of a typical XPS system consists of the sample stage, Ulchamber, X-ray source, energy analyser and detector [170].                                                                                                                                                                                                       |            |

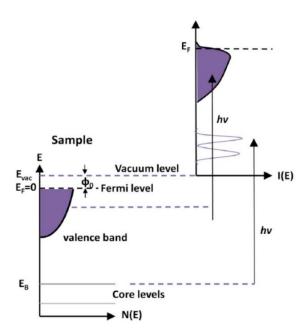

| Figure 2.6: An illustration of the photoemission process showing the energy levels within the material [171].                                                                                                                                                                                                                                      | s<br>_38   |

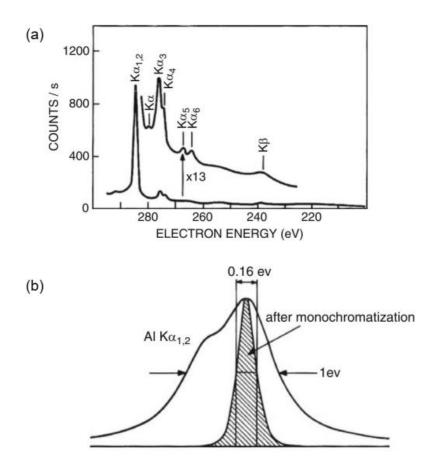

| Figure 2.7: (a) Al X-ray satellites of the low binding energy side of a C 1s spectrum (without monochromator); (b) Action of a monochromator crystal on the Al $K\alpha_{1,2}$ radiation. The shadowed region is the excitation line shape with a full width at half maximum FWHM = 0.16 eV which puts a limit to the experiment resolution [172]. |            |

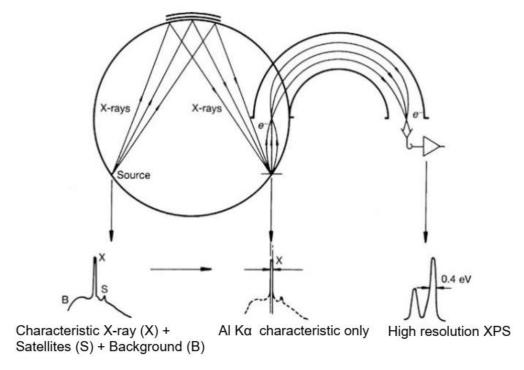

| Figure 2.8: Monochromatic X-ray source provide high resolution XPS spectrum [172], [174].                                                                                                                                                                                                                                                          | _44        |

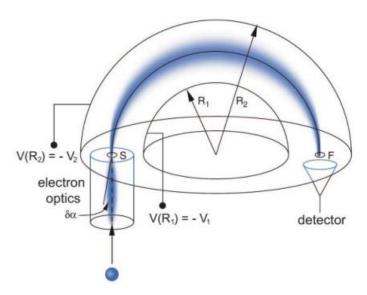

| Figure 2.9: Schematic of a concentric hemispherical analyser. Both hemispheres at a negative potential, with $V(R_2) < V(R_1)$ , where $V_2 > V_1$ [175].                                                                                                                                                                                          |            |

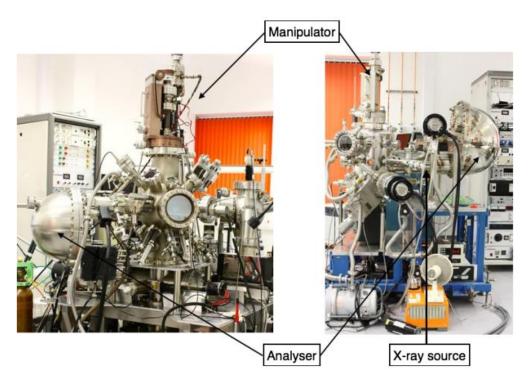

| Figure 2.10: XPS system used in this work at the University of Liverpool, UK [176].                                                                                                                                                                                                                                                                | 48         |

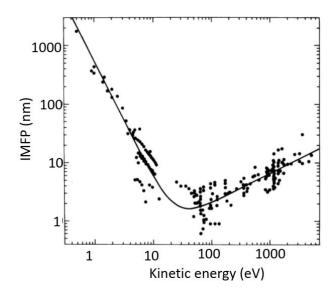

| Figure 2.11: The "universal curve" of inelastic mean free path of electrons in a sol as a function of kinetic energy [177].                                                                                                                                                                                                                        | lid<br>_51 |

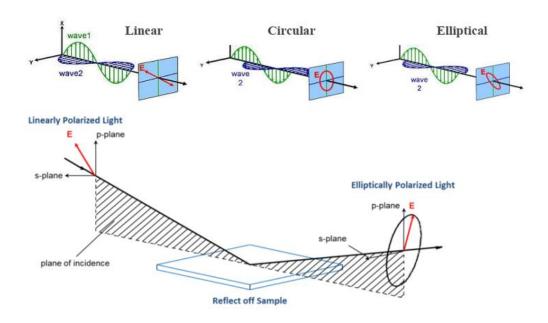

| Figure 2.12: A simplified schematic showing the change from linearly polarised light to elliptically polarized light [178].                                                                                                                                                                                                                        | tht<br>52  |

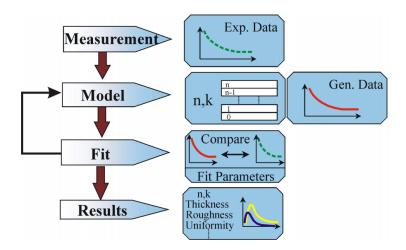

| Figure 2.13: The SE data analysis flowchart [178].                                                                                                                                                                                                                                                                                                 | _53        |

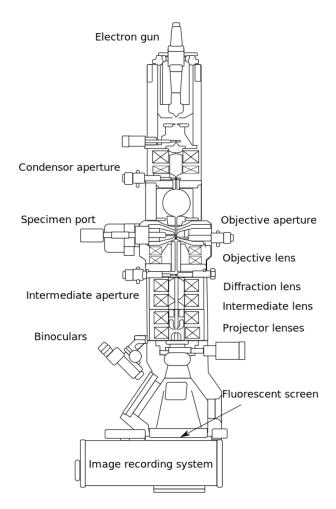

| Figure 2.14: A schematic of a typical transmission electron microscope [181].                                                                                                                                                                                                                                                                      | _58        |

| Figure 2.15: MOS band diagrams showing several electrode-limited conduction mechanisms (a) Schottky emission, (b) Fowler-Nordheim tunnelling and (c) direct tunnelling.                                                                                                                                                                            | _59        |

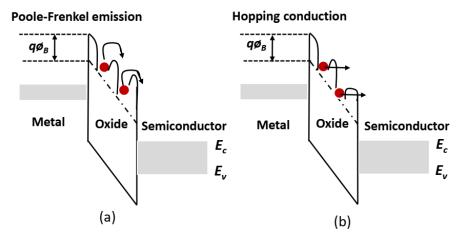

| Figure 2.16: MOS band diagrams showing several bulk-limited conduction mechanisms: (a) Poole-Frenkel emission and (b) hopping conduction                                                                                                                                                                                                           | _59        |

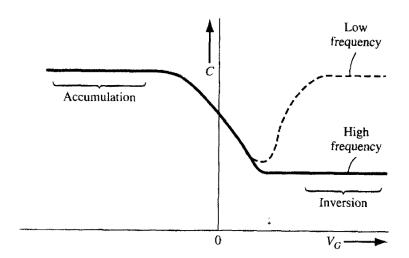

| Figure 2.17: Idealized low-frequency and high-frequency CV plots of a MOS capacitor (p-type substrate) [21].                                                                                                                                                                                                                                       | _65        |

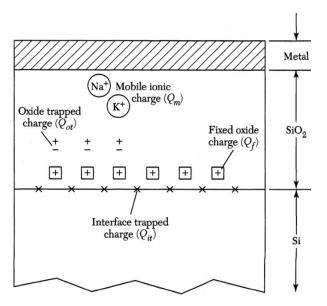

| Figure 2.18: Terminology for charges associated with thermally oxidised silicon [185].                                                                                                                                                                                                                                                             | _66        |

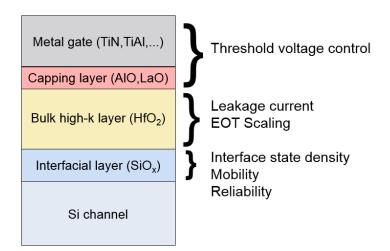

| Figure 3.1: The schematic diagram of Hf-based/metal gate stack that has been integrated in CMOS technology since 2007 [191].                                                                                                                                                                                                                       | _71        |

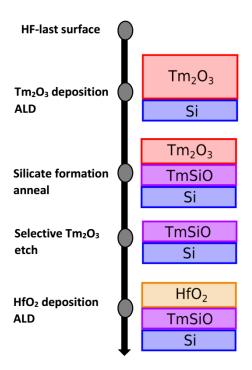

| Figure 3.2: The process flow of TmSiO/HfO <sub>2</sub> gate dielectric stack [59].                                                                                                                                                                                                                                                                 | 76         |

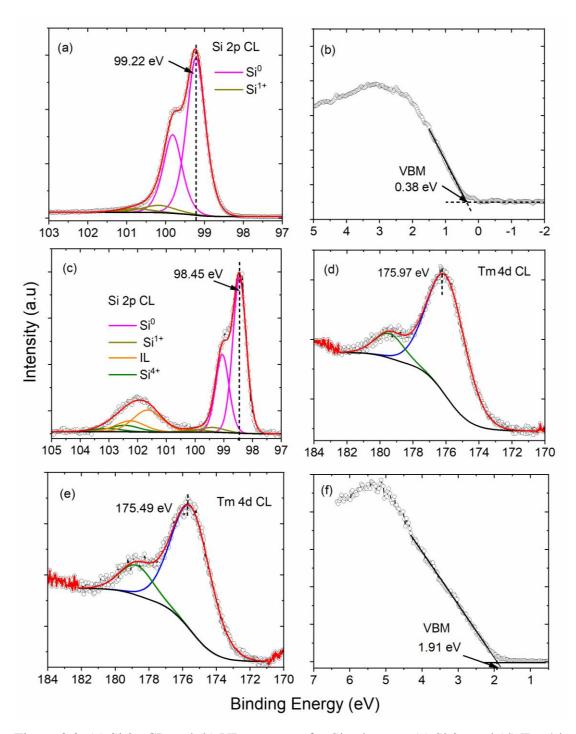

| Figure 3.3: (a) Si 2p CL and (b) VB spectrum for Si substrate; (c) Si 2p and (d) Tm 4d CLs for interfacial $Tm_2O_3/Si$ sample; (e) Tm 4d and (f) VB spectrum for bulk $Tm_2O_3$ sample82                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.4: Schematic energy band diagram of $Tm_2O_3/Si$ gate stack derived from XPS and VASE measurements in this study83                                                                                                                                                                                                                                                                                                                                                                                    |

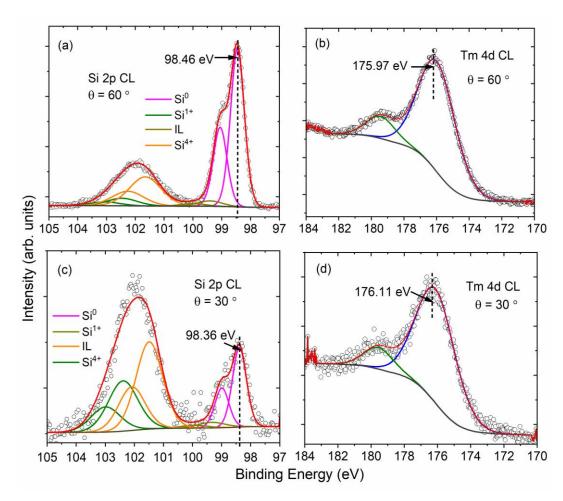

| Figure 3.5: The angle-resolved XPS of Si 2p and Tm 4d CLs spectra for the interfacial $Tm_2O_3/Si$ sample83                                                                                                                                                                                                                                                                                                                                                                                                    |

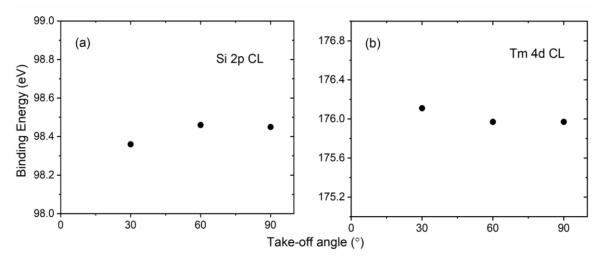

| Figure 3.6: Dependence of measured binding energies on take-off angles for Si 2p and Tm 4d XPS CL spectra for the interfacial $Tm_2O_3/Si$ sample84                                                                                                                                                                                                                                                                                                                                                            |

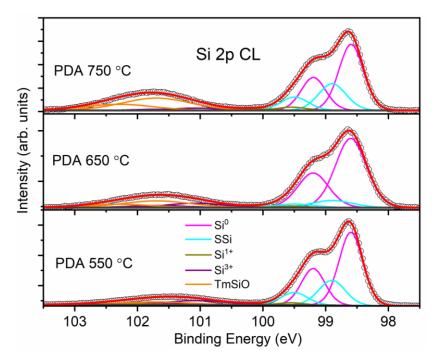

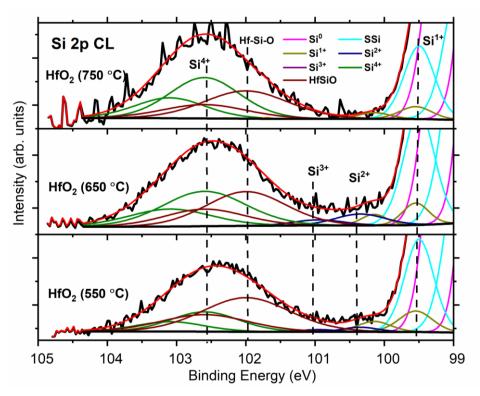

| Figure 3.7: Fitted Si 2p XPS CL spectra for $Tm_2O_3/Si$ samples annealed at three different temperatures: $550^{\circ}C$ , $650^{\circ}C$ and $750^{\circ}C$ . Both spin-orbit $2p_{3/2}$ and $2p_{1/2}$ components are included in each spectrum. The sub-peak towards higher binding energy refers to the interfacial layer; it is apparent that the area of the sub-peak is enhanced for higher PDA temperatures. SSi refers to the effect of surface charges in the atomic layers closer to the surface86 |

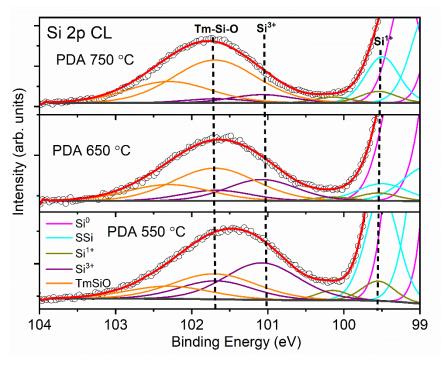

| Figure 3.8: A close-up image of the sub-peak of Si 2p XPS CL for annealed $Tm_2O_3/Si$ samples. Both spin-orbit doublet 3/2 and 1/2 components are included for each fitted core level referring to $Tm-Si-O$ , $Si^{3+}$ and $Si^{1+}$ .                                                                                                                                                                                                                                                                      |

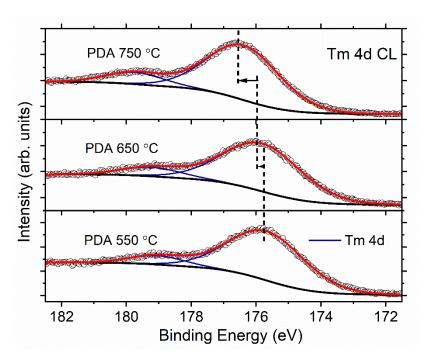

| Figure 3.9: Tm 4d XPS CL spectra for $Tm_2O_3/Si$ samples annealed at different PDA temperatures (550 °C – 750 °C)88                                                                                                                                                                                                                                                                                                                                                                                           |

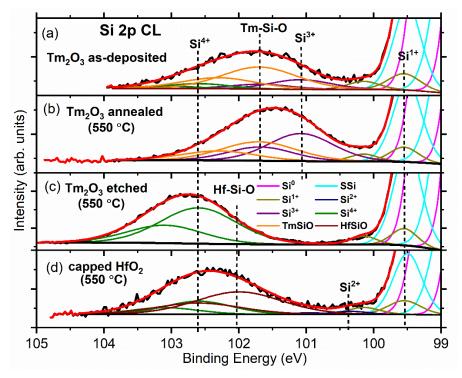

| Figure 3.10: The comparison spectra of Si 2p XPS core levels for (a) as-deposited $Tm_2O_3$ , (b) $Tm_2O_3$ annealed at a temperature of 550 °C, (c) $Tm_2O_3$ on top etched after PDA of 550 °C, and (d) $HfO_2$ -capped sample with IL formed at 550 °C89                                                                                                                                                                                                                                                    |

| Figure 3.11: Si 2p XPS core level for HfO <sub>2</sub> -capped samples with ILs formed at varying PDA temperatures90                                                                                                                                                                                                                                                                                                                                                                                           |

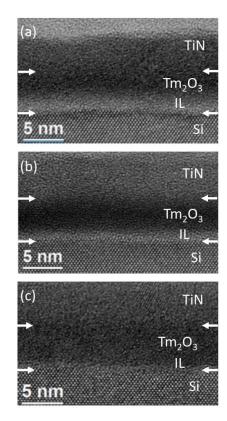

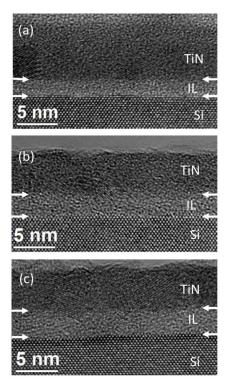

| Figure 3.12: HRTEM images of (a) 3 nm $Tm_2O_3/0.9$ nm $TmSiO$ IL formed at 550 °C, (b) 3 nm $Tm_2O_3/1.3$ nm $TmSiO$ IL formed at 650 °C and (c) 3 nm $Tm_2O_3/2.1$ nm $TmSiO$ IL formed at 750 °C PDA. The overall thickness of the stack increases with annealing temperature (courtesy of Dr Schamm-Chardon, CEMES-CNRS, Toulouse, France.) 93                                                                                                                                                             |

| Figure 3.13: HRTEM image of $Tm_2O_3/TmSiO/Si$ stacks when top $Tm_2O_3$ layer is etched off, revealing only IL $TmSiO$ : (a) 0.9 nm $TmSiO$ IL formed at 550 °C; (b) 1.3 nm $TmSiO$ IL formed at 650 °C; and (c) 2.1 nm $TmSiO$ IL formed at 750 °C. The layers were capped with $TiN$ for protection (courtesy of $Dr$ Schamm-Chardon, CEMES-CNRS, $Toulouse$ $France$ .)94                                                                                                                                  |

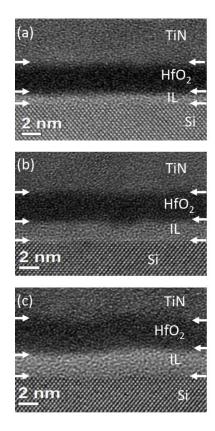

| Figure 3.14: HRTEM images of 3 nm HfO <sub>2</sub> /TmSiO IL/Si stacks, where IL is formed by PDA temperature of (a) 550 °C, (b) 650 °C, and (c) 750 °C. (courtesy of Dr Schamm-Chardon, CEMES-CNRS, Toulouse France.)95                                                                                                                                                                                                                                                                                       |

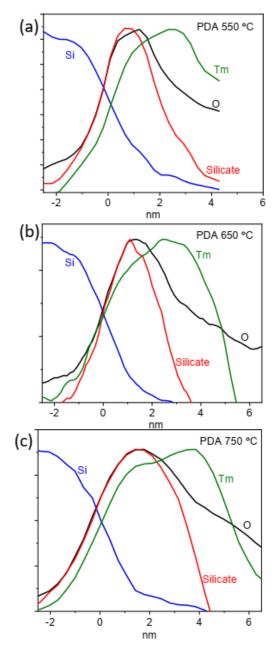

| different PDA temperatures: (a) 550 °C, (b) 650 °C, and (c) 750 °C. (courtesy of Dr Schamm-Chardon, CEMES-CNRS, Toulouse France.)                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

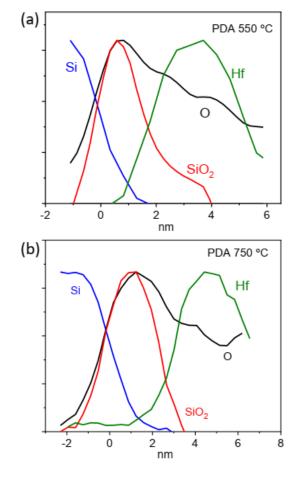

| Figure 3.16: The EELS profiles of HfO <sub>2</sub> /TmSiO/Si stacks, with TmSiO formed at different PDA temperatures: (a) 550 °C, and (b) 750 °C. (courtesy of Dr Schamm-Chardon, CEMES-CNRS, Toulouse France.)                                                 |

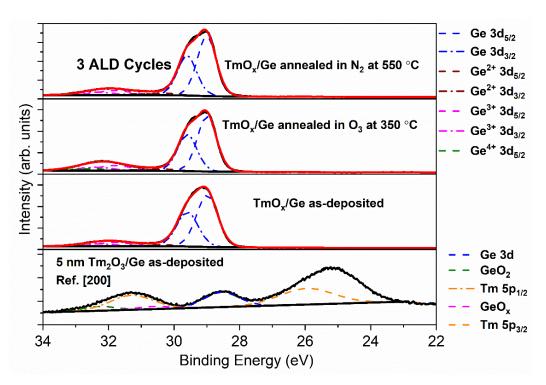

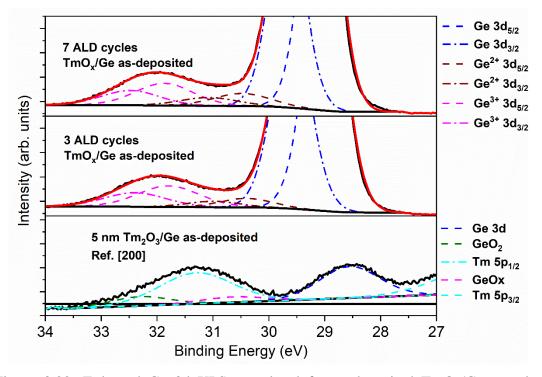

| Figure 3.17: Ge 3d XPS core level for 3 ALD cycles of $Tm_2O_3$ on Ge: for as-deposited and annealed $Tm_2O_3$ /Ge samples compared to previous work in Ref. [200]. 10:                                                                                         |

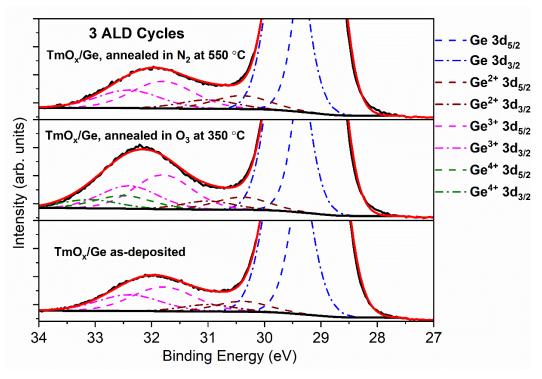

| Figure 3.18: Enlarged area of high BE side of Ge 3d XPS CL peak shown in Fig. 3.16. The results relate to 3 ALD cycles of $Tm_2O_3$ deposited on Ge: for as-deposited and annealed samples10:                                                                   |

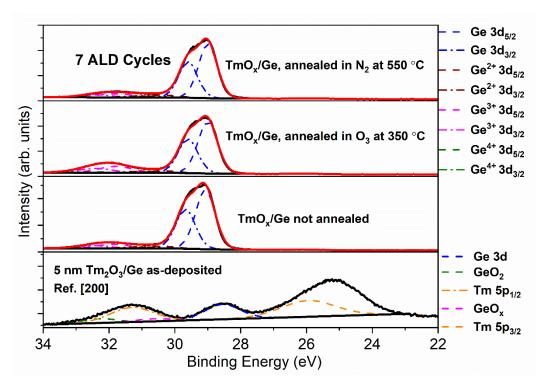

| Figure 3.19: Ge 3d XPS core level for 7 ALD cycles of $Tm_2O_3$ on Ge for as-deposited and annealed samples compared to previous work [200]10.                                                                                                                  |

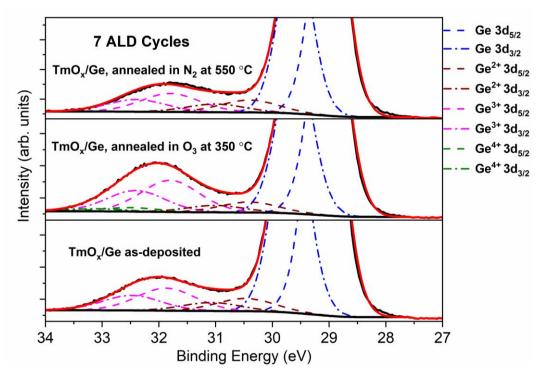

| Figure 3.20: Enlarged high BE side of the main Ge 3d XPS core level for 7 ALD cycles of $Tm_2O_3$ on Ge for as-deposited and annealed $TmOx/Ge$ samples103                                                                                                      |

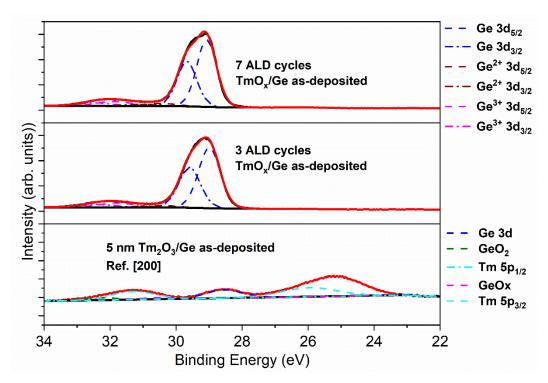

| Figure 3.21: Ge 3d XPS CL fitted spectra for 3 and 7 ALD cycles TmO <sub>x</sub> /Ge asdeposited samples compared to the similar spectrum from previous work [200]104                                                                                           |

| Figure 3.22: Enlarged Ge 3d XPS core level for as-deposited $TmO_x/Ge$ samples formed using 3 and 7 ALD cycles and compared to the similar spectrum from previous work [200]. Note that there is no $Tm 5p_{3/2}$ component for $TmO_x/Ge$ samples104           |

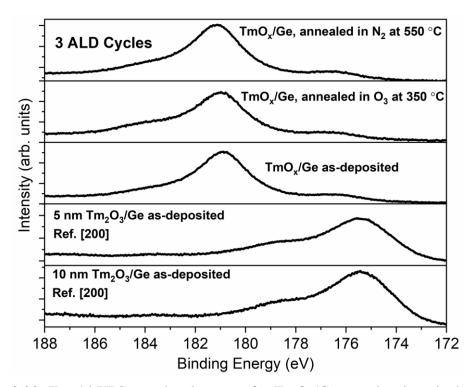

| Figure 3.23: Tm 4d XPS core level spectra for TmO <sub>x</sub> /Ge samples deposited using 3 ALD cycles, as-deposited and annealed samples compared to similar spectra from previous work of 5 and 10 nm Tm <sub>2</sub> O <sub>3</sub> /Ge [200]10 <sup></sup> |

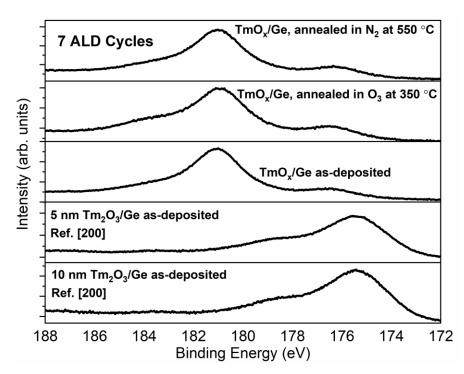

| Figure 3.24: Tm 4d XPS core level spectra for TmO <sub>x</sub> /Ge deposited using 7 ALD cycles for as-deposited and annealed samples compared to similar spectra from previous work of 5 and 10 nm Tm <sub>2</sub> O <sub>3</sub> /Ge [200]108                 |

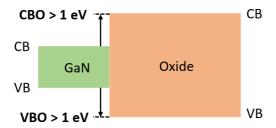

| Figure 4.1: The requirement of large band offsets of over 1 eV at oxide/GaN interface11                                                                                                                                                                         |

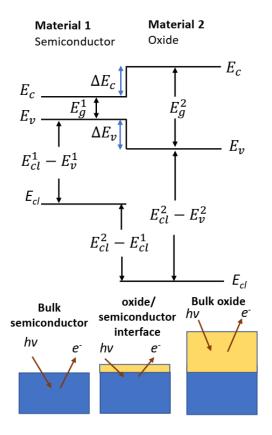

| Figure 4.2: A schematic energy band diagram illustrating the basic principle of XPS band offset measurements based on Kraut's method [201], [231]11                                                                                                             |

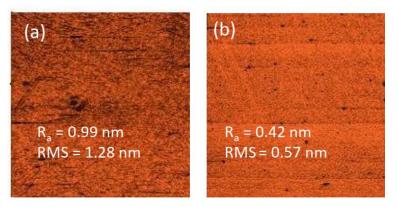

| Figure 4.3: Atomic force microscopy (AFM) images of (a) GaN and (b) 10 nm Ta $_2$ O $_5$ with the scanned area of 10 $\mu$ m $	imes$ 10 $\mu$ m.                                                                                                                |

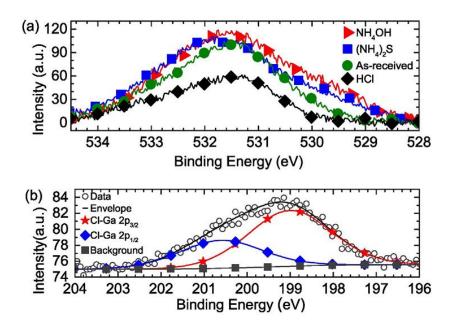

| Figure 4.4: (a) Background subtracted O 1s core level after different cleaning treatments (NH <sub>4</sub> OH, (NH <sub>4</sub> ) <sub>2</sub> S, and HCl) of GaN surface as compared to as-                                                                    |

|                       | level of the GaN surface after HCl cleaning treatment                                                                                                                                                                                                                                                                                                              | 119       |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

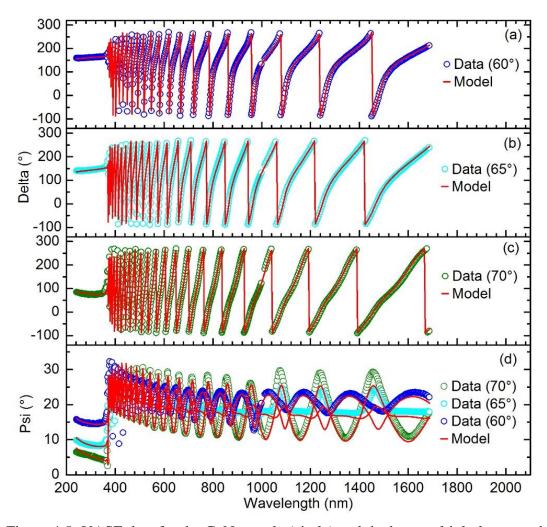

| fit (fu               | S: VASE data for the GaN sample (circle) and the best multiple-layer modull line) in the wavelength range of 240–1700 nm: $\Delta$ for incident angles ((b) 65°, (c) 70°, and (d) Ψ for three incident angles (60–75°).                                                                                                                                            |           |

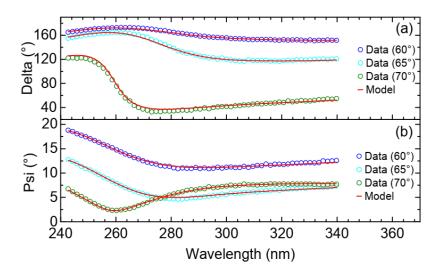

| (full  <br>for th     | i: VASE data for the bulk $Ta_2O_5/GaN$ sample (circle) and the best model fine) in the transparent wavelength region (240–340 nm): (a) $\Delta$ and (b) where incident angles (60 – 75°). The thickness of $Ta_2O_5$ is estimated to be $\pm$ 0.2 eV.                                                                                                             | μ         |

| _                     | ?: Photon energy dependence of parametric dielectric function, $\epsilon_1$ and $\epsilon_2$ a) as-received GaN substrate, and (b) 10 nm (nominal) Ta <sub>2</sub> O <sub>5</sub> /GaN2                                                                                                                                                                            |           |

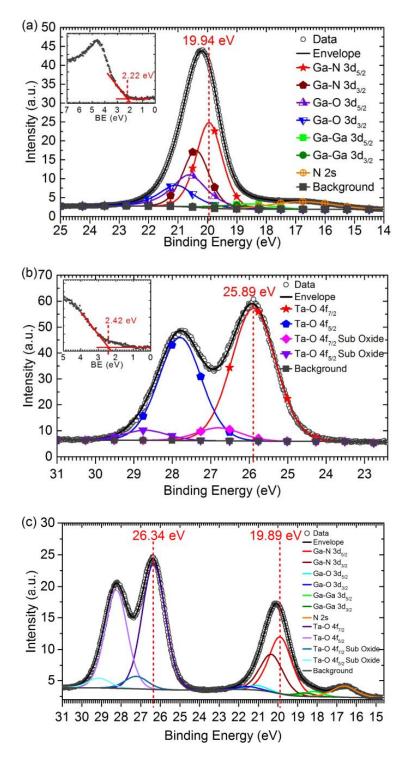

| Ta₂O<br>show<br>estin | E: The XPS spectra of (a) Ga 3d CL for GaN substrate; (b) Ta 4f CL for bulk 5/GaN sample; (c) Ga 3d and Ta 4f CLs for interfacial Ta <sub>2</sub> O <sub>5</sub> /GaN sample ving the difference between the CLs. The insets in (a)–(b) show the VBM nation from valence band leading edge linear fitting. The envelope refer e fitted curve to experimental data. |           |

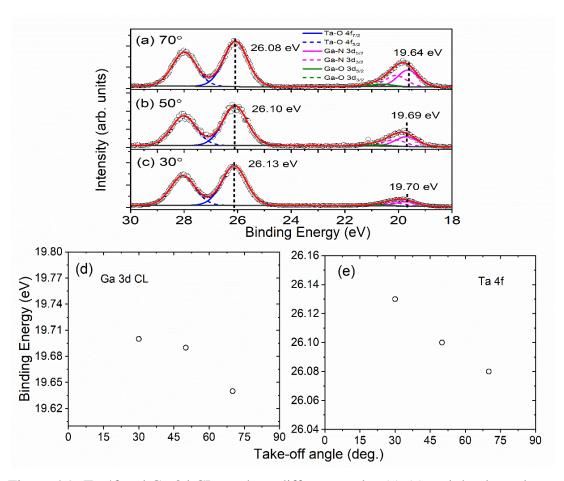

| of m                  | easured binding energies on take-off angles (a)-(c) and the dependen (a) (d) and (e) for 3 nm (5/GaN                                                                                                                                                                                                                                                               |           |

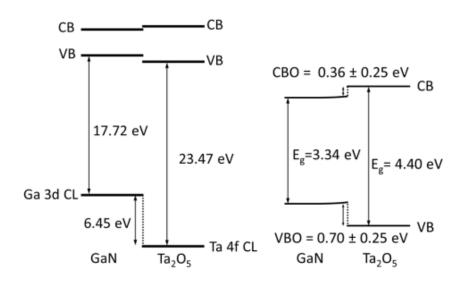

| Ta₂O                  | .0: Band diagrams of experimentally derived band alignment for the 5/GaN interface: (left) Kraut's method for VBO measurement, and (right derived using band gap energies measured by VASE.                                                                                                                                                                        | :)<br>127 |

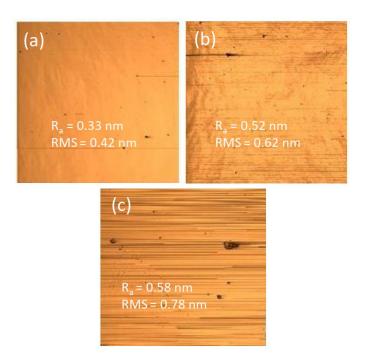

| 100 /                 | .1: AFM images of bulk samples (a) ZrO <sub>2</sub> with a scanned area of 100 $\mu$ m $\mu$ m, (b) Al <sub>2</sub> O <sub>3</sub> with a scanned area of 90 $\mu$ m $\times$ 90 $\mu$ m and (c) MgO with a ned area of 100 $\mu$ m $\times$ 100 $\mu$ m.                                                                                                          |           |

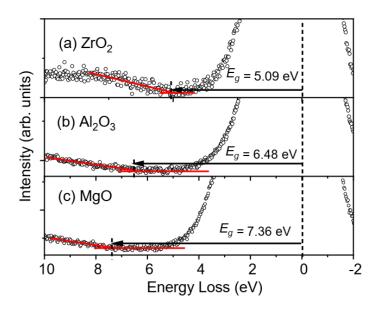

|                       | .2: The XPS O 1s energy loss spectra for (a) $ZrO_2$ , (b) $Al_2O_3$ and (c) $MgO_2$ cting extraction of the band gap.                                                                                                                                                                                                                                             | 139       |

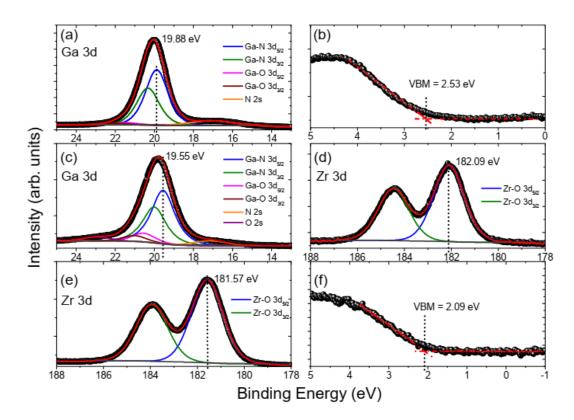

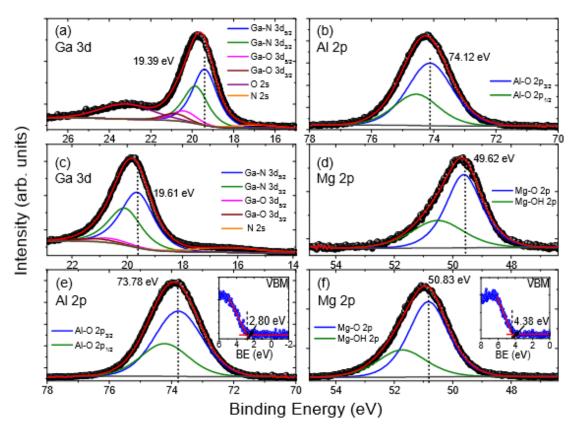

| GaN<br>(e) th         | 3: The XPS spectra of (a) Ga 3d CL and (b) valence band spectrum for 5 on sapphire; (c) Ga 3d and (d) Zr 3d CLs for interfacial ZrO <sub>2</sub> /GaN sample are Zr 3d CL and (f) valence band spectrum showing VBM extraction for be a                                                                                                                            | ;         |

| Ga 3<br>bulk          | .4: The XPS spectra for (a) Ga 3d, (b) Al 2p CLs for interfacial Al <sub>2</sub> O <sub>3</sub> /GaN; d and (d) Mg 2p CLs for interfacial MgO/GaN; (e) Al 2p and Mg 2p CLs fo Al <sub>2</sub> O <sub>3</sub> and MgO films. The insets in both (e) and (f) refer to VB spectra and ction of VBM for both bulk oxide films.                                         | r         |

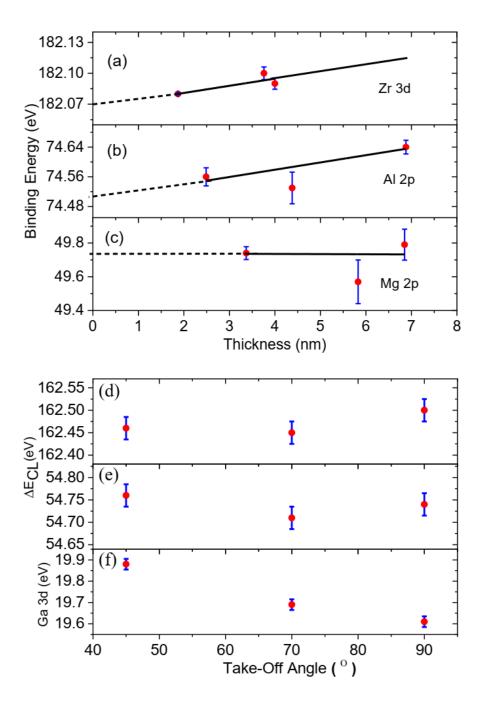

| range                 | 5: The binding energy of (a) Zr 3d, (b) Al 2p, (c) Mg 2p measured for a e of thin (up to 7 nm) oxide/GaN samples. A small differential charging at can be seen in (b) and (c) for Al <sub>2</sub> O <sub>3</sub> and MgO respectively. The CL                                                                                                                      |           |

| thin (3 nm nominal) $ZrO_2/GaN$ and $Al_2O_3/GaN$ samples as a function of XPS take-off angle. (f) The variation of Ga 3d CL for thin (3 nm nominal) MgO/Gal sample vs XPS take-off angle.                                                                                                                                                                                                                                                                                                                          |            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

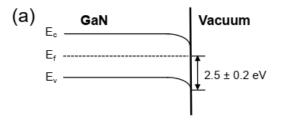

| Figure 4.16: The schematics of XPS experimentally derived band alignments: (a) a GaN surface; (b) for $ZrO_2/GaN$ , $Al_2O_3/GaN$ and $MgO/GaN$ fabricated in this work by sputtering. (The diagrams are not to scale.)                                                                                                                                                                                                                                                                                             | t<br>148   |

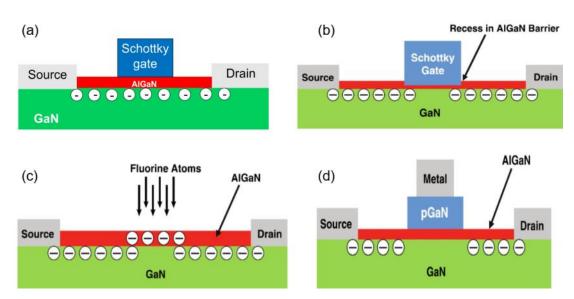

| Figure 5.1: The structure of (a) D-mode HEMT – where the channel is formed with V on the gate (normally-on) and there need to be large negative voltage on t gate to turn the transistor off, (b) recessed gate E-mode HEMT – is achieved through thinning the AlGaN barrier layer by etching, (c) implanted gate E-mode HEMT – the 2DEG is removed by implanting fluorine atoms into the AlGaN barrier where the F atoms cause a trapped negative charge effect within that area, and (d) p-GaN E-mode HEMT [287]. | the<br>ode |

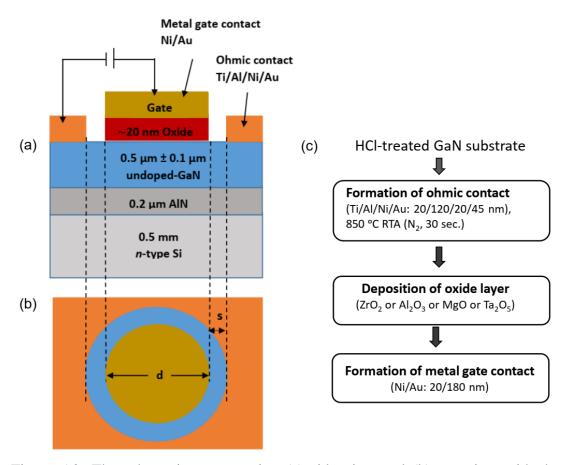

| Figure 5.2: The schematic cross-section (a) side view and (b) top view with the diameter of metal gate, d and the spacing between metal gate and ohmic contacts, s; and (c) fabrication flow for the GaN-based MIS-capacitor with ox layers ( $ZrO_2$ or $Al_2O_3$ or $MgO$ or $Ta_2O_5$ ).                                                                                                                                                                                                                         | ide<br>160 |

| Figure 5.3: The VASE model used to extract thickness of RF-sputtered oxide layers for (a) ZrO <sub>2</sub> /Si; (b) Al <sub>2</sub> O <sub>3</sub> /Si; (c) MgO/Si; and (d) Ta <sub>2</sub> O <sub>5</sub> /Si reference samples.                                                                                                                                                                                                                                                                                   |            |

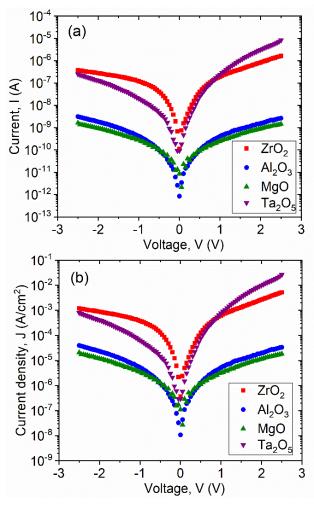

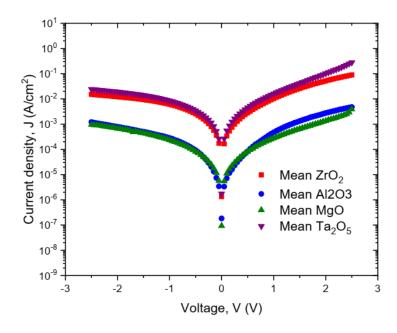

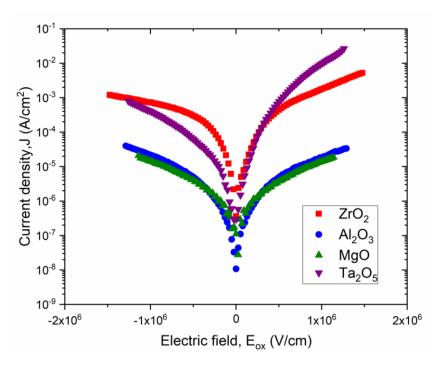

| Figure 5.4: (a) The $IV$ and (b) $JV$ plots for MIS-capacitors on GaN with four different gate dielectrics ( $ZrO_2$ , $Al_2O_3$ , MgO, and $Ta_2O_5$ ) deposited by RF sputtering technique.                                                                                                                                                                                                                                                                                                                       | nt<br>164  |

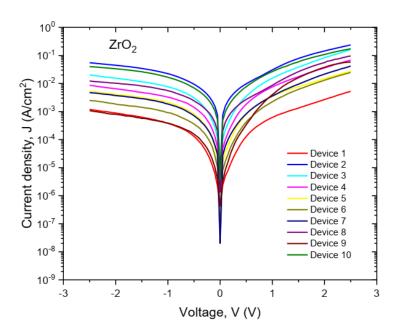

| Figure 5.5: JV plots for the GaN-based MIS-capacitors with ZrO <sub>2</sub> gate dielectrics.                                                                                                                                                                                                                                                                                                                                                                                                                       | 165        |

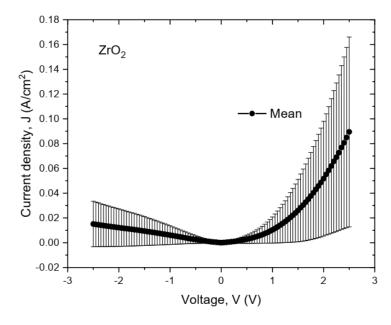

| Figure 5.6: JV plots showing the mean and standard deviation for the GaN-based MIS-capacitors with ZrO <sub>2</sub> gate dielectrics.                                                                                                                                                                                                                                                                                                                                                                               | 165        |

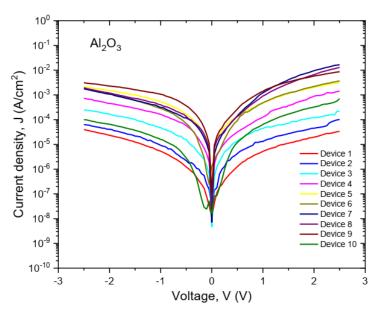

| Figure 5.7: JV plots for the GaN-based MIS-capacitors with Al <sub>2</sub> O <sub>3</sub> gate dielectrics.                                                                                                                                                                                                                                                                                                                                                                                                         | 166        |

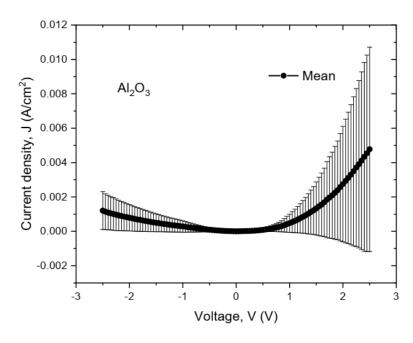

| Figure 5.8: $JV$ plots showing the mean and standard deviation for the GaN-based MIS-capacitors with $Al_2O_3$ gate dielectrics.                                                                                                                                                                                                                                                                                                                                                                                    | 166        |

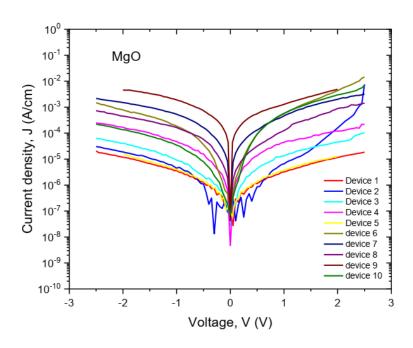

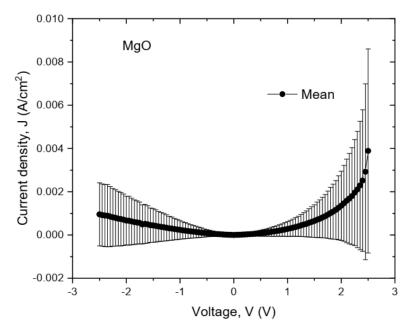

| Figure 5.9: JV plots for the GaN-based MIS-capacitors with MgO gate dielectrics.                                                                                                                                                                                                                                                                                                                                                                                                                                    | 167        |

| Figure 5.10: JV plots showing the mean and standard deviation for the GaN-based MIS-capacitors with MgO gate dielectrics1                                                                                                                                                                                                                                                                                                                                                                                           | d<br>167   |

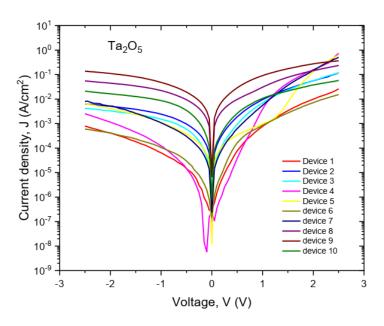

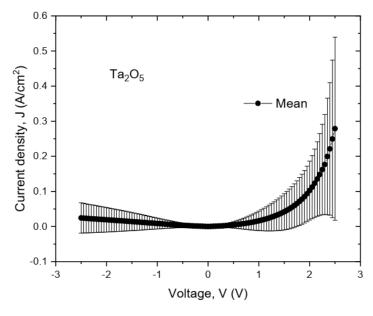

| Figure 5.11: <i>JV</i> plots for the GaN-based MIS-capacitors with Ta <sub>2</sub> O <sub>5</sub> gate dielectrics                                                                                                                                                                                                                                                                                                                                                                                                  | s.<br>168  |

| Figure 5.12: JV plots showing the mean and standard deviation for the GaN-based MIS-capacitors with Ta <sub>2</sub> O <sub>5</sub> gate dielectrics.                                                                                                                                                                                                                                                                                                                                                                | d<br>168   |

| based MIS-capacitors with different dielectrics (ZrO <sub>2</sub> , Al <sub>2</sub> O <sub>3</sub> , MgO, and Ta <sub>2</sub> O <sub>5</sub> ).                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.14: $JE$ plots for MIS-capacitors on GaN with four different gate dielectrics ( $ZrO_2$ , $Al_2O_3$ , MgO, and $Ta_2O_5$ ) at both negative and positive biases measured at room temperature measurement171 |

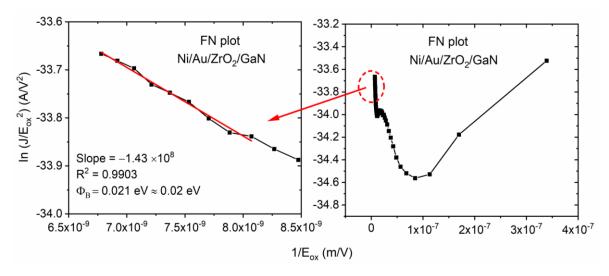

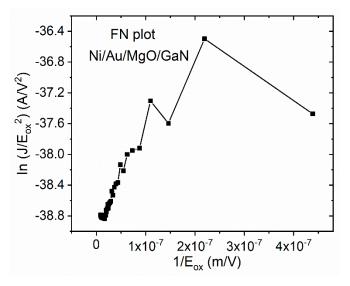

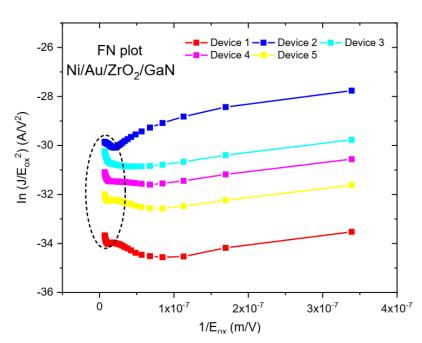

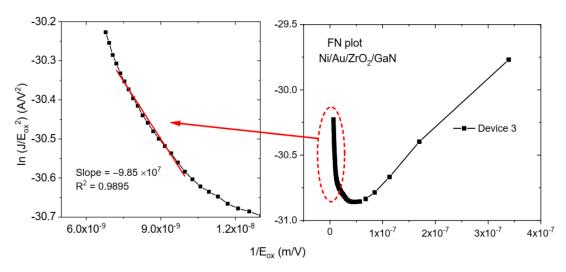

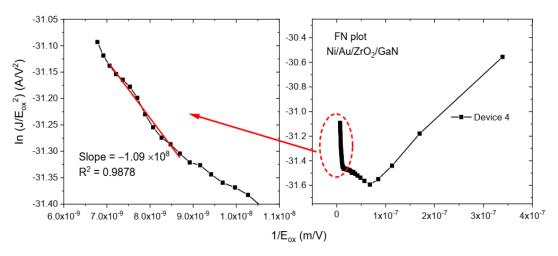

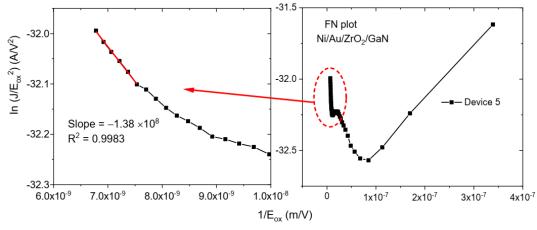

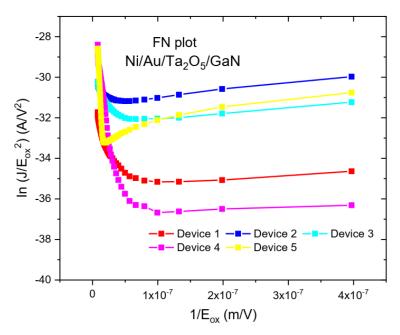

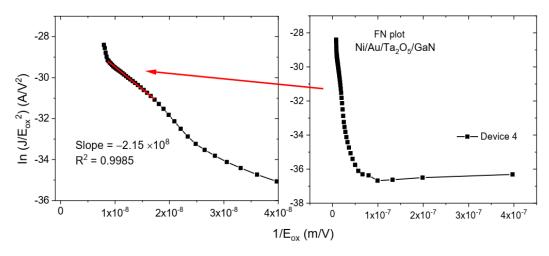

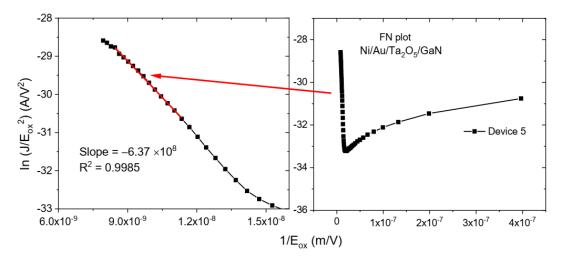

| Figure 5.15: FN plots for GaN MIS-capacitor with ZrO <sub>2</sub> as a dielectric layer172                                                                                                                           |

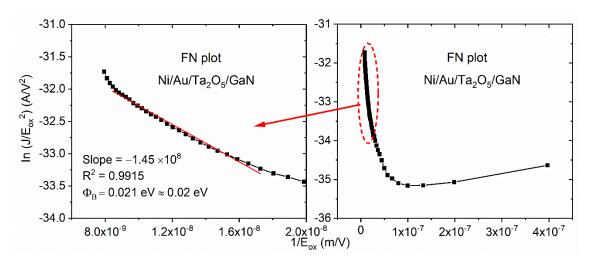

| Figure 5.16: FN plots for GaN MIS-capacitor with Ta <sub>2</sub> O <sub>5</sub> as a dielectric layer173                                                                                                             |

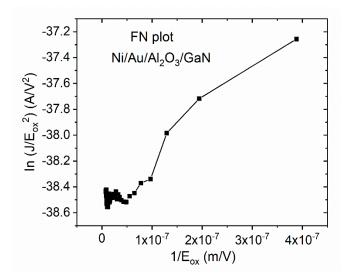

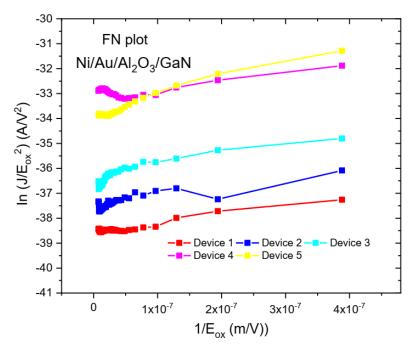

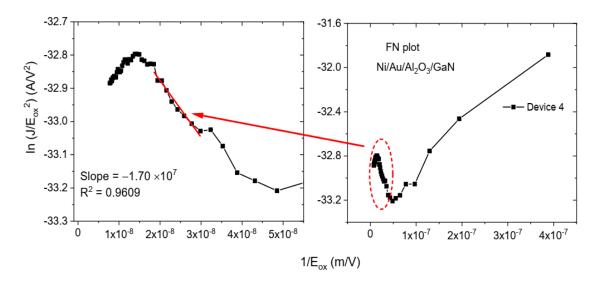

| Figure 5.17: FN plot for GaN MIS-capacitor with $Al_2O_3$ as a dielectric layer173                                                                                                                                   |

| Figure 5.18: FN plot for GaN MOS-capacitor with MgO as a dielectric layer173                                                                                                                                         |

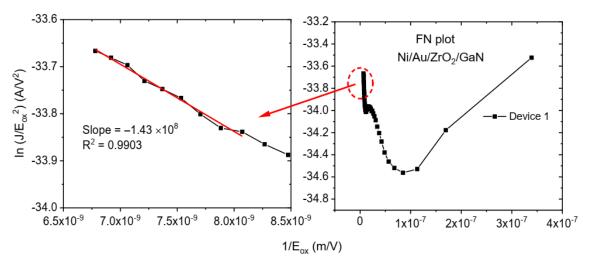

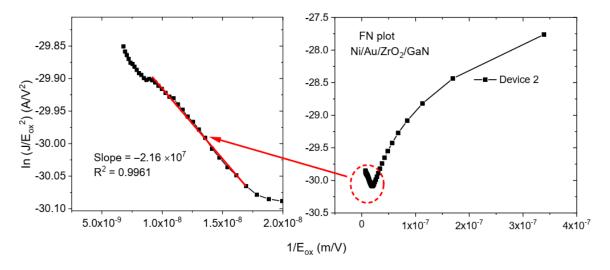

| Figure 5.19: FN plots for the GaN-based MIS-capacitors with $ZrO_2$ as a dielectric layer174                                                                                                                         |

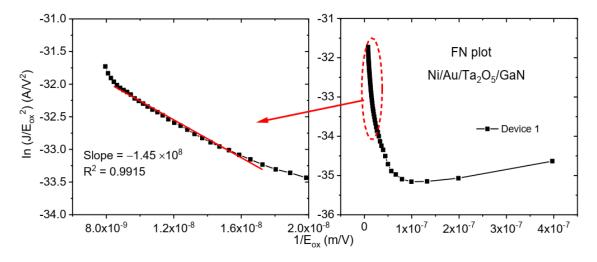

| Figure 5.20: FN plots for the GaN-based MIS-capacitor with $ZrO_2$ as a dielectric layer (Device 1)175                                                                                                               |

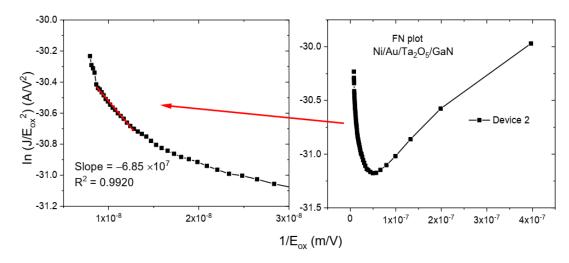

| Figure 5.21: FN plots for the GaN-based MIS-capacitor with ZrO <sub>2</sub> as a dielectric layer (Device 2)175                                                                                                      |

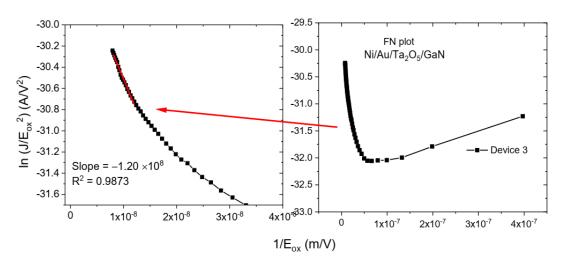

| Figure 5.22: FN plots for the GaN-based MIS-capacitor with ZrO <sub>2</sub> as a dielectric layer (Device 3)176                                                                                                      |

| Figure 5.23: FN plots for the GaN-based MIS-capacitor with ZrO <sub>2</sub> as a dielectric layer (Device 4)176                                                                                                      |

| Figure 5.24: FN plots for the GaN-based MIS-capacitor with ZrO <sub>2</sub> as a dielectric layer (Device 5)176                                                                                                      |

| Figure 5.25: FN plots for the GaN-based MIS-capacitors with $Al_2O_3$ as a dielectric layer177                                                                                                                       |

| Figure 5.26: FN plots for the GaN-based MIS-capacitor with $Al_2O_3$ as a dielectric layer (Device 4)178                                                                                                             |

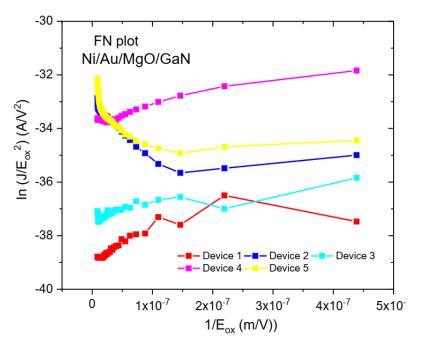

| Figure 5.27: FN plots for the GaN-based MIS-capacitors with MgO as a dielectric layer179                                                                                                                             |

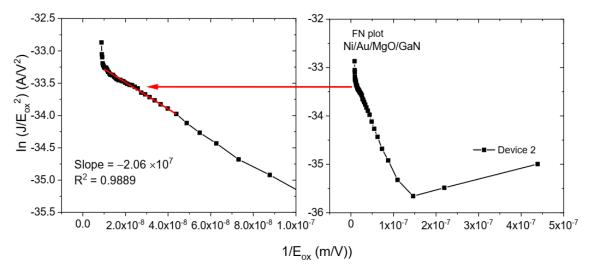

| Figure 5.28: FN plots for the GaN-based MIS-capacitor with MgO as a dielectric layer (Device 2)179                                                                                                                   |

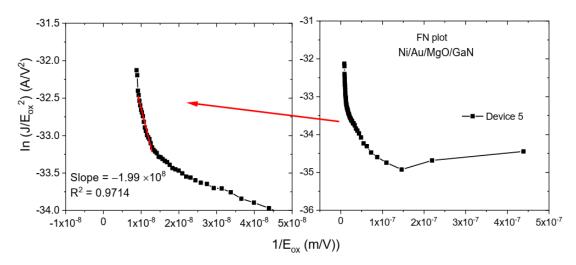

| Figure 5.29: FN plots for the GaN-based MIS-capacitor with MgO as a dielectric layer (Device 5)180                                                                                                                   |

| Figure 5.30: FN plots for the GaN-based MIS-capacitors with $Ta_2O_5$ as a dielectric layer.                                                                              | 181         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Figure 5.31: FN plots for the GaN-based MIS-capacitor with $Ta_2O_5$ as a dielectric layer (Device 1).                                                                    | 181         |

| Figure 5.32: FN plots for the GaN-based MIS-capacitor with $Ta_2O_5$ as a dielectric layer (Device 2).                                                                    | 182         |

| Figure 5.33: FN plots for the GaN-based MIS-capacitor with $Ta_2O_5$ as a dielectric layer (Device 3).                                                                    | 182         |

| Figure 5.34: FN plots for the GaN-based MIS-capacitor with $Ta_2O_5$ as a dielectric layer (Device 4).                                                                    | 182         |

| Figure 5.35: FN plots for the GaN-based MIS-capacitor with $Ta_2O_5$ as a dielectric layer (Device 5).                                                                    | 183         |

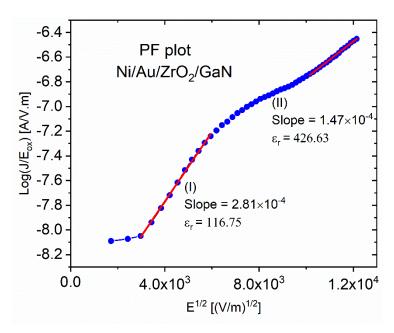

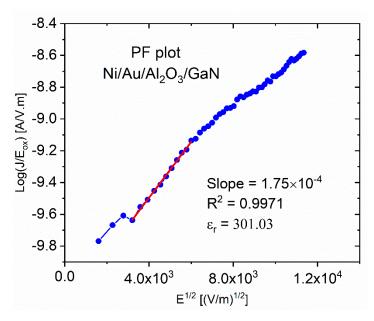

| Figure 5.36: PF plot for GaN MIS-capacitor with ZrO <sub>2</sub> as a dielectric layer                                                                                    | 185         |

| Figure 5.37: PF plot for GaN MIS-capacitor with Al <sub>2</sub> O <sub>3</sub> as a dielectric layer                                                                      | 185         |

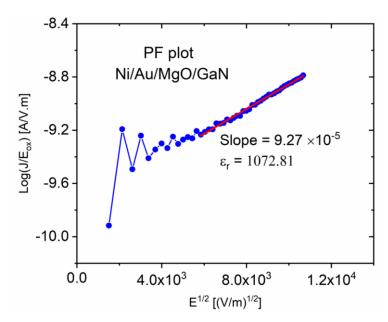

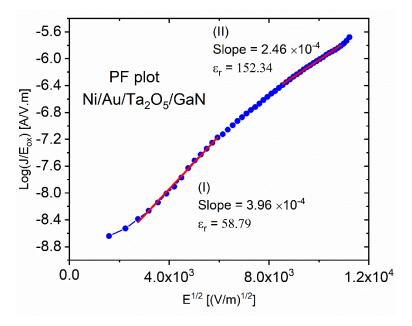

| Figure 5.38: PF plot for GaN MIS-capacitor with MgO as a dielectric layer.                                                                                                | 186         |

| Figure 5.39: PF plot for GaN MIS-capacitor with Ta <sub>2</sub> O <sub>5</sub> as a dielectric layer                                                                      | 186         |

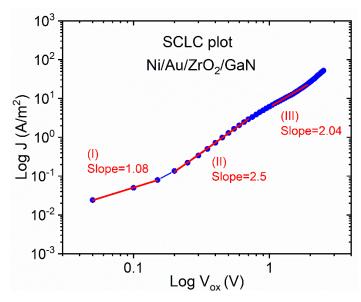

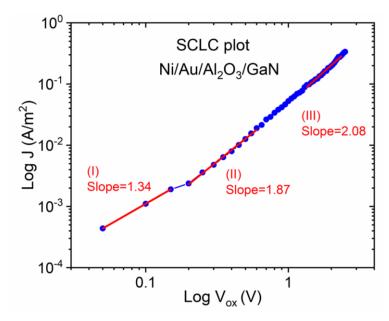

| Figure 5.40: SCLC plot for GaN MIS-capacitor with ZrO <sub>2</sub> as a dielectric layer                                                                                  | 189         |

| Figure 5.41: SCLC plot for GaN MIS-capacitor with Al <sub>2</sub> O <sub>3</sub> as a dielectric layer                                                                    | 189         |

| Figure 5.42: SCLC plot for GaN MIS-capacitor with MgO as a dielectric layer                                                                                               | 190         |

| Figure 5.43: SCLC plot for GaN MIS-capacitor with $Ta_2O_5$ as a dielectric layer                                                                                         | 190         |

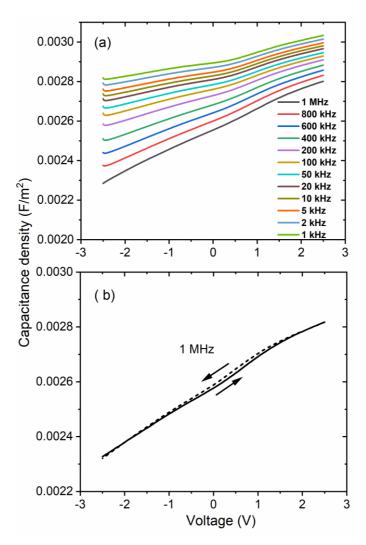

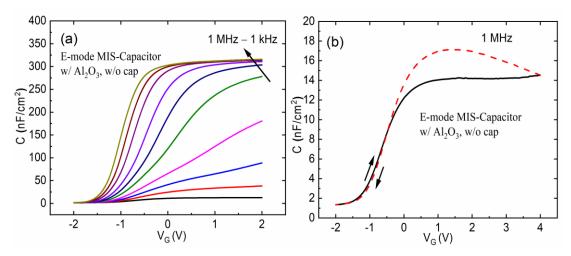

| Figure 5.44: The $CV$ plot: (a) frequency dependent and (b) hysteresis at a frequency of 1 MHz for GaN MIS-capacitor with $Al_2O_3$ as a dielectric layer                 | -           |

| Figure 5.45: The $CV$ plots: (a) frequency dependent and (b) hysteresis at frequence MHz for GaN MIS-capacitor with $ZrO_2$ as a dielectric layer.                        | •           |

| Figure 5.46: The <i>CV</i> plots: (a) frequency dependent and (b) hysteresis at frequence MHz for GaN MIS-capacitor with MgO as a dielectric layer.                       | cy 1<br>194 |

| Figure 5.47: The $CV$ plots: (a) frequency dependent and (b) hysteresis at frequence MHz for GaN MOS-capacitor with Ta <sub>2</sub> O <sub>5</sub> as a dielectric layer. | cy 1<br>195 |

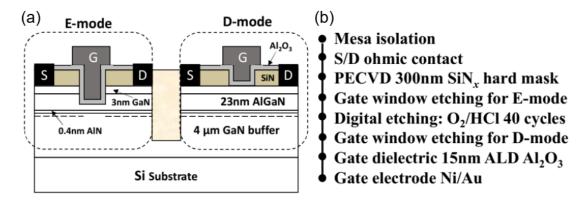

| Figure 5.48 (a) The schematic structure and (b) fabrication steps of E- and D-mod MIS-HEMTs                                                                               | le<br>197   |

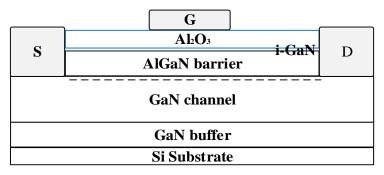

| Figure 5.49: Schematic cross-sectional view of the fabricated MIS-HEMT without GaN cap layer.                                                                             | 199         |

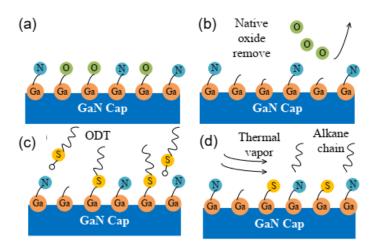

| a           | e 5.50: Schematic of the ODT treatment procedure: (a) the non-treated GaN cap; (b) the HCl treatment for removal of the native oxide; (c) the formation dense ODT SAM on the HCl-cleaned GaN surface; (d) the in vacuo thermal vapour removal of the carbon chain, leaving sulphur atoms behind [310] 2 |            |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

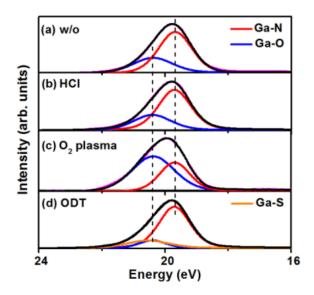

| E           | e 5.51: The XPS Ga 3d CL spectra for GaN samples: (a) A-without treatment; 3-with the HCl; (c) C-with the $O_2$ plasma; (d) D-with the ODT for 24 hours surface treatments [310].                                                                                                                       | (b)<br>202 |

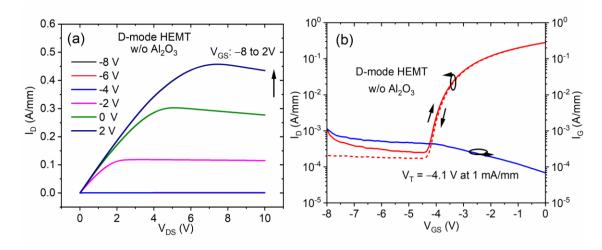

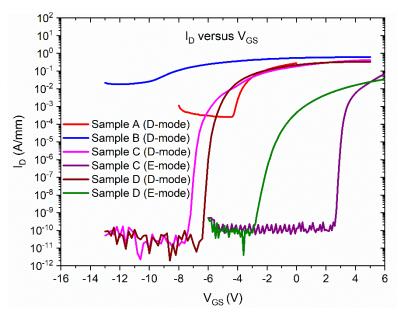

| -           | e 5.52: (a) Output characteristics and (b) transfer characteristics of D-mode HEMT for sample A. Device dimension: $L_{GS}/W_{GS}/L_{G}/L_{GD} = 5/50/3/10 \mu m.$                                                                                                                                      | 203        |

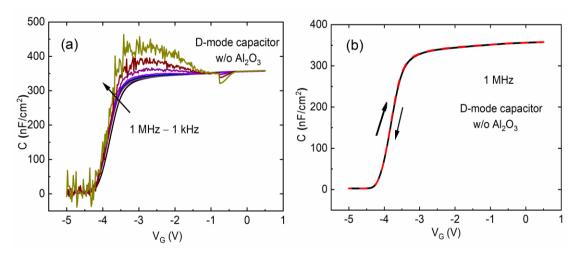

| _           | e 5.53: <i>CV</i> curves for D-mode capacitor for sample A: (a) frequency depende b) hysteresis at 1 MHz                                                                                                                                                                                                | nt,<br>204 |

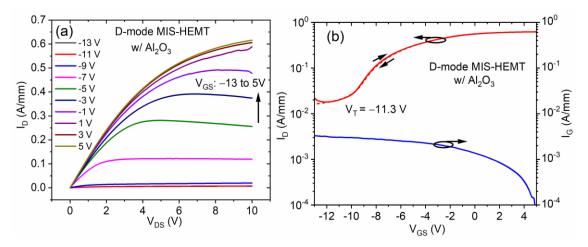

| _           | e 5.54: (a) Output characteristics and (b) transfer characteristics of D-mode MIS-HEMT for sample B. Device dimension: $L_{GS}/W_{GS}/L_{G}/L_{GD} = 5/100/3/5 \mu m$ .                                                                                                                                 | 205        |

| -           | e 5.55: (a) Output characteristics and (b) transfer characteristics of D-mode MIS-HEMT for sample C. Device dimension: $L_{GS}/W_{GS}/L_{G}/L_{GD} = 5/100/3/5 \mu m$ .                                                                                                                                 | 206        |

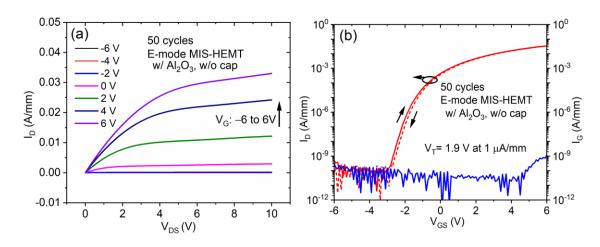

|             | e 5.56: (a) Output characteristics and (b) transfer characteristics of E-mode MIS-HEMT for sample C. Device dimension: $L_{GS}/W_{GS}/L_{G}/L_{GD} = 5/50/3/5$ μm. 2                                                                                                                                    | 206        |

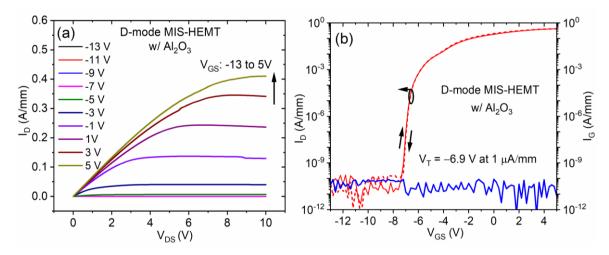

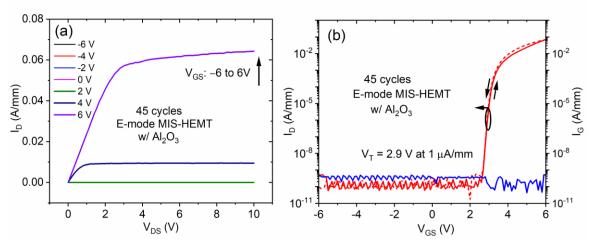

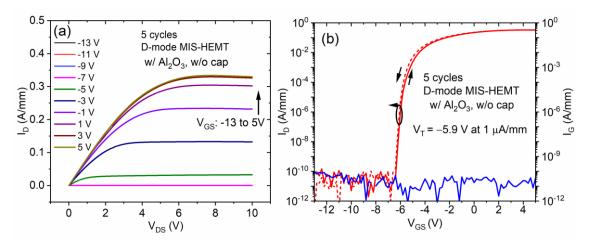

| _           | e 5.57: (a) Output characteristics and (b) transfer characteristics of D-mode MIS-HEMT for sample D. Device dimension: $L_{GS}/W_{GS}/L_{G}/L_{GD} = 5/100/3/5$ μm.                                                                                                                                     | 207        |

| _           | e 5.58: (a) Output characteristics and (b) transfer characteristics of E-mode MIS-HEMT for sample D. Device dimension: $L_{GS}/W_{GS}/L_{G}/L_{GD} = 5/100/3/5$ μm.                                                                                                                                     | 208        |

| Figure<br>- | e 5.59: The comparison of sub-threshold graphs for all samples (A, B, C, and                                                                                                                                                                                                                            | D).<br>209 |

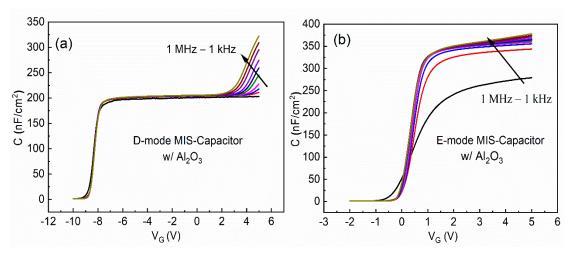

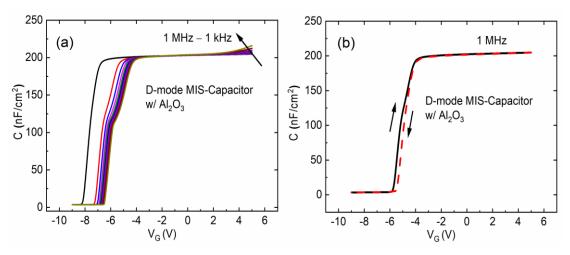

| _           | e 5.60: <i>CV</i> curves of MIS-capacitor for sample B (a) D-mode frequency dependent, (b) E-mode frequency dependent.                                                                                                                                                                                  | 211        |

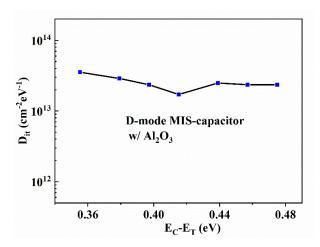

|             | e 5.61: Extracted $Dit$ from $CV$ curves for sample B (D-mode MIS-capacitor w $Al_2O_3$ as gate dielectric).                                                                                                                                                                                            | ith<br>212 |

| -           | e 5.62: <i>CV</i> curves of MIS-capacitor for sample C (a) D-mode frequency dependent, (b) D-mode hysteresis at 1 MHz.                                                                                                                                                                                  | 212        |

| _           | e 5.63: <i>CV</i> curves of MIS-capacitor for sample C (a) E-mode frequency dependent, (b) E-mode hysteresis at 1 MHz.                                                                                                                                                                                  | 212        |

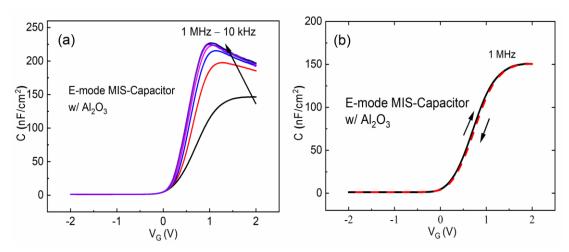

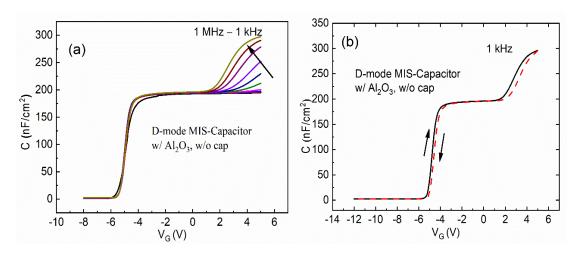

| Figure 5.64: CV curves MIS-capacitor for sample D (a) D-mode frequency dependent, (b) D-mode hysteresis at 1 MHz                                                                                                                                                                                                                          | 213          |

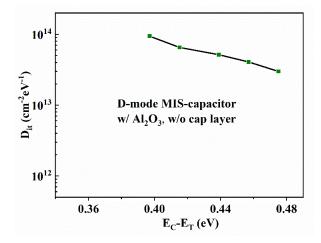

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Figure 5.65: Extracted $Dit$ from $CV$ curves for sample D (D-mode MIS-capacitor w $Al_2O_3$ as gate dielectric, without GaN cap layer).                                                                                                                                                                                                  | vith<br>213  |

| Figure 5.66: <i>CV</i> curves of MIS-capacitor for sample D (a) E-mode frequency dependent, (b) E-mode hysteresis at 1 MHz.                                                                                                                                                                                                               | 213          |

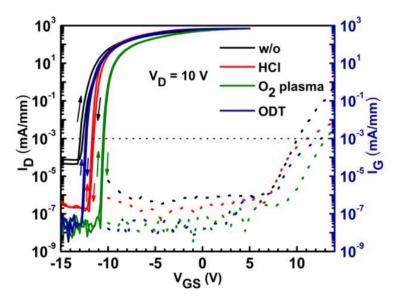

| Figure 5.67: Transfer characteristics curves of the MIS-HEMT devices at $V_{DS}$ of 10 [310].                                                                                                                                                                                                                                             | V<br>216     |

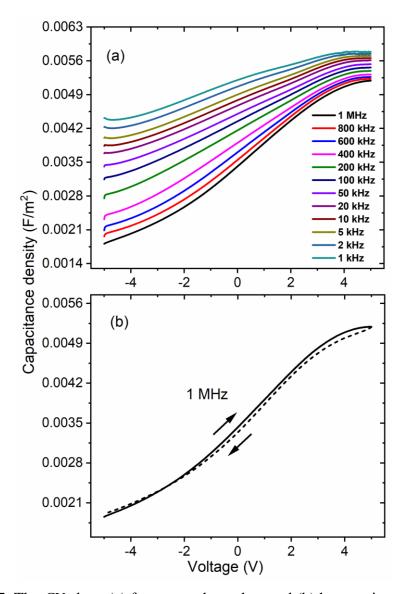

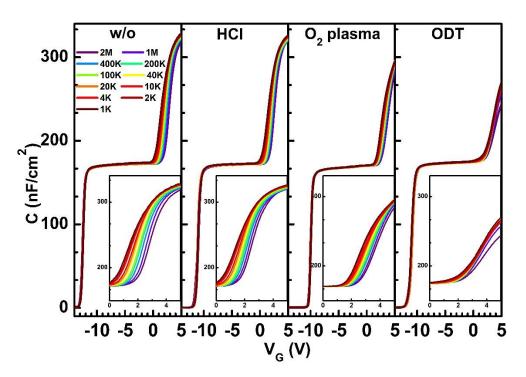

| Figure 5.68: Multi-frequency $CV$ characteristics of ALD-Al <sub>2</sub> O <sub>3</sub> /GaN/AlGaN/GaN M capacitor structures (without (sample E) and with the HCl (sample F), O <sub>2</sub> plast (sample G) and ODT (sample H) surface passivation treatments [310].                                                                   | sma          |

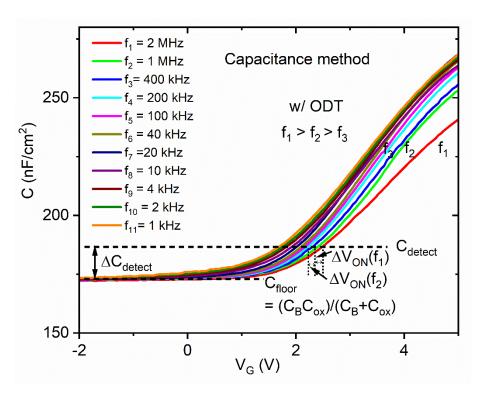

| Figure 5.69: Schematic showing the extraction of the gate voltage shift, $\Delta V_f$ , from the second $CV$ step for ALD-Al <sub>2</sub> O <sub>3</sub> /GaN/AlGaN/GaN MIS-capacitor structure with ODT surface treatment (sample H).                                                                                                    | n<br>218     |

| Figure 5.70: Distribution of $Dit$ vs $EC-ET$ at an ALD-Al <sub>2</sub> O <sub>3</sub> /GaN interface for for types of GaN surface treatments used in this work [310].                                                                                                                                                                    | ur<br>219    |

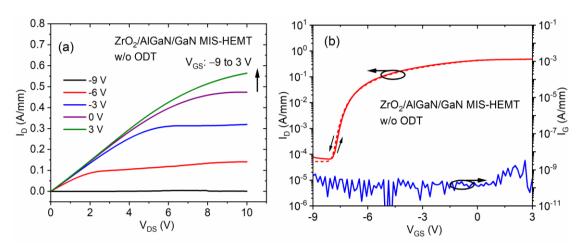

| Figure 5.71: (a) Output characteristics and (b) transfer characteristics of D-mode $ZrO_2$ -based MIS-HEMT without ODT surface treatment. Device dimension: $L_{GS}/W_{GS}/L_G/L_{GD} = 3/50/3/10 \ \mu m.$                                                                                                                               | 222          |

| Figure 5.72: (a) Output characteristics and (b) transfer characteristics of D-mode $ZrO_2$ -based MIS-HEMT with ODT GaN surface treatment. Device dimension: $L_{GS}/W_{GS}/L_G/L_{GD} = 3/100/3/10 \ \mu m.$                                                                                                                             | 223          |

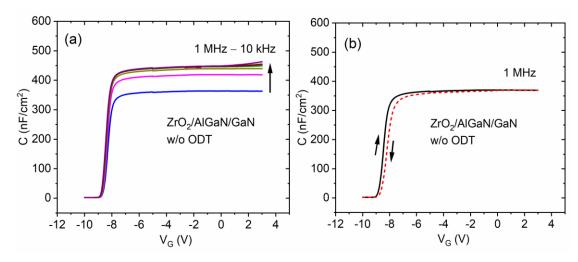

| Figure 5.73: <i>CV</i> curves for ZrO <sub>2</sub> -based MIS-capacitor without ODT surface treatment. (a) frequency dependent, (b) hysteresis at 1 MHz.                                                                                                                                                                                  | 225          |

| Figure 5.74: CV curves for ZrO <sub>2</sub> -based MIS-capacitor with ODT surface treatment frequency dependent, (b) hysteresis at 1 MHz.                                                                                                                                                                                                 | . (a)<br>225 |

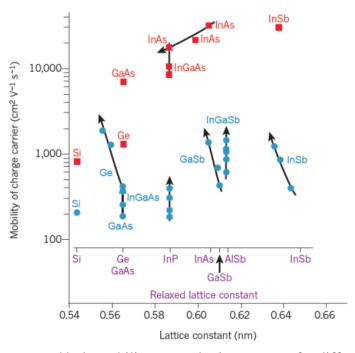

| Figure 6.1: Electron and hole mobility versus lattice constant for different conventional semiconductors [93].                                                                                                                                                                                                                            | 228          |

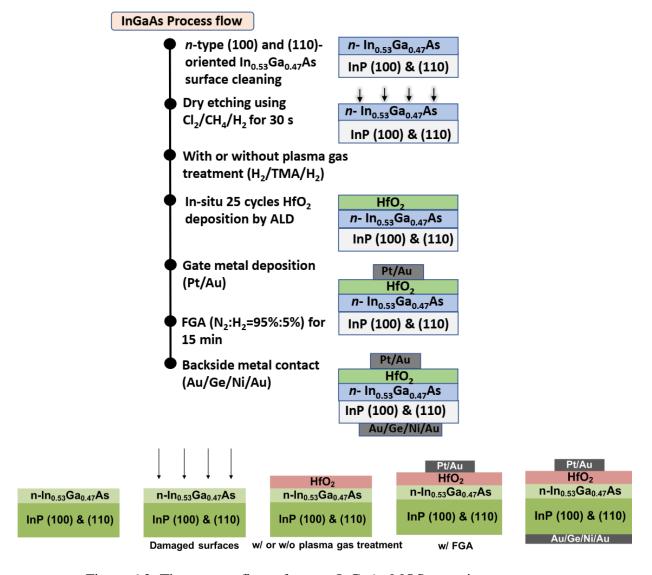

| Figure 6.2: The process flow of <i>n</i> -type InGaAs MOS-capacitor.                                                                                                                                                                                                                                                                      | 233          |

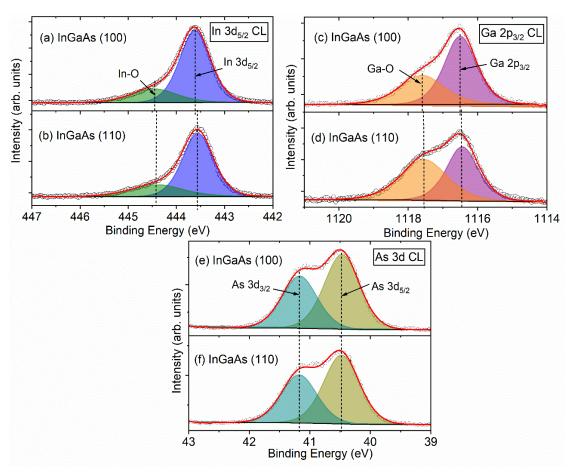

| Figure 6.3: The deconvoluted XPS spectra for (100) and (110) InGaAs blanket samples of (a) In $3d_{5/2}$ , (b) Ga $2p_{3/2}$ and (c) As 3d CLs.                                                                                                                                                                                           | 235          |

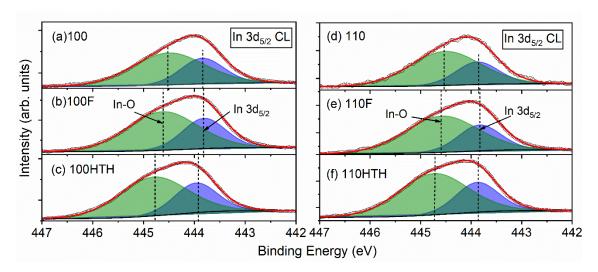

| Figure 6.4: The deconvoluted XPS spectra of In $3d_{5/2}$ CL for HfO <sub>2</sub> /(100) InGaAs samples under different surface treatments: (a) control sample 100, (b) afte FGA 100F and (c) plasma surface treatment and FGA, 100HTH; in compariso to the same samples but on (110) InGaAs substrate: (d) 110, (e) 110F and (f) 110HTH. | n            |

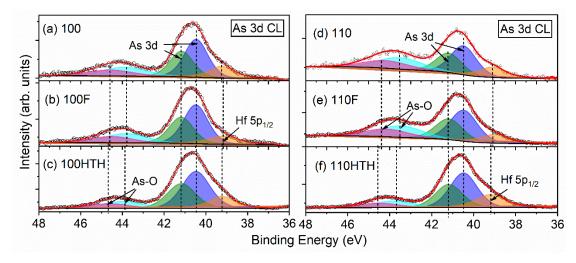

| Figure 6.5: The deconvoluted XPS spectra of As 3d CL under different surface treatments for $HfO_2/(100)$ InGaAs samples: (a) 100, (b) 100F and (c) 100HTH; in comparison to $HfO_2/(110)$ InGaAs samples: (d) 110, (e) 110F and (f) 100HTH.                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

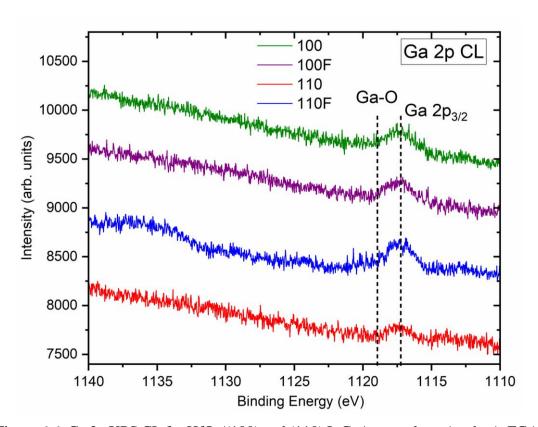

| Figure 6.6: Ga 2p XPS CL for HfO <sub>2</sub> /(100) and (110) InGaAs samples w/ and w/o FGA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

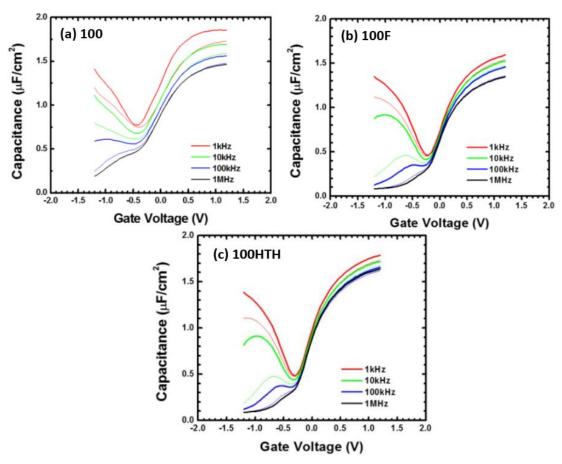

| Figure 6.7: Room-temperature high frequency <i>CV</i> plots of Au/Pt/HfO <sub>2</sub> /(100) <i>n</i> -InGaAs/InP MOS capacitors: (a) (100) control sample w/o FGA, (b) (100F) with FGA, and (c) (100HTH) plasma based surface pre-cleaning and FGA [325]241                                                                                                                                                                                                                                                                                                                                                                                                       |

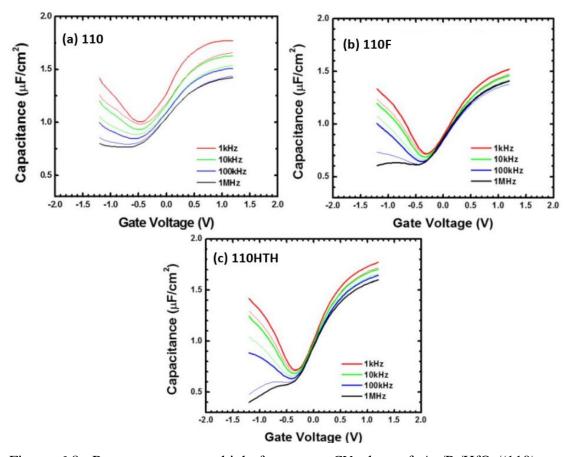

| Figure 6.8: Room-temperature high frequency $CV$ plots of Au/Pt/HfO <sub>2</sub> /(110) $n$ -InGaAs/InP MOS capacitors: (a) (110) control sample w/o FGA, (b) (110F) with FGA, and (c) (110HTH) plasma based surface pre-cleaning and FGA [325]242                                                                                                                                                                                                                                                                                                                                                                                                                 |

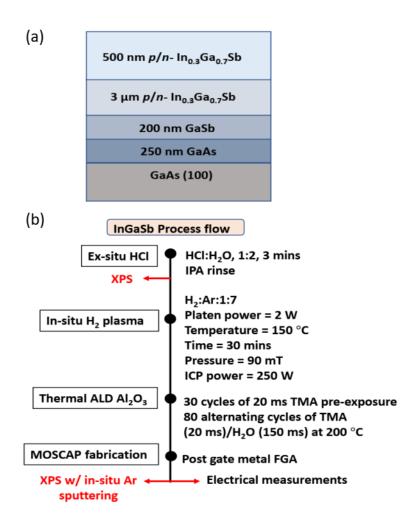

| Figure 6.9: (a) The layer structure of the InGaSb samples; (b) the process flow depicting surface treatments used on InGaSb samples followed by fabrication of $Al_2O_3$ -based MOSCAPs247                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

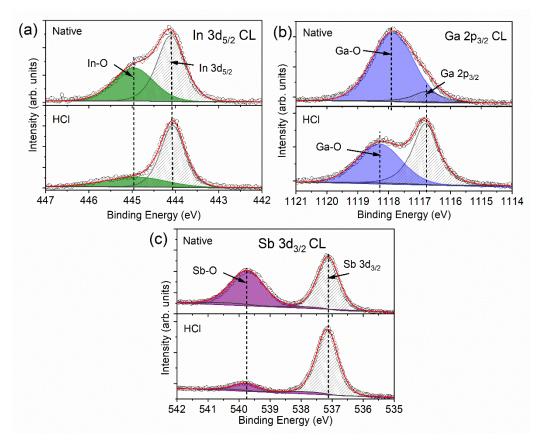

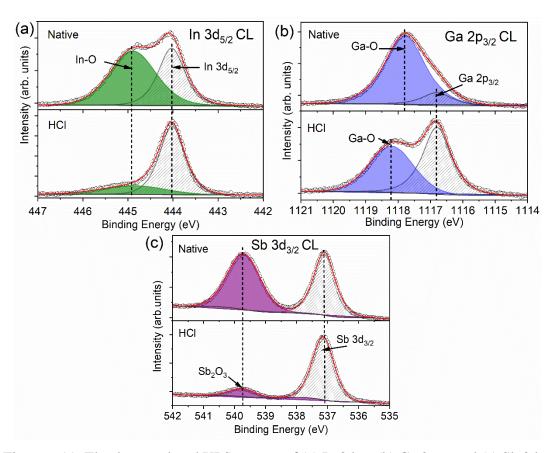

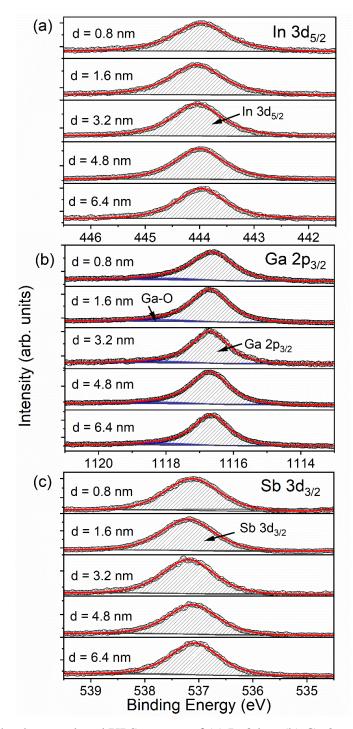

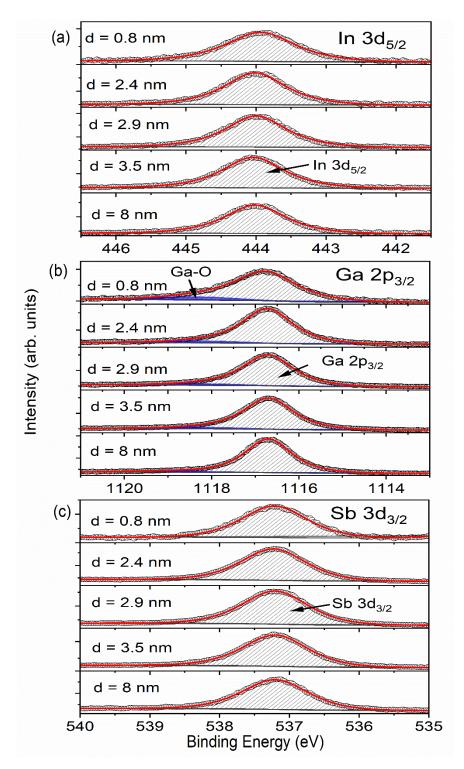

| Figure 6.10: The deconvoluted XPS spectra of (a) In $3d_{5/2}$ , (b) Ga $2p_{3/2}$ and (c) Sb $3d_{3/2}$ CLs for $n$ -type In <sub>0.3</sub> Ga <sub>0.7</sub> Sb before and after HCl cleaning250                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

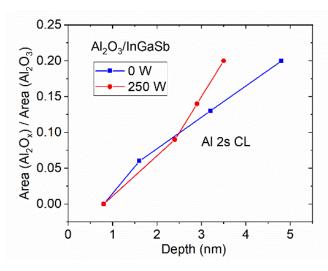

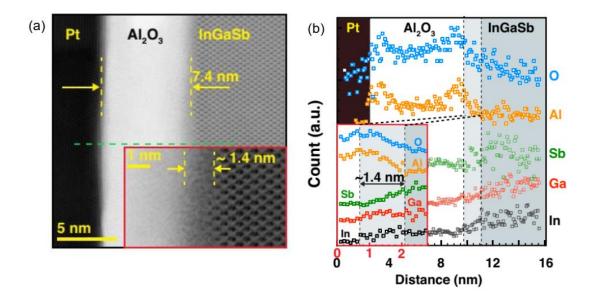

| Figure 6.11: The deconvoluted XPS spectra of (a) In $3d_{5/2}$ , (b) Ga $2p_{3/2}$ and (c) Sb $3d_{3/2}$ CLs for $p$ -type In <sub>0.3</sub> Ga <sub>0.7</sub> Sb before and after HCl cleaning251                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |