# Heterogeneous 2.5D integration on through silicon interposer

Xiaowu Zhang, Jong Kai Lin, Sunil Wickramanayaka, Songbai Zhang, Roshan Weerasekera, Rahul Dutta, Ka Fai Chang, King-Jien Chui, Hong Yu Li, David Soon Wee Ho, Liang Ding, Guruprasad Katti, Suryanarayana Bhattacharya, and Dim-Lee Kwong

Citation: Applied Physics Reviews 2, 021308 (2015); doi: 10.1063/1.4921463

View online: http://dx.doi.org/10.1063/1.4921463

View Table of Contents: http://scitation.aip.org/content/aip/journal/apr2/2/2?ver=pdfcov

Published by the AIP Publishing

### Articles you may be interested in

Through-silicon via-induced strain distribution in silicon interposer

Appl. Phys. Lett. 106, 141905 (2015); 10.1063/1.4915604

Plasticity mechanism for copper extrusion in through-silicon vias for three-dimensional interconnects

Appl. Phys. Lett. 103, 211906 (2013); 10.1063/1.4833020

# Low-temperature Al-Ge bonding for 3D integration

J. Vac. Sci. Technol. B 30, 06FK01 (2012); 10.1116/1.4762844

Characterization of thermal stresses in through-silicon vias for three-dimensional interconnects by bending beam technique

Appl. Phys. Lett. 100, 041901 (2012); 10.1063/1.3678020

### Process integration for through-silicon vias

J. Vac. Sci. Technol. A 23, 824 (2005); 10.1116/1.1864012

Journal of Applied Physics is pleased to announce André Anders as its new Editor-in-Chief

# **APPLIED PHYSICS REVIEWS**

# Heterogeneous 2.5D integration on through silicon interposer

Xiaowu Zhang, Jong Kai Lin, Sunil Wickramanayaka, Songbai Zhang, Roshan Weerasekera, Rahul Dutta, Ka Fai Chang, King-Jien Chui, Hong Yu Li, David Soon Wee Ho, Liang Ding, a) Guruprasad Katti, Suryanarayana Bhattacharya, b) and Dim-Lee Kwong

Institute of Microelectronics, A\*STAR (Agency for Science, Technology and Research), 11 Science Park Road, Singapore Science Park II, Singapore 117685

(Received 14 September 2014; accepted 18 March 2015; published online 23 June 2015)

Driven by the need to reduce the power consumption of mobile devices, and servers/data centers, and yet continue to deliver improved performance and experience by the end consumer of digital data, the semiconductor industry is looking for new technologies for manufacturing integrated circuits (ICs). In this quest, power consumed in transferring data over copper interconnects is a sizeable portion that needs to be addressed now and continuing over the next few decades, 2.5D Through-Si-Interposer (TSI) is a strong candidate to deliver improved performance while consuming lower power than in previous generations of servers/data centers and mobile devices. These low-power/high-performance advantages are realized through achievement of high interconnect densities on the TSI (higher than ever seen on Printed Circuit Boards (PCBs) or organic substrates), and enabling heterogeneous integration on the TSI platform where individual ICs are assembled at close proximity (<1 mm separation) compared with several centimeters on a typical PCB. In this paper, we have outlined the benefits of adopting 2.5D TSI technology and also highlighted the current day approaches to implement this technology in Si fabrication facilities, and in assembly/packaging factories. While the systems and devices that power the mobile society benefit from exploiting advantages of 2.5D integration on TSI, there do exist surmountable challenges that need to be addressed for this relatively new technology to be used in high volume production of next generation semiconductor devices. The key areas of focus and challenges include: Technology planning and design-execution that are necessary for harnessing 2.5D TSI for building systems, processing flow for the fabrication of 100 μm thick TSI at acceptable costs, manufacturing flow for assembling multiple ICs on a 100  $\mu$ m thick TSI in a repeatable, and reliable manner, thermo-mechanical analysis and optimization for addressing warpage issues, and thermal management for addressing heat dissipation. We have outlined design, manufacturing methodologies, and challenges, along with solutions to the challenges associated with taking 2.5D TSI technology to high volume production within the next few years. © 2015 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4921463]

| <b>TABLE</b> | OF | CON | ITEN | ITS |

|--------------|----|-----|------|-----|

|              |    |     |      |     |

|                                                                             | execution                                   | 1  |

|-----------------------------------------------------------------------------|---------------------------------------------|----|

| I CYCTEMC TRENDS AND 25D/2D                                                 | 2. Processing flow for fabrication of       |    |

| I. SYSTEMS TRENDS AND 2.5D/3D TECHNOLOGY INTEGRATION BENEFITS 2             | 100 μm thick TSI                            | 7  |

| A. Interconnect bottleneck                                                  | 3. Manufacturing flow for assembling        | _  |

| 1. More-on-Moore SoC scaling                                                | multiple ICs on a 100 µm thick TSI          | 7  |

| 2. More-than-Moore system scaling 3                                         | Thermo-mechanical analysis and optimization | 8  |

| 3. Application examples                                                     | 5. Thermal management of 2.5D TSI           | 8  |

| C. Challenges for heterogeneous 2.5D                                        | 6. Development of next generation           |    |

| integration                                                                 | manufacturing equipment                     | 8  |

| on TSI6                                                                     | II. KEY TECHNOLOGY MODULES FOR 2.5D         |    |

|                                                                             | HETEROGENEOUS INTEGRATION                   | 8  |

|                                                                             | A. TSV module                               | 8  |

| a)Present address: Inphi International Pte. Ltd., 988 Toa Payoh North, #05- | 1. TSV deep Si etch process                 | 9  |

| 01 & #05-07/08, Singapore 319002.                                           | 2. TSV liner deposition                     | 10 |

| b) Electronic mail: bhattass@ime.a-star.edu.sg                              | 3. Seed layer and barrier layer deposition  | 11 |

1. Technology planning and design-

|      | 4. ECP                                         | 12 | 1. Design for reducing TSV wafer warpage                  | 42    |

|------|------------------------------------------------|----|-----------------------------------------------------------|-------|

|      | 5. CMP                                         | 13 | 2. Design for avoiding die-cracking during                |       |

|      | B. BEOL and RDL scheme                         | 13 | chip stacking                                             | 43    |

|      | C. Bumping                                     | 15 | C. Packaging and long-term reliability                    | 43    |

|      | 1. Solder bumping and Cu pillar bumps          | 15 | 1. CPI and micro solder bump reliability of               |       |

|      | 2. Bumps in 2.5D TSI package                   | 15 | TSI                                                       | 43    |

|      | 3. Fabrication of Cu pillar micro-bumps        | 15 | 2. Design for enhancing solder joint                      |       |

|      | 4. Reliability assessment of Cu pillar         |    | reliability                                               |       |

|      | bumps                                          | 17 | of packages with Si carrier                               | 44    |

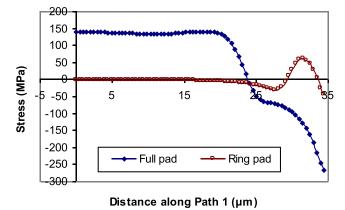

|      | D. Thin wafer handling                         | 19 | 3. Demonstration a low stress bond pad                    |       |

|      | 1. Carrier substrates                          | 19 | design for low temperature micro bumps                    |       |

|      | 2. Temporary bonding and debonding             | 19 | on TSVs                                                   | 44    |

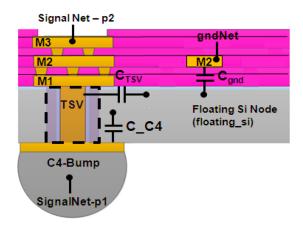

|      | 3. Adhesives requirement                       | 21 | VII. EDA CONSIDERATIONS AND READINESS.                    | 45    |

| III. | 2.5D TSI ASSEMBLY CHALLENGES                   | 21 | A. 2.5D IC PDK                                            | 45    |

|      | A. Introduction                                | 21 | 1. Technology LEF files                                   | 45    |

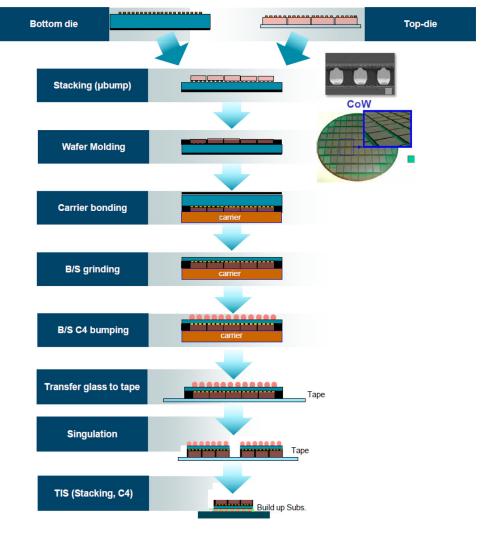

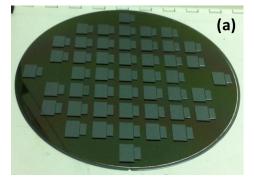

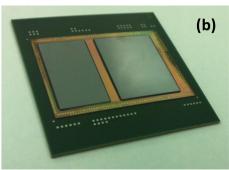

|      | B. TSI package assembly process flow           | 21 | 2. PEX rule decks and TSV extraction                      | 45    |

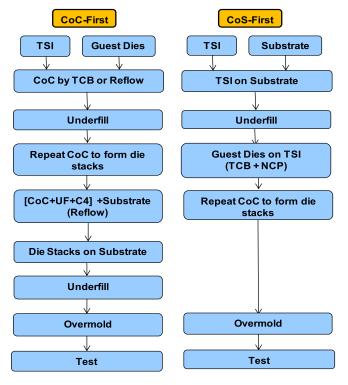

|      | 1. Chip-on-substrate (CoS) first assembly      |    | 3. DRC/LVS rule decks                                     | 46    |

|      | flow                                           | 22 | B. 2.5D IC EDA flow                                       | 46    |

|      | 2. Chip-on-chip (CoC) first assembly flow.     | 22 | 1. Design import                                          | 46    |

|      | 3. Chip-on-wafer (CoW) first assembly          |    | 2. Floor planning and placement                           | 47    |

|      | flow                                           | 22 | 3. Routing on 2.5D TSI                                    | 47    |

|      | C. Assembly Challenges and Warpage Control.    | 24 | 4. Parasitic extraction                                   | 47    |

|      | D. Summary                                     | 24 | 5. SI and PI verification                                 | 47    |

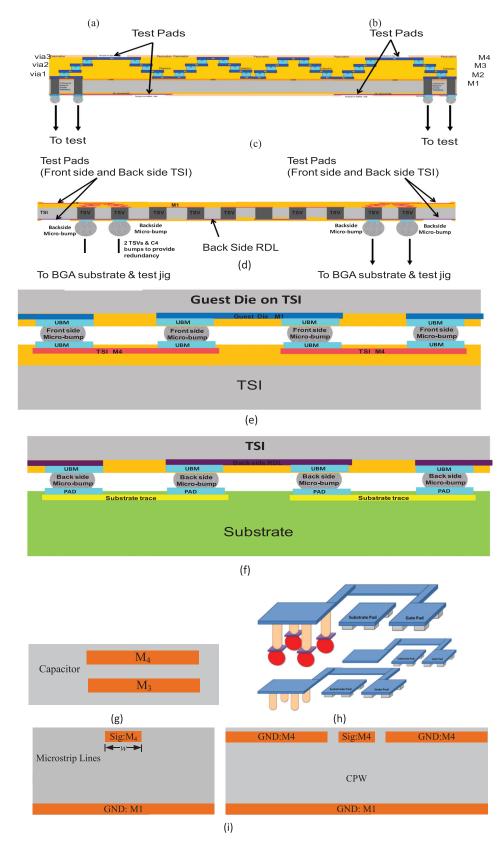

| IV.  | 2.5D TSI TEST AND CHARACTERIZATION .           | 25 | 6. DRC and LVS verification                               | 47    |

|      | A. Test structures for 2.5D TSI electrical     |    | C. 2.5D functional vehicle design—A case                  |       |

|      | characterization                               | 25 | study                                                     | 47    |

|      | 1. TSV characterization structures             | 25 | VIII. REVISITING APPLICATIONS AND                         |       |

|      | 2. High density wiring characterization        | 27 | BENEFITS OF 2.5D TSI TECHNOLOGY                           | 48    |

|      | 3. Chip-to-chip link characterization          | 28 | A. 2.5D TSI technology—Application space                  | 48    |

|      | 4. Micro joint reliability characterization    | 28 | B. Application roadmap                                    | 50    |

|      | 5. Decoupling capacitors                       | 29 | IX. FUTURE OUTLOOK/CONCLUSIONS                            | 50    |

|      | THERMAL CONSIDERATIONS OF 2.5D                 |    | A. 2.5D TSI technology roadmap                            | 50    |

|      | PACKAGES                                       | 29 | 1. Solder technology                                      | 51    |

|      | A. Thermal challenges in the context of 2.5D   |    | 2. Metal-metal bonding                                    | 52    |

|      | package                                        | 29 | B. 2.5D/3D EDA outlook                                    | 53    |

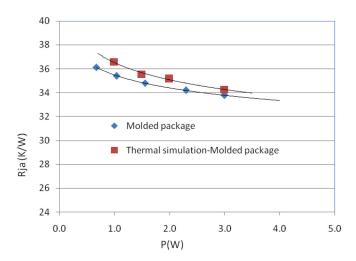

|      | B. Passive cooling                             | 30 | 1. Inability of existing 3D EDA tools to                  |       |

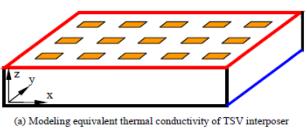

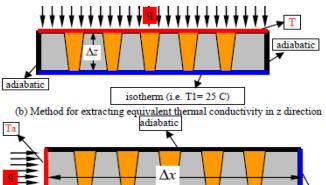

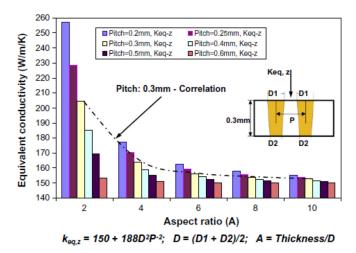

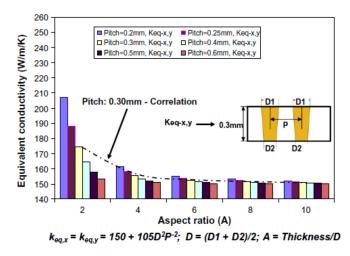

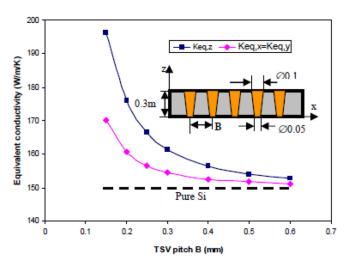

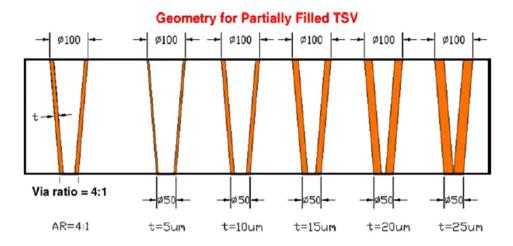

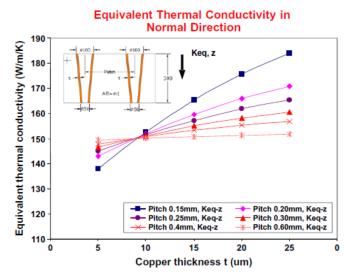

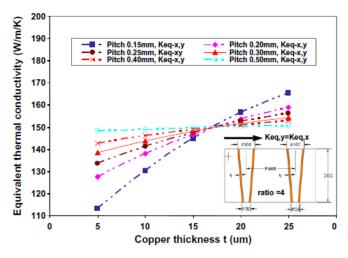

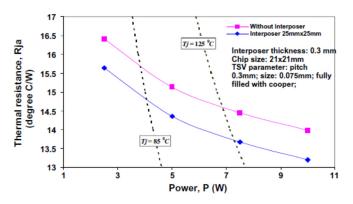

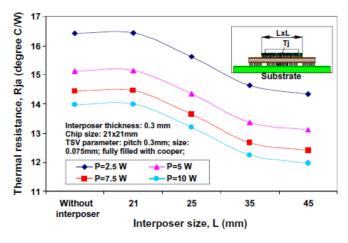

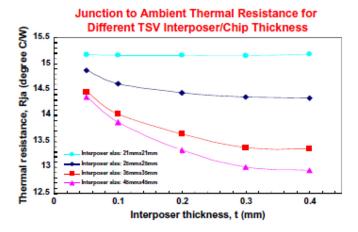

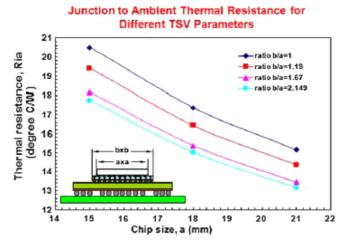

|      | 1. TSV thermal enhancement                     | 30 | analyze unified 3D netlist                                | 53    |

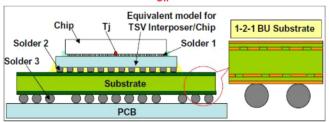

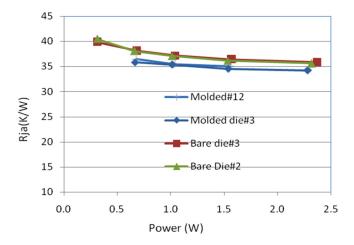

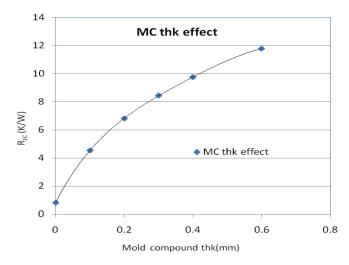

|      | 2. Effect of TSV interposer on package         |    | 2. Employing calibrated TSV lumped "RC"                   |       |

|      | thermal performance                            | 32 | model                                                     | 54    |

|      | 3. Thermal characterization of stacked         |    | X. SUMMARY                                                | 54    |

|      | chips                                          | 33 |                                                           |       |

|      | 4. Thermal characterization of 2.5D            |    | I. SYSTEMS TRENDS AND 2.5D/3D TECHNOLOGY                  |       |

|      | package                                        | 35 | INTEGRATION BENEFITS                                      |       |

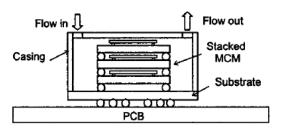

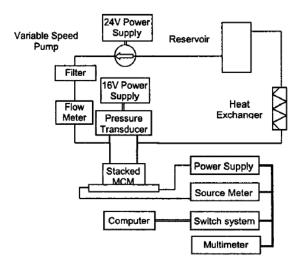

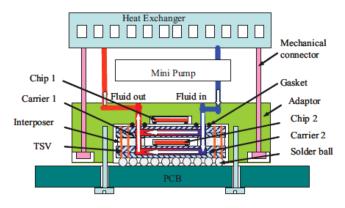

|      | C. Active cooling                              | 36 | We live in a mobile assistant base mobile decises         | .11   |

|      | 1. Active air cooling                          | 36 | We live in a mobile society where mobile devices a        |       |

|      | 2. Liquid cooling                              | 36 | us to communicate readily with people that are socially   |       |

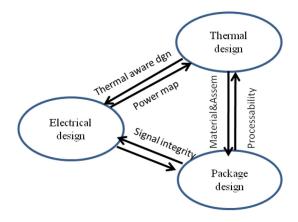

|      | D. Thermal aware 2.5D design and               |    | professionally connected to us. Today's mobile so         | •     |

|      | implementation                                 | 39 | leverages on the performance and reliability of mobile of |       |

| VI.  | THERMO-MECHANICAL DESIGN AND                   |    | ces (phones and tablets) and the vast internet infrastruc |       |

|      | MODELING FOR 2.5D PACKAGING                    | 40 | In these two areas, amazing technical innovations         |       |

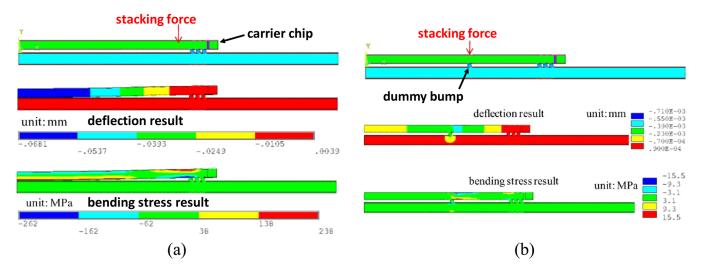

|      | A. Manufacturability and functionality of TSI. | 40 | strongly driven by the large market size and customer l   |       |

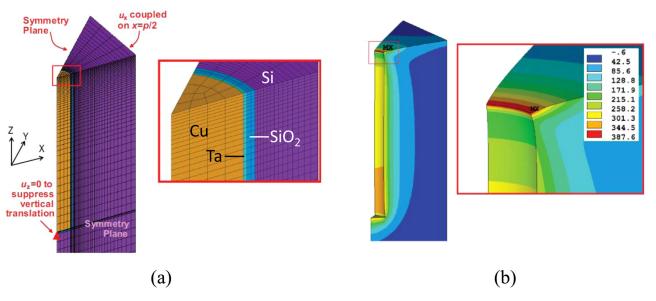

|      | 1. Design rules for avoiding wafer cracking    | 41 | Continued innovations are needed as the adoption of mo    |       |

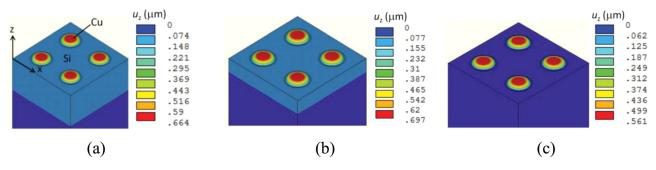

|      | 2. Design rules for reducing copper            |    | devices rapidly penetrates developed as well as emer      |       |

|      | protrusion                                     | 41 | economies of the world. Innovations are necessary s       |       |

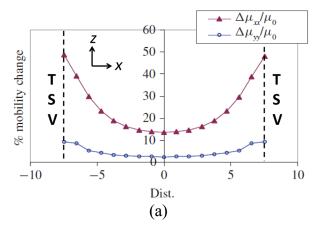

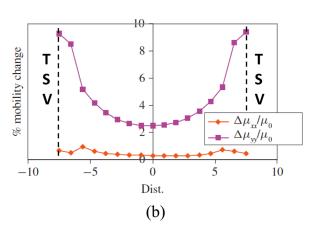

|      | 3. Design for reducing mobility change of      |    | such adoption will drive the processing and transfer of l | large |

|      | MOSFETs near TSVs                              | 42 | volumes of data in the mobile society.                    |       |

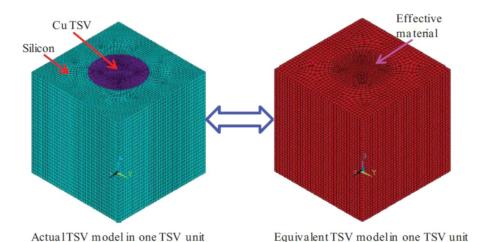

|      | B. Handling of TSV wafers and chips during     |    | Recent data show that there is a greater than 10 t        |       |

|      | fabrication and assembling                     | 42 | increment in the mobile data traffic from 2012 to 2017    | and   |

the daily data traffic amounts to be quintillion bytes ("Big Data"). These data originate from all around the world in the forms of climate information, pictures and videos, banking transactions, and global positioning system (GPS) data, etc. Handling such data traffic is dependent on the use of various Si technologies (e.g., Logic-CMOS, dynamic random access memory (DRAM), BiCMOS, Si Photonics, etc.). A key concern is the performance and power consumption of integrated circuits (ICs) and devices for transferring large amounts of data. In this review paper, we look into the opportunities and trends in the heterogeneous integration of various Si technologies using 2.5D Through-Si-Interposer (TSI) as a next generation Si technology platform to manufacture next generation IC and devices that will support the explosion in the data traffic.

#### A. Interconnect bottleneck

When one looks closely at data traffic at the system/subsystem level (e.g., mobile phones, tablets, data centers, and line cards), the data traffic most typically occurs between the logic and memory devices and is transmitted across Cu interconnects. With large amounts of data processed or transferred, a key bottleneck is the movement of the data between a logic device and a memory or between 2 or more logic devices. Such data transfer happens over interconnects. Interconnects within computers, mobile devices, and within data-centers are typically using Cu lines on Printed Circuit Boards (PCBs) or Organic Substrates, or on System-on-Chip (SoC) interconnects—for electrical data transfer. A simplest case that can be considered is that of a multi-core processor transferring data to a nearby memory (known as logicmemory interface) over Cu interconnects. Such data transfer occurs all the time in a mobile device or in a data-center or in a switching network. It turns out, the performance of, and the power consumed by the logic-memory interface is a critical bottleneck that needs to be addressed for both mobile devices and data-centers that form a central part of today's internet infrastructure.

#### 1. More-on-Moore SoC scaling

The challenge with improving the efficiency and speed of the logic-to-memory interface is also referred to as the "memory-wall." This is because logic-device (or processor) performance is steadily improving over past decades due to CMOS technology advancement that is guided by Moore's law.<sup>2</sup> The More-on-Moore miniaturization<sup>3</sup> drives the minimum chip feature size (transistor gate length) to shrink about 50% every 18 months, allowing for faster transistors on logic devices (processors). Processor optimization has also led to the use of multi-core (8-core, 32-core, 64-core, and so on) processors to enhance the performance of advanced processors called Central Processing Units (CPU). In a high performance system, this means that each of these individual processor-cores needs to have separate access channel to data in the memory. However, there is a limitation to how fast multiple processors can exchange data with increasingly large amounts of memory. This is a fundamental interconnect related challenge faced by today's PCBs and electronic

packages. Therefore, they cannot support the density of interconnects that is needed to support this data transfer. In addition to interconnect density, the length of the interconnects on PCBs is quite long (order of centimeters), which means that significantly higher power consumption is required when multiple processors send and receive data from memory devices.

CMOS technology miniaturization (Moore's law<sup>2</sup>) can be translated into system level performance improvements by using the System-On-Chip architecture—where both logic and memory are fabricated in the same Si wafer. However, as mentioned above, the advent of multi-core processors that need to have large amounts of adjacent memory (several Gigabytes) places several limitations on the Moore's law-enabled SoC architecture in terms of the sheer size of Si needed (larger Si chip means lower yields). In addition, the high performance Si technology for producing logic processors is highly unsuitable for making low-power memory functions (e.g., DRAM). The separation of the logic and memory functions into discrete packages places the burden on the PCB, and the electronic packages. When the complexity of ICs increases, the number of I/O pins rises exponentially according to the well known Rents rule,<sup>4</sup> thereby giving rise to increased wiring demands<sup>5,6</sup> on the system level. For next generation systems, the PCB and electronic packages face serious challenges from (a) limited interconnect density of electronic packages that connect logic and memory, (b) I/O circuit power consumption related to higher parasitics from longer PCB and package wire lengths, and (c) power disadvantage (1/2 f.C.V<sup>2</sup>) at higher clock rates are typically used to transfer large amounts of data within systems with I/O count limitations. Package (C4) bump-pitch has scaled at a significantly slower rate in comparison with CMOS technology nodes, and it demonstrates the manifestation of the interconnect challenge.<sup>7</sup>

Therefore, traditional electronic packaging combined with Moore's Law presents a bottleneck for system scaling, i.e., increasing system speed, reducing system power, and shrinking system size.

### 2. More-than-Moore system scaling

In order to provide a multi-generational solution to address the challenges to system-scaling, one needs an alternative approach that overcomes the limitations on system scaling placed by the memory-wall, limitations of Moore's law/SoC architecture, and the lack of interconnect scaling on PCBs and electronic packages. First, high performance systems need optimized Si technologies to obtain the necessary performance and power requirements of different parts of the system, namely, logic gates, memory cells, RF/Analog blocks, etc. Thus, one needs to think in terms of "disintegrating" the SoC to achieve optimization of given function: (a) Logic-speed and power, (b) memory density/ power/ performance, (c) RF/Analog performance, and (d) optimized interconnect that links these features to make high performance/low-power systems. With the ability to optimize Si technologies based on the functions, one can develop both memory and logic (CPU) ICs with the necessary number of I/O counts that can overcome the memory-wall. To Micro Bump

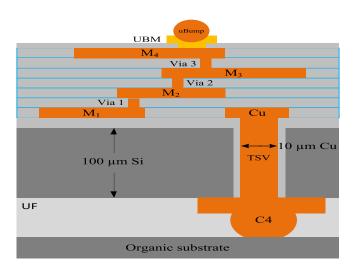

interconnect the tens to hundreds of thousands of I/Os, between logic ICs and memory ICs, one can use fine pitch copper wiring that can be readily derived from CMOS copper interconnects using Si fabrication. This provides Si substrate to connect several thousands of interconnects between ICs, and deliver power and ground supply to the ICs on the Si substrate. Second, unpackaged individual ICs are attached using micro-solder-joints or micro-bumps to the Si substrate containing fine pitch interconnects (pitch capable of reaching  $<2 \mu m$  line/space compared to 10–20  $\mu m$  line/space on organic packages and PCBs). Such unpackaged ICs have much reduced package parasitics. The signal, power, and ground connections are provided by Through-Si-Vias (TSVs), enabling electrical connections from the bottom side of the Si substrate to the front side where the ICs are attached. Such a Si substrate is called a TSI. 9-11 This technology referred to as 2.5D integration (or 2.5D ICs) using TSIs offers significant benefits to overcome limitations to system-scaling and is considered a game-changer for current and future systems that are expected to drive mobile-handheld and data-center applications for decades to come. The term 2.5D stems from the fact that using TSI technology for stacking ICs side-byside on a TSI can be considered a midpoint between traditional ICs in package representing 2D integration, and chips stacked on top of one another that represents 3D integration. The TSI offers a technology platform to integrate disparate technologies (such as CMOS, memory, sensors, high density copper interconnects, optical interconnects supported by Si photonics, etc.) and thus enable heterogeneous integration. This form of integration is also known as Morethan-Moore integration.

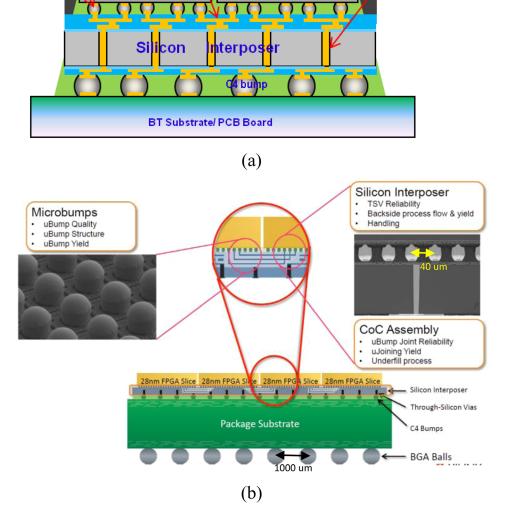

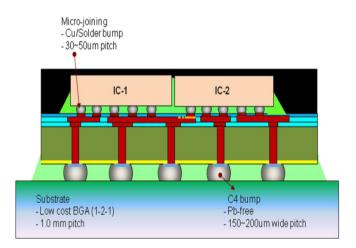

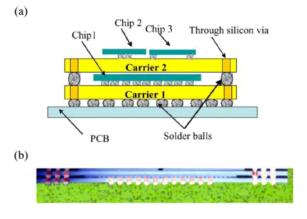

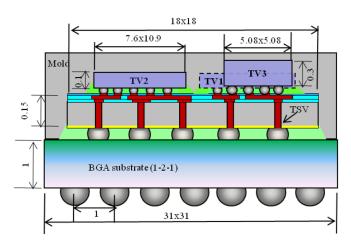

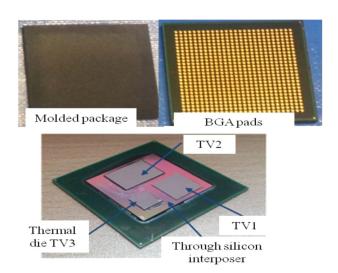

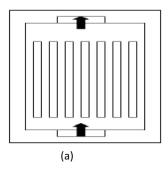

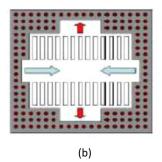

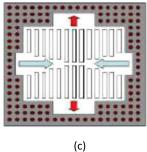

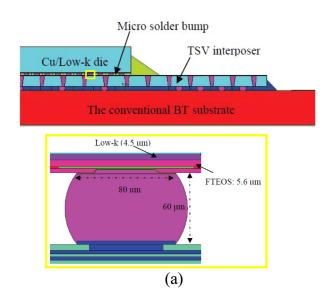

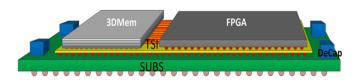

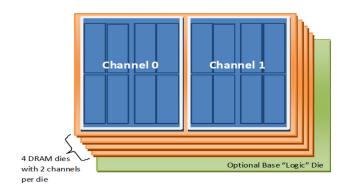

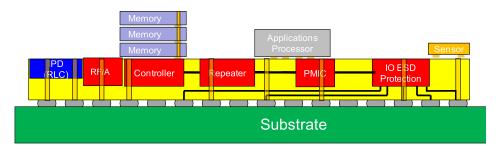

Figure 1(a) shows an example of a TSI platform which provides the necessary high density interconnects to address the gap between chip scaling and system wiring in many of the heterogeneous systems. TSI allows designers to connect multiple ICs with high density and significantly shorter (<1 mm), fine pitch (<4  $\mu$ m) sub micron interconnects (than provided by traditional packaging), and microbump (pitch < 40  $\mu$ m) technology. TSVs provide the access to a package/PCB for power supply or ground and external I/Os.

Figure 1(b) illustrates how the fine pitch (pitch =  $40 \mu m$ ) micro-bumps connect field-programmable gate array (FPGA) slice to the TSV interposer. The C4 bumps (pitch =  $200 \mu m$ ) in turn connect the TSI to the package. Large package balls (pitch =  $1000 \mu m$ ) connect the package to the PCB.

IC-2

FIG. 1. (a) Schematic of IC integration on a TSI platform. (b) Cross-section of the Xilinx 2.5D TSI based Virtex-7HT FPGA. <sup>12</sup> Reproduced with permission from Madden *et al.*, "Advancing high performance heterogeneous integration through die stacking," in Proceedings of European Solid-State Device Research Conference (ESSDERC) (2012). Copyright 2012 Institute of Electrical and Electronics Engineers.

Through-Silicon Via (TSV)

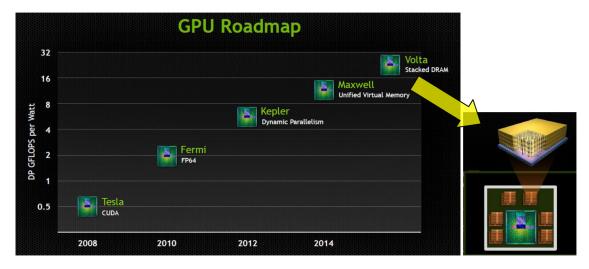

FIG. 2. Si interposer application examples and development roadmap.

Over the past few years, a significant research effort has been invested on 2.5D integration technologies encompassing fabrication, assembly, packaging, and design automation tools and electrical design issues such as signal integrity/power integrity (SI/PI). This review paper attempts to capture the advantages of this technology and reviews major challenges and solutions developed by the industry, IME, and other research institutes.

### 3. Application examples

SerDes (Xilinx)

Figure 2 shows a proposed roadmap for the application of 2.5D TSI technology for mobile devices and data centers. In 2012, Xilinx<sup>12</sup> demonstrated virtex-7 FPGA with 2.5D TSI technology integrating high density gate arrays with high-speed Serializer-Deserializer (SERDES). The next phase of heterogeneous integration using 2.5D TSI will allow the integration of high-speed Graphic Processor Units (GPU) or Application Processor Engines (APE) with high density 3D stacked memories (High-Band-Width Memory (HBM)<sup>14</sup> and Hybrid Memory Cube (HMC)<sup>15</sup>) for graphic computing, and mobile tablets. As data traffic continues to explode, optical interconnects are needed for transferring large volumes of data between racks in data centers and high performance computers. In such applications, the photonic IC (PIC)<sup>16</sup> needs to be in close proximity with logic device/ SERDES. 2.5D TSI can heterogeneously integrate logic and memory subsystems with photonics that drive optical data communications at sub pJ/bit energy efficiencies. Thus 2.5D TSI technology has the potential to be a key enabler in high speed data communications in the next several decades.

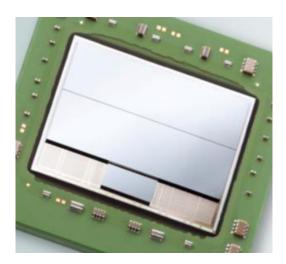

Figure 3 shows a larger picture of the Xilinx Virtex 7HT FPGA. The individual FPGA slices are manufactured using an optimized 28 nm CMOS technology, while the SERDES is manufactured using 28 nm high-performance CMOS technology. This optimized technology choice for the FPGA and SERDES functions allows unprecedented 2.8 Tb/s data transfer capability using 2.5D ICs at lower power consumption. Figure 5 shows how 2.5D/3D TSV/TSI technology can help reduce the footprint of a state-of-the-art logic processor

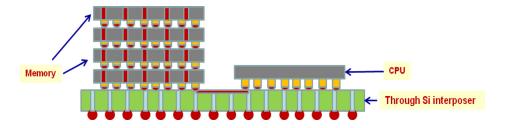

(CPU) and DDR4 DRAM system. On the left side, we show a PCB which is typically greater than 20 cm on one side. On either sides of the packaged CPU, there are multiple banks of packaged DDR4 memories. The length of interconnect between CPU and memory IOs can be of the order of 10 cm. This results in higher parasitic capacitances, as well as signal reflections due to different physical boundaries. In addition, due to the required bandwidth (BW) of 4 Tb/s between CPU and DRAM total power can be up to 640 W (20 pJ/bit energy consumption for IOs). On the right side of Figure 4, the same system is implemented on a 2.5D TSI that is around  $40 \,\mathrm{mm} \times 40 \,\mathrm{mm}$  in size. The four banks of DDR4 are replaced by four 3D stacked high density DRAMs that are in bare die form. The 3D DRAMs are attached to the TSI (yellow color) with fine pitch micro-bumps that can connect thousands of 3D DRAM IOs to the TSI. The CPU, also in an unpackaged, bare die form, is connected to the TSI through fine pitch micro-bumps. The thousands of IOs between the

FIG. 3. Xilinx Virtex 7HT with a 2 slices of FPGA integrated with SERDES IC. 12 Reproduced with permission from Madden *et al.*, "Advancing high performance heterogeneous integration through die stacking," in Proceedings of European Solid-State Device Research Conference (ESSDERC) (2012). Copyright 2012 Institute of Electrical and Electronics Engineers.

FIG. 4. A typical CPU-memory system showing (a) higher interconnect density and (b) shorter interconnects in TSI based system.

CPU and 3D DRAM are laid out on the TSI using fine pitch copper interconnects. Typically, interconnects in the TSI can support up to 1000 connections per mm cross-section. Because we are using bare die that can be assembled at close proximity (<1 mm), the length of interconnect can be around 10 mm, leading to a significantly lower energy consumption of <3.2 pJ/bit. Therefore, for a BW of 4 Tb/s, the power consumption is 12.8 W, which corresponds to 84% energy saving. Another benefit of this approach stems from the improvement of the form-factor of the sub-system from  $20 \, \text{cm} \times 20 \, \text{cm}$  on a PCB to a package size of around  $6 \, \text{cm} \times 6 \, \text{cm}$ . The details of the logic memory connection are shown in Figure 5, which schematically shows a TSI that heterogeneously integrates a CPU and 3D memory.

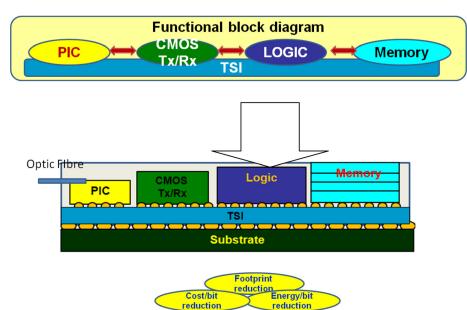

Optical interconnects are known to have the highest bandwidth and lowest power consumption, making them suitable for high bandwidth applications. With future high bandwidth systems, one needs to have optical interconnects to carry data in and out of PCBs that are in server racks. The challenge for using optical interconnects is to bring "optics" as close to CMOS electronics as possible. 2.5D integration using TSI technology can bring optical communication close to high performance CMOS technology—thus allowing servers in datacenters to have the best of both worlds (CMOS technology and optical interconnects). Figure 6 shows another application that benefits from the use of 2.5D TSI technology. It is a high performance line card that may be used in the racks of a server. In this example, an optical fiber connector is used to take data in and out of the line-card. Using 2.5D TSI technology, the PIC and the CMOS drivers can be integrated on the interposer and achieve significant improvements of form-factor. A typical 180 mm × 90 mm line card can be reduced to a  $35 \, \text{mm} \times 40 \, \text{mm}$  area. The schematic representation of the Electronic -PIC on 2.5D TSI is shown in Figure 6.

One way to implement optical interconnects is to use photonic integrated circuits. Optical interconnects are implemented through continuous wave Distributed Feed Back (DFB) lasers with Si photonics ICs. Heterogeneous integration of electronic and photonic ICs on TSI allows

independent technology optimization for Si CMOS processors, memory, CMOS/BiCMOS drivers, and silicon on insulator (SOI) PIC. The integration of Si photonics with TSI will enable the performance requirement of data-centers, super-computers, and high-performance-networking to be met (Fig. 7).

#### B. General summary in advancement

Up to this point, we started with how the exploding data traffic in the mobile society is expected to challenge the way we design and manufacture systems. From the application examples shown above, it can be seen that 2.5D Heterogeneous integration on TSI is a technology platform that can enable system-scaling for the next generation of systems that will be a part of our mobile society. Systems using 2.5D TSI can address both performance and power constraints in a manner that traditional packaging of SoC's built with Moore's law scaling alone cannot. In summary, 2.5D integration allows for a scalable approach to meet power and performance requirements of future generation systems. Heterogeneous integration allows for a manufacturing approach to realize the improvements in power performance metrics that are needed to achieve system scaling for mobile devices, data-centers, and high performance computers. In the rest of this paper, we will highlight the detailed features of this technology to facilitate an understanding of what it takes to design, fabricate, and assemble 2.5D ICs using TSI technology.

# C. Challenges for heterogeneous 2.5D integration on TSI

While opportunities abound, as is typical with a technology that is on path to wide adoption by industry, 2.5D heterogeneous integration on TSI has yet to address challenges in the design, fabrication, and assembly of 2.5D<sup>9–11</sup> and 3D ICs. <sup>17,18</sup> In this section, we outline the key challenges faced by TSI technology. Through the course of this paper, we shall elaborate on the same and highlight the techniques and continuing developments that address key challenges.

FIG. 5. Cross-section of CPU and 3D memory system showing the die level interconnections.

FIG. 6. Electro-photonic integration in TSI in a line card application.

The main technical challenges with designing 2.5D and 3D systems fall in the following areas: (A) Technology planning and design-execution that are necessary for harnessing 2.5D TSI for building systems, (B) processing flow for the fabrication of 100  $\mu$ m thick TSI at acceptable costs, (C) manufacturing flow for assembling multiple ICs on a 100  $\mu$ m thick TSI in a repeatable, and reliable manner, (D) thermal management for addressing heat dissipation of 2.5D TSI, (E) thermo-mechanical analysis and optimization for addressing warpage issues, and (F) electrical characterization and process design kit (PDK) for electronic design automation (EDA) flow of 2.5D TSI.

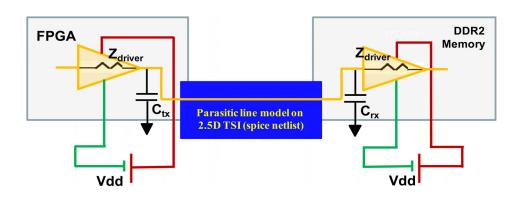

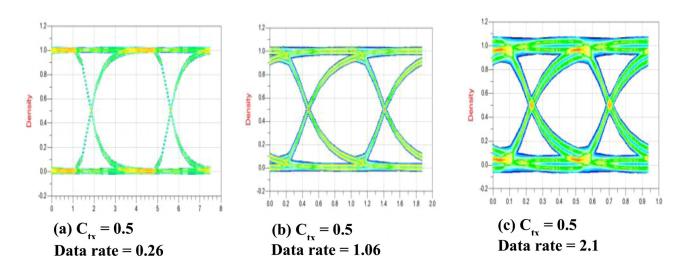

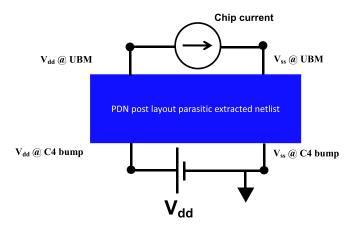

# 1. Technology planning and design-execution

In designing 2.5D TSI for integrating multiple functions, typically, one needs to start with interconnect planning that would satisfy the design requirements. There are two principle requirements for design engineers: (a) to meet the routing ability requirements of the design and (b) to satisfy the design SI/PI requirements. Routing ability refers to the ability of the TSI to handle the large number of IC-to-IC and IC-to-package interconnections. This is influenced by the available TSI routing area, interconnect size/pitch as well as the number of interconnect layers. More metal layers, larger routing area as well as smaller routing metal size/pitch offer larger routing ability. Increasing the number of metal layers and larger TSI area impose more technology challenges and a concomitant increase in the system cost. In addition, smaller metal size adversely increases the line resistance, giving rise to signal integrity issues. Thus designing a system on 2.5D TSI involves technology planning. For example, there are two fabrication techniques for forming fine-pitch interconnects on a TSI. Typically, two fabrication flows are available to choose from: (1) more expensive Cu-damascene based fine pitch (line width, space  $\leq 1 \mu m$ ; Pitch  $\leq 2$   $\mu$ m, Cu thickness  $\sim$ 1  $\mu$ m with multiple >4 levels of interconnects) and (2) less expensive polymer based Curedistribution layer (RDL) flow with coarse pitch (Size > 2  $\mu$ m; Pitch > 4  $\mu$ m, Cu thickness of 3  $\mu$ m, with up to 4 levels of interconnects). Thus, a designer needs to optimize the choices based on the application needs of routing and SI/PI requirements versus cost of processing. The next step is the physical implementation of the 2.5D TSI. To do this, one needs accurate electrical models of the TSI (R, L, and C), and a PDK that is implemented on an EDA flow. In addition, testing of 2.5D ICs needs to be addressed as well.

#### 2. Processing flow for fabrication of 100 µm thick TSI

A key challenge with Si processing for TSI fabrication is with the formation of TSVs which involves etching, dielectric deposition, and Cu electroplating to fill the TSVs that are typically formed on the front-side of the TSI. Each of these steps needs to be optimized based on TSV density in the TSI. In addition, processing throughput is also a key challenge to ensure cost-containment for these steps. Another challenge arises from handling thinned 300 mm TSI wafers. Upon thinning, the back-side of the TSI needs specific processing that includes passivation and formation of solder-bumps for attaching to the package substrate. Thin wafer handling is a major challenge in the fabrication of TSI wafers, where industry uses what is called temporary bonding and de-bonding (TBDB).

# 3. Manufacturing flow for assembling multiple ICs on a 100 $\mu m$ thick TSI

Upon fabrication of the TSI, individual ICs need to be attached to the top-side of the TSI. This can typically be done in many ways depending on product requirements. One technique involves singulating the TSI into individual dies, and then performing IC to TSI front-side assembly. This is

referred to as chip-to-chip (C2C) assembly flow. After this step, the TSI backside is attached to the package substrate (with multiple ICs assembled on the front-side of the TSI). This assembly flow can be time consuming. Therefore, the industry is moving to a chip-to-wafer (C2W) assembly flow where ICs are attached to the TSI while the TSI is still in a wafer form. Such wafer level packaging (WLP) allows for much higher manufacturing efficiency. Both C2C and C2W approaches have challenges in manufacturing—which need to be addressed to ensure high yields and adequate reliability.

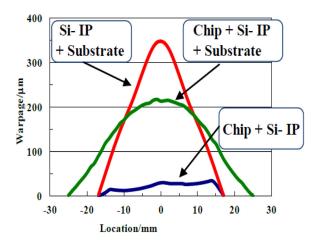

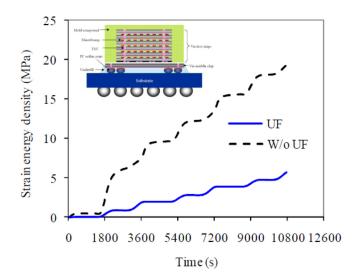

#### 4. Thermo-mechanical analysis and optimization

The TSI with ICs attached to the front-side is assembled on the package substrate using solder-joints as shown in Figures 4(a) and 4(b). The solder-joint is placed under stress due to the fact that Si has a low (3 ppM/°C) coefficient of thermal expansion (CTE) and the organic (laminate) package has a higher (~16 ppM/°C) CTE. The difference in the CTE means that the joined materials expand at different rates during thermal processing and during actual operation when heat is dissipated. This results in solder-joint stress and TSI warpage. Thus, a key challenge in designing a package for 2.5DTSI is to perform accurate thermomechanical analysis/finite element-modeling (FEM), and optimize solder joint placement to ensure reliability of the system.

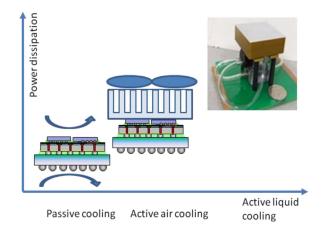

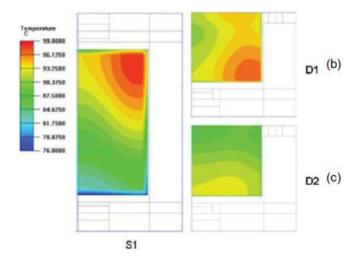

#### 5. Thermal management of 2.5D TSI

With high performance ICs interconnected on the 2.5D TSI, heat dissipation becomes a challenge. This challenge is commonly referred to as thermal management. Thermal management issues can be understood in two aspects. On one hand, the chip-level power delivery could reach high level such as 100 W/cm<sup>2</sup> for high performance ICs and this requires proximate cooling. Without compromising processing speed, the integration of multi-chips in one interposer on the package tends to generate higher heat density, which in

turn can compromise IC performance. On the other hand, the temperature sensitive chips such as photonic ICs prone to wavelength shifts due to the temperature excursions, which need to be thermally controlled. Thermal management uses passive cooling, or active air-cooling or active liquid cooling. As part of this optimization, one needs to design a thermal solution that meets the needs of the end application.

# 6. Development of next generation manufacturing equipment

In order to take 2.5D TSI technology to high volume manufacturing, improvements in manufacturing efficiencies are needed. As noted earlier, these improvements are focused on WLP to support TSI fabrication and assembly. Key areas where efficiencies are needed include: (a) TBDB for handling thin TSI wafers. Currently, this process has a throughput bottleneck since just a few wafers can be processed per hour through TBDB steps. (b) Chip-to-wafer bonding—where ICs need to be attached to TSI wafer at high alignment accuracies to support fine pitch (<40  $\mu$ m pitch) microbumps. Here also, throughput is a key figure of merit.

# II. KEY TECHNOLOGY MODULES FOR 2.5D HETEROGENEOUS INTEGRATION

Improvement in VLSI performance by downscaling of device dimensions is faced with limitations in system design due to increased power density, higher I/O count, interconnect bandwidth, and timing closure requirements. Si substrate with TSVs or TSI technology is identified as a solution to overcome these challenges. In this section, key 2.5D TSI technology modules and integration schemes are reviewed. Current development status and readiness of each technology modules and the respective processes will also be discussed in detail.

#### A. TSV module

TSV is one of the essential modules in 2.5D heterogeneous integration. This section will focus on the key TSV

FIG. 7. Functional schematic of electronic–Photonic Integrated Circuits (PIC) on 2.5D TSI.

fabrication processes in a typical TSV integration flow (including TSV etch, liner oxide deposition, Cu barrier seed layer deposition, Cu electroplating, and Chemical mechanical polishing (CMP)).

First of all, there are many approaches to fabricate TSV. In summary, TSV module fabrication can be classified into three main approaches—TSV via-first (VF), TSV via-middle (VM), and TSV via-last (VL). Each TSV approach is defined by the stage (of a CMOS process flow) at which the TSV module is integrated. For via-first approach, TSV is first developed and fabricated before any device fabrication. For via-middle approach, the fabrication of TSV is done after device (contact) and before back end of line (BEOL) process. For TSV-last approach, the TSV is fabricated after device fabrication and BEOL process. In addition, the integration of the TSV-last approach can be further done in 2 different ways: (1) TSV last integration from the top-side of the wafer and (2) TSV last integration from the backside of the wafer.

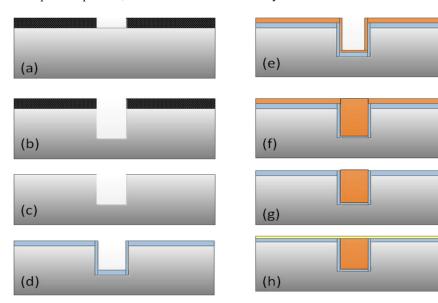

In any case, the main TSV process modules include: (a) TSV mask, (b) TSV etching, (c) TSV Photo Resists (PRS) and we clean, (d) liner oxide deposition, (e) barrier and seed layer, (f) Cu plating, and (g) Cu CMP. A typical TSV fabrication process flow is as illustrated in Figure 8.

TSV etching, liner oxide deposition, barrier layer and Cu seed sputter deposition, Electro-copper-plating (ECP) and Cu CMP will be described in subsequence.

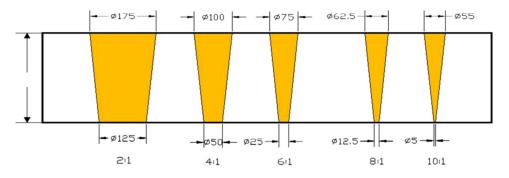

#### 1. TSV deep Si etch process

TSV etching is a forming of high aspect ratio (AR) Si etch process. Deep Si etching (from a few tens of to a few hundreds of  $\mu$ m) is technically more challenging than shallow, low aspect ratio etching in conventional CMOS Si etching process.<sup>24</sup>

As such, high aspect ratio TSV etching faces many challenges. In particular, high etch rate is required for large volume production. Other challenges relating to deep Si etch include the control of sidewall roughness, tilt, sidewall angle, micro-loading, notching, and micro-grass. Currently, a time-multiplexed process, which is more commonly known as

Robert Bosch GmbH's process (BOSCH Process), has become the main TSV etching process adopted by the industry. <sup>25,26</sup>

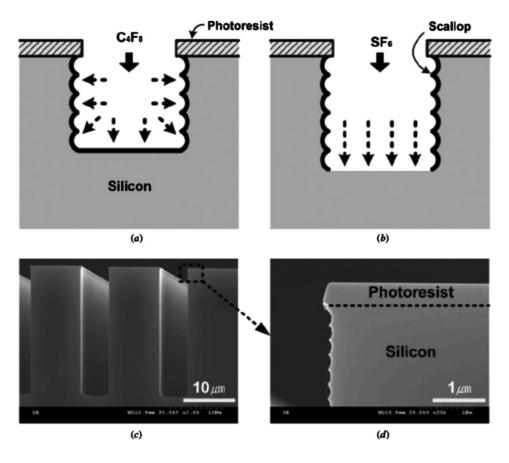

Bosch etch process is performed using a multiple inductively coupled plasma etching system. It is an alternating two-step process, consisting of a polymerization step and a Si etch step. The Si etch step rapidly removes the polymer layer on the bottom of the feature while partially removing the polymer layer on the sidewall, protecting the sidewall. Etch and passivation steps are alternated until the desired etch depth is reached. Typically, SF<sub>6</sub> and O<sub>2</sub> are applied as gas source in the Si etching cycle while C<sub>4</sub>F<sub>8</sub> is applied as polymer generation source during the sidewall passivation cycle. Due to the strong isotropic nature of the SF<sub>6</sub>/O<sub>2</sub> etch chemistry, each etch cycle will form an unwanted sidewall recess known as a scallop. The formation of this unwanted scallop repeats with each etch cycle. The etch mechanism due to SF<sub>6</sub> gases can be explained as follows:<sup>26</sup>

$$SF_6 + e^- \to SF_5^+ + F + 2e^-.$$

(2.1)

Usually, 10% of  $O_2$  is added to help in liberating more fluorine radicals in the plasma reaction between  $SF_6$  and  $O_2$ . Si is then subsequently etched away by the fluorine according to the following reaction:<sup>26</sup>

$$Si (solid) + 4F(gas) \rightarrow SiF_4(gas).$$

(2.2)

During the passivation phase of the BOSCH process, CF<sub>2</sub> is formed from C<sub>4</sub>F<sub>8</sub> as follows:<sup>26</sup>

$$C_4F_8 + e^- \rightarrow C_3F_6 + CF_2 + e^-.$$

(2.3)

CF<sub>2</sub> then adsorbs on the surfaces and forms a Teflon-like polymer according to the reaction<sup>26</sup>

$$nCF_2 \to (CF_2)_n.$$

(2.4)

During the etch phase, the  $CF_2$  molecules are removed by a combination of physical ion sputtering and chemical reactions. The physical component in the Bosch process is contributed by the positively charged  $S_xF_y^+$ , and the chemical etch is mainly due to the F and  $O_2$ , which are generated

FIG. 8. Major process modules in TSV formation. (a) TSV mask lithography, (b) deep Si etch, (c) PRS and wafer cleaning, (d) liner oxide deposition, (e) barrier metal and Cu seed sputtering, (f) Cu ECP, (g) Cu CMP, and (h) TSV capping deposition if needed.

FIG. 9. Schematic of Bosch method: (a) sidewall passivation using C4F8, (b) Si isotropic etching using SF6, (c) SEM images of deep trenches, and (d) magnified SEM image of the sidewall showing nano-scallops.<sup>27</sup>

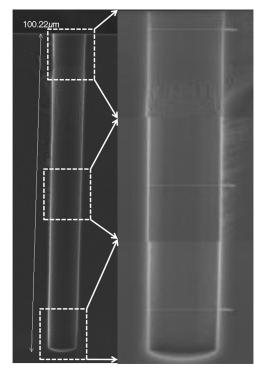

during each etch step. The scallops are due to the isotropic etching mechanism as shown in reaction (2). A schematic of the Bosch etch process is illustrated in Fig. 9.<sup>27,28</sup> Figure 10 shows a 10  $\mu$ m diameter by 100  $\mu$ m depth TSV etch profile obtained via Bosch etch process.

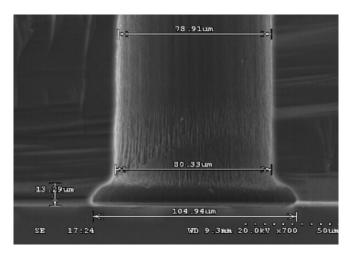

Although Bosch process is able to meet the requirements of a TSV etch, there are still issues associated with the process. Some issues in TSV Bosch etch include micro-loading effect, undercut (also known as over-hang), Si grass, undercut, and notching. Wu et al did a detailed review on the loading effect and Si micro-grass for TSV etching, with corresponding proposed solutions.<sup>27</sup> The undercut issue had been observed more frequently in via-middle scheme<sup>29</sup> and TSV in SOI wafers.<sup>30</sup> Figure 11 shows SEM images of undercut issues in TSV fabrication. Both undercut and scallop will result in liner coverage uniformity issues, barrier metal and Cu seed step coverage issues, which will then cause incomplete TSV filling or leave voids inside TSVs. This effect becomes more pronounced as the TSV diameter gets smaller. On the other hand, notching is normally observed in via-last scheme when the etching gas hits the boundary between Si and the underlying layer, as shown in Figure 12.<sup>27</sup> The reason is charge accumulation that occurs where Si is underlain by a dielectric layer. Increasing the thickness of polymer during over etch by increasing is proposed to prevent notching issue. 31,32 Another method to control notching is to apply intermittent or pulsed bias RF power to cathode. 33,34

The post-etch cleaning of the TSV is a critical process. In particular, the F-containing polymers deposited during the passivation cycle of a Bosch process have to be removed fully before downstream process

# 2. TSV liner deposition

TSV liner deposition is a process that is used to deposit a layer of dielectric film, e.g., typically  $SiO_2$ , along the sidewalls of the deep Si via, and it is used as an electrical

FIG. 10. TSV profile after deep reaction ion etching by using Bosch method. The size of TSV shown in the figure is 10  $\mu$ m in diameter and 100  $\mu$ m in depth, which has been widely accepted for interposer application.

FIG. 11. Undercut issues of TSV etching. (a) Undercut of TSV in SOI wafer, <sup>30</sup> (b) undercut of TSV in viamiddle scheme, <sup>29</sup> and (c) improved etching recipe showing less undercut.

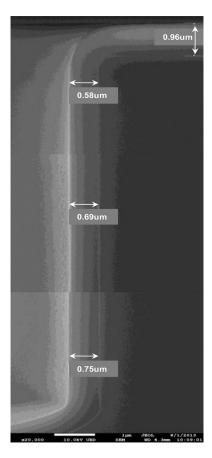

isolation for the TSV structure. It can be done either by using high temperature thermal oxide deposition or by plasma enhanced chemical vapor deposition (PECVD) with the use of silane and tetrathylorthosilicate (TEOS). 35,36 There is wide application of Sub-atmospheric CVD (SACVD) of Ozone (O3)-TEOS as liner in TSV formation. 37-39 Different TSV approaches have different requirements. But the basic requirement that is expected for liner deposition is good step coverage for the TSV insulation from the Si substrate. Thermal oxide is used in the TSV first approach because high temperature process will not have any effect on the active devices since the TSV is fabricated before the front end of line (FEOL) process. SACVD oxide is commonly used in the TSV middle and via last from top-side approach because the active devices are fabricated before the TSV integration. High liner deposition temperature can affect the performances of the active devices in via middle approach and the BEOL in the TSV last from top-side approach. The type of pre-cursor that is more commonly used in the SACVD process for the TSV middle and TSV last from top integration is TEOS. The reason being that using TEOS (as the pre-cursor) will give a better SiO<sub>2</sub> step coverage than silane (as the pre-cursor) in the PECVD process. Low temperature (<250 °C) TEOS-PECVD is normally used in the TSV VL from backside approach due to the thermal budget limitation of the type of bonding material used. SEM images of TSV liner oxide at different depth are shown in Figure 13, and Table I summarizes the liner oxide step coverage (SC) at various TSV depths and wafer locations.

FIG. 12. Notching observed at the interface between Si and SiO<sub>2</sub> layer.<sup>27</sup>

# 3. Seed layer and barrier layer deposition

Next key process after liner deposition in TSV fabrication is the barrier and seed layer deposition. The purpose of the barrier layer is to prevent any copper (Cu) diffusion from the TSV into the Si during any subsequent high temperature process. The deposition of the barrier and seed layer is normally carried out using a chemical or physical vapor deposition (CVD or PVD). CVD-based process technology (e.g., metal organic chemical vapor deposition (MOCVD)) can cater for barrier and seed deposition in very high aspect ratio (>15:1) TSVs but incurs higher cost and is not the mainstream process in the industry. Conventional PVD process is less costly but poses more limitations with respect to step coverage on the TSV side wall. Improvements in PVD equipment have extended the process window for PVD barrier and Cu seed layer deposition. TSV Tantalum (Ta) and Ti

FIG. 13. SEM images of O3-TEOS liner oxide for a TSV with the diameter of 10  $\mu m$  and depth of 100  $\mu m$ .

TABLE I. Summary of the liner thickness in various TSV depths and die locations.

| Die location | Field (μm) | Invia field (0.21 μm) | Top sidewall (μm) | SC (%) | Middle sidewall (μm) | SC (%) | Bottom sidewall (μm) | SC (%) | Bottom (µm) | SC (%) |

|--------------|------------|-----------------------|-------------------|--------|----------------------|--------|----------------------|--------|-------------|--------|

| Bottom       | 0.95       | 0.74                  | 0.62              | 83.8   | 0.69                 | 93.2   | 0.77                 | 104.1  | 0.75        | 101.4  |

| Center       | 0.98       | 0.77                  | 0.58              | 75.3   | 0.73                 | 94.8   | 0.73                 | 94.8   | 0.71        | 92.2   |

| Edge         | 0.92       | 0.71                  | 0.62              | 87.3   | 0.69                 | 97.2   | 0.74                 | 104.2  | 0.73        | 102.8  |

| Left         | 0.93       | 0.72                  | 0.6               | 83.3   | 0.68                 | 94.4   | 0.75                 | 104.2  | 0.73        | 101.4  |

| Middle       | 0.96       | 0.75                  | 0.58              | 77.3   | 0.69                 | 92.0   | 0.75                 | 100.0  | 0.75        | 100.0  |

| Тор          | 0.92       | 0.71                  | 0.64              | 90.1   | 0.73                 | 102.8  | 0.78                 | 109.9  | 0.78        | 109.9  |

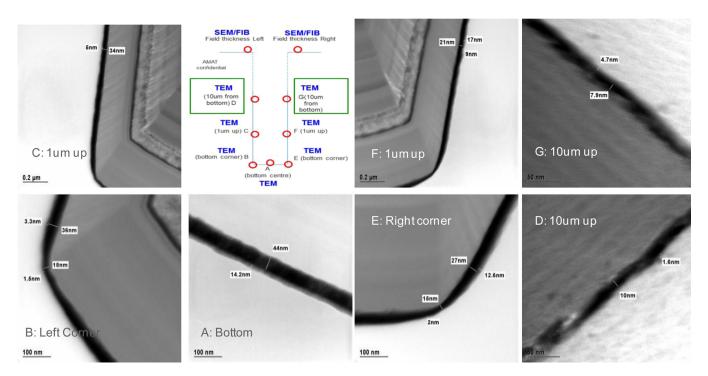

are prevalent barrier metals used. These barrier layers also have the function of improving the adhesion between TSV Cu and the liner dielectric. After barrier deposition, Cu seed is sputtered in a separate chamber. Ar plasma is first applied to the metal target that is used for sputtering. The metal atom is then dislodged from the metal target and deposited onto the bottom wafer surface to form the metal film. SEM images of a PVD barrier metal and Cu seed at various depth in a  $10~\mu m \times 100~\mu m$  TSV are shown in Figure 14.

The continuity of barrier metal and Cu seed is the basic and most essential requirement of the PVD process. As shown in Figure 14, the barrier metal and Cu seed fully covers the side-walls surface within the TSV. Ti step coverage can achieve 0.63%–5.97% at different depth of TSV. PVD Cu has better step coverage compared with Ti. Typical step coverage of Cu is about 1.06%–6.03% in a  $10~\mu m \times 100~\mu m$  TSV.

## 4. ECP

ECP process is another important process step in the fabrication of a TSV. The purpose of this step is to fill up the deep Si etched TSV with either copper or other types of

conducting materials (aluminum or tungsten) for the TSV. Via plating defects can have various negative effects on the TSV interconnect properties and subsequent TSV processes. Voids in the TSV fill can cause variations in via resistance, or even electrically open-circuit connections.

ECP is a plating process in which metal ions in a solution is moved by an electric field to coat an electrode. <sup>41</sup> ECP can be done using either by conformal or bottom-up deposition methods, and that will depend on the types of chemistry and electroplating conditions that are used. Conformal Cu deposition for the TSV is fast but will result in a high Cu overburden in the field region and a potential high risk of voids in the TSV. On the other hand, bottom up plating method has lower risk of void formation, and there will be less Cu overburden even though the process time is long. A TSV ECP process encompasses a combination of both conformal and bottom-up methods.

The ECP bath chemistry plays an important role in the TSV filling process. The presence of organic additives in the bath chemistry has strong influence on the Cu deposition process. In summary, there are three main types of organic additives applied to optimize the process of TSV filling—suppressor, accelerator, and leveler. Suppressor is a long

FIG. 14. SEM images of Ti and Cu as barrier and seed layer for  $10 \, \mu m \times 100 \, \mu m$  TSV.

FIG. 15. Cu filling process to form a void-free TSV. (a) Initial stage, (b) intermediate stage, (c) final stage, and (d) void-free Cu filling and the image of actual TSV after Cu filling.

chain polymer and is usually used to coat the Cu surface to create a "blocking layer" during Cu deposition. Accelerator is a catalyst that is used during the Cu deposition process to increase the Cu deposition rate. A leveler is applied to deactivate the effect of the accelerator. 41

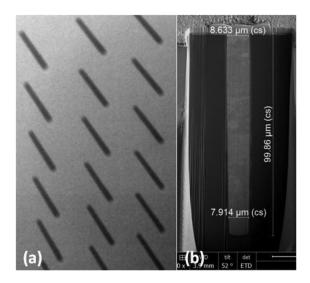

Nowadays, the TSVs are mostly filled with Cu by ECP process. This step is considered as the most critical step for TSV formation, because it determines if the Cu filling is successful. If there are any issues in the process, Cu filling defects, also known as voids, will be observed inside the TSVs. Figure 15 shows the conventional model of bottom up filling for void-free TSV Cu filling when all processes are controlled well. 42 Choi et al. 42 and Malta et al. 43 have studied and investigated the mechanism of failure and defect generation of TSV filling during ECP process, to realize a low-cost 3D IC based on the TSV. X-ray is a non-destructive method employed to inspect for voids in TSVs. Figure 16 shows x-ray and X-SEM images of TSV with 10 μm in diameter and 100 µm in depth. Throughput and Cu overburden reduction remain as key challenges to be addressed for cost saving.44 A thick Cu overburden will not only affect overall throughput but also cause failures due to the serious warpage. In the case of a  $10 \times 100 \mu m$  TSV, a well-optimized TSV Cu filling process by electroplating should typically have a Cu overburden thickness of below  $4 \mu m$ . In addition, because the Cu overburden thickness depends on the TSV dimensions, it can be much thicker for bigger dimensions of TSV applications.

FIG. 16. X-ray (a) and X-SEM images (b) of  $10\,\mu\mathrm{m}\times100\,\mu\mathrm{m}$  TSV after ECP.

#### 5. CMP

After the ECP process of the TSV, CMP has to be carried out to remove any Cu overburden and Cu mounts that have occurred during the ECP process. 45,46 The Cu TSV will have to be exposed by using a CMP process in order to proceed with further process integration.

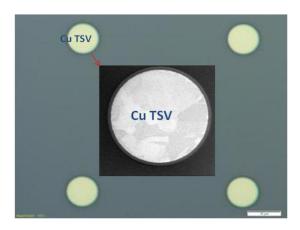

Conventional Cu CMOS process needs to go through a high temperature annealing step before Cu CMP in order to achieve Cu grain stability. Because most of TSV wafers have thicker Cu overburden, e.g.,  $>4 \mu m$ , two-step Cu CMP process are employed for surface planarization. Higher Cu overburden will cause wafer to have a higher warpage after TSV Cu CMP. The first copper CMP process is carried out right after copper ECP process, the wafer is then sent for Cu annealing, followed by a second Cu CMP process to remove the remaining Cu protrusion and Cu annealing defects. The mechanisms involve in the CMP process of different types of metals are relatively simple. In general, an oxide of the metal is chemically formed on the metal film surface. It is then removed mechanically with abrasives in the CMP slurry. 46 A hybrid e-CMP/CMP has been proposed by Takeda and coworkers<sup>47</sup> and applied for Cu TSV CMP, and this method shows higher Cu removal rate as well as minimum dishing of 100 nm for TSVs with 100  $\mu$ m diameters. Figure 17 shows typical images of TSV after CMP process.

#### B. BEOL and RDL scheme

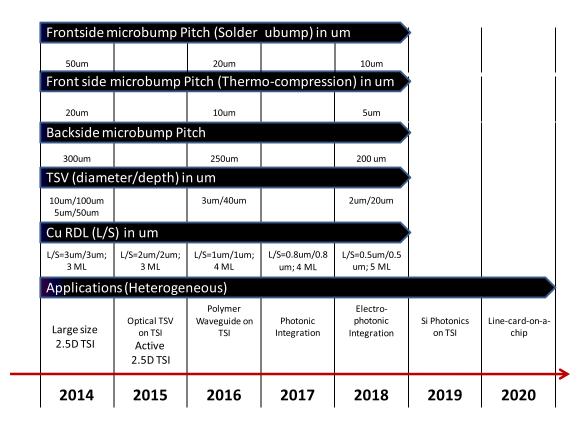

For fine pitch and high density TSV interposer, industry is looking at multiple interconnect layers on the interposer front side with less than 5  $\mu$ m/5  $\mu$ m L/S and via diameter

FIG. 17. Optical inspection and SEM inspection (inset) results of  $10~\mu m \times 100~\mu m$  TSV after CMP process.

less than  $10 \, \mu m$ . To achieve fine pitch Cu routing in through Si interposer, the main stream technology adopted is foundry-based BEOL process. <sup>48</sup> BEOL fabrication is based on single or dual Cu damascene process with inorganic dielectric materials, e.g., SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, or low-K materials. In damascene process, the underlying dielectric insulator material is patterned and etched with open trenches and vias and a thick layer of Cu is deposited to overfill the etched structures. CMP is then used to remove the Cu overburden leaving Cu filled in the trenches. Cu remaining in the trench forms the conducting traces.

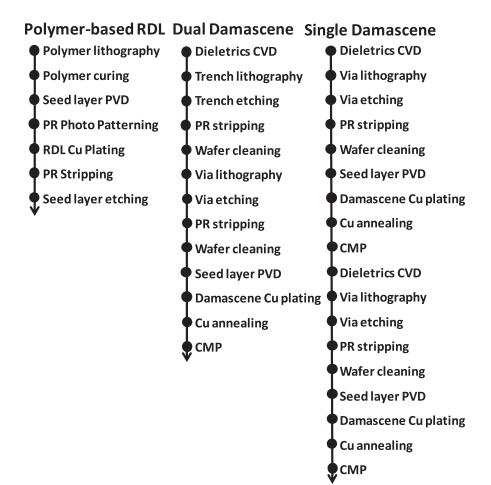

Compared to damascene process, polymer-based Cu RDL process offers lower cost interconnect solution, since it avoids deep ultraviolet (DUV) lithography, plasma etching, and CMP process. The RDL process involved using a semiadditive process to form Cu conducting traces and photo-pattern-able polymer materials are used as the dielectric insulating layer. The contact via opening can be formed directly in the polymer material by photo-lithography and developing the material away. Polymer-based Cu RDL process offers a cost effective interconnect solution, since it avoids DUV lithography, plasma etching, and CMP process. As shown in Figure 18,<sup>49</sup> process step count of polymer-based RDL is reduced by ~45% as compared with dual-damascene process, and  $\sim$ 60% as compared with single damascene process. However, current polymer-based Cu RDL processes are normally coarse in terms of L/S and photo-lithography resolution of photo-dielectric materials are often very poor in achieving very small contact via opening. Fine-pitch polymer-based RDL process is becoming more in demand under the pressure of cost reduction of 2.5D interposer and 3D-IC.

RDL process is a standard process in the packaging area. <sup>50,51</sup> IME has been developing RDL process for packaging application with wider dimension. <sup>52</sup> Later, low temperature damascene interconnect has been developed for 3D interconnect. <sup>53</sup> Shrinkage of RDL has become a popular topic of interest recently. Spin-on photo-dielectric based Cu RDL integrated with TSV interposer was reported with 4  $\mu$ m/4  $\mu$ m line/space (L/S) and 10  $\mu$ m in via diameter by Kumagai et al., <sup>50</sup> and Ho et al. reported 2  $\mu$ m/2  $\mu$ m L/S RDL with 2  $\mu$ m polymer via diameter. <sup>49</sup> Taiwan Semiconductor Manufacturing Company, Limited (TSMC) reported 0.8- $\mu$ m/0.8- $\mu$ m L/S RDL in VLSI 2014. <sup>54</sup> The shrinkage of RDL has become an important research direction in the foundry for cost reduction in TSI application.

$2 \,\mu \text{m}/2 \,\mu \text{m}$  line/space (L/S) RDL was developed and characterized in Ref. 49. Figure 19 shows the cross-section of 2 layers polymer-based RDL meander (a) and daisy chain (b) and (c) structures fabricated on Si wafer. Metal 1 layer consists of  $2 \,\mu \text{m}/2 \,\mu \text{m}$  L/S Cu traces fabricated using the semi-additive process. Metal 2 layers consist of  $2.5 \,\mu \text{m}$  line width Cu trace with  $1.5 \,\mu \text{m}/1.5 \,\mu \text{m}$  line/space in Figure 19(a). The 2 layers are insulated by polymer-based dielectric material. The spin-on polymer-based material shows good gap-filling capability with no voids observed in between the line space. The daisy chain consists of metal 1 and 2 with

FIG. 18. Comparison of process steps of different Cu wiring processes, i.e., polymer-based RDL, dual damascene, and single damascene.

FIG. 19. Cross-section of (a) 2 layer fine pitch RDL meander, (b) daisy chain structures, and (c) enlarged view of via.

vias connecting the 2 metal layers in Figure 19(b). The contact via is enlarged and shown in Figure 19(c) that has a tapered slope profile. The top opening diameter for the contact via is  $\sim 3.2 \, \mu \text{m}$ , and the bottom diameter is  $\sim 1.8 \, \mu \text{m}$ . The tapered slope via sidewall is preferred in RDL processing as it allows better step coverage of the PVD seed layer.

#### C. Bumping

# 1. Solder bumping and Cu pillar bumps

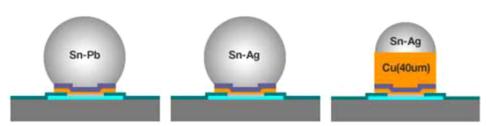

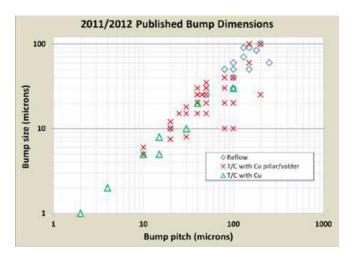

Solder bumping technology (the process of joining a chip to a substrate without shorting using solder) is first conceived and implemented by IBM in the early 1960s. Fine pitch solder micro-bumps are one of the key elements to form high density interconnections on a through Si interposer or functional dies. To meet Tera-scale computing needs and to reduce power consumption for next generation information devices, short and high density interconnections between high-capacity memory chips and microprocessor unit are required. 55–57 In order to achieve interconnections with low resistance, most frequently solder micro-bumps are made up of Cu and a solder cap, i.e., Cu pillar bumps. Figure 20 shows the evolution map of Cu pillar bumps. Table II below shows summarization of bumping technology for chip to chip interconnects in terms of scaling and bonding technology.

As compared to solder bumps, the pillar bumps are more rigid and thus allow assembly with only a small solder volume on top of pillars. This results in two benefits: (1) the standoff can be kept high even with very fine pitch, and (2) the solder will not spread out much on wettable surfaces Nowadays, fine pitch Cu pillar bumps are applicable in various packaging technologies, from wire bonded chip stacking to chip stacking with TSVs, from system in package (SiP) to 3D IC integration. As a result, Cu pillar bumping technology has attracted intensive attentions. As to the assembly, different metallurgical bonding processes have been developed, such as solid-liquid-inter diffusion method.<sup>58</sup> and thermal compression method.<sup>59,60</sup> In IBM, Wright *et al.* developed

solder micro bumping technology.<sup>61</sup> Different solder materials, such as e-PbSn and CuSn systems, have been studied.

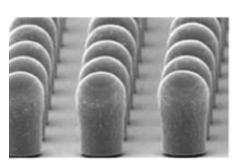

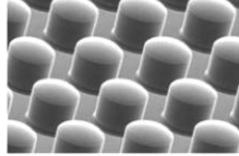

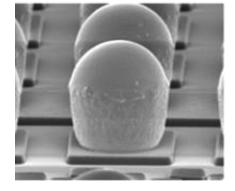

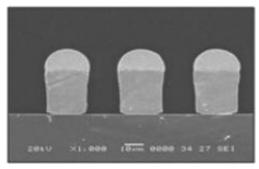

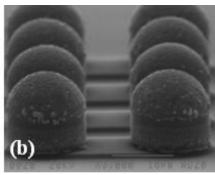

Fine-pitch Cu pillar bumps have replaced conventional flip chip solder bumps driven by the need for extremely low profile and high connectivity interconnects. Devices, such as high-end processors, graphics, FPGAs, power amplifiers, MEMS, and High brightness light emitting diode (HB-LED), have incorporated fine-pitch Cu pillar bumps and demonstrated the range of the technology. Figure 21 shows four SEM images of 40  $\mu$ m pitch copper pillar bumps capped with SnAg solder. The SnAg solder reflows to join the die to the Si interposer. Sub-40  $\mu$ m pitch has also been demonstrated.

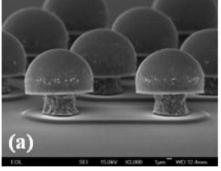

#### 2. Bumps in 2.5D TSI package

To support high speed data transfer and preserve signal integrity between dies, a very fine-geometry circuit board and enabling interconnect solution is required. TSIs and finepitch Cu pillar bumps are two representative technologies that have played an integral role in defining the 2.5D package approach. Figure 22 shows the schematic of a typical 2.5D TSI system with two-die side-by-side integration. Interposer inclusion defines the 2.5D approach. It routes thousands of interconnections between the devices. IC1 and IC2 can also serve as TSV-enabled 3D stacks. As shown in Fig. 21, Cu pillar microbumps provide short, low inductance, efficient interconnections (a) between ICs in vertical stacks as well as (b) between and IC and the through Si interposer. Together, the micro-bumps and Si interposer provide a highspeed and high-bandwidth communication high way for side-by-side die (and stack) placement. The interposer bottom fans out to wider pitches that employ conventional solder bumps for connection onto the ball grid array (BGA) substrate.

#### 3. Fabrication of Cu pillar micro-bumps

The structure and production process of a pillar bump are very similar to an electro-plated solder bump.

FIG. 20. Evolution map of Cu pillar bumps by Samsung.

TABLE II. Scaling of chip-to-chip interconnect.

| Bonding Method                           | C4 FC (Contolled<br>Collapse Chip<br>Connect) | C2 FC<br>(Chip Connect)                   | TC/LR (Local<br>Reflow) FC               | TC FC                      |

|------------------------------------------|-----------------------------------------------|-------------------------------------------|------------------------------------------|----------------------------|

| Schematic Diagram                        |                                               |                                           | E                                        |                            |

| Major Bump Pitch Range at<br>Application | > 130 um                                      | 140 um ~ 60 um                            | 80 um ~ 20 um                            | < 30 um                    |

| Bonding Method                           | Conventional<br>Reflow                        | Reflow with Cu<br>pillar                  | Thermal<br>Compression<br>with Cu pillar | Thermal<br>Compression     |

| Bump Metallurgy                          | Solder (SnAg or<br>SnAgCu)                    | Cu + Solder<br>(SnAg or Sn)               | Cu + Solder<br>(SnAg or Sn)<br>Cap       | Cu                         |

| Bump Collapse                            | Yes                                           | No                                        | No                                       | No                         |

| Underfill Method                         | - Capillary<br>- No flow                      | - Capillary<br>- No flow<br>- Wafer Level | - No flow<br>- Wafer Level               | - No flow<br>- Wafer Level |

- A thin sputtered adhesion layer (e.g., Ti or TiW) covers the chip pad and overlaps onto the chip passivation.

- A sputtered conductive plating base (Cu) is required as a 2nd layer for the subsequent deposition steps.

- A barrier layer (e.g., Ni or Cu) is electroplated to prevent inter diffusion of solder and pad. In the case of a pillar bump, this layer is extended to a tall pillar of several  $10 \, \mu \mathrm{m}$  height.

- Solder (e.g., lead-free SnAg) is plated on top of the barrier or pillar and reflowed to form a solder bump or cap.

In the case of a solder bump, the standoff between chip and substrate, on which the bumps are soldered, is determined by the controlled collapse of the large solder volume. The surface tension of the molten solder keeps the chip at a distance during flip chip assembly. A solder mask around the substrate pads and the non-wettable chip passivation prevents the solder from spreading out indefinitely. One major benefit of collapsible bumps during reflow is that the formation of the flip chip bonds is very robust and highly tolerant to bump height variations. The pillar bumps, on the other hand, are more rigid and thus allow assembly with only a small solder volume on top of the pillars, which has two clear benefits, i.e., (1) the standoff can be kept high, even at very fine pitch, and (2) the solder will not spread out much on wettable surfaces, even without a solder mask barrier, due to the restricted solder volume. The main drawback of the

FIG. 21. SEM images of Cu pillar bumps.

FIG. 22. Schematic of a typical 2.5D TSI system with two-die side-by-side integration.

reduced collapse of the small solder cap is that it requires tighter bump co-planarity control to prevent non-wetting of shorter bumps.

A tall Cu pillar offers additional advantages: thermal and electrical conductivity are higher than in a solder ball of similar size. Even more importantly, electro-migration (EM) reliability performance is much better in a Cu pillar where current crowding at the corner between chip and pad and bumps is located within higher EM-resistance bulk Cu instead of low-melting solder. A thin under bump metallurgy (UBM) in a solder bump cannot prevent high current densities at bump corner caused by current crowding. This leads to EM induced voids at the UBM/solder interface, which finally causes an open interconnect after high-current stress. The solder cap of the pillar bump makes it possible to use identical assembly process, assembly materials, and assembly equipment as for a solder bump of the same material.

<50  $\mu$ m pitch Cu pillar bumps are reported by several organizations. ME reported their studies on fine-pitch (40  $\mu$ m) Cu pillar process integration and proposed a combined of wet and dry etching of seed layer removal method to reduce the Cu pillar undercut issue. MEC reported on 10  $\mu$ m electroplated CuSn micro-bumps with 20  $\mu$ m pitch in 2011. With further scaling down of Cu pillar bump diameter, seed layer etching was found to be a more and more important processing parameter to form finer pitch Cu pillar bumps. The seed etch process is compared between Ti/Cu and TiW/Cu seed layers. During Ti etch, the etch rate dropped when the Al measurement pads are exposed. In

order to remove the Ti layer between bumps to prevent shorts, the etch time needed to be increased, resulting in a non-uniform attach of Al measurement pads due to severe galvanic effect. With a TiW/Cu seed, no damage on the Al probing pads is observed. In addition, the TiW/Cu based bumps has no undercut, while on the Ti/Cu bump at each side more than 1  $\mu$ m undercut was observed. TiW was concluded as the preferred seed layer for fine-pitch Cu pillar bump. Based on the yield of the daisy chains, a defective density of the bumps below 50 ppm is predicted. ITRI reported results on their 12  $\mu$ m micro-bumps (5  $\mu$ m Cu/3  $\mu$ m Ni/2.5  $\mu$ m SnAg) with 20  $\mu$ m pitch.<sup>70</sup> Severe undercut caused by seed layer etching process is also found. Figure 23 shows the typical undercut of Cu pillar bump and the improved process for minimizing the undercut. 70 Huang et al. reported that the reduction of Cu seed layer thickness from 5000 Å to 2000 Å and a dry etching process have been found to improve the undercut performance. 70 Cu pillar bumps with sub-20  $\mu$ m pitch have also been reported by IME (15  $\mu$ m pitch)<sup>66</sup> and Tohoku University (10  $\mu$ m pitch).<sup>67</sup> For IME's 15 μm pitch Cu pillar bumps, traditional electrochemical plating is used to deposit the Cu and Sn sequentially followed by photo resist stripping and seed layer etching which was carried out by a combination of wet Cu etching and dry Ta etching. Tohoku University reported an electroplatedevaporation bumping (EEB) technology to form 10 µm pitch Cu pillar bumps, which is a combination of Cu electroplating and Sn evaporation. Resistance of Cu/Sn bump was measured to be 35 m $\Omega$ /bump.

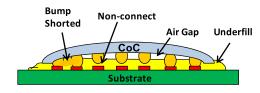

#### 4. Reliability assessment of Cu pillar bumps

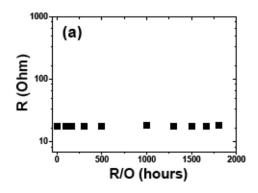

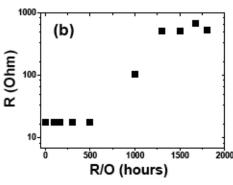

Samsung did high temperature storage (HTS) test for Cu pillar bumps with 20  $\mu$ m in diameter and found that Ni<sub>3</sub>Sn<sub>4</sub> intermetallic compound (IMC) formations at interface between SnAg solder and their 4  $\mu$ m Ni UBM degrade the mechanical properties of solder joint and increase resistance of solder bump. <sup>71</sup> IMC growth rate and Ni UBM dissolution rate are calculated. The IMC changes into thick IMC during HTS as shown below in the SEM images. As shown in Figure 24, <sup>71</sup> thin IMC changes into thick IMC during High Storage Temperature (HST). During 150 °C HST, Ni UBM is converted into Ni<sub>3</sub>Sn<sub>4</sub> IMC, but resistance of the microbumps remains unchanged. Resistance started to degrade after 1000 h at 180 °C storage due to void formation at interface between IMC and Al trace line, resulting in open failure upon complete consumption of Ni UBM. Figure 25 presents

FIG. 23. Cu pillar bumps (a) with severe Cu post undercut and (b) fabricated with optimized process having minimized Cu post undercut.

FIG. 24. SEM images of solder joints (a) as reflow condition, (b) HTS 150 °C for 1300 h, and (c) 180 °C for 1300 h.

the resistance evolution with time during HTS test at 150 °C and 180 °C, respectively.

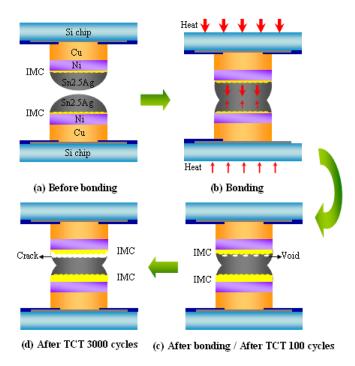

ITRI has also studied the failure mechanism of  $20 \, \mu m$ pitch using thermal cycling (TC) test.<sup>70</sup> The IMC formed at the interface is identified as Ni<sub>3</sub>Sn<sub>4</sub>. The IMC thickness is also found to increase with time and/or temperature, which is consistent with the results reported by Samsung. Ni normally functions as a diffusion barrier to inhibit the reaction of Sn and Cu having very low solubility in Sn. During the bonding process, the bottom interposer is at 100 °C, and the top chip is at 280 °C to melt SnAg solder alloy. It is concluded that the bonding temperature drives Ni atoms to dissolve into the melted solder and saturates the Sn matrix. As Ni has higher density than that of Sn, gravity segregation occurs and causes the Ni atoms to accumulate at the interface and result in the thicker Ni<sub>3</sub>Sn<sub>4</sub> formation. It is proposed that the failure mechanism of the micro-joints, as shown in Figure 26, is due to a Sn depletion zone which forms at the interface between Ni layer and Sn solder of the top chip due to the consumption of Sn. Eventually, the crack propagated along the interface and then the micro-joint fails when stress induced by Z-axial expansion of underfill is exerted on the interface.

EM is the migration of metal in the direction of electron flow which results in void formation at the electrons entrance (or current exit, I-) and metal pile-up at the electrons exit (or current entrance, I+). Since void formation is the most detrimental effect of EM, the current exit I- is the most critical interface. While there have been many EM studies of  $100 \, \mu m$  and larger bumps, there are not many studies on fine pitch Cu pillar bumps, especially below  $20 \, \mu m$  size. It was found that with good Ni barrier structures, CuSn bumps may have EM

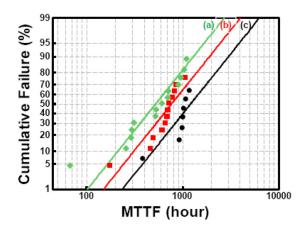

lifetimes similar to or greater than eutectic PbSn bumps.  $^{54,61}$  Samsung reported EM accelerated life time assessment for Cu pillar bumps. Figure 27 shows the microstructure of microbumps with  $6.4 \times 10^4$  A/cm² current stressing and without current stressing for 624 h at  $150\,^{\circ}$ C.  $^{71}$  In Figure 27, polarity effect was observed. During current stressing, the migration direction of Ni is the same as the electron flow, so Ni UBM at cathode side was consumed. Also migrated Ni from cathode to anode enhances IMC growth at anode. It is calculated based on memory device application conditions of  $105\,^{\circ}$ C. The EM life time of Cu pillar bump with Ni UBM achieved more than 100 years based on 0.1% EM failure, as shown in Figure 28.

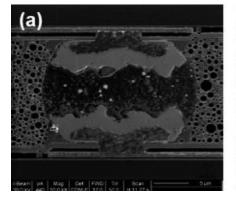

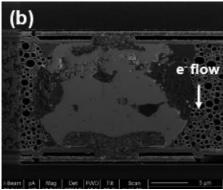

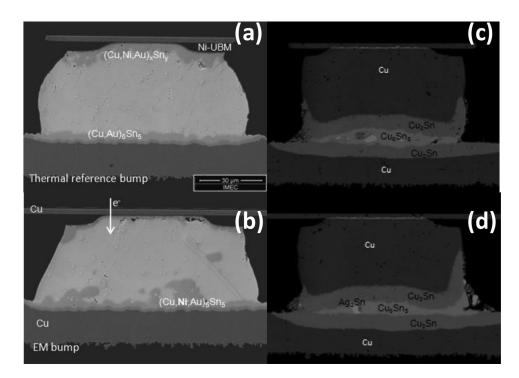

IMEC has studied on the EM performance comparison between solder flip chip bumps (thin layer of Ni/Au UBM and a SAC solder) and Cu pillar bumps (40 µm Cu pillar with 20  $\mu$ m SnAg cap) with same diameter, i.e., 60  $\mu$ m. <sup>72</sup> A clear difference in EM behavior was observed between standard NiAu/SAC and Cu pillar bumps. Figure 29 shows SEM images of solder bumps under thermal stress without and with EM stress for both standard solder bump and Cu pillar bump. 72 Standard bumps with Ni/Au UBM show a consistent failure mechanism of micro-structural degradation through void formation at the interface of solder and IMC, and this occurs for all test conditions used (150-170 °C and 300-500 mA). However, Cu pillar bumps did not show any electrical, nor micro-structural degradation. It was concluded that less current crowding for Cu pillar bumps was expected that that of solder bumps, which causes less local EM damage. The other reason of the outstanding EM performance of Cu pillar bumps is its faster formation of a full intermetallic phase. As soon as all solder materials is transferred into

FIG. 25. Resistance as a function of storage time during HTS test at (a) 150 °C and (b) 180 °C.

FIG. 26. Schematic diagrams of the failure mechanism of micro-joint. (a) Before bonding, (b) bonding, (c) after bonding/after TCT 100 cycles, and (d) after TCT 3000 cycles.

intermetallic phase, the joint is no longer expected to fail at reasonable testing conditions which are compatible with packaging materials.

#### D. Thin wafer handling

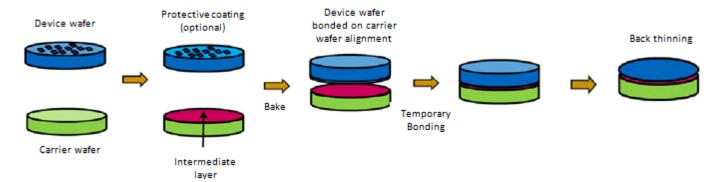

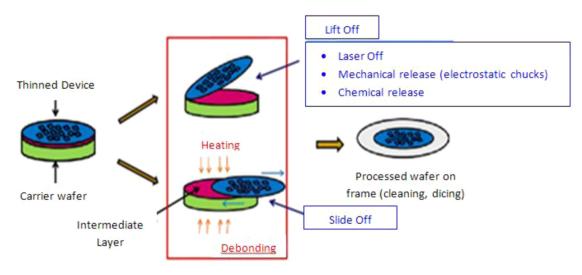

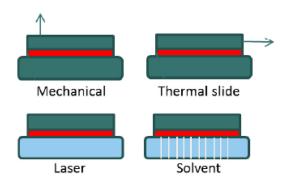

TSVs are continuously being scaled down for various benefits. These benefits include higher I/O densities, smaller form factor, reduced process cost, and smaller keep-out-zones (KOZ) for logic devices. TSV dimensions indirectly determine the thickness of an interposer. However, as TSV dimensions are scaled downwards (in particular TSV depth), wafer handling becomes an issue. For wafer thickness below 100  $\mu$ m, warpage becomes an issue without any support. As such, the device wafer would have to be temporary supported on tape or on a carrier wafer by means of adhesives. <sup>73,74</sup> Figures 30 and 31 illustrate a typical bonding and debonding process, respectively.

In summary, thin-wafer handling can be simplified into different categories based on (1) type of carrier and handling wafer and (2) bonding and debonding mechanisms.<sup>52,53</sup>

FIG. 28. Log-normal distribution of EM failure at 150 °C under various current densities of (a)  $6.4 \times 10^4 \,\text{A/cm}^2$ , (b)  $5.6 \times 10^4 \,\text{A/cm}^2$ , and (c)  $5.1 \times 10^4 \,\text{A/cm}^2$ .

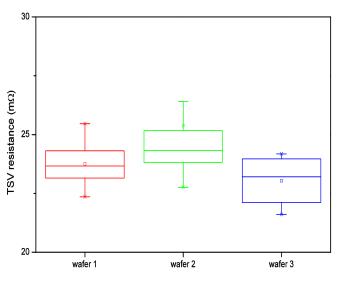

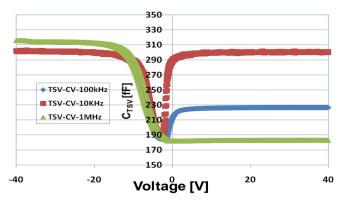

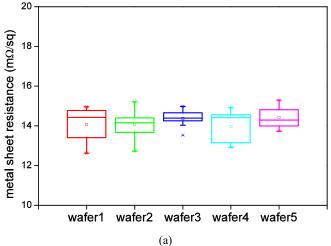

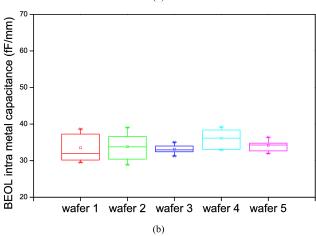

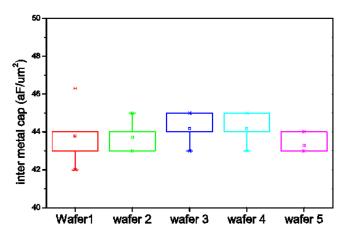

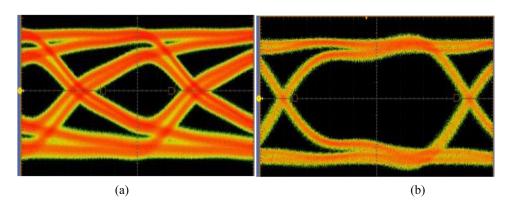

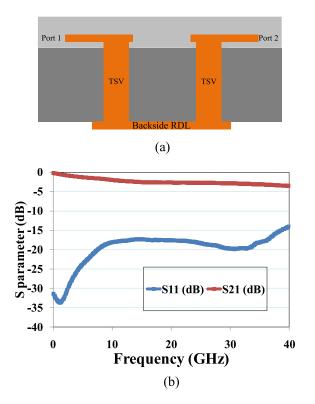

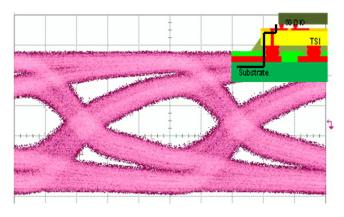

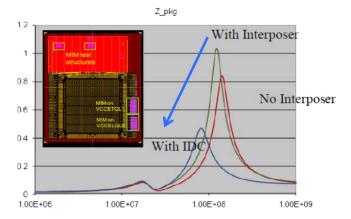

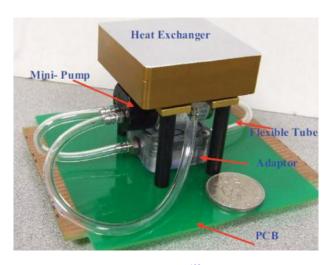

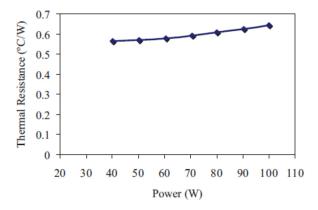

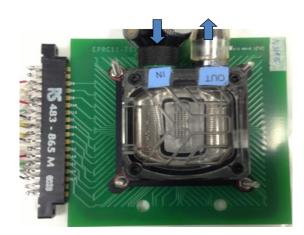

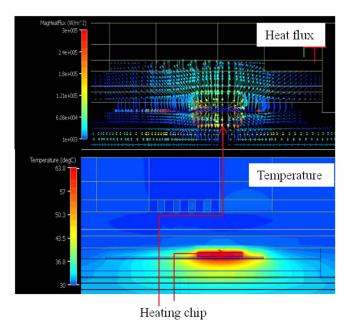

#### 1. Carrier substrates