# 10 kV SiC MOSFET Power Module with Reduce Common-Mode Noise and Electric Field

Christina M. DiMarino, *Member, IEEE*, Bassem Mouawad, C. Mark Johnson, *Member, IEEE*, Dushan Boroyevich, *Fellow, IEEE*, Rolando Burgos, *Member, IEEE*

Abstract- The advancement of silicon carbide (SiC) power devices with voltage ratings exceeding 10 kV is expected to revolutionize medium- and high-voltage systems. However, present power module packages are limiting the performance of these unique switches. The objective of this research is to push the boundaries of high-density, high-speed, 10 kV power module packaging. The proposed package addresses the well-known electromagnetic and thermal challenges, as well as the more recent and prominent electrostatic and electromagnetic interference (EMI) issues associated with high-speed, 10 kV devices. The high-speed switching and high voltage rating of these devices causes significant EMI and high electric field. Existing power module packages are unable to address these challenges, resulting in detrimental EMI and partial discharge that limit the converter operation. This paper presents the design and testing of a 10 kV SiC MOSFET power module that switches at a record 250 V/ns without compromising the signal and ground integrity due to an integrated screen reduces the common-mode current by ten times. This screen connection simultaneously increases the partial discharge inception voltage by more than 50 %. With the integrated cooling system, the power module prototype achieves a power density of 4 W/mm3.1

#### I. INTRODUCTION

Wide-bandgap (WBG) semiconductors, such as silicon carbide (SiC), have demonstrated improved efficiency, reduced size and weight, and lower system cost compared to silicon [1],[2],[3],[4],[5]. SiC semiconductors have also demonstrated superior high-voltage capability [3],[4],[6]. While silicon devices have proven reliability and ruggedness, they have limited voltage ratings (typically 6.5 kV or less), thus requiring complex series connection of devices or multilevel converter topologies [7]. Moreover, medium-voltage silicon devices have slow switching speeds, which constrain the efficiency and switching frequency of the power converter [8],[9].

10 kV SiC MOSFETs are of great interest due to their high blocking voltage, fast switching speed, simple drivability, reverse conduction capability, and moderate on-state losses. These features can increase the efficiency, reliability, and switching frequency, and reduce the complexity, siweight of medium- and high-voltage power consystems [10],[11]. Applications include electric ship traction [9],[13], data center distribution, direct renintegration [14], fast charging stations [15], HVDC [ FACTS [17],[18], and transformer-less intelligent substations [11],[14],[19],[20],[21].

Due to the vast possibilities for ≥10 kV SiC devices resources have been devoted to their development. The majority of the reports on these devices have been on the characterization [6],[11],[19],[22],[23],[24], gate design [25],[26],[27],[28], and converter evaluation [11],[24],[29]. However, the packaging of the semicodies has a significant impact on the performance, currently hindering their switching speed, voltage current rating, and operating temperature. It is nontrolled a suitable package for 10 kV SiC MOSFI addition to the well-known electromagnetic and challenges associated with packaging WBG devices, to voltage rating creates new and more prominent elect and electromagnetic interference (EMI) issues, which addressed to utilize the full capabilities of these devices

The first-generation 10 kV SiC MOSFETs were ass into a power module using a modified 6.5 kV silicon package [30]. Upon analysis and testing of the power it was found that the parasitic inductances and capar were large and unbalanced [31], limiting the diperformance and causing significant EMI. An impackage for third-generation 10 kV SiC MOSFET presented in [32]. This package has lower and symmetrical parasitic inductances [32], though improvement in the EMI is unknown.

EMI arises from the voltage and current transcruring during operation of the switching cell, and conducted through the electrical connections, or radiate the surrounding space. Typically, filters are added to the EMI; however, these increase the cost, size complexity of the power conversion system. Addin external filters diminishes the power density and sir benefits gained by using 10 kV SiC MOSFETs.

In particular, conducted common-mode (CM) noi major issue with high-speed devices. CM noise is cau the high-dv/dt switching of the semiconductor devices causes current to flow through the parasitic capac These capacitances exist in the power module and a circuitry, such as the gate driver isolation. The latter h

This work was supported in part by the UK Engineering and Physical Sciences Research Council (EPSRC) under grant EP/K035304/1 and the CPES High Density Integration Consortium.

C. DiMarino, D. Boroyevich, and R. Burgos are with Virginia Tech, Blacksburg, VA 24061 USA (e-mail: dimaricm@vt.edu, dushan@vt.edu, rolando@vt.edu).

B. Mouawad and C. M. Johnson are with the University of Nottingham, Nottingham NG7 2RD UK (e-mail: bassem.mouawad@nottingham.ac.uk, mark.johnson@nottingham.ac.uk).

addressed in other work by reducing the isolation capacitance of the gate driver power supply [25],[26],[27],[28].

To address the issue of current flowing through the parasitic capacitances within the package, [33] proposed a method for diverting the current back to the dc bus by using two stacked direct-bonded-copper (DBC) substrates, where the intermediate metal layer is connected to the positive or negative dc bus. The amount of current that is diverted will strongly depend on the high-frequency impedance of the connection back to the dc bus. Accordingly, the implementation of this screen is critical. In [33], wire bonds are used for the interconnections, and "lugs" are used for the terminals. These connection methods have large parasitic inductances, which will reduce the effectiveness of the screen.

In [34], a similar screen is proposed. The 1.2 kV SiC MOSFET power module in [34] uses a multilayer DBC substrate, and dc-link capacitors located close to the dies. Vias in the multilayer substrate create a low-inductance connection between the middle metal layer and the negative dc bus [34]. The module has a 14-dB reduction compared to the reference module [34],[35]. While this module has several advantageous features, there are some areas for improvement. First, by connecting the middle metal to the negative dc bus, as in [33], the top ceramic is providing all the voltage isolation, and thus the second ceramic is not being fully utilized. Second, by placing the capacitors on the same plane as the MOSFETs, the footprint of the module is significantly increased. Third, the module parasitics are not well balanced, which has been shown to cause greater high-frequency noise compared to balanced designs [36].

The high-voltage rating of the 10 kV SiC MOSFETs poses a challenge for the electrostatic performance. If the electric field exceeds the breakdown field strength of the insulation materials, such as the encapsulation or insulating substrate, then partial discharge (PD) can occur. Repetitive PD events can ultimately result in insulation failure, such as cracking of the ceramic substrate, as shown in [37], thus destroying the power module. Furthermore, the PD inception voltage (PDIV) has been shown to decrease with increased dv/dt and switching frequency [38]. Due to the high-speed switching capabilities of these 10 kV SiC MOSFETs, measures must be taken to reduce the electric field concentration within the power module to ensure sufficient PDIV and breakdown voltage.

In this work, an optimized high-voltage power module package was designed, prototyped, and tested using 10 kV SiC MOSFETs. With the proposed package, the 10 kV SiC MOSFETs are able to switch at record speeds with minimal ringing and voltage overshoot. This fast switching results in significantly reduced switching losses compared to medium-voltage silicon transistors, and allows the switching frequency of medium- and high-voltage converters to be increased by orders of magnitude, which drastically reduces the size of passive components, thereby increasing the system power density. To mitigate the conducted EMI that could result from this high dv/dt, this work proposes to fully integrate a low-inductance screen into the package that limits the amount of

CM current that flows out of the power module. implementation, the capacitors are arranged abov MOSFET switch pair to balance parasitic inductance maintaining a small footprint. The middle metal 1 connected to the dc bus midpoint, which evenly distribule electric field in the ceramic layers and reduces the electric field at the critical triple points. Thus, the primplementation will mitigate the CM current, whi improving the voltage isolation, increasing the PDIV power module, and maintaining a small footprint for power density.

In this paper, the EMI issues encountered during terms the first-generation 10 kV SiC power modules from [5] be presented, followed by a description of the proposed module for 10 kV SiC MOSFETs. The a implementation, and preliminary testing of the integral screen will then be discussed. Methods for reducible electric field concentration within the power module reviewed, and the proposed technique will be an Finally, the experimental switching tests that demonst high-speed transients and low CM current of the proposed will be presented. Partial discharge tests value the improved voltage capability provided by the CM will also be shown.

# II. EMI LIMITATIONS FOR HIGH-VOLTAGE SIC POW

The development of 10 kV SiC MOSFETs [39] and SiC junction barrier Schottky (JBS) diodes [40] gave the first 10 kV SiC power module [30]. The half modules comprise twelve parallel 10 kV, 10 DMOSFETs, and six parallel 10 kV, 10 A SiC JBS dio switch position, yielding a current rating of 120 A [30] 10 kV SiC modules demonstrated higher efficien switching frequency potential than 6.5 kV silicon modules [8], and were critical components in the devel of a high-density 1 MVA solid-state power substation employed soft switching techniques and was capa switching up to 20 kHz [41]. These modules were also demonstrate the first medium-voltage impedance measu unit (IMU) capable of characterizing in-situ source at impedances of dc and ac networks up to 4160 V ac, dc, 300 A, and 2.2 MVA [42]. Unfortunately, the full and power levels could not be achieved due to sigr unresolvable EMI. Upon further evaluation, it was for substantial current was flowing through the system The contaminated ground was causing the control malfunction, thereby limiting the operating conditions.

As mentioned previously, under a voltage exc parasitic capacitances can become a path for CM cu flow. Within the power module, parasitic capacitance across the ceramic substrate that isolates the semico devices from the cooling system. Since the cooling sy generally grounded for safety, under high-speed transients, this parasitic capacitance becomes a path a current to flow through the system ground [36]. Therefore capacitance should be minimized, especially for fast-switching devices.

From ANSYS Q3D simulations, the parasitic capacitance between the output node of the half-bridge and the module baseplate is approximately 300 pF. Discrete switching tests were conducted on these power modules to characterize the dynamic performance [43]. At 4.7 kV and 100 A, the power modules had a maximum dv/dt of 22 V/ns [43]. This measured dv/dt and simulated parasitic capacitance give a calculated peak current of nearly 7 A. It should be noted that the 22 V/ns switching speed was achieved with internal and external gate resistances slowing down the devices. If these resistances were reduced or eliminated, then the switching speed would increase, which would raise the efficiency, but worsen the CM current. Therefore, this capacitance is limiting the operation of the 10 kV SiC MOSFETs. The package proposed in this work reduces this EMI without sacrificing the efficiency by minimizing the parasitic capacitance, and integrating a screen that contains the generated CM current within the power module.

#### III. MODULE OVERVIEW

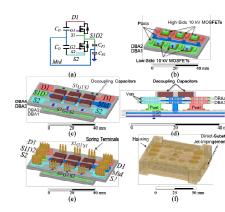

Fig. 1 shows the designed half-bridge power module, which has three 10 kV, 350 m $\Omega$  SiC MOSFET dies in parallel per switch position. No external anti-parallel diodes are used. The module has a planar, sandwich structure, using metal posts and direct-bonded-aluminum (DBA) substrates as the die interconnection instead of wire bonds. Similar structures were proposed in [44] and [45] for lower-voltage silicon IGBTs. This type of structure allows for increased power density, and reduces the parasitic inductances and capacitances in the module, thereby improving the dynamic performance. Furthermore, by eliminating the wire bonds, the module will be able to withstand higher-energy faults, as shown in [46]. This structure also allows decoupling capacitors to be embedded within the module to further improve the dynamic performance without increasing the module footprint.

In total, four substrates are used in the power module: two beneath the dies (DBA1 and DBA2) and two on top (DBA3 and DBA4). DBA1 and DBA2 are used to reduce the CM current flowing through the system ground and to decrease the peak electric field strength within the power module. With the housing and integrated cooler, the module dimensions are 70 mm  $\times$  80 mm  $\times$  25 mm. Details on the design and prototyping of this power module are reported in [47],[48],[49].

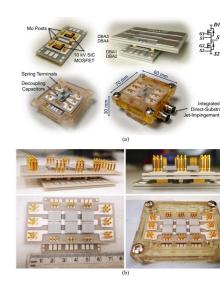

Fig. 2 shows two module prototypes: a low-current module with two dies (Fig. 2(a)), and a high-current module with six dies (Fig. 2(b)). The low-current module was fabricated to test the prototyping procedures, and was used for initial testing. The testing of these module prototypes will be presented in section VI.

### IV. COMMON-MODE SCREEN

### A. Impedance Analysis

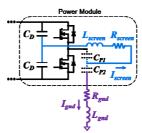

In this section, the CM path impedances will be analyzed. Fig. 3 shows a schematic of the power module with the key impedances that will be considered. For the generated CM

Fig. 1 (a) Schematic and 3D models of the (b) bottom and (c) co assemblies, (d) side-view of the module, (e) terminal arrangemen housing with integrated cooler. The colors in the 3D models corn to the nodes in the schematic with the same color.

Fig. 2 10 kV SiC MOSFET module prototypes with (a) two 10 kV MOSFET dies, and (b) six 10 kV SiC MOSFET dies.

current to be diverted from the ground to the scree impedance of the screen path must be much lower than the ground path, especially at high frequency. The correquired for the screen to effectively divert the CM from the ground path to the dc bus may be summar follows:

$$Z_{screen} \ll Z_{end}$$

where  $Z_{screen}$  and  $Z_{gnd}$  are the impedances of the screen and ground paths, respectively. Considering the parasitic elements shown in Fig. 3, these impedances can be defined as:

$$Z_{screen} = \omega L_{screen} + 1/(j\omega C_D) + R_{screen}$$

(2)

$$Z_{gnd} = \omega L_{gnd} + 1/(j\omega C_{P2}) + R_{gnd}$$

(3)

where  $L_{screen}$  and  $L_{gnd}$  are the parasitic inductances in the screen and ground paths,  $R_{screen}$  and  $R_{GND}$  are the parasitic resistances in the screen and ground paths,  $C_D$  is the decoupling capacitance, and  $C_{P2}$  is the parasitic capacitance of the bottom substrate, which is connected to ground (Fig. 1(d)). As shown by (2), to minimize  $Z_{screen}$ ,  $L_{screen}$  should be as small as possible, while  $C_D$  should be large. From (3), it can be seen that a smaller  $C_{P2}$  results in a greater  $Z_{gnd}$ . Substituting (2) and (3) into (1) gives:

$$\omega L_{screen} + 1/(j\omega C_D) + R_{screen} << \omega L_{gnd} + 1/(j\omega C_{P2}) + R_{gnd}$$

(4)

From (4), it can be seen that the effectiveness of the screen is dependent on the parasitic elements, which are determined by the implementation. To effectively reduce the CM current, the power module should be compact such that  $C_{P2}$  and  $L_{screen}$  are small, yet capable of accommodating sufficient decoupling capacitance  $C_D$ . The  $L_{gnd}$  and  $R_{gnd}$  will vary depending on the system integration, and are therefore out of the control of the power module designer. Accordingly, this work focuses on minimizing  $C_{P2}$  and  $L_{screen}$ , and maximizing  $C_D$ . A more general theoretical analysis of CM impedances is presented in [50].

#### B. Preliminary Testing

Prior to constructing the 10 kV SiC MOSFET power modules, it was desirable to understand the effects of the proposed screen on the CM noise. Accordingly, a half-bridge module with 1.2 kV, 80 m $\Omega$  SiC MOSFETs (C2M0080120D) was built and tested in a boost converter. For the test, the module substrate was directly mounted onto a copper ground plane. No cooling system was added between the substrate and the ground plane to improve the measurement results. Due to the absence of a cooling system, the tests were conducted at

Fig. 3 Power module schematic with parasitic impedances of the ground (purple) and screen (blue) paths.

low power (360 W). The output voltage was 60 V, switching frequency was 50 kHz.

For the prototyped 1.2 kV SiC modules, the properties of the prototyped 1.2 kV SiC modules, the properties of the prototype using an impedance analyzed were verified by calculation and Q3D simulation.  $C_{P2}$  in the prototype using an impedance analyzed were verified by calculation and Q3D simulation.  $C_{P2}$  in the prototype using an impedance analyzed were verified by calculation and Q3D simulation.  $C_{P2}$  in the prototype using an impedance analyzed were verified by calculation and Q3D simulation.  $C_{P2}$  in the prototype using an impedance analyzed prototype using an impedance analyzed

For the tests, a high-frequency current transformer (was used to measure the current of the line importabilization network (LISN). The output of the HFC connected to an EMC analyzer. The measured current cases are shown in Fig. 4. The first case has a single stand no decoupling capacitors. The second case has tacked substrates and no decoupling capacitors. The case has two stacked substrates and two 680-pF decapacitors in parallel and two in series, but the middl layer of the substrate stack is left floating. The fourth similar to the third, but has two series 10-nF capacitor fifth case connects the middle metal layer of the stack to the midpoint of the series decoupling capacitors.

When two substrates are stacked together (case 2), the decreases by just a few dB compared to case 1 with a substrate. This indicates that the reduction in the p capacitance offered by the second substrate is not suffi lower the CM noise. The addition of 680-pF dec capacitors in case 3, on the other hand, reduces the frequency noise by more than 10 dB compared to case a single substrate. The decoupling capacitors also ca resonant frequency to decrease. When the dec capacitance is increased to 10 nF (case 4), then the r frequency further decreases, and the high-frequency is reduced by a few more dB. This is in agreement w which shows that increasing the decoupling capacitance to reduce the high-frequency impedance of the scree When the middle metal of the substrate stack is conne the midpoint of the two series 10-nF capacitors (case : the high-frequency noise decreases by more than 15 dE larger frequency range. This is because there is now impedance, high-frequency path for the generated CM to flow. This preliminary testing demonstrates the pote the screen to reduce the CM noise.

The gate-source and drain-source voltages and drain of the 1.2 kV SiC MOSFET were also monitored dut testing. By adding decoupling capacitors, the frequency in the drain-source voltage reduced, and the increased, resulting in greater current overshoot and amplitude ringing. This ringing and overshoot can be by decreasing the power-loop inductance, which woptimized in this module prototype. Connecting the metal layer to the decoupling capacitor midpoint did not noticeable changes in the MOSFET voltage and waveforms. Therefore, if the parasitic inductances and

Fig. 4 Measured LISN current in 1.2 kV-SiC-based boost converter with (green waveform) and without (black, grey, and blue waveforms) the proposed CM screen.

decoupling capacitors are carefully designed, the proposed CM screen will have minimal impact on the MOSFET losses.

#### C. Implementation

To achieve a low-impedance implementation for the CM screen in the 10 kV power module, it is proposed to embed capacitors, and to use vias within the insulating ceramic substrates to make the connection between the middle metal layer and the capacitor potentials. In [50], the capacitors are placed above the semiconductor devices, creating a vertical high-frequency power loop that does not increase the module footprint, as it takes advantage of the third dimension. In this work, this vertical-capacitor-loop concept was adopted with some modifications. Each 10 kV SiC MOSFET switch pair has its own set of decoupling capacitors located above it (Fig. 1(c)), resulting in a symmetric power loop inductance of just 4.4 nH for each. In this embodiment, two capacitors are placed in series, and the midpoint, which is at half of the dc bus voltage, is connected to the middle metal of the substrate stack. By connecting the screen to the decoupling capacitors within the power module, the influence of the parasitic impedances external to the package are diminished thereby improving the effectiveness of the screen.

According to ANSYS Q3D simulations, this connection method has less than 2 nH parasitic inductance, allowing for a high proportion of the CM current to be diverted to the dc bus and contained within the power module. Additionally, the S1D2 pad area was designed as small as possible to minimize  $C_{Pl}$ . For the proposed high-current 10 kV power module shown in Fig. 1 and Fig. 2(b),  $C_{Pl}$  is 46 pF, and  $C_{P2}$  is 160 pF, according to ANSYS Q3D simulations. For the decoupling capacitors ( $C_D$ ), a surface-mount, 680 pF, C0G, 5 kV multilayer ceramic capacitor was selected. As shown in Fig. 1(c), there are three capacitors in parallel—one above each MOSFET switch pair—giving an equivalent capacitance of 2.04 nF

#### V. ELECTRIC FIELD REDUCTION

To address the enhanced electric field associated high-voltage, high-density package, the ceramic so must be thoughtfully designed and evaluated. In modules, the electric field concentrates at the intersect the ceramic, metal, and encapsulation [52],[53],[54],[55] is known as the triple point. If this electric field excebreakdown field strength of the insulation materials, the ceramic or encapsulation, then PD can occur. Re PD events can ultimately result in insulation failure, cracking of the ceramic substrate as shown in [37] destroying the power module.

In the literature, it has been shown that the PL standard 1-mm-thick aluminum nitride (AlN) DBC su is less than 10 kV rms [37], and can be as low as 5 [56]. This does not provide sufficient margin for 10 MOSFETs. Accordingly, methods for reducing th electric field within the power module need to be ex There have been several proposed solutions to red electric field strength at the triple point, including: inc the ceramic thickness [37]; varying the metal pad size pad corner curvature [37], offset between the top and [37], and metal-ceramic interface ge [57],[58],[59]; and stacking multiple substrates [56]. N these previously proposed solutions were implement tested in an actual power module, and several of the complicate the module manufacturing. The method pr in this work, is an adaptation of the latter met effectively increases the PDIV, and is simple to implem

In [56], it was shown that stacking DBC sureduces the electric field strength within the bulk cerar at the critical triple points. The PD tests revealed the PDIV could be increased by 94 % by stacking two 0 substrates compared to having a single 0 substrate [56]. However, the practical implementation method was not explored. In a power module, the tobottom metal layers are not symmetrical; the top in patterned to create the circuit (e.g., half bridge), a various traces are at different potentials during the operation. As a result, it is not clear what potential shapplied to the middle metal layer to achieve a mea reduction in the electric field strength. This key factor realization of this method is explored in this work.

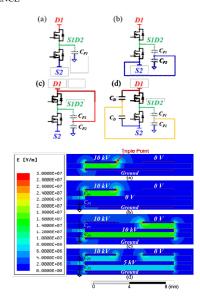

Fig. 5 shows the simulated 2D electric field districted for the case when the top metal is patterned and higherent potentials. One of the potentials represents the of the high-side switch, and the other represents the of the low-side switch. The former is consistently at the place bus potential while the latter switches between the pland negative dc bus potentials. The worst-case scenario when the low-side switch is conducting and its drain in negative dc bus potential. This worst-case was simulate positive dc bus is set to 10 kV, and the negative is set The bottom-most metal is at the same potential as the system, which is grounded (0 V).

Fig. 5(a) shows the simulated electric field plo single DBA substrate. It can be seen that the electr distribution is non-uniform within the bulk of the ceramic, and that the peak electric field occurs at the triple points. The peak electric field exceeds 20 kV/mm, which is the typical breakdown field strength for ceramic substrates.

Fig. 5(b) shows the simulated electric field plot for two stacked DBA substrates with the middle metal layer connected to the negative dc bus (0 V), as proposed in [33] and [34]. Comparing Fig. 5(a) and Fig. 5(b), it can be seen that connecting the middle metal to the negative dc bus does not reduce the peak electric field at the triple point, nor does it improve the distribution within the bulk ceramic, compared to the single substrate case. This is because the bottom substrate has 0 V across it, while the top substrate has 10 kV. In this implementation, the bottom substrate is not helping to support the voltage, and is therefore not being fully utilized.

If the middle metal is connected to the positive dc bus, as proposed in [33], then the triple points at which the peak electric field occur will change, and the electric field distribution within the bulk ceramic will shift. This is shown in Fig. 5(c). Although the distribution and critical triple points have changed, the peak electric field, and therefore the PDIV, are similar to the case with a single substrate. This is because both the top and bottom substrates have 10 kV across them.

If instead the middle metal is connected to half of the applied voltage, then both the top and bottom substrates have a potential of 5 kV across them. The simulated electric field distribution for this case is shown in Fig. 5(d). The simulated peak electric field is reduced by 58 % compared to the single-substrate case (Fig. 5(a)), and the electric field in the bulk ceramic is uniformly distributed in the two substrates. Therefore, in this work, the middle metal layer of the DBA stack is connected to half of the bus voltage.

The connection of the middle metal layer to half of the bus potential can be realized with the embedded decoupling capacitors. Each set of decoupling capacitors shown in Fig. 1(c) consists of two, 5 kV ceramic capacitors placed in series. From Fig. 1(d), it can be seen that the midpoint of the capacitors is connected to the middle metal layer of the bottom DBA stack through vias and metal posts. This connection allows the middle metal layer to be connected to half of the bus voltage, thus reducing the peak electric field in the power module.

#### VI. EXPERIMENTAL RESULTS

# A. Switching Testing

To evaluate the switching performance of the proposed 10 kV power module, double-pulse tests (DPT) were performed on the low-current prototype shown in Fig. 2(a). The DPT schematic and setup are shown in Fig. 6. The gate driver used for the DPTs was adapted from the one presented in [60]. The low-side 10 kV SiC MOSFET was driven from +20 V in the on-state to -5 V in the off-state. The body diode of the high-side 10 kV SiC MOSFET was used as the free-wheeling

Fig. 5 Simulated 2D electric field distribution for (a) a single substand two stacked substrates with the middle metal at the (b) negative bus, (c) positive dc bus, and (d) dc bus midpoint.

Fig. 6 Double-pulse test (a) schematic with the power module indib by the yellow box, (b) hardware setup, and (c) module connection.

diode. The gate driver PCB is mounted on top of the power module to achieve small gate-loop inductance between the driver and the module.

The gate-source and drain-source voltages of the low-side SiC MOSFET were monitored using a 300 V passive probe with a bandwidth of 1 GHz, and a 20 kV passive probe with a bandwidth of 75 MHz, respectively. As shown in Fig. 6(c), these probes are placed directly above the MOSFET terminals to minimize the parasitic inductance in the measurement loop. Due to the embedded decoupling capacitors, the drain current of the SiC MOSFETs could not be measured. A 15 kV power supply was used to charge the external decoupling capacitors. Each capacitor is 0.82  $\mu F$  and rated at 3.3 kV (MP80CV824K [61]). Six total capacitors were used—two in series and three in parallel for a total capacitance of 1.2  $\mu F$  and voltage rating of 6.6 kV. Three capacitors were put in parallel to increase the capacitance and to reduce the inductance; each capacitor has an equivalent series inductance of 30 nH [61].

Fig. 7 shows the gate-source and drain-source voltage waveforms for the turn-on and turn-off transients for the DPTs performed on the module shown in Fig. 2(a). The switching tests were performed up to 5 kV and 20 A with turn-on and turn-off gate resistances of 0.33  $\Omega$  and 0.17  $\Omega$ , respectively. Table I lists the measured overshoot, undershoot, rise and fall times, and switching rates from the DPTs. During the turn-on transient, the fall time of the drain-source voltage is 16 ns, giving a dv/dt of 250 V/ns. At turn-off, the voltage rise time is 50 ns, which is a dv/dt of 80 V/ns. The voltage rise time is longer because it is controlled by the output capacitance and load current. Negligible voltage overshoot and ringing were measured, indicating low power- and gate-loop inductances. This is due to the low-inductance module design, as well as careful layout and connection of the gate driver, bus bar, external decoupling capacitors, and measurement probes.

To the best of the author's knowledge, these are the fastest switching speeds reported for similarly-rated SiC MOSFETs and IGBTs. In fact, this is more than two times faster than those reported in [24],[32],[62],[63]. In [32], switching results for a module populated with a single die had turn-on and turn-off transition times of approximately 80 ns and 120 ns, respectively, giving switching speeds of 88 V/ns and 58 V/ns at a bus voltage of 7 kV, drain current of 15 A, and gate resistance of 21  $\Omega$ . The switching waveforms also showed a moderate voltage overshoot of approximately 300 V (4.3 %) [32].

For a discrete 4 kV silicon IGBT, the datasheet reports voltage rise and fall times of 146 ns and 514 ns at 1.25 kV, 30 A, and 2  $\Omega$  external gate resistance [64]. These switching times result in dv/dt values of 8.6 V/ns and 2.4 V/ns for the rise and fall, respectively, which are 10 and 100 times slower than the switching speeds achieved in this work. Accordingly, the proposed power module can enable faster-switching, higher-voltage power converters while maintaining high efficiency.

Fig. 7 (a) Turn-on and (b) turn-off gate-source (blue, right axis) and rain-source (red, left axis) voltages.

TABLE I 10 kV, 350 m $\Omega$  SiC MOSFET Module Prototype Switching Res

|            | Value               |                      |  |

|------------|---------------------|----------------------|--|

| Parameter  | Gate-Source Voltage | Drain-Source Voltage |  |

| Overshoot  | None                | None                 |  |

| Undershoot | None                | None                 |  |

| Rise Time  | 24 ns               | 50 ns                |  |

| Rise dv/dt | 0.9 V/ns            | 80 V/ns              |  |

| Fall Time  | 26 ns               | 16 ns                |  |

| Fall dv/dt | 0.8 V/ns            | 250 V/ns             |  |

#### B. Common-Mode Screen Testing

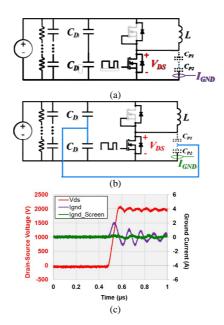

To evaluate the effectiveness of the integrated CM screen on the 10 kV power module, switching test performed. As mentioned earlier, the CM current incret the dv/dt and parasitic capacitances increase. To imprisional-to-noise ratio of the CM current measurement, the was reduced. This was achieved by lowering the voltage to 2 kV. To ensure sufficient CM current comeasured, the larger power module with three 10 kMOSFET dies in parallel per switch position was use 2(b)) [65]. The  $C_{P1}$  and  $C_{P2}$  of this 10 kV prototype and 162 pF, respectively.

Fig. 8(a) shows the schematic of the tests when a screen is not connected (the middle metal layer of the substrate stack is floating). Fig. 8(b) shows the schemathe tests when the CM screen is connected to the camidpoint. An inductor with high-voltage wire for the was connected across the high-side switch of the half module. The body diode of the high-side SiC MOSI used to freewheel the current in the inductor when the side switch was off.

To validate the performance of the CM screen, the through the ground path,  $I_{gnd}$ , was measured, as shown in

Fig. 8 Schematic of the testing setup when the screen is (a) not connected and (b) connected, and (c) drain-source (red, left axis) and ground current (right axis) waveforms with (green) and without (purple) the commonde screen.

8, using an RF current transformer with a bandwidth of 200 MHz. For these tests, the middle metal layer was connected to the midpoint of the two series 680-pF decoupling capacitors. Three capacitors were placed in parallel.

Fig. 8(c) shows the turn-off drain-source voltage and ground current waveforms with and without the screen at 2 kV and 20 A with no external gate resistance. The voltage rise time at turn off is 66 ns, which gives a dv/dt of 24 V/ns. This dv/dt is lower than the previous switching tests because of the lower bus voltage and larger device capacitance due to the three MOSFET dies in parallel. The measured peak current through the ground path without the proposed screen is 2 A. This peak current will increase as the dc bus voltage, and therefore the dv/dt, increases. With the CM screen connected, the measured peak current through the ground path is reduced to 0.2 A. This is an order of magnitude reduction.

# C. Partial Discharge Testing

PD tests were conducted to validate the electrostatic simulation results. The PD tests were performed using a 50 kV, 100-mA, 60-Hz power supply as the excitation source. To detect the PD events, a Doble PD Smart with HFCT-300 sensor was used [66]. The Doble PD Smart complies with IEC 60270 and VDE 0434, among other standards [66]. PD signals at frequencies from 35 kHz to 20 MHz and an apparent charge as low as 0.2 pC can be measured [66].

PD tests were performed on a patterned, 1-mm-thic DBA substrate. The spacing between metal traces and the metal traces to the edge of the ceramic was 2 mm cases were tested: 1) a single substrate, 2) two substrates with the middle metal connected to the ground, and 3) two stacked substrates with the middle connected to half of the applied excitation voltage. Ear was tested under two conditions: 1) S1D2= D1 (the his switch is conducting and the low-side switch is blocking 2) S1D2= S2 (the high-side switch is blocking and the switch is conducting).

First, the PD tests were performed with the sample to have a high signal-to-noise ratio. These tests reveal as was shown in the electrostatic simulations, the PD DBA substrates will occur at the triple points. Specifica PD will take place along the edge of the metal pad whigh potential is applied. The resulting PDIV for the when the samples are tested in air are listed in Table II S1D2 is equal to D1 (the applied voltage), and the metal is connected to half of the applied voltage, the increases by 53 % compared to the single-substrate ca The same increase in PDIV was observed when S1D2 to S2 (ground). These results, which are in good agree with the simulations, demonstrate that connecting the metal to half of the applied voltage gives predicted to substrate the substrate that some consistent results for both switching states.

Since the power module will be encapsulated, P were also performed on a stacked substrate sample the encapsulated with SilGel 612 from Wacker. For this the S1D2 potential was connected to S2 (the worst case measured PDIVs for this sample are listed in Table II the middle metal is connected to the source ground, the middle metal is connected to the source ground, the source ground, the state of the same case, bread occurred at 8.5 kV rms (12.0 kV peak). This means middle metal is connected to ground, or if a single subsused, then there is 20 % margin between the peak bread voltage and the voltage rating of the 10 kV SiC MOSFI

When the middle metal is connected to half of the voltage, no PD could be measured up to 10.5 kV rms (1 peak). The testing was stopped at 10.5 kV rms due reduced signal-to-noise ratio. This suggests that encar stacked substrates with the middle metal connected to the applied voltage will have more than a 40 % higher I

TABLE II Partial Discharge Testing Summary

| Sample                                | Voltage of<br>Middle<br>Metal  | Surrounding<br>Medium | S1D2<br>Potential | PDI<br>(rm: |

|---------------------------------------|--------------------------------|-----------------------|-------------------|-------------|

| Single<br>Substrate                   | N/A                            | Air                   | D1                | 1.7 k       |

|                                       | N/A                            | Air                   | S2                | 1.7 k       |

| Stacked<br>Substrates                 | $^{1\!/_{\!2}}\!\times V_{AC}$ | Air                   | D1                | 2.6 k       |

|                                       | $1/_2 \times V_{AC}$           | Air                   | S2                | 2.6 k       |

| Encapsulated<br>Stacked<br>Substrates | 0 V                            | SilGel 612            | S2                | 7.4 k       |

|                                       | $1/2 \times V_{AC}$            | SilGel612             | S2                | >10.5       |

compared to a single substrate or a stacked substrate with the middle metal connected to ground. Therefore, it is advantageous to use the stacked substrate structure with the middle metal connected to half the applied voltage to increase the high-voltage performance of the power module.

#### VII. CONCLUSIONS

This work proposed a high-density power module for 10 kV SiC MOSFETs with reduced CM current and electric field strength. The optimal layout and system interface enable the module to switch 5 kV in tens of nanoseconds with negligible ringing and voltage overshoot. This is the fastest switching speed reported to date for 10 kV SiC MOSFETs. To reduce the adverse EMI effects of this high-speed switching, a CM screen was incorporated into the power module design. This screen was realized by stacking two DBA substrates and connecting the middle metal to the midpoint of embedded decoupling capacitors through vias and metal posts. This proposed method creates a low-impedance path at high frequency, and contains the current that would normally flow to the system ground within the power module. With this screen, the measured CM current leaving the power module decreases by ten times. This proposed integrated screen will reduce the need for filtering at the system level, thereby increasing the power density, lowering the cost, and simplifying the design of power electronic systems. Moreover, it will permit the operation of the 10 kV SiC MOSFETs at faster speeds, thereby reducing losses and increasing efficiency.

This screen also increases the voltage rating of the power module. PD tests showed that stacking two substrates and connecting the middle metal to half of the applied voltage increases the PDIV by 53 % compared to a single substrate. When testing two encapsulated stacked substrates with the middle metal connected to the source ground, breakdown occurred at 8.5 kV rms (12.0 kV peak). This breakdown voltage limits the voltage rating of the package. When the middle metal of the encapsulated substrates is connected to half of the applied voltage, the PDIV exceeds 10.5 kV rms. This method for reducing the electric field is effective and simple to implement, and will enable high-voltage packages with greater power density.

# ACKNOWLEDGMENT

The authors would like to acknowledge the experimental assistance from Ke Li and Yue Xu. The authors also acknowledge the assistance of Dr. Xiangyong Feng and the Center for Electromechanics at the University of Texas at Austin in conducting the partial discharge tests. The substrates used in the power module prototypes were donated by DOWA, and the external decoupling capacitors used for the switching tests were donated by Electronic Concepts. This work was funded in part by the UK Engineering and Physical Sciences Research Council (EPSRC) through research grant [EP/K035304/1] and the CPES High Density Integration Consortium. This work was conducted with the use of A Maxwell 2D, ANSYS Maxwell 3D, and ANSYS Extractor, donated in-kind by Ansoft Corporation of the Industry Partnership Program.

#### REFERENCES

- H. Zhang, L. M. Tolbert, B. Ozpineci, "Impact of SiC de [1] H. Zhang, E. M. Torlert, B. Ozphiect, impact of size hybrid electric and plug-in hybrid electric vehicles," *IEE Ind. Appl.*, vol. 47, no. 2, pp. 912-921, Mar.-Apr. 2011.

A. Bindra, "SiC-based PV inverters display reduced size and cost," *How2Power Today*, May 2013.

- [2]

- J. Rabkowski, D. Peftitsis, H. P. Nee, "Silicon carbic transistors- A new era in power electronics is initiated," I [3] Electron. Mag., vol. 6, no. 2, pp. 17-26, June 2012. J. Millan, P. Godignon, X. Perpina, A. Perez-Tomas, J.

- [4] "A survey of wide bandgap power semiconductor device Trans. Power Electron., vol. 29, no. 5, pp. 2155-2163, Ma "Train trial shows a 40 % energy saving for SiC inverters The Computer No. 2015."

- [5]

- and Controls, June 2015.

J. W. Palmour, L. Cheng, V. Pala, E. V. Brun Lichtenwalner, G. Y. Wang, J. Richmond, M. O'Loughlir S. T. Allen, A. A. Burk, C. Scozzie, "Silicon carbic [6] MOSFETs: Breakthrough performance from 900 V up to in IEEE International Symposium on Semiconductor De

- IC's, June 2014.

T. Lu, Z. Zhao, S. Ji, H. Yu, L. Yuan, "Parameter design of [7] balancing circuit for series connected HV-IGBTs," International Power Electronics and Motion Control Co June 2012.

- H. Mirzaee, A. De, A. Tripathi, S. Bhattacharya, comparison of high-power medium-voltage converters be 6.5-kV Si-IGBT/Si-PiN diode, a 6.5-kV Si-IGBT/SiC-JI and a 10-kV SiC-MOSFET/SiC-JBS diode," IEEE Tr Appl., vol. 50, no. 4, July/Aug. 2014.

J. Casarin, P. Ladoux, P. Lasserre, "10kV SiC MOSFE"

- [9] 6.5kV Si-IGBTs for medium frequency transformer appl railway traction," in IEEE International Conference on I Systems for Aircraft, Railway, Ship Propulsion, and Road Mar. 2015.

- [10] K. Hatua, S. Dutta, A. Tripathi, S. Baek, G. Karimi, S. Bhattacharya, "Transformer less intelligent power substati design with 15kV SiC IGBT for grid interconnection," in Energy Conversion Congress and Exposition, Sept. 2011.

- Energy Conversion Congress and Exposition, Sept. 2011.

S. Madhusoodhanan, A. Tripathi, D. Patel, K. Mainali, A. Kadavelugu, S. Hazra, S. Bhattacharya, K. Hatua, "Solid stransformer and MV grid tie applications enabled by 15 k" IGBTs and 10 kV SiC MOSFETs based multilevel convertience Trans. Ind. Appl., vol. 51, no. 4, pp. 3343-3360, Aug IEEE Recommended Practice for 1 kV to 35 kV Medium DC Power Systems on Ships, IEEE Standard 1709-2010, **[11]**

- [12]

- Nov. 2010. C. Zhao, D. Dujic, A. Mester, J. K. Steinke, M. Weiss, S. [13] C. Zhao, D. Dujic, A. Mester, J. K. Steinke, M. Weiss, S. Schmid, T. Chaudhuri, P. Stefanutti, "Power electror transformer- Medium voltage prototype," *IEEE Tre Electron.*, vol. 61, no. 7, pp. 3257-3268, Aug. 2013.

D. C. Patel, A. Kadavelugu, S. Madhusoodhanan, S. Bhat K. Hatua, S. Leslie, S. H. Ryu, D. Grider, A. Agarwal, "1

- [14] IGBT based three-phase three-level modular-leg power co in IEEE Energy Conversion Congress and Exposition, Sep S. Srdic, X. Liang, C. Zhang, W. Yu, S. Lukic, "A SiC-ba

- performance medium-voltage fast charger for plug-in elective vehicles," in IEEE Energy Conversion Congress and Experience of the Energy Conversion Congress and Energy Conversion Co Sept. 2016.

- M. S. Chinthavali, L. M. Tolbert, B. Ozpineci, "4H-SiC G thyristor and p-n diode loss models for HVDC converter," [16]

- Halustry Applications Conference, Oct. 2004.

Y. Koyama, Y. Nakazawa, H. Mochikawa, A. Kuzumaki,

N. Okada, "A transformerless 6.6-kV STATCOM based o [17]

#### IEEE POWER ELECTRONICS REGULAR PAPER/LETTER/CORRESPONDENCE

- hybrid cascade multilevel converter using SiC devices," in *IEEE Trans. Power Electron.*, vol. 33, no. 9, pp. 7411-7423, Nov. 2017. P. Wolfs, F. Yang, Q.-L. Han, "Distribution level SiC FACTS devices with reduced de bus capacitance for improved load capability and solar integration," in *IEEE International Symposium on Industrial Electronics*, June 2014.

M. K. Dec, Capaell, D. F. Grider, S. Lackie, I. Oston, P. Pair, M. [18]

- M. K. Das, C. Capell, D. E. Grider, S. Leslie, J. Ostop, R. Raju, M. Schutten, J. Nasadoski, A. Hefner, "10 kV, 120 A SiC half H-bridge power MOSFET modules suitable for high frequency, **[19]** medium voltage applications," in *IEEE Energy Conversion Congress and Exposition*, Sept. 2011.

- R. Chattopadhyay, S. Bhattacharya, N. C. Foureaux, S. M. Silva, F. Braz Cardoso, H. de Paula, I. A. Piers, P. C. Cortizio, L. [20] Moraes, J. A. de S. Brito, "Low-voltage PV power integration into medium voltage grid using high-voltage SiC devices," in *International Power Electronics Conference*, May 2014.

A. Q. Huang, Q. Zhu, L. Wang, L. Zhang, "15 kV SiC MOSFET:

- [21]

- A. Q. Huang, V. Zhul, L. Wang, L. Zhang, T. S. V. Sir. WOSFEL. An enabling technology for medium voltage solid state transformers," CPSS Trans. Power Electron. Appl., vol. 2, no. 2, pp. 118-130, Aug. 2017.

V. Pala, E. V. Brunt, L. Cheng, M. O'Loughlin, J. Richmond, A. Burk, S. T. Allen, D. Grider, J. W. Palmour, "10 kV and 15 kV silicon carbide power MOSFETs for next-generation energy conversion and transmission systems," in IEEE Trans. Conversion. [22] conversion and transmission systems," in IEEE Energy Conversion

- conversion and transmission systems, in *IEEE Energy Conversion Congress and Exposition*, Sept. 2014.

M. Das, C. Capell, D. Grider, S. Leslie, J. Ostop, R. Raju, M. Schutten, J. Nasadoski, A. Hefner, "10 kV, 20 A SiC half H-bridge power MOSFET modules suitable for high frequency, medium [23] voltage applications," in IEEE Energy Conversion Congress and Exposition, Sept. 2011.

- Exposition, Sept. 2011.

K. Vechalapu, S. Bhattacharya, E. Van Brunt, S.-H. Ryu, D. Grider, J. W. Palmour, "Comparative evaluation of 15-kV SiC MOSFET and 15-kV SiC IGBT for medium-voltage converter under the same dv/dt conditions," in IEEE J. Emerging Sel. Topics [24]

- Power Electron., vol. 5, no. 1, pp. 469-489, Mar. 2017.

A. Kadavelugu, "Medium voltage power conversion enabled by 15 kV SiC IGBTs," Ph.D. dissertation, North Carolina State Univ., [25] NC, 2015

- X. Zhang, H. Li, J. A. Brothers, L. Fu, M. Perales, J. Wu, J. Wang [26] "A gate drive with power over fiber-based isolated power supply and comprehensive protection functions for 15-kV SiC MOSFET, IEEE J. Emerging Sel. Topics Power Electron., vol. 4, no. 3, pp 946-955, Sept. 2016.

- A. Tripathi, K. Mainali, S. Madhusoodhanan, A. Yadav, K. Vechalapu, S. Bhattacharya, "A MV intelligent gate driver for 15kV SiC IGBT and 10kV SiC MOSFET," in *IEEE Applied Power Electronics Conference and Exposition*, Mar. 2016. [27]

- D. Berning, T. Duong, J. Ortiz-Rodfriguez, A. Rivera-Lopez, A. Hefner, "High-voltage isolated gate drive circuit for 10 kV, 100 A [28] SiC MOSFET/JBS power modules," in IEEE IAS Annual Meeting,

- pp. 1-7, 2008. S. Moballegh, S. Madhusoodhanan, S. Bhattacharya, "Evaluation [29] of high voltage 15 kV SiC IGBT and 10 kV SiC MOSFET for ZVS and ZCS high power DC -DC converters," in *International* Power Electronics Conference, May 2014. M. Das, D. Grider, S. Leslie, R. Raju, M. Schutten, A. Hefner, "10

- [30] kV SiC power MOSFETs and JBS diodes: enabling revolutionary module and power conversion technologies," J. Mat. Sci. Forum,

- Vol. 717-720, pp. 1225-1228, May 2012.

Z. Chen, R. Burgos, D. Boroyevich, F. Wang, S. Leslie, "Modeling and simulation of 2 kV 50 A SiC MOSFET/IBS power modules," [31] in IEEE Electric Ship Technol. Symp., Apr. 2009.

- B. Passmore, Z. Cole, B. McGee, M. Wells, J. Stabach, J. Bradshaw, R. Shaw, D. Martin, T. McNutt, E. VanBrunt, B. Hull, D. Grider, "The next generation of high voltage (10 kV) silicon carbide power modules," in *IEEE Workshop on Wide Bandgap Power Devices and Applications*, Nov. 2016. [32]

- D. Domes, "Semiconductor arrangement," U.S. Patent 2013/0043593 A1, Feb. 21, 2013. [33]

- T. Huber, A. Kleimaier, S. Polster, O. Mathieu, "Low inductive SiC power module design using ceramic multilayer substrates," in [34] International Exhibition and Conference for Power Electronics,

- Intelligent Motion, Renewable Energy and Energy Manag

- [35] T. Huber, A. Kleimaier, R. Kennel, "Ultra-low inductive pmodule design with integrated common mode noise shield European Conference on Power Electronics Applications,

- A Domurat-Linde E Hoene "Analysis and reduction of [36] EMI of power modules," in International Conference on Integrated Power Electronics Systems, Mar. 2012.

- C. Bayer, U. Waltrich, R. Schneider, A. Soueidan, E. Schletz, "Enhancing partial discharge inception voltage by geometrical variations based on simulations of the electronstraint, in *International Conference on Integrated* Electronics Systems, Mar. 2016.

P. Wang, A. Cavallini, G. C. Montanari, "The influence of

- [38] repetitive square wave voltage parameters on enameled we endurance," *IEEE Trans. Dielectr. Electr. Insul.*, vol. 21, 1 1276-1284, June 2014.

- S. H. Ryu, S. Krishnaswami, B. Hull, J. Richmond, A. Ag [39] Hefner, "10 kV, 5 A 4H-SiC power DMOSFET," in Inte Symposium on Power Semiconductor Devices and IC's,

- B. A. Hull, J. J. Sumakeris, M. J. O'Loughlin, Q. 2 [40] Richmond, A. R. Powell, E. A. Imhoff, K. D. Hobart, A

- Lopez, A. R. Hefner, "Performance and stability of large SiC 10-kV junction barrier Schottky rectifiers," *IEE Electron. Devices*, vol. 55, no. 8, pp. 1864-1870, 2008.

D. Grider, M. Das, R. Raju, M. Schutten, S. Leslie, J. 6 Hefner, "10 kV/120 A SiC DMOSFET half H-bridg modules for 1 MVA solid state power substation," *Electric Phin Technologies Symposium*, pp. 131, 134, 2011. [41]

- modules for 1 MVA solid state power substation,"

Electric Ship Technologies Symposium, pp. 131-134, 2011

M. Jaksic, Z. Shen, I. Cvetkovic, D. Boroyevich, R. B

DiMarino, F. Chen, "Medium-voltage impedance mea

unit for assessing the system stability of electric ship

Trans. Energy Convers., vol. 32, no. 2, pp. 829-841, Apr.

C. DiMarino, I. Cvetkovic, Z. Shen, R. Burgos, D. Bo

"10 kV, 120 A SiC MOSFET modules for a power e

bilding block (DEPDR)" in IEEE Workshen v. Wide [42]

- [43] building block (PEBB)," in *IEEE Workshop on Wide Power Devices and Applications*, Oct. 2014.

S. Haque, K. Xing, R. L. Lin, C. T. A. Suchicital, G. Q. Nelson, D. Borojevic, F. C. Lee, "An innovative tech packaging power electronic building blocks using me interconnected parallel plate structures," *IEEE Trans. A* [44]

- Packag, vol. 22, no. 2, pp. 136-144, May 1999.

B. Mouawad, J. Li, A. Castellazzi, C. M. Johnson, "Hybridge package for high voltage application," international Symposium on Semiconductor Devices of [45]

- June 2016. I. Yaqub, J. Li, C. M. Johnson, "Dependence of overcurre

- modes of IGBT modules on interconnect techn Microelectron. Reliab., vol. 55, no. 12, pp. 2596-2605, De C. DiMarino, M. Johnson, B. Mouawad, J. Li, D. Boroyev [47] Burgos, G.-Q. Lu, M. Wang, "Design of a novel, high-der high-speed 10 kV SiC MSOFET module," *IEEE Energy*

- Conversion Congress and Exposition, Sept. 2017. C. DiMarino, M. Johnson, B. Mouawad, J. Li, R. Skuriat, [48] Wang, Y. Tan, G.-Q. Lu, D. Boroyevich, R. Burgos, "Fab and characterization of a high-power-density, planar 10 k

- MOSFET power module," in International Conference on Integrated Power Electronics Systems, Mar. 2018.

C. DiMarino, B. Mouawad, C. M. Johnson, M. Wang, Y. [49] Q. Lu, D. Boroyevich, R. Burgos, "Design and experimen validation of a wire-bond-less 10 kV SiC MOSFET power module," submitted to IEEE Journal of Emerging and Spe

- Topics in Power Electronics, 2019. Z. Zhang, C. M. Johnson, "Suppression of electromagnetic interference using screening and shielding techniques with

- switching cells," in IEEE International Workshop on Integ Power Packaging, Apr. 2017. E. Hoene, A. Ostmann, C. Marczok, "Packaging very fast switching semiconductors," in *International Conference of* [51]

- Integrated Power Electronics Systems, Feb. 2014.

### IEEE POWER ELECTRONICS REGULAR PAPER/LETTER/CORRESPONDENCE

- J. H. Fabian, S. Hartmann, A. Hamidi, "Analysis of insulation failure modes in high power IGBT modules," in *Industry Applications Society Annual Meeting*, pp. 799-805, Oct. 2005. J. H. Fabian, S. Hartmann, A. Hamidi, "Partial discharge failure

- [53] analysis of AlN substrates for IGBT modules," Microelectron. vol. 44, pp. 1425-2430, 2004.

- G Mitic G Lefranc "Localization of electrical-insulation-and [54] G. Witte, G. Editaic, Localization of electrical-insulation-and partial-discharge failures of IGBT modules," *IEEE Trans. Ind. Appl.*, vol. 38, no. 1, pp. 175-180, Jan./Feb. 2002.

C. F. Bayer, E. Baer, U. Waltrich, D. Malipaard, A. Schletz, "Simulation of the electric field strength in the vicinity of

- [55] metallization edges on dielectric substrates," *IEEE Trans. Dielectr. Electr. Insul.*, vol. 22, no. 1, pp. 257-265, Feb. 2015.

- O. Hohlfeld, R. Bayerer, T. Hunger, H. Hartung, "Stacked substrates for high voltage applications," in *International Conference on Integrated Power Electronics Systems*, Mar. 2012. H. Hourdequin, L. Laudebat, M.-L. Locatelli, P. Bidan, "Design of [56]

- [57] Packaging structures for high voltage power electronics devices: electric field stress on insulation," in *IEEE International Conference on Dielectrics*, July 2016.

D. Frey, J. L. Schanen, J. L. Auge, O. Lesaint, "Electric field

- [58] investigation in high voltage power modules using finite element simulations and partial discharge measurements," in *Industry Applications Society Annual Meeting*, Oct. 2003.

- H. Reynes, C. Buttay, H. Morel, "Protruding ceramic substrates for high voltage packaging of wide bandgap semiconductors," in *IEEE Workshop on Wide Bandgap Power Devices and Applications*, [59] Nov. 2017.

- C. DiMarino, J. Wang, R. Burgos, D. Boroyevich, "A high-power-density, high-speed gate driver for a 10 kV SiC MOSFET [60] module," in IEEE Electric Ship Technologies Symposium, Aug.

- Electronic Concepts, "MP80 series metallized polypropylene," MP80 datasheet, Rev. 4. Available: https://www.ecicaps.com/film-[61] capacitors/mp80-series/

- A. Kadavelugu, S. Bhattacharya, S.-H. Ryu, E. Van Brunt, D [62] Grider, A. Agarawal, S. Leslie, "Characterization of 15 kV SiC n-IGBT and its application considerations for high power converters," in IEEE Energy Conversion Congress and Exposition, Sept. 2013.

- D. Johannesson, M. Nawaz, K. Ilves, "Assessment of 10 kV, 100 [63] D. Johannesson, M. Nawaz, K. Ilves, "Assessment of 10 kV, 100 A silicon carbide MOSFET power modules," *IEEE Trans. Power Electron.*, vol. 33, no. 6, pp. 5215-5225, June 2018. IXYS, "High voltage IGBT for capacitor discharge applications", IXGF30N400 datasheet, 2009. Available: http://ixapps.ixys.com/DataSheet/DS99978C(IXGF30N400).pdf C. DiMarino, B. Mouawad, K. Li, Y. Xu, M. Johnson, D. Boroyevich, R. Burgos, "A wire-bond-less 10 kV SiC MOSFET

- [64]

- [65] power module with reduced common-mode noise and electric field," in International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, June 2018.

- Doble Engineering Company, "Doble in-service testing & assessment PD-Smart partial discharge analyzer," PD-Smart [66] datasheet, Mar. 2016.