# Design and Experimental Validation of a Wirebond-less 10 kV SiC MOSFET Power Module

Christina DiMarino, *Member, IEEE*, Bassem Mouawad, C. Mark Johnson, *Member, IEEE*, Meiyu Wang, Yan-Song Tan, Guo-Quan Lu, *Fellow, IEEE*, Dushan Boroyevich, *Fellow, IEEE* and Rolando Burgos, *Member, IEEE*

Abstract— Wide-bandgap power devices with voltage ratings exceeding 10 kV have the potential to revolutionize medium- and high-voltage systems due to their high-speed switching and lower on-state losses. However, present power module packages are limiting the performance of these unique switches. The objective of this work is to push the boundaries of high-density, high-speed, 10 kV power module packaging. The proposed package addresses the well-known electromagnetic and thermal challenges, as well as the more recent and prominent electrostatic and electromagnetic interference issues associated with high-speed, 10 kV devices. The module achieves low and balanced parasitic inductances, resulting in a record switching speed of 250 V/ns with negligible ringing and voltage overshoot. An integrated screen reduces the commonmode current that is generated by these fast voltage transients by ten times. This screen connection simultaneously increases the partial discharge inception voltage by more than 50 %. A compact, medium-voltage termination and system interface design is also proposed in this work. With the integrated jet-impingement cooler, the power module prototype achieves a power density of 4 W/mm<sup>3</sup>. This paper presents the design, prototyping, and testing of this optimized package for 10 kV SiC MOSFETs.

Index Terms—Electromagnetic interference, high-voltage techniques, packaging, silicon carbide

# I. INTRODUCTION

Por Several decades, silicon has been the primary semiconductor choice for power electronics applications [1]. However, silicon is quickly approaching its limits in power conversion [2],[3]. Wide-bandgap (WBG) semiconductors have demonstrated improved efficiency, reduced size and weight, and lower system cost [2],[3],[4],[5],[6]. Of the various WBG semiconductors, silicon carbide (SiC) is currently one of the most promising for medium- and high-voltage applications [2],[3],[7]. Today, medium- and high-voltage systems use silicon insulated gate bipolar junction transistors (IGBT), integrated gate-commutated thyristors (IGCT), or gate turn-off thyristors (GTO). While these devices have proven reliability and ruggedness, they have limited voltage ratings (typically 6.5 kV or less), requiring the series connection of devices or

multilevel converter topologies [8]. The series connection of devices raises the issue of voltage imbalance, and multilevel converters require additional components and complex control [8]. Moreover, these bipolar silicon devices have limited switching speed, which constrains the efficiency and switching frequency of the power converter [9],[10].

SiC power semiconductors are advantageous in these respects. Thus far, medium-voltage SiC MOSFETs [11],[12],[13], junction field effect transistors (JFET) [14],[15], bipolar junction transistors (BJT) [16], IGBTs [17],[18], GTOs [19], and emitter turn-off thyristors (ETO) [20],[21] have been demonstrated. Of these devices, the 10 kV SiC MOSFETs are of great interest due to their high blocking voltage, fast switching speed, simple drivability, reverse conduction capability, and moderate on-state losses. These features can increase the efficiency, reliability, and switching frequency, and reduce the complexity, size, and weight of medium- and high-voltage power conversion systems [18],[22]. Applications for 10 kV SiC devices include electric ships [23], traction [10],[24], data center distribution, direct renewables integration to a medium-voltage (13.8 kV) grid [17], fast charging stations [25], HVDC [26], flexible ac transmission systems (FACTS) [27],[28], and transformer-less intelligent power substations [17],[22],[29],[30],[31].

Due to the vast possibilities for ≥10 kV SiC devices, many resources have been devoted to their development. To date, the majority of the reports on these devices have been focused on the characterization [7],[13],[22],[29],[32],[33], gate driver design [34],[35],[36],[37], and converter evaluation [22],[33],[38]. However, the packaging of the semiconductor die has a significant impact on the performance, and is currently limiting their full potential; namely, their switching speed, voltage and current ratings, and operating temperature. Accordingly, the development of a suitable package will be critical for the adoption of high-voltage SiC devices.

However, the packaging of high-voltage SiC power semiconductors is nontrivial. The key benefits of these devices are also the primary challenges; specifically, the high-speed switching and the high voltage rating. A background of these

This work was supported in part by the UK Engineering and Physical Sciences Research Council (EPSRC) under grant EP/K035304/1 and the CPES High Density Integration Consortium.

C. DiMarino, G.-Q. Lu, D. Boroyevich, and R. Burgos are with Virginia Tech, Blacksburg, VA 24061 USA (e-mail: dimaricm@vt.edu, gqlu@vt.edu, dushan@vt.edu, rolando@vt.edu).

B. Mouawad and C. M. Johnson are with the University of Nottingham, Nottingham NG7 2RD UK (e-mail: bassem.mouawad@nottingham.ac.uk, mark.johnson@nottingham.ac.uk).

M. Wang and Y.-S. Tan are with Tianjin University, Tianjin CN (e-mail: meiyuwang01@126.com, tomorrow2019@hotmail.com).

challenges, review of solutions proposed in the literature, and the unique solutions proposed in this work are described in the remainder of this section.

Due to their faster switching capability, SiC devices are more sensitive to parasitic elements in the module package, as well as in the bus bar and gate driver circuitry, than silicon. In particular, parasitic inductances can resonate with the device parasitic capacitances, causing undesirable ringing that increases electromagnetic interference (EMI) [39]. Also, during high speed current transients (di/dt), these parasitic inductances can cause disastrous overvoltage across the drain-source of the device. This is particularly a concern in the event of a short-circuit fault since the di/dt values can far exceed those seen during normal operating conditions.

Moreover, in order to increase the module current rating, several die are connected in parallel. If there exists a wide variation in the parasitic inductances for each of the paralleled die, then current imbalance can occur during the switching transients. It has been shown for a commercial silicon IGBT module that the current overshoots for each of the paralleled die can vary by more than two times [40],[41]. The die that experience the higher current overshoots will have larger switching losses [40],[41], and thus higher junction temperatures [41], which can reduce the overall lifetime of the module. Since SiC transistors are faster than silicon IGBTs, this problem is intensified.

To mitigate these issues of voltage overshoot, ringing, and dynamic current imbalance, it has become common practice for module manufacturers to integrate resistors into the power module, and users to add external gate resistors to slow down the switching speed. Adding resistance is not an ideal solution since it increases the switching times and losses, thereby diminishing the high-speed, high-efficiency advantages of SiC devices.

Instead, it is preferable to develop a module package with lower parasitic inductances. Several research groups and manufacturers have proposed to reduce the package inductance by replacing the traditional wire bond interconnections with ribbon [42],[43]; flexible PCB [44],[45],[46],[47],[48], solid posts, shims, or bumps [49],[50],[51]; solder balls [52]; direct-bonded solder [53]; or vias in PCB or ceramic substrates [54],[55],[56],[57]. Several packages also include integrated decoupling capacitors to mitigate the impact of stray inductances [55],[58],[59],[60],[61].

These embedded capacitors can also be used to create a symmetric layout for the die, as proposed in [58],[60]. However, since the modules in [58],[60] use wire bonds for the interconnection, the capacitors must be placed beside the die, thereby increasing the footprint of the module. Instead, in [55], the capacitors are placed above the semiconductor devices, creating a vertical high-frequency power loop that does not increase the module footprint, as it takes advantage of the third dimension.

To date, the majority of these low-inductance packages have been developed for silicon and SiC devices with voltage ratings of 1.2 kV or less, though some packages for higher-voltage devices have been reported. In [50], a flip-chip sandwich

structure was applied for 3.3 kV silicon IGBTs. However, no electric field analysis or partial discharge (PD) tests were performed to ensure the package could reliably operate at the rated voltage. In [53], a sandwich structure with ceramic substrates on the top and bottom was used for a 6.5 kV silicon super GTO (SGTO). Electric field simulations showed that increasing the solder bondline thickness between the die and the top substrate could reduce the electric field in that region [53]. However, increasing the solder thickness increases the device junction temperature [53]. Benzocyclobutene (BCB) and underfill were also used for further insulation [53]. Leakage current tests at the rated device voltage of 6.5 kV were performed on the module [53]; however, this does not test the ability of the module to operate at the rated voltage for extended periods of time.

In addition to the parasitic inductances, parasitic capacitances within the power module are also a concern with high-speed devices, as they can become a path for commonmode (CM) current. In traditional power modules, there exists a parasitic capacitance across the insulating ceramic substrate (e.g., DBC). Since the cooling system (e.g., heatsink or coldplate) is generally grounded for safety, under high-speed voltage transients (dv/dt), this parasitic capacitance becomes a path for common-mode (CM) current to flow through the system ground [60]. This problem is especially critical for the fast-switching SiC devices, which have higher dv/dt transients than silicon IGBTs. Typically, filters and/or chokes are added to help reduce the EMI; however, these add cost, size, and complexity to the power conversion system. A simpler solution additional components is the that requires fewer implementation of a screen layer that returns the CM current back to the dc bus [62],[63],[64]. This can be realized with multilayer ceramic substrates, and has been shown to reduce the high-frequency noise [63],[64].

The high voltage rating of these SiC devices also poses a challenge for the packaging. To minimize the parasitic inductances and increase power density, it is desirable to have a compact power module; however, the high-voltage rating means the electric field strength within the package will be greater. If the electric field strength exceeds the electrical breakdown strength of the dielectric materials, then PD can occur, potentially causing permanent damage to the insulating materials, such as the insulating ceramic substrate [65]. Accordingly, the electric fields, both within the power module and at the external terminations to the rest of the power conversion system, must be carefully controlled. Recently, there has been focus on reducing the electric field strength near the insulating substrate, as this is typically where the PD occurs inside the power module [65],[66],[67].

Proposed solutions to reduce the electric field strength at this critical location include: increasing the ceramic thickness [65] and the permittivity of the encapsulation material [68]; adding a dielectric coating with high permittivity [69] or high breakdown field strength [70]; applying a high resistivity coating along the ceramic surface [70],[71]; using high permittivity non-linear dielectrics [72] or nonlinear resistive gel [73]; stacking multiple substrates [74]; and varying the metal-

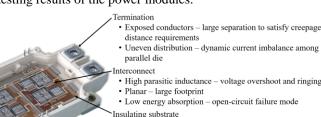

ceramic interface geometry [70],[75]. Of these methods, those that are simple to implement have limited improvement on the PD inception voltage (PDIV), and those that have the highest improvement are complicated to fabricate or have questionable reliability. Furthermore, none of these methods have been implemented and tested in an actual power module. The primary challenges with using traditional power modules for packaging high-speed, high-voltage WBG devices are summarized in Fig. 1.

The objective of this work is to push the boundaries of highdensity, high-speed, 10 kV power module packaging. The proposed 10 kV power module package enables the SiC devices to switch thousands of voltages in tens of nanoseconds with negligible voltage overshoot and ringing, while having low EMI, a small footprint, and high PDIV. The sandwich structures presented in [49] and [50] and the vertical-capacitor-loop reported in [55] are modified to create a low-inductance, symmetrical power module that is suitable for 10 kV SiC MOSFETs. The resulting module has a power-loop inductance of 4.4 nH, per MOSFET switch pair [76]. This is the lowest reported parasitic inductance for 10 kV power modules to date. Additionally, each MOSFET has its own gate and Kelvin source connection to the external gate driver, yielding symmetrical gate-loop inductances of 3.8 nH for each, thereby further improving the dynamic current sharing [76].

To reduce the EMI generated by this high-speed switching, a CM current screen that is fully integrated into the power module is proposed in this work. The proposed screen can reduce the ground current by 10 times [77]. This screening layer simultaneously increases the PDIV of the power module by 53 % [77]. To maintain low electric field strength in the air surrounding the power module, while also minimizing size and inductance, a unique housing and bus bar interfacing scheme is proposed. The bus bar compresses the spring terminals of the power module, creating a sealed connection so that there are no exposed conductors. In this way, creepage and clearance distances can be disregarded. Field-grading plates are included inside the bus bar to shift the peak electric field from the surrounding air to inside the solid dielectric. This is the first work reported in the literature to proposed electric field reduction methods both internal and external to the package of a high-density 10 kV SiC MOSFET power module.

In this paper, the detailed design of a high-power-density, high-speed, half-bridge power module package for 10 kV,  $350 \text{ m}\Omega$  SiC MOSFET die [13] will be presented. The fabrication procedures for the 10 kV module prototypes will then be discussed, followed by the dynamic characterization and PD testing results of the power modules.

Large parasitic capacitance – common-mode current

High electric field - partial discharge and breakdown

Fig. 1. Challenges with traditional power modules.

#### II. MODULE DESIGN

## A. Module Overview

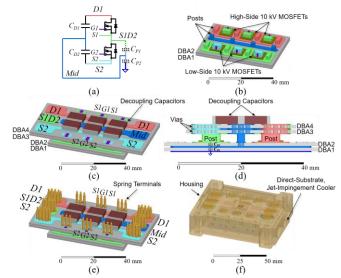

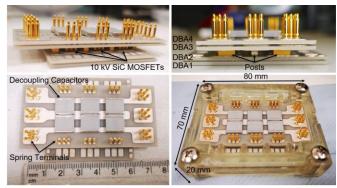

Fig. 2 shows the schematic and 3D model of the designed half-bridge power module. The colors of the metal pads in the 3D model (Fig. 2(b)–Fig. 2(f)) correspond to the node in the schematic (Fig. 2(a)) with the same color. The half-bridge module has three 10 kV, 350 m $\Omega$ , 8.1 mm  $\times$  8.1 mm die in parallel per switch position. To increase the power density and reduce the cost, no external antiparallel diodes will be used in the module; instead, the reverse current will flow through the MOSFET channel, and the body diode will only conduct during the dead time. This synchronous operation is made possible by the symmetrical reverse conduction and superior internal body diode of SiC MOSFETs, which have lower reverse recovery and thus lower losses than silicon MOSFET body diodes [78],[79]. In the past, conduction of the body diode of highvoltage SiC MOSFETs was avoided because it led to the propagation of stacking faults, which degraded the device performance [80],[81]. However, it was shown that the body diode of recent high-voltage SiC MOSFETs is stable [13],[82],[83]. As a result, Wolfspeed's latest 10 kV, 240 A module, does not include external antiparallel diodes [84].

The proposed module in this work has a planar, sandwich structure, using molybdenum (Mo) posts and direct-bonded-aluminum (DBA) substrates as the die interconnection instead of wire bonds. This type of structure allows for increased power density, and reduces the parasitic inductances and capacitances in the module, thereby improving the transient performance. Furthermore, by eliminating the wire bonds, the energy absorption capability during faults is increased, as shown in [85]. This structure also allows decoupling capacitors to be embedded within the module to further improve the dynamic performance without increasing the module footprint.

In total, four substrates are used in the power module: two beneath the die (DBA1 and DBA2) and two on the top (DBA3 and DBA4). The Mo posts act as standoffs that reduce the

Fig. 2. (a) Schematic, (b) bottom stacked substrates with six 10 kV SiC MOSFET die and posts, (c) top substrates stack and embedded decoupling capacitors, (d) side view with the vias shown, (e) module with spring terminals, and (f) housing with integrated direct-substrate cooler.

electric field strength between the die and the top DBA substrate. Mo was chosen as the post material because it has a coefficient of thermal expansion (CTE) of 4.9, which is closer to that of SiC (3.7) than Cu (17), and thus will result in lower thermomechanical stresses at the post–die interface [86].

The total module footprint is 74 mm  $\times$  49 mm  $\times$  11 mm without the housing. This gives a power density of 13 W/mm3. With the housing and integrated cooler, the dimensions become 83 mm  $\times$  68 mm  $\times$  25 mm, which results in a power density of 4 W/mm3. For reference, the power density of Wolfspeed's 10 kV, 240 A SiC MOSFET module is 4 W/mm3 without the cooling system [84]. Details of the module design will be discussed in the following subsections.

## B. Electric Field Reduction

To address the enhanced electric field associated with a high-voltage, high-density package, the ceramic substrate must be thoughtfully designed and evaluated. In power modules, the electric field concentrates at the intersection of the ceramic, metal, and encapsulation [65],[66],[87],[88]. This is known as the triple point. If this electric field exceeds the breakdown field strength of the insulation materials, such as the ceramic or encapsulation, then PD can occur. Repetitive PD events can ultimately result in insulation failure, such as cracking of the ceramic substrate, as shown in [65].

According to the literature, the PDIV for standard 1-mm-thick aluminum nitride (AlN) DBC substrates is less than 10 kV rms [65], and can be as low as 5 kV rms [74]. To achieve sufficient margin for 10 kV SiC MOSFETs, methods for reducing the peak electric field within the power module must be employed. The method proposed in this work, is an adaptation of the stacked-substrate approach presented in [74], which effectively increases the PDIV, and is simple to implement.

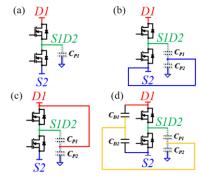

In [74], it was shown that stacking DBC substrates reduces the electric field strength within the bulk ceramic and at the critical triple points. The PD tests revealed that the PDIV could be increased by 94 % by stacking two 0.32-mm Al2O3 substrates compared to having a single 0.63-mm substrate [74]. However, the practical implementation of this method was not explored. In a power module, the top and bottom metal layers are not symmetrical; the top metal is patterned to create the circuit, and the traces are at different potentials during the module operation. As a result, it is not clear what potential should be applied to the middle metal layer to achieve a meaningful reduction in the electric field strength. This key factor in the realization of this method is explored in this work.

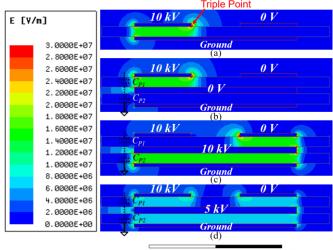

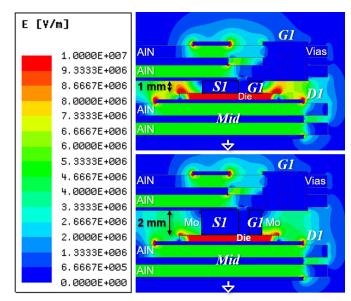

Fig. 3 shows the simulated 2D electric field distribution for the case when the top metal is patterned and has two different potentials. One of the potentials represents the drain of the high-side switch, and the other represents the drain of the low-side switch. The former is consistently at the positive dc bus potential while the latter switches between the positive and negative dc bus potentials. The worst-case scenario is when the low-side switch is conducting and its drain is at the negative dc bus potential. This worst-case was simulated. The positive dc bus is set to 10 kV, and the negative is set to 0 V. The bottommost metal is at the same potential as the cooling system, which

is grounded (0 V).

Fig. 3(a) shows the simulated electric field plot for a single DBA substrate. It can be seen that the electric field distribution is non-uniform within the bulk of the ceramic, and that the peak electric field occurs at the triple points. This peak electric field exceeds the typical dielectric strength for ceramic substrates (20 kV/mm).

Fig. 3(b) shows the simulated electric field plot for two stacked DBA substrates with the middle metal layer connected to the negative dc bus (0 V). Comparing Fig. 3(a) and Fig. 3(b), it can be seen that connecting the middle metal to the negative dc bus does not reduce the peak electric field at the triple point, nor does it improve the distribution within the bulk ceramic, compared to the single substrate case. This is because the bottom substrate has 0 V across it, while the top substrate has 10 kV. In this configuration, the bottom substrate does not help to support the voltage.

If the middle metal is connected to the positive dc bus, then the triple points at which the peak electric field occur will change, and the electric field distribution within the bulk ceramic will shift. This is shown in Fig. 3(c). However, the peak electric field, and therefore the PDIV, are similar to the case with a single substrate. This is because both the top and bottom substrates have 10 kV across them.

If the middle metal is connected to half of the bus voltage, then both the top and bottom substrates have a potential of 5 kV

Fig. 3. Simulated 2D electric field distribution for (a) a single substrate, and two stacked substrates with the middle metal at the (b) negative dc bus, (c) positive dc bus, and (d) dc bus midpoint.

across them. The simulated electric field distribution for this case is shown in Fig. 3(d). The peak electric field is reduced by 58 % compared to the single-substrate case (Fig. 3(a)), and the electric field in the bulk ceramic is uniformly distributed in the two substrates. Therefore, in this work, the middle metal layer of the DBA stack is connected to half of the bus voltage. This connection can be realized with the embedded decoupling capacitors. Each set of decoupling capacitors shown in Fig. 2(c) consists of two, 5-kV ceramic capacitors placed in series. It is proposed in this work to connect the midpoint of the capacitors to the middle metal layer of the bottom DBA stack through vias and metal posts, as shown in Fig. 1(d). This compact, integrated connection method is made possible by the sandwich structure.

The metal post between the die and the top substrate acts as a standoff to reduce the electric field and improve the voltage isolation. The optimal post height is a tradeoff between the electromagnetic and electrostatic performances; a shorter post height will reduce the parasitic inductances and resistances, but will increase the electric field strength. In [89], the influence of the post height on the electric field strength was evaluated. In this work, the electric field distribution of the module crosssection was simulated to determine the optimal height of the posts (Fig. 4). In this simulation, the voltage distribution was graded along the top surface of the 10 kV SiC MOSFET to mimic the guard rings of the MOSFET die, as was done in [89]. It can be seen from Fig. 4 that the electric field strength between the die and the top DBA reduces when the post height is increased from 1 mm to 2 mm. If the electric field between the die and the top DBA exceeds the breakdown field strength of the encapsulation material, then PD or breakdown could occur. Based on these results, a post height of 2 mm was selected for this work.

#### C. EMI Reduction

For the 10 kV SiC MOSFETs to switch at high speeds, the negative effects of the high dv/dt must be addressed. One such effect is the conducted EMI that flows through parasitic capacitances. The primary capacitance of concern is the one that exists across the ceramic substrate between the S1D2 terminal and the cooling system. The S1D2 node experiences high dv/dt as it switches between D1 and S2. Since the cooling system is often grounded, this capacitance becomes a path for current to flow through the system ground.

To resolve this issue, [62] proposed a method for diverting the current back to the dc bus by using two stacked direct-bonded-copper (DBC) substrates, where the intermediate metal layer is connected to either the positive or negative bus. The amount of current that is diverted will strongly depend on the high-frequency impedance of the connection back to the dc bus, so the implementation of this screen is critical. In [62], wire bonds are used for the interconnections, and "lugs" are used for the terminals. These connection types have large parasitic inductance, which will increase the high-frequency impedance, thereby reducing the effectiveness of the screen.

In [63], a similar screen is proposed. For this implementation, a multilayer DBC substrate, and integrated dc-link capacitors are used to create a low-inductance connection between the

Fig. 4. Simulated electric field distributions for 1-mm post height (top) and 2-mm post height (bottom).

middle metal layer and the negative dc bus [63]. This method resulted in a 14-dB reduction compared to the reference module [63],[64]. However, by connecting the middle metal to the negative dc bus, the top ceramic is providing all the voltage isolation, as shown by Fig. 3(b). Additionally, placing the capacitors on the same plane as the MOSFETs, as is done in [63], increases the footprint of the module.

To mitigate the conducted EMI for a compact, high-voltage design, this work connects the middle metal layer to the midpoint of the embedded decoupling capacitors, which are arranged above each MOSFET switch pair. This implementation results in a low-inductance path for the CM current to flow, balances and reduces the power-loop inductances for the MOSFET switch pairs, and reduces the peak electric field at the critical triple points without increasing the module footprint.

# D. System Integration

The module housing has a significant impact on the overall size, thermal resistance (current capacity), and voltage rating. To safely and reliably utilize the module at the rated voltage, creepage and clearance requirements [90], and PD and breakdown standards, should be considered. At 10 kV operating voltage, the minimum creepage distance is 100 mm for material group IIIa,b and pollution degree 2 [90]. This will significantly limit the minimum size of the power module. No previous literature was found on the development or investigation of high-density power module connectors for medium-voltage applications. Accordingly, a new connection scheme is proposed in this work.

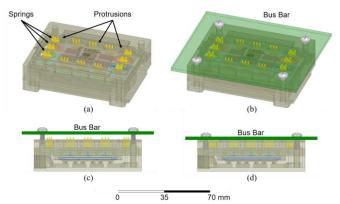

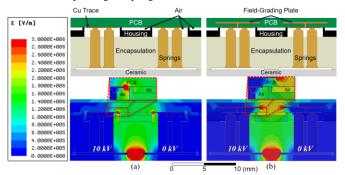

First, to circumvent the creepage and clearance requirements, a sealed connection is designed. The housing design and system interface scheme that was developed for this 10-kV power module is shown in Fig. 5. The external bus bar is mounted on top of the power module. Pressure is applied to the top of the bus bar through mounting screws. This pressure compresses the springs until the bus bar contacts the protrusions in the housing

Fig. 5. 3D model of the (a) module with the housing and lid, (b) module with the bus bar, (c) side view of the module, and (d) side view of the module with the bus bar compressing the spring terminals.

Fig. 6. Simulated electric field distribution (a) without and (b) with field-grading plates in the PCB.

lid. In this way, the springs are not exposed, and thus creepage and clearance restrictions do not apply.

Next, electric field strength for this connection scheme must be checked to ensure there will be sufficient PDIV and breakdown voltage. The electric field concentration in the air is critical due to the low dielectric strength of air (3 kV/mm). For this reason, protrusions were added to the housing lid (Fig. 4(a)). Without these protrusions, small air gaps could exist between the bus bar and the module lid; the smaller the air gap, the larger the electric field strength, and thus the lower the PDIV and breakdown voltage. Accordingly, increasing the height of the protrusions will increase the PDIV. However, increasing the height of the protrusions will also increase the inductance and resistance of the gate and power terminals. Given these considerations, a protrusion height of 1 mm was selected, though this air gap alone is not sufficient.

Fig. 6 shows the simulated 2D electric field distribution for a cross-section of the module—bus bar interface. As shown by Fig. 6(a), even with the 1-mm air gap, the electric field strength in the air exceeds 3 kV/mm. To further reduce the electric field strength in the air gap, this work proposes to add field-control plates within the bus bar. Fig. 6(b) shows how the field-grading plates can be used to shift the peak electric field strength from the air to the solid insulation of the bus bar, which has a greater dielectric strength. The plates shown in this embodiment are at the same potential as the spring terminals.

# E. Thermal Management

Traditional power modules have the substrates and housing mounted to a baseplate. The substrates are typically attached to

the baseplate with solder, which is susceptible to delamination and voiding, resulting in low reliability and high thermal resistance [91],[92]. Bending stresses caused by the baseplate can also cause cracking of the ceramic substrates and semiconductor die [91]. A thermal interface material is commonly used between the baseplate and the cooling system, which further increases the thermal resistance. Overall, the many layers used in this traditional stack-up result in high thermal resistance and low reliability.

Previous work has shown that the baseplate can be eliminated if the cooling system provides sufficiently high heat transfer [93],[94]. As shown in [93],[94], targeted jet-impingement cooling is able to satisfy this requirement. In this work, the baseplate and thermal grease are eliminated, and a targeted jetimpingement cooling system is integrated into the module housing. The bottom DBA is sealed to the housing, and the jets impinge the coolant directly onto the lower surface of the substrate. The impingement cells are located underneath each SiC MOSFET die for targeted, efficient cooling. Further details on the design, simulation, and testing of the cooling system used for the proposed power module can be found in [95]. The final power density of the designed module with the housing and jet-impingement cooler is 4 W/mm<sup>3</sup>, which is similar to that of the 10 kV, 240 A SiC MOSFET module in [84] without the cooling system.

#### III. MODULE FABRICATION

Table I summarizes the materials evaluated for the prototyping of the designed 10 kV power module. For each module component, several processing methods and materials were evaluated. Ag sintering was chosen for the substrate-substrate, die, and post attach because it creates a bond with lower voiding content, higher thermal conductivity, and improved reliability compared to solder [96].

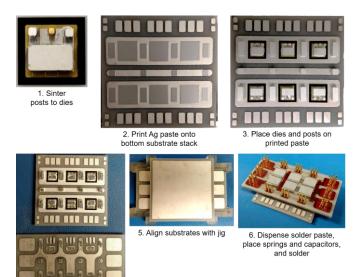

Fig. 7 shows one of the procedures used for prototyping the 10 kV SiC MOSFET power modules. In this procedure, pressure-less Ag sintering is used for the post and die attachments. Pressure-assisted sintering procedures were also evaluated (Table I). With proper equipment, it could be possible to sinter multiple components simultaneously, thereby reducing the number of steps and shortening the manufacturing time. The details of the fabrication steps will be discussed in the following subsections.

## A. Substrate Stacking

As shown in the previous section, stacking two ceramic substrates can reduce the electric field strength and conducted EMI of the power module. While multilayer ceramic substrates, such as LTCC [97],[98] and ceramic PCBs [99], are commercially available, they are not suitable for high power applications due to limited via sizes and Cu thicknesses. The performance of these multilayer ceramics under medium-voltages has also not been reported. As a result, in this work, a bonding process for attaching two separate substrates to create the stack was developed [100],[101].

A pressure-assisted Ag-sintering process was developed for bonding the  $50 \text{ mm} \times 50 \text{ mm}$  bottom and the  $35 \text{ mm} \times 75 \text{ mm}$

$TABLE\ I$  Packaging Processes and Materials Selected for the 10 kV SiC Module

| Component                     | Process                               | Material                     | Advantages                                                               |  |

|-------------------------------|---------------------------------------|------------------------------|--------------------------------------------------------------------------|--|

| Substrate                     | Direct-bonded aluminum (DBA)          | Ag-plated 1-mm AlN with vias | High thermal conductivity, voltage isolation, and reliability            |  |

|                               | Direct-bonded copper (DBC)            | Au-plated 1-mm AlN with vias | High thermal conductivity, voltage isolation                             |  |

| Substrate attach              | Pressure-assisted sintering           | Nano-Ag paste                | Low voiding and high thermal conductivity                                |  |

| Die attach                    | Pressure-less sintering               | Nano-Ag paste                | Low voiding, and high temperature, thermal conductivity, and reliability |  |

|                               | Pressure-assisted sintering           | Dried nano-Ag paste          | Low voiding, and high temperature, thermal conductivity, and reliability |  |

| Interconnect                  | e-beam deposition of Ti, Ni, and Ag   | Mo posts                     | Low inductance, low effective CTE                                        |  |

|                               | N/A                                   | Au-plated Cu-Mo-Cu posts     | Compatible with soldering, no extra processing                           |  |

| Interconnect<br>attach        | Pressure-less sintering               | Nano-Ag paste                | Low voiding and high thermal conductivity                                |  |

|                               | Pressure-assisted sintering           | Dried nano-Ag paste          | Low voiding and high thermal conductivity                                |  |

|                               | Soldering                             | Sn96.3/Ag3.7 paste           | Thick bondline, compliant                                                |  |

| Terminals                     | Pressure contact                      | Au-plated springs            | Round geometry, easy connection, good reliability                        |  |

| Terminal and capacitor attach | Soldering                             | Sn63/Pb37 paste              | Thick bondline, compliant, low melting temperature                       |  |

| Encapsulation                 | Deareation in vacuum, cure in furnace | Silicone gel                 | Good dielectric strength, medium hardness                                |  |

top stacked substrates. Ag sintering was chosen because of its lower voiding content and higher thermal conductivity and reliability compared to solder [96]. Furthermore, since the melting temperature after sintering (960 °C) is higher than the sintering temperature ( $\leq 260$  °C), the sample can undergo multiple sintering processes without affecting the previously-sintered joints. This allows the substrates, die, and posts to be easily attached in stages. Solder, on the other hand, will reflow

vacuum, and cure

Fig. 7. Module prototyping procedure with pressure-less sintering.

4. Print solder paste

when its melting point is reached. Accordingly, different solder alloys with varying melting points would be needed, which would limit the maximum operating temperature of the module.

For the developed large-area sintering process, 200-µm of the X-series nano-Ag paste from NBE Tech was printed onto one of the two substrates to be bonded. The printed paste was then dried in an oven at 130 °C for 30 minutes. The two substrates were then aligned and stacked together. The stacked sample was put into a hydraulic press, and 1 MPa was slowly applied. The temperature was then increased to 260 °C and held for 30 minutes to perform the sintering. After the sintering, the hotplate was turned off and the sample cooled under pressure. This prevents the substrate from bending due to CTE mismatch between the Al and AlN and the differences in the metal patterns between the two substrates. It is important to have uniform pressure distribution during this sintering process. If the pressure is not uniform, then the force applied to the substrate will not be homogeneously distributed and could result in cracking of the ceramic or poor bonding quality.

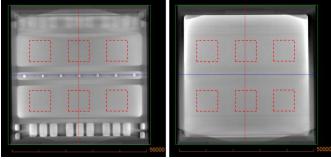

X-ray computed tomography (XCT) scans were performed to check the quality of the bonding layer and condition of the ceramic. The XCT images do not show any significant cracks, voids, defects, or misalignment (Fig. 8). It is particularly important to have low voiding content in the areas below the SiC MOSFET die so the heat can be effectively removed. The approximate die locations are outlined in Fig. 8. No significant voiding is observed in these critical areas.

To further check the thermal characteristics of the sintered bottom substrates, thermal impedance tests were performed at six locations along the surface of the sample where the SiC die would be located [96]. Cumulative structure-function analysis was then used to find the thermal resistance of the bond-line at each location [100]. The measured thermal resistances were 0.11 K/W to 0.14 K/W, which indicate good uniformity of the bond, and confirms that no large voids or cracks exist in these

Fig. 8. XCT images of the substrate stack after sintering. The dashed red boxes indicate the approximate location of the 10 kV SiC MOSFET die.

Fig. 9. X-ray image of the die attach layer for the 8.1~mm x 8.1~mm 10 kV die using the pressure-less sintering process.

locations.

#### B. Post Attachment

Mo posts are used to increase the distance and thereby reduce the electric field between the die and the top substrate. Mo was chosen because it has a low CTE, which reduces the thermomechanical stresses on the die. Pressure-less and pressure-assisted Ag sintering methods were evaluated for the post attachment. For the pressure-less sintering of the Mo post to the substrate, 50-µm-thick Ag paste was stenciled onto the substrate. The posts were then placed on top of the stenciled paste, and the sample was transferred to a hotplate and sintered. Bonding strengths between 31 MPa and 67 MPa (depending on the area of the post) were achieved when the posts were sintered to a Ag-plated substrate. The shear strength between the Mo posts and the MOSFET die using the same process were 47 MPa, on average, for the Kelvin source posts (1.0 mm × 1.0 mm) and 33 MPa for the power source posts (5.2 mm × 3 mm).

For the pressure-assisted process, Ag paste was dried and then the posts were stamped onto the dry film. This stamping transfers the Ag film to the post. The sample was then sintered under 10 MPa. This pressure-assisted sintering method yielded comparable bonding strength as the pressure-less process.

# C. Semiconductor Die Attachment

As mentioned above, Ag sintering was chosen for the die attach because it has been shown to have lower thermal impedance and higher thermal cycling capability compared to solder [96]. Both pressure-less and pressure-assisted Ag sintering processes using different types of nano-Ag paste were evaluated. The 10 kV SiC MOSFET die are 8.1 mm  $\times$  8.1 mm  $\times$  0.5 mm and have Au backside metallization. Since Ag diffuses faster than Au, a sintering profile that limits the Ag diffusion is needed to prevent the formation of Kirkendall

Fig. 10. 10 kV SiC MOSFET module prototype.

voids, which cause low shear strength [102],[103]. In this work, the sintering temperature was lowered to 230 °C and held for 90 minutes. This profile resulted in an average shear strength of 15 MPa, with a peak of 18 MPa. X-ray images of the sintered die attach layer shows low voiding content and defect density (Fig. 9).

Applying pressure during sintering can further improve the shear strength by creating a denser Ag layer [102]. However, pressure-assisted sintering can be more complex, especially when sintering multiple die simultaneously, since the pressure must be uniformly applied to all the die. For the pressure-assisted process, 100-µm-thick Ag paste was printed onto the substrate, and then dried in an oven at 130 °C for 10 minutes. Once the paste was dried, a 10-kV die was placed on top, and the sample was sintered in a hydraulic press at 250 °C and 10 MPa for 5 minutes. The die shear strength of the pressure-assisted Ag-sintered sample was 25 MPa.

# D. Module Assembly

The top substrate stack is attached to the posts using solder paste. Solder is chosen for this bonding instead of sintering because it can create a thicker bondline to accommodate height tolerances and curvature of the substrates, and it is more compliant so it will enable some thermomechanical movement. The spring terminals and decoupling capacitors were also attached with solder. The springs used in this power module have a continuous current rating of 10 A [104]. The shear strength for the soldered springs, which have a diameter of 1.88 mm, is 64 MPa on average, with a maximum of 70 MPa.

The housing and integrated jet-impingement cooler were 3D printed out of high-temperature resin [105]. Silicone sealant was used to seal the bottom substrate stack to the housing. After curing, the module was encapsulated. Silicone gel was selected for the encapsulation because of its simple processing and good reliability and dielectric strength [69],[106]. Silicone gels with low viscosity were chosen so that the encapsulant can fill small gaps in the power module, leaving fewer air pockets. Fig. 10 shows the 10 kV SiC MOSFET module prototype. The testing of the module prototypes will be presented in the following section.

## IV. MODULE TESTING

# A. Dynamic Characterization

To evaluate the switching performance of the module,

double-pulse tests (DPT) were conducted. Fig. 11 shows the gate-source and drain-source voltage waveforms for the turn-on and turn-off transients for the DPTs performed on a scaleddown module prototype with two 10 kV SiC MOSFET die. The switching tests were performed at 5 kV and 20 A with turn-on and turn-off gate resistances of 0.33  $\Omega$  and 0.17  $\Omega$ , respectively. The drain current could not be measured due to the embedded decoupling capacitors and compact design. Table II lists the measured overshoot, undershoot, rise and fall times, and switching rates from the DPTs. During the turn-on transient, the fall time of the drain-source voltage was 16 ns (250 V/ns). At turn-off, the voltage rise time was 50 ns (80 V/ns). The voltage rise time is slower because it is controlled by the output capacitance and load current. Negligible voltage overshoot and ringing were measured, indicating low power- and gate-loop inductances. This is due to the low-inductance module design, as well as careful layout and connection of the gate driver, bus bar, external decoupling capacitors, and measurement probes.

To the best of the author's knowledge, these are the fastest switching speeds reported for similarly-rated SiC MOSFETs and IGBTs [33],[84],[107],[108],[109]. In [84], switching results for a module populated with a single die had turn-on and turn-off transition times of approximately 80 ns and 120 ns, respectively, giving switching speeds of 88 V/ns and 58 V/ns at a bus voltage of 7 kV, drain current of 15 A, and gate resistance of 21  $\Omega$ . The switching waveforms also showed a moderate voltage overshoot of approximately 300 V (4.3 %) [84].

## B. Common-Mode Current Test

Further switching tests were performed to evaluate the impact of this high-speed switching on the conducted EMI. For these tests, the current through the ground path was measured

Fig. 11. (a) Turn-on and (b) turn-off gate-source (blue, right axis) and drain-source (red, left axis) voltages.

TABLE II  $10~\text{kV}, 350~\text{m}\Omega~\text{SiC MOSFET Module Prototype Switching Results}$

| D          | Value               |                      |  |

|------------|---------------------|----------------------|--|

| Parameter  | Gate-Source Voltage | Drain-Source Voltage |  |

| Overshoot  | None                | None                 |  |

| Undershoot | None                | None                 |  |

| Rise time  | 24 ns               | 50 ns                |  |

| Rise dv/dt | 0.9 V/ns            | 80 V/ns              |  |

| Fall time  | 26 ns               | 16 ns                |  |

| Fall dv/dt | 0.8 V/ns            | 250 V/ns             |  |

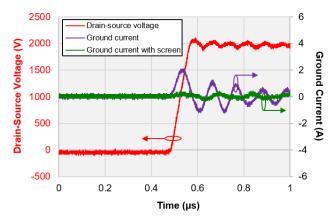

using an RF current transformer with a bandwidth of 200 MHz. Fig. 12 shows the turn-off drain-source voltage and ground current waveforms with and without the proposed CM screen. The dv/dt at this turn-off transient was 24 V/ns. This slower dv/dt is due to the lower bus voltage and larger device capacitance due to the three MOSFET die in parallel per switch position. A slower dv/dt was desired to improve the measurement accuracy.

For the case without the CM screen, the middle metal layer of the bottom substrate stack was left floating, and the measured peak current through the ground path during the turn-off transient was 2 A (Fig. 12). This peak current will increase as the dc bus voltage, and therefore the dv/dt, increases. When the middle metal layer of the bottom substrate stack was connected to the midpoint of two series decoupling capacitors, the peak current reduced to 0.2 A. This is an order of magnitude reduction, and validates the effectiveness of the proposed integrated CM screen.

# C. Partial Discharge Test

PD tests were conducted to validate the electrostatic simulation results. The PD tests were performed using a 50 kV, 60-Hz ac excitation source, and a Doble PD Smart with the HFCT-300 sensor to detect the PD events [110]. PD tests were performed on a patterned, 1-mm-thick AlN-DBA substrate with 2-mm spacing between metal traces. Three cases were tested: 1) a single substrate, 2) two stacked substrates with the middle metal connected to the source ground, and 3) two stacked

Fig. 12. Measured drain-source (red, left axis) and ground current (right axis) waveforms with (green) and without (purple) the CM screen at 2 kV and 20 A with no external gate resistance.

substrates with the middle metal connected to half of the applied excitation voltage. Each case was tested under the worst-case switching state, which is when the high-side switch is blocking and the low-side switch is conducting such that S1D2 is equal to S2.

First, the PD tests were performed with the samples in air in order to have a high signal-to-noise ratio. These tests revealed that, as was shown in the electrostatic simulations, the PD for the DBA substrates will occur at the triple points. Specifically, the PD will take place along the edge of the metal pad where the high potential is applied. The resulting PDIV for the cases when the samples are tested in air are listed in Table III. When the middle metal is connected to half of the applied voltage, the PDIV increases by 53 % compared to the single-substrate case. These results are in good agreement with the simulations.

Since the power module will be encapsulated, PD tests were also performed on a stacked substrate sample that was encapsulated with silicone gel. When the middle metal is connected to the source ground, the PDIV is 7.4 kV rms (10.5 kV peak). For this same case, breakdown occurred at 8.5 kV rms (12.0 kV peak). This means if the middle metal is connected to ground, or if a single substrate is used, then there is 20 % margin between the peak breakdown voltage and the voltage rating of the 10 kV SiC MOSFETs.

When the middle metal is connected to half of the applied voltage, no PD could be measured up to 10.5 kV rms (14.8 kV peak). The testing was stopped at 10.5 kV rms due to the reduced signal-to-noise ratio. This suggests that encapsulated stacked substrates with the middle metal connected to half of the applied voltage will have more than a 40 % higher PDIV compared to a single substrate or a stacked substrate with the middle metal connected to ground. Therefore, it is advantageous to use the stacked substrate structure with the middle metal connected to half the applied voltage in order to increase the high-voltage performance of the power module.

# D. Thermal Characterization

To evaluate the performance of the integrated direct-substrate, jet-impingement cooler, thermal impedance measurements were carried out on a Mentor Graphics Power Tester [111]. The lowest junction-to-ambient specific thermal resistance of the module was measured to be 26 mm2·K/W (0.38 K/W) for a flowrate of 0.47 l/min. Further details on the thermal characterization of the cooling system developed for this power module can be found in [95].

# V. CONCLUSION

This work proposed a high-density power module for 10 kV SiC MOSFETs with high-speed switching, improved high-voltage performance, and lower CM current. The optimal layout and system interface enabled the module to switch 5 kV in tens of nanoseconds with negligible ringing and voltage overshoot. This is the fastest switching speed reported to date for 10 kV SiC MOSFETs. The significantly reduced switching losses will enable medium-voltage converters to hard switch thousands of volts at tens of kilohertz while maintaining high efficiency. The increased switching frequency will dramatically

TABLE III

PARTIAL DISCHARGE TESTING SUMMARY

| Sample                  | Voltage of<br>Middle Metal | Surrounding<br>Medium | PDIV (rms) |

|-------------------------|----------------------------|-----------------------|------------|

| Single Substrate        | N/A                        | Air                   | 1.7 kV     |

| Stacked<br>Substrates   | $1/2 \times V_{AC}$        | Air                   | 2.6 kV     |

| Encapsulated<br>Stacked | 0 V                        | Silicone gel          | 7.4 kV     |

| Stacked Substrates      | $1/2 \times V_{AC}$        | Silicone gel          | >10.5 kV   |

reduce the size of the passive components, thereby further increasing the power density of the system.

However, this high-speed switching can reduce the PDIV and increase the conducted EMI. To increase the PDIV, it is proposed in this work to stack two substrates and connect the middle metal layer to the dc bus midpoint. This method was shown to increase the PDIV by 53 % compared to that for a single substrate. This connection also forms a low-impedance path at high frequency, diverting the current that would normally flow to the system ground to the bus through the embedded decoupling capacitors. Switching tests revealed a ten-time reduction in the ground current. This simple, integrated solution enables the 10 kV SiC MOSFETs to switch at high speeds without compromising the voltage isolation or system integrity. Moreover, the integrated screen reduces the need for external filters, thereby reducing the size and complexity of the power conversion system.

#### ACKNOWLEDGMENT

The authors would like to acknowledge the simulation and design assistance from Jianfeng Li and Robert Skuriat, and experimental assistance from Ke Li, Yue Xu, and Shan Gao. The authors also acknowledge the assistance of Dr. Xiangyong Feng and the Center for Electromechanics at the University of Texas at Austin in conducting the partial discharge tests. The DBA substrates used in the power module prototypes were donated by DOWA, the X-series nano-Ag paste was donated by NBE Tech, and the external decoupling capacitors used for the switching tests were donated by Electronic Concepts. This work was conducted with the use of ANSYS Maxwell 2D, ANSYS Maxwell 3D, ANSYS Q3D Extractor, and ANSYS Workbench, donated in-kind by Ansoft Corporation of the CPES Industry Partnership Program.

#### REFERENCES

- [1] B. K. Bose, "The past, present, and future of power electronics," *IEEE Ind. Electron. Mag.*, vol. 3, no. 2, pp. 7-11, June 2009.

- [2] J. Rabkowski, D. Peftitsis, H. P. Nee, "Silicon carbide power transistors-A new era in power electronics is initiated," *IEEE Ind. Electron. Mag.*, vol. 6, no. 2, pp. 17-26, June 2012.

- [3] J. Millan, P. Godignon, X. Perpina, A. Perez-Tomas, J. Rebollo, "A survey of wide bandgap power semiconductor devices," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2155-2163, May 2014.

- [4] H. Zhang, L. M. Tolbert, B. Ozpineci, "Impact of SiC devices on hybrid electric and plug-in hybrid electric vehicles," *IEEE Trans. Ind. Appl.*, vol. 47, no. 2, pp. 912-921, Mar.-Apr. 2011.

- [5] A. Bindra, "SiC-based PV inverters display reduced size, weight and cost," How2Power Today, May 2013.

- [6] "Train trial shows a 40 % energy saving for SiC inverters," *Drives and Controls*, June 2015.

- [7] J. W. Palmour, L. Cheng, V. Pala, E. V. Brunt, D. J. Lichtenwalner, G. Y. Wang, J. Richmond, M. O'Loughlin, S. Ryu, S. T. Allen, A. A. Burk, C. Scozzie, "Silicon carbide power MOSFETs: Breakthrough performance from 900 V up to 15 kV," in *IEEE International Symposium on Semiconductor Devices and IC's*, June 2014.

- [8] T. Lu, Z. Zhao, S. Ji, H. Yu, L. Yuan, "Parameter design of voltage balancing circuit for series connected HV-IGBTs," in *IEEE International Power Electronics and Motion Control Conference*, June 2012.

- [9] H. Mirzaee, A. De, A. Tripathi, S. Bhattacharya, "Design comparison of high-power medium-voltage converters based on a 6.5-kV Si-IGBT/Si-PiN diode, a 6.5-kV Si-IGBT/SiC-JBS diode, and a 10-kV SiC-MOSFET/SiC-JBS diode," *IEEE Trans. Ind. Appl.*, vol. 50, no. 4, July/Aug. 2014.

- [10] J. Casarin, P. Ladoux, P. Lasserre, "10kV SiC MOSFETs versus 6.5kV Si-IGBTs for medium frequency transformer application in railway traction," in *IEEE International Conference on Electrical Systems for Aircraft, Railway, Ship Propulsion, and Road Vehicles*, Mar. 2015.

- [11] T. Sakaguchi, M. Aketa, T. Nakamura, M. Nakanishi, M. Rahimo, "Characterization of 3.3 kV and 6.5 kV SiC MOSFETs," in *International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management*, May 2017.

- [12] S. Sabri, E. Van Brunt, A. Barkley, B. Hull, M. O'Loughlin, A. Burk, S. Allen, J. Palmour, "New generation 6.5 kV SiC power MOSFET," in *IEEE Workshop on Wide Bandgap Power Devices and Applications*, Nov. 2017.

- [13] V. Pala, E. V. Brunt, L. Cheng, M. O'Loughlin, J. Richmond, A. Burk, S. T. Allen, D. Grider, J. W. Palmour, "10 kV and 15 kV silicon carbide power MOSFETs for next-generation energy conversion and transmission systems," in *IEEE Energy Conversion Congress and Exposition*, Sept. 2014.

- [14] J. L. Hostetler, P. Alexandrov, X. Li, L. Fursin, A. Bhall, "6.5 kV SiC normally-off JFETs—technology status," in *IEEE Workshop on Wide Bandgap Power Devices and Applications*, Oct. 2014.

- [15] J. L. Hostetler, X. Li, P. Alexandrov, X. Huang, A. Bhalla, M. Becker, J. Colombo, D. Dieso, J. Sherbondy, "6.5 kV enhancement mode SiC JFET based power module," in *IEEE Workshop on Wide Bandgap Power Devices and Applications*, Nov. 2015.

- [16] S. Sundaresan, S. Jeliazkov, B. Grummel, R. Singh, "10 kV SiC BJTs—static, switching and reliability characteristics," in *International Symposium on Power Semiconductor Devices and IC's*, May 2013.

- [17] D. C. Patel, A. Kadavelugu, S. Madhusoodhanan, S. Bhattacharya, K. Hatua, S. Leslie, S. H. Ryu, D. Grider, A. Agarwal, "15 kV SiC IGBT based three-phase three-level modular-leg power converter," in *IEEE Energy Conversion Congress and Exposition*, Sept. 2013.

- [18] K. Hatua, S. Dutta, A. Tripathi, S. Baek, G. Karimi, S. Bhattacharya, "Transformer less intelligent power substation design with 15kV SiC IGBT for grid interconnection," in *IEEE Energy Conversion Congress and Exposition*, Sept. 2011.

- [19] L. Cheng, A. K. Agarwal, C. Capell, M. O'Loughlin, E. V. Brunt, K. Lam, J. Richmond, A. Burk, J. W. Palmour, H. O'Brien, A. Ogunniyi, C. Scozzie, "20 kV, 2 cm², 4H-SiC gate turn-off thyristors for advanced pulsed power applications," in *IEEE Int. Conf. Plasma Sci.*, June 2013.

- [20] X. Song, A. Q. Huang, M. Lee, C. Peng, L. Cheng, H. O'Brien, A. Ogunniyi, C. Scozzie, J. Palmour, "22 kV SiC emitter turn-off (ETO) thyristors and its dynamic performance including SOA," in *IEEE International Symposium on Semiconductor Devices and IC's*, May 2015.

- [21] X. Song, A. Q. Huang, M.-C. Lee, C. Peng, "Theoretical and experimental study of 22 kV SiC emitter turn-off (ETO) thyristor," *IEEE Trans. Power Electron.*," vol. 32, no. 8, pp. 6381-6393, Aug. 2017.

- [22] S. Madhusoodhanan, A. Tripathi, D. Patel, K. Mainali, A. Kadavelugu, S. Hazra, S. Bhattacharya, K. Hatua, "Solid state transformer and MV grid tie applications enabled by 15 kV SiC IGBTs and 10 kV SiC MOSFETs based multilevel converters," *IEEE Trans. Ind. Appl.*, vol. 51, no. 4, pp. 3343-3360, Aug. 2015.

- [23] IEEE Recommended Practice for 1 kV to 35 kV Medium-Voltage DC Power Systems on Ships, IEEE Standard 1709-2010, pp. 1-54, Nov. 2010.

- [24] C. Zhao, D. Dujic, A. Mester, J. K. Steinke, M. Weiss, S. Lewdeni-Schmid, T. Chaudhuri, P. Stefanutti, "Power electron traction transformer-Medium voltage prototype," *IEEE Trans. Ind. Electron.*, vol. 61, no. 7, pp. 3257-3268, Aug. 2013.

- [25] S. Srdic, X. Liang, C. Zhang, W. Yu, S. Lukic, "A SiC-based high-performance medium-voltage fast charger for plug-in electric vehicles," in *IEEE Energy Conversion Congress and Exposition*, Sept. 2016.

- [26] M. S. Chinthavali, L. M. Tolbert, B. Ozpineci, "4H-SiC GTO thyristor and p-n diode loss models for HVDC converter," in *IEEE Industry Applications Conference*, Oct. 2004.

- [27] Y. Koyama, Y. Nakazawa, H. Mochikawa, A. Kuzumaki, K. Sano, N. Okada, "A transformerless 6.6-kV STATCOM based on a hybrid cascade multilevel converter using SiC devices," in *IEEE Trans. Power Electron.*, vol. 33, no. 9, pp. 7411-7423, Nov. 2017.

- [28] P. Wolfs, F. Yang, Q.-L. Han, "Distribution level SiC FACTS devices with reduced dc bus capacitance for improved load capability and solar integration," in *IEEE International Symposium on Industrial Electronics*, June 2014.

- [29] M. K. Das, C. Capell, D. E. Grider, S. Leslie, J. Ostop, R. Raju, M. Schutten, J. Nasadoski, A. Hefner, "10 kV, 120 A SiC half H-bridge power MOSFET modules suitable for high frequency, medium voltage applications," in *IEEE Energy Conversion Congress and Exposition*, Sept. 2011.

- [30] R. Chattopadhyay, S. Bhattacharya, N. C. Foureaux, S. M. Silva, F. Braz Cardoso, H. de Paula, I. A. Piers, P. C. Cortizio, L. Moraes, J. A. de S. Brito, "Low-voltage PV power integration into medium voltage grid using high-voltage SiC devices," in *International Power Electronics Conference*, May 2014.

- [31] A. Q. Huang, Q. Zhu, L. Wang, L. Zhang, "15 kV SiC MOSFET: An enabling technology for medium voltage solid state transformers," CPSS Trans. Power Electron. Appl., vol. 2, no. 2, pp. 118-130, Aug. 2017.

- [32] M. Das, C. Capell, D. Grider, S. Leslie, J. Ostop, R. Raju, M. Schutten, J. Nasadoski, A. Hefner, "10 kV, 20 A SiC half H-bridge power MOSFET modules suitable for high frequency, medium voltage applications," in *IEEE Energy Conversion Congress and Exposition*, Sept. 2011.

- [33] K. Vechalapu, S. Bhattacharya, E. Van Brunt, S.-H. Ryu, D. Grider, J. W. Palmour, "Comparative evaluation of 15-kV SiC MOSFET and 15-kV SiC IGBT for medium-voltage converter under the same dv/dt conditions," in *IEEE J. Emerging Sel. Topics Power Electron.*, vol. 5, no. 1, pp. 469-489, Mar. 2017.

- [34] A. Kadavelugu, "Medium voltage power conversion enabled by 15 kV SiC IGBTs," Ph.D. dissertation, North Carolina State Univ., NC, 2015.

- [35] X. Zhang, H. Li, J. A. Brothers, L. Fu, M. Perales, J. Wu, J. Wang, "A gate drive with power over fiber-based isolated power supply and comprehensive protection functions for 15-kV SiC MOSFET," *IEEE J. Emerging Sel. Topics Power Electron.*, vol. 4, no. 3, pp. 946-955, Sept. 2016

- [36] A. Tripathi, K. Mainali, S. Madhusoodhanan, A. Yadav, K. Vechalapu, S. Bhattacharya, "A MV intelligent gate driver for 15kV SiC IGBT and 10kV SiC MOSFET," in *IEEE Applied Power Electronics Conference and Exposition*, Mar. 2016.

- [37] D. Berning, T. Duong, J. Ortiz-Rodfriguez, A. Rivera-Lopez, A. Hefner, "High-voltage isolated gate drive circuit for 10 kV, 100 A SiC MOSFET/JBS power modules," in *IEEE IAS Annual Meeting*, pp. 1-7, 2008

- [38] S. Moballegh, S. Madhusoodhanan, S. Bhattacharya, "Evaluation of high voltage 15 kV SiC IGBT and 10 kV SiC MOSFET for ZVS and ZCS high power DC -DC converters," in *International Power Electronics Conference*, May 2014.

- [39] F. Merienne, J. Roudet, J. L. Schanen, "Switching disturbance due to source inductance for a power MOSFET: analysis and solutions," in *IEEE Power Electronics Specialists Conference*, June 1996.

- [40] R. Wu, L. Smimova, H. Wang, F. Iannuzzo, F. Blaabjerg, "Comprehensive investigation on current imbalance among parallel chips inside MW-scale IGBT power modules," in *International Conference on Power Electronics and Energy Conversion Congress and Exposition Asia*, June 2015.

- [41] Y. Zhong, J. Meng, P. Ning, D. Zhang, X. Wen, "Comprehensive comparative analysis of two types of commonly-used layouts of IGBT packages," in *International Conference on Electrical Machines and Systems*, Oct. 2014.

- [42] C. Luechinger, "Large aluminum ribbon bonding: an alternative interconnect solution for power module applications," in *International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management*, May 2005.

- [43] E. Milke, T. Mueller, "High temperature behaviour and reliability of Alribbon for automotive applications," in *Electronics System-Integration Technology Conference*, Sept. 2008.

- [44] T. Stockmeier, P. Beckedahl, C. Gobl, T. Malzer, "SKiN: Double side sintering technology for new packages," in *IEEE International* Symposium on Semiconductor Devices and IC's, May 2011. repeated

- [45] B. Ozmat, C. S. Korman, R. Fillion, "An advanced approach to power module packaging," in *International Workshop on Integrated Power Packaging*, July 2000.

- [46] R. Fillion, E. Delgado, R. Beaupre, P. McConnelee, "High power planar interconnect for high frequency converters," in *Electronics Packaging Technology Conference*, Dec. 2004.

- [47] L. D. Stevanovic, R. A. Beaupre, E. C. Delgado, A. V. Gowda, "Low inductance power module with blade connector," in *IEEE Applied Power Electronics Conference and Exposition*, Feb. 2010.

- [48] J. G. Bai, G.-Q. Lu, X. Liu, "Flip-chip on flex integrated power electronics modules for high-density power integration," IEEE Trans. on Advanced Packaging, vol. 26, no. 1, pp. 54-59, Feb. 2003.

- [49] S. Haque, K. Xing, R. L. Lin, C. T. A. Suchicital, G. Q. Lu, D. J. Nelson, D. Borojevic, F. C. Lee, "An innovative technique for packaging power electronic building blocks using metal posts interconnected parallel plate structures," *IEEE Trans. Advanced Packag.*, vol. 22, no. 2, pp. 136-144, May 1999.

- [50] B. Mouawad, J. Li, A. Castellazzi, C. M. Johnson, "Hybrid half-bridge package for high voltage application," in *IEEE International Symposium* on Semiconductor Devices and IC's, June 2016.

- [51] J. N. Calata, J. G. Bai, X. Liu, S. Wen, G.-Q. Lu, "Three-dimensional packaging for power semiconductor devices and modules," IEEE Trans. on Advanced Packaging, vol. 28, no. 3, pp. 404-412, Aug. 2005.

- [52] Z. Liang, P. Ning, F. Wang, L. Marlino, "A phase-leg power module packaged with optimized planar interconnections and integrated doublesided cooling," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 2, no. 3, pp. 443-450, Sept. 2014.

- [53] H. Zhang, S. S. Ang, A. Mantooth, J. C. Balda, "A 6.5kV wire-bondless, double-sided cooling power electronic module," IEEE Energy Conversion Congress and Exposition, Sept. 2012.

- [54] A. B. Sharma, D. Paul, M. Kreck, Y. Rahmoun, P. Anders, M. Gruber, T. Huesgen, "PCB embedded power package with reinforced top-side chip contacts," 6th Electronic System-Integration Technology Conference, Sept. 2016.

- [55] E. Hoene, A. Ostmann, C. Marczok, "Packaging very fast switching semiconductors," in *International Conference on Integrated Power Electronics Systems*, Feb. 2014.

- [56] J. Yin, Z. Liang, J. D. van Wyk, "High temperature embedded SiC chip module (ECM) for power electronics applications," IEEE Trans. on Power Electronics, vol. 22, no. 2, pp. 392-398, Mar. 2007.

- [57] A. Alderman, L. L. Burgyan, B. Narveson, E. Parker, "3-D embedded packaging technology: analyzing its needs and challenges," *IEEE Power Electron. Mag.*, vol. 2, no. 4, pp. 30-39, Dec. 2015.

- [58] K. Takao, S. Kyogoku, "Ultra low inductance power module for fast switching SiC power devices," in *IEEE International Symposium on Semiconductor Devices and IC's*, May 2015.

- [59] Y. Ren, X. Yang, F. Zhang, L. Tan, X. Zeng, "Analysis of a low-inductance packaging layout for full-SiC power module embedding split damping," in *IEEE Applied Power Electronics Conference and Exposition*, Mar. 2016.

- [60] A. Domurat-Linde, E. Hoene, "Analysis and reduction of radiated EMI of power modules," in *International Conference on Integrated Power Electronics Systems*. Mar. 2012.

- [61] Z. Chen, Y. Yao, D. Boroyevich, K. D. T. Ngo, P. Mattavelli, K. Rajashekara, "A 1200-V, 60-A SiC MOSFET multichip phase-leg module for high-temperature, high-frequency applications," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2307-2320, May 2014.

- [62] D. Domes, "Semiconductor arrangement," U.S. Patent 2013/0043593 A1, Feb. 21, 2013.

- [63] T. Huber, A. Kleimaier, S. Polster, O. Mathieu, "Low inductive SiC power module design using ceramic multilayer substrates," in International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, June 2018.

- [64] T. Huber, A. Kleimaier, R. Kennel, "Ultra-low inductive power module design with integrated common mode noise shielding," in *European Conference on Power Electronics Applications*, Sept. 2017.

- [65] C. Bayer, U. Waltrich, R. Schneider, A. Soueidan, E. Baer, A. Schletz, "Enhancing partial discharge inception voltage of DBCs by geometrical variations based on simulations of the electric field strength," in *International Conference on Integrated Power Electronics Systems*, Mar. 2016.

- [66] G. Mitic, G. Lefranc, "Localization of electrical-insulation-and partial-discharge fialures of IGBT modules," *IEEE Trans. Ind. Appl.*, vol. 38, no. 1, pp. 175-180, Jan./Feb. 2002.

- [67] H. Chen, W. Cao, P. Bordignon, R. Yi, H. Zhang, W. Shi, "Design and testing of the world's first single-level press-pack IGBT based submodule for MMC VSC HVDC applications," in *IEEE Energy Conversion* Congress and Exposition, Sept. 2015.

- [68] C. F. Bayer, U. Waltrich, A. Soueidan, R. Schneider, E. Baer, A. Schletz, "Enhancement of the partial discharge inception voltage of DBCs by adjusting the permittivity of the encapsulation," in *International Conference on Integrated Power Electronics Systems*, Mar. 2016.

- [69] U. Waltrich, C. F. Bayer, M. Reger, A. Meyer, X. Tang, A. Schletz, "Enhancement of the partial discharge inception voltage of ceramic substrates for power modules by trench coating," in *International Conference on Electronics Packaging*, pp. 536-541, Apr. 2016.

- [70] D. Frey, J. L. Schanen, J. L. Auge, O. Lesaint, "Electric field investigation in high voltage power modules using finite element simulations and partial discharge measurements," in *Industry Applications Society Annual Meeting*, Oct. 2003.

- [71] G. Mitic, T. Licht, G. Lefranc, "IGBT Module Technology with High Partial Discharge Resistance," in *Industry Applications Society Annual Meeting*, Oct. 2001.

- [72] N. Wang, I. Cotton, J. Robertson, S. Follmann, K. Evans, D. Newcombe, "Partial discharge control in a power electronic module using high permittivity non-linear dielectrics," *IEEE Trans. Dielectr. Electr. Insul.*, vol. 17, no. 4, pp. 1319-1326, Aug. 2010.

- [73] L. Donzel, J. Schuderer, "Nonlinear resistive electric field control for power electronic modules," *IEEE Trans. Dielectr. Electr. Insul.*, vol. 19, no. 3, pp. 955-959, June 2012.

- [74] O. Hohlfeld, R. Bayerer, T. Hunger, H. Hartung, "Stacked substrates for high voltage applications," in *International Conference on Integrated Power Electronics Systems*, Mar. 2012.

- [75] H. Reynes, C. Buttay, H. Morel, "Protruding ceramic substrates for high voltage packaging of wide bandgap semiconductors," in *IEEE Workshop* on Wide Bandgap Power Devices and Applications, Nov. 2017.

- [76] C. DiMarino, M. Johnson, B. Mouawad, J. Li, D. Boroyevich, R. Burgos, G.-Q. Lu, M. Wang, "Design of a novel, high-density, high-speed 10 kV SiC MSOFET module," in *IEEE Energy Conversion Congress and Exposition*, Sept. 2017.

- [77] C. DiMarino, B. Mouawad, K. Li, Y. Xu, M. Johnson, D. Boroyevich, R. Burgos, "A wire-bond-less 10 kV SiC MOSFET power module with reduced common-mode noise and electric field," in *International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management*, June 2018.

- [78] S. Jahdi, O. Alatise, R. Bonyadi, P. Alexakis, C. Fisher, J. Ortiz Gonzalez, L. Ran, P. Mawby, "An analysis of the switching performance and robustness of power MOSFETs body diodes: a technology evaluation," *IEEE Trans. Power Electron.*, vol. 30, no. 5, pp. 2383-2394, July 2014.

- [79] T. Funaki, M. Matsushita, M. Sasagawa, T. Kimoto, T. Hikihara, "A study on SiC devices in synchronous rectification of dc-dc converters," in *IEEE Applied Power Electronics Conference and Exposition*, pp. 339-344, 2007.

- [80] A. Agarwal, H. Fatima, S. Haney, S. H. Ryu, "A new degradation mechanism in high-voltage SiC power MOSFETs," *IEEE Electron Device Lett.*, vol. 25, no. 7, pp. 587-589, July 2007.

- [81] T. Funaki, "A study on performance degradation of SiC MOSFET for burn-in test of body diode," in *IEEE International Symposium on Power Electronics for Distributed Generation Systems*, pp. 1-5, July 2013.

- [82] B. Hull, S. Allen, Q. Zhang, D. Gajewski, V. Pala, J. Richmond, S. Ryu, M. O'Loughlin, E. VanBrunt, L. Cheng, A. Burk, J. Casady, D. Grider, J. Palmour, "Reliability and stability of SiC power MOSFETs and next-generation SiC MOSFETs," in *IEEE Workshop on Wide Bandgap Power Devices and Applicat.*, Oct. 2014.

- [83] D. Sadik, J. Lim, P. Ranstad, H. Nee, "Investigation of long-term parameter variations of SiC power MOSFETs," in *European Conference* on Power Electronics Applications, pp. 1-10, Sept. 2015.

- [84] B. Passmore, Z. Cole, B. McGee, M. Wells, J. Stabach, J. Bradshaw, R. Shaw, D. Martin, T. McNutt, E. VanBrunt, B. Hull, D. Grider, "The next generation of high voltage (10 kV) silicon carbide power modules," in *IEEE Workshop on Wide Bandgap Power Devices and Applications*, Nov. 2016.

- [85] I. Yaqub, J. Li, C. M. Johnson, "Dependence of overcurrent failure modes of IGBT modules on interconnect technologies," *Microelectron. Reliab.*, vol. 55, no. 12, pp. 2596-2605, Dec. 2015.

- [86] J. Li, A. Castellazzi, T. Dai, M. Corfield, A. K. Solomon, C. M. Johnson, "Built-in reliability design of highly integrated solid-state power switches with metal bump interconnects," *IEEE Trans. Power Electron.*, vol. 30, no. 5, pp. 2587-2600, Sept. 2014.

- [87] J. H. Fabian, S. Hartmann, A. Hamidi, "Analysis of insulation failure modes in high power IGBT modules," in *Industry Applications Society Annual Meeting*, pp. 799-805, Oct. 2005.

- [88] J. H. Fabian, S. Hartmann, A. Hamidi, "Partial discharge failure analysis of AlN substrates for IGBT modules," *Microelectron. Rel.*, vol. 44, pp. 1425-2430, 2004.

- [89] X. Cao, T. Wang, K. D. T. Ngo, G. Q. Lu, "Parametric study of joint height for a medium-voltage planar package," *IEEE Trans. Compon. Packag. Technol.*, vol. 33, no. 3, pp. 553-562, Sept. 2010.

- [90] Standard for Insulation Coordination Including Clearances and Creepage Distances for Electrical Equipment, UL-840, 2007.

- [91] M. Ciappa, "Some reliability aspects of IGBT modules for high-power applications," Ph.D. dissertation, ETH Zurich, Switzerland, 2000.

- [92] E. Herr, T. Frey, R. Schlegel, A. Stuck, R. Zehringer, "Substrate-to-base solder joint reliability in high power IGBT modules," *Microelectron. Reliab*. Vol. 37, no. 10/11, pp. 1719-1722, 1997.

- [93] C. M. Johnson, A. Castellazzi, R. Skuriat, P. Evans, J. Li, and P. Agyakwa, "Integrated High Power Modules," in 7th International Conference on Integrated Power Electronics Systems (CIPS), 2012, pp. 357–366.

- [94] R. Skuriat and C. M. Johnson, "Thermal Performance of Baseplate and Direct Substrate Cooled Power Modules," in 4th IET Conference on Power Electronics, Machines and Drives (PEMD2008), 2008.

- [95] B. Mouawad, R. Skuriat, J. Li, C. M. Johnson, C. DiMarino, "Development of a highly integrated 10 kV SiC MOSFET power module with a direct jet impingement cooling system," in *IEEE International Symposium on Power Semiconductor Devices and ICs*, 2018.

- [96] X. Cao, T. Wang, K. D. T. Ngo, G. Q. Lu, "Characterization of lead-free solder and sintered nano-silver die-attach layers using thermal impedance," *IEEE Trans. Compon. Packag. Manuf. Technol.*, vol. 1, no. 4, pp. 495-501, Apr. 2011.

- [97] Kyocera, "Multilayer ceramic substrates for ECUs," [Online]. Available: https://global.kyocera.com/prdct/semicon/semi/compo/auto\_ecu.html

- [98] Murata, "Low temperature co-fired ceramics (LTCC) multi-layer module boards," [Online]. Available: https://www.murata.com/~/media/webrenewal/support/library/catalog/pr oducts/substrate/ltcc/n20e.ashx

- [99] DK Thermal, "Ceramic PCB: high thermal conductivity, low expansion," [Online]. Available: https://www.dk-ceramics.com/ceramic-pcb/

- [100] S. Gao, Z. Yang, Y. Tan, X. Li, X. Chen, Z. Sun, G.-Q. Lu, "Bonding of large substrates by silver sintering and characterization of the interface thermal resistance," in *IEEE Energy Conversion Congress and Exposition*, Oct. 2017.

- [101] C. DiMarino, M. Johnson, B. Mouawad, J. Li, R. Skuriat, M. Wang, Y. Tan, G.-Q. Lu, D. Boroyevich, R. Burgos, "Fabrication and characterization of a high-power-density, planar 10 kV SiC MOSFET power module," in *International Conference on Integrated Power Electronics Systems*, Mar. 2018.

- [102] F. Yu, R. W. Johnson, M. C. Hamilton, "Pressureless sintering of microscale silver paste for 300 °C applications," *IEEE Trans. Compon. Packag. Manuf. Technol.*, vol. 5, no. 9, pp. 1258-1264, Aug. 2015.

- [103] G.-Q. Lu, M. Wang, Y. Mei, X. Li, "Advanced die-attach by metal-powder sintering: the science and practice," in *International Conference on Integrated Power Electronics Systems*, Mar. 2018.

- [104] Smiths Connectors, "C series spring probes: battery & connector probes," C series datasheet, version 1.3, 2016. Available: https://cloud.3dissue.com/116047/116397/136380/C-Series-Spring-Probes-Catalog-US/html5/index.html?page=1&noflash

- [105] Formlabs, "High temp resin for heat resistance," FLHTAM01 datasheet, Rev. 01, Apr. 2017. Available: https://formlabs.com/media/upload/HighTemp-DataSheet.pdf

- [106]Y. Yao, "Thermal stability of Al<sub>2</sub>O<sub>3</sub>/silicone composites as hightemperature encapsulants," Ph.D. dissertation, Virginia Tech, Sept. 2014.

- [107] A. Kadavelugu, S. Bhattacharya, S.-H. Ryu, E. Van Brunt, D. Grider, A. Agarawal, S. Leslie, "Characterization of 15 kV SiC n-IGBT and its application considerations for high power converters," in *IEEE Energy Conversion Congress and Exposition*, Sept. 2013.

- [108] D. Johannesson, M. Nawaz, K. Ilves, "Assessment of 10 kV, 100 A silicon carbide MOSFET power modules," *IEEE Trans. Power Electron.*, vol. 33, no. 6, pp. 5215-5225, June 2018.

- [109]IXYS, "High voltage IGBT for capacitor discharge applications", IXGF30N400 datasheet, 2009. Available: http://ixapps.ixys.com/DataSheet/DS99978C(IXGF30N400).pdf

- [110] Doble Engineering Company, "Doble in-service testing & assessment PD-Smart partial discharge analyzer," PD-Smart datasheet, Mar. 2016.

[111]Mentor Graphics, "Power tester 1500A—Lifetime testing and failure diagnosis of high-power semiconductors," 04-14 MGC, 1032500.

Christina DiMarino received her B.S. in engineering from James Madison University in 2012, and M.S. and Ph.D. in electrical engineering from Virginia Polytechnic Institute and State University in 2014 and 2018, respectively. She was a Webber Fellow from 2012 to 2015, and a Rolls-Royce Graduate Fellow from 2016 to 2017.

She had summer internships with General Electric Global Research Center, Cree, and Sumitomo Electric Industries. She participated in an NSF International Research Exchange for Students program during which she conducted research at the University of Nottingham.