# UNIVERSIDADE DE LISBOA Faculdade de Ciências Departamento de Informática

## PROGRAMMING MULTICORES SAFELY: HANDLING BARRIER DEADLOCKS

Tiago Soares Cogumbreiro Garcia

#### DOUTORAMENTO EM INFORMÁTICA

Especialidade em Ciência da Computação

# UNIVERSIDADE DE LISBOA Faculdade de Ciências Departamento de Informática

## PROGRAMMING MULTICORES SAFELY: HANDLING BARRIER DEADLOCKS

Tiago Soares Cogumbreiro Garcia

Tese orientada pelo Prof. Doutor Francisco Cipriano da Cunha Martins especialmente elaborada para a obtenção do grau de doutor no ramo de Informática, especialidade de Ciência da Computação

### Resumo

Actualmente, a generalidade dos dispositivos de computação inclui um processador *multicore*. As aplicações que correm em processadores *multicore* só aumentam o seu desempenho se computarem em paralelo, aproveitando assim o poder computacional dos núcleos disponíveis. Para este efeito, as linguagens de programação mais populares, tal como Java e C#, adoptaram, nos últimos anos, várias técnicas de programação paralela. Esta tese lida com uma classe de falhas que origina da utilização de uma técnica de programação paralela, chamada barreira, cuja funcionalidade é a de sincronizar grupos de tarefas. Uma barreira coordena a ordem de execução de um grupo de tarefas, disponibilizando um ponto de execução em que as várias tarefas dum grupo podem esperar umas pelas outras. As tarefas que usam barreiras são vulneráveis ao problema de impasse, em que pelo menos duas tarefas estão (indirectamente) à espera uma da outra em barreiras diferentes sem que qualquer uma das tarefas possa avançar. Os impasses constituem uma classe de falhas, da área de concorrência, com grande impacto em programas paralelos. O nosso objectivo é aumentar a produtividade da programação paralela tratando do problema de impasses em barreiras. Nesta tese propomos duas técnicas complementares para lidar com o problema de impasses: uma ferramenta de verificação especializada em impasses sobre barreiras que é distribuída, tolerante a falhas e verifica aplicações X10 e Java; um modelo de programação isento de impasses.

**Palavras-chave:** impasse, barreira, sincronização, verificação, programação paralela, programação distribuída, Java, X10.

### Resumo estendido

Actualmente, a generalidade dos dispositivos de computação inclui um processador *multicore*, constituído por vários elementos de processamento (chamados núcleos). As aplicações feitas ignorando múltiplos núcleos, só aumentam o desempenho com o aumento da velocidade de cada núcleo. No entanto, por restrições físicas, os fabricantes de processadores *multicores* deixaram de aumentar a velocidade dos núcleos e, ao invés disso, aumentam o número núcleos disponíveis em cada processador. As aplicações que correm em processadores *multicore* só aumentam o seu desempenho se computarem em paralelo, aproveitando assim o poder computacional dos núcleos disponíveis. Para este efeito, as linguagens de programação mais populares, tal como Java e C‡, adoptaram, nos últimos anos, várias técnicas de programação paralela.

Esta tese lida com uma classe de falhas que origina da utilização de uma técnica de programação paralela, chamada barreira, cuja funcionalidade é a de sincronizar grupos de tarefas. Uma barreira coordena a ordem de execução de um grupo de tarefas, disponibilizando um ponto de execução em que as várias tarefas dum grupo podem esperar umas pelas outras. Isto é, a tarefa bloqueia ao executar a instrução barreira até que todos os membros do grupo executem a mesma barreira ("cheguem" à barreira). As tarefas que usam barreiras são vulneráveis ao problema de *impasse*, em que pelo menos duas tarefas estão (indirectamente) à espera uma da outra em barreiras diferentes sem que qualquer uma das tarefas possa avançar. Os impasses constituem uma classe de falhas, da área de concorrência, com grande impacto em programas paralelos.

O nosso objectivo é aumentar a produtividade da programação paralela tratando do problema de impasses em barreiras. Com o intuito de tratar rigorosamente este problema, surge a necessidade de caracterizar matematicamente (*i.e.*, formalizar) o mecanismo de sincronização existente numa barreira. Nesta tese, fazemos um levantamento de primitivas de sincronização baseadas em barreiras. Com esta pesquisa concluímos que o construtor *phaser*, que origina da linguagem Habanero Java, consegue ser adaptado para representar os vários padrões de sincronização por nós documentado. A nossa primeira contribuição é a linguagem de programação paralela Brenner que define as operações essenciais para representar os vários padrões de sincronização capturados por *phasers*.

Propomos duas técnicas complementares para lidar com o problema de impasses. A primeira técnica, considerada dinâmica, consiste numa análise contínua da execução do programa, com o objetivo de identificar situações de impasse. A segunda técnica, considerada estática, propõe um modelo de programação isento de impasses. Técnicas dinâmicas são mais gerais que as técnicas estáticas, podendo ser aplicadas a mais programas existentes, mas incorrem numa degradação da velocidade de execução. Técnicas estáticas, embora menos gerais, garantem propriedades—neste caso a ausências de impasses—sem influenciar o desempenho do programa. Qualquer programa que respeite o nosso modelo de programação não sofrerá de impasses causados por barreiras.

**Verificação dinâmica** Propomos a ferramenta Armus que é capaz de verificar aplicações Java e X10, e que incorpora a nossa técnica de verificação dinâmica. Utilizamos a linguagem Brenner e as operações sobre *phasers* como base da nossa técnica de verificação. Com esta base conseguimos identificar mais padrões de sincronização que as técnicas disponíveis em trabalho relacionado. Adicionalmente, Armus é a primeira ferramenta de verificação que identificas impasses sobre barreiras nas linguagens Java e X10.

O problema da verificação dinâmica de impasses pode ser visto como um sistema de restrições em que quando não existe solução, estamos na situação indesejada de impasse. As restrições correspondem a dependências de concorrência existentes entre tarefas e mecanismos de sincronização. Por exemplo, podemos representar uma dependência entre a tarefa bloqueada numa barreira e as tarefas participantes nessa barreira que ainda não a executaram. No contexto da verificação dinâmica de impasses, a teoria de grafos é a mais utilizada para modelar dependências de concorrência. No nosso caso, resolver as dependências de concorrência equivale a encontrar um ciclo num grafo. O Armus escolhe entre duas representações de dependências para gerar grafos mais pequenos, que demoram menos tempo a serem analisados. Para isso mostramos formalmente que a existência de um ciclo num grafo da primeira representação implica a existência de um ciclo no grafo da segunda representação, e vice-versa. Uma das representações favorece situações em que há mais tarefas do que barreiras, a outra representação favorece a situação oposta. Mostramos mais dois resultados cruciais para garantir a correcção da nossa técnica de verificação: (i) a verificação é fidedigna, visto que qualquer situação de impasse corresponde a uma situação de impasse no programa; (ii) a verificação é completa, visto que qualquer caso em que o programa esteja num impasse é identificado pela análise.

A linguagem de programação X10 permite o desenvolvimento de programas distribuídos. Um programa distribuído corre simultaneamente em vários computadores, utilizando os seus recursos. A nossa técnica de análise melhora o

estado da arte na verificação dinâmica de programas distribuídos. O trabalho relacionado só inclui informação sobre as tarefas bloqueadas, o que é insuficiente para verificar padrões de sincronização em que os participantes de uma barreira não são conhecidos *a priori*. Para suplantar esta limitação, a nossa técnica regista adicionalmente as barreiras a que cada tarefa bloqueada ainda não chegou. Uma implicação desta novidade é que com esta informação extra, a análise consegue ser efectuada em qualquer computador da rede sem sincronização adicional. Em contraste, o trabalho relacionado necessita de introduzir sincronização adicional entre as várias máquinas que estão a ser analisadas.

Avaliamos o Armus usando três conjuntos de benchmarks, em cenários locais e distribuídos numa máquina com 64 núcleos. No primeiro conjunto de benchmarks avaliamos o impacto que a verificação tem no tempo de execução de programas Java paralelos, num contexto local. O impacto de verificação é na maioria nulo e no pior dos casos a aplicação demora mais 15% to tempo a terminar. No segundo conjunto de benchmarks avaliamos o impacto que a verificação tem no tempo de execução de programas X10 distribuídos. O impacto de verificação é nulo. No terceiro conjunto de benchmarks avaliamos o impacto que a escolha de um modelo de grafos tem na análise, num contexto local. Os resultados da avaliação mostram que a nossa técnica de selecção automática de modelos de grafos pode aumentar encurtar o tempo da análise até 7 vezes, versus a técnica efectuada por trabalho relacionado que só utiliza um modelo de grafos.

Verificação estática Este trabalho visa criar um modelo de programação isento de impasses adaptando a linguagem Brenner. Usamos como ponto de partida o modelo de programação isento de impasses existente na linguagem X10, que é mais limitada em termos de padrões de sincronização do que Brenner. Os padrões de sincronização extra na linguagem Brenner são o produtor-consumidor com e sem limite, necessário para representar o paralelismo *streaming* e o paralelismo *pipeline*. O nosso trabalho também pode ser visto como uma adaptação da linguagem Habanero-Java para um modelo de programação isento de impasses, que adicionalmente unifica as várias funcionalidades propostas para os *phasers*. O modelo de programação é formalizado na linguagem SBrenner, que é composto por uma definição de uma sintaxe, de uma semântica operacional e dum sistema de tipos. A semântica operacional caracteriza matematicamente o estado da computação e o efeito que cada instrução tem neste estado. Um sistema de tipos consiste num conjunto de regras que especificam o comportamento válido da linguagem, identificando estados válidos e inválidos de computação.

Os dois resultados principais que mostramos são: a preservação de tipos e o progresso. A preservação de tipos garante que: dado um estado válido

identificado pelo sistema de tipos, se alguma tarefa executar uma instrução, então o resultado do estado de computação também é considerado válido pelo sistema de tipos. Este resultado mostra que, partindo dum estado válido, a computação não "chega" a um estado inválido.

O resultado de progresso garante que, para qualquer estado válido, existe um passo de computação ou então que a computação termina. O progresso garante a ausência de impasses, pois nesse caso a computação não termina mas é impossível dar um passo de computação. Para conseguir provar que há sempre uma tarefa que está pronta a executar, e visto estarmos na presença do padrão de sincronização de produtor-consumidor limitado, introduzimos uma invariante em sistemas que sincronizam com *phasers*. Uma tarefa a dista a fases de uma tarefa a se e só se para qualquer *phaser* em que ambas tarefas participem a diferença da fase local entre a tarefa a e a e a0 e a0. Um *phaser* pode ser visto como uma série de barreiras, a fase local a1 representa a a2-ésima barreira desta série. A invariante do sistema de *phasers* é que, embora a diferença de fases entre tarefas possa alterar à medida que o programa executa, existe sempre uma diferença de fases entre quaisquer duas tarefas. Desta invariante conseguimos estabelecer uma ordem total sobre as tarefas que executam e mostramos que a menor destas tarefas não está bloqueada em qualquer *phaser*.

#### Abstract

Nowadays, most produced computing devices include multicore processors. Applications that run on these devices only scale if they can compute in parallel. To this end, mainstream programming languages, like Java and C‡, adopted various parallel programming techniques.

This thesis focuses on a parallel technique, called barrier, used for synchronisation. A barrier coordinates the execution order of parallel activities, by letting them wait for each other. Tasks using barriers are susceptible to the problem of deadlocks, where at least two activities are (indirectly) in a stalemate because of a conflicting ordering of some barriers. Deadlocks are a class of concurrency failures with a big impact in parallel programs.

To help make parallel programming more productive, we propose two complementary techniques that handle deadlocks caused by barriers: a runtime verification tool, and a deadlock-free programming model. We present Armus, a runtime verification tool specialised in barrier deadlocks that is distributed, fault-tolerant, and verifies X10 and Java programs. Our technique verifies more barrier synchronisation patterns than existing state-of-the-art techniques. We improve deadlock verification based on graph analysis: our technique selects from two alternative graph representations of concurrency dependencies to hasten deadlock checking. Armus is evaluated with three benchmark suites in local and distributed scenarios.

To handle barrier deadlocks at design time we propose a language called SBRENNER that extends and formalises a programming model that originates from the Habanero-Java and the X10 languages. The outcome is a deadlock-free programming model that leverages pipeline parallelism. We present an operational semantics and a type system for SBRENNER. Our type system enjoys the properties of progress and subject reduction.

**Keywords:** deadlock, barrier, synchronisation, verification, parallel programming, distributed programming, Java, X10.

## Acknowledgements

I am extremely grateful to my advisor, Francisco Martins, for his support and enthusiasm. His passion for education and science are a constant source of inspiration. I am grateful for Francisco's attention to detail, rigour, and wisdom.

I am in debt to Vivek Sarkar for welcoming me at Rice University and for our thoughtful discussions. I also want to thank Vivek Sarkar and Jun Shirako for the discussions regarding the semantics of phasers and Habanero Java.

During my doctorate studies I had the privilege to work at Universidade de Lisboa, Rice University, and the Imperial College London. Thank you to Vasco Vasconcelos, Nobuko Yoshida, and Raymond Hu for our collaborations, which greatly improved the outcome of this disseration. I am grateful to the members of LASIGE (Universidade de Lisboa), the Habanero group (Rice University), and the Mobility Reading Group (Imperial College London) for the friendly and insightful discussions.

## Contents

| Co | onter | ats                                             | X   |

|----|-------|-------------------------------------------------|-----|

| Li | st of | Figures                                         | хi  |

| Li | st of | Tables                                          | xii |

| 1  | Intı  | oduction                                        | 1   |

|    | 1.1   | Problem statement                               | 1   |

|    | 1.2   | Objectives                                      | 4   |

|    | 1.3   | Thesis outline                                  | 5   |

| 2  | Bar   | riers and its applications                      | 7   |

|    | 2.1   | Historical background                           | 7   |

|    | 2.2   | Related work                                    | 13  |

| 3  | Bri   | ENNER                                           | 15  |

|    | 3.1   | Syntax                                          | 15  |

|    | 3.2   | Operational Semantics                           | 20  |

| 4  | Rui   | ntime deadlock verification                     | 27  |

|    | 4.1   | Resource dependencies                           | 27  |

|    | 4.2   | Basic graph theory                              | 29  |

|    | 4.3   | Graph-based deadlock identification             | 30  |

|    | 4.4   | Results                                         | 32  |

|    | 4.5   | Armus: a tool for runtime deadlock verification | 38  |

|    | 4.6   | Evaluation                                      | 42  |

| 5  | Dea   | dlock prevention                                | 47  |

|    | 5.1   | Language restrictions                           | 47  |

|    | 5.2   | Syntax                                          | 53  |

|    | 5.3   | Operational Semantics                           | 56  |

|    | 5.4   | Type System                                     | 67  |

|     | 6.2              | Typing states                                                    |  |  |  |  |  |

|-----|------------------|------------------------------------------------------------------|--|--|--|--|--|

|     | 6.3              | Inversion                                                        |  |  |  |  |  |

|     | 6.4              | The domain of typing contexts                                    |  |  |  |  |  |

|     | 6.5              | Strengthening                                                    |  |  |  |  |  |

| 7   | •                | ect reduction 93                                                 |  |  |  |  |  |

|     | 7.1              | Async                                                            |  |  |  |  |  |

|     | 7.2              | Phaser creation                                                  |  |  |  |  |  |

|     | 7.3              | Deregistration                                                   |  |  |  |  |  |

|     | 7.4              | Advance phase                                                    |  |  |  |  |  |

|     | 7.5              | Change bound                                                     |  |  |  |  |  |

|     | 7.6              | Await                                                            |  |  |  |  |  |

|     | 7.7              | Next                                                             |  |  |  |  |  |

|     | 7.8              | Finish                                                           |  |  |  |  |  |

|     | 7.9              | Join                                                             |  |  |  |  |  |

|     | 7.10             | Control flow                                                     |  |  |  |  |  |

|     | 7.11             | Main result                                                      |  |  |  |  |  |

| 8   | Prog             | gress 139                                                        |  |  |  |  |  |

| 9   | Con              | clusion 149                                                      |  |  |  |  |  |

|     | 9.1              | Contributions                                                    |  |  |  |  |  |

|     | 9.2              | Summary of personal publications                                 |  |  |  |  |  |

|     | 9.3              | Future work                                                      |  |  |  |  |  |

| Bi  | Bibliography 155 |                                                                  |  |  |  |  |  |

|     |                  |                                                                  |  |  |  |  |  |

|     |                  |                                                                  |  |  |  |  |  |

|     |                  |                                                                  |  |  |  |  |  |

|     |                  | List of Figures                                                  |  |  |  |  |  |

|     |                  | J                                                                |  |  |  |  |  |

| 3.1 | To               | p-level syntax                                                   |  |  |  |  |  |

| 3.2 |                  | ntax of the abstract machine                                     |  |  |  |  |  |

| 3.3 |                  | e small-step semantics of Brenner (tasks)                        |  |  |  |  |  |

| 3.4 |                  | e small-step semantics of Brenner (phasers)                      |  |  |  |  |  |

| 3.5 | Sm               | all step semantics for control flow instructions $c; b \to b$ 23 |  |  |  |  |  |

|     |                  |                                                                  |  |  |  |  |  |

**73**

6 Type system properties

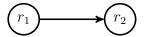

| 4.1 | Two different graphs representing a deadlocked system                | 32 |

|-----|----------------------------------------------------------------------|----|

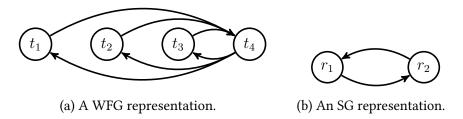

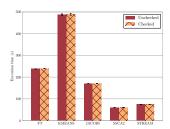

| 4.2 | Comparative execution time for non-distributed benchmarks (lower     |    |

|     | means faster).                                                       | 44 |

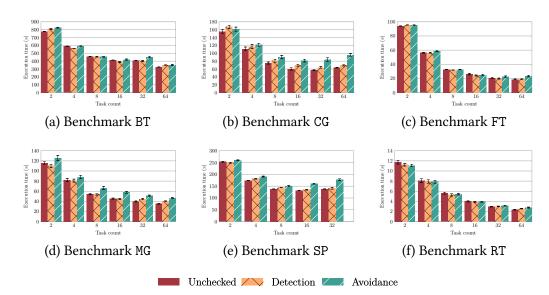

| 4.3 | Comparative execution time for distributed deadlock detection (lower |    |

|     | means faster).                                                       | 45 |

| 4.4 | Comparative execution time for different graph model choices (lower  |    |

|     | means faster), using deadlock avoidance.                             | 45 |

| 4.5 | Comparative execution time for different graph model choices (lower  |    |

|     | means faster), using deadlock detection.                             | 45 |

| 5.1 | SBrenner syntax                                                      | 54 |

| 5.2 | Syntax of the abstract machine                                       | 61 |

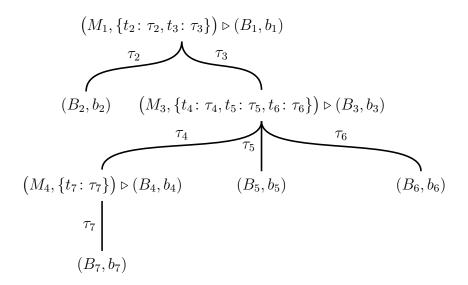

| 5.3 | A dependency tree of tasks                                           | 62 |

| 5.4 | Small step semantics for states (phaser related) $S \to S$           | 63 |

| 5.5 | Small step semantics for states (finish, control flow) $S \to S$     | 67 |

| 5.6 | Small step semantics for control flow instructions $c; b \to b$      | 67 |

| 5.7 | Typing rules for arguments $\Gamma \vdash s : \Gamma$                | 68 |

| 5.8 | Typing rules for instructions $\Gamma \vdash i : \Gamma$             | 70 |

| 5.9 | Typing rules for programs $\Gamma \vdash b : \Gamma$                 | 70 |

| 6.1 | Typing rules for phasers and phaser maps                             | 76 |

| 6.2 | Typing rules for permissions, bounds, tasks, and task maps           | 78 |

| 6.3 | Typing rules for states                                              | 79 |

|     |                                                                      |    |

## List of Tables

| 4.1 | Relative execution overnead in detection mode                      | 45 |

|-----|--------------------------------------------------------------------|----|

| 4.2 | Relative execution overhead in avoidance mode                      | 44 |

| 4.3 | Edge count and verification overhead per benchmark per graph mode. | 46 |

#### Chapter One

### Introduction

We want to improve the productivity of multicore programmers, by reducing program failures. Recently, mainstream languages incorporated parallel programming techniques that introduced new forms of failures. Our work studies a technique called barrier synchronisation and a form of failure called a deadlock. We propose two different strategies to solve barrier deadlocks and implement one of these strategies as a tool.

#### 1.1 Problem statement

This thesis centres on the impact of the "multicore revolution" on programming languages. Physical restrictions made chip manufacturers develop multicore processors composed of multiple processing units, called cores. The execution model of these processors is *parallel*: all cores work at the same time and communicate through a main memory. Each core executes *sequentially*, running a sequence of instructions, one after the other. The trend of processor design for the past decade has been to increase the number of cores linearly and to stabilise the execution speed [98].

Applications stopped scaling with multicores because they were not designed to compute in parallel [83]. The reaction of mainstream programming languages, like Java, and C‡, was to incorporate parallel programming techniques. Surveys [20, 82] analyse the usage parallel programming techniques in Java and C‡. At the foundation of parallel programming is task parallelism [27], which is both a *programming model* that defines a an interface for programming a system, and also an *execution model* that defines how actions are executed by the system. Tasks correspond to a logical unit of work that is composed of a series of actions that are executed sequentially, while sharing and manipulating memory. The system executes multiple tasks *concurrently*, *i.e.*, at the same time.

With parallelism comes the need to synchronise the concurrent execution of multiple tasks. A barrier [55] coordinates the execution of a group of tasks: it can ensure all members wait for each other before advancing to their next action. Barrier synchronisation was developed in 1978 and rapidly became a cornerstone

of parallel programming. The most popular choices for parallel programming are MPI [40] and OpenMP [36], through C or Fortran. The performance of barrier synchronisation is of such high importance that active research exists on implementing this mechanism in hardware [2, 54, 93].

Mainstream programming languages provide a multitude of abstractions that perform barrier synchronisation [20, 82]. Java 5.0–7.0 (2004–2011) and  $C\sharp$  (2010) introduced four abstractions that use barrier synchronisation: latches, cyclic barriers, futures [48], and the fork/join programming model. Futures are also a novelty of C++ version 2011. A latch, or countdown event, is a counter that can only be decreased until it reaches zero. Besides decreasing the value of the latch, tasks can also wait (once) for the latch to reach zero. The wait on the latch represents a barrier synchronisation. A cyclic barrier can be used for synchronisation repeatedly. A future, or promise, is a placeholder for a value that is computed asynchronously (concurrently). Any task holding the future can wait for its value to be computed in what can be seen as a barrier synchronisation. Stream programming [100] also includes a form of reusable barrier synchronisation and is included in Java,  $C\sharp$ , and there is a proposal for OpenMP [87].

High-performance computing (HPC) champions the development of parallel programming to solve complex scientific problems. There is a recent interest in two well-studied aspects of mainstream languages [45, 71, 74]: language usability and application robustness. To address language usability, new task parallel languages were proposed: Chapel [26], Habanero-Java (HJ) [24], Titanium [110], UPC [37], and X10 [28]. All five languages include abstractions to perform barrier synchronisation. There many proposals to tackling the problem of concurrency-related failures: structured abstractions [28, 94], source code analysis [106, 76], and program monitoring [34, 51, 52].

Parallel programming techniques introduce concurrency-related bugs, notably difficult to track and reproduce. Deadlocks [114] are a class of nefarious concurrency failures that have a wide expression in task parallel programs [39, 72]. Barrier deadlocks arise from a cyclic-dependency among tasks that participate on multiple barriers. An example of a deadlock is when two tasks block on distinct barriers and are (indirectly) waiting for each other. Techniques that handle deadlocks for mainstream languages cannot cope with *ad hoc* synchronisation mechanisms [57]. In particular, these techniques cannot handle barrier deadlocks.

Literature considers four strategies to handle deadlocks [58]: ignoring, preventing, avoiding, and detecting. The plainest strategy is to just *ignore* the error, a useful strategy when the deadlock only shows up rarely, and the effort of handling it is steep. Barrier deadlocks are usually deterministic, because the arrival order does not disturb barrier synchronisation. It is often the case that if

the program can deadlock, it does deadlock, which renders impractical, ignoring these class of failures.

Prevention reduces the expressiveness of the abstraction in such a way that any program that runs is known beforehand to be free of deadlocks. To achieve prevention there are syntactic and semantic approaches. The fork/join programming model of OpenMP and of X10 uses syntactic scoping to ensure that there are no deadlocks while tasks join their execution, *i.e.*, there is no syntax to write a program that deadlocks just by joining the execution of tasks. The fork/join programming model is also available in many languages as a library, but in such cases deadlocks are not prevented syntactically. The X10 language [28] provides a limited programming model that prevents all barrier deadlocks, although any use of synchronisation codes outside of this programming model voids the deadlock freedom guarantee. An alternative approach is to perform source code analysis to predict deadlocks. Promising work from Le *et al.* [69] annotates C code to verify some safety properties of barriers. Prevention is too limiting to be applied to the whole system, so language designers use this strategy to eliminate some deadlock patterns.

Avoidance and detection happen at run-time. With *avoidance*, the system proactively compensates calls that lead to a deadlock, *e.g.*, by delaying a call, or aborting execution. Some systems, such as MPI [40], deadlock if a barrier participant forgets to synchronise and terminates. The synchronisation algorithm of X10 disregards terminated participants to avoid this class of deadlocks. The HJ language dynamically avoids deadlocks that arise from the interference between cyclic barriers and the fork/join programming model at a cost of expressiveness. Avoiding deadlocks caused by misaligned barriers is usually too expensive as every call that uses barrier synchronisation must be monitored, so language designers opt for deadlock detection instead.

The strategy of *detection* requires a system that is capable of introspecting its state to identify deadlocked states. This monitoring does not interfere with the program execution, so the system must break—or just inform the user of—any deadlock it identifies. Works on barrier deadlock detection are largely concerned with the idiosyncrasies of the system and with the performance of the tool at hand. For example, works on deadlock detection for MPI, *e.g.*, [52], are not applicable to UPC, nor *vice versa* [34], because neither has a barrier construct capable of encoding the other. In the context of parallel programming, there is a need for run-time error detection [74] and a need for formalisation [45]. The programming language and formal methods community payed little attention to runtime strategies that handle deadlocks, *i.e.*, to detection and to avoidance. A notable exception is the work from Boudol [21] that presents a language equipped with locks along with a formal semantics that avoids deadlocks.

There is a lack of a precise, mathematical description of what barrier synchro-

nisation actually is. Throughout its 30 years of existence, there are many different ways of employing barrier synchronisation but no surveys on its fundamental semantics. Formal methods can help assess the correctness of the design early on and acts as a crucial guide to a more accurate implementation [19]. In particular, runtime techniques cannot verify existing barrier-based abstractions and prevention techniques are too limited to be useful.

#### 1.2 Objectives

We want improve the productivity of parallel programming, by reducing the number of faults caused by concurrency. This thesis revisits the classical problem of deadlocks in the point of view of programming languages, in particular we focus on a *comprehensive* approach to handle deadlocks caused by barriers. Our objectives can be summarised in five topics:

- 1. Survey the usual barrier properties. We study the origins of parallel programming and associated programming models to identify the abstractions that use this synchronisation mechanism. We catalogue the properties found and illustrate them with programming examples.

- 2. Propose a general theoretical framework to reason about barriers. The idea is to distil the semantics of the surveyed properties into a single, unifying abstraction that can then be used as the cornerstone of our techniques to handle deadlocks.

- 3. Introduce techniques that handle deadlocks at runtime. We show how to detect (or avoid) deadlocks on our general barrier framework. Dynamic techniques are the only ones that can cope with the full expressiveness of barrier synchronisation.

- 4. Present deadlock-free techniques. We restrict our initial model to include the prevention techniques used by X10 and HJ. Our proposal pushes the limits of expressiveness set forth by X10 and HJ while maintaining the deadlock-free guarantee, that we prove to be hold.

- 5. Develop tools that can help programmers avoid barrier deadlocks. We implement the synchronisation mechanism behind our theoretical framework and build two tools that detect or avoid barrier deadlocks for Java and X10.

5

#### 1.3 Thesis outline

Chapter 2 surveys the properties of abstractions that use barrier synchronisation. We give a brief historical context of the evolution and the different uses of this synchronisation mechanism. Each barrier idiom is accompanied with code listings and an informal description of its semantics. We conclude the chapter discussing related work on the formalisation of barrier synchronisation and on handling barrier deadlocks.

Chapter 3 presents a minimal task parallel language that contains a general barrier abstraction. The language is defined by a syntax and a formal semantics. We describes the semantics operationally: so we characterise the state of a program, and specify how each primitive alters this state.

Chapter 4 explores the detection and avoidance of barrier deadlocks. The basic idea is to abstract the state of a program as a graph, and then reduce the problem of deadlock detection and avoidance to finding a cycle in a graph. We introduce some basic notions of graph theory, then show how to obtain a graph from a program state, and finally establish the soundness and completeness of our detection algorithm. The realisation of the theory are two runtime verification tools: one for Java, and another for one X10. The tools can perform deadlock avoidance, and fault-tolerant and distributed deadlock detection.

Chapter 5 explores the prevention of barrier deadlocks. We restrict the language introduced in Chapter 3 in such a way that programs are deadlock-free by construction, *i.e.*, there is no syntax to write programs that deadlock. The syntactic and semantic limitations we impose to achieve deadlock freedom are taken from the languages X10 and HJ. Our contributions of this chapter are: pushing the limits of expressiveness under a deadlock-free setting, and establishing the properties of subject reduction and of progress.

Chapter 9 summarises the thesis, outlines our technical contributions and key findings, and presents future directions of our work.

#### Chapter Two

## Barriers and its applications

Parallel programming includes several abstractions that perform barrier synchronisation. We examine common properties of this synchronisation mechanism with the objective of identifying a single unifying abstraction to reason about barrier deadlocks.

Section 2.1 highlights the different uses of barrier synchronisation in programming languages through the history of computing. The outcome is a survey on different barrier properties. In Section 2.2, we examine the state-of-the-art on handling barrier deadlocks to identify our research opportunities.

#### 2.1 Historical background

The importance of coordinating the execution of independent processing units (tasks, processors, or even computers) can be traced back to the first computers ever designed. The 1960's brings into play the simplest form of barrier synchronisation, the fork/join programming model. The Gamma 60 computer [18] is announced in 1958, a machine that includes multiple processing units that can synchronise upon the completion of an instruction. Any processing unit can run an instruction on another unit with a "fork" instruction and then wait for that instruction to complete with a "join" instruction. In 1963, Melvin E. Conway proposes a multiprocessor design [33] based the fork/join programming model, where the join instruction can wait for multiple instructions to conclude, instead of just one. John A. Gosden presents a historical survey of this subject in [46].

In 1965, Ascher Opler elevates the fork/join programming model to a lan-

Listing 2.1: Matrix multiplication in Fortran.

```

do LOOP I=1,21

do LOOP J=1,21

do LOOP K=1,21

LOOP: C(I,J) = C(I,J) + A(I,K) * B(K,J)

```

Listing 2.2: Matrix multiplication programmed with do-together.

```

1

do together BLOCK1, BLOCK2, (END)

2

BLOCK1: do LOOP1 I1=1,21,2

3

do LOOP1 J1=1,21

do LOOP1 K1=1,21

4

C(I1, J1) = C(I1, J1) + A(I1, K1) * B(K1, J1)

5

LOOP1:

BLOCK2: do LOOP2 I2 = 2,20,2

6

7

do LOOP2 J2 = 1,21

8

do LOOP2 K2 = 1,21

C(12, J2) = C(I2, J2) + A(I2, K2) * B(K2, J2)

9

L00P2:

END: hold

10

```

guage abstraction [84] called do-together. Listing 2.1 is a sequential program that multiplies matrices A and B and places the result in matrix C. The matrices are 21 rows by 21 columns. Listing 2.2 is the parallel version of the sequential algorithm. Instruction DO TOGETHER receives the instruction sequences to be executed in parallel and an instruction label between parenthesis that marks the end of the block—the language used in the example lacks the concept of structured code. Here, there are two instruction sequences: BLOCK1, that ranges from lines 2–5, and BLOCK2, that ranges from lines 6–9. The instruction sequence BLOCK1 multiplies cells with odd rows, and instruction sequence BLOCK2 multiplies cells with even rows. Instruction hold is a join barrier that waits for the completion of both instruction sequences.

Listing 2.3: Matrix multiplication using Lamport's concurrent-do.

```

do LOOP conc I=1,21

do LOOP J=1,21

do LOOP K=1,21

LOOP: C(I,J) = C(I,J) + A(I,K) * B(K,J)

```

The late 1960's bring the ILLIAC IV [17], a computer with multiple processors that execute a single instruction stream. Leslie Lamport proposes two language constructs to coordinate the execution of parallel loops [66]. Any do-loop that includes the keyword conc schedules each iteration to a different processor. Listing 2.3 revisits the matrix multiplication, but assigns the computation of each row to a different processor. Similarly to the do together, there is an implicit barrier at the end of the outermost cycle, where all processors synchronise. A do-loop with the keyword sim also schedules each iteration to a different

Listing 2.4: An iterative averaging algorithm.

```

for (i=1;i<=N;i++) do par

for (k=1;k<=M;k++) do seq

P[i] = (P[(i+1) % N] + P[(i-1) % N])/2;</pre>

```

processor, but differently than CONC, it makes every processor executing the parallel cycle to synchronises at each instruction. This is the first time the notion of a *reusable* barrier synchronisation appears in a programming language, although in this case it is an implicit notion. A reusable barrier can also be seen as a stream of barriers. We call *phase* to each barrier of a stream of barriers.

Harry F. Jordan coins the term "barrier synchronisation" in 1978 [55], in the context of the design of a parallel machine that performs finite element analysis. The author proposes a primitive to perform reusable barrier synchronisation. The intent of this synchronisation mechanism is to separate two phases of the element analysis algorithm. The processors must wait for each other at the barrier before advancing to the second phase of the algorithm.

The 1980's are marked, at the software level, by the exploration of parallelising compilers that take a sequential program and make it parallel [108]. Parallelising compiler introduce barriers in the generated code to enforce data dependence. Programmers can provide source code annotations to improve the work of the compiler. The programming languages Force [56]—initiated by Harry F. Jordan, among others—and PISCES [89] included a reusable barrier primitive.

Listing 2.4 shows a typical smoothing algorithm picked from [47], a pattern seen, for example, in computing a partial differential equation. The array P holds N numbers. Each value in the array is calculated by using its neighbours from the previous iteration. The outer loop iterates over the contents of the array and executes its steps in parallel (hence the keyword par). The inner loop performs the smoothing and executes sequentially.

A parallelising compiler must notice the data dependency between iteration i and iteration i+1, or otherwise there is a race condition. In Listing 2.5, the compiler adds two (reusable) barriers. Every task waits for the others to read the neighbouring values into tmp, and then all tasks wait for each other after updating their own cell.

Rajiv Gupta introduces fuzzy barriers [47], in 1989, as an optimisation technique to overlap synchronisation with computation. A similar technique, called *split-phase communication*, is used to hide communication latency [25, 29, 113], so nowadays fuzzy barriers are also known as split-phase barriers. A split-phase barrier consists of two primitives: initBarrier initiates the synchronisation

Listing 2.5: Iterative averaging programmed with barrier synchronisation.

```

for (i=1;i<=N;i++) do par

for (k=1;k<=M;k++) do seq {

tmp = (P[(i+1) % N] + P[(i-1) % N])/2;

barrier;

P[i] = tmp;

barrier;}</pre>

```

mechanism concurrently, and primitive waitBarrier waits for the synchronisation to happen. A task blocks on waitBarrier until all other participants execute initBarrier. Listing 2.6 rewrites the smoothing algorithm with a split-phase barrier. With split-phase barriers Line 5 can be run concurrently with Line 7.

Listing 2.6: Iterative averaging programmed with barrier synchronisation.

```

for (i=1;i<=N;i++) do par

for (k=1;k<=M;k++) do seq {

l = P[(i-1) % N]; r = P[(i+1) % N];

initBarrier;

tmp = (l + r)/2;

waitBarrier;

P[i] = tmp;

barrier;}</pre>

```

At the time, research is mostly geared towards the performance of the synchronisation algorithm [9, 22, 49]. Rajiv Gupta also introduces the notion of barrier synchronisation in a subset of tasks in the system, in contrast with a global barrier that affects all tasks.

In the 1980's, there are also some advances related to the fork/join programming model. The parallel functional languages Multilisp [48] and Id [11] include abstractions that mix communication with a barrier synchronisation. Multilisp introduces *futures*, or promises, that can be seen as a placeholder for the outcome of a function that is being computed concurrently, possibly in parallel. An arbitrary number of consumer tasks can be awaiting a result to be produced on the placeholder (the barrier). Once the function evaluates, the waiting tasks can resume their work and have access to the outcome of the function. The language Id proposes *I-structures* as a simplification of futures. An I-structure can also be seen as a placeholder for the outcome of a computation, yet, unlike futures, this

Listing 2.7: A deadlock using synchrons.

mechanism does not spawn any tasks. Tasks can observe and consume values written in an I-structure. Writing to the I-structure is synchronised with all the pending reads. Writing is a non-blocking operation, so the writer task does not wait for the readers tasks.

In the 1990's there is an ongoing exploration of (explicit) task parallelism, a continued work on the fork/join programming model, and barriers appear as first-class values and varying participation is introduced. Two notable languages based on the fork/join programming are announced: Cilk [41] (as a C extension) and OpenMP [36] (as a Fortran extension). As barriers make their appearance in more programming languages, their semantics become richer. This decade introduces barrier synchronisation where the group of participants varies over time. In 1990, varying participation appears first in hardware barrier synchronisation [81]. In 1996, Franklyn Turbak proposes synchrons [102]: the barrier abstraction is a first-class value that can be stored in any data structure. Furthermore, synchrons also allow for varying participation, the first time such property appears in software-based barriers. In Listing 2.7 two tasks wait for two synchrons in a alternative order, rendering them in a deadly embrace. A main task creates two synchrons, in line 1, and then uses primitive par to spawn two new tasks. One of the spawned tasks, in line 3, waits first on synchron a and then on synchron b. The other spawned task, in line 4, waits on b first and on synchron a second.

MPI [40], an extension of C or of Fortran, is announced in 1992. There is support for *collective operations* and the possibility to group tasks. Collective operations must be executed by every member of a group of tasks, introducing an implicit barrier at each operation. For example, if a task executes an MPI\_Broadcast while another task executes a MPI\_Scatter, then we have a deadlock caused by misaligned barriers. Additionally, any task that shares (transitively) a group with any of the deadlocked tasks also becomes deadlocked.

The 2000's give rise to a new family of parallel programming languages called PGAS (Partitioned Global Address Space) for task parallel languages with access to a hierarchic shared memory. Some languages that are part of this family include Chapel, Titanium, UPC, and X10. In 2001, Jung *et al.* promotes the split-phase barrier synchronisation to a first-class synchronisation mech-

anism [59], in contrast with Gupta's view of split-phase barrier as a compiler optimisation. MPI, UPC, and X10 offer split-phase barrier synchronisation. X10 includes a fork/join programming model and a barrier abstraction called *clock*, that is a first-class value and supports group synchronisation with a varying number of participants.

Only in the 2000's do mainstream languages start incorporating barrier synchronisation in their libraries. Java and the language family behind the .NET framework did not change their syntax to accommodate barrier synchronisation; all abstractions that perform barrier synchronisation are first-class values. Java 5.0, in 2005, include three abstractions that perform barrier synchronisation: latches, cyclic barriers, and futures. A latch performs one-shot barrier synchronisation for a fixed number of participants. The cyclic barrier performs reusable barrier synchronisation, also for a fixed number of participants. The .NET framework 4.0, in 2010, includes latches, a cyclic barrier that supports varying participation, futures, and a fork/join programming model.

HJ is a derivation of X10, so they share the programming model and most language constructs. A novelty of HJ is the proposal of phasers [94] to replace clocks. The semantic novelty in this abstraction is the way tasks can influence barrier synchronisation, which resembles latches and I-structures. A task can observe a phaser and just await participants, without others waiting for it. A task can cross the barrier (*i.e.*, arrive and proceed without waiting), yet others still need to wait for it to arrive at the barrier. A task can still use a phaser for regular reusable barrier synchronisation, by arriving and waiting. Phasers can be used to perform producer/consumer synchronisation, usually done with condition variables [53], whose deadlocks are known to be very difficult to handle [4, 57]. Later, there is a phaser extension to support bounded producer/consumer synchronisation patterns, called phaser beams [96]. Finally, in 2011, Java 7.0 adds an abstraction inspired by phasers, but that does not support observers; a Java phaser is essentially a clock but, confusingly, it is also called a phaser.

To summarise, the barrier properties we consider are:

- **Group synchronisation:** A subset of the available tasks can synchronise together as a group. Examples: clocks, cyclic barriers, join barriers, latches, MPI collective operations, phasers, and synchrons.

- **Reuse:** Participants may use the same abstraction to perform more than one barrier synchronisation. Examples: clocks, cyclic barriers, MPI/UPC collective operations, phasers, and synchrons.

- **Split-phase synchronisation:** The synchronisation mechanism must be able to be commenced asynchronously. Examples: clocks, latches, MPI/UPC collective operations, and phasers.

**Varying participation:** A task can join and leave a group that is synchronised with a barrier. Examples: clocks, MPI collective operations, phasers, and synchrons.

**Phase observing:** A task can observe the barrier without influencing it. In the case of a reusable barrier, the task must be able to observe a specific phase. A task can arrive without needing to await any participant. Examples: futures, I-structures, join barriers, latches, and phasers.

#### 2.2 Related work

The seminal work from Peter J. Landin [68] along with the programmer's manual of LISP 1.5 [79] pioneered the idea of reasoning in terms of families of programming languages, called *calculi*. The goal of a calculus is to unify multiple programming languages by abstracting mere syntactic variations. Examples of calculi include the  $\lambda$ -calculus [30] for functional programming languages, process algebras (*e.g.*, the  $\pi$ -calculus [80]) for concurrent languages, and the object calculus [1] for object-oriented languages.

Calculi that include barrier synchronisation are usually limited to a specific barrier idiom. SPMD languages usually have global collective operations, so a calculus that targets this family of languages only concerns with global barrier synchronisation. Similarly, a calculus that deals with futures, or with join barriers, only concerns with one-shot barrier synchronisation. Yet HJ, Java, the .NET framework, OpenMP, and X10 are just some examples of languages that comprise varied barrier idioms.

**Deadlock prevention.** The literature around source code analysis to prevent global barrier deadlocks is vast: MPI [76, 85, 97, 111], OpenMP [112], OpenSH-MEM [88], and Split-C [7] (a predecessor of UPC). It is worth noting that MPI supports group barrier synchronisation, but works on deadlock prevention can only cope with global synchronisation.

The fork/join programming model is easily restricted syntactically to prevent deadlocks from happening. The  $\lambda_S$ -calculus by Arvind et~al.~[10] and the calculus by Aditya et~al.~[3] study the fork/join programming model in the context of functional programming languages. Lee and Palsberg presented a calculus for a fork/join programming model [70], suited for inter-procedural analysis through type inference, and establishes the deadlock freedom property. The work by Lee and Palsberg also includes a type system that is used to identify may-happen-parallelism, further explored by Agarwal et~al.~ in [5].

There is some work surrounding the formalisation of barrier semantics with complex properties of barrier synchronisation, but do not establish deadlock-freedom. Saraswat and Jagadeesan formalise a subset of X10 that prevents deadlocks [92], comprising join barriers and clocks. Le *et al.* devise a verification for the correct use of a cyclic barrier in a fork/join programming language [69]. Vasudevan *et al.* have a similar approach on verifying the correct use of clocks [104].

The tool X10X [44] is a *model checker* for X10. Model checkers perform source code analysis and can be used to discover potential deadlocks. This class of tools suffers from the state explosion problem: the analysis grows exponentially with the possible interleaves of the program. Thus, X10X may not be able to verify complex programs.

There is a research opportunity on formal techniques that prevent general barrier deadlocks.

**Deadlock avoidance and detection.** To our best knowledge, techniques that avoid deadlocks in the context of barrier synchronisation are incomplete, i.e., only handle a few situations of barrier deadlocks. For instance, in X10 and HJ, tasks deregister from all barriers upon termination; this mitigates deadlocks that arise from missing participants. HJ avoids deadlocks that originate from the interaction between phasers and finish blocks by limiting the use of phasers to the scope of finish blocks. Deadlock detection tools for Titanium [60] and UPC-CHECK [91] can only handle global barrier synchronisation. Literature concerning MPI deadlock detection is still not general enough for languages like Java and X10 and lacks formal specifications. DAMPI [105], Marmot [64], and MPI-CHECK [73] report a programs as deadlocked after a period of inactivity, so it can misidentify a slow program as a being deadlocked. Umpire [51] and MUST [52] (a successor of Umpire) use a graph-based deadlock detection algorithm, but omit a formal description on how the graph is actually generated from the language. Furthermore, MUST is incapable of verifying split-phase synchronisation, known in MPI as non-blocking collective operations.

There is a research opportunity on deadlock avoidance and detection for general barrier synchronisation.

#### Chapter Three

# Brenner: a calculus for parallel programming

We present phasers and a core-language to reason about task parallelism with this abstraction. The following section revisits some examples to introduce the primitives that comprise a phaser. Section 3.1 presents the syntax of Brenner. We discuss the operational semantics in Section 3.2.

The definitions and examples in this chapter are mechanised in Coq [78] and available online<sup>1</sup>.

#### 3.1 Syntax

A phaser is used to count and observe events generated by a group of tasks, similarly to a collective event counter [90]. The primitives we introduce distil the semantics cf. [94, 96]. Each participant is registered with an event counter, called a *local phase*, that is a non-decreasing, non-negative integer. Instruction adv increments the local phase of the issuing task. Instruction await(p,n) blocks until all members of phaser p reach phase n, *i.e.*, their local phase is at least n. Instruction newPhaser creates a phaser.

Tasks are referred by task names. Instruction newTid creates a task name. To dynamically create and launch a named task there is instruction fork. The members of a phaser are controlled with reg to add (register) a participant to a phaser, and dereg to remove (deregister) a participant from a phaser. Data transfers and data-related computation are abstracted and in their place we use instruction skip. Similarly, we represented structured control flow instructions, like for-loops and conditionals, with instruction loop that unfolds its body an arbitrary number of times.

**Join barriers** Listing 3.1 describes an one-shot barrier synchronisation as seen in the fork/join programming model. Our example revisits Listing 2.3, matrix

https://bitbucket.org/cogumbreiro/brenner-coq/

Listing 3.1: Matrix multiplication programmed with a phaser.

```

1

p = newPhaser();

loop( // for (i = 0; i < 21; i++) {

2

t = newTid();

3

reg(t, p);

4

fork(t,

5

loop( // for (j = 0; j < 21; i++)

6

loop( // for (k = 0; k < 21; k++)

7

skip; // C[i][j] += A[i][k] * B[k][i];

8

end); // inner loop

9

end); // outer loop

10

adv(p); // signal termination

11

end); // fork

12

end); // loop

13

14

adv(p);

15

await(p, 1); // join

16

end

```

multiplication programmed with a task processing each row of the matrix. A driver task executes the code in Listing 3.1; it is responsible for forking the worker tasks processing the rows, and for joining their execution with a phaser p. In detail, the driver tasks creates phaser p, in Line 1, with instruction newPhaser, automatically registering the driver at phase 0. The driver uses reg to register t with p (Line 4); the registered task will inherit the phase of their registrant, in this case it is phase 0. The workers (Lines 6 to 12) advance their phase, in Line 11, to notify the driver that awaits their terminus, in Line 15. Since the driver is also registered with p, it advances its local phase before awaiting phase 1, in Line 14, otherwise it deadlocks all tasks.

**Cyclic barriers** Listing 3.2 revisits the split-phase synchronisation example seen in Listing 2.6. To encode a cyclic barrier, every participant advances its phase and then awaits at its local phase in Line 13, so that all members await each other. There are two variants of instruction await, when a task omits the phase number,  $\mathtt{await}(p)$ , then this task awaits at its local phase. Split-phase synchronisation commences with a phase advance in Line 8, and terminates with an await in Line 10.

**Pipeline parallelism** Phasers enable distinct synchronisation patterns when compared to other barrier-based abstractions. A case in point is the producer-

3.1. SYNTAX 17

Listing 3.2: Split-phase synchronisation with a phaser.

```

1

p = newPhaser(); // c = new Clock();

loop( // for (i = 0; i < N; i++)

2

t = newTid();

3

reg(t, p);

4

fork(t, // async clocked(p)

5

loop( // for (k=1; k \le M; k++)

6

// l=P[(i-1) % N]; r=P[(i+1) % N];

7

skip;

// c.resume();

8

adv(p);

// tmp = (1 + r) / 2;

9

skip;

// c.advance();

await(p);

10

// P[i] = tmp;

skip;

11

adv(p);

12

// c.advance();

await(p);

13

14

end); // for

end); // task

15

end); // outer loop

16

dereg(p); // revoke participation

17

end // program

18

```

consumer synchronisation pattern, sketched in Listing 3.3. Two groups of tasks, the producers and the consumers, synchronise their execution with a phaser p. Producer tasks only advance the phaser, while consumer tasks await consecutive phases of that phaser. Cyclic barriers cannot be used effectively to describe the producer-consumer pattern: since all participants of a cyclic barrier must wait for each other, then the execution of producers is constrained by the execution of consumers, which does not happen in Listing 3.3.

Pipeline parallelism is a parallel programming model based on the producer-consumer synchronisation pattern. In this programming model, computation is divided in stages that can run concurrently, where barrier synchronisation coordinates the execution order of different stages. Recent proposals of pipeline parallelism in the context of parallel programming languages include: Open-Stream [87] for OpenMP, StreamX10 [107] and clocked variables [12] for X10, and phaser beams [96] for HJ.

Listing 3.3: Producer-consumer synchronisation with phasers.

```

p = newPhaser(); // c = new Phaser();

1

loop( // producers

2

3

t1 = newTid(); reg(t1, p); // producer

4

fork(t1,

loop( // for (i = 0; i < N; i++)

5

// B[i] = produce(i);

6

// signal consumer

7

adv(p);

end); // loop

8

end); // t1

9

end);

10

loop( // consumers

11

t2 = newTid(); reg(t2, p); // consumer

12

fork(t2,

13

14

loop( // for (i = 0; i < N; i++)

15

adv(p); await(p);

16

skip;

// consume(B[i]);

end); // loop

17

end); // t2

18

end);

19

dereg(p);

20

21

end // program

```

**Syntax** We propose the core language Brenner<sup>2</sup> to reason about task parallelism with phasers. The language itself is very basic—not even Turing-complete!—but provides a sufficient programming model to reason about the barrier abstractions surveyed in Chapter 2. We abstain from adding constructs unrelated to synchronisation, like data types, since such additions only complicates the semantics without bringing into play any novelty.

**Definition 3.1.1** (Language syntax). *The grammar in Fig. 3.1 defines our language.*

The grammar specifies how to construct a program in Brenner in an abstract syntax based *cf.* [86]. A *term* can be elementary or composed of other terms. A grammar defines *categories* (*i.e.*, sets) of terms. The set of all programs is

<sup>&</sup>lt;sup>2</sup> Originating from the Star Trek television series, the minor character Brenner [8] is referred as a phaser specialist on the script for the episode "Balance of Terror". Brenner serves under the command of Captain James T. Kirk and is responsible for coordinating and maintaining the phaser weapons of the USS Enterprise.

3.1. SYNTAX 19

```

b ::=

Programs

end program

end

| i; b

construct program

i ::=

Instructions

| t = newTid()

new task identifier

| fork(t, b)

spawns the execution of a task

p = newPhaser()

create a phaser

| \operatorname{reg}(t, p) |

register task with phaser

deregister current task from phaser

\mid dereg(p)

\mid adv(p)

advance local phase

\mid await(p, n)

await for phase n

await(p)

await current phase

control the flow

Control flow

c ::=

skip

internal action

| loop(b)|

non-deterministic loop

```

Figure 3.1: Top-level syntax.

an example of a category of terms. In Brenner, a program is composed by instructions, which are themselves other terms. Notation ::= declares a term category: in the left-hand side there is a *meta-variable* (a letter) that ranges over the terms of that category; in the right-hand side the declaration of the alternative terms, separated by a vertical bar |, that reads as "or."

The grammar of Brenner consists of two categories of terms: programs ranged over by b, and instructions ranged over by i. The definition of a program b has two possible terms: it is either (i) an elementary term end, or (ii) a construct program term that is composed of an instruction i followed by the continuation program b. The alternatives in the right-hand side of ::= work as templates, so any meta-variable that appears in the right-hand side of ::= does not represent a specific instance, but a placeholder for a term of that category. For instance, term b that appears in i; b represents a placeholder for any program term that can be constructed using the grammar Fig. 3.1.

The grammar relies on a base set of phaser names  $\mathcal{P}$ , ranged over by p and by q; a base set of task names  $\mathcal{T}$ , ranged over by t; and a set  $\mathcal{N}$  of natural numbers, ranged over by n and by m.

```

S ::= (M,T) State M ::= \{p_1 \colon P_1, \dots, p_n \colon P_n\} Phaser maps T ::= \{t_1 \colon b_1, \dots, t_n \colon b_n\} Task maps P ::= \{t_1 \colon n_1, \dots, t_m \colon n_m\} Phaser value b ::= \dots \mid idle

```

Figure 3.2: Syntax of the abstract machine.

#### 3.2 Operational Semantics

The formalism that specifies the meaning of Brenner is known as *operational* semantics, and it describes how computation develops. Operational semantics can be divided into two categories: small-step semantics that describes the individual steps of computation, and big-step semantics that describes how the overall results are obtained (*i.e.*, given an input state, what is the final outcome state). Concurrent languages are usually specified in small-step semantics since big-step semantics "hides" the intermediate steps that lead to a result. The gist of small-step operational semantics is to define (i) the state of an abstract machine (or abstract computer), and (ii) the effects of each possible action on a given state. A grammar specifies the state of an abstract machine. A (binary) reduction relation  $(\rightarrow)$  defines (ii), by relating the state of the machine before execution with the state of the machine after execution of a single indivisible action.

**Definition 3.2.1** (Abstract machine). Fig. 3.2 depicts the syntax of the abstract machine.

An abstract machine has a state S that pairs a phaser map M with a task map T. The phaser map M stores the available phasers, mapping addresses to phasers. A phaser P maps task identifiers to naturals. The task map T holds programs b, labelled by task names t. We extend the syntax of programs, by adding the runtime-only instruction idle, to represent a task that is ready to be started (a side effect of instruction newTid).

The following function loads a program into the abstract machine. We use notation  $\stackrel{\text{def}}{=}$  for the definition of functions and constants. The initial state consists of an empty phaser map and a single task  $t_d$ . The program is loaded into task  $t_d$ , which commences without being registered with any phaser.

**Definition 3.2.2** (Load function).

$$load(b) \stackrel{\text{def}}{=} (\emptyset, \{t_d \colon b\})$$

$$\begin{split} \left(M,T \uplus \{t\colon t' = \mathtt{newTid}();b\}\right) &\to \left(M,T \uplus \{t\colon b\} \uplus \{t'\colon \mathtt{idle}\}\right) \text{ (R-NEW-T)} \\ \left(M,T \uplus \{t\colon \mathtt{fork}(t',b');b\} \uplus \{t'\colon \mathtt{idle}\}\right) &\to \left(M,T \uplus \{t\colon b\} \uplus \{t'\colon b'\}\right) \\ & \qquad \qquad \qquad \qquad \qquad \qquad \qquad \qquad \\ \frac{c;b \to b'}{\left(M,T \uplus \{t\colon (B,c;b)\}\right) \to \left(M,T \uplus \{t\colon (B,b')\}\right)} \end{split} \tag{R-Flow)} \end{split}$$

Figure 3.3: The small-step semantics of Brenner (tasks).

Let b be the program in Listing 3.2. An abstract machine running b has an initial state load(b), defined as follows.

$$(\emptyset, \{t_d: p = \texttt{newPhaser}(); \texttt{loop}(b_l); \texttt{dereg}(p); \texttt{end}\})$$

(3.1)

**Definition 3.2.3** (Domain, empty map, and update.). Given a map, we write dom M for the domain of map M. We use notation  $\emptyset$  for the empty map, such that no element is in its domain. When x is not in the domain of map  $M_1$ , we write  $M_1 \uplus \{x \colon y\}$  for map  $M_2$  such that dom  $M_2 = \text{dom } M_1 \cup \{x\}$ ,  $M_2(x) = y$ , and  $M_2(z) = M_1(z)$  for all  $z \in \text{dom } M_1$ .

The reduction relation  $(\rightarrow)$  for Brenner is defined by a set of *inference rules* in Figs. 3.3 to 3.5. The rules are syntax-oriented, which means that there is only one rule per instruction i, e.g., rule R-new-p describes the behaviour of instruction newPhaser.

An inference rule defines a conclusion C that follows from some premises  $P_1, P_2, \ldots, P_n$ . The general notation of an inference rule is

$$\frac{P_1 \qquad P_2 \qquad \cdots \qquad P_n}{C}$$

considering that symbol  $\land$  is the logical conjunction and symbol  $\implies$  is the logical implication the above notation is equivalent to

$$P_1 \wedge P_2 \wedge \cdots \wedge P_n \implies C$$

When there are no premises (n=0), the rule is called an *axiom* and we omit the over bar, as in rule R-fork.

Given a reduction  $S \to S'$ , state S is an input parameter and state S' an output parameter. A system of inference rules, such as an operational semantics, matches any input parameters and infers, or produces, any output parameters. Henceforth, we say task t (phaser p) as short for the task (phaser) labelled by t.

(R-AWAIT)

Figure 3.4: The small-step semantics of Brenner (phasers).

$\frac{M(p)(t) = n}{\left(M, T \uplus \{t \colon \mathsf{await}(p); b\}\right) \to \left(M, T \uplus \{t \colon \mathsf{await}(p, n); b\}\right)}$

Recall the initial state of program b, defined in Formula 3.1, and let it be state  $S_1$ .

$$\left(\emptyset, \left\{t_d \colon p = \mathtt{newPhaser}(); t_1 = \mathtt{newTid}(); \mathtt{reg}(t_1, p); \mathtt{fork}(t_1, b_1); b_d\right\}\right)$$

If we can construct a state  $S_2$  that is in the reduction relation with  $S_1$

$$S_1 \rightarrow S_2$$

then we say that state  $S_1$  reduces to state  $S_2$ . Yet, not all states reduce. In particular, since all reduction rules expect a task map with at least one task, state  $(\emptyset, \emptyset)$  does not reduce.

To check that  $S_1 \to S_2$  holds, we match the syntax of  $S_1$  with every reduction rule. Multiple rules may match the syntax, so it is possible to have more than one state  $S_2$  that is in relation with  $S_1$ —in fact, that is how we encode concurrency!

The inference rules have implicit universal quantification on every metavariable that appears in an input parameter. In the case of rule R-New-P there is an implicit  $\forall M, T, t, p, b$ :

$$\big(M,T \uplus \{t \colon p = \mathtt{newPhaser}();b\}\big) \to \big(M \uplus \big\{p \colon \{t \colon 0\}\big\}, T \uplus \{t \colon b\}\big)$$

$$\begin{array}{c} \mathtt{skip}; b \to b & \text{(R-skip)} \\ \mathtt{loop}(b); b' \to b \cdot (\mathtt{loop}(b); b') & \text{(R-iter)} \\ \mathtt{loop}(b); b' \to b' & \text{(R-elide)} \end{array}$$

Figure 3.5: Small step semantics for control flow instructions  $c; b \to b$ .

Hence, applying rule R-New-P to  $S_1 \rightarrow S_2$  yields

$$\begin{split} & \big(\emptyset, \big\{t_d \colon p = \mathtt{newPhaser}(); \mathtt{loop}(b_l); \mathtt{dereg}(p); \mathtt{end} \big\} \big) \\ \rightarrow & \big( \big\{p \colon \{t_d \colon 0\} \big\}, \big\{t_d \colon \mathtt{loop}(b_l); \mathtt{dereg}(p); \mathtt{end} \big\} \big) \end{split}$$

with  $M \stackrel{\text{def}}{=} \emptyset$ ,  $T \stackrel{\text{def}}{=} \emptyset$ ,  $t \stackrel{\text{def}}{=} t_d$ ,  $p \stackrel{\text{def}}{=} p$ , and  $b \stackrel{\text{def}}{=} \mathsf{loop}(b_l)$ ;  $\mathsf{dereg}(p)$ ; end. Rule R-NEW-P allocates a new phaser, with a single registered task (the creator of the phaser).

Let  $S_3$  be such that relation  $S_2 \to S_3$ . The relation holds with rule R-flow, but we must show that the control flow instruction loop  $b_l$  reduces. Reduction for control flow instructions is defined in Fig. 3.5. Program concatenation is defined as expected.

#### **Definition 3.2.4** (Sequence concatenation).

$$(i;b) \cdot b' \stackrel{\text{def}}{=} i; (b \cdot b')$$

end  $\cdot b \stackrel{\text{def}}{=} b$

Applying rule R-ITER yields

$loop(b_l); dereg(p); end \rightarrow t_1 = newTid(); reg(t_1, p); fork(t_1, b_f); b_d$  where

$$b_l \cdot \mathtt{loop}(b_l); \mathtt{dereg}(p); \mathtt{end} \stackrel{\mathrm{def}}{=} t_1 = \mathtt{newTid}(); \mathtt{reg}(t_1, p); \mathtt{fork}(t_1, b_f); b_d$$

Hence, with rule R-FLOW we have that  $S_2 \rightarrow S_3$ .

$$\begin{split} & \big(\big\{p\colon\{t_d\colon 0\}\big\}, \big\{t_d\colon \mathtt{loop}(b_l); \mathtt{dereg}(p); \mathtt{end}\big\}\big) \\ \rightarrow & \big(\big\{p\colon\{t_d\colon 0\}\big\}, \big\{t_d\colon t_1 = \mathtt{newTid}(); \mathtt{reg}(t_1, p); \mathtt{fork}(t_1, b_f); b_d\big\}\big) \end{split}$$

Let  $S_4$  be such that relation  $S_3 \to S_4$  holds. With rule R-New-T we get the following formula

$$\begin{aligned} & \big(\big\{p\colon\{t_d\colon 0\}\big\}, \big\{t_d\colon t_1 = \mathtt{newTid}(); \mathtt{reg}(t_1,p); \mathtt{fork}(t_1,b_f); b_d\big\}\big) \\ \rightarrow & \big(\big\{p\colon\{t_d\colon 0\}\big\}, \big\{t_d\colon \mathtt{reg}(t_1,p); \mathtt{fork}(t_1,b_f); b_d, t_1\colon \mathtt{idle}\big\}\big) \end{aligned}$$

Rule R-New-T extends the task map with an idle task  $t_1$ . At the syntax level, newTid only displays a task name, but at the operational semantics level the instruction creates a special "idle" task to ensure that there are no task-name clashes. An idle task becomes a running one with a fork.

Let  $S_5$  be such that relation  $S_4 \to S_5$  holds. With rule R-reg we get the following formula

$$(\{p: \{t_d: 0\}\}, \{t_d: \mathtt{reg}(t_1, p); \mathtt{fork}(t_1, b_f); b_d, t_1: \mathtt{idle}\}) \\ \rightarrow (\{p: \{t_d: 0, t_1: 0\}\}, \{t_d: \mathtt{fork}(t_1, b_f); b_d, t_1: \mathtt{idle}\})$$

Rule R-reg extends the phaser addressed by p with the new participant  $t_1$ . The local phase of the registered task is inherited from the registrant, so in this case both are at the local phase 0. The configuration of the phaser map indicates that the task invoking R-reg is registered with the phaser.

Let  $S_5$  be such that relation  $S_4 \to S_5$  holds. With rule R-fork we get the following formula

$$(\{p: \{t_d: 0, t_1: 0\}\}, \{t_d: \mathtt{fork}(t_1, b_f); b_d, t_1: \mathtt{idle}\}) \\ \rightarrow (\{p: \{t_d: 0, t_1: 0\}\}, \{t_d: b_d, t_1: b_f\})$$

Rule R-fork simply replaces the body of idle task  $t_1$  with the parameter of fork, program  $b_f$ . The parameter of idle identifies the creator of the task name. The syntactic restriction in the rule ensures that only task  $t_d$  can fork a task named  $t_1$ .

Recall that

$$b_d \stackrel{\text{def}}{=} \mathsf{loop}(b_l); \mathsf{dereg}(p); \mathsf{end}$$

and

$$b_f \stackrel{\mathrm{def}}{=} \mathtt{adv}(p); \mathtt{await}(p); \mathtt{adv}(p); \mathtt{await}(p); \mathtt{end}$$

There are two possible reductions for state  $S_5$ , one uses rule R-flow, another uses rule R-advance. Such nondeterminism represents the concurrency present in parallel execution. We continue reducing with task  $t_d$  to conclude the discussion of task membership. We place the rule next to the reduction operator

to help the reader.

```

\left\{ \{p \colon \{t_d \colon 0, t_1 \colon 0\} \}, \\ \{t_d \colon \mathsf{loop}(b_l); \mathsf{dereg}(p); \mathsf{end}, t_1 \colon b_f \} \right)   \mathsf{R}\text{-FLOW} \to \left( \left\{ p \colon \{t_d \colon 0, t_1 \colon 0\} \right\}, \\ \{t_d \colon t_2 = \mathsf{newTid}(); \mathsf{reg}(t_2, p); \mathsf{fork}(t_2, b_f); b_d, t_1 \colon b_f \} \right)   \mathsf{R}\text{-NEW-T} \to \left( \left\{ p \colon \{t_d \colon 0, t_1 \colon 0\} \right\}, \\ \{t_d \colon \mathsf{reg}(t_2, p); \mathsf{fork}(t_2, b_f); b_d, t_1 \colon b_f, t_2 \colon \mathsf{idle} \right\} \right)   \mathsf{R}\text{-REG} \to \left( \left\{ p \colon \{t_d \colon 0, t_1 \colon 0, t_2 \colon 0\} \right\}, \\ \{t_d \colon \mathsf{fork}(t_2, b_f); b_d, t_1 \colon b_f, t_2 \colon \mathsf{idle} \right\} \right)   \mathsf{R}\text{-FORK} \to \left( \left\{ p \colon \{t_d \colon 0, t_1 \colon 0, t_2 \colon 0\} \right\}, \\ \{t_d \colon \mathsf{loop}(b_l); \mathsf{dereg}(p); \mathsf{end}, t_1 \colon b_f, t_2 \colon b_f \right\} \right)   \mathsf{R}\text{-FLOW} \to \left( \left\{ p \colon \{t_d \colon 0, t_1 \colon 0, t_2 \colon 0\} \right\}, \\ \{t_d \colon \mathsf{dereg}(p); \mathsf{end}, t_1 \colon b_f, t_2 \colon b_f \right\} \right)

```

Let  $S_6 \to S_7$  hold With rule R-dereg.

$$\left( \left\{ p \colon \{t_d \colon 0, t_1 \colon 0, t_2 \colon 0\} \right\}, \left\{ t_d \colon \mathsf{dereg}(p); \mathsf{end}, t_1 \colon b_f, t_2 \colon b_f \right\} \right) \\ \to \left( \left\{ p \colon \{t_1 \colon 0, t_2 \colon 0\} \right\}, \left\{ t_d \colon \mathsf{end}, t_1 \colon b_f, t_2 \colon b_f \right\} \right)$$

Rule R-dereg removes the issuer task  $t_d$  from the phaser addressed by p. The syntactic configuration of the phaser after reduction indicates that  $t_d$  revoked its membership with phaser p.

We proceed by reducing state  $S_7$ . Let  $b_2 \stackrel{\text{def}}{=} \mathtt{adv}(p)$ ; await(p); end. At this point we can reduce term with either task  $t_1$  or task  $t_2$ . We choose to reduce with task  $t_1$ . With rule R-ADVANCE and then with R-AWAIT we get the following formula.

```

\begin{split} & \big( \big\{ p \colon \{t_1 \colon 0, t_2 \colon 0 \} \big\}, \big\{ t_d \colon \mathsf{end}, t_1 \colon \mathsf{adv}(p); \mathsf{await}(p); b_2, t_2 \colon b_f \big\} \big) \\ & \to \big( \big\{ p \colon \{t_1 \colon 1, t_2 \colon 0 \} \big\}, \\ & \quad \big\{ t_d \colon \mathsf{end}, t_1 \colon \mathsf{await}(p); b_2, t_2 \colon \mathsf{adv}(p); \mathsf{await}(p); b_2 \big\} \big) \\ & \to \big( \big\{ p \colon \{t_1 \colon 1, t_2 \colon 0 \} \big\}, \\ & \quad \big\{ t_d \colon \mathsf{end}, t_1 \colon \mathsf{await}(p, 1); b_2, t_2 \colon \mathsf{adv}(p); \mathsf{await}(p); b_2 \big\} \big) \end{split}

```

Rule R-advance increments the local phase of the registered task  $t_1$ , enforced by the syntactic structure of the phaser. Rule R-await rewrites the await by making the wait explicit at the local phase of task  $t_1$ .

The only rule that can be applied to the state above is R-advance, which executes task  $t_2$ . Task  $t_1$  must wait for task  $t_2$  to advance its phase to 1. With rule R-advance we get the next formula.

```

\begin{split} & \big( \big\{ p \colon \{t_1 \colon 1, t_2 \colon 0 \} \big\}, \\ & \big\{ t_d \colon \mathsf{end}, t_1 \colon \mathsf{await}(p, 1); b_2, t_2 \colon \mathsf{adv}(p); \mathsf{await}(p); b_2 \big\} \big) \\ & \to \big( \big\{ p \colon \{t_1 \colon 1, t_2 \colon 1 \} \big\}, \big\{ t_d \colon \mathsf{end}, t_1 \colon \mathsf{await}(p, 1); b_2, t_2 \colon \mathsf{await}(p); b_2 \big\} \big) \end{split}

```

Synchronisation happens with rule R-SYNC.

```

\big( \big\{ p \colon \{t_1 \colon 1, t_2 \colon 1\} \big\}, \big\{ t_d \colon \mathtt{end}, t_1 \colon \mathtt{await}(p, 1); b_2, t_2 \colon \mathtt{await}(p); b_2 \big\} \big) \\ \to \big( \big\{ p \colon \{t_1 \colon 1, t_2 \colon 1\} \big\}, \big\{ t_d \colon \mathtt{end}, t_1 \colon b_2, t_2 \colon \mathtt{await}(p); b_2 \big\} \big)

```

Rule R-sync consumes the await when its premise is enabled, by checking that every registered task is at least at phase 1.