## **AIR Project Final Report**

José Rufino (DI-FCUL) Sérgio Filipe (Skysoft Portugal, SA.)

DI-FCUL

TR-07-35

December 2007

Departamento de Informática Faculdade de Ciências da Universidade de Lisboa Campo Grande, 1749-016 Lisboa Portugal

Technical reports are available at http://www.di.fc.ul.pt/tech-reports. The files are stored in PDF, with the report number as filename. Alternatively, reports are available by post from the above address.

## Abstract

This document describes the main results of AIR, an innovation initiative sponsored by ESA, the European Space Agency. The acronym AIR stands for ARINC 653 Interface in RTEMS. The ARINC 653 is a civil aviation world specification addressing safety critical and certification issues in embedded systems software. The AIR Project studied the adoption of ARINC 653 in space on-board software together with the utilization of RTEMS, the Real-Time Executive for Multiprocessor Systems.

This document: (i) describes the main issues regarding the AIR architecture specification; (ii) addresses how space and time partitioning could be provided in an abstract processor infrastructure, as well as those requirements can be mapped into both SPARC ERC32/LEON and Intel IA-32 (80x86) architectures; (iii) describes how to achieve the mapping of the ARINC 653 service interface in RTEMS; (iv) identifies the most relevant module dependencies of RTEMS with regard to AIR implementations; (v) identifies a preliminary set of modifications to be introduced in the RTEMS application production chain for the implementation of AIR-based systems (exemplified through a proof of concept prototype).

AIR WP3 Deliverable

**AIR Final Report**

Company: Skysoft Portugal & FCUL

Date: 12-11-2007 Issue: 1.0

# AIR

## **ARINC 653 Interface in RTEMS**

# **AIR Final Report**

|          | Name          | Title             | Signature  | Date       |

|----------|---------------|-------------------|------------|------------|

| Written  | José Rufino   | Senior Researcher |            | 12-11-2007 |

| Written  | Sérgio Filipe | Technical Manager | 12-11-2007 |            |

| Verified | José Rufino   | Senior Researcher |            | 12-11-2007 |

| Verified | Sérgio Filipe | Technical Manager |            | 12-11-2007 |

| Verified | José Neves    | Project Manager   |            | 12-11-2007 |

| Approved | José Neves    | Project Manager   |            | 12-11-2007 |

|          |               |                   |            |            |

|          |               |                   |            |            |

| Date       | Description                                 | Author                     |

|------------|---------------------------------------------|----------------------------|

| 12-11-2007 | ARINC 653 Interface in RTEMS – Final Report | Sérgio Filipe, José Rufino |

|            |                                             |                            |

|            |                                             |                            |

|            |                                             |                            |

|            |                                             |                            |

|            |                                             |                            |

|            |                                             |                            |

AIR WP3 Deliverable

**AIR Final Report**

Company: Skysoft Portugal & FCUL

Date: 12-11-2007 Issue: 1.0

## **Table of Contents**

| TABLE                                                   | OF CONTENTS                                                                                                                                                                                                                                                                                          | 2             |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| LIST O                                                  | F FIGURES                                                                                                                                                                                                                                                                                            | 4             |

| LIST O                                                  | F TABLES                                                                                                                                                                                                                                                                                             | 5             |

| 1                                                       | INTRODUCTION                                                                                                                                                                                                                                                                                         | 6             |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6                  | PURPOSE<br>SCOPE<br>APPLICABLE DOCUMENTS<br>REFERENCE DOCUMENTS<br>DOCUMENT OUTLINE<br>DOCUMENT CONTRIBUTIONS                                                                                                                                                                                        |               |

| 1.7                                                     | ACRONYMS AND ABBREVIATIONS                                                                                                                                                                                                                                                                           |               |

| 2                                                       | AIR FUNDAMENTAL CONCEPTS                                                                                                                                                                                                                                                                             | 9             |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5                         | INTRODUCTION<br>ARINC 653 STANDARD<br>ARINC 653 APPLICATION PARTITIONING<br>ARINC 653 SYSTEM ARCHITECTURE<br>AIR DEFINITION FUNDAMENTAL ISSUES                                                                                                                                                       | 9<br>11<br>11 |

| 3                                                       | AIR ARCHITECTURE DESIGN SPECIFICATION                                                                                                                                                                                                                                                                | 13            |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.4.1<br>3.5<br>3.6         | DEFINING THE AIR ARCHITECTURE.<br>AIR PMK – THE AIR PARTITION MANAGEMENT KERNEL.<br>AIR PROCESS SCHEDULING HIERARCHICAL INTEGRATION<br>AIR RTOS INTEGRATION.<br><i>AIR RTOS Integration: RTEMS.</i><br>BUILDING THE AIR ARCHITECTURE AND ITS COMPONENTS .<br>SUMMARY OF AIR ARCHITECTURE ATTRIBUTES. |               |

| 4                                                       | AIR MECHANISMS FOR SPATIAL AND TEMPORAL SEGREGATION                                                                                                                                                                                                                                                  | 20            |

| 4.1<br>4.1.2<br>4.2<br>4.2.1<br>4.2.2<br>4.2.2<br>4.2.3 | SPATIAL SEGREGATION<br>Memory Protection Mechanisms in SPARC LEON Cores<br>Memory Protection Mechanisms in Intel IA-32 (80X86) Processors<br>TEMPORAL SEGREGATION<br>Partition Scheduling<br>Partition Dispatching<br>Process Scheduling and Dispatching.                                            |               |

| 5                                                       | AIR APEX INTERFACE IMPLEMENTATION                                                                                                                                                                                                                                                                    | 31            |

| 5.1<br>5.1.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3          | DEVELOPMENT ENVIRONMENT<br>Initialization<br>IMPLEMENTED APEX SERVICES<br>AIR Partition Management<br>AIR Process Management<br>AIR Blackboard services                                                                                                                                              |               |

| 6                                                       | AIR RTEMS INTEGRATION                                                                                                                                                                                                                                                                                |               |

| 7                                                       | AIR APPLICATION BUILD PROCESS                                                                                                                                                                                                                                                                        | 40            |

| 7.1                                                     | BUILD TOOLS AND ITS UTILIZATION                                                                                                                                                                                                                                                                      | 40            |

| 8                                                       | AIR PROOF OF CONCEPT PROTOTYPES                                                                                                                                                                                                                                                                      | 41            |

#### AIR WP3 Deliverable

Company: Skysoft Portugal & FCUL

# Faculdade de Ciências

AIR Final Report

Date: 12-11-2007 Issue: 1.0

| 8.1   | PROTOTYPING ENVIRONMENT                                         | 41 |

|-------|-----------------------------------------------------------------|----|

| 8.2   | MULTI-EXECUTIVE CORE DEMONSTRATOR                               | 43 |

| 8.3   | APEX INTERFACE DEMONSTRATOR                                     |    |

| 8.3.1 | APEX interfaces demonstrator resources                          |    |

| 8.3.2 | APEX Interface Demonstrator functionality                       | 45 |

| 8.3.3 | APEX Interface Demonstrator execution and results visualization | 47 |

| 9     | CONCLUSIONS AND FUTURE CHALLENGES                               | 49 |

| ANNEX | A AIR RESULTS SUMMARY                                           | 51 |

| A.1   | AIR DELIVERABLE REPORTS                                         |    |

| A.2   | AIR PROTOTYPE DEMONSTRATORS                                     |    |

| A.3   | AIR CURRENT PUBLICATIONS                                        | 51 |

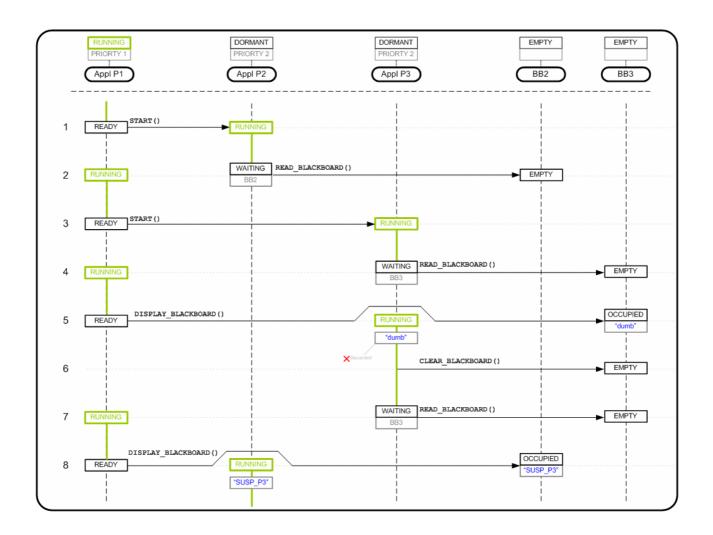

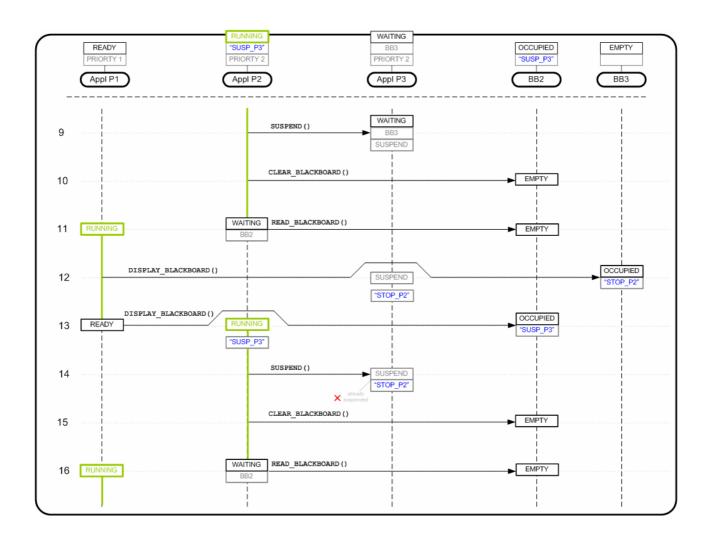

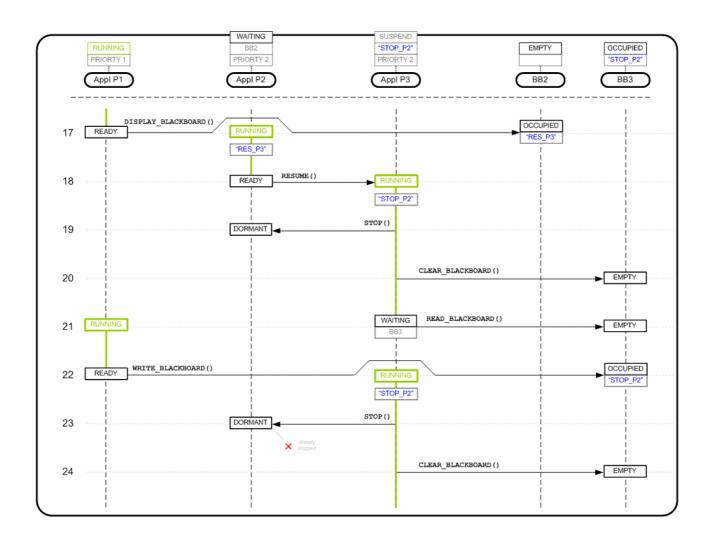

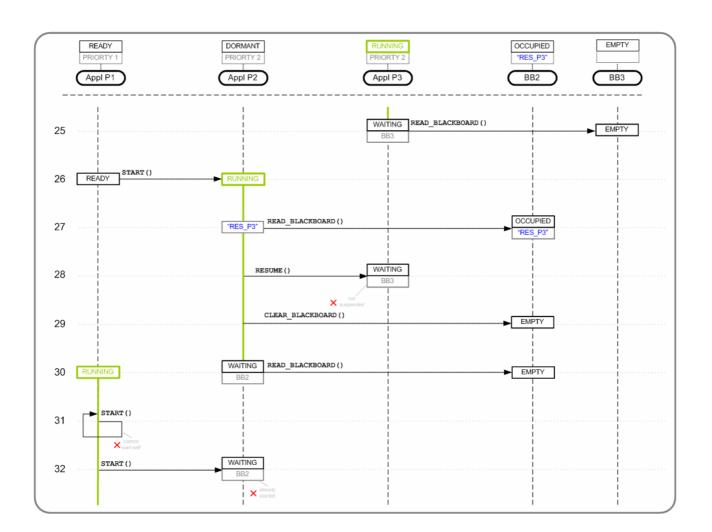

| ANNEX | B APEX INTERFACE DEMONSTRATOR ACTIVITY DIAGRAMS                 |    |

AIR WP3 Deliverable Company: Skysoft Portugal & FCUL

AIR Final Report

Date: 12-11-2007 Issue: 1.0

## List of Figures

| Figure 1 – Overview of the standard ARINC 653 System Architecture                               | 11 |

|-------------------------------------------------------------------------------------------------|----|

| Figure 2 – Overview of the AIR System Architecture                                              |    |

| Figure 3 – Typical structure of a RTEMS Application                                             | 17 |

| Figure 4 – Building an AIR System.                                                              | 18 |

| Figure 5 – Memory Protection through Monitoring of Addressing Spaces                            | 20 |

| Figure 6 – The ATMEL AT697E SPARC LEON2 RAM Memory Protection Mechanisms                        | 23 |

| Figure 7 – Usage of ATMEL AT697E RAM Memory Protection Mechanisms in AIR                        |    |

| Figure 8 – The Gaisler SPARC LEON3 SPARC V8 MMU Architecture                                    |    |

| Figure 9 – The Gaisler SPARC LEON3 MMU Operation                                                | 25 |

| Figure 10 – The Intel IA-32 Segment-based Memory Protection Mechanisms                          | 26 |

| Figure 11 – The Intel IA-32 Page-based Memory Protection Mechanisms                             | 27 |

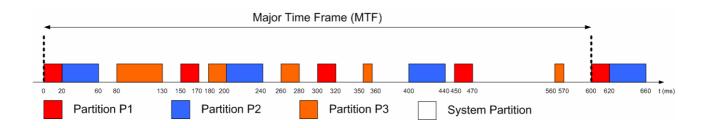

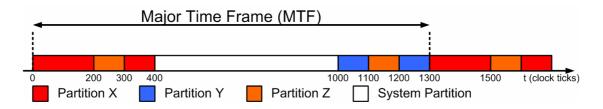

| Figure 12 - Example of Partition Scheduling over a Major Time Frame                             | 28 |

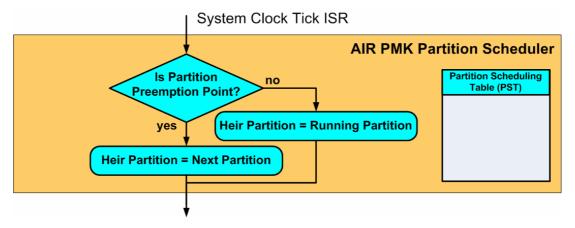

| Figure 13 - AIR PMK Partition Scheduler functionality                                           |    |

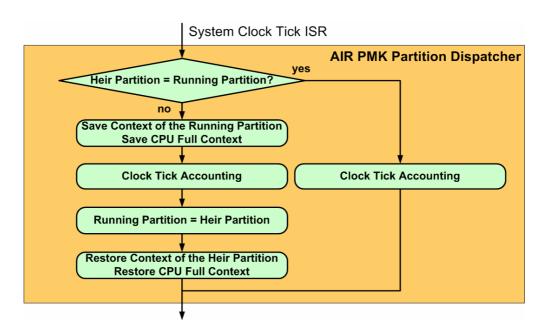

| Figure 14 – AIR PMK Partition Dispatcher functionality                                          |    |

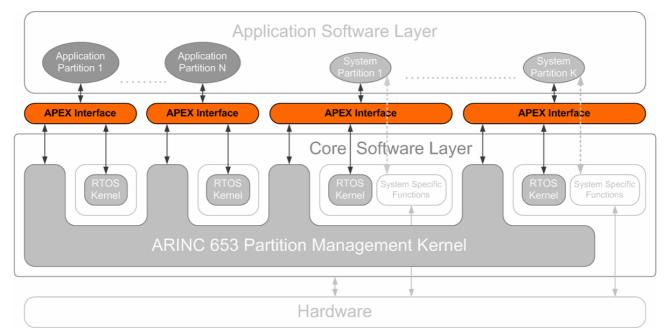

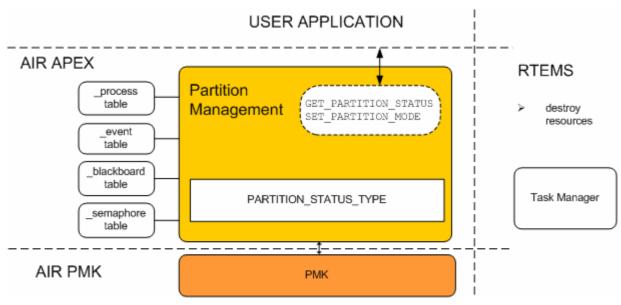

| Figure 15 – The APEX interface in the multi-executive AIR architecture                          | 31 |

| Figure 16 – init CODE                                                                           |    |

| Figure 17 - Partition Management interfaces                                                     | 33 |

| Figure 18 – AIR Process Control Data                                                            | 34 |

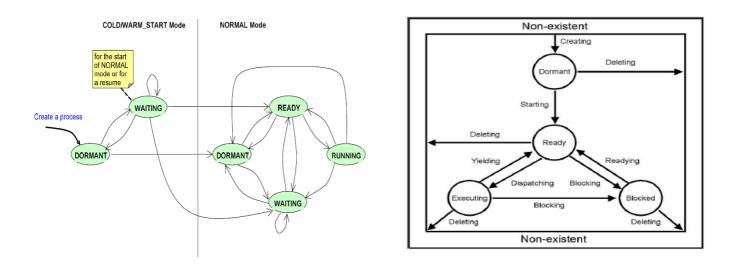

| Figure 19 – ARINC 653 process states (on the left) vs RTEMS task states                         | 35 |

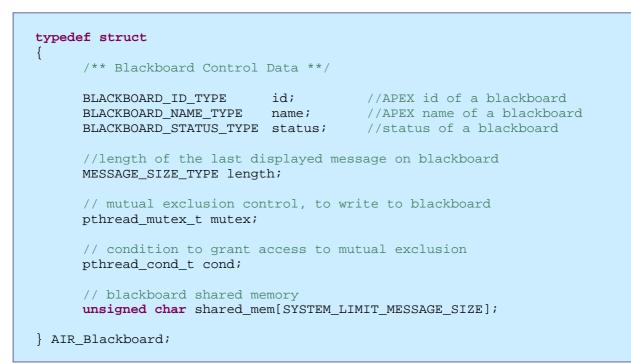

| Figure 20 – AIR Blackboard Control Data                                                         | 37 |

| Figure 21 – RTEMS modules excluded from partitions by AIR design                                | 38 |

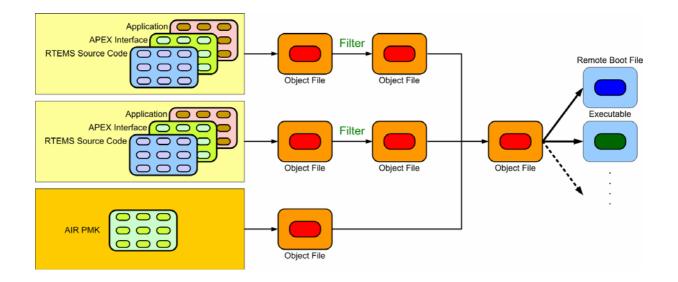

| Figure 22 – Specialized Use of Canonical Build Tools in Multi-Executive Core Development        | 40 |

| Figure 23 - The VITRAL visualization environment as used in the AIR proof of concept prototypes | 41 |

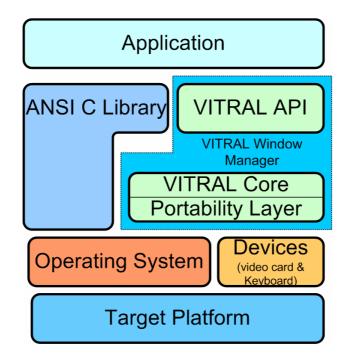

| Figure 24 – Architecture of the VITRAL visualization environment                                | 42 |

| Figure 25 - Example of Partition function assignment and scheduling over a Major Time Frame     | 43 |

| Figure 26 – Start task pseudo code                                                              | 45 |

| Figure 27 – Generic P2 and P3 process pseudo code                                               | 46 |

| Figure 28 – P1 operation pseudo code                                                            | 47 |

AIR WP3 Deliverable Company: Skysoft Portugal & FCUL

AIR Final Report

Date: 12-11-2007 Issue: 1.0

## List of Tables

| Table 1 – Applicable Documents                                           | 6 |

|--------------------------------------------------------------------------|---|

| Table 2 – Reference Documents                                            |   |

| Table 3 – Acronyms and Abbreviations                                     |   |

| Table 4 – Summary of AIR Multi-Executive Core Architecture Attributes    |   |

| Table 5 – Summary of AIR Process Scheduler Integration Attributes        |   |

| Table 6 – Characteristics of ATMEL AT697E RAM Address Space              |   |

| Table 7 – APEX Interface development environment                         |   |

| Table 8 – ARINC 653 and RTEMS process priorities                         |   |

| Table 9 - RTEMS Components and their integration in the AIR Architecture |   |

| Table 10 – AIR Deliverable Reports                                       |   |

| Table 11 – AIR Prototype Demonstrators                                   |   |

| Table 12 – AIR Current Publications                                      |   |

AIR WP3 Deliverable

**AIR Final Report**

Company: Skysoft Portugal & FCUL

Date: 12-11-2007 Issue: 1.0

#### 1 Introduction

#### 1.1 Purpose

The purpose of this document is to describe the study and results of the activities performed on the AIR (ARINC 653 Interface in RTEMS) project.

#### 1.2 Scope

This document defines the AIR Project WP3 output: <u>AIR Final Report</u>.

#### **1.3 Applicable Documents**

| Reference | Title                                                                              |

|-----------|------------------------------------------------------------------------------------|

| [AIRPROP] | AIR Proposal, Skysoft, September 2005                                              |

| [TMREPLY] | Technical Memo for the AIR Proposal (negotiation points replies)                   |

| [AIRMMIN] | Minutes of Meeting (From Project's Kick-Off Meeting to the Sixth Internal Meeting) |

| [AIRWP1]  | AIR WP1 Output: Requirements, Architecture and Services                            |

| [AIRWP2]  | AIR WP2 Output: Overall System Specification                                       |

| [AIR WP3] | AIR WP3 Output: AIR Design Results and Proof of Concept                            |

#### Table 1 – Applicable Documents

#### **1.4 Reference Documents**

| Reference    | Title                                                                                                                                                                                                                    |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [A653P1]     | ARINC Specification 653 Part 1 (Supplement 2), Required Services, Aeronautical Radio Inc., 2006                                                                                                                          |

| [A653P2]     | ARINC Specification 653 Part 2, Extended Services DRAFT 5, Aeronautical Radio Inc., 2006                                                                                                                                 |

| [RUFDIN]     | N. Diniz, J. Rufino, ARINC 653 In Space, Dasia 2005, Eurospace, Edinburgh                                                                                                                                                |

| [RUSHB1]     | J. Rushby, Partitioning in Avionics Architectures: Requirements, Mechanisms, and Assurance, Technical Report NASA / CR-1999-209347, SRI International, 1999                                                              |

| [DO248B]     | RTCA DO-248B, Final Annual Report For Clarification Of DO-178B "Software Considerations In Airborne Systems<br>And Equipment Certification"                                                                              |

| [RTEMSQUAL]  | J. Seronie-Vivien, C. Cantenot, RTEMS Operating System Qualification for the ERC32 Target, DASIA 2005, Eurospace Edinburgh                                                                                               |

| [RTEMSAPI]   | RTEMS C Users Guide – Native API, Edition 4.6.6, for RTEMS 4.6.6 - OAR                                                                                                                                                   |

| [RTEMSPOSIX] | RTEMS POSIX API User's Guide - Edition 4.6.6, for RTEMS 4.6.6 - OAR                                                                                                                                                      |

| [RTEMSI386]  | RTEMS Intel i386 Applications Supplement - Edition 4.6.6, for RTEMS 4.6.6 - OAR                                                                                                                                          |

| [RTEMSSPARC] | RTEMS SPARC Applications Supplement - Edition 4.6.6, for RTEMS 4.6.6 - OAR                                                                                                                                               |

| [COUT05a]    | M. Coutinho, J. Rufino, C. Almeida. Control of Event Handling Timeliness in RTEMS. Proceedings of the 17th IAESTED International Conference Parallel and Distributed Computing Systems, Phoenix, USA, November 2005.     |

| [COUT06a]    | M. Coutinho, C. Almeida, J. Rufino. VITRAL - A Text Mode Window Manager for Real-Time Embedded Kernels.<br>Proc. 11th IEEE Int. Conf. Emerging Technologies Factory Automation, Prague, Czech Republic, September, 2006. |

**AIR Final Report**

Date: 12-11-2007 Issue: 1.0

#### **Table 2 – Reference Documents**

#### 1.5 Document Outline

| Section 1 | Introduces the document by indicating its purpose and scope, its content and which documents it refers to.            |

|-----------|-----------------------------------------------------------------------------------------------------------------------|

| Section 2 | Introduces the AIR fundamental concepts.                                                                              |

| Section 3 | Describes the AIR architecture specification.                                                                         |

| Section 4 | Addresses the fundamental mechanisms for securing spatial and temporal segregation.                                   |

| Section 5 | Describes the interactions between the APEX interface and the AIR Partition Management Kernel (PMK)                   |

| Section 6 | Describes the RTEMS Module Dependency in the implementation of AIR-based systems and applications.                    |

| Section 7 | Addresses details of AIR applications production tool chain and its relation with canonical development environments. |

| Section 8 | Provides an overview of the AIR proof of concept prototypes                                                           |

| Section 9 | Concludes the document.                                                                                               |

| Annex A   | Summarizes a set of AIR Project Result indicators.                                                                    |

| Annex B   | Presents the APEX Interface Demonstrator Activity Diagrams                                                            |

#### **1.6 Document Contributions**

This document was jointly prepared by Faculdade de Ciências da Universidade de Lisboa (FCUL) and Skysoft Portugal.

Date: 12-11-2007 Issue: 1.0

#### 1.7 Acronyms and Abbreviations

| Acronym | Definition                                         |  |  |  |

|---------|----------------------------------------------------|--|--|--|

| AEEC    | Airlines Electronic Engineering Committee          |  |  |  |

| AIR     | ARINC 653 Interface in RTEMS                       |  |  |  |

| APEX    | Application Executive                              |  |  |  |

| ARINC   | Aeronautical Radio, Inc.                           |  |  |  |

| API     | Application Programming Interface                  |  |  |  |

| BSP     | Board Support Package                              |  |  |  |

| COTS    | Commercial Off The Shelf                           |  |  |  |

| CPU     | Central Processing Unit                            |  |  |  |

| DDD     | Data Display Debugger                              |  |  |  |

| eCos    | Embedded Configurable Operating System             |  |  |  |

| EUROCAE | European Organization for Civil Aviation Equipment |  |  |  |

| FAA     | Federal Aviation Administration                    |  |  |  |

| FCUL    | Faculdade de Ciências da Universidade de Lisboa    |  |  |  |

| FIFO    | First In First Out                                 |  |  |  |

| GCD     | Greatest Common Divisor                            |  |  |  |

| GDB     | GNU Debugger                                       |  |  |  |

| GNU     | GNU's Not Unix                                     |  |  |  |

| GRUB    | GRand Unified Bootloader                           |  |  |  |

| HAL     | Hardware Abstraction Layer                         |  |  |  |

| IMA     | Integrated Modular Avionics                        |  |  |  |

| ISR     | Interrupt Service Routine                          |  |  |  |

| MEC     | Multi-Executive Core                               |  |  |  |

| MILS    | Multiple Independent Levels of Security            |  |  |  |

| MMU     | Memory Management Unit                             |  |  |  |

| MTF     | Major Time Frame                                   |  |  |  |

| OS      | Operating System                                   |  |  |  |

| РМК     | Partition Management Kernel                        |  |  |  |

| PST     | Partition Scheduling Table                         |  |  |  |

| PTD     | Page Table Descriptor                              |  |  |  |

| PTE     | Page Table Entry                                   |  |  |  |

| RAM     | Random Access Memory                               |  |  |  |

| RTCA    | Radio Technical Commission for Aeronautics         |  |  |  |

| RTEMS   | Real-Time Executive for Multiprocessor Systems     |  |  |  |

| RTOS    | Real-time Operating System                         |  |  |  |

| SEC     | Single-Executive Core                              |  |  |  |

| SIS     | SPARC Instruction Simulator                        |  |  |  |

| ТСВ     | Task Control Block                                 |  |  |  |

#### Table 3 – Acronyms and Abbreviations

AIR WP3 Deliverable

Company: Skysoft Portugal & FCUL

AIR Final Report

Date: 12-11-2007 Issue: 1.0

## Faculdade de Ciências

#### 2 AIR Fundamental Concepts

#### 2.1 Introduction

In both avionics and space industries, the safety concept is of paramount importance. The ARINC 653 standard was developed with the purpose that all safety critical software embedded in a system must follow very strict and demanding rules both in terms of operation and certification.

ARINC 653 and Integrated Modular Avionics (IMA) are the answers provided by the civil aviation world to problems that are also identified in the space world. The space world is looking for a standardized interface for the Operating Systems (OS) located on board the spacecrafts. Most of the requirements from the civil aviation world that led to the definition of ARINC 653 are also requirements from the space world and thus the adaptation of the specification to the space world needs can be performed with minor changes, keeping its basic principles.

The adoption of the **ARINC 653 concept in space on-board software** will not only provide the space industry the same benefits the aviation industry has already profited with by adopting the standard – software portability and modularity, partitioning and less certification effort, etc. It will also promote the reusability of Research and Development (R&D) efforts already invested in the scope of another industry domain, further increase the synergies in the development of software for the parallel domains of civil aviation and space and potentiate reduction in the development costs of on-board software. Finally, the space world will benefit from ARINC 653's improvement in the development framework available for both application developers and integrators.

Furthermore, there is a general demand for the use and re-utilization of commercial off-the-shelf (COTS) components in the design of complex embedded systems, such as those found in aerospace applications. The AIR – <u>ARINC 653 Interface in RTEMS</u> – innovation initiative has emerged complying to this requirement, exploiting the utilization of a COTS licence-free open-source real-time operating system, the Real-Time Executive for Multiprocessor Systems (RTEMS). The use of RTEMS is particularly interesting given its qualification for critical on-board software of unmanned space programs.

The present document summarizes the main AIR design results: (i) it describes the AIR architecture specification; (ii) addresses how space and time partitioning could be provided in an abstract processor infrastructure, as well as those requirements can be mapped into both SPARC ERC32/LEON and Intel IA-32 (80x86) architectures; (iii) describes how to achieve the mapping of the ARINC 653 service interface in RTEMS; (iv) identifies the most relevant module dependencies of RTEMS with regard to AIR implementations; (v) identifies a preliminary set of modifications to be introduced in the RTEMS application production chain for the implementation of AIR-based systems (exemplified through a proof of concept prototype).

#### 2.2 ARINC 653 Standard

The ARINC 653 standard in essence defines an Application Executive (APEX) interface between the Operating System (OS) of a safety critical system and the application software developed for that system. The standard specification defines how data may be exchanged statically (through a given configuration profile) or dynamically (via the use of services). The ARINC 653 standard specifies the behavior of the set of services provided by the OS and used by the application.

The runtime environment provided by the APEX interface enables independently produced applications to execute together in the same hardware, providing support to spatial and time segregation of these applications through the usage of **partitions**.

Company: Skysoft Portugal & FCUL

AIR Final Report

Date: 12-11-2007 Issue: 1.0

The ARINC 653 standard specification aims language and hardware independency, thus promoting portability of the software whilst allowing modularity and versatility in the design, and flexibility in the selection of development tools, host platforms and target infrastructures. The standard specification also establishes a strict control over a computational system, both in terms of temporal and spatial segregation, as well as in the provision of a standard application programming interface (API).

### 2.3 ARINC 653 Application Partitioning

The ARINC 653 specification is one of the most important blocks from the Integrated Modular Avionics definition, where the partitioning concept emerges as a way to ensure protection and functional separation between applications. The partitioning concept aims enforcing fault containment, preventing fault propagation from one partition to another. It also eases system verification, validation and certification procedures.

The ARINC 653 standard specification describes a partition as being roughly the same as a program in a **single application environment** (comprising code and data, its configuration attributes and execution context) where one or more processes concurrently execute by sharing access to the processor infrastructure and other hardware resources.

The standard demands the functions resident on a core module to be partitioned with respect to space (memory partitioning) and time (temporal partitioning). A partition is therefore a program unit of the application designed to satisfy these partitioning constraints. A core module is responsible for enforcing partitioning and for the management of the individual partitions. Spatial (or memory) partitioning is achieved through allocation of predetermined areas of memory to each partition. Temporal partitioning ensures each partition uninterrupted access to common resources during predetermined time periods. Partitions are scheduled on a fixed, cyclic basis.

Configuration of all partitions throughout the whole system is expected to be under the control of the system integrator and maintained with configuration tables. The configuration table for the partition schedule will define the system major time frame (MTF).

#### 2.4 ARINC 653 System Architecture

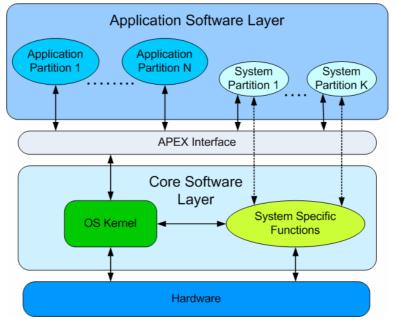

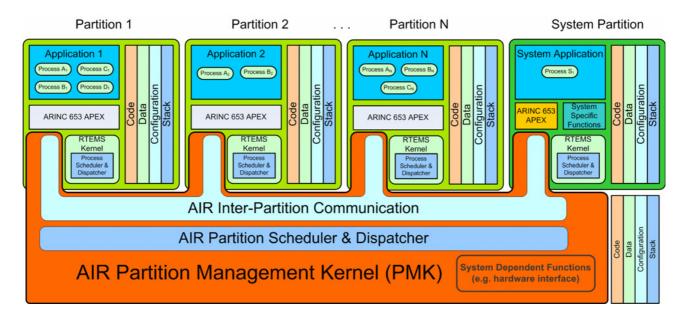

The general architecture of a standard ARINC 653 system is illustrated in Figure 1. It comprises the application software layer, with each application executing in a dedicated partition, and a given set of system partitions. The system partitions are optional components and are intended to manage the interactions with specific hardware devices. Appropriate support from the core software layer (e.g. hardware interfacing and device drivers) is required.

Figure 1 – Overview of the standard ARINC 653 System Architecture

**AIR Final Report**

Date: 12-11-2007 Issue: 1.0

Application partitions consist in general of one or more processes. The application partitions software exclusively uses the services provided by a **logical** Application Executive (APEX) interface, meaning it performs calls only to the set of primitives defined in the ARINC 653 standard specification. However, a system partition may use also a set of specific functions provided by the core software layer and may therefore bypass the standard APEX interface (cf. Figure 1).

In any case, the execution environment provided by the OS kernel module must furnish a relevant set of operating system services, such as process scheduling and management, time and clock management as well as inter-process synchronization and communication. The application software layer is obliged to strict robust space and time partitioning. Containment of possible faults inside the domain of each partition must be ensured by the core software layer.

Thus, each partition makes use of a **logical** execution environment. Given most of the process-level services that need to be supplied by the OS kernel module are already provided by common off-the-shelf real-time operating system (RTOS) kernels, a natural approach to the definition and design of ARINC 653 systems may use the functionality provided by the RTOS kernel, completed with the specific functions needed for ARINC 653 system operation, namely partition management mechanisms. From an architectural perspective the application executive (APEX) interface services are mapped into:

- the RTOS kernel canonical services, such as process management, time and clock management, inter-process synchronization and communication;

- the system specific OS and processor/platform functions, such as hardware interfacing and device driver functions, facilities for application downloading and support for built-in-self-testing;

- ARINC 653 specific functions, such as partition management and inter-partition communication.

The execution environment of each partition includes the corresponding application program (code and data), its configuration attributes and execution context.

#### 2.5 AIR Definition Fundamental Issues

The key point in the <u>definition and design of the AIR architecture</u> do concern how the functionality provided by the RTOS kernel should be integrated with the ARINC 653 specific mechanisms that need to be added to the core software layer.

The additional components, introduced to support ARINC 653 specific mechanisms, must exhibit a well defined interface specification in order to secure the <u>modularity</u> and <u>versatility</u> requirements.

Furthermore, the RTOS native components needing to be modified for the <u>integration in the AIR architecture</u> should be restricted to a minimum.

AIR WP3 Deliverable Company: Skysoft Portugal & FCUL

AIR Final Report

Date: 12-11-2007 Issue: 1.0

#### 3 AIR Architecture Design Specification

This section presents the <u>AIR Architecture Specification</u>, defining how the specific mechanisms required for conformity with the ARINC 653 standard specification can be effectively integrated with the functional structure of common RTOS kernels.

#### 3.1 Defining the AIR Architecture

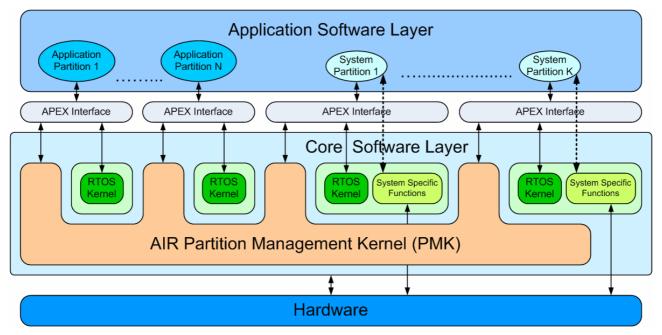

The fundamental architecture definition of the AIR system overall architecture is sketched in the diagram of Figure 2. It makes use of:

- a multi-executive core software layer;

- a two-level hierarchical scheduler.

A different instance of a RTOS kernel is used per partition. Even if the RTOS integration is homogeneous, i.e. even if the same RTOS kernel (e.g. RTEMS) is being used in every partition, these should be regarded as different RTOS kernels, with its own process scheduler. This structure allows the implementation of the hierarchical scheduler design approach.

Figure 2 – Overview of the AIR System Architecture

The integration of the different components in the architecture of Figure 2 assumes a well-defined specification of their interfaces in order to preserve the modularity characteristics of the architecture. The components added to the native RTOS kernel aim to supply the functionality missing in those operating systems, to be in conformity with the standard ARINC 653 specification. The fundamental AIR design components integrated in the architecture of Figure 2 are the following:

- the application executive (APEX) interface defining, for <u>each partition</u> in the system, the set of services defined in the ARINC 653 standard specification;

- the **native RTOS kernel**, which in conformity with the architectural attributes of the multi-executive core design can be specifically configured for each partition;

AIR WP3 Deliverable AIR Final Report

Date: 12-11-2007 Issue: 1.0

- the system partitions do an additional use of **system specific OS functions**, in general supplied also with the native RTOS distribution and that, again, may be individually configured in a perpartition basis;

- the **AIR Partition Management Kernel (PMK)**, made from a fundamental set of functional modules providing the specific functionality that needs to be added for conformity with the ARINC 653 standard specification.

The **application executive (APEX) interface** should be designed as much as possible by mapping the ARINC 653 service primitives into the service interface of the native RTOS kernel, i.e. into the native RTEMS primitives [RTEMSAPI], for the particular case of the current AIR architecture. As a design alternative, other OS interfaces may be used, such as the POSIX interface, also offered by RTEMS [RTEMSPOSIX]. In some specific cases, where the calling conventions or the functionality provided does not exactly match, a more complex design approach may be required.

In addition, the APEX interface may need to use specific services provided by the AIR Partition Management Kernel (PMK), allowing the invocation of specific functions and the exchange of system specific information such as partition configuration tables, partition status and operating modes, as well as other system-level parameters.

The use of highly configurable **RTOS kernels** allows an effective adaptation of the services provided by the RTOS kernel to the requirements of each partition. This is especially true for system partitions, where in addition to the standard application executive (APEX) interface there is a need for system specific OS functions.

The **system specific OS functions** in essence establish a set of interface stubs to address the specific details of each hardware platform. In conformity with the ARINC 653 standard specification, this functionality is only allowed in system partitions. However, even for system partitions, special attention must be given by the system integrator so that two partitions do not collide when controlling the same hardware. Usually the hardware is accessed through device drivers, so two system partitions should not access the same driver unless the driver itself supports this requirement.

Finally, the **AIR Partition Management Kernel (PMK)** includes the fundamental modules required to support the standard ARINC 653 functionality complemented with a set of complementary modules required to make the integration of the RTOS kernel and of the corresponding specific system OS functions effective. The AIR Partition Management Kernel (PMK) also has an attachment for the application executive (APEX) interface, intended for the provision of the AIR inter-partition communication services and other relevant system functions.

#### 3.2 AIR PMK – The AIR Partition Management Kernel

The main components of the <u>AIR Partition Management Kernel (PMK)</u> include the following functional modules:

- AIR inter-partition communication, allowing the exchange of information between different partitions without violating spatial segregation constraints.

- AIR partition dispatcher, which has the responsibility of saving the execution context of the partition to be deactivated (the currently running partition) and of restoring the execution context for the partition to be executed next (the heir partition). It also secures the management of spatial segregation.

- AIR partition scheduler, selecting at given times which partition owns system resources, namely the processing infrastructure. In conformity with the ARINC 653 standard specification, a cyclic fixed scheduler is used.

Date: 12-11-2007 Issue: 1.0

- AIR time manager, which has the responsibility of processing the strict time references provided by the hardware system clock, forwarding them to the appropriate system components in the AIR architecture.

- AIR Hardware Abstraction Layer (HAL), providing an effective level of abstraction for accessing the hardware resources.

The **AIR** inter-partition communication module is responsible for the encapsulation and transference of data from one partition to another in a spatial segregated environment. This implies the management of the corresponding memory protection mechanisms.

The **AIR partition dispatcher** is responsible for switching between partitions. It starts by saving the execution context of the partition being deactivated. Activating the next partition implies restoring the execution context for the partition, including the management of the spatial segregation mechanisms.

The **AIR partition scheduler** is responsible for securing time segregation, by restricting the processing time assigned to each partition, as defined by ARINC 653 system configuration. The ARINC 653 partition scheduler assigns the processor infrastructure to each partition in a cyclic fashion, within the period of a major time frame defined by system configuration. In the context of the AIR System Architecture, using a **two-level hierarchical scheduler** approach, the native RTOS kernel (e.g. RTEMS) is responsible for the scheduling of the processes inside each partition.

The **AIR time manager** should keep a record of the system clock ticks for latter announcement to the RTOS process scheduler of inactive partitions. This deferred announcement of system clock ticks is performed upon partition switching. The running partition and the corresponding RTOS process scheduler are immediately notified of each clock tick.

A specific **AIR Hardware Abstraction Layer (HAL)** should be included in the AIR Partition Management Kernel (PMK) for the processor architecture, processor family variant and hardware platform supported by a given AIR system. Within the scope of AIR project two case studies are currently addressed: the SPARC ERC32 and LEON processor cores; the Intel IA-32 (80x386) architecture.

The mapping of system specific OS functions related to the management of spatial segregation into the specific details that characterize a given processor architecture could be effectively handled by the AIR Hardware Abstraction Layer (HAL).

Other fundamental issues which have a significant impact in the design of the AIR Hardware Abstraction Layer (HAL) concerns the management of input/output (I/O) related functions and the management of interrupts and therefore of interrupt handlers. For example, the AIR Hardware Abstraction Layer (HAL) can provide a set of primitives that allow the establishment of interrupt handlers by the system partitions. The management of interrupts and of interrupt handlers is critical in the AIR Architecture and should be performed on a per-partition basis. This avoids that external events triggered inside the time window of a given partition may cause temporal interference in the running partition. Avoiding interrupt handlers associated to a given partition to be executed on the context of other partition also helps to preserve the integrity of the system.

The structure and the design of the AIR Partition Management Kernel (PMK) components, such as the AIR partition scheduler and dispatcher, should be made as much as possible independent of a given operating system. This contributes to a modular and flexible design of those components and therefore for a highly modular AIR Partition Management Kernel (PMK). All the processing infrastructure dependencies shall be included in AIR Hardware Abstraction Layer (HAL).

The AIR Partition Management Kernel (PMK) does not exhibit strict configuration requirements. The presence of almost all AIR Partition Management Kernel (PMK) functional components is mandatory. The only exception concerns the AIR inter-partition communication module, which only needs to be included in the architecture when such services are required.

Date: 12-11-2007 Issue: 1.0

The architecture of the AIR Partition Management Kernel (PMK) also needs a specific component to be included:

• AIR partition manager, which has the responsibility of performing the general initialization of the system, including invocation of all specific RTOS initialization managers. The AIR partition manager also allows reporting at the APEX interface specific AIR Partition Management Kernel (PMK) data, such as partition configuration tables and other system-level parameters.

The **AIR partition manager** is a fundamental component of the AIR PMK architecture in the sense it is responsible for the general initialization of all AIR PMK components including the initialization of each specific RTOS kernel. This concerns the preparation for starting multi-tasking mode and process execution in the RTOS kernel of each partition. Setting up multi-tasking mode and therefore process execution can only be started in one (and only one) partition after all partitions have been prepared to enter multi-tasking mode. This has been revealed as <u>one key point</u> in the design of the AIR PMK Multi-Executive Core architecture.

#### 3.3 AIR Process Scheduling Hierarchical Integration

The AIR architecture uses a two-level scheduler hierarchical approach to support the integration and effective interaction between the AIR Partition Scheduler and the scheduler provided at each partition for the scheduling of the processes contained in each partition.

The hierarchical integration of RTOS kernel schedulers in a multi-executive environment assumes that a different instance or even a completely different RTOS kernel is used for each partition. Each partition has its own instance of a RTOS process scheduler.

A single **flat scheduler** performs partition scheduling and selects at given points in time which will be the next running partition. This is the function of the <u>AIR PMK Partition Scheduler</u>, which performs a periodic fixed cycle scheduling.

A **RTOS process scheduler** is used for process scheduling inside each partition. A given RTOS process scheduler becomes active upon the switching to the given partition. All the process scheduling operations, including clock tick processing, is restricted to the scope of the active partition. Thus, the temporal interference between partitions is minimal with this regard.

All the overheads concerning clock tick processing and process status update do arise upon partition context switching. This delay is a function of the number of clock ticks that need to be processed and of the number of processes that require a status update. However, for most of the commercial off-the-shelf RTOS kernels this operation can be optimized. At most, it will exhibit only a slight penalization of the system overall timeliness values.

The hierarchical integration of process schedulers simplifies the utilization of different RTOS kernels in each partition. No fundamental changes are needed in the RTOS native scheduler. It also allows the utilization of diversified set of process schedulers.

In conformity with the ARINC 653 standard specification, partitions use a priority-based preemptive process scheduler. However, the AIR architecture two-level hierarchical process scheduler makes simple the integration of other schedulers in a per-partition basis. Some partition may use a different kind of scheduler, such as rate monotonic, deadline monotonic, earliest deadline first or least laxity first.

Most of the commercial off-the-shelf RTOS kernels perform process scheduling according to a preemptive priority-based algorithm. The RTOS process scheduler selects for the running state the highest priority ready process, i.e. the highest priority process that has all the resources required for execution with the possible exception of the processor.

AIR WP3 Deliverable AIR Final Report

Date: 12-11-2007 Issue: 1.0

#### 3.4 AIR RTOS Integration

The integration of a given RTOS in the AIR Architecture should follow as much as possible a very modular strategy. All the specific ARINC 653 functionality should be supported by AIR specific components integrated in the design of the AIR Partition Management Kernel (PMK).

The addition (or in some cases the migration from the RTOS distribution) of the AIR Hardware Abstraction Layer (HAL) and all the corresponding functionality (management of hardware resources, such as system clock, interrupt controllers, input/output ports) is a step towards a modular integration of the RTOS Kernel.

On the other hand, only the set of services effectively required by the APEX interface needs to be included in the RTOS instance for that partition. For example, all the services related with dynamic memory allocation are usually excluded from ARINC 653 compliant designs in order to ensure bounded processing times. Thus, those services do not need to be included in any instance of the RTOS Kernel. This is true for both application and system partitions. This property is closely related with the configurability characteristics of each RTOS Kernel.

#### 3.4.1 AIR RTOS Integration: RTEMS

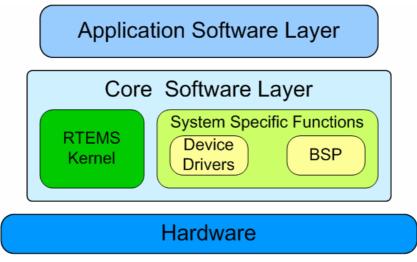

Conforming to the AIR architecture, RTEMS, the Real-Time Executive for Multiprocessor Systems offers interesting characteristics to be integrated in its design. One aspect concerns the interest around the RTEMS Kernel, given its qualification for space on-board software developments [RTEMSQUAL]. On other hand, it is able to provide the functionality required for the execution of each individual partition, in the sense it provides a comprehensive set of services such as preemptive process scheduling, process management, time management and inter-process synchronization and communication. This functionality is required not only for the fundamental temporal requirements of the ARINC 653 specification<sup>1</sup> but also for the provisioning of an extensive set of primitives that allow a mapping with the APEX interface.

Figure 3 – Typical structure of a RTEMS Application

The RTEMS architecture is illustrated in Figure 3, where the resemblance with the AIR architecture defined in Figure 2 is noticeable. The RTEMS kernel executes in a diversified set of processor platforms. Included in the system specific OS functions, the RTEMS BSP (Board Support Package) module contains the methods to address a specific hardware target, leaving the RTEMS kernel unmodified throughout several processor

<sup>&</sup>lt;sup>1</sup> Processes scheduled by a preemptive priority-based algorithm.

The contents of this document are the property of Skysoft Portugal, S.A and FCUL. All rights reserved. Company Confidential

Date: 12-11-2007 Issue: 1.0

families. In fact, the engineering of a new RTEMS BSP is not hard to achieve. Additionally, the RTEMS device driver module introduces the methods by which the hardware devices are accessed.

Furthermore, each RTEMS intrinsic component only needs to be included in a given application and/or system partition when required. For example, to preserve timeliness none of the RTEMS dynamic memory related modules (e.g. region and dual-ported managers) is included in the AIR architecture.

#### 3.5 Building the AIR Architecture and its Components

The profile represented in Figure 4 illustrates some of the engineering issues concerning the usage of canonical development tools in the production of the AIR system. For each component in the system, i.e. the AIR Partition Management Kernel (PMK), the RTOS Kernel, the APEX Interface and the application using it at each partition, the illustration in Figure 4 identifies the corresponding program (code and data), its configuration data and execution context (stack) memory spaces.

Entirely canonical build tools (e.g. cross compilers, linkers, libraries and library managers and other object level tools) may be used inside each partition. However, the use of the same RTOS Kernel in more of one partition in the scope of the multi-executive core approach implies a non-standard use of the RTOS production chain in order to cope with a common RTOS Kernel naming structure at each partition.

Figure 4 – Building an AIR System

### 3.6 Summary of AIR Architecture Attributes

The AIR architecture is built from a **multi-executive core two-level hierarchical multi-scheduler solution**. The engineering of this solution requires an effective integration of AIR components with the RTOS object libraries and with the corresponding application production chain. A limited number of RTOS components require effective integration at the source level.

The architectural attributes of the <u>multi-executive core</u> design in respect to the definition of a service interface conformant with the ARINC 653 standard, using a commercial off-the-shelf RTOS kernel such as RTEMS, is summarized in Table 4.

|                     | Multi-Executive Core Architecture Attribute |            |                 |           |                      |                                  |                     |                                 |  |  |

|---------------------|---------------------------------------------|------------|-----------------|-----------|----------------------|----------------------------------|---------------------|---------------------------------|--|--|

| RTOS<br>Integration | Versatility                                 | Modularity | Configurability | Integrity | Fault<br>Confinement | Footprint<br>Size                | Bootstrap<br>Method | Development<br>Tools            |  |  |

| partitioned         | good good good                              | boob       | aood            | good      | good                 | non                              | single-file         | canonical plus object filtering |  |  |

| partitioned         |                                             | good       | good            | optimal   | multi-file           | canonical plus<br>bootstrap tool |                     |                                 |  |  |

#### Table 4 – Summary of AIR Multi-Executive Core Architecture Attributes

The multi-executive core design allows a high integrity partitioned environment for the execution of applications which can be made highly effective in respect to: versatility, modularity, configurability and confinement of faults to a partition domain. Since multiple instances of the same RTOS are in general present, the corresponding footprint size is non-optimal.

A multi-executive core solution allows two methods for application deployment. The single-file approach is in strict conformity with canonical bootstrap methodologies, such as those provided by the GRUB tool, for both real and synthetic processor targets. However, it requires at least an object file processing step before the final linking into a <u>single application file</u> may take place.

The multi-file approach allows applications to be built into <u>different application files</u> using a completely canonical methodology. Unfortunately, it requires a non-canonical method for system bootstrapping.

| Partition Process<br>Scheduler Scheduler |              | Process       |             |            | Partition             |                          | ARINC 653       |

|------------------------------------------|--------------|---------------|-------------|------------|-----------------------|--------------------------|-----------------|

|                                          |              | RTOS Kernel   | Versatility | Modularity | Switching<br>Overhead | Temporal<br>Interference | Core Target     |

| flat                                     | hierarchical | homogeneous   | good        | good       | slight                | minimal                  | multi-executive |

| nat                                      | merarchical  | heterogeneous | good        | yuuu       | Sign                  | minina                   | multi-executive |

#### Table 5 – Summary of AIR Process Scheduler Integration Attributes

The attributes of the <u>two-level hierarchical</u> integration of partition and process schedulers in the partitioned multi-executive core architecture are summarized in Table 5.

A single <u>first-hierarchy flat scheduler</u> is used to select which will be the running partition according to a fixed cycle schedule. Inside each partition, processes are scheduled in a <u>second-hierarchy</u> level using the native process scheduler of the RTOS deployed in that partition. Both homogeneous (same RTOS in all partitions) and heterogeneous (a different RTOS in some partition) solutions are possible, exhibiting in both cases almost optimal properties in respect to timeliness attributes.

AIR WP3 Deliverable

### Faculdade de Ciências

**AIR Final Report**

#### 4 AIR Mechanisms for Spatial and Temporal Segregation

This section thoroughly describes the specific mechanisms defined in the AIR architecture to secure segregation of applications in both spatial and temporal domains.

#### 4.1 Spatial Segregation

The ARINC 653 standard imposes that the software components operating in a given partition, exception made for inter-partition communication mechanisms, cannot access the addressing space of other partitions (or at the least cannot do so with write privileges). This mechanism is known as spatial segregation and it implies the use of protection mechanisms in the access to a given addressing space. This may involve protection of both memory and input/output (I/O) addressing spaces. Partitioning of the addressing space prevents applications of interfering with each other.

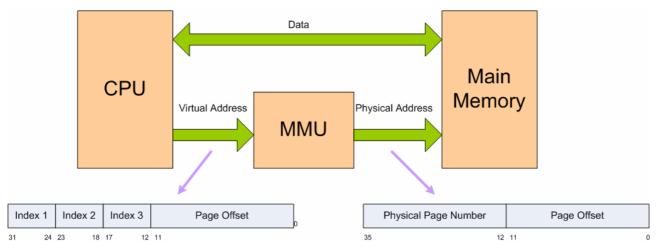

To be effective these mechanisms should be supported directly in hardware address validation mechanisms, typically implemented in Memory Management Units (MMU). In essence two kind of memory protection for an addressing space do exist.

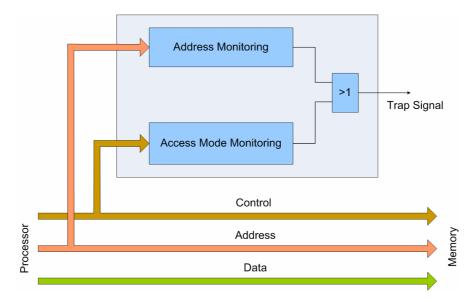

The first method simply performs the monitoring of the addressing spaces and the detection of address access violations. Given its simplicity a hardware unit performing only the monitoring of addressing spaces is sometimes simply referred as a Memory Protection Unit (MPU). The diagram in Figure 5 illustrates the fundamental mechanisms for the monitoring of addressing spaces and protection through the detection of address access (range and/or mode) violations.

Figure 5 – Memory Protection through Monitoring of Addressing Spaces

The diagram in Figure 5 specifies a continuous monitoring of the CPU address bus: the contents of the CPU address bus are compared with the valid address range, either by specifying the beginning and the ending of the allowed addressing space or through the specification of base address and address space size parameters. The two methods are roughly equivalent and do exhibit a similar complexity.

In addition to the monitoring of the addressing range, the memory access mode can also be monitored. For example, a given address space can be configured for: read access only; read and write access; read and execute; execute only; etc.

A basic memory protection scheme, employing the monitoring of the RAM addressing space, is used in the SPARC LEON2 implementation of the ATMEL AT697E memory write protection mechanisms.

Memory protection methods based on address monitoring are simple to implement and, as referred in [RUSHB1], are methods inherently less vulnerable to bit-flips caused by single-event upsets (SEU).

Furthermore, such methods can provide in general a fine-grained protection of different kinds of memory addressing spaces. In the context of the AIR architecture, memory protection based in address monitoring exhibits the following advantages:

- simplicity of implementation and management;

- possible combination with access modes classification and other protection mechanisms;

- possible fine-grained range of address protection (e.g. double word natural boundary in 32-bit processors);

- an inherent low susceptibility to bit-flips caused by single-event upsets.

On the other hand, memory protection based address monitoring methods may be too simple and therefore slightly inflexible in the support of AIR Inter-partition Communication schemes, in the sense the system designer/integrator may wish to provide different mappings for the transmit and receive ports of a given communication channel, for example.

The second method performs a translation of the valid addressing space: a given logical address is translated into a (linear) physical address, usually from a base address specified through a Memory Management Unit (MMU) descriptor. This method exhibits a complexity similar to the detection method. The address translation option provides additional flexibility in respect to the mapping of a logical address space into a physical address space. In addition, it also allows the mapping of different logical addresses in the same physical address references thus creating some sort of address alias. However, it potentially exhibits a higher vulnerability to bit-flips caused by single-event upsets.

A fault in the memory translation mechanisms should be regarded as very serious with regard to the implementation of the memory protection mechanisms required by the ARINC 653 standard specification. Given address translation may be a useful mechanism for the implementation of AIR inter-partition communication, one possible solution to increase fault coverage would be the combination of memory translation and memory detection schemes in this particular case.

The applications run in non-privileged mode and each memory access is checked (and sometimes translated) by the processor Memory Management Unit (MMU), using memory and/or I/O addressing descriptors tables. A trap signal is generated upon the detection of an unauthorized access to an addressing segment. The memory translation scheme is used in the segmentation model of the Intel IA-32 architecture.

The design of these mechanisms and its use within the scope of the ARINC 653 standard should either incorporate **fault-tolerant mechanisms** at design level or use a **combination** of memory translation and memory detection mechanisms. In addition, they should also prevent ill interactions with other advanced addressing resources such as processor internal data and instruction caches.

Other subtle processor architecture details, such as hidden MMU descriptor registers should also be taken into account in the design and/or utilization of the mechanisms enforcing spatial segregation. Furthermore, an adequate combination of hardware address checking mechanisms with software-based approaches, such as Software Fault Isolation (SFI), may provide additional dependability coverage guarantees.

The provision of spatial segregation mechanisms exhibiting a high fault coverage and conformity with the ARINC 653 standard specification are foreseen to be integrated in the operation of the AIR Partition Management Kernel (PMK). The management of such mechanisms should be included in the design of the AIR Partition Dispatcher with the implementation of some functions delegated to the low-level AIR Hardware Abstraction Layer (HAL).

## AIR WP3 Deliverable

### Faculdade de Ciências

AIR Final Report

In particular, these AIR Partition Management Kernel (PMK) modules need to provide memory and/or I/O addressing space management for the following specific functions:

- handling of hardware interrupt sources, namely the system clock tick interrupt;

- operation of AIR PMK components (Partition Scheduling and Dispatching) upon system clock tick notification;

- normal operation of a given AIR application partition;

- normal operation of the corresponding APEX interface;

- normal operation of the APEX AIR PMK interface;

- management of AIR inter-partition communication.

The functionality required for the management of such memory and/or I/O addressing spaces can be mapped into:

- a segment-based model, implementing either an address monitoring or an address translation scheme, or a combination of both;

- a page-based model, which usually uses address translation schemes.

The Intel IA-32 architecture uses both the segmentation and page-based models while the specification of the SPARC V8 architecture (ERC32, LEON2, LEON3) uses a three-level paging scheme. Both the approaches can be used for the mapping of the different AIR functional elements in the memory protection resources. For example, the AIR inter-partition communication module may use either a segmentation model or a paging-scheme to create alias in the different partitions for the same communication channel.

Within the scope of the ARINC 653 standard specification there are no provisions to spatial segregation at process-level inside each partition.

#### 4.1.1 Memory Protection Mechanisms in SPARC LEON Cores

Though the bare SPARC V8 architecture does not imposes the implementation of a given MMU, some common processor core designs may include either some simple memory protection schemes or more complex units using a memory paging mechanism compliant with the SPARC V8 specification. We address next both situations.

#### ATMEL AT697E SPARC V8 LEON2-FT Processor

This implementation of the SPARC LEON2 architecture has a 32-bit address bus that allows the addressing of external address spaces, in function of a given memory type. With respect to external RAM memory space, the corresponding attributes are summarized in Table 6.

| Memory<br>Type | Address Range           | Size  | Write<br>Protection |

|----------------|-------------------------|-------|---------------------|

| RAM            | 0x40000000 – 0x7FFFFFFF | 1 GiB | ✔ (2 units)         |

#### Table 6 – Characteristics of ATMEL AT697E RAM Address Space

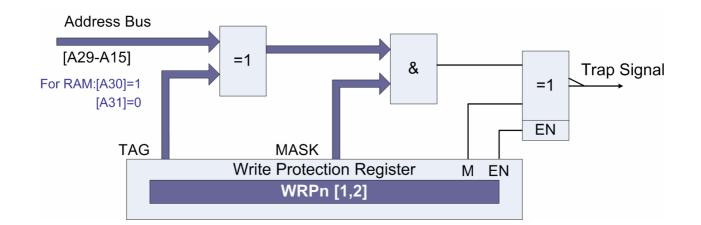

The ATMEL AT697E processor allows protection of the external RAM address space through <u>two write</u> <u>protection units</u>. These write protection units<sup>2</sup> are simple segment-oriented mechanisms for external RAM

<sup>&</sup>lt;sup>2</sup> A simple form of this mechanism is usually referred in the literature as a *fence register*.

| ))s | KYS | PORTUGAL |

|-----|-----|----------|

Date: 12-11-2007 Issue: 1.0

write protection to be performed over 32 KiB blocks<sup>3</sup>. Sets of such write protected memory segments can be located in contiguous or interleaved memory spaces.

The RAM write protection functions are configured and controlled through <u>two write protection registers</u>. Their functional details are summarized in Figure 6. The mechanism specifies the following fields:

- a **TAG address**, which defines fifteen of the most significant bits [A29-A15] of the address block/segment to be protected;

- a **MASK**, specifying which bits of the tag address should be monitored. This includes:

- a (possibly empty) set of zero bits at the least significant positions, defining the size of the memory block, which must be always a power of two multiple of 32KiB. If no such set exists, the size of the memory block is 32 KiB.

- a (possibly empty) set of zero bits at other positions but the least significant ones, defining a group of interleaved memory blocks. If no such set exists, a single (non-interleaved) memory block is defined in the address space.

- two protection modes can be specified: active within the segment or active outside the segment.

- M=0 the exterior of the segment is write protected (segment mode)

- $\circ$  M=1 write protection within the segment (block mode)

- enable/disable of the write protection features:

- EN=0 no write protection

- EN=1 write protection is active (enabled)

When the RAM write protection mode is active, if an address range violation is detected the memory write cycle is stopped and a trap (0x2B) error is generated.

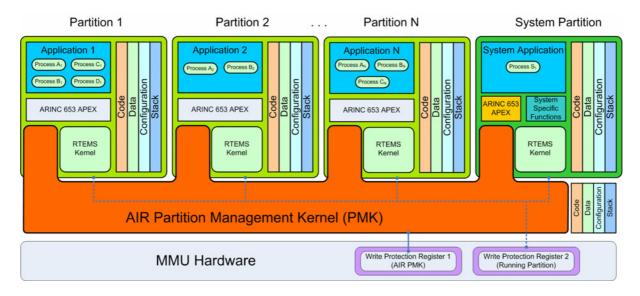

This RAM write protection function roughly corresponds to the minimum mechanisms required to support the AIR (and therefore ARINC 653) spatial segregation requirements, as illustrated in Figure 7.

| WRP bi  | t | 31  | 30   | 29 | 28                                           | 27 | 26 | 25 | 24 | 23 | 22   | 21 | 20 | 19 | 18  | 17   | 16   | 15   | 14   | 13  | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 1 | 3 | 2 | 1 | 0 |

|---------|---|-----|------|----|----------------------------------------------|----|----|----|----|----|------|----|----|----|-----|------|------|------|------|-----|----|----|----|---|---|---|---|---|---|---|---|---|---|---|

| Field   | E | EN  | Μ    |    | TAG Address                                  |    |    |    |    |    | MASK |    |    |    |     |      |      |      |      |     |    |    |    |   |   |   |   |   |   |   |   |   |   |   |

| Meaning | g | con | trol |    | fifteen of the most significant address bits |    |    |    |    |    |      |    |    | 3  | 2 K | ίB β | orot | ecte | ed b | loc | k  |    |    |   |   |   |   |   |   |   |   |   |   |   |

Figure 6 – The ATMEL AT697E SPARC LEON2 RAM Memory Protection Mechanisms

<sup>&</sup>lt;sup>3</sup> This document follows a notation in conformity with the IEC 60027-2 standard in respect to the usage of prefixes for the multiples of binary quantities.

#### Date: 12-11-2007 Issue: 1.0

For example, one of the ATMEL AT697E write protection registers may be used for the protection of the AIR Partition Management Kernel (PMK) address space (cf. Figure 7). This needs to include:

- handling of hardware interrupt sources, namely the system clock tick interrupt;

- normal operation of the AIR APEX PMK interface, through the AIR PMK Partition Management module;

- the management of AIR inter-partition communication channels.

The second write protection register may be used to enable a given running partition addressing space (cf. Figure 7). This includes:

- the application code, data and stack spaces;

- the RTOS kernel instance for the partition;

- the corresponding AIR APEX interface components.

Enabling a valid addressing space for the running partition has to be managed by the AIR PMK Partition Dispatcher and by the AIR Hardware Abstraction Layer (HAL), upon partition switching. This may also need to include the management of AIR inter-partition communications.

The mapping of partition (and of AIR PMK) addressing spaces in segments with a size multiple of 32 KiB needs also to be managed at the application production chain level, e.g. using the linker/locater address alignment features.

Figure 7 – Usage of ATMEL AT697E RAM Memory Protection Mechanisms in AIR

#### Gaisler LEON2-FT and LEON3-FT SPARC V8 Processor Cores

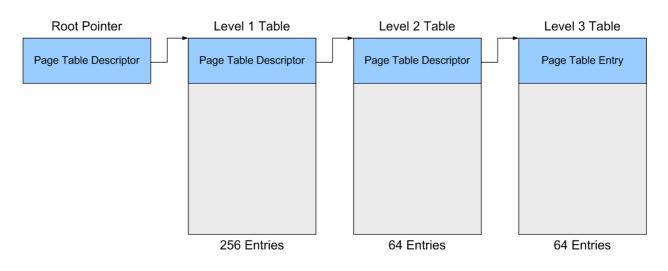

These implementations of the SPARC LEON3 architecture includes an optional component that implements the Memory Management Unit (MMU) described in the SPARC V8 specification. In essence this document specifies a three-level paging scheme for translating a 32-bit virtual page address into 36-bit physical page address. The page size is 4 KiB. The operation of this mechanism is illustrated in Figure 8.

Figure 8 – The Gaisler SPARC LEON3 SPARC V8 MMU Architecture

On the other hand, the operation of the Gaisler SPARC LEON3 MMU is illustrated in Figure 9, showing the full address translation (i.e. from virtual to physical) scheme. The mapping of AIR system protection requirements can then be summarized as follows:

- context level (root pointer) specifies the active partition reference;

- partition level (index 1) also specifies the active partition;

- entity level (index 2) specifies the AIR component in use (application, APEX interface, RTOS,...).

- object level (index 3) specifies one particular element in the AIR component (e.g. a channel in the AIR inter-partition communication module).

- method (page offset) specifies the specific function or functional element being accessed.

Date: 12-11-2007 Issue: 1.0

#### 4.1.2 Memory Protection Mechanisms in Intel IA-32 (80X86) Processors

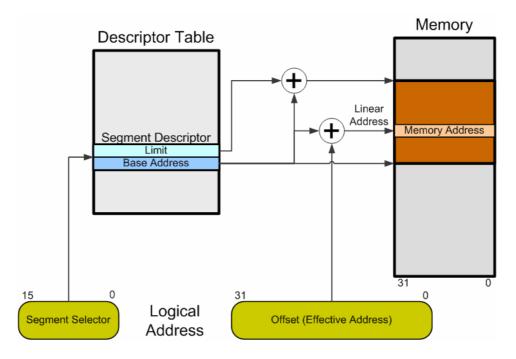

The Intel IA-32 processor architecture directly provides hardware-based segment mediation allowing address translation (and validation), through the use of the so-called segmentation mechanisms. The fundamental operation of this mechanism is illustrated in Figure 10.

Using, the IA-32 nomenclature a segment is a protected addressing space, which can be used to support ARINC 653 partitions. The memory management mechanisms provided by the IA-32 architecture are in essence a memory address translation and validation scheme. An exception (trap) is generated upon the detection of an unauthorized access to a given addressing segment.

The Intel IA-32 address translation and validation mechanism works as follows. The processor logical address can be divided in two components:

- <u>a segment selector</u>, usually stored in one of the segment registers (for example: by default, the CS register is used for code references, the DS register is used for data and the SS register is used while accessing the stack)

- an <u>offset</u>, also known as effective address, specifies the relative displacement of a given address reference with respect to the base address of the segment.

The <u>base address</u> for the segment (i.e. the physical address where the segment begins) and its <u>limit</u> (i.e. the size of the segment) are specified in a <u>descriptor</u> located in a memory space under the supervision of the memory management unit (MMU). Under normal operation (i.e. if the offset does not exceed the specified limit) the value of the offset is added to the base address to generate the linear physical address. If the offset value exceeds the segment limit an exception (trap) is generated and the memory access is not performed.

Figure 10 – The Intel IA-32 Segment-based Memory Protection Mechanisms

No particular memory alignment requirements are placed either on the AIR PMK components or on the AIR Application modules: all these components can be aligned on the Intel 80x86 32-bit natural boundaries. The usage of physical memory can be very effective. In addition, no particular limitation is placed on the usage of canonical development tools with this regard.

#### AIR WP3 Deliverable

Company: Skysoft Portugal & FCUL

## Faculdade de Ciências

AIR Final Report

Date: 12-11-2007 Issue: 1.0

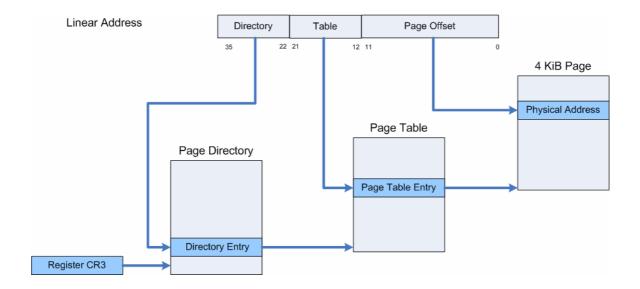

As an alternative the Intel IA-32 architecture also offers the possibility of using a two-level paging scheme, as illustrated in Figure 11. These mechanisms, thought simpler, are similar to those used in the Gaisler SPARC LEON3 architecture.

Figure 11 – The Intel IA-32 Page-based Memory Protection Mechanisms

**AIR Final Report**

Date: 12-11-2007 Issue: 1.0

#### 4.2 Temporal Segregation

Temporal segregation in the ARINC 653 standard specification enforces strict time windows for each partition. This ensures that each partition has a given execution period, even if other partitions are faulty. Partitions are scheduled on a fixed, cyclic basis. Inside the time windows of a given partition, its processes are scheduled preemptively according to their priority and state.

The AIR partition scheduler determines at each point in time what should be the running partition, based on a time table defined off-line. It determines, at partition preemption points, the next running partition: the heir partition. The AIR partition dispatcher is responsible for replacing the running partition with the heir partition.

The AIR architecture follows a multi-executive two-level hierarchical multi-scheduler approach. This means that each partition provides its own process scheduler, usually through the native priority-based preemptive scheduler of each RTOS kernel.

#### 4.2.1 Partition Scheduling

The scheduling of partitions defined by the ARINC 653 standard specification is strictly deterministic over time, that is to say, each partition has a fixed temporal window in which it has control over the computational platform. Furthermore, each partition is scheduled on a fixed, cyclic basis. The Partition Management Kernel maintains a Major Time Frame (MTF) of fixed duration, defined off-line, which is periodically repeated throughout the runtime operation [A653P1]. An example of the temporal partitioning is provided by Figure 12.

| Partition Scheduling Table |                |             |                |  |  |  |  |  |  |

|----------------------------|----------------|-------------|----------------|--|--|--|--|--|--|

| <b>Clock Ticks</b>         | Heir Partition | Clock Ticks | Heir Partition |  |  |  |  |  |  |

| 0                          | P1             | 280         | System         |  |  |  |  |  |  |

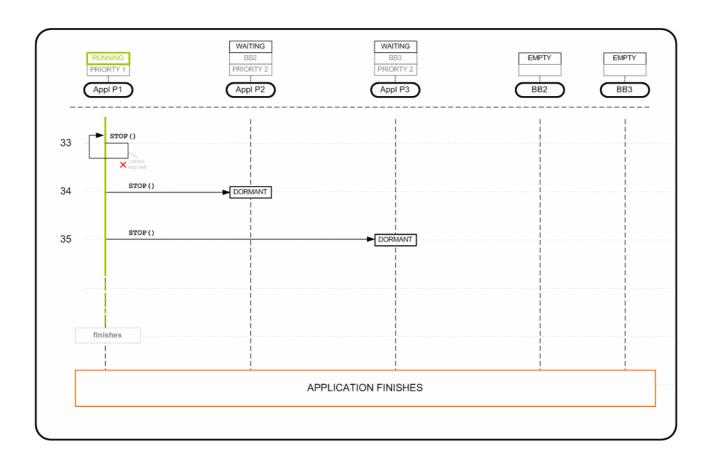

| 20                         | P2             | 300         | P1             |  |  |  |  |  |  |