UNIVERSIDADE DE LISBOA FACULDADE DE CIÊNCIAS DEPARTAMENTO DE INFORMÁTICA

## Real-Time Scheduling in Multicore Time- and Space-Partitioned Architectures

## João Pedro Gonçalves Crespo Craveiro

DOUTORAMENTO EM INFORMÁTICA ESPECIALIDADE ENGENHARIA INFORMÁTICA

2013

UNIVERSIDADE DE LISBOA FACULDADE DE CIÊNCIAS DEPARTAMENTO DE INFORMÁTICA

## Real-Time Scheduling in Multicore Time- and Space-Partitioned Architectures

## João Pedro Gonçalves Crespo Craveiro

Tese orientada pelo Prof. Doutor José Manuel de Sousa de Matos Rufino, especialmente elaborada para a obtenção do grau de DOUTOR em INFORMÁTICA, especialidade ENGENHARIA INFORMÁTICA

2013

#### This work was partially supported by

the European Space Agency Innovation (ESA) Triangle Initiative program through ESTEC Contract 21217/07/NL/CB, Project AIR-II

the European Commission Seventh Framework Programme (FP7) through project KARYON (IST-FP7-STREP-288195)

Fundação para a Ciência e a Tecnologia (FCT), with Égide/CAMPUSFRANCE through the PESSOA programme transnational cooperation project SAPIENT

Fundação para a Ciência e a Tecnologia (FCT) through multiannual funding to the LaSIGE research unit, the CMU|Portugal programme, the Individual Doctoral Grant to the author (SFRH/BD/60193/2009), and project READAPT (PTDC/EEI-SCR/3200/2012)

FCT Fundação para a Ciência e a Tecnologia

MINISTÉRIO DA EDUCAÇÃO E CIÊNCIA

UNIAO EUROPEI. Fundo Social Europe

#### Abstract

The evolution of computing systems to address size, weight and power consumption (SWaP) has led to the trend of integrating functions (otherwise provided by separate systems) as subsystems of a single system. To cope with the added complexity of developing and validating such a system, these functions are maintained and analyzed as components with clear boundaries and interfaces. In the case of real-time systems, the adopted component-based approach should maintain the timeliness properties of the function inside each individual component, regardless of the remaining components. One approach to this issue is time and space partitioning (TSP)—enforcing strict separation between components in the time and space domains. This allows heterogeneous components (different real-time requirements, criticality, developed by different teams and/or with different technologies) to safely coexist. The concepts of TSP have been adopted in the civil aviation, aerospace, and (to some extent) automotive industries. These industries are also embracing multiprocessor (or multicore) platforms, either with identical or nonidentical processors, but are not taking full advantage thereof because of a lack of support in terms of verification and certification. Furthermore, due to the use of the TSP in those domains, compatibility between TSP and multiprocessor is highly desired. This is not the present case, as the reference TSP-related specifications in the aforementioned industries show limited support to multiprocessor. In this dissertation, we defend that the active exploitation of multiple (possibly non-identical) processor cores can augment the processing capacity of the time- and space-partitioned (TSP) systems, while maintaining a compromise with size, weight and power consumption (SWaP), and open room for supporting self-adaptive behavior. To allow applying our results to a more general class of systems, we analyze TSP systems as a special case of hierarchical scheduling and adopt a compositional analysis methodology.

### Resumo

A evolução dos sistemas computacionais para endereçar questões de tamanho, peso e consumo energético conduziu à tendência de integrar funções (de outra forma fornecidas por sistemas separados) como subsistemas de um único sistema. Para lidar com a complexidade do desenvolvimento e validação de tal sistema, estas funções são mantidas e analisadas como componentes com fronteiras e interfaces bem definidos. No caso dos sistemas de tempo-real, a abordagem baseada em componentes adotada deve preservar as propriedades de pontualidade das funções dentro de cada componente, independentemente dos restantes. Uma abordagem para este problema é a compartimentação no espaço e no tempo (CET)—impor uma estrita separação entre os componentes nos domínios do tempo e do espaço. Tal permite que componentes heterogéneos (diferentes requisitos de tempo-real, criticidade, desenvolvidos por equipas diferentes e/ou com diferentes tecnologias) coexistam em segurança. Os conceitos de CET têm sido adotados nas indústrias da aviação civil, aeroespacial, e (até certo ponto) automóvel. Estas indústrias também estão a adotar plataformas multiprocessador (ou multinúcleo), tanto com processadores idênticos e não-idênticos, mas não estão a tirar partido destas por falta de suporte em termos de verificação e certificação. Além disso, devido ao uso de CET nesses domínios, a compatibilidade entre CET e multiprocessador é altamente desejada. Este não é o estado atual, dado que as especificações relacionadas com CET usadas como referência nas indústrias referidas mostram suporte limitado para multiprocessador.

Nesta tese, defendemos que tirar partido de vários núcleos (possivelmente não-idênticos) de processador pode aumentar a capacidade de processamento dos sistemas CET (mantendo um compromisso com o tamanho, peso e consumo de energia) e abrir caminho para suportar comportamentos auto-adaptativos. Para permitir a aplicação dos nossos resultados a uma classe mais geral de sistemas, analisamos os sistemas CET como um caso particular de escalonamento hierárquico e adotamos uma metodologia de análise composicional.

# Keywords

Compositional analysis Hierarchical scheduling Multiprocessor Real-time systems Time- and space-partitioned systems

## Palavras Chave

Análise composicional Escalonamento hierárquico Multiprocessador Sistemas tempo-real Sistemas compartimentados no espaço e no tempo

## Resumo Alargado

Um sistema computacional de tempo-real é aquele cujos resultados devem observar correção, não apenas lógica, mas também temporal. A relação entre a pontualidade (face a uma determinada meta temporal) com que o sistema garante o fornecimento de resultados e a sua utilidade permite a definição de diferentes classes de temporeal—classicamente, tempo-real estrito (hard) e lato (soft). Um sistema de temporeal estrito contém, pelo menos, uma tarefa de tempo-real estrito—uma tarefa cujo resultado tem de ser fornecido, sempre, dentro da sua meta temporal (caso contrário, o seu resultado não tem utilidade). Um sistema de tempo-real lato não contém qualquer tarefa de tempo-real estrito, mas contém pelo menos uma tarefa de tempo-real lato — uma tarefa que deve cumprir a sua meta temporal, mas que pode ocasionalmente falhá-la (em cujo caso a utilidade do seu resultado diminui com o tempo) (Kopetz, 1997; Verissimo & Rodrigues, 2001). A investigação sobre sistemas de tempo-real tem se focado no conjunto de algoritmos e técnicas de análise que permitam aos desenvolvedores de um sistema saberem, antes de colocarem este em produção, se é possível garantir o cumprimento dos seus requisitos de tempo-real (estrito ou lato).

Os sistemas computacionais têm vindo a evoluir para acomodar determinadas necessidades, incluindo preocupações com as suas dimensões, peso e consumo energético (e, consequentemente, custo). Esta evolução conduziu a uma tendência de integrar sistemas separados como subsistemas de um único sistema computacional, mais complexo. Esta integração pode incluir a coexistência de subsistemas com diferentes classes de requisitos de tempo-real (estrito e lato), ou subsistemas desenvolvidos por diferentes equipas e/ou com diferentes níveis de certificação. A complexidade acrescida do sistema aplica-se às atividades dos seus desenvolvimento, testes, validação e manutenção. A abordagem de desenhar estes sistemas em torno da noção de *componente*, permitindo assim uma *análise baseada em componentes*, traz vários benefícios, alguns dos quais específicos aos sistemas de tempo-real (Lipari *et al.*, 2005; Lorente *et al.*, 2006). No caso da coexistência de diferentes classes de tempo-real, as vantagens de manter as partes do sistema com requisitos de tempo-real estrito logicamente separadas das de tempo-real lato estão relacionadas com dois aspetos. Por um lado, a análise separada permite cumprir os requisitos de

tempo-real estrito dos respetivos componentes sem impor pessimismo desnecessário à análise dos componentes de tempo-real lato. Por outro lado, com considerações de desenho apropriadas, as falhas de pontualidade permitidas aos componentes de tempo-real lato não invalidam a pontualidade dos componentes de tempo-real estrito (Abeni & Buttazzo, 1998). Uma abordagem de desenho para este efeito é a *compartimentação no tempo e no espaço* (CET), na qual cada componente constitui uma unidade de separação lógica e contenção (*partição*).

Um exemplo proeminente da aplicação da abordagem CET ao desenho Contexto. de sistemas computacionais é a adoção das especificações ARINC 651 (AEEC, 1991) e ARINC 653 (AEEC, 1997) no domínio da aviação civil. A abordagem tradicional até então, denominada aviónica federada, faz uso de funções distribuídas alojadas em componentes dedicados. Tendo cada função os seus recursos computacionais dedicados (e, por vezes, fisicamente separados), que não podem ser reatribuídos em tempo de execução, o potencial para uma utilização ineficiente dos recursos surge como um contraponto à inerente independência de falhas (Audsley & Wellings, 1996; Sánchez-Puebla & Carretero, 2003). Por outro lado as arquiteturas de Aviónica Modular Integrada (AEEC, 1991) empregam um ambiente compartimentado de alta integridade que aloja múltiplas funções de aviónica com diferentes níveis de criticidade numa plataforma computacional partilhada. A identificação de requisitos semelhantes ao da indústria aeronáutica levou a indústria aeroespacial a exprimir interesse em aplicar os conceitos de compartimentação no tempo e no espaço da Aviónica Modular Integrada ao *software* a bordo de missões espaciais. Este interesse surgiu quer do lado de parceiros norte-americanos como a NASA (Black & Fletcher, 2006; Fletcher, 2009; Hodson & Ng, 2007; Rushby, 1999) quer de parceiros europeus como a Agência Especial Europeia (ESA), a agência espacial francesa (CNES), e as empresas Thales Alenia Space e EADS Astrium (Planche, 2008; Plancke & David, 2003; Windsor & Hjortnaes, 2009). Além destas, também a indústria automóvel está ativa na adopção de desenhos de sistema CET. A iniciativa AUTOSAR (AUTomotive Open System ARchitecture) para a especificação de uma arquitetura padrão de software para a indústria automóvel, na especificação dos requisitos de alto nível para um sistema operativo, inclui provisões que correspondem, até certo ponto, às noções de compartimentação no tempo e no espaço.

**Motivação.** O emprego de múltiplos núcleos de processador surgiu como resposta à necessidade de estagnação do aumento da velocidade de relógio dos processadores (dado o consequente aumento de dissipação de energia ter atingido os limites práticos dos sistemas de arrefecimento). Um processador que aloja múltiplos nícleos no mesmo chip é denominado um processador multinúcleo (ou *multicore*). Os núcleos de processador podem ter espaços de endereçamento privados ou partilhados, sendo o último caso o tipicamente empregue em processadores multinúcleo (Patterson & Hennessy, 2009).

Os processadores multinúcleo estão a ganhar terreno no domínio dos sistemas embebidos, nomeadamente sistemas de segurança crítica e com requisitos de temporeal estrito—como os encontrados nas indústrias aeronáutica e aeroespacial. As últimas versões dos processadores SPARC LEON, amplamente usados pela Agência Espacial Europeia, suportam configurações multinúcleo (com núcleos idênticos ou não-idênticos) (Andersson *et al.*, 2010). Contudo, tais capacidades são rotineiramente desativadas e consequentemente não exploradas, dada a falta de suporte às mesmas em termos de verificação e certificação (Anderson *et al.*, 2009). Dado o uso e interesse prevalentes das indústrias aeronáutica, aeroespacial e automóvel no que toca aos conceitos de compartimentação no tempo e no espaço, a compatibilidade entre sistemas CET e plataformas com múltiplos núcleos de processador, quer idênticos quer não, é assim altamente desejada; esse não é, porém, o cenário atual.

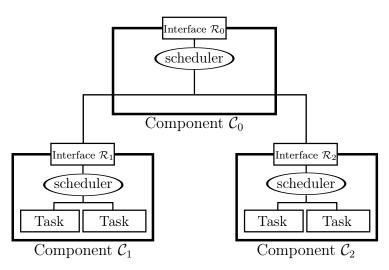

Metodologia. Como foi referido, os sistemas CET empregam tipicamente um escalonamento hierárquico de dois níveis. Analisar os sistemas CET como um caso particular de escalonamento hierárquico permite reutilizar os resultados obtidos num conjunto mais geral de sistemas e aplicações. O escalonamento hierárquico é um tópico atual na comunidade de investigação em escalonamento de tempo-real, na tentativa de resolver problemas em cenários reais de aplicação de *software* embedido (Abeni & Buttazzo, 1998; Lackorzyński *et al.*, 2012; Mok & Feng, 2002; Santos *et al.*, 2011; Xi *et al.*, 2011). A possibilidade de desenvolvimento independente e de hierarquias com mais de dois níveis constituem motivação e vantagem para a aplicação de *análise composicional*. Composicionalidade é a propriedade de um sistema complexo que pode ser analisado avaliando algumas propriedades dos seus componentes (sem saber a estrutura ou hierarquia interna destes) e a forma como são conjugados (Easwaran *et al.*, 2006; Hausmans *et al.*, 2012). Neste sentido, um componente compreende uma aplicação a executar (que pode ser constituída por tarefas e/ou subcomponentes), um escalonador, e a especificação da disponibilidade de recursos — nomeadamente, o(s) processador(es). Este componente pode ser abstraído utilizando uma *interface* que, por um lado, esconde as suas caraterísticas internas perante o restante sistema e, por outro lado, esconde perante o próprio componente as caraterísticas extrínsecas da disponibilidade de recursos. A análise composicional compreende três pontos principais (Shin & Lee, 2007):

- 1. Análise de escalonabilidade ao nível local Analisar a escalonabilidade da aplicação de um componente com o escalonador e a disponibilidade de recurso especificados.

- 2. *Abstração do componente* Derivar a interface do componente a partir das suas caraterísticas internas.

- 3. *Composição de interfaces* Derivar, a partir de um conjunto de interfaces que exprimem os requisitos individuais de disponibilidade de recurso de componentes, o requisito cumulativo de disponibilidade de recurso para escalonar estes componentes de acordo com uma dada estratégia de escalonamento.

**Tese e contribuições.** Neste tese defendemos que tirar partido de múltiplos núcleos de processador (potencialmente não-idênticos) pode (i) aumentar a capacidade de processamento dos sistemas compartimentados no tempo e no espaço, mantendo um compromisso com as dimensões, peso e consumo energético do sistema, e (ii) abrir caminho ao suporte a comportamentos auto-adaptativos para lidar com mudanças imprevistas nas condições operacionais e ambientais. No âmbito desta tese, são apresentadas as contribuições que se enumeram e descrevem de seguida.

Arquitetura e modelo de sistema. Propomos uma arquitetura de referência melhorada para sistemas CET com suporte a multiprocessador. Esta arquitetura constitui uma aproximação mais flexível ao multiprocessador do que aquela preconizada no estado da prática (nomeadamente, ARINC 653 e AUTOSAR). A nossa proposta permite paralelismo entre partições, paralelismo dentro das partições, e comportamento auto-adaptativo. Análise composicional em multiprocessadores uniformes. Propomos o primeiro modelo para interfaces de componentes que permite a definição de hierarquias composicionais em multiprocessadores uniformes (aqueles cujos processadores podem ser não-idênticos, mas apenas em termos de velocidade). Esta contribuição permite a análise formal de sistemas CET com paralelismo entre e/ou dentro das partições em multiprocessadores potencialmente não-identicos. A nossa contribuição abrange os três aspetos da análise composicional de estruturas de escalonamento hierárquico análise de escalonabilidade ao nível local, abstração do componente, e composição de interfaces — aplicando e estendendo resultados anteriores de outros autores (Baruah & Goossens, 2008; Easwaran *et al.*, 2009b). Os diferentes aspetos desta contribuição são validados analiticamente e demonstrados experimentalmente com recurso a simulação.

Análise, geração e simulação de escalonamento. Apresentamos o desenho e concretização do hsSim, uma ferramenta orientada a objetos para simulação e análise de escalonamento e geração de tabelas estáticas de escalonamento. O hsSim foi cuidadosamente desenhado com atenção aos padrões de desenho de software aplicáveis, com objetivos de modularidade, extensibilidade e interoperabilidade. Esta abordagem cuidadosa não é habitualmente aplicada na concretização de utilitários de suporte a experiências académicas, sendo esta a principal razão pela qual desenhamos uma ferramenta de raíz em vez de modificarmos uma ferramenta existente. Este facto não preclude porém que algumas das contribuições apresentadas sejam importadas para o código de outras ferramentas, como o Cheddar—que apresenta já bastante maturidade no que respeita à análise e simulação de escalonamento nãohierárquico. Concretizamos o suporte a algoritmos de escalonamento tradicionais, e ainda incorporamos as nossas contribuições no âmbito da análise composicional (teste de escalonabilidade, abstração de componentes, e algoritmo de escalonamento de componentes).

Resultados preliminares sobre auto-adaptação em sistemas CET. Reportamos as experiências levadas a cabo, com um protótipo de sistema CET e através de simulação, para endereçar a segunda parte da tese defendida.

**Conclusão e trabalho futuro** Nesta tese, abordámos o problema do escalonamento tempo-real em sistemas compartimentados no tempo e no espaço assentes sobre processadores multinúcleo. Acrescentámos ao estado da arte a primeira aproximação à análise composicional sobre multiprocessadores não-idênticos; os resultados formais que desenvolvemos analiticamente são corroborados pelos testes que efetuámos com conjuntos de tarefas gerados aleatoriamente, e são consentâneos com os resultados encontrados na literatura para plataformas multiprocessador dedicadas. Provámos analiticamente que o algoritmo de escalonamento gEDF não assegura a composicionalidade na presença de multiprocessadores não-idênticos; para este efeito, crucial quando se consideram as vantagens de desenvolvimento e verificação independentes trazidas por abordagens composicionais, propusémos um novo algoritmo de escalonamento, o umprEDF. Apresentámos também o desenho e desenvolvimento do hsSim, uma ferramenta orientada a objetos para análise, simulação e geração de tabelas de escalonamento; o hsSim será disponibilizado como ferramenta de código aberto para usufruto da comunidade de investigação em escalonamento tempo-real, e é uma prova de conceito para a inclusão de suporte a escalonamento hierárquico numa ferramenta mais madura. Usámos o hsSim para mostrar em acção os métodos formais que apresentámos.

Panorama de aplicabilidade. O modelo de sistema utilizado contém assunções relacionadas com o impacto temporal de fenómenos relacionados com o hardware (preempção e migração de tarefas, contenção no barramento, memória cache). Esta assunção é comum na investigação em escalonamento tempo-real, e não é totalmente díspar da realidade (Jalle *et al.*, 2013; Jean *et al.*, 2012); iremos porém, no futuro, olhar com mais detalhe para este impacto temporal.

Ao longo dos anos, houve vários projetos de investigação, financiados por entidades europeias, a empregar abordagens baseadas em componentes e/ou compartimentação no tempo e no espaço para atingir hibridização arquitetual ou lidar com sistemas de criticidade mista (exemplos: ACTORS, RECOMP, KARYON). Em alguns destes projetos, essencialmente contemporâneos com o trabalho desta tese, os processadores multinúcleo são abordados até certo ponto. O trabalho apresentado nesta tese é aplicável às arquiteturas consideradas em ou resultantes destes projetos, endereçando até aspetos deixados em aberto no final dos mesmos. Em particular, os nossos resultados transpõem a fasquia destes projetos no que respeita ao paralelismo entre componentes e ao uso de processadores SPARC LEON permitem configurações com núcleos de processador não-idênticos, mas a falta de suporte de sistema operativo tem desencorajado o seu aproveitamento.

Além do inicialmente estabelecido foco em domínio de aplicação críticos, os nossos resultados também contribuem para a verificação formal de sistemas baseados emc omponentes assentes multiprocessadores não-idênticos como o Cell e o big.LITTLE. Embora estes não sejam tipicamente empregues em domínios críticos, aplicar uma abordagem baseada em componentes ao desenvolvimento de software complexo para executar sobre os mesmos permite reduzir a complexidade e custo deste processo, enquanto se assegura que os componentes individuais tem garantias mínimas de qualidade de serviço. Tal será particularmente verdade à medida que o suporte de sistema operativo ao escalonamento hierárquico aumenta (Abdullah *et al.*, 2013; Bini *et al.*, 2011b).

*Trabalho futuro*. As vias de trabalho futuro relacionado com a presente tese que identificamos desde já incluem (i) suporte de hardware e assunções do modelo de sistema; (ii) algoritmos de escalonamento; (iii) análise composicional com garantias temporais variadas, como sejam tempo-real lato e escalonamento de criticidade mista; e (iv) reconfiguração e tolerâncias a faltas proativa.

### Acknowledgments

Although individually authored, this dissertation owes its completion to the support of quite some people. I now take the opportunity to thank them.

To my advisor José Rufino, for his full scientific, institutional and personal support. I particularly praise the attention to detail with which he scrutinized the papers we cowrote (and the drafts of this dissertation), the concern he puts in providing adequate and fair conditions for his students to carry on their work, and how he strives to give his PhD students the proper training for independent research by assigning complementary responsibilities (such as reviewing papers, and actively participating in the elaboration of project funding proposals).

To FCUL Professors André Falcão, Isabel Nunes, Luís Correia, Mário Calha, Pedro M. Ferreira and Vasco T. Vasconcelos, and to IST Professor Leonel Sousa, for the insightful comments I received at the different stages of evaluation of my work.

To the SAPIENT team at Lab-STICC (Université de Bretagne Occidentale, Brest, France), especially Laurent Lemarchand, Vincent Gaudel, and Frank Singhoff. The collaboration and idea exchanges within the SAPIENT project had a great influence in the way some parts of this work were conducted.

To LaSIGE and the Department of Informatics, for enabling such a lively and stimulating environment for learning, researching and teaching. To the Navigators group in general, and more specifically to the TADS research line leaders Paulo Verissimo and António Casimiro and to the "Toutiçanos" with whom I most closely collaborated: Jeferson Souza, Joaquim Rosa, Kleomar Almeida, Pedro Nóbrega da Costa, Ricardo Pinto, Rui Pedro Caldeira and Rui Silveira.

For the less work-oriented companionship, to my regular LaSIGE office and lunch mates Luís Duarte, Nádia Fernandes, Tiago Gonçalves, and — finally and specially — José Baptista Coelho. More than a colleague, José has been true friend for all occasions, enabling me to behave more like a human being than I was used to.

To my mother Mafalda, my sister Joana and my "sister" Sophie, for having been always, since way back in time, a permanent source of comfort and support.

Last but not least, to Catarina, my love. For having endured my periods of absence, unavailability, frustration, impatience and mood swings, and for countering them with copious amounts of love, dedication, understanding and good moments, you definitely deserve the dedication of this dissertation.

> João Pedro Gonçalves Crespo Craveiro Lisbon, August 2013

Para a minha querida Catarina. Para o Nós.

"Vogons!" snapped Ford, "we're under attack!"

Arthur gibbered.

"Well what are you doing? Let's get out of here!"

"Can't. Computer's jammed. [...] It says all its circuits are occupied." [...]

"Tell me ... did the computer say what was occupying it? I just ask out of interest ..."

[...] "I think a short while ago it was trying to work out how to ... make me some tea."

"That's right guys," the computer sang out suddenly, "just coping with that problem right now, and wow, it's a biggy. Be with you in a while." It lapsed back into a silence that was only matched for sheer intensity by the silence of the three people staring at Arthur Dent.

As if to relieve the tension, the Vogons chose that moment to start firing.

— DOUGLAS ADAMS (1980). The Restaurant at the End of the Universe. Pan Books.

# Contents

| Li               | st of  | igures                                                                                                                       | V |

|------------------|--------|------------------------------------------------------------------------------------------------------------------------------|---|

| Li               | st of  | ables vi                                                                                                                     | i |

| Li               | st of  | heorems i                                                                                                                    | ĸ |

| Li               | st of  | cronyms x                                                                                                                    | i |

| Li               | st of  | ymbols xii                                                                                                                   | i |

| $\mathbf{P}_{1}$ | ublica | ons x                                                                                                                        | V |

| 1                | Intr   | luction                                                                                                                      | 1 |

|                  | 1.1    | ontext                                                                                                                       | 2 |

|                  |        | 1.1 Civil aviation                                                                                                           | 2 |

|                  |        | 1.2 Aerospace                                                                                                                | 5 |

|                  |        | 1.3 Automotive industry                                                                                                      | 6 |

|                  | 1.2    |                                                                                                                              | 7 |

|                  | 1.3    | hesis statement                                                                                                              | 8 |

|                  | 1.4    | fethodology                                                                                                                  | 9 |

|                  | 1.5    | $\mathbb{C}$ ontributions                                                                                                    | C |

|                  | 1.6    | Ocument outline                                                                                                              | 2 |

| <b>2</b>         | Bac    | round and Related Work 1                                                                                                     | 3 |

|                  | 2.1    | eal-time scheduling background                                                                                               | 3 |

|                  |        | 1.1 Task models $\ldots \ldots 1$ | 4 |

|                  |        | 1.2 Platform models $\ldots \ldots 1$    | 7 |

#### CONTENTS

|   |     | 2.1.3    | Scheduling algorithm classification 18                                                                                                          | ; |

|---|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|---|

|   |     | 2.1.4    | Schedulability analysis notions                                                                                                                 | ) |

|   | 2.2 | Hard :   | real-time scheduling on dedicated platforms $\ldots \ldots \ldots \ldots 20$                                                                    | ) |

|   |     | 2.2.1    | Scheduling on uniprocessor platforms                                                                                                            | ) |

|   |     | 2.2.2    | Partitioned scheduling on identical multiprocessors 22                                                                                          | ) |

|   |     | 2.2.3    | Global scheduling on identical multiprocessors                                                                                                  | F |

|   |     | 2.2.4    | Global scheduling on uniform multiprocessors                                                                                                    | 3 |

|   | 2.3 | Sched    | uling approaches for mixed systems                                                                                                              | ) |

|   |     | 2.3.1    | Resource reservation frameworks                                                                                                                 | ) |

|   |     | 2.3.2    | Hierarchical scheduling frameworks (HSF)                                                                                                        | 2 |

|   | 2.4 | Comp     | ositional analysis $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 35$                                                   | ) |

|   |     | 2.4.1    | Common definitions                                                                                                                              | 7 |

|   |     | 2.4.2    | Uniprocessor                                                                                                                                    | 3 |

|   |     | 2.4.3    | Identical multiprocessor                                                                                                                        | 2 |

|   | 2.5 | Techn    | ological support to TSP                                                                                                                         | 3 |

|   |     | 2.5.1    | Operating system support                                                                                                                        | 3 |

|   |     | 2.5.2    | Scheduling analysis and simulation tools                                                                                                        | 2 |

|   | 2.6 | Summ     | nary                                                                                                                                            | L |

| ~ |     | <b>.</b> |                                                                                                                                                 |   |

| 3 |     |          | ure and Model for Multiprocessor Time- and Space-                                                                                               | - |

|   |     |          | ed Systems 57                                                                                                                                   |   |

|   | 3.1 |          | 57                                                                                                                                              |   |

|   |     | 3.1.1    | Architecture components                                                                                                                         |   |

|   | 2.0 | 3.1.2    | Achieving time partitioning $\dots \dots \dots$ |   |

|   | 3.2 |          | tion for multiprocessor $\dots \dots \dots$     |   |

|   |     | 3.2.1    | Interpartition parallelism                                                                                                                      |   |

|   |     | 3.2.2    | Intrapartition parallelism                                                                                                                      |   |

|   |     | 3.2.3    | Enhanced spatial partitioning                                                                                                                   |   |

|   |     | 3.2.4    | Self-adaptive fault tolerance                                                                                                                   |   |

|   | 3.3 |          | ystem model                                                                                                                                     |   |

|   |     | 3.3.1    | Platform model                                                                                                                                  |   |

|   |     | 3.3.2    | Component model                                                                                                                                 |   |

|   |     | 3.3.3    | Global-level scheduling                                                                                                                         | 5 |

#### CONTENTS

|          | 3.4 | Summ   | nary                                                                              | 68        |

|----------|-----|--------|-----------------------------------------------------------------------------------|-----------|

| 4        | Cor | nposit | ional Analysis on (Non-)Identical Uniform                                         |           |

|          |     |        | cessors                                                                           | <b>71</b> |

|          | 4.1 | Resou  | rce model                                                                         | 71        |

|          |     | 4.1.1  | Supply bound function                                                             | 73        |

|          |     | 4.1.2  | Linear lower bound on the supply bound function                                   | 75        |

|          | 4.2 | Local- | level schedulability analysis                                                     | 76        |

|          |     | 4.2.1  | Interference interval                                                             | 77        |

|          |     | 4.2.2  | Component demand                                                                  | 79        |

|          |     | 4.2.3  | Sufficient local-level schedulability test                                        | 82        |

|          | 4.3 | Comp   | onent abstraction                                                                 | 84        |

|          |     | 4.3.1  | Minimum resource interface                                                        | 85        |

|          |     | 4.3.2  | Uniform vs. identical multiprocessor platform                                     | 85        |

|          |     | 4.3.3  | Number of processors                                                              | 87        |

|          |     | 4.3.4  | Simulation experiments                                                            | 88        |

|          | 4.4 | Interc | omponent scheduling                                                               | 94        |

|          |     | 4.4.1  | Transforming components to interface tasks                                        | 94        |

|          |     | 4.4.2  | Compositionality with gEDF intercomponent scheduling $\ldots$                     | 99        |

|          |     | 4.4.3  | The $umprEDF$ algorithm for intercomponent scheduling $\ . \ . \ .$               | 101       |

|          |     | 4.4.4  | Interface composition                                                             | 102       |

|          | 4.5 | Summ   | nary                                                                              | 104       |

| <b>5</b> | Sch | edulin | g Analysis, Generation and Simulation Tool                                        | 107       |

|          | 5.1 | Objec  | t-oriented analysis and design                                                    | 107       |

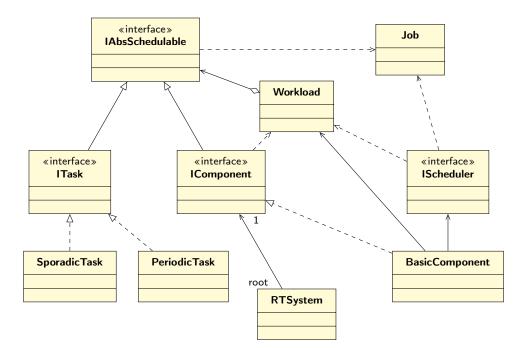

|          |     | 5.1.1  | Domain analysis                                                                   | 108       |

|          |     | 5.1.2  | $n$ -level hierarchy: the Composite pattern $\ldots$                              | 108       |

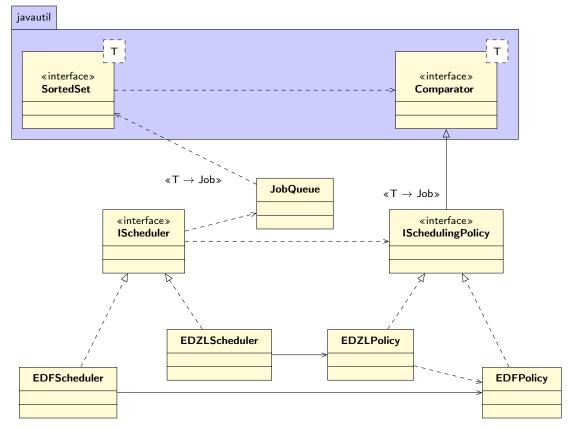

|          |     | 5.1.3  | Scheduling algorithm encapsulation: the Strategy pattern                          | 110       |

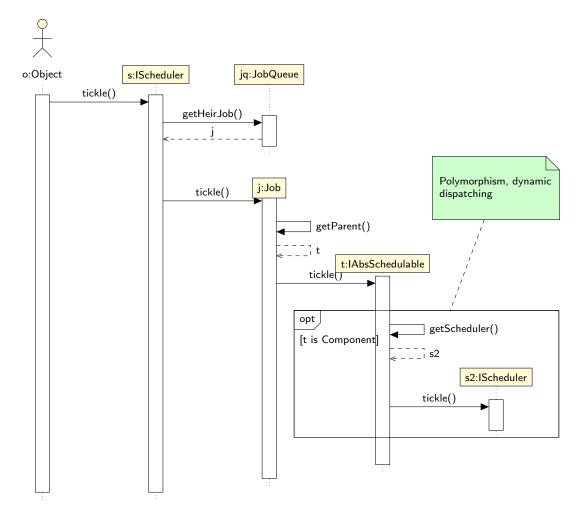

|          |     | 5.1.4  | $n$ -level hierarchy and polymorphism $\ldots \ldots \ldots \ldots \ldots \ldots$ | 111       |

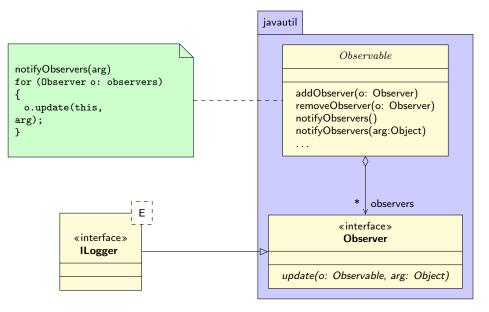

|          |     | 5.1.5  | Decoupling the simulation from the simulated domain using                         |           |

|          |     |        | the Observer and Visitor patterns                                                 | 113       |

|          |     | 5.1.6  | Multiprocessor schedulers                                                         | 115       |

|          |     | 5.1.7  | Interfaces aiding scheduling analysis                                             | 116       |

|          |     | 5.1.8  | Compositional analysis with the Decorator pattern                                 | 117       |

#### CONTENTS

|    | 5.2    | Implen  | nentation                                                                                                  | 118 |

|----|--------|---------|------------------------------------------------------------------------------------------------------------|-----|

|    |        | 5.2.1   | Extensions                                                                                                 | 118 |

|    | 5.3    | Examp   | ble use case                                                                                               | 121 |

|    |        | 5.3.1   | Scheduling analysis                                                                                        | 121 |

|    |        | 5.3.2   | Scheduling simulation and visualization                                                                    | 121 |

|    |        | 5.3.3   | Schedule generation                                                                                        | 125 |

|    | 5.4    | Summa   | ary                                                                                                        | 125 |

| 6  | Tow    | ards S  | elf-Adaptation in Time- and Space-                                                                         |     |

|    | Part   | itione  | d Systems                                                                                                  | 129 |

|    | 6.1    | Monito  | pring and adaptation mechanisms                                                                            | 129 |

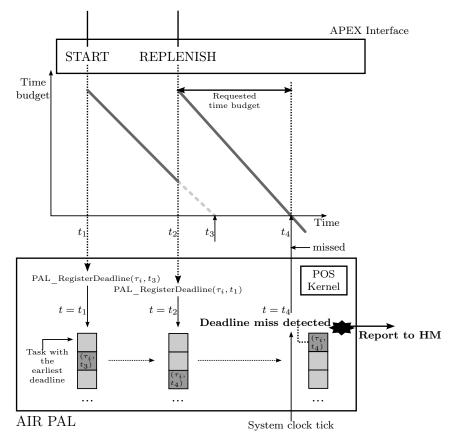

|    |        | 6.1.1   | Task deadline violation monitoring $\ldots \ldots \ldots \ldots \ldots \ldots$                             | 130 |

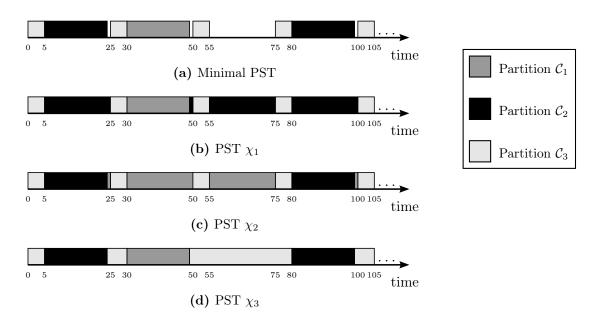

|    |        | 6.1.2   | Mode-based schedules $\ldots \ldots \ldots$ | 133 |

|    |        | 6.1.3   | Prototype implementation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                  | 135 |

|    |        | 6.1.4   | Evaluation                                                                                                 | 136 |

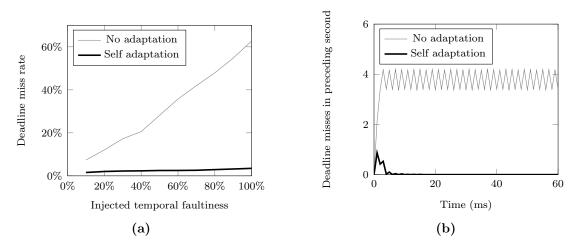

|    | 6.2    | Self-ad | aptation upon temporal faults                                                                              | 138 |

|    |        | 6.2.1   | Evaluation                                                                                                 | 139 |

|    | 6.3    | Improv  | vements discussion                                                                                         | 142 |

|    |        | 6.3.1   | Multiprocessor                                                                                             | 143 |

|    |        | 6.3.2   | Reconfiguration                                                                                            | 143 |

|    |        | 6.3.3   | Proactivity                                                                                                | 144 |

|    | 6.4    | Summa   | ary                                                                                                        | 144 |

| 7  | Con    | clusior | n and Future Work                                                                                          | 145 |

|    | 7.1    | Applic  | ability perspective                                                                                        | 146 |

|    | 7.2    | Future  | work                                                                                                       | 148 |

|    |        | 7.2.1   | Hardware support and system model assumptions $\ldots \ldots \ldots$                                       | 149 |

|    |        | 7.2.2   | Scheduling algorithms                                                                                      | 149 |

|    |        | 7.2.3   | Compositional analysis                                                                                     | 150 |

|    |        | 7.2.4   | Reconfiguration and proactivity                                                                            | 151 |

| Re | eferer | ices    | :                                                                                                          | 153 |

# List of Figures

| 1.1 | Basic architecture of an IMA computing module                                                               | 3  |

|-----|-------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Standard ARINC 653 architecture                                                                             | 4  |

| 2.1 | Execution pattern considered in Baker (2003)'s proof and thereon                                            |    |

|     | inspired works.                                                                                             | 26 |

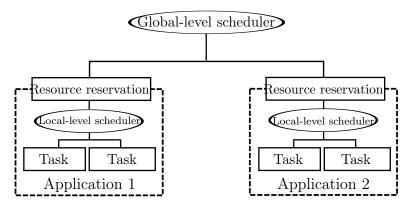

| 2.2 | Resource reservation framework                                                                              | 30 |

| 2.3 | Hierarchical scheduling framework                                                                           | 32 |

| 2.4 | Compositional scheduling framework                                                                          | 36 |

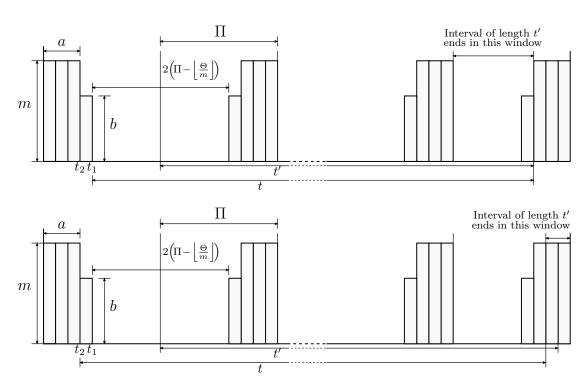

| 2.5 | Minimum supply schedule for an MPR interface $\mu = (\Pi, \Theta, m)$                                       | 42 |

| 3.1 | Architecture overview                                                                                       | 58 |

| 3.2 | Two-level scheduling scheme                                                                                 | 59 |

| 3.3 | Example comparison between a multiprocessor system implemented                                              |    |

|     | as interconnected uniprocessor TSP nodes, and a multicore (or shared- $% \mathcal{A}$                       |    |

|     | memory multiprocessor) TSP system implemented with our proposal                                             |    |

|     | of an evolved architecture $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 61 |

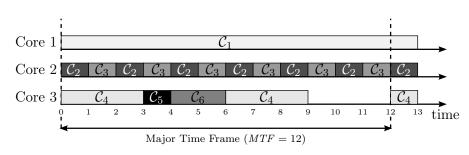

| 3.4 | Interpartition parallelism example timeline                                                                 | 63 |

| 3.5 | $Example \ timeline \ with \ a \ combination \ of \ both \ inter- \ and \ intrapartition$                   |    |

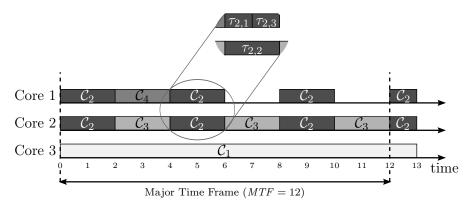

|     | parallelism                                                                                                 | 64 |

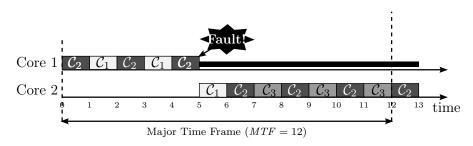

| 3.6 | Fault tolerance example timeline                                                                            | 65 |

| 3.7 | Example timeline showing a combination of fault tolerance with inter-                                       |    |

|     | and intrapartition parallelism                                                                              | 65 |

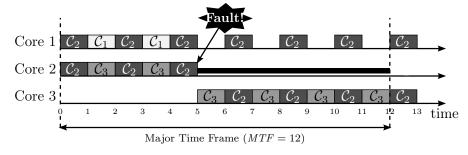

| 3.8 | System model                                                                                                | 66 |

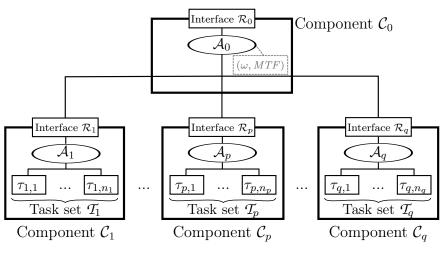

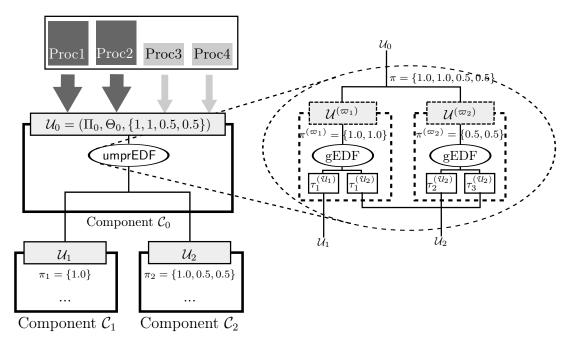

| 4.1 | Compositional scheduling framework with the UMPR                                                            | 72 |

#### LIST OF FIGURES

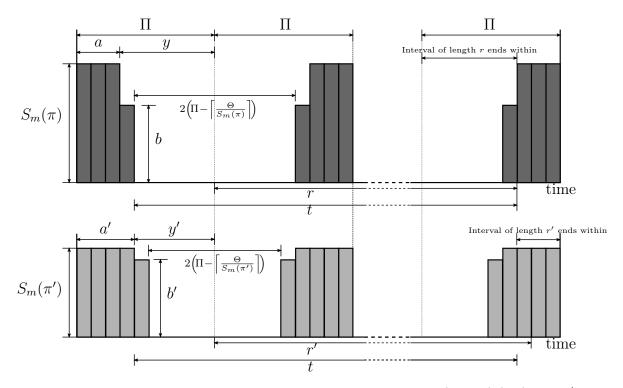

| 4.2  | Minimum supply schedule for two UMPR interfaces: $\mathcal{U} = (\Pi, \Theta, \pi)$                                                                                                        |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | and $\mathcal{U}' = (\Pi, \Theta, \pi')$ , where $S_m(\pi) > S_m(\pi')$ (both with <i>m</i> processors) 74                                                                                 |

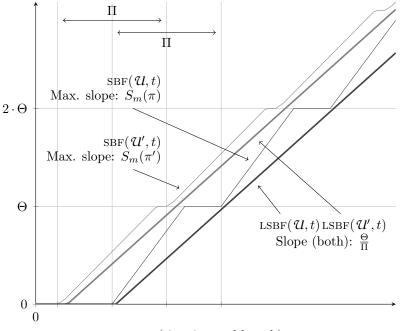

| 4.3  | Plot of SBF and LSBF for $\mathcal{U}$ and $\mathcal{U}'$                                                                                                                                  |

| 4.4  | Considered execution pattern                                                                                                                                                               |

| 4.5  | Comparison between minimal bandwidth for UMPRs based on iden-                                                                                                                              |

|      | tical and non-identical uniform multiprocessors                                                                                                                                            |

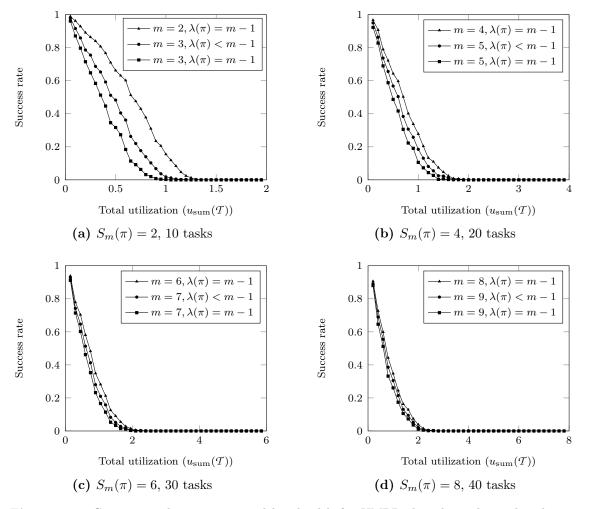

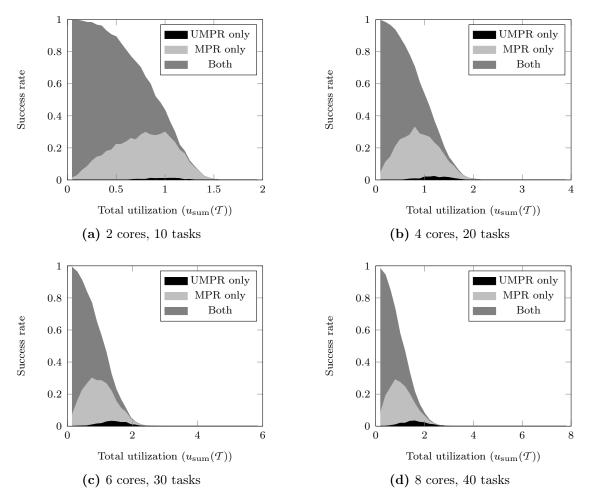

| 4.6  | Success rates for MPR and UMPR interfaces with identical multipro-                                                                                                                         |

|      | cessor platforms                                                                                                                                                                           |

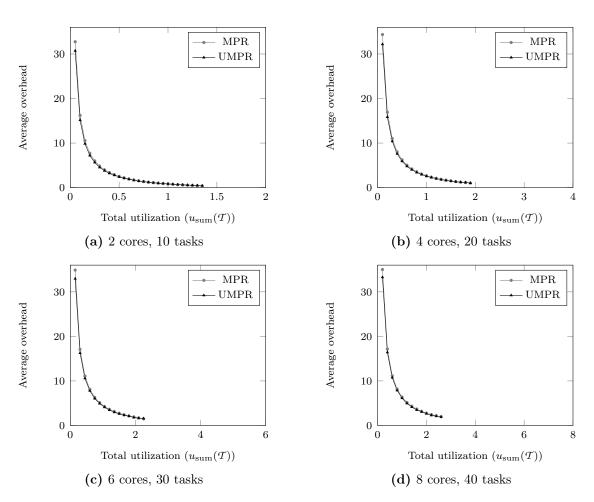

| 4.7  | Average overhead for MPR and UMPR interfaces with identical mul-                                                                                                                           |

|      | tiprocessor platforms                                                                                                                                                                      |

| 4.8  | Formalization of umprEDF with pseudocomponents                                                                                                                                             |

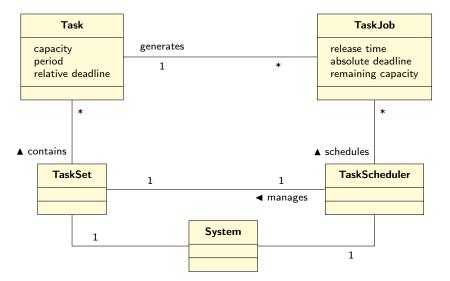

| 5.1  | Traditional 1-level system domain model                                                                                                                                                    |

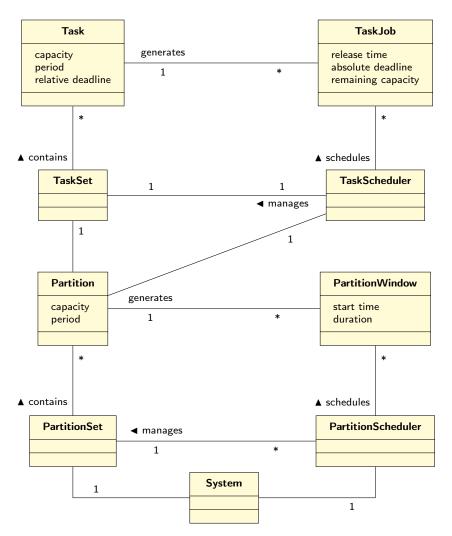

| 5.2  | 2-level hierarchical scheduling system domain model                                                                                                                                        |

| 5.3  | $n\mbox{-level}$ hierarchical scheduling system using the Composite pattern .<br>. 110                                                                                                     |

| 5.4  | Scheduling algorithm encapsulation with the Strategy pattern $~~.~.~.~111$                                                                                                                 |

| 5.5  | Sequence diagram for the scheduler tickle operation $\ldots \ldots \ldots$ |

| 5.6  | Application of the Observer pattern for loggers                                                                                                                                            |

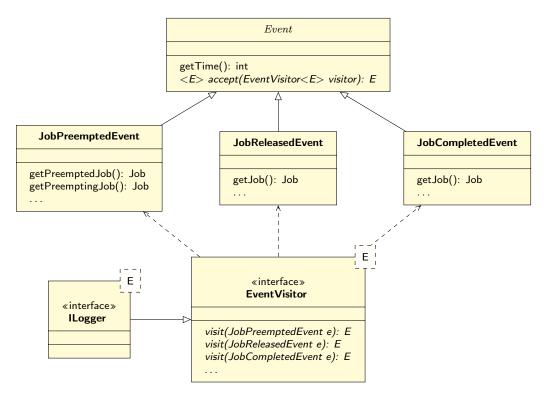

| 5.7  | Application of the Visitor pattern for loggers                                                                                                                                             |

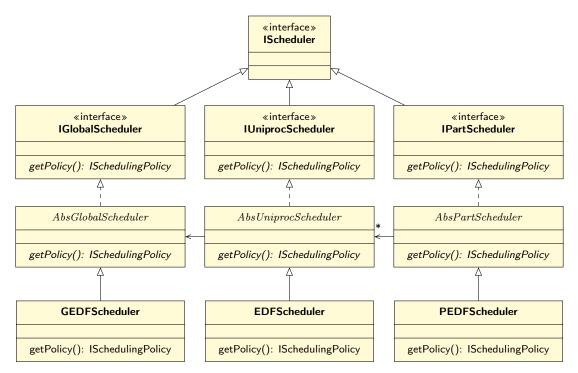

| 5.8  | Multiprocessor schedulers                                                                                                                                                                  |

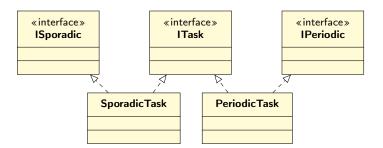

| 5.9  | Interfaces implemented by the periodic and sporadic task classes. $$ 116                                                                                                                   |

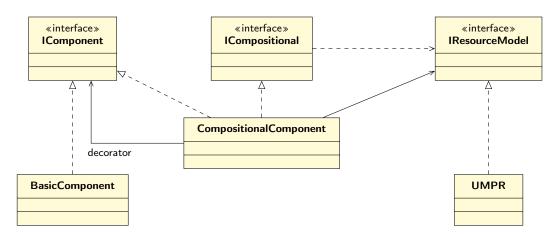

| 5.10 | Support for compositional analysis with the Decorator pattern $\ . \ . \ . \ 118$                                                                                                          |

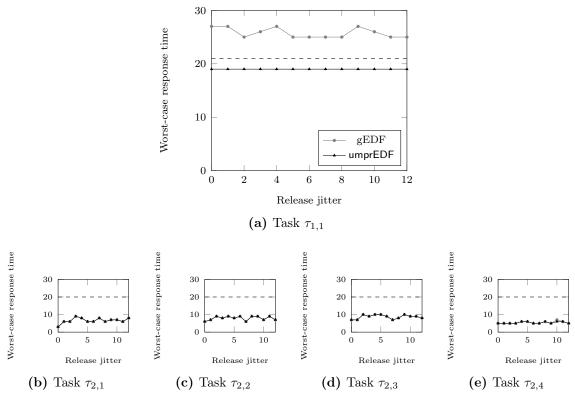

| 5.11 | Worst-case response time                                                                                                                                                                   |

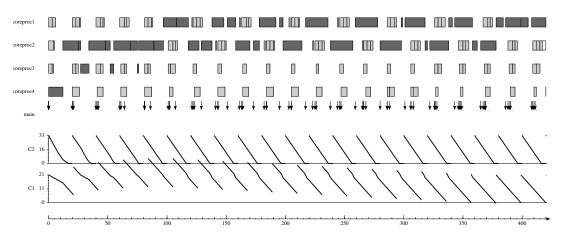

| 5.12 | Grasp trace of the simulation with gEDF global-level scheduling $123$                                                                                                                      |

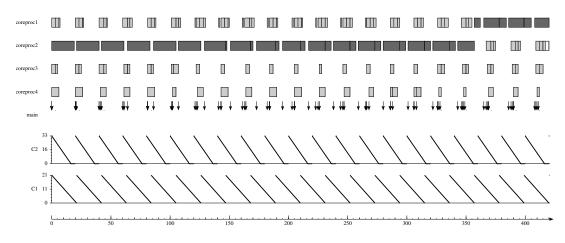

| 5.13 | Grasp trace of the simulation with $umprEDF$ global-level scheduling $124$                                                                                                                 |

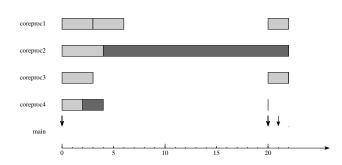

| 5.14 | Grasp trace for the simulation of task set $\mathcal{T}_1 \cup \mathcal{T}_2$ being scheduled with                                                                                         |

|      | gEDF directly on the physical platform                                                                                                                                                     |

| 6.1  | Deadline violation monitoring example                                                                                                                                                      |

| 6.2  | Screenshot of the Intel IA-32 prototype of the AIR architecture 135 $$                                                                                                                     |

| 6.3  | Example                                                                                                                                                                                    |

| 6.4  | Simulation results: deadline miss rate; deadline misses over time 142                                                                                                                      |

# List of Tables

| 4.1 | Success rates of MPR and UMPR interfaces with identical multipro-<br>cessor platforms (among feasible cases)                                           |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1 | Mapping between hsSim events and Grasp trace content                                                                                                   |

| 6.1 | APEX services in need of modifications to support task deadline vi-                                                                                    |

|     | olation monitoring                                                                                                                                     |

| 6.2 | Essential APEX services for Health Monitoring                                                                                                          |

| 6.3 | Essential APEX services to support mode-based schedules $\ldots \ldots 135$                                                                            |

| 6.4 | Logical SLOC and cyclomatic complexity (CC) for the AIR Partition                                                                                      |

|     | Scheduler with mode-based schedules                                                                                                                    |

| 6.5 | Logical SLOC and cyclomatic complexity (CC) for the implementa-                                                                                        |

|     | tion of deadline violation monitoring in AIR PAL                                                                                                       |

| 6.6 | AIR Partition Scheduler (with mode-based schedules) execution time                                                                                     |

|     | — basic metrics $\ldots \ldots \ldots$ |

# List of Theorems

| 4.1 | Theorem (Sufficient gEDF-schedulability test for the UMPR) 83        |

|-----|----------------------------------------------------------------------|

| 4.2 | Theorem (Superiority of less identical platforms)                    |

| 4.3 | Theorem (Superiority of platforms with less processors)              |

| 4.4 | Theorem (Generalization of the task transformation for the MPR) $95$ |

| 4.5 | Theorem (Correctness of the transformation to interface tasks) $98$  |

| 4.6 | Theorem (Inadequacy of gEDF for intercomponent scheduling) $100$     |

| 4.7 | Theorem (Adequacy of $umprEDF$ for intercomponent scheduling) 102    |

|     |                                                                      |

# List of Acronyms

| Acronym        | Meaning                                             |

|----------------|-----------------------------------------------------|

| APEX           | Application Executive                               |

| ARINC          | Aeronautical Radio, Incorporated                    |

| AEEC           | Airlines Electronic Engineering Committee           |

| AUTOSAR        | Automotive Open Systems Architecture                |

| DBF            | Demand Bound Function                               |

| $\mathrm{EDF}$ | Earliest Deadline First                             |

| EDZL           | Earliest Deadline until Zero Laxity                 |

| ESA            | European Space Agency                               |

| FCT            | Fundação para a Ciência e a Tecnologia              |

| $_{ m gEDF}$   | Global <b>EDF</b>                                   |

| HM             | Health Monitoring                                   |

| HRT            | Hard Real-Time                                      |

| HSF            | Hierarchical Scheduling Framework                   |

| IMA            | Integrated Modular Avionics                         |

| LLF            | Least Laxity First                                  |

| MPR            | Multiprocessor Periodic Resource (model, interface) |

| MTF            | Major Time Frame                                    |

| PAL            | <b>POS</b> Adaptation Layer                         |

| PMK            | Partition Management Kernel                         |

| POS            | Partition Operating System                          |

| $\mathbf{PST}$ | Partition Scheduling Table                          |

| RM             | Rate Monotonic                                      |

| RTEMS          | Real-Time Executive for Multiprocessor Systems      |

|                | (continues on next page)                            |

## LIST OF ACRONYMS

| Acronym | Meaning                                                     |

|---------|-------------------------------------------------------------|

| SBF     | Supply Bound Function                                       |

| SRT     | Soft Real-Time                                              |

| TSP     | Time and Space Partitioning                                 |

| UML     | Unified Modelling Language                                  |

| UMPR    | Uniform Multiprocessor Periodic Resource (model, interface) |

| WCET    | Worst-Case Execution Time                                   |

| XML     | Extensible Markup Language                                  |

(continued from previous page)

# List of Symbols

| Symbol                            | Meaning                                                               |

|-----------------------------------|-----------------------------------------------------------------------|

| $\overline{C_i}$                  | worst-case execution requirement of task $\tau_i$                     |

| $D_i$                             | relative deadline of task $\tau_i$                                    |

| $J_{i,j}$                         | $j$ th job of task $\tau_i$                                           |

| MTF                               | major time frame                                                      |

| $O_i$                             | offset of time window $\omega_i$ relative to the beginning of the MTF |

| $S_{\ell}(\pi)$                   | total capacity of the $\ell$ fastest processors in platform $\pi$     |

| $S_m(\pi)$                        | total capacity of platform $\pi$                                      |

| $T_i$                             | minimum interarrival time (or period) of task $\tau_i$                |

| $a_{i,j}$                         | arrival time of job $J_{i,j}$                                         |

| $c_i$                             | duration of time window $\omega_i$                                    |

| $d_{i,j}$                         | absolute deadline of job $J_{i,j}$                                    |

| $e_{i,j}$                         | execution requirement of job $J_{i,j}$                                |

| $i,j,k,\ell,p$                    | indices                                                               |

| m                                 | number of processors                                                  |

| n                                 | number of tasks                                                       |

| q                                 | number of components                                                  |

| $s_i$                             | schedulable utilization of the <i>i</i> th fastest processor in $\pi$ |

| t                                 | time (context-specific indices are used)                              |

| $u_i$                             | utilization of task $\tau_i$                                          |

| $u_{\max}(\mathcal{T})$           | maximum task utilization in task set ${\mathcal T}$                   |

| $u_{\mathrm{sum}}(\mathcal{T})$   | total utilization of task set ${\mathcal T}$                          |

| $\overline{\text{DBF}(\tau_i,t)}$ | demand bound function of $\tau_i$ for EDF/gEDF                        |

|                                   | (continues on next page)                                              |

# LIST OF SYMBOLS

| $\mathbf{Symbol}$                   | Meaning                                                                     |

|-------------------------------------|-----------------------------------------------------------------------------|

| $\operatorname{SBF}(\mathcal{R},t)$ | supply bound function of resource interface $\mathcal{R}$                   |

| $\mathcal{A}$                       | scheduling algorithm                                                        |

| $\mathcal{C}$                       | component                                                                   |

| $\mathcal{R}$                       | an interface, expressed with some resource model                            |

| S                                   | schedule (in the sense of a job scheduling sequence)                        |

| $\mathcal{T}$                       | task set                                                                    |

| $\mathcal{U}$                       | an interface, expressed with the UMPR model <sup>1</sup>                    |

| $\mathbb{R}$                        | the set of real numbers                                                     |

| $\mathbb{R}^+$                      | the set of positive real numbers                                            |

| $\mathbb{N}$                        | the set of natural numbers (positive integers)                              |

| $\mathbb{N}_0$                      | the set of non-negative integers $(\mathbb{N} \cup \{0\})$                  |

| Θ                                   | interface budget                                                            |

| П                                   | interface period                                                            |

| $\overline{\alpha}$                 | interface bandwidth                                                         |

| $\delta_i$                          | density of task $\tau_i$                                                    |

| $\delta_{\max}(\mathcal{T})$        | maximum task density in task set $\mathcal{T}$                              |

| $\delta_{	ext{sum}}(\mathcal{T})$   | total density of task set $\mathcal{T}$                                     |

| $\lambda(\pi)$                      | lambda parameter of platform $\pi$                                          |

| $\mu$                               | an interface, expressed with the MPR model (Easwaran <i>et al.</i> , 2009b) |

| $\pi$                               | uniform multiprocessor platform                                             |

| $	au_i$                             | <i>i</i> th task                                                            |

| $\omega_i$                          | ith time window in a partition scheduling table                             |

(continued from previous page)

<sup>&</sup>lt;sup>1</sup>Proposed in Chapter 4 of this thesis

# Publications

The contributions of this thesis have been reported, partially and in preliminary versions, in the following publications.

# **Book chapters**

CRAVEIRO, J., RUFINO, J. & VERISSIMO, P. (2010a). Architecting robustness and timeliness in a new generation of aerospace systems. In A. Casimiro, R. de Lemos & G. Gacek, eds., *Architecting Dependable Systems VII*, vol. 6420 of Lecture Notes in Computer Science, 146–170, Springer Berlin / Heidelberg. DOI: 10.1007/978-3-642-17245-8\_7

# Journals

CRAVEIRO, J., RUFINO, J. & SINGHOFF, F. (2011a). Architecture, mechanisms and scheduling analysis tool for multicore time- and space-partitioned systems. *ACM SIGBED Review*, 8(3):23–27, special issue of the 23rd Euromicro Conference on Real-Time Systems (ECRTS '11) Work-in-Progress session. DOI: 10.1145/2038617.2038622.

# Formal proceedings of international conferences

CRAVEIRO, J. & RUFINO, J. (2010b). Schedulability analysis in partitioned systems for aerospace avionics. In 15th Internacional Conference on Emerging Technologies and Factory Automation (ETFA 2010), Bilbao, Spain. DOI: 10.1109/ETFA.2010.5641243

## PUBLICATIONS

RUFINO, J. & CRAVEIRO, J. & VERISSIMO, P. (2010b). Building a time- and space-partitioned architecture for the next generation of space vehicle avionics. In 8th IFIP Workshop on Software Technologies for Future Embedded and Ubiquitous Systems (SEUS 2010), 179–190, Waidhofen an der Ybbs, Austria.

DOI: 10.1007/978-3-642-16256-5\_18

CRAVEIRO, J. & RUFINO, J. (2010a). Adaptability support in time- and spacepartitioned aerospace systems. In 2nd International Conference on Adaptive and Self-adaptive Systems and Applications (ADAPTIVE 2010), 152–157, Lisbon, Portugal.

ISBN: 978-1-61208-109-0

ROSA, J., CRAVEIRO, J. & RUFINO, J. (2011). Safe online reconfiguration of timeand space-partitioned systems. In 9th IEEE International Conference on Industrial Informatics (INDIN 2011), Caparica, Lisbon, Portugal. DOI: 10.1109/INDIN.2011.6034932

# Informal proceedings, national conferences

CRAVEIRO, J.P., ROSA, J. & RUFINO, J. (2011b). Towards self-adaptive scheduling in time- and space-partitioned systems. In *32nd IEEE Real-Time Systems Symposium (RTSS 2011) Work-in-Progress session*, Vienna, Austria.

CRAVEIRO, J.P., SILVEIRA, R.O. & RUFINO, J. (2012a). hsSim: an extensible interoperable object-oriented *n*-level hierarchical scheduling simulator. In *3rd International Workshop on Analysis Tools and Methodologies for Embedded and Real-time Systems (WATERS 2012)*, Pisa, Italy.

CRAVEIRO, J.P., SOUZA, J.L.R., RUFINO, J., GAUDEL, V., LEMARCHAND, L., PLANTEC, A., RUBINI, S. & SINGHOFF, F. (2012b). Scheduling analysis principles and tool for time- and space-partitioned systems. In *INFORUM 2012 - Simpósio de Informática*, Lisbon, Portugal.

CRAVEIRO, J.P. & RUFINO, J. (2013b). Uniform Multiprocessor Periodic Resource Model. In 4th International Real-Time Scheduling Open Problems Seminar (RTSOPS 2013), Paris, France.

# Technical reports

CRAVEIRO, J.P. & RUFINO, J. (2012). Towards compositional hierarchical scheduling frameworks on uniform multiprocessors. Tech. Rep. TR-2012-08, University of Lisbon, DI–FCUL, revised January 2013.

# Chapter 1

# Introduction

A real-time (computing) system is a computing system such that its computations' correctness (or utility) is defined, not only in terms of the accuracy of the logical results, but also in terms of the time at which these results are provided. The relationship between the timeliness of result provision and their utility allows considering different classes of real-time. Real-time systems have been classically divided into hard real-time (HRT) systems and soft real-time (SRT) systems. An HRT system contains, at least, an HRT task—a task which *must always* meet its timeliness requirements (deadline); otherwise, the results of that task's computation have no utility. HRT systems are usually associated with applications where failure to meet temporal constraints may cause catastrophical effects, including the loss of human lives or harm thereto. An SRT system contains no HRT tasks, but contains at least an SRT task—a task which *should* meet its timeliness requirements, but may occasionally miss them (in which case the utility of the result degrades through time). SRT systems are usually associated with applications where the beneficial outcome from the observance of temporal constraints lies within the spectrum of user experience, or comfort. Research on real-time systems has focused on the set of algorithms and analysis techniques which allow system developers to know, prior to the system's deployment and execution, if it will be able to guarantee the fulfillment of its timeliness requirements (either HRT or SRT) (Kopetz, 1997; Verissimo & Rodrigues, 2001).

Computing systems have evolved throughout the years to meet various needs, including concerns about size, weight and power consumption (and, consequently,

#### **1. INTRODUCTION**

cost). This led to a trend towards integrating separate systems as subsystems of a more complex mixed-criticality system on a common computing platform. Such system features the coexistence of different classes of real-time (SRT and HRT), and subsystems which may be developed by different teams and with different levels of assurance. The classical approach, often called *federated*, was to host each of these subsystems in separate communicating nodes with dedicated resources—with the consequent added weight and cost of computing hardware and cables. The added complexity of the system propagates to system's development, testing, validation and maintenance activities. Designing such complex systems around the notion of component, thus allowing component-based analysis, brings several benefits, some specific to real-time systems (Lipari et al., 2005; Lorente et al., 2006). In the case of different classes of real-time, the advantages of keeping the SRT and HRT parts of the system logically separated (and analyzing them as such) are twofold. On the one hand, the separate analysis allows fulfilling the HRT requirements of such components without imposing unnecessary pessimism on the analysis of the SRT components. On the other hand, with appropriate design considerations, the tardiness permitted to the SRT components shall not void the timeliness of the HRT components (Abeni & Buttazzo, 1998). One such design approach is time and space partitioning (TSP). Each component is hosted on a logical separation and containment unit — *partition*. In a TSP system, the various onboard functions are integrated in a shared computing platform, however being logically separated into partitions. Robust temporal and spatial partitioning means that partitions do not mutually interfere in terms of fulfillment of real-time and addressing space encapsulation requirements.

# 1.1 Context

## 1.1.1 Civil aviation

A prominent example of TSP system design is the adoption of the ARINC specifications 651—Design Guidance for Integrated Modular Avionics (AEEC, 1991)—and 653—Avionics Application Software Standard Interface (AEEC, 1997)—in the aviation and aerospace domains.

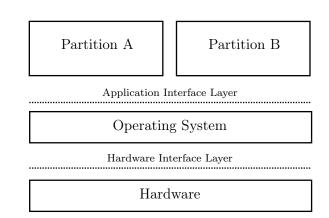

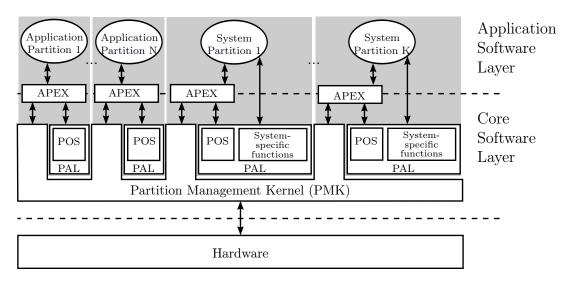

Figure 1.1: Basic architecture of an IMA computing module

The traditional approach, called *federated avionics*, makes use of distributed avionics functions packaged as self-contained units: Line Replaceable Units (LRU) and Line Replaceable Modules (LRM) (Watkins & Walter, 2007). An avionics system can be comprised of multiple LRUs or LRMs, potentially built by different contractors. What distinguishes LRUs from LRMs is that, while the former are potentially built according to independent specifications, the latter consummate a philosophy in which the use of a common specification is defended (Little, 1991). With each avionics function having its own dedicated (and sometimes physically apart) computer resources, which cannot be reallocated at runtime, inefficient resource utilization is a potential drawback from the inherent independence of faults (Audsley & Wellings, 1996; Sánchez-Puebla & Carretero, 2003).

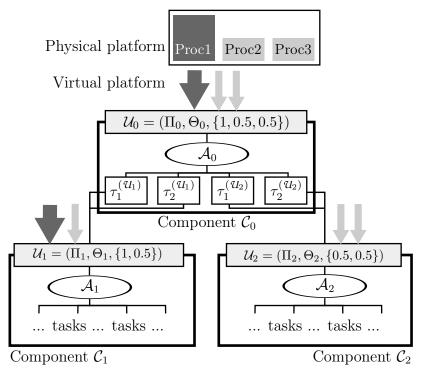

On the other hand, Integrated Modular Avionics (IMA) architectures employ a high-integrity, partitioned environment that hosts multiple avionics functions of different criticalities on a shared computing platform. Figure 1.1 portrays a basic example of the layered architecture of a IMA module. IMA addresses the needs of modern systems, such as optimizing the allocation of computing resources, reducing size, weight and power consumption (a set of common needs in the area of avionics, which is commonly represented by the acronym SWaP), and consolidation development efforts (releasing the developer from focusing on the target platform, in favor of focusing on the software and easier development and certification processes) (Watkins & Walter, 2007).

The ARINC 653 specification (AEEC, 1997) is a fundamental block from the

#### **1. INTRODUCTION**

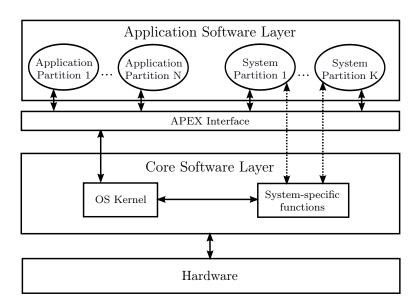

Figure 1.2: Standard ARINC 653 architecture — adapted from (AEEC, 1997)

IMA definition, where the partitioning concept emerges for protection and functional separation between applications, usually for fault containment and ease of validation, verification, and certification (AEEC, 1997; Rushby, 1999).

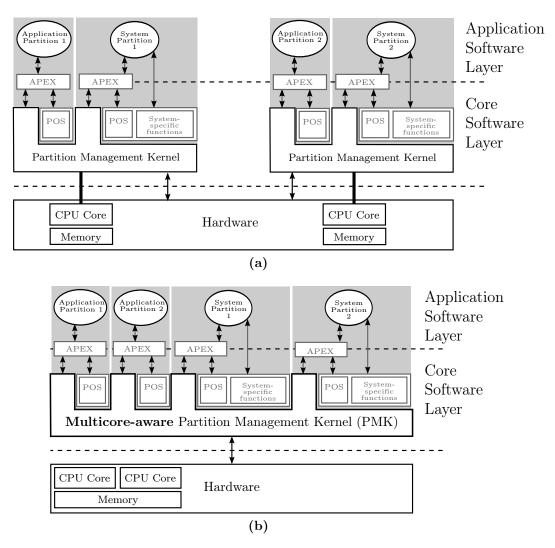

The architecture of a standard ARINC 653 system is sketched in Figure 1.2. At the application software layer, each application is executed in a confined context — a partition. The application software layer may include system partitions intended to manage interactions with specific hardware devices. Application partitions consist in general of one or more processes and can only use the services provided by a logical application executive (APEX) interface, as defined in the ARINC 653 specification (AEEC, 1997). System partitions may use also specific functions provided by the core software layer (e.g. hardware interfacing and device drivers), being allowed to bypass the standard APEX interface.

The ARINC 653 specification defines a standard interface between the software applications and the underlying operating system, known as application executive (APEX) interface. The first part of the specification (AEEC, 1997) describes a set of mandatory services, concerning partition management, process management, time management, intrapartition communication (i.e., between processes in the same partition), interpartition communication (i.e., between processes in different partitions), and health monitoring. The Part 2 of the ARINC 653 specification (AEEC, 2007)

adds, to the aforementioned mandatory services, optional services or extensions to the required services.

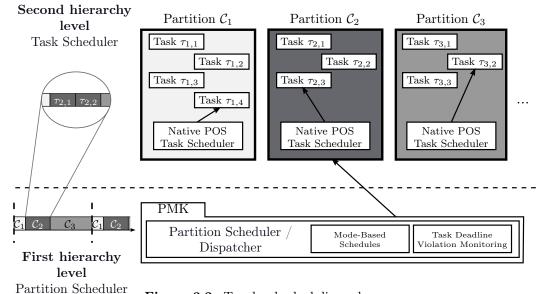

In ARINC 653 TSP systems, time partitioning is typically guaranteed by a twolevel scheduler (AEEC, 1997). On the first level, partitions are selected to execute according to some schedule. When each partition is active according to such schedule, its tasks compete according to a local-level scheduler. This is a particular case of *hierarchical scheduling*, which is considered a good first building block for a component-based design and analysis approach (Lorente *et al.*, 2006).

## 1.1.2 Aerospace

The identification of similar requirements with the aviation industry led to the interest expressed from space industry partners in applying the time and space partitioning concepts of IMA and ARINC 653 to space missions onboard software.

**North America** The National Agency for Space Exploration (NASA) is one of the space industry players with documented interest in the concepts of TSP. Rushby (1999) analyzes the requisites and issues in providing time and space partitioning in IMA, which interfere with aspects of system design such as scheduling, communication, and fault tolerance. Formal methods are called for to be able to assure and certify safety-critical software for the deployment of an IMA system. Hodson & Ng (2007) at the NASA Software and Avionics Integration Office presented ideas for future avionics systems; one of the ideas consists of a modular, layered and partitioned software approach with support for ARINC 653 (AEEC, 1997) functionality. The presentation also highlights the need for tunable, scalable and reconfigurable avionics, and the problematic of power management. Black & Fletcher (2006) analyze the various aspects of the definition of an *open* system, in order to meet NASA's interest thereupon. The resulting recommendation for the design of a new system is to seriously consider employing widely used standards (e.g., for communications), non-proprietary hardware interfaces, and commercially available development tools. Fletcher (2009) picks up on these results, and documents the employment of IMA time and space partitioning concepts to create an open architecture solution which

#### 1. INTRODUCTION

addresses NASA's requirements, including cost savings and the avoidance of vendor lockin.

**Europe** In the European space industry domain, the TSP Working Group was established to cope with the issues of adopting TSP in space. This working group comprises representatives from the European Space Agency (ESA), the French government space agency (CNES, Centre National d'Études Spatiales), and from contractor companies Thales Alenia Space and EADS Astrium (a subsidiary of the European Aeronautic Defence and Space Company, dedicated to space transportation and satellite systems). Plancke & David (2003) proposed ensuring compatibility with ARINC 653/IMA as a future standardization action, so that the exchange of functional building blocks with the aeronautic industry (which had already adopted IMA) would be made possible. To manage the problem of how applications interface with the underlying operating system, ARINC 653 should be taken into account as an example, in order to define such an interface in a way that allows OS-independent software components. Windsor & Hjortnaes (2009) summarize the work of the TSP Working Group regarding the adoption of IMA-inspired time and space partitioning techniques into spacecraft avionics systems. The authors explain the principles of TSP, and both the benefits and the remaining technology gap to the intended adoption — to which no technological feasibility impairments were found. Planche (2008) establishes links between each aspect of the ARINC 653 specification and the relevant requirements and restrictions of its application in the space domain, in order to attain the applicability of each of those aspects.

## 1.1.3 Automotive industry