# SiGe BiCMOS Front-end Integrated Circuits for

# X-Band Phased Arrays

by

Tolga Dinç

Submitted to the Graduate School of Engineering and Natural Sciences in partial fulfillment of the requirements for the degree of Master of Science

Sabancı University

Spring, 2012

SiGe BiCMOS Front-end Integrated Circuits for X-Band Phased Arrays

#### APPROVED BY

Prof. Dr. Yaşar GÜRBÜZ (Thesis Supervisor)

Assoc. Prof. Dr. İbrahim TEKİN

Assoc. Prof. Dr. Meriç ÖZCAN

Assist. Prof. Dr. Volkan ÖZGÜZ

Assist. Prof. Dr. Hüsnü YENİGÜN

Assist. Prof. Dr. Cem ÖZTÜRK (Reserve Member)

DATE OF APPROVAL: 0.6 - 0.5 - 2012

© Tolga Dinç 2012

All Rights Reserved

#### Acknowledgements

This thesis would not have been completed without the support, help and inspiration of the many people; my professors, co-workers and friends as well as my parents. Here I would like to convey my thanks and gratitude to all those people whose influences made me the person who I am today.

First of all, I would like to thank my advisor Prof. Yaşar Gürbüz who has one of the largest influences on my life over the there past year. I am indebted to him for his guidance, encouragement, confidence, patience and for providing all the opportunities to me to excel in the field of RFIC during my undergraduate and master studies at SU. Thanks to his guidance and confidence in me, I have achieved academic highs that many master students could never have dreamed of.

I would also like to thank to Prof. İbrahim Tekin, Prof. Meriç Özcan, Prof. Volkan Özgüz, and Prof. Hüsnü Yenigün for serving in my master's thesis committee. I am grateful for their precious time and valuable comments.

The summer internships at IHP Microelectronics, Germany, in the summer of 2010 and 2011 were an invaluable experience to me. I am very thankful to Mehmet Kaynak for making these internships productive. I am also grateful to IHP Micro-electronics for providing IC fabrication and technical support.

This work is supported by the Scientific and Technological Research Council of Turkey under grant 110E107. Additionally, I want to express my sincere gratitude to TUBITAK-BIDEB for providing a generous financial scholarship for my master studies.

I am thankful to my comrade designers Samet Zihir and Ilker Kalyoncu for their contribution to this work. I would also like to thank the following past and present members of the Microsystems group for creating a friendly environment and all their help: Ferhat Taşdemir, Hüseyin Kayahan, Melik Yazıcı, M. Burak Baran and Ömer Ceylan. Additionally, the help and efforts of laboratory staff of the EE program, Mehmet Doğan, Ali Kasal and Bülent Köroğlu, does not go unnoticed. Besides, I would like to thank Utku Ülkü and Serkan Yalıman for their friendship during my master studies.

Finally I would like to thank my parents Bedrive and Nusret, and my sister Kumru for their unconditional love, encouragement and sacrifices over the years. I would never have made it to this point without their support.

#### SiGe BiCMOS Front-End Circuits for X-Band Phased Arrays

Tolga Dinç EE, Master's Thesis, 2012 Thesis Supervisor: Prof. Dr. Yaşar GÜRBÜZ

Keywords: Phased Arrays, T/R module, SiGe BiCMOS, X-Band Integrated Circuits, Low Noise Amplifier, T/R Switch and SPDT Switch.

#### Abstract

The current Transmit/Receive (T/R) modules have typically been implemented using GaAs- and InP-based discrete monolithic microwave integrated circuits (MMIC) to meet the high performance requirement of the present X-Band phased arrays. However their cost, size, weight, power consumption and complexity restrict phased array technology only to certain military and satellite applications which can tolerate these limitations. Therefore, next generation X-Band phased array radar systems aim to use low cost, silicon-based fully integrated T/R modules. For this purpose, this thesis explores the design of T/R module front-end building blocks based on new approaches and techniques which can pave the way for implementation of fully integrated X-Band phased arrays in low-cost SiGe BiCMOS process.

The design of a series-shunt CMOS T/R switch with the highest  $IP_{1dB}$ , compared to other reported works in the literature is presented. The design focuses on the techniques, primarily, to achieve higher power handling capability ( $IP_{1dB}$ ), along with higher isolation and better insertion loss of the T/R switch. Also, a new T/R switch was implemented using shunt NMOS transistors and slow-wave quarter wavelength transmission lines. It presents the utilization of slow-wave transmissions lines in T/R switches for the first time in any BiCMOS technology to the date. A fully integrated DC to 20 GHz SPDT switch based on series-shunt topology was demonstrated. The resistive body floating and on-chip impedance transformation networks (ITN) were used to improve power handling of the switch.

An X-Band high performance low noise amplifier (LNA) was implemented in 0.25  $\mu$ m SiGe BiCMOS process. The LNA consists of inductively degenerated two cascode stages with high speed SiGe HBT devices to achieve low noise figure (NF), high gain and good matching at the input and output, simultaneously. The performance parameters of the LNA collectively constitute the best Figure-of-Merit value reported in similar technologies, to the best of author's knowledge. Furthermore, a switched LNA was implemented SiGe BiCMOS process for the first time at X-Band. The resistive body floating technique was incorporated in switched LNA design, for the first time, to improve the linearity of the circuit further in bypass mode.

Finally, a complete T/R module with a state-of-the-art performance was implemented using the individually designed blocks. The simulations results of the T/R module is presented in the dissertation. The state-of-the-art performances of the presented building blocks and the complete module are attributed to the unique design methodologies and techniques.

#### X-Band Faz Dizinleri için SiGe BiCMOS Ön Uç Devreleri

Tolga Dinc EE, Yüksek Lisans Tezi, 2012 Tez Danışmanı: Prof. Dr. Yaşar GÜRBÜZ

Anahtar Kelimeler: Faz Dizinleri, T/R modülü,SiGe BiCMOS, X-Bandında entegre devre, Düşük Güç Kuvvetlendiricisi, T/R Anahtarı, SPDT Anahtarı.

#### Özet

Günümüzde X-Band faz dizinlerinin yüksek performans gereksinimi karşılamak için alıcı-verici (T/R) modülleri genellikle GaAS, InP temelli tektaş mikrodalga tümdevreler kullanılarak gerçeklenmektedir. Ancak III-V yarı iletken teknolojisine dayanan bu modüllerin maliyeti, boyutu, ağırlığı, güç tüketimi ve karmaşıklığı faz dizini teknolojisinin kullanımını sadece bunlara musamaha gösterebilen askeri ve uzay uygulamalarıyla sınırlamaktadır. Bu kısıtlamayı, gelecek nesil X-Band faz dizinli radar sistemleri düşük maliyetli, silikon tabanlı entegre T/R mödülleri kullanarak aşmayı amaçlamaktadır. Bu amaçla, bu tez düşük maliyetli SiGe BiCMOS prosesinde tamamen entegre X-Band faz dizinlerinin gerçeklenmesine katkıda bulunacak yeni yaklaşım ve tekniklere dayalı T/R modül ön uç bloklarının tasarımını inceleyecektir.

Literatürdeki diğer çalışmalar ile karşılaştırıldığında en yüksek IP1dB değerine sahip seri-paralel CMOS T/R anahtarının tasarımı sunulmaktadır. Tasarım daha yüksek izolasyon ve daha iyi ekleme kaybı elde etme tekniklerinin yanında özellikle daha yüksek güce dayanıklılık elde etme teknikleri üzerinde odaklanmaktadır. Ayrıca, paralel NMOS tranzistörler ve dalga yavaşlatan çeyrek dalga boyundaki iletim hatları kullanılarak yeni bir T/R anahtarı tasarlanmıştır. Şu ana kadarki tüm BiC-MOS teknolojileri göz önüne alındığında, dalga yavaşlatan iletim hatlarının T/R anahtarında kullanımı ilk defa sunulmaktadır. Ek olarak, seri-paralel topolojisine dayalı DC-20 GHz tek giriş çift çıkış (SPDT) anahtarı gösterilmiştir.

X-Band yüksek performans bir düşük güç kuvvetlendiricisi (LNA) 0.25  $\mu$ m SiGe BiCMOS prosesinde gerçeklenmiştir. LNA aynı anda düşük gürültü figürü, yüksek kazanç ve giriş ve çıkışlarda güzel uydurma elde etmek için endüktif olarak dejenere edilmiş ve yüksek hızlı SiGe HBT kullanan iki kaskot katından oluşmaktadır. Yazarın bilgisine göre, LNA'in toplu olarak performans parametreleri benzer teknolojilerde yayınlanan başarım ölçütleri arasında en iyisidir. Buna ek olarak, yazarın bilgisi dahilinde X-Band'ta çalışan anahtarlamalı bir LNA SiGe BiCMOS teknolojisinde ilk defa uygulanmıştır. Dirençsel gövde dalgalandırma tekniği baypas modunda devrenin doğrusallığını arttırmak için ilk defa anahtarlamalı LNA tasarımına dahil edilmiştir.

Son olarak, teker teker tasarlanan bloklar kullanılarak teknolojinin geldiği son nokta bir performansa sahip T/R modül bütün olarak entegre edilmiştir. T/R modülün benzetim sonuçları tezde sunulmaktadır. Teker teker sunulan yapı bloklarının ve bütün T/R modülünün en son teknoloji performansı özgün tasarım metodlarına ve tekniklerine atfedilmektedir.

## Contents

| A        | cknov         | vledgements                                                                                                        |       | iv        |

|----------|---------------|--------------------------------------------------------------------------------------------------------------------|-------|-----------|

| Al       | ostra         | $\mathbf{ct}$                                                                                                      |       | v         |

| Li       | st of         | Figures                                                                                                            |       | xi        |

| Li       | st of         | Tables                                                                                                             |       | xii       |

| Li       | st of         | Abbreviations                                                                                                      |       | xiii      |

| 1        | Intr          | oduction                                                                                                           |       | 1         |

|          | 1.1           | An Overview of Radar History                                                                                       |       | 1         |

|          | 1.2           | Phased Array Principle                                                                                             |       | 1         |

|          | 1.3           | Phased Array Systems                                                                                               |       | 5         |

|          | 1.4           | Downsizing of T/R Modules                                                                                          |       | 9         |

|          | 1.5           | SiGe HBT Technology                                                                                                |       | 12        |

|          | 1.6           | Previously Proposed T/R Module                                                                                     |       | 14        |

|          |               | 1.6.1 Building Blocks and Specifications                                                                           |       | 14        |

|          |               | 1.6.2 Power Amplifier $\ldots \ldots  |       | 17        |

|          | 1.7           | Motivation                                                                                                         |       | 18        |

|          | 1.8           | Organization                                                                                                       |       | 19        |

| <b>2</b> | $\mathbf{RF}$ | CMOS Switches for the X-Band SiGe T/R Module                                                                       |       | <b>21</b> |

|          | 2.1           | An X-Band Highly Linear CMOS T/R Switch                                                                            |       | 21        |

|          |               | 2.1.1 Introduction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                |       | 21        |

|          |               | 2.1.2 Circuit Design and Analysis                                                                                  |       | 22        |

|          |               | 2.1.3 Measurement Results                                                                                          |       | 32        |

|          |               | 2.1.4 Performance Comparison                                                                                       |       | 35        |

|          | 2.2           | A DC-20 GHz CMOS SPDT Switch                                                                                       |       | 35        |

|          |               | 2.2.1 Introduction                                                                                                 |       | 35        |

|          |               | 2.2.2 Circuit Design and Analysis                                                                                  |       | 37        |

|          |               | 2.2.3 Measurement Results                                                                                          |       |           |

|          |               | 2.2.4 Performance Comparison                                                                                       |       |           |

|          | 2.3           | An X-Band T/R Switch based upon Slow-wave Transmission Li                                                          |       |           |

|          |               | 2.3.1 Introduction                                                                                                 |       |           |

|          |               | 2.3.2 Circuit Design and Analysis                                                                                  |       |           |

|          |               | 2.3.3 Measurement Results                                                                                          |       |           |

|          |               | 2.3.4 Performance Comparison                                                                                       |       |           |

| 3        | SiG           | e HBT Low Noise Amplifiers for the X-Band T/R Modu                                                                 | ıle   | 51        |

|          | 3.1           | An X-Band, High Performance, SiGe-HBT LNA for Phased A                                                             | Array |           |

|          |               | Radar Applications                                                                                                 | •     | 51        |

|          |               | 3.1.1 Introduction                                                                                                 |       |           |

|          |               | 3.1.2 SiGe HBT Technology                                                                                          |       |           |

|          |               | 3.1.3 Circuit Design Procedure                                                                                     |       |           |

|          |               | 3.1.4 Measurement Results                                                                                          |       |           |

|          |               | 3.1.5 Performance Comparison                                                                                       |       |           |

|          | 3.2           | An X-Band Switched LNA in $0.25$ - $\mu$ m SiGe BiCMOS for Phased-                                                 |       |           |

|          |               | ,                                                                                                                  | 5     |           |

|          |       | 3.2.1   | Introduction                              |   |   |      | 62        |

|----------|-------|---------|-------------------------------------------|---|---|------|-----------|

|          |       | 3.2.2   | Circuit Design and Analysis               |   |   |      | 62        |

|          |       | 3.2.3   | Measurement Results                       |   |   |      | 64        |

|          |       | 3.2.4   | Performance Summary                       |   |   |      | 69        |

| 4        | An    | X-Ban   | d SiGe BiCMOS T/R Module for Phased Array | A | ٩ | pli- |           |

|          | cati  | ons     |                                           |   |   |      | <b>70</b> |

|          | 4.1   | Introd  | uction                                    |   |   |      | 70        |

|          | 4.2   | Design  | and Implementation                        |   |   |      | 71        |

|          | 4.3   | Simula  | ation Results                             |   |   |      | 73        |

|          | 4.4   | Perform | mance Comparison                          |   |   |      | 80        |

| <b>5</b> | Con   | clusio  | n & Future Work                           |   |   |      | 82        |

|          | 5.1   | Summ    | ary of Work                               |   |   |      | 82        |

|          | 5.2   | Future  | Work                                      |   |   |      | 83        |

| Re       | efere | nces    |                                           |   |   |      | 90        |

# List of Figures

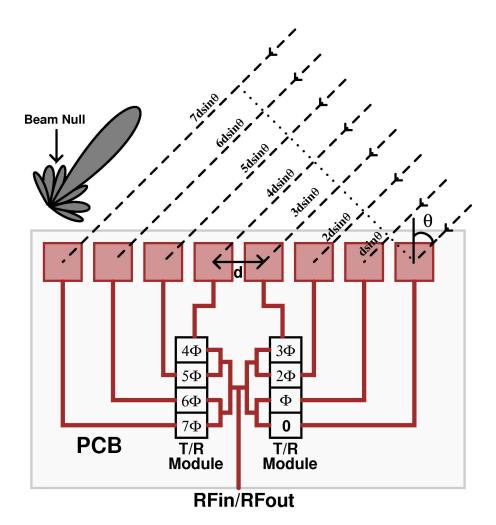

| 1  | Phased array system with 8 antenna elements                                    | 2  |

|----|--------------------------------------------------------------------------------|----|

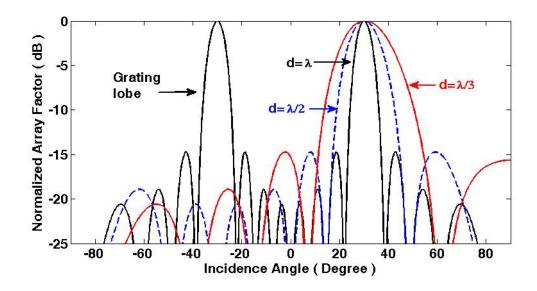

| 2  | Normalized array factor of a 8-element phased array with three dif-            |    |

|    | ferent antenna spacing                                                         | 3  |

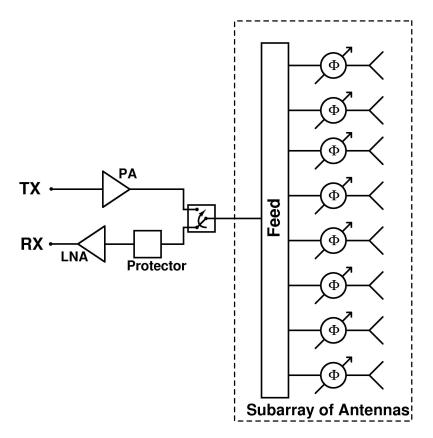

| 3  | Simple block diagram of a passive phased array radar                           | 6  |

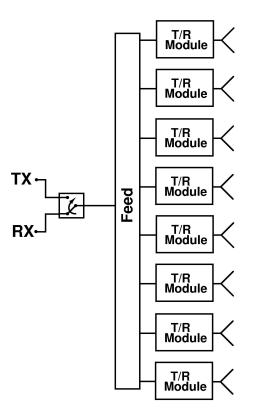

| 4  | Simple block diagram of an active phased array radar                           | 7  |

| 5  | Photograph of a passive and active phased array radar                          | 8  |

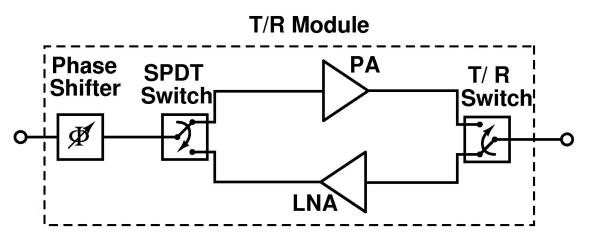

| 6  | Simple block diagram of a solid state T/R Module                               | 8  |

| 7  | A III-V based T/R Module in different platforms                                | 9  |

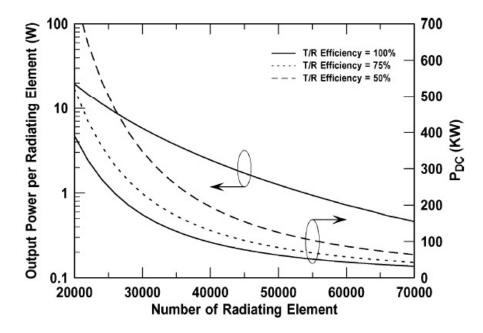

| 8  | Output power per radiating element and total DC power required for             |    |

|    | all of the T/R modules versus number of elements                               | 11 |

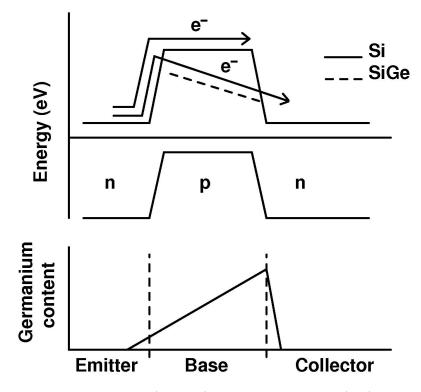

| 9  | Ge concentration (bottom) and band structure (top) of a SiGe HBT .             | 13 |

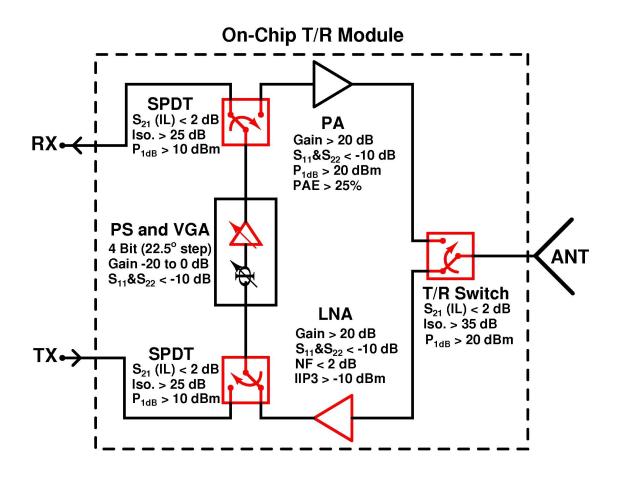

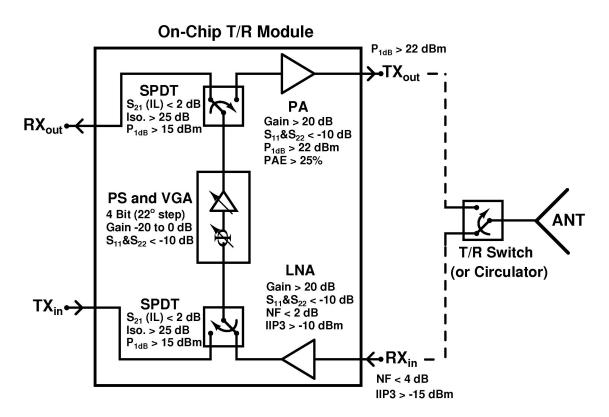

| 10 | SiGe X-Band T/R module system block diagram                                    | 15 |

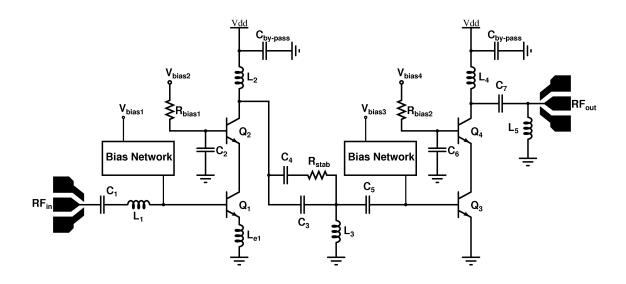

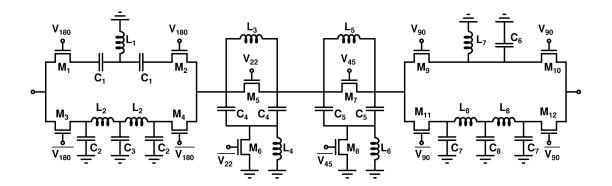

| 11 | Schematic of the designed two-stage power amplifier.                           | 17 |

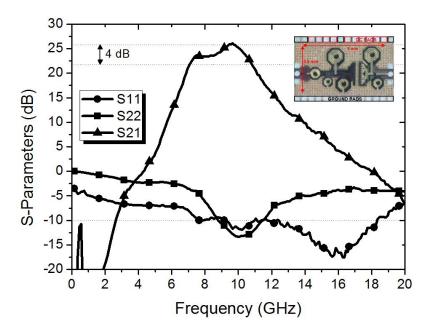

| 12 | Measured small-signal gain and return loss of the two-stage power              |    |

|    | amplifier.                                                                     | 18 |

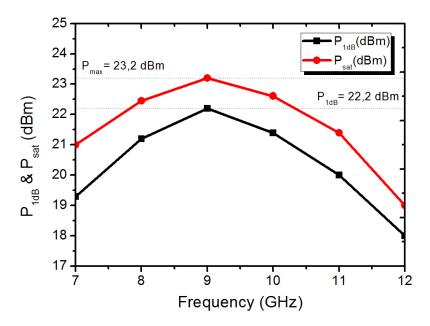

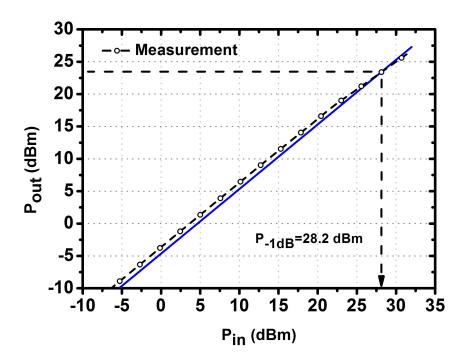

| 13 | Measured saturated output power and the output referred $P_{1dB}$              | 18 |

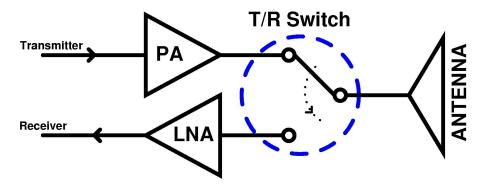

| 14 | A simple block diagram of T/R module                                           | 21 |

| 15 | Circuit schematic of the designed SPDT T/R switch.                             | 22 |

| 16 | (a) OFF-state Model and (b) ON-state Model of NMOS                             | 23 |

| 17 | Transmit mode small-signal simplified model.                                   | 23 |

| 18 | Circuit configuration to derive S21 of the ON transistor.                      | 24 |

| 19 | Transistor width versus insertion loss of the SPDT T/R switch                  | 26 |

| 20 | T/R switch in the transmit mode                                                | 29 |

| 21 | Cross-sectional view of a typical isolated NMOS transistor                     | 31 |

| 22 | The switch core with body floating technique in TX mode                        | 31 |

| 23 | The die photo of the $T/R$ switch. The chip area including pads is             |    |

|    | $0.44 \ mm_2$                                                                  | 32 |

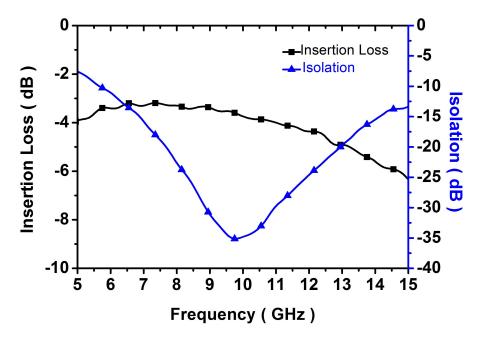

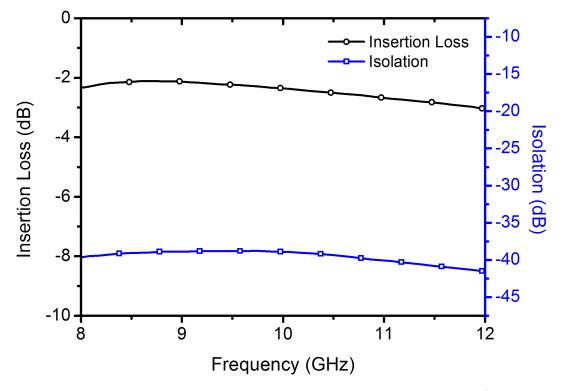

| 24 | Measured insertion loss and isolation of the $T/R$ switch                      | 33 |

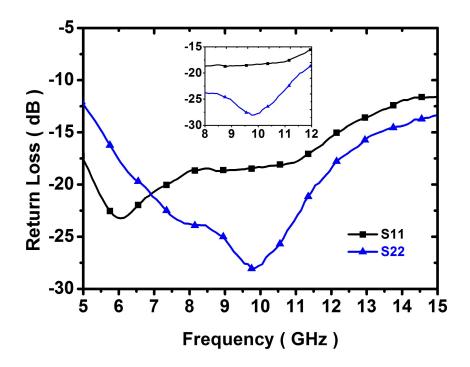

| 25 | Measured input return loss, $S_{11}$ , and output return loss, $S_{22}$ of the |    |

|    | T/R switch.                                                                    | 34 |

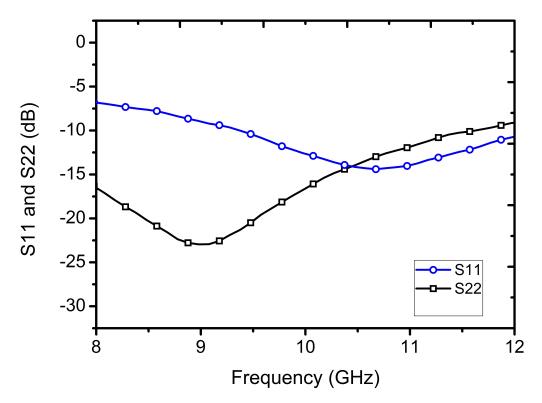

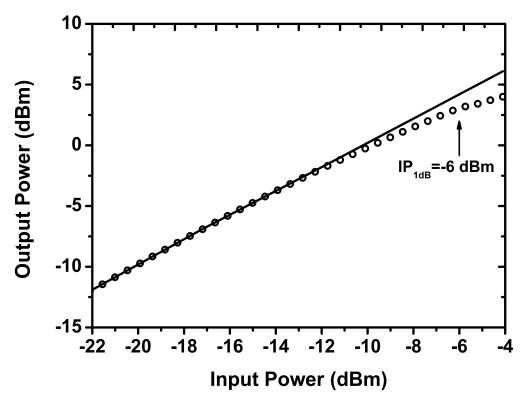

| 26 | Measured 1 dB compression point $(IP_{1dB})$ of the switch at 10 GHz.          | 34 |

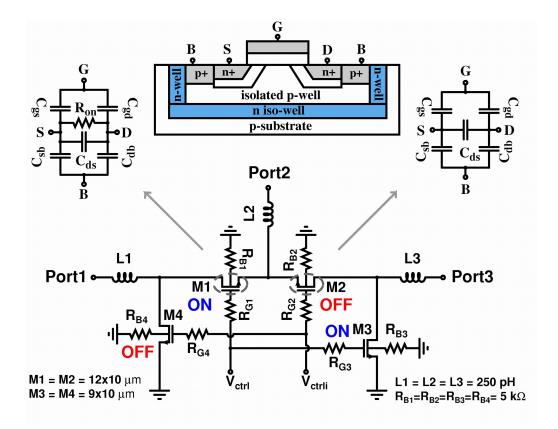

| 27 | Circuit schematic of the designed SPDT switch and cross-sectional              |    |

|    | view of a typical isolated NMOS transistor                                     | 37 |

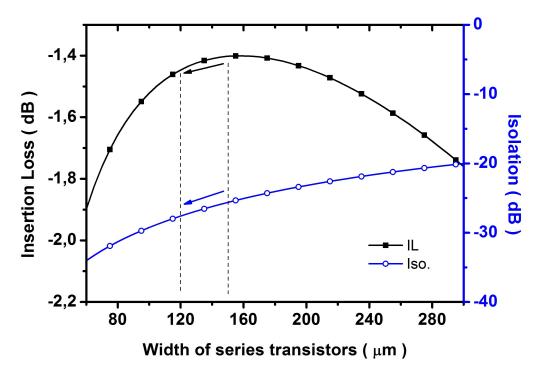

| 28 | Simulated series transistor width versus insertion loss and isolation.         | 38 |

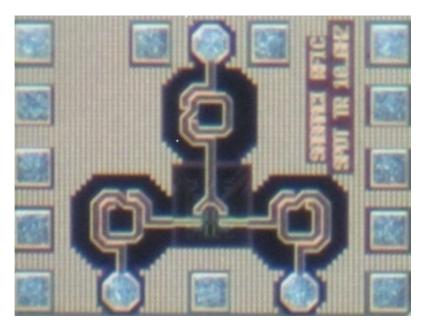

| 29 | Die photo of the DC-20 GHz SPDT switch. The active chip area is                |    |

|    | $0.48 \times 0.36 \ mm^2.$                                                     | 39 |

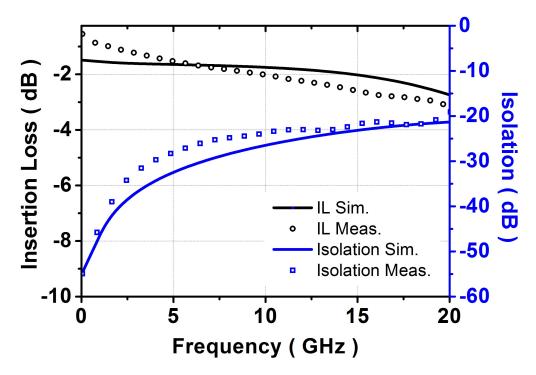

| 30 | Measured insertion loss and isolation of the SPDT switch                       | 40 |

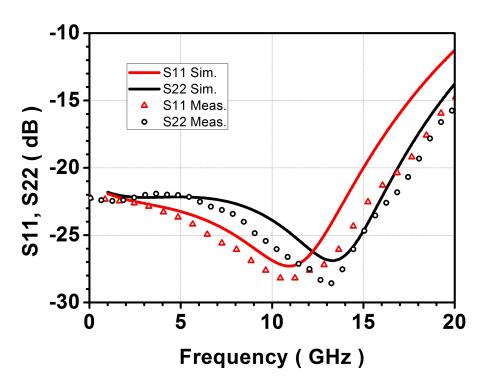

| 31 | Measured and simulated return loss of the SPDT switch                          | 40 |

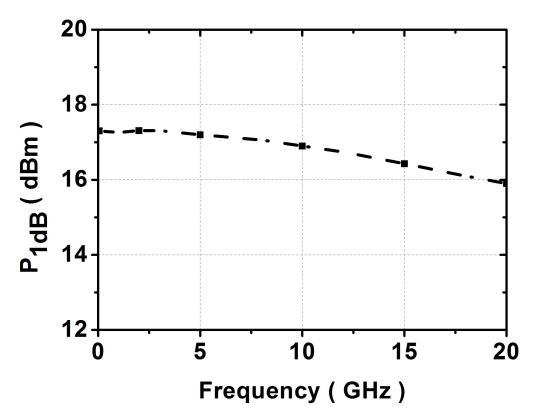

| 32 | P1dB versus frequency of the SPDT switch.                                      | 42 |

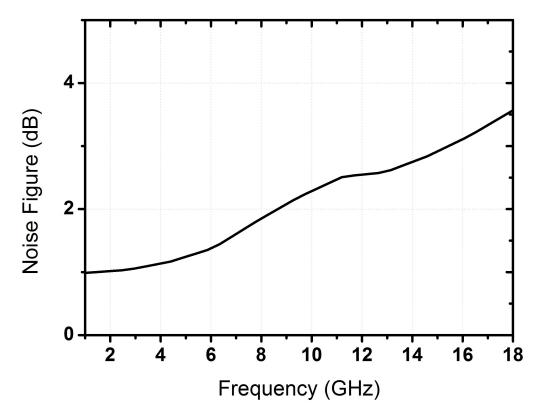

| 33 | Measured noise figure of the SPDT switch                                       | 42 |

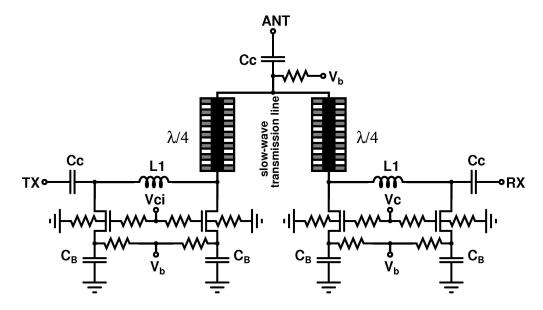

| 34 | Schematic of the designed T/R switch using slow-wave transmission              |    |

|    | lines                                                                          | 43 |

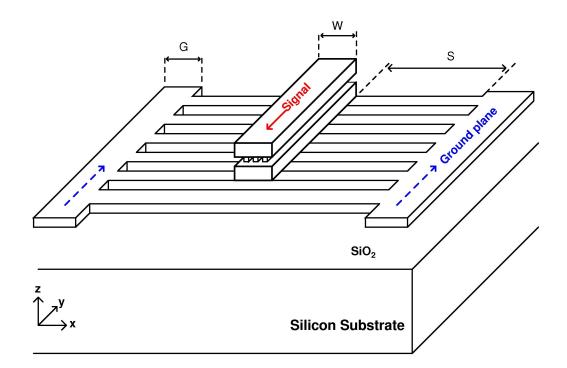

| 35 | Structure of the slow-wave microstrip transmission line (S-MSL)                | 44 |

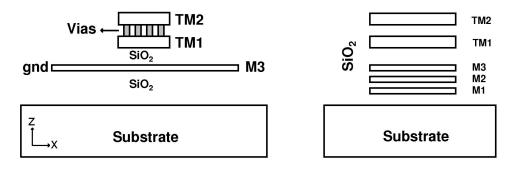

| 36 | Simplified cross-section of the slow-wave transmission line and metal          |    |

|    | layers in the technology.                                                      | 44 |

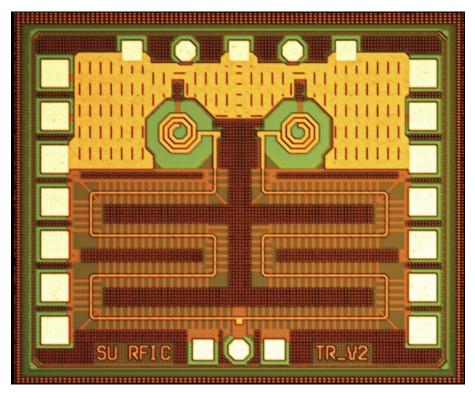

| 37 | Die photo of the DC-20 GHz SPDT switch. The active chip area is $0.48 \times 0.36 \ mm^2$ . | 16       |

|----|---------------------------------------------------------------------------------------------|----------|

| 38 | Measured insertion loss and isolation of the S-MSL based T/R switch.                        | 46<br>47 |

| 39 | Measured return losses of the S-MSL based T/R switch.                                       | 48       |

| 40 | Measured 1 dB compression point $(IP_{1dB})$ of the T/R switch at 10                        | 10       |

| 10 | GHz.                                                                                        | 48       |

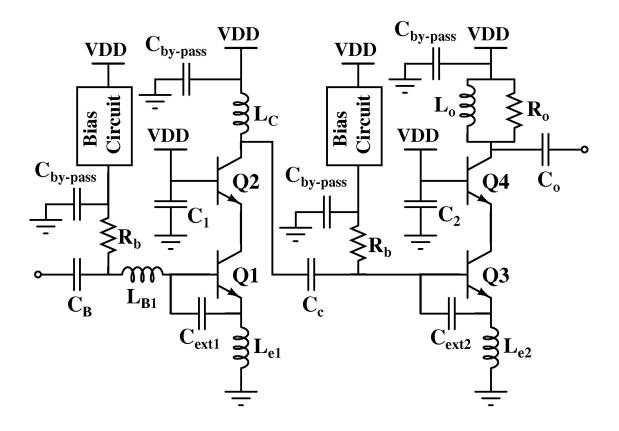

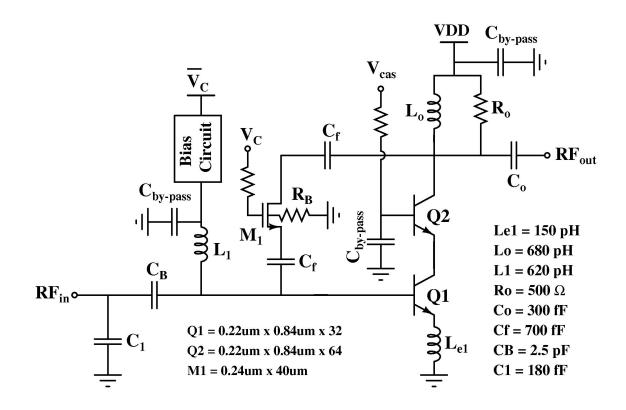

| 41 | Schematic of the designed two-stage low noise amplifier.                                    | 52       |

| 42 | Schematic of the active bias circuit                                                        | 54       |

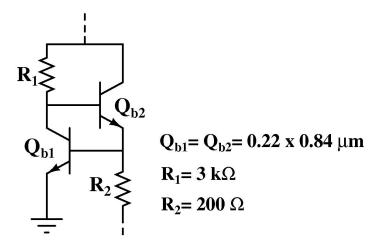

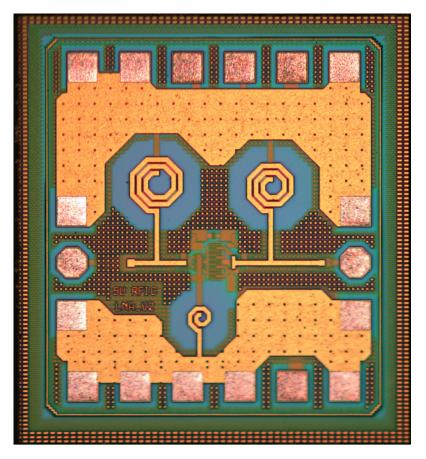

| 43 | Micrograph of the X-Band two-stage low noise amplifier.                                     | 56       |

| 44 | Measured $S_{11}$ and $S_{22}$ of the LNA (input and output matching)                       | 57       |

| 45 | Measured $S_{21}$ and $S_{12}$ of the LNA (gain and isolation).                             | 58       |

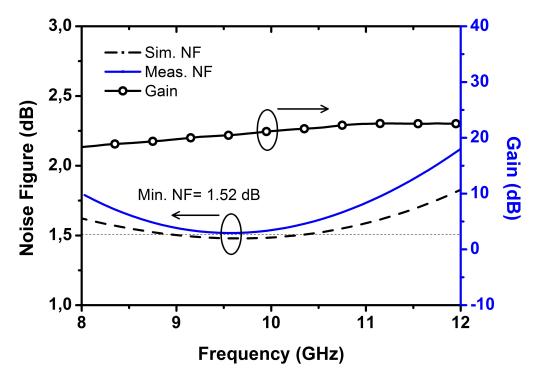

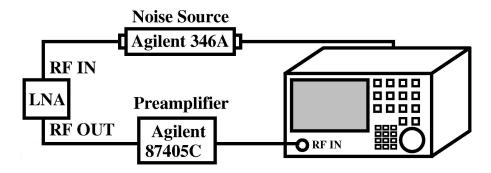

| 46 | Measured noise figure and gain of the LNA across X-Band                                     | 58       |

| 47 | Measurement setup for noise figure                                                          | 59       |

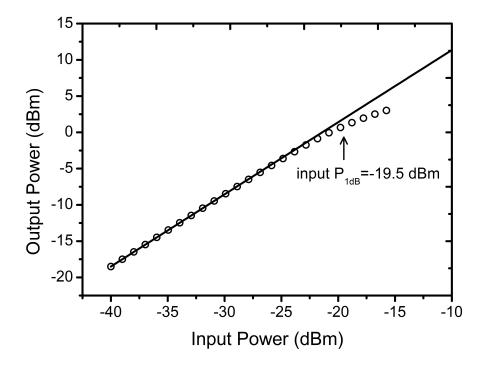

| 48 | Measured 1-dB compression point of the LNA                                                  | 59       |

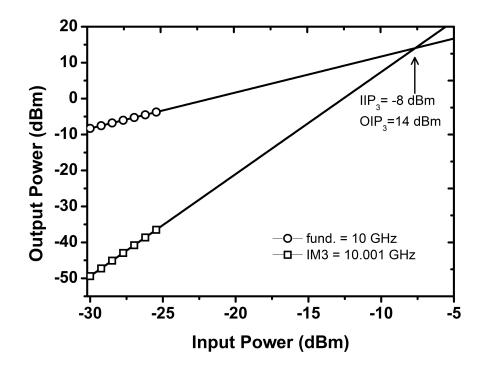

| 49 | Measured input third-order intercept point                                                  | 60       |

| 50 | Circuit schematic of the switched gain LNA.                                                 | 63       |

| 51 | Bias circuit of the switched gain LNA.                                                      | 63       |

| 52 | Die photo of the switched gain LNA. The active chip area, without                           |          |

|    | pads, is $0.52 \times 0.58 = 0.3 \ mm^2$ .                                                  | 65       |

| 53 | Measured S-parameters of the switched LNA in gain mode                                      | 65       |

| 54 | Measured noise figure of the switched LNA in gain mode                                      | 66       |

| 55 | Measured P1dB of the switched LNA in gain mode                                              | 66       |

| 56 | Measured S-parameters of the LNA in bypass mode                                             | 67       |

| 57 | Measured P1dB of the LNA in bypass mode                                                     | 67       |

| 58 | Input-referred third-order intercept point (IIP3) in bypass mode                            | 68       |

| 59 | Block diagram of the X-Band SiGe BiCMOS T/R Module                                          | 70       |

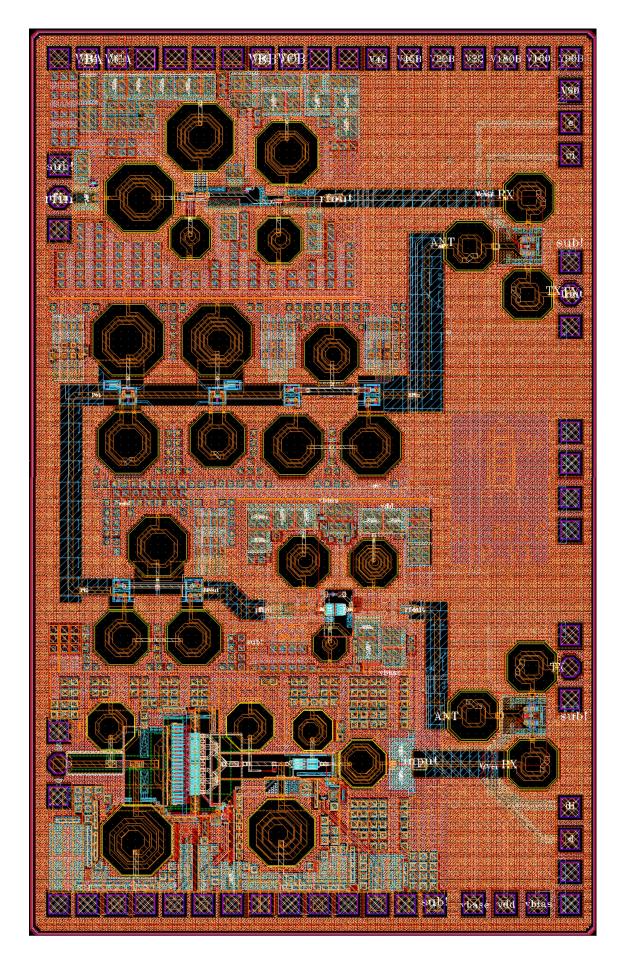

| 60 | Layout of the X-Band T/R Module in IHP 0.25- $\mu m$ SiGe BiCMOS                            | - 1      |

| 01 | process                                                                                     | 71       |

| 61 | Layout of the X-Band T/R Module in IHP 0.25- $\mu$ m SiGe BiCMOS                            | 72       |

| 62 | process                                                                                     | 12       |

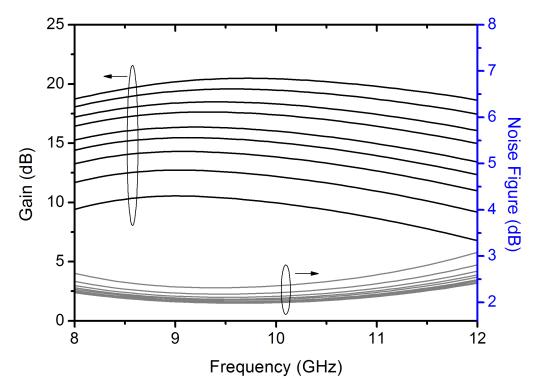

| 02 | states.                                                                                     | 74       |

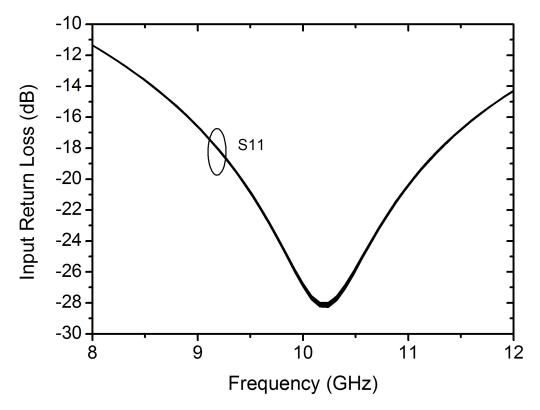

| 63 | Simulated input return loss of the T/R module in the receive mode                           | 14       |

| 00 | for all phase states.                                                                       | 74       |

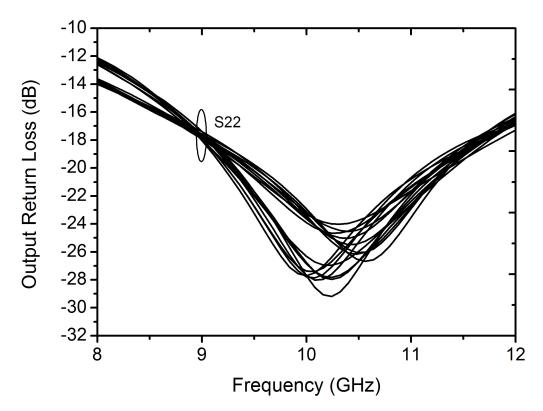

| 64 | Simulated output return loss of the T/R module in the receive mode                          | 14       |

| 01 | for all phase states.                                                                       | 75       |

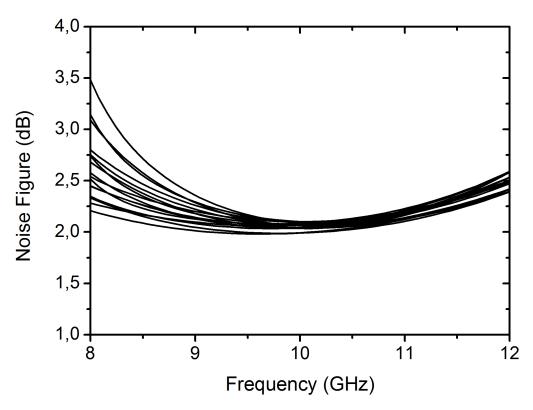

| 65 | Simulated noise figure of the T/R module in the receive mode for all                        | 10       |

| 00 | phase states                                                                                | 75       |

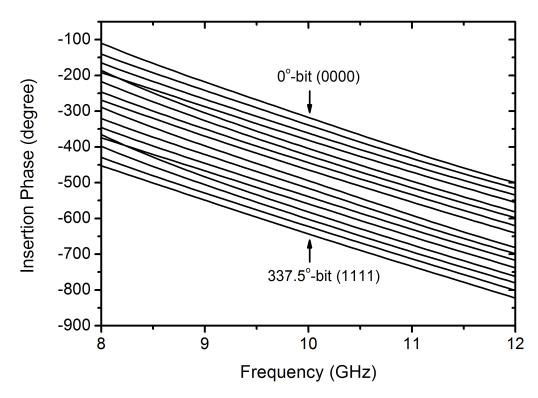

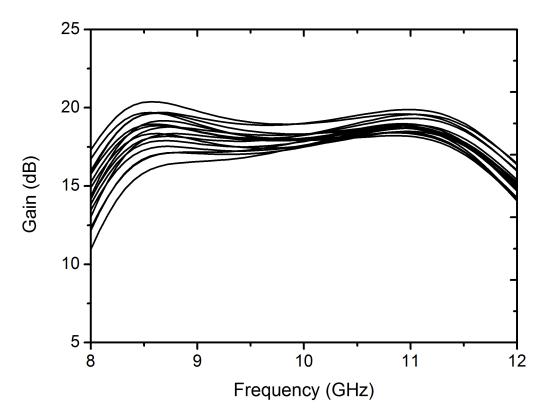

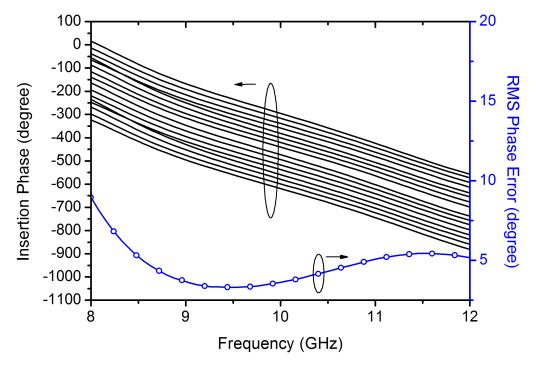

| 66 | Simulated 4-bit phase response of the T/R module in the receive mode.                       | 76       |

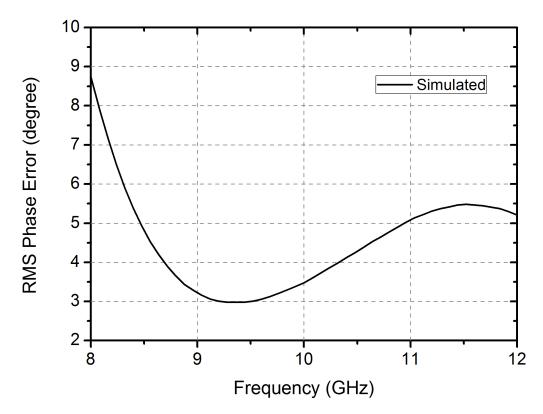

| 67 | Simulated RMS phase error of the $T/R$ module in the receive mode.                          | 77       |

| 68 | Simulated variation of the gain and noise figure of the $T/R$ module                        | • •      |

| 00 | in receive mode                                                                             | 77       |

| 69 | Simulated gain of the $T/R$ module in the transmit mode for all phase                       |          |

| 00 | states.                                                                                     | 78       |

| 70 | Simulated input and output return losses of the T/R module in the                           | 10       |

| 10 | transmit mode for all phase states.                                                         | 79       |

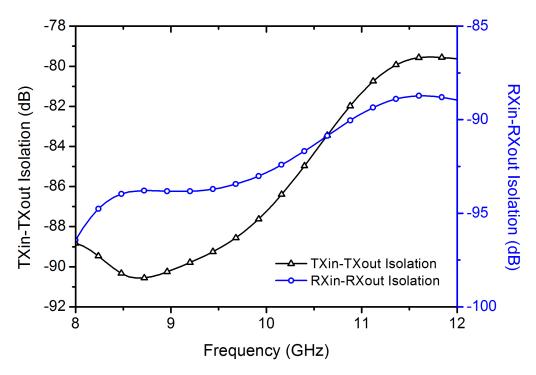

| 71 | Simulated 4-bit phase response and RMS phase error of the $T/R$                             | .0       |

|    | module in the transmit mode.                                                                | 79       |

72 Simulated isolation of the transmit and receive modes. . . . . . . . . . . . . 80

## List of Tables

| 1 | Comparison of the Radar Architectures.                                | 8  |

|---|-----------------------------------------------------------------------|----|

| 2 | Comparison of the T/R switch with the state-of-the-art reported works | 36 |

| 3 | Comparison of the wideband CMOS SPDT switches                         | 41 |

| 4 | Comparison of the T/R switch based upon slow-wave transmission        |    |

|   | lines with the state-of-the-art reported works                        | 50 |

| 5 | Comparison of state-of-the-art X-Band SiGe Low Noise Amplifiers       | 61 |

| 6 | Comparison of the state-of-the-art X-Band $T/R$ Modules               | 81 |

|   |                                                                       |    |

## List of Abbreviations

| $\mathbf{AF}$          | Array Factor                             |

|------------------------|------------------------------------------|

| $\mathbf{A}\mathbf{M}$ | Amplitude Modulation                     |

| ANT                    | Antenna                                  |

| $BV_{CEO}$             | Collector-Emitter Breakdown Voltage      |

| BV <sub>CBO</sub>      | Collector-Base Breakdown Voltage         |

| CMOS                   | Complementary Metal Oxide Semiconductor  |

| EIRP                   | Equivalent Isotropically Radiated Power  |

| FOM                    | Figure-of-Merit                          |

| GaAs                   | Gallium-Arsenide                         |

| $\operatorname{HBT}$   | Heterojunction Bipolar Transistors       |

| IC                     | Integrated Circuit                       |

| $\mathbf{IL}$          | Insertion Loss                           |

| IIP3                   | Input Third-order Intercept Point        |

| InP                    | Indium phosphide                         |

| ITN                    | Impedance Transformation Network         |

| iNMOS                  | Isolated NMOS                            |

| $\mathbf{LNA}$         | Low Noise Amplifier                      |

| MEMS                   | Microelectromechanical System            |

| MIM                    | Metal-Insulator-Metal                    |

| MMIC                   | Monolithic Microwave Integrated Circuits |

| mm-Wave                | Millimeter-wave                          |

| MOS                    | Metal-Oxide-Semiconductor                |

| PCB                    | Printed Circuit Board                    |

| PA                     | Power Amplifier                          |

| $\mathbf{PAE}$         | Power-Added-Efficiency                   |

| $\mathbf{PS}$          | Phase Shifter                            |

| $\mathbf{Q}$           | Quality Factor                           |

| RADAR                  | Radio Detecting And Ranging              |

| $\mathbf{RF}$          | Radio Frequency                          |

| RX                     | Receiver                                 |

| SiGe                   | Silicon-Germanium                        |

| $SiO_2$                | Silicon Dioxide                          |

| S-MSL                  | Slow-wave Microstrip Transmission Line   |

| SPDT                   | Single-Pole Double-Throw                 |

| T/R                    | Transmit/Receive                         |

| TX                     | Transmitter                              |

| TWT                    | Traveling Wave Tubes                     |

| UWB                    | Ultra Wide Band                          |

| VGA                    | Variable Gain Amplifier                  |

| $V_{GS}$               | Gate-to-Channel Voltage                  |

| WWII                   | World War II                             |

### 1 Introduction

#### 1.1 An Overview of Radar History

The history of the radar, RAdio Detecting and Ranging, systems which can both detect and provide the range information of the potential objectives by using radio waves starts with World War II (WWII). The early radar systems during WWII consisted of fixed antennas driven with high power electro-magnetic devices called magnetrons which were capable of producing high power microwave pulses and determined the echoes reflected from targets [1].

The importance of detection and ranging became indispensable during and after WWII so that radars have gradually evolved into more complex and multi-functional systems since then. During this evolution, first the conventional mechanically steerable antennas with hundreds of scans per minute have been developed to increase the visible area of the radar systems. Eventually the electrically steerable radar systems which were capable of hundreds of scans per second over wide monitoring angles were introduced. These systems are more commonly known as phased arrays or beem-forming arrays [2].

As the radar systems have advanced with the development in phased array technology, so have the application areas. Although radar systems continued to be predominantly used for military and satellite applications, they have also spread into commercial applications such as vehicular collision avoidance [3], weather monitoring [4], and presence detection for smart houses [5]. The spread of the phased arrays has come true with everlasting trend of pushing for smaller, more solid state solutions with an ultimate goal of integrating all the front-end circuits on a single chip [6].

#### **1.2** Phased Array Principle

Phased arrays have been proposed in 1950's and widely used to achieve electronic beam forming and scanning much faster than mechanically steerable systems [7– 9]. Phased arrays can be used either on the transmitter or receiver side, or in transceivers.

The phased arrays consist of thousands of antenna elements spaced at the frac-

Figure 1: Phased array system with 8 antenna elements

tional wavelength of the operation in typically two dimensions to steer overall antenna beam electronically. The amplitude and phase of the signals feeding each element are varied so that the effective radiation pattern and gain of the array is reinforced in a desired direction and suppressed in other directions [10]. This property of phased arrays is widely used for addressing the emerging requirements of military radar systems for detecting incoming airplanes or missiles and satellite communications. On the transmitter side, phased array focuses the beam at a desired direction while on the receiver side focuses on the desired signal while alleviating interferences from other directions.

Fig. 1 shows a basic concept of phased arrays with linearly arranged 8 antenna elements. In this system, the length of the transmission lines can be arranged so that the phase introduced by them is equal to multiple of  $2\pi$  to provide a progressive phase difference of  $\Phi$  between antennas. Another way of doing this is compensating

Figure 2: Normalized array factor of a 8-element phased array with three different antenna spacing

for phase differences introduced by the antenna feeds in T/R module. In a linear array similar to shown in Fig. 1, in receive mode, the phase difference between signals that arrive in adjacent antenna elements is given by

$$\phi_{\Delta} = \frac{2\pi}{\lambda} d\sin\theta \tag{1}$$

where  $\lambda$  is the wavelength, d is the spacing between antennas, and  $\theta$  is the incidence angle. When a progressive phase difference of  $\Phi$  is introduced at antenna elements by phase shifters in T/R modules, the direction of antenna beam can be changed to

$$\theta = \sin^{-1} \frac{\lambda}{2\pi d} \Phi \tag{2}$$

The radiation pattern of an antenna array, as can be seen on the left side in Fig. 1, is given by the multiplication of a single antenna element pattern with a factor which is known as array factor (AF) [11]. The normalized array factor of a progressively excited, equally spaced linear array is calculated as

$$f(\psi) = \frac{\sin(N\psi/2)}{N\sin(\psi/2)} \tag{3}$$

where  $\psi$  is  $\beta dsin \theta + \Phi$ . Fig. 2 shows the normalized array factor of a 8-element

phased array with different antenna spacing. As can be seen, increasing the spacing between antenna elements decreases the main beam width and thus improves the performance of the array. However, increasing spacing more than  $\lambda/2$  may introduce grating lobes which makes system more vulnerable to interference from other directions. Therefore, it is common practice to set the spacing between antenna elements to  $\lambda/2$  to achieve a high directivity without creating any grating lobes.

Phased arrays do not only steer the radiation pattern electronically and suppress the interferences from other directions, they also improve the overall signal-to-noise (SNR) at the output of the receiver and hence provides better sensitivity at the receiver [12]. This merit of the phased arrays arises from the fact that signals from the antenna add coherently while the noise generated in each receive path adds incoherently, given that the distance between successive antennas is large enough [13], [14]. On the transmitter side, the coherent addition of the signals increases the radiated power in the main beam direction while creating less interference to nearby communication channels. Hence, assuming an n-element phased array transmitter where each element is radiating  $P_e$  watts omni directionally, in the main beam direction the Effective Isotropic Radiated Power (EIRP) will be  $n^2 P_e$  watts or  $P_e(dBm)+20\log(n)$  dBm. Considering the 8-element phased array in Fig. 1, if each antenna is radiating 20 dBm, the EIRP is 20+18 dBm. This merit of the phased arrays is really beneficial at microwave/mm-wave frequencies, especially in silicon-based technologies since the output power of power amplifiers is limited due to the low breakdown voltages of the devices and lossy substrates. On the receiver side, the combined signal output is given by

$$S_{out} = n^2 G S_{in} \tag{4}$$

where n is the number of antenna elements, G is the total gain in a single receive path and  $S_{in}$  is the input signal. Assuming that antenna noise in different receive paths are uncorrelated, total noise power at the output is given by

$$N_{out-array} = n(N_i + N_{added})G \tag{5}$$

where  $N_i$  is the input noise from feeding antenna and  $N_{added}$  is the noise power added

by the receiver network. SNR at the output is given by

$$SNR_{out-array} = \frac{S_{out-array}}{N_{out-array}} = \frac{nS_{in}}{N_i + N_{added}}$$

(6)

For a single receiver channel the signal and the noise power at the output would be

$$S_{out} = GS_{in} \tag{7}$$

$$N_{out} = (N_i + N_{added})G\tag{8}$$

Thus signal-to-noise ratio at the output of a single receiver would be

$$SNR_{out} = \frac{S_{out}}{N_{out}} = \frac{S_{in}}{N_i + N_{added}}$$

(9)

Eventually dividing (6) by (9) it is found that an n-element phased array can improve the SNR at the output of the receiver by  $10\log(n)$  dB. For instance, in an 8-element phased array SNR can be improved by  $10\log(8)=9$  dB. A better SNR results in several improvements in radar such as rapid beam forming, accurate target location and ability to perform multiple functions at the same frequency [15].

#### **1.3** Phased Array Systems

Phased array systems can be divided into two main types according to how the antenna elements are driven; passive phased arrays and active phase arrays. The block diagram of a passive phased array radar is shown in Fig. 3. As can be seen, passive phased array radars drive multiple antennas, a sub array of phase shifters and antennas, on transmit mode using high-power tubes such as magnetrons, Traveling Wave Tubes (TWT), Klystrons and Gyrotrons. Similarly, in the receive mode, multiple phase shifters drive a single high performance LNA. The passive phased arrays were early detection system of choice for military applications such as scanning rapidly for single or multiple enemy targets, assisting with missile defense and guidance systems [16]. The most eminent ground based passive phased array radar is Patriot that is widely used during the Gulf War in 1990s [17]. Unlike passive systems, in active phased array radars each antenna element has its own dedicated solid state transmit/receive module as shown in Fig. 4. Photos of a passive and

Figure 3: Simple block diagram of a passive phased array radar.

active phased array radars is shown in Fig. 5. Both passive and active phased array radars has several advantages like offering excellent beam agility, mechanical reliability due to lacking moving parts and smaller radar cross section over the conventional mechanically steerable radars [18].

An active phased arrays offers several advantages over passive arrays so that they are usually more favorable. As can be seen in Fig. 3, in passive phased array phase shifter, which is typically lossy due to implementation by passive components, comes right after antenna and degrades the overall noise figure of the system in receive mode [19]. Similarly, phase shifter comes after power amplifier and right before the radiating element in transmit mode and this increases the transmit loss and in return degrades the transmit efficiency of the overall system. Conversely, active phased arrays, offer inherently lower overall system noise figures since a low noise amplifier comes right after antenna along with a low loss T/R switch. Furthermore, in passive phase arrays, performance requirements for phase shifters are more stringent compared to active phased arrays since they should be able to handle relatively high transmit signals coming from power amplifier. In addition, passive systems are

Figure 4: Simple block diagram of an active phased array radar.

more vulnerable from the reliability standpoint since a sub array of antenna element would be directly affected by a failure in PA or LNA. For instance, in Patriot a sub array of 16 antenna elements are driven by a single PA and LNA and a failure in either amplifier would take out the contributions from 16 antenna elements [20]. Contrary to Patriot, Terminal High Altitude Area Defense (THAAD) system is comprised of five times more radiating elements [21], but each antenna element has its own dedicated solid state T/R module. Therefore, a failure in either PA or LNA would has an effect on only a single antenna in contrary to sixteen antennas of Patriot and in return reliability of the overall system is improved. The active phased array architecture, also relaxes the required output power per amplifier as well as power handling requirement of the phase shifters by driving only a single antenna rather than being distributed over multiple radiating elements. Thus, high power tube devices with hundreds of kilowatts output power in passive arrays are no longer required and actually are replaced by relatively lower power monolithic microwave integrated circuits (MMIC) in the T/R modules of active arrays. Table 1 summarizes the pros and cons of the radar architectures.

Fig. 6 shows a simple block diagram of a typical T/R module in active phased

Figure 5: Photograph of a passive and active phased array radar

Figure 6: Simple block diagram of a solid state T/R Module

|      | Dish Antenna            | Passive Phased Array   | Active Phased Array   |  |

|------|-------------------------|------------------------|-----------------------|--|

|      | (mechanical steering)   |                        |                       |  |

|      | Very low cost           | Beam agility           | Highest performance   |  |

| Pros | Frequency diversity     | Effective resource     | Effective resource    |  |

|      |                         | management             | management            |  |

|      |                         |                        | Low distribution loss |  |

|      | Slow scan rate          | High distribution loss |                       |  |

| Cons | High distribution loss  | Higher cost            | Highest cost          |  |

|      | Single point of failure | Moderate reliability   |                       |  |

Table 1: Comparison of the Radar Architectures.

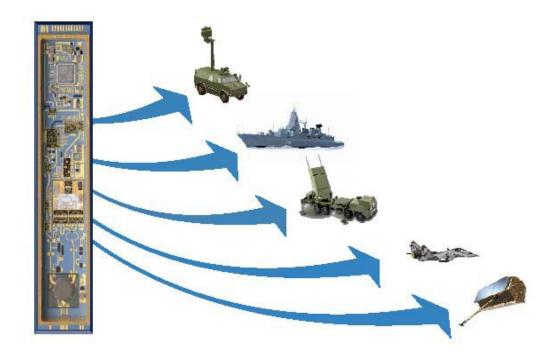

array radars which consist of a T/R switch or a circulator, an LNA, a PA, an SPDT switch and a phased shifter. The performances of the current, active, phased array radar systems are mainly determined by the performance of transmit/receive (T/R) modules. The current T/R modules have typically been implemented using GaAsand InP-based discrete monolithic microwave integrated circuits (MMIC), especially at X-Band and higher frequencies. Fig. 7 shows an example of such a module based

Figure 7: A III-V based T/R Module in different platforms [23].

on assembling III-V MMICs in different platforms. These III-V technologies completely meet high speed performance, especially lower noise, requirements of the present phased array radars. However, the extremely good performance of III-V compound semiconductors comes at the expense of relatively higher manufacturing cost, higher power consumption and lower integration density, resulting in higher deployment and operational expenses for X-Band phased array radars [22]. Therefore, low-cost, weight, size and highly integrated T/R modules for future phased array radar systems are required to decrease all these expenses.

#### 1.4 Downsizing of T/R Modules

The performance of phased array radar systems are determined by using several figure-of-merits for search, track and track accuracy. Among these, the maximum range  $R_{MAX}$  in which a radar system can successfully detect and track a target is the fundamental FOM for radar systems.  $R_{MAX}$  can be calculated as

$$R_{MAX} = \left(\frac{P_t G A_e \sigma}{(4\pi)^2 S_{min}}\right)^{1/4} \tag{10}$$

where  $P_t$  is the transmitted power, G is the transmitting gain,  $A_e$  is the aperture, effective area, of the antenna,  $S_{min}$  is the minimum detectable signal, and  $\sigma$  is the radar cross section of the target [15]. The power-aperture-gain product for track, is another figure-of-merit which is widely used to evaluate the performance of the radar systems and can be expressed as

$$FOM_{track} = P_t A_e G \tag{11}$$

As can be seen from (10) and (11), once the operation frequency of the phased array is specified, a given system performance can only be achieved by changing the radiated power, sensitivity of the system and effective aperture area. In active phased array radars, the power, effective aperture area and the transmitting gain of the entire array can be redefined in terms of individual antenna element parameters as [24]

$$P = P_e N \tag{12}$$

$$Ae = A_{es}N\tag{13}$$

$$G = G_e N \approx \frac{4\pi A_e}{\lambda^2} N \tag{14}$$

where  $P_e$  is the radiated power per element,  $A_{es}$  is the equivalent area of a single antenna element,  $G_e$  is the gain of a single antenna element,  $\lambda$  is the wavelength of the frequency of operation and N is the number of antenna elements in the phased array. The track FOM for an active phased array can then be expressed as

$$FOM_{track} = \frac{4\pi P_t A_e^2}{\lambda^2} \approx N^3 \frac{4\pi P_e A_{es}^2}{\lambda^2}$$

(15)

Hence, improvements in the active phased arrays can be achieved by either increasing the radiated power per element  $P_e$ , aperture of a single element  $A_{es}$ , or the number of antenna elements N. Increasing  $P_e$  and  $A_e$  provides a linear and squared increase in the track figure of merit, respectively. However, increasing radiated power per element will increase the heat generation and require better cooling systems which in return increase the deployment and operational expenses of the radar. Similarly, increasing the elemental aperture is not an attractive approach since it may degrade the steering ability of the phased array by introducing grating

Figure 8: Output power per radiating element and total DC power required for all of the T/R modules versus number of elements for a fixed power-aperture-gain product [24].

lobes.

On the other hand, increasing number of antenna elements, T/R modules, provides a cubic improvement in the track figure of merit. Additionally, for a given power-aperture-gain product the radiated power per element  $P_e$  can be reduced drastically, at the expense of a modest increase in the number of radiating elements N [24]. However,  $P_e$  can not be decreased to an arbitrarily small value as can be seen in Fig. 8 and a radiated power of 0.4-0.5 Watts per element is optimal. This reduction in elemental power will also allow a lower DC power for the complete system, as seen in Fig. 8. Another benefit is decreasing deployment and operational expenses by the reduction in raw materials and equipments needed to transport, power and cool the system. Based on this concept, moving toward a low-power density radar system which includes tens of thousands of single-chip T/R modules (costing < \$ 10 each) can significantly reduce the cost of the next generation phased array radars [25].

To implement this new low-power density radar systems, a lower-cost technology with higher integration potential capabilities are needed to be used for the T/Rmodule design. The current T/R modules need relatively high output powers (>5W) so that they require a III-V solution. However, a SiGe BiCMOS is a more viable and cost-effective solution for next generation low-power density T/R modules than III-V Technologies for increasing cost savings and integration capabilities.

#### 1.5 SiGe HBT Technology

With the recent advancements in SiGe heterojunction bipolar transistor (HBT) technology, it is possible to implement low-cost microwave and mm-wave systems on a single chip. Although the idea of using SiGe alloys to practice bandgap engineering in silicon dates back to the 1960's, the first functional SiGe HBT was demonstrated only twenty five years ago [26]. Since the first SiGe HBT demonstration, SiGe HBT technology has shown an incredible improvement in terms of performance.

In SiGe HBT technology, Ge which has a smaller bandgap of 0.66 eV compared to that of Si, 1.12 eV, is introduced into the base of transistor to tailor the device performance. The introduction of Ge results in improvements in main performance parameters of the transistor such as current gain ( $\beta$ ), base transit time ( $\tau_b$ ), cutoff frequency ( $f_T$ ) and maximum oscillation frequency ( $f_{max}$ ) which foster high frequency operation. The improvements are better illustrated on an energy band diagram of a typical SiGe HBT. As seen in Fig. 9, in a typical SiGe HBT, the Ge content is not constant but linearly graded from emitter-base (EB) junction to collector-base junction and thus induces a decreasing bandgap in the direction of electron flow. The content of Ge at EB junction lowers the potential barrier and in return increases the electron injection into the base exponentially for a given applied base-emitter voltage ( $V_{BE}$ ). Hence a higher current gain,  $\beta$  is achieved.

The unity gain frequency  $(f_T)$ , which is defined as the maximum frequency at which the transistor demonstrates unity current gain, is the most common figure of merit for comparing the transistors and given by [27]

$$\frac{1}{2\pi f_T} \approx \frac{kT}{qI_E} (C_{EB} + C_{CB}) + R_C C_{CB} + \tau_B + \tau_C \tag{16}$$

where  $C_{EB}$  is the emitter-base capacitance,  $C_{CB}$  is the collector-base capacitance,  $R_C$  is the collector resistance,  $\tau_B$  and  $\tau_C$  are the base transit time and collector transit time, respectively. The grading of Ge across the base of SiGe HBTs, bends the energy diagram as shown in Fig. 9 and this generates a field in the opposite

**Figure 9:** Ge concentration (bottom) and band structure (top) of a SiGe HBT. The Ge provides a lower barrier to injection from emitter to base as well as an accelerating field through the base.

direction of electron flow. Thus, the electrons are accelerated across the device, thereby the base transit time  $\tau_B$  is reduced and in return  $f_T$  and  $f_{max}$  are improved. In addition, HBTs have been scaled vertically and laterally to lower dimensions to improve  $f_T$  and  $f_{max}$  further by reducing the parasitics, especially base, emitter and collector resistances and total collector-base capacitance. Recently the record setting transistors in SiGe with  $f_T/f_{max}$  of 300/500 GHz at room temperature has been reported [28].

The most remarkable advantage of the SiGe HBT BiCMOS technology is that it provides a performance competitive with III-V devices for microwave and mmwave applications, while preserving the yield, cost and manufacturing advantages associated with conventional Si CMOS fabrication. Therefore, in SiGe technology digital circuits with CMOS transistors can be easily integrated with RF building blocks. This advantage over III-V technologies makes SiGe HBT technology a more viable and cost effective solution for system-on-chip integration of T/R modules than the III-V technologies used today. In brief, SiGe BiCMOS is a low-cost technology with high integration capabilities and with the recent advances, it has shown the potential to be utilized for the next generation low-cost, small size, light weight, low-power density X-Band phased array radars.

#### 1.6 Previously Proposed T/R Module

#### 1.6.1 Building Blocks and Specifications

Fig. 10 presents the system block diagram of the X-Band SiGe BiCMOS T/R module proposed last year in the context of a master dissertation [29]. The T/R module is based on the all-RF system architecture in where phase shifting is performed at RF frequencies. It consists of a T/R switch, two single-pole double-throw (SPDT) switches, a power amplifier (PA), a low noise amplifier (LNA), a phase shifter and a variable gain amplifier (VGA). The signal amplification blocks such as LNA, VGA, PA are designed using HBTs while T/R and SPDT switches are designed using CMOS transistors in IHP 0.25  $\mu$ m SiGe BiCMOS technology. In this module, the phase shifter is shared for both the receiving and transmitting paths through SPDT switches. Thus, in this architecture, there is no need to use a bidirectional phase and magnitude control circuit and thus a VGA can be employed right after a passive phase shifter as shown in Fig. 10 to compensate the signal losses for different phase states of the T/R module.

In this section the function of each building block will be summarized while explaining how the specifications shown in Fig. 10 are determined. Firstly, the power amplifier is the main block which directly affects the performance of the complete T/R module in transmit mode. As discussed before, 0.4-0.5 W output power per element is optimum to build next generation active phased arrays with an increase in the number of elements. This correlates to a minimum radiated power of 26 dBm from each antenna. In practice, most antennas used in phased arrays provide about 6 dB gain. Thereby, assuming 6 dB antenna gain and a 2 dB insertion loss for the T/R switch in transmit mode, a output power higher than 22 dBm is required for the power amplifier. A two-stage, high gain power amplifier which can fulfill this requirement was reported last year and its performance will be briefly summarized in the next subsection.

In receive mode, low-noise amplifier is one of the most important building blocks of the T/R module. It has a direct impact on the noise performance and in return

Figure 10: SiGe X-Band T/R module system block diagram. The highlighted blocks are the main focus of this thesis.

on the sensitivity of the T/R module. Considering the state of the art performances reported in the literature an overall noise figure around 5 dB is aimed for the module. Assuming a 2 dB insertion loss for the T/R switches, a noise figure lower than 2 dB is required to be able to achieve a state-of-the-art performance for the T/R module. Additionally, low noise amplifier require a high gain to suppress the noise contributions of the consecutive stages, especially from the lossy phase shifter. However, linearity, input referred third order intercept point ( $IIP_3$ ) of the T/R module deteriorates with increasing gain in first stages. Therefore a minimum 20 dB gain and -10 dBm  $IIP_3$  are aimed to reduce to noise added by later stages significantly without degrading the linearity of the module. These are clearly challenging performance specifications to achieve simultaneously in SiGe BiCMOS technology.

In a typical T/R module, primary aims are to direct high power RF signal from transmitter to antenna while preventing leakage of that large signal into more sensitive front-end of receiver and to provide a low loss path between TX/ANT, in particular between ANT/RX ports. Therefore, the T/R switch should provide a low loss and a high isolation between TX and RX paths, as well as handling high power output signals of power amplifier during transmit mode of operation. The power handling capability of a T/R switch is defined as the input referred 1dB compression point of the switch. It should be at least equal to output referred 1dB compression point of the PA, minimal 22 dBm. Additionally, an insertion loss lower than 2 dB is required to be able to satisfy the overall noise figure specification of the T/R module in receive mode. Considering the  $IIP_3$  specification of the LNA, the isolation of the T/R switch should be higher than 35 dB, higher than 40 dB is favorable, to be able to reduce the leakage signal level from PA to LNA which can saturate the LNA.

The function of the SPDT switches is similar to T/R switch; routing signal to two different terminals depending on the control voltage. The figures of merit of the SPDT switch are similar to the T/R switch. However, the isolation and power handling capability requirements of the SPDT switches are less stringent since they are located before the power amplifier and do not experience high power signals. Therefore, in the SPDT switch design the main aim will be to minimize the insertion loss while occupying a small die area.

The phase shifter is the most essential building block of a T/R module for the scanning functionality of the phased array systems. The resolution of phase shifter determines side-lobe, grating-lobe and main-lobe levels as well as scanning array of the array. The phase shifter is located after the LNA in the receive path and should have a high  $IIP_3$  not to degrade the overall linearity of the T/R module. Therefore, a passive 4-bit phase shifter with 22.5° phase resolution is chosen. The phase shifter can be easily controlled with MOS switches without any DC power consumption, theoretically. Using 4-bit phase shifters, phased arrays can steer main beam almost continuously with a negligible variation in array gain or sidelobe levels [30].

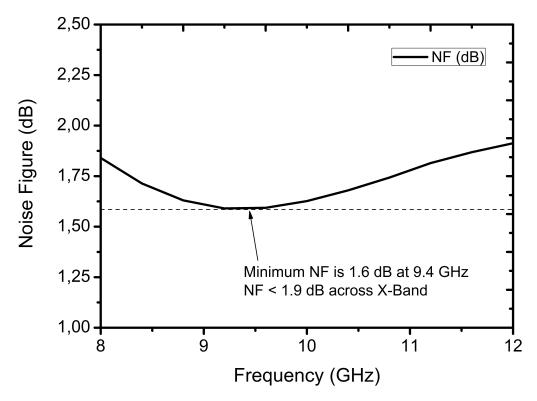

Up to now, a two stage PA, a SPDT switch, a high performance LNA, a switched LNA and two different types of T/R switches have been designed and their performances have been verified with measurements. The two-stage PA was reported in detail last year in the context of a master dissertation [29]. In the next section, its performance will be briefly given. The other blocks except phase shifter are the main focus of this dissertation and will be covered in detail in the following chapters.

Figure 11: Schematic of the designed two-stage power amplifier.

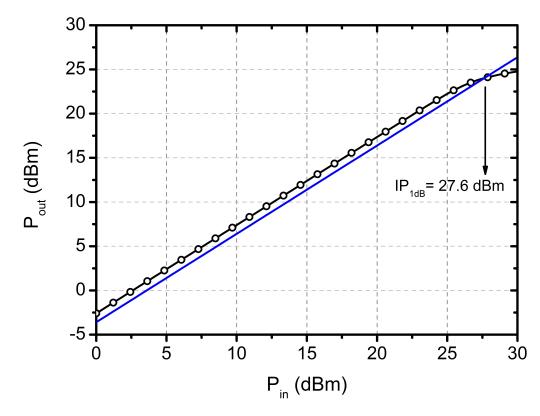

#### 1.6.2 Power Amplifier

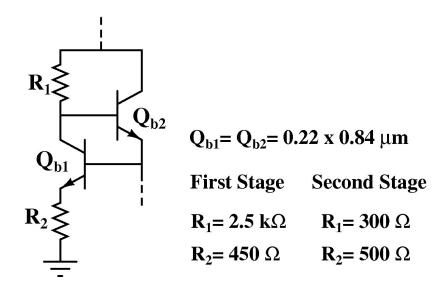

A linear two-stage single-ended PA is designed using SiGe HBTs as shown in Fig. 11 [31]. Both stages are based on cascode topology to overcome the technology's 2.5 V  $BV_{CEO}$  breakdown voltage by presenting low impedance at the base terminal of the cascode transistors. In each stage, fastest HBTs in the process are used for the common emitter part and medium voltage and speed transistors are used for the common base part. Moreover, active bias networks are used to enhance the linearity of the PA effectively [32]. To improve the stability of the PA,  $C_3$  and  $C_4$  coupling capacitors are shunted with a series RC network to introduce resistive loss at low frequencies.

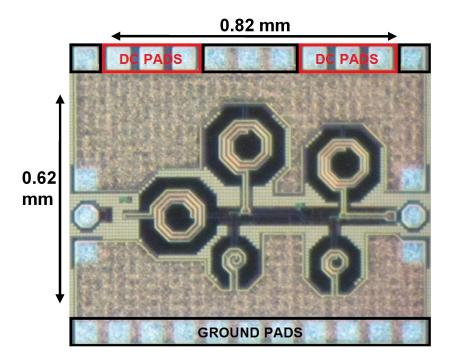

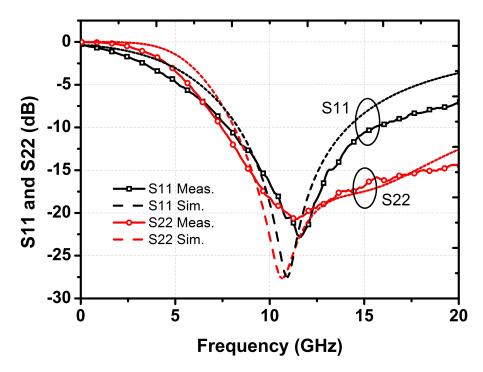

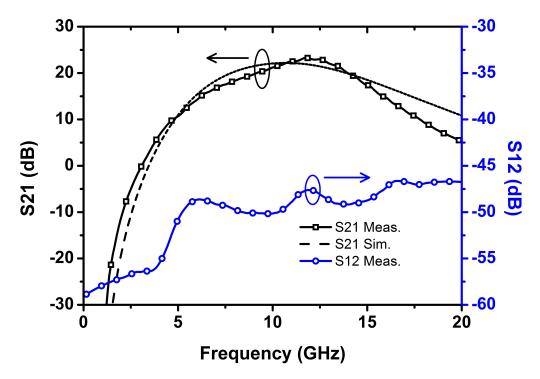

The PA occupies 0.6  $mm^2$  chip area without pads. Biased at Class-A mode, the PA resulted in peak small-signal gain of 25.5 dB as shown in Fig. 12.  $S_{11}$  is better than 10 dB at X-Band while  $S_{22}$  is better than 10 dB in a 2 GHz bandwidth. The measured saturated output power is more than 23 dBm, and more than 20 dBm linear output power is achieved in a 4 GHz bandwidth (Fig. 13). While operating at  $P_{1dB}$  output power the PA draws 100 mA from 4 V supply, and achieves a peak PAE of 28 %, and more than 25 % PAE in a 3 GHz bandwidth centered at 9 GHz.

Figure 12: Measured small-signal gain and return loss of the two-stage power amplifier.

Figure 13: Measured saturated output power and the output referred  $P_{1dB}$ .

#### 1.7 Motivation

As discussed in the previous sections, the cost, size, weight, power consumption and complexity of the current phased array T/R modules restrict this technology only to certain military and satellite applications which can tolerate these limitations. The significant spread of phased arrays in next generation military and satellite applications as well as commercial markets is only possible by overcoming these technical limitations and reducing the unit cost. Therefore, next generation X- Band phased array radar systems aim to use low cost, fully integrated T/R modules to overcome these hurdles. Considering the high frequency and digital capabilities, SiGe HBT BiCMOS technology can be an excellent candidate for this purpose.

Therefore, the objective of this thesis is to replace III-V T/R module components with high performance SiGe BiCMOS front-end circuits for building next generation X-Band phased array radar systems. For this purpose, high speed circuits which can satisfy the demanding requirements of the next generation T/R modules are implemented in IHP 0.25  $\mu$ m SiGe BiCMOS technology. This dissertation aims to present unique T/R module front-end circuits based on new approaches and techniques.

#### **1.8** Organization

Chapter II presents the design of a highly linear CMOS series-shunt T/R switch, a slow-wave transmission line based T/R switch and a DC-20 GHz SPDT switch, primarily optimized at X-Band, in 0.25- $\mu$ m SiGe BiCMOS process for a fully integrated active phased array T/R module. The series-shunt T/R switch resulted in a measured IL of 3.6 dB, isolation of 34.8 dB and  $IP_{1dB}$  of 28.2 dBm at 10 GHz. This switch achieves the highest power handling capability among the single-ended CMOS X-Band switches, to the best of our knowledge, attributed to the unique design methodologies and techniques. The slow-wave T/R switch was implemented using shunt NMOS transistors and slow-wave quarter wavelength transmission lines. It presents the utilization of slow-wave transmissions lines in T/R switches for the first time in any BiCMOS technology to the date. The SPDT switch resulted in a measured insertion loss of 0.5-3.1 dB, isolation of 55-21 dB and  $IP_{1dB}$  of 16-17.3 dBm from DC to 20 GHz. It is a successful demonstration of the full integration of ultra-wideband SPDT switches in CMOS process.

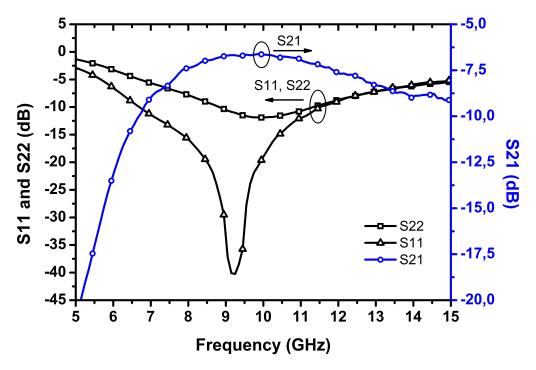

Chapter III presents the design of a high performance two-stage and a switched LNA at X-Band in 0.25- $\mu$ m SiGe BiCMOS process. The high performance LNA is composed of two cascode stages using SiGe HBTs to achieve low noise figure, high gain and a better matching to 50  $\Omega$  at the input and output, simultaneously. First stage is designed for low noise performance while the second stage is optimized to improve the  $IIP_3$ . The LNA resulted in a measured gain of 21 dB, a noise figure

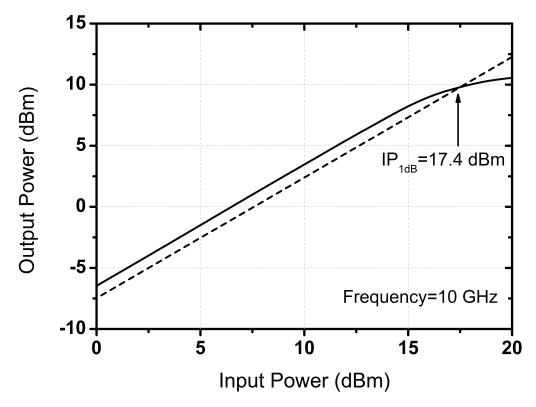

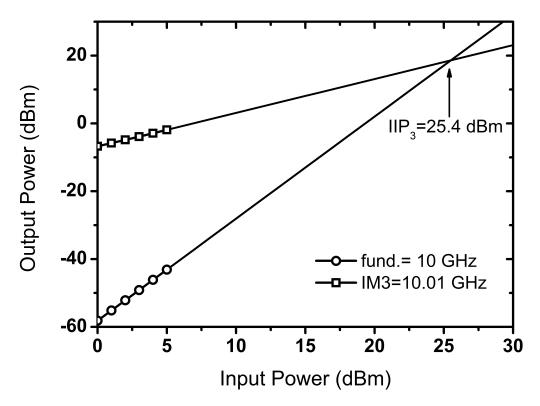

of 1.52 dB and an input third-order intercept point of -8 dBm at 10 GHz. These performance parameters collectively constitute the best Figure-of-Merit reported in similar technologies. The switched LNA is based on single stage bipolar cascode topology and the switching circuitry is designed by a series isolated NMOS switch. In gain mode, the switched LNA achieves a NF of 1.6-1.9 dB, a gain of 9.5-11.5 dB and an input-referred  $P_{1dB}$  of -6 dBm with 18.6 mW power consumption. In bypass mode, the switched LNA resulted in a measured insertion loss of 6 dB and an input-referred  $P_{1dB}$  of 17.4 dBm at 10 GHz. To the best of author's knowledge, this is the first SiGe switched LNA reported at X-band. Furthermore, the resistive body floating technique is incorporated in switched LNA design, for the first time, to improve the linearity of the circuit in bypass mode.

Chapter IV shows the integration of a complete X-Band SiGe BiCMOS T/R module using separately designed 50  $\Omega$  building blocks presented. 50  $\Omega$  microstrip lines are implemented in the BEOL of the process to connect the building blocks together. The module does not employ a T/R switch and it is assumed an off-chip circulator, with a lower insertion loss, would be used to improve sensitivity of the system in receive mode.

Chapter V summarizes the contributions of this thesis and concludes the dissertation with a discussion on possible future work.

# 2 RF CMOS Switches for the X-Band SiGe T/R Module

#### 2.1 An X-Band Highly Linear CMOS T/R Switch

#### 2.1.1 Introduction

A major challenge for next generation fully integrated SiGe BiCMOS T/R modules is to implement a high performance CMOS T/R switch which can handle high transmit powers and provide high isolation as well as a low insertion loss. In the literature, several single ended T/R switches implemented in CMOS processes are reported [33–45]. However, none of them is capable of handling relatively high output powers required for viability of SiGe T/R modules, typically higher than 0.4 W at X-Band.

This section presents the design and implementation of a CMOS SPDT T/R switch in 0.25- $\mu$ m GHz SiGe BiCMOS technology for an X-Band, fully integrated T/R module presented in Chapter I. As mentioned before, SPDT T/R switch comes right after the antenna and is a crucial component in a T/R module that routes antenna to either transmitter (TX) or receiver (RX) (Fig. 14). Thereby, it directly affects the transmission efficiency and the receiver noise figure of the system. The T/R switch in this work was designed using techniques to achieve, primarily, the highest  $P_{1dB}$ , without sacrificing IL and isolation. These techniques include resistivebody floating, using on-chip impedance transformation networks (ITN) and DC biasing of all terminals of the T/R switch. In addition, optimization of transistor widths and parallel resonance technique are used to improve insertion loss (IL) and

Figure 14: A simple block diagram of T/R module

isolation, respectively. Section 2.1.2 presents the design of the T/R switch and these tecniques. In Section 2.1.3, layout considerations and the measurement results are presented.

#### 2.1.2 Circuit Design and Analysis

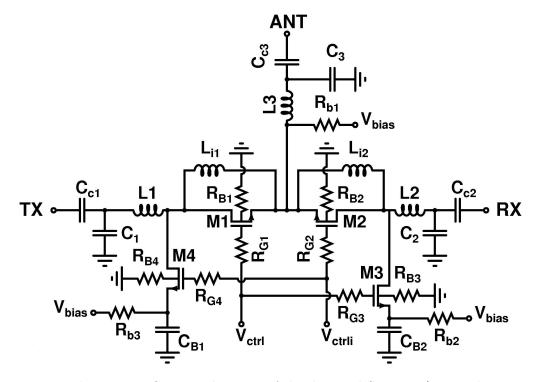

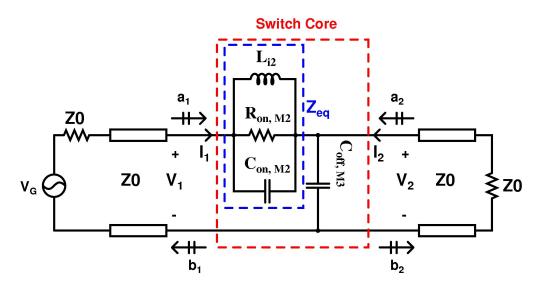

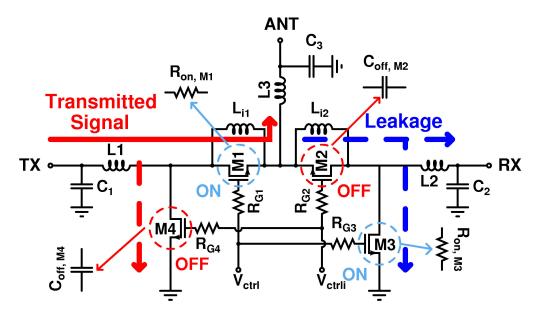

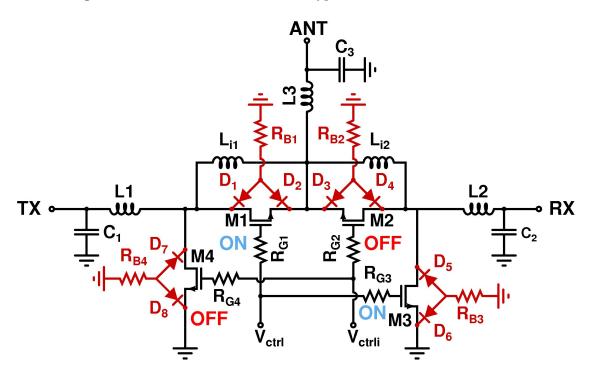

Fig. 15 shows the circuit schematic of the designed X-Band SPDT T/R switch, based on series-shunt topology. M1 and M2 transistors perform the main switching function of directing signal between TX/ANT or ANT/RX ports. M3 and M4 transistors are used to improve isolation between TX and RX ports by grounding the leakage signal. Operation of the switch is as follow: when  $V_{ctrl}$  is high and  $V_{ctrli}$ is low, the switch operates in the transmit mode. In this mode, M1 and M3 operate in deep triode region (ON state) while M2 and M4 operate in cut off region (OFF state). Hence, the channel resistance of M1 is very low, forming a low loss connection between TX and ANT so that incoming signal from transmitter is routed to antenna. Since M2 is operating in cut off region, the channel resistance is very high, isolating RX port from TX and ANT. Also, leakage signal due to parasitic coupling in M2 is directed to ground through low resistance path formed by M3 transistor before reaching receiver end. In receive mode, basic operation of the switch is similar to

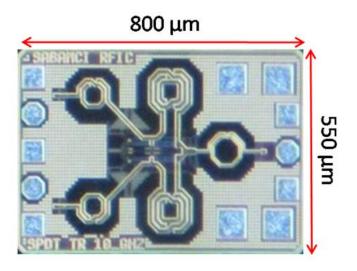

Figure 15: Circuit schematic of the designed SPDT T/R switch.

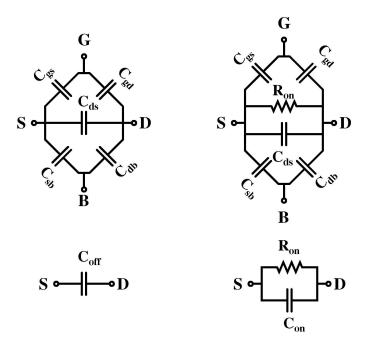

Figure 16: (a) OFF-state Model and (b) ON-state Model of NMOS.

Figure 17: Transmit mode small-signal simplified model.

transmit mode, with an only difference of roles of M1 and M3 are replaced by M2 and M4 transistors, respectively.

In either mode, insertion loss is mainly dominated by the channel resistances of M1 or M2 in the ON state,  $R_{on}$ . Also port matching has a significant effect on insertion loss since IL can be defined as reciprocal of transducer gain. Simplified triode and cut-off models of a MOS transistor with both gate and body floated are shown in Fig. 16. In the receive mode, the circuit in Fig. 15 is reduced to the equivalent circuit in Fig. 17 by using triode and cut-off models of the MOS transistors and by neglecting coupling to transmitter. Based on this approach, the transducer gain of the equivalent circuit can be defined by [42],

Figure 18: Circuit configuration to derive S21 of the ON transistor.

$$G_T = \frac{1 - |\Gamma_s|^2}{|1 - \Gamma_s \Gamma_{in}|^2} |S_{21}|^2 \frac{1 - |\Gamma_L|^2}{|1 - S_{22} \Gamma_L|^2}$$

(17)

$$IL = \frac{1}{G_T} \propto \frac{1}{|S_{21}|^2}$$

(18)

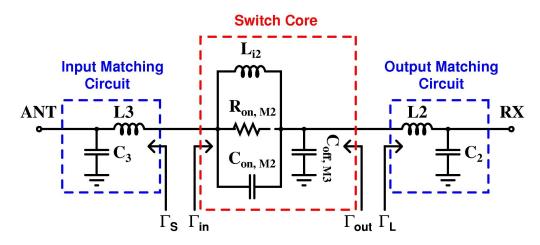

According to (18), insertion loss of the switch is inversely proportional with the  $S_{21}$  parameter of the switching core.  $S_{21}$  of a MOS transistor in the ON state can be calculated by using the configuration in Fig. 18

$$S_{21} = \frac{b_2}{a_1} \bigg|_{a_2=0} = \frac{V_2 - I_2 Z_0}{V_1 + I_1 Z_0} = \frac{2V_2}{I_1(Z_1 + Z_0)}$$

(19)

where  $a_1$  is the incident power wave in port 1,  $b_2$  is the reflected power wave in port 2,  $Z_1$  is the total impedance seen looking into port 1,  $V_n$  and  $I_n$  is the total voltages and currents where the index n refers to port number.

$$S_{21} = \frac{2\left(Z_0 \parallel \frac{1}{j\omega C_{off,M3}}\right)}{Z_0 + Z_{eq} + \left(Z_0 \parallel \frac{1}{j\omega C_{off,M3}}\right)}$$

(20)

$$Z_{eq} = \frac{1}{j\omega C_{on,M2} + \frac{1}{R_{on,M2}} + \frac{1}{j\omega L_{i2}}}$$

(21)

By substituting (20) into (18)

$$IL \propto \left(\frac{Z_0 + Z_{eq} + \left(Z_0 \parallel \frac{1}{j\omega C_{off,M3}}\right)}{2\left(Z_0 \parallel \frac{1}{j\omega C_{off,M3}}\right)}\right)^2$$

(22)

where  $Z_0$  denotes the characteristic impedance of the system and  $R_{on,M2}$  is on resistance of the M2 transistor. Furthermore, by neglecting the  $C_{on,M2}$ ,  $C_{off,M3}$  and  $L_{i2}$  equation (22) simplifies to

$$IL \propto \left(\frac{2Z_0 + R_{on,M2}}{2Z_0}\right)^2 \tag{23}$$

According to equation (23), resistance of the MOS transistor in the ON-state should be lower to decrease insertion loss of the switch. The resistance of a MOS transistor operating in the deep triode region is defined by

$$R_{on} = \frac{1}{\mu_n C_{ox}(\frac{W}{L})(V_{GS} - V_{th})}$$

(24)

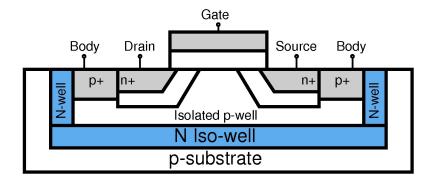

Equation (24) shows that lower  $R_{on}$  can be achieved by using high mobility ( $\mu$ ) transistors, large aspect ratio (W/L) and high gate-to-source/channel voltage ( $V_{GS}$ ). Based on the first criterion, NMOS transistors are chosen to implement T/R switch since mobility of the NMOS transistors is approximately three times higher than the mobility of PMOS transistors in the used technology. Transistors in the ON-state are biased by using 2.5 V gate-to-channel voltage, also the maximum allowed voltage of the used technology to prevent avalanche and gate-oxide breakdown. Additionally, aspect ratio (W/L) is the dominant factor determining the ON-resistance of M1 or M2 and insertion loss in return. As seen in (23) and (24), as the aspect ratio increases, ON-resistance decreases, in return, decreasing insertion loss. In order to achieve a larger aspect ratio, length of the M1 or M2 should be minimized, provided that minimum length limited to 240 nm, while larger widths are used for transistors.

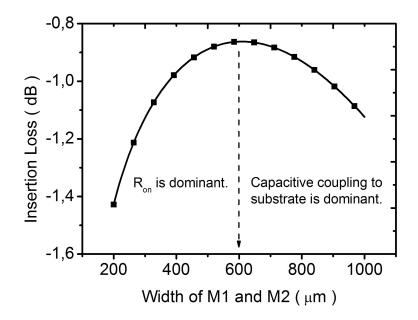

#### 2.1.2.1 Optimization of Transistor Widths

There is a practical limit in increasing transistor width. That is as the width is increased, source/drain to body parasitic capacitances and in return coupling to

Figure 19: Transistor width versus insertion loss of the SPDT T/R switch.

substrate increases. If the width of transistor is extremely increased, signal loss through capacitive coupling to substrate becomes significant and, consequently, insertion loss increases [38]. Increase in the parasitic capacitances also increases the OFF-capacitance of the transistors, leading to more coupling to undesired port and resulting in degradation of isolation. In brief, there is a trade-off between  $R_{on}$  and parasitic capacitance, resulting in an optimum value for the width of the transistor at a given operating frequency. The optimum width for the minimum insertion loss has been found by simulations using Cadence Spectre-RF tool at 10 GHz. Fig. 19 shows the simulation results of insertion loss versus the width of the switching transistors. As can be seen, M1 and M2 should be around 600  $\mu$ m to achieve a minimum insertion loss for 2 V of  $V_{bias}$  and 4.5 V control voltage.

As the frequency increases, the effect of the parasitic capacitances on the isolation becomes significant. Therefore, the use of different techniques to achieve a better isolation, without significantly degrading insertion loss, becomes essential at higher frequencies. One approach to improve isolation is to increase width of shunt transistors to direct leakage signals to ground better in the undesired ports. However, as the width of the transistors increases, parasitic capacitances increase, accordingly. In particular  $C_{db}$  of M3/M4 becomes more important since they are between signal path and substrate. Therefore, coupling of RF signal to substrate and in return insertion loss increase as  $C_{db}$  of M3/M4 increases. Taken into account the trade-off between insertion loss and isolation introduced by shunt transistors, widths of M3/M4 are chosen as 240  $\mu$ m to improve isolation without considerable degradation on insertion loss.

#### 2.1.2.2 DC Biasing

In addition to transistor widths, parasitic capacitances of the transistors and in return insertion loss of the switch are affected by the DC bias of the circuit. Source/drain to body junction capacitances in the MOS model are voltage dependent. As the reverse bias voltage is increased between source/drain-to-body, depletion width in corresponding junctions increases. Since these junction capacitances are inversely proportional with depletion width,  $C_{sb}$  and  $C_{db}$  decrease with increasing reverse bias. Bias dependence of  $C_{sb}$  and  $C_{db}$  can be formulated as [44]

$$C_{sb/db} = \frac{Area.C_{j0}}{\left(1 + \frac{V_{SB/DB}}{V_{0j}}\right)^{m_j}} + \frac{Perimeter.C_{jsw0}}{\left(1 + \frac{V_{SB/DB}}{V_{0jw}}\right)^{m_{jw}}}$$

(25)

where  $V_{SB/DB}$  is the reverse bias voltage across the junction,  $V_{0j}$  and  $V_{0jw}$  are the junction and sidewall built-in potentials,  $C_{j0}$  and  $C_{jsw0}$  are the capacitance value of unit area of bottom junction and unit length of sidewall at zero bias voltage. This equation clearly shows that smaller junction capacitances, thus, reduced coupling of RF signal to substrate for improvement in insertion loss can be obtained by higher  $V_{SB/DB}$ . Additionally, biasing source/drain of the series and shunt transistors improve the power handling capability of the switch. Power handling capability of the SPDT T/R switch, input referred  $P_{1dB}$ , is mostly limited by turn on voltages of the drain/source-to-body junctions of M1/M2 due to large RF signals. DC biasing the sources and drains of M1/M2 increases the turn on voltage of the drain/sourceto-body junctions. When  $V_{SB/DB}$  potential goes below the turn on voltage of the junction during the negative cycle of large input signal, a conduction path between substrate and source/drain would occur. Thus significant portion of the RF signal would be routed to substrate and in return output power would compress. Amplitude of RF input signal, forward biasing source/drain-to-body junctions of M1 and M2 for different DC biases, can be formulated as

$$V_{RF} = V_{bias} + V_{turnon} \approx V_{bias} + 0.5V \tag{26}$$

and corresponding power level for the input

$$P = \frac{V_{RF}^2}{2Z_0} \tag{27}$$

where  $V_{bias}$  is the DC bias applied to source and drain terminals of M1/M2 and  $V_{turnon}$  is the minimum voltage required to turn on source/drain-to-body diodes. These expressions signify that as the DC bias voltage is increased, allowed maximum voltage swing and power handling capability  $(IP_{1dB})$  of the switch increases.

Taking into account of the effects of DC biasing on the insertion loss, power handling capability and power consumption of the switch, all the sources and drain of NMOS transistors are biased by 2 V. The complete biasing method is shown in Fig. 15. The antenna node and sources of the shunt transistors are biased by 2 V through  $R_{b1}$  -  $R_{b3}$  to prevent forward biasing of source/drain-to-body junctions and to decrease voltage dependent parasitic capacitance. The values of  $R_{b1}$  -  $R_{b3}$  should be high enough to prevent leakage into bias port. Otherwise, considerable amount of the RF input signal would be lost due to leakage and thus insertion loss would increase. Additionally,  $C_{B1}$  and  $C_{B2}$  by-pass capacitors are used to bias the source of M3/M4 while introducing RF ground to the sources of M3 and M4. Considering the maximum allowed voltage across four terminal of transistors in this technology, 2.5 V,  $V_{ctrl}$  and  $V_{ctrli}$  has been set to 4.5 V and 0 V for transmit mode and vice versa for receive mode.

The gates of all transistors are biased through large gate resistors  $R_{G1}$ - $R_{G4}$  to make the gates of transistors float at AC signals and prevent signal coupling. The bias resistors allow gate capacitance to keep gate-to-channel voltage constant when different cycles of RF signal arrived. Without these resistors, variation in gate-tochannel voltage ( $V_{GS}$ ) would occur and insertion loss would vary with RF signal at a given frequency [46]. The resistors at the gate of transistors also affect the switching time, defined as the time required for switch to change from transmit mode to receive mode or vice versa. Fast switching time entails low gate resistors to

Figure 20: T/R switch in the transmit mode.