# Real-time DSP-enabled digital subcarrier cross-connect (DSXC) for optical communication networks

Ву

# Tong Xu

Submitted to the graduate degree program in the Electrical Engineering and Computer Science and the Graduate Faculty of the University of Kansas in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

| Chair: Dr. Rongqing Hui |

|-------------------------|

| Dr. Christopher Allen   |

| Dr. Erik Perrins        |

| Dr. Esam Eldin Aly      |

| Dr. Jie Han             |

Date Defended: August 20th, 2019

| The dissertation committee for Tong Xu certifies t version of the following disserta |                         |

|--------------------------------------------------------------------------------------|-------------------------|

|                                                                                      |                         |

| Real-time DSP-enabled digital subcarrier cross-                                      |                         |

| optical communication netwo                                                          | rks                     |

|                                                                                      |                         |

|                                                                                      |                         |

|                                                                                      |                         |

|                                                                                      | Chair: Dr. Rongqing Hui |

|                                                                                      |                         |

Date Approved: August 23<sup>rd</sup>, 2019

#### Abstract

Elastic optical networking (EON) is intended to offer flexible channel wavelength granularity to meet the requirement of high spectral efficiency (SE) in today's optical networks. However, optical cross-connects (OXC) and switches based on optical wavelength division multiplexing (WDM) are not flexible enough due to the coarse bandwidth granularity imposed by optical filtering. Thus, OXC may not meet the requirements of many applications which require finer bandwidth granularities than that carried by an entire wavelength channel.

In order to achieve highly flexible and fine enough bandwidth granularities, electrical digital subcarrier cross-connect (DSXC) can be utilized in EON. As presented in this dissertation, my research work focuses on the investigation and implementation of real-time digital signal processing (DSP) enabled DSXC which can dynamically assign both bandwidth and power to each individual sub-wavelength channel, known as subcarrier. This DSXC is based on digital subcarrier multiplexing (DSCM), which is a frequency division multiplexing (FDM) technique that multiplexes a large number of digitally created subcarriers on each optical wavelength. Compared with OXC based on optical WDM, DSXC based on DSCM has much finer bandwidth granularities and flexibilities for dynamic bandwidth allocation.

Based on a field programmable gate array (FPGA) hardware platform, we have designed and implemented a real-time DSP-enabled DSXC which uses Nyquist FDM as the multiplexing scheme. For the first time, we demonstrated real-time DSP enabled real-time DSXC which uses resampling filters for channel selection and frequency translation. This circuit-based DSXC supports flexible and fine data-rate subcarrier channel granularities, offering a low latency data plane, transparency to modulation formats, and the capability of compensating transmission impairments in the digital domain. The experimentally demonstrated  $\mathbf{8} \times \mathbf{8}$  DSXC makes use of

a Virtex-7 FPGA platform, which supports any-to-any switching of eight subcarrier channels with mixed modulation formats and data rates. Digital resampling filters, which enable frequency selections and translations of multiple subcarrier channels, have much lower DSP complexity and reduced FPGA resources requirements (DSP slices used in FPGA) in comparison to the traditional technique based on I/Q mixing and filtering.

We have also investigated the feasibility of using distributed arithmetic (DA) for real-time DSXC to completely eliminate the usage of DSP slices in FPGA implementation. For the first time, we experimentally demonstrated the implementation of real-time frequency translation and channel selection based on the DA architecture in the same FPGA platform. Compared with resampling filters that leverage multipliers, the DA-based approach eliminates the need of DSP slices in the FPGA implementation and significantly reduces the hardware cost. In addition, with a processing latency that equals to a few clock cycles, a DA-based resampling filter is significantly faster when compared to a conventional direct-structured FIR filter whose overall latency is proportional to the filter order. The DA-based DSXC is, therefore, able to achieve not only the improved spectral efficiency, programmability of multiple orthogonal subcarrier channels, and low hardware resources requirements, but also much reduced cross-connect switching latency when implemented in a real-time DSP hardware platform. This reduced latency can be critically important for time-sensitive applications such as 5G mobile fronthaul, cloud radio access network (C-RAN), cloud-based robot control, tele-surgery and network gaming.

#### Acknowledgments

First of all, I would like to sincerely thank my supervisor, Dr. Rongqing Hui, for supporting me in conducting research on this challenging and interesting topic. Without his support and patient supervision, I wouldn't have been able to overcome the difficulties and make progress in my research.

I would also like to thank Dr. Christopher Allen, Dr. Erik Perrins, Dr. Esam Eldin Aly and Dr. Jie Han, who served as my committee members.

I also want to thank Mr. Robert Young, Mr. Daniel DePardo and Ms. Paulette Place for helping me in setting up the hardware platform.

Thanks to my colleagues and friends Govind Vedala, Mustafa Al-Qadi and Kishanram Kaje for the happy times of discussion and collaboration in our research lab.

Finally, I would like to thank my parents and my sister. I wouldn't have been able to complete my PhD without their support.

## Table of Contents

| List of Figures                                                   | viii |

|-------------------------------------------------------------------|------|

| List of Tables                                                    | X    |

| Chapter 1: Introduction                                           | 1    |

| 1.1 Motivation and background of research                         | 1    |

| 1.2 Digital subcarrier cross-connect (DSXC)                       | 6    |

| 1.3 Digital subcarrier multiplexing techniques                    | 8    |

| 1.4 Overview of proposed work                                     | 11   |

| 1.4.1 Real-time DSP hardware platform                             | 11   |

| 1.4.2 Channel selection and frequency translation in DSXC         | 11   |

| 1.4.3 Implementation of DSXC based on hardware platform           | 12   |

| Chapter 2: Real-time DSP hardware platform                        | 13   |

| 2.1 Hardware Platform                                             | 13   |

| 2.2 Data Interfaces                                               | 16   |

| 2.2.1 JESD204B interface                                          | 17   |

| 2.2.2 Design in Xilinx Vivado                                     | 20   |

| 2.3 Considerations in FPGA Implementation                         | 21   |

| Chapter 3: Real-time DSP-enabled DSXC based on resampling filters | 24   |

| 3.1 Digital subcarrier cross-connect based on FPGA                | 24   |

| 3.2 Frequency translation techniques                              | 26   |

| 3.2.1 I/Q mixing and filtering                                    | 26   |

| 3.2.1 Resampling Filters                                          | 28   |

| 3.3 Resource utilization of frequency translation                 | 36   |

| 3.4 Experiments                                       | 40 |

|-------------------------------------------------------|----|

| 3.5 Conclusion                                        | 47 |

| Chapter 4: DA based real-time DSP-enabled DSXC        | 49 |

| 4.1 Distributed Arithmetic                            | 49 |

| 4.1.1 Principle of DA                                 | 51 |

| 4.1.2 Polyphase decomposition of DA resampling filter | 54 |

| 4.2 Experiment                                        | 58 |

| 4.3 Resource requirement and discussion               | 65 |

| 4.3.1 Resource Utilization                            | 65 |

| 4.3.2 Latency                                         | 70 |

| 4.3.3 Power Consumption                               | 72 |

| 4.4 Conclusion                                        | 72 |

| Chapter 5: Conclusion and Future work                 | 74 |

| 5.1 Conclusion                                        | 74 |

| 5.2 Future work                                       | 74 |

| References                                            | 76 |

| Acronyms                                              | 85 |

| Appendix I                                            | 88 |

## **List of Figures**

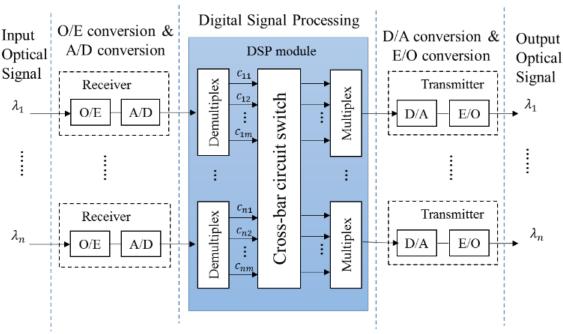

| Figure 1.1 Digital subcarrier cross-connect                                                       |

|---------------------------------------------------------------------------------------------------|

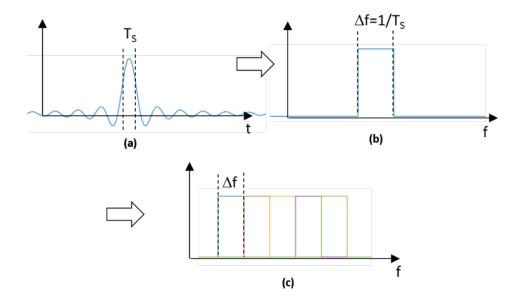

| Figure 1.2 (a) Nyquist pulse in time domain (b) spectrum of a single Nyquist pulse (c) spectrum   |

| of Nyquist FDM9                                                                                   |

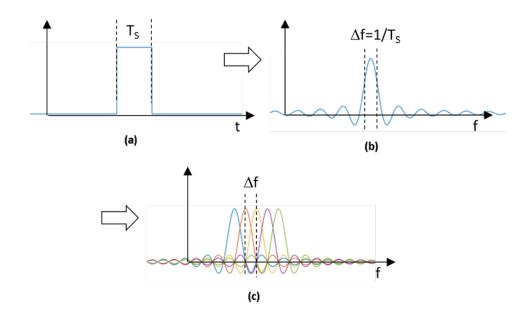

| Figure 1.3 Principle of OFDM (a) single pulse shape (b) spectrum of a single OFDM symbol (c)      |

| spectrum of OFDM                                                                                  |

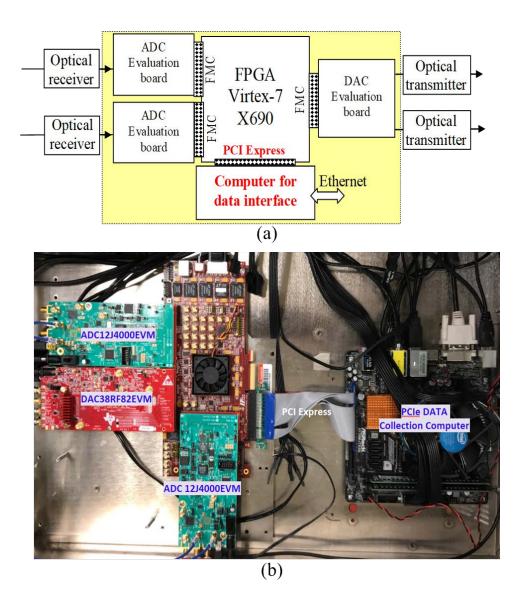

| Figure 2.1 (a) block diagram and (b) photo of DSCM testbed.                                       |

| Figure 2.2 JESD204B standard                                                                      |

| Figure 2.3 Block diagram of real-time Transmitter based on FPGA and DAC18                         |

| Figure 2.4 Block diagram of High-Speed Receiver based on FPGA and ADC20                           |

| Figure 3.1 Block diagram of digital subcarrier cross-connect (DSXC) based on FPGA24               |

| Figure 3.2 Frequency translation through I/Q mixing and filtering                                 |

| Figure 3.3 (a) DDC through BPF and down-sampling, (b) DDC through interpolation BPF, (c)          |

| DUC through up-sampling and BPF, (d) DUC through decimation BPF29                                 |

| Figure 3.4. (a) DFT of $y[n]$ , and (b) DFT of $z[n]$ for down sampling                           |

| Figure 3.5. (a) DFT of $[n]$ , and (b) DFT of $y[n]$ for up-sampling30                            |

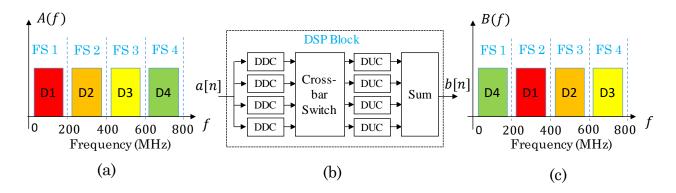

| Figure 3.6 (a) spectrum of a[n], (b) DSP block of DSXC, and (c) spectrum of b[n]37                |

| Figure 3.7 FPGA resource cost of a 4 × 4 DSXC                                                     |

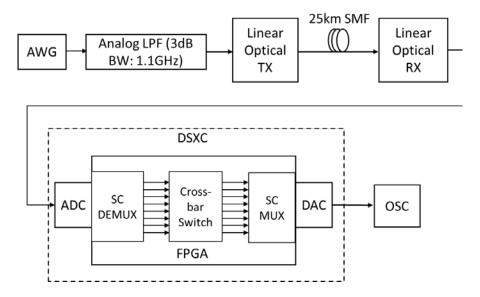

| Figure 3.8 Experimental setup                                                                     |

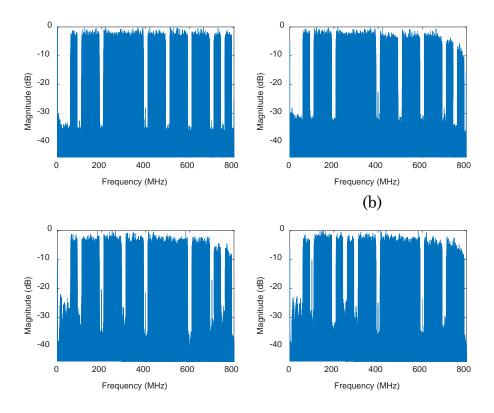

| Figure 3.9 Spectra of output signal: (a) at optical receiver output which is DSXC input (b) after |

| DSP platform but without switching (c) after DSP platform with switching assignment of            |

| DSXC1 (d) after DSP platform with switching assignment of DSXC243                                 |

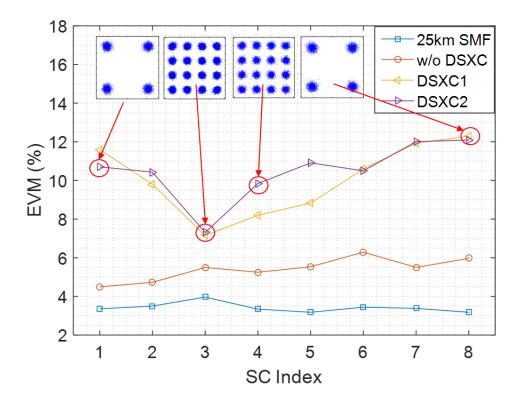

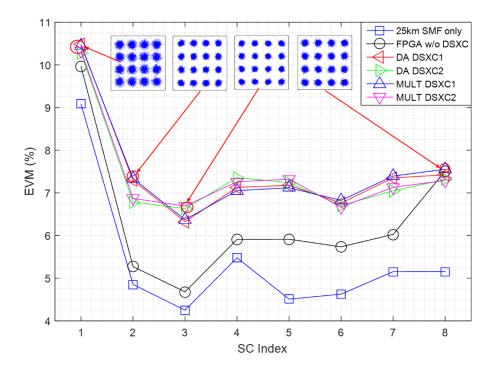

| Figure 3.10. Signal EVM of recovered subcarrier channels                                          |

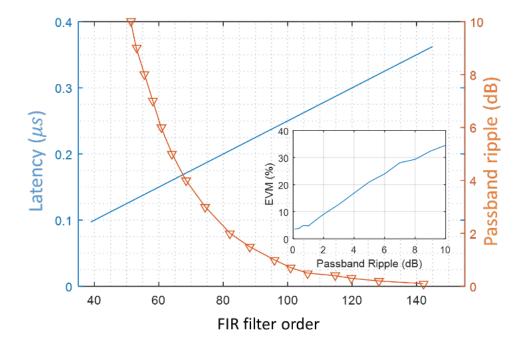

| Figure 3.11 Effects vs FIR filter order                                              | 46        |

|--------------------------------------------------------------------------------------|-----------|

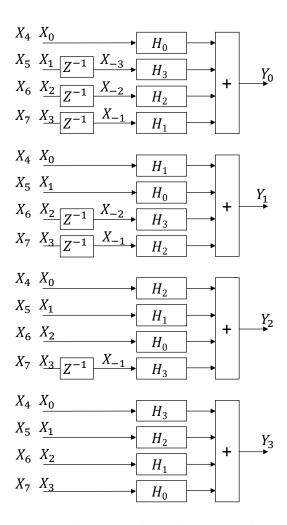

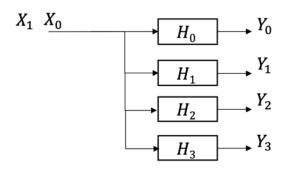

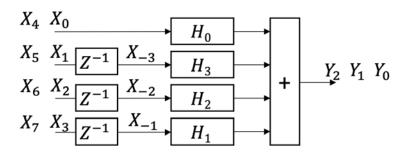

| Figure 4.1 A super sample rate FIR filter with a degree of parallelism of 4          | 56        |

| Figure 4.2 Block diagram of an interpolation FIR filter                              | 57        |

| Figure 4.3 Block diagram of a decimation FIR filter                                  | 57        |

| Figure 4.4 Experimental setup.                                                       | 58        |

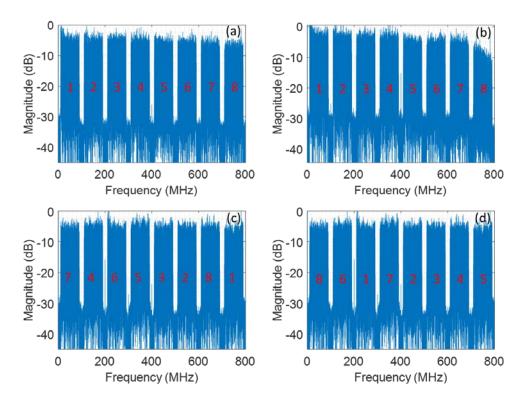

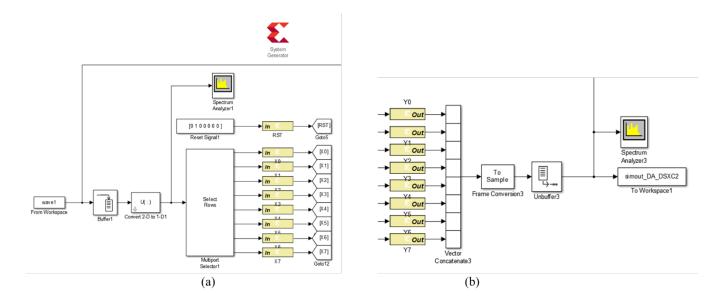

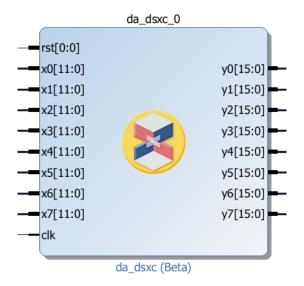

| Figure 4.5 Spectrum of (a) output of optical receiver (b) output of DAC without cros | s-connect |

| switching (c) output of DA-DSXC1 (d) output of DA-DSXC2                              | 60        |

| Figure 4.6 Signal EVM of recovered subcarriers                                       | 61        |

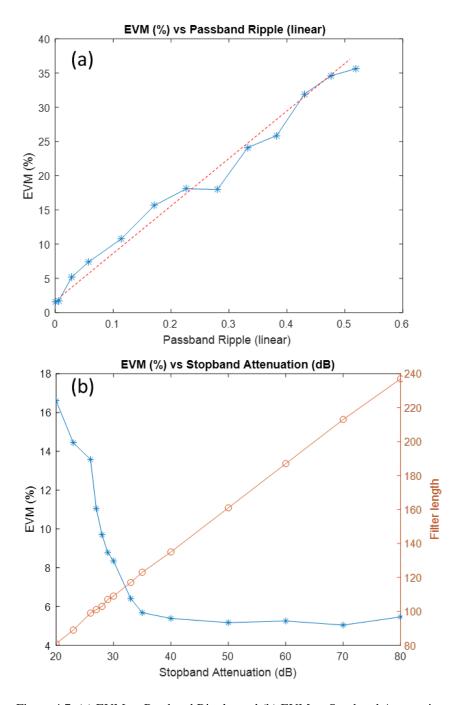

| Figure 4.7 (a) EVM vs Passband Ripple, and (b) EVM vs Stopband Attenuation           | 63        |

## **List of Tables**

| Table 2.1 Available FPGA resources on Virtex 5 and Virtex 7        | .15 |

|--------------------------------------------------------------------|-----|

| Table 2.2 Specifications of ADC12J4000 and DAC38RF82               | .16 |

| Table 2.3 Specifications of Optical Tx and Rx                      | 16  |

| Table 3.1 AWG generated input signal to 8 × 8 DSXC                 | 42  |

| Table 3.2 FPGA resource cost of DSXC.                              | 45  |

| Table 4.1 FPGA resource utilization of DA DSXC IP and MULT DSXC IP | 68  |

| Table 4.2 FPGA resource utilization of DA DSXC and MULT DSXC       | 69  |

#### **Chapter 1: Introduction**

#### 1.1 Motivation and background of research

Due to the ever-increasing data traffic in today's optical networks and the demand for high data rates, improving spectral efficiency (SE) in optical communication systems and networks is of the essence. Compared with a traditional wavelength division multiplexing (WDM) system of fixed 50GHz wavelength grid, elastic optical networking (EON) offers more flexibility, with channel wavelength granularity down to 12.5GHz or lower, which may yield tangible SE improvement in optical networks [1, 2]. Both bandwidth and channel allocation are flexible in EON and can be chosen to best accommodate the modulation formats of choice, transmission distance, system capacity, and number of required channels [3-5]. However, due to the limited spectral selectivity of extant optical filters, further reduction of channel wavelength granularity can prove to be challenging in the optical domain. Yet, many applications could benefit from finer channel bandwidth granularities below 10GHz. Optical domain EON alone may not suffice to achieve the fine bandwidth allocation which may be required in some access and metro area network deployments. For this and other reasons conventional solutions combine the use of optical circuits with electronic packet switching technologies (Ethernet, IP, PON), i.e., multiple connections are multiplexed together by interleaving their data packets in time, thus filling up the relatively large bandwidth of the optical circuit.

Subcarrier multiplexing (SCM) can provide much finer granularity by multiplexing a large number of subcarrier channels in the electrical domain [6, 7]. Subcarrier circuits can be flexibly multiplexed and individually switched electronically, offering dedicated circuits to the application down to MHz of bandwidth. Earlier SCM solutions are analog. While the radio frequency (RF) analog filter solutions offer much better spectral selectivity compared to optical

filters, the transition between passband and stopband in the transfer function of an RF filter still may not be sharp enough to separate closely spaced subcarrier channels. As a result, analog based SCM usually requires sufficiently large spectral guard-bands between adjacent subcarriers, resulting in a suboptimal solution. In addition, the bandwidth and the central frequency of high order RF filters are usually not dynamically adjustable after they are built, and thus analog SCM systems tend to be static and not suitable for dynamic switching.

Thanks to the rapid development of CMOS-based digital electronics, high speed analog to digital converters (ADC), digital to analog converters (DAC) and digital signal processing (DSP) hardware is widely available nowadays [8]. Processing high data rate signals in the digital domain has become practical and offers many advantages compared to traditional analog techniques [9-12]. For example, high order digital filters can be designed to achieve nearly ideal transfer functions, along with dynamically reconfigurable of roll-off rate, bandwidth, and central frequency. Digitally generated and processed subcarrier channels are referred to as digital subcarrier multiplexing (DSCM). DSCM offers a high degree of flexibility because the applied DSP algorithms can be reconfigurable, and yields high spectral efficiency because minimum spectral guard-band is required between adjacent subcarriers. Real-time generation of DSCM signals based on either high order Nyquist filters, or orthogonal frequency division multiplexing (OFDM) has been demonstrated using FPGA platform [13, 14]. DSP-enabled real-time reconfigurable optical add/drop multiplexing (ROADM) technologies have also been demonstrated using FPGA platforms [15, 16]. In addition to being used as a modulation format for optical signal transmission [17], DSCM can also be used to carry orthogonal channel which can be switched individually by digital subcarrier cross-connect (DSXC) devices as introduced in [18, 20]. A DSXC-based network is a circuit switching solution in which subcarrier channels are

individually routed end-to-end to provide dedicated circuits with custom data rates. Compared with optical domain cross-connect (OXC) based on wavelength channels, DSXC in the electronic domain can provide a more flexible and finer data rate granularity, which can help maximize the network spectral efficiency. In comparison with packet based routers, DSXC provides dedicated bandwidth to users without the requirement of packet buffering and forward engine, resulting in a deterministic switching latency [21, 22].

An application example of DSCM is the 5G wireless network fronthaul, which is the network segment between remote radio head (RRH) and central office (CO) [23]. In some solutions common public radio interface (CPRI) is the protocol used in the mobile fronthaul with digital radio over fiber (DRoF) transmitted using on-off keying (OOK). This approach is known to require a relatively high data rate in the fronthaul compared to the radio data rate, due to the sampling of the radio wave and the required high-resolution sampling of ADC and DAC. In DRoF, the received analog wireless waveforms are digitized and encoded into digital bits for transmission. In this analog to digital conversion process, the data rate and thus the bandwidth required for transmission over the fronthaul is scaled roughly by b times higher than the original analog signal bandwidth where b is the bit resolution of the ADC. For example, for 8 channels of 20MHz LTE signals using 40MS/s ADC sampling rate at 15-bit resolution for each I- and Qcomponent of the complex RF waveform, the digital data rate will be approximately 8 × 40 ×  $15 \times 2 = 12,000 \,\mathrm{Mb/s}$  (Reference [24] has more detailed data rate estimation taking into account control words and line coding). Further considering multiple antenna elements for MIMO beam forming, the required data rate can easily reach up to 100Gb/s.

In order to improve the spectral efficiency of the fronthaul, analog radio over fiber (ARoF) has been proposed and actively investigated [25, 26]. Compared with DRoF, ARoF can transmit the

same radio wave using a narrower bandwidth in the fronthaul. Considering that 5G fronthaul is expected to support numerous RRHs, DSCM would be an efficient technology for aggregating and de-aggregating multiple radio waves while offering spectrum flexibility and efficiency at the same time. The DSCM solution would also offer the ability to compensate for transmission impairments in the digital domain [27, 28]. Recently, an ARoF transmission of a multicarrier signal with a carrier frequency of 60GHz, and an aggregation of hundreds of subcarriers to occupy 152MHz of total bandwidth, has been demonstrated experimentally over 25km of single mode fiber (SMF) [29]. In addition, the deployment of DSXC nodes in the fronthaul makes DSCM channel aggregation, de-aggregation and routing dynamically programmable, which would be desirable in a fronthaul connecting multiple RRHs and COs.

For real-time implementation of the DSXC key functions efficient utilization of DSP resources is a major concern. While application-specific integrated circuit (ASIC) is commonly used in commercial communication equipment, FPGA represents a more flexible platform for prototyping and testing the DSP algorithms that are required in DSXC.

We have demonstrated a real-time DSP-enabled DSXC based on resampling digital filters to achieve frequency translation and channel selection of subcarriers [30], as described in Chapter 3. We demonstrated the first implementation of a real-time DSXC node, realizing one of its basic functionalities (switching individual subcarriers in frequency) using digital resampling filters, and experimentally assessing the DSXC node (deterministic) latency to be less than 1µs. This latency is mainly determined by the order of Finite Impulse Response (FIR) filters and the clock period of the digital circuit. Compared to commodity packet switches, DSXC may therefore provide a simple and cost-effective switching solution that achieves zero-jitter even in the presence of high link utilization.

Although these resampling filters reduce DSP resource utilization compared to the traditional frequency translation scheme based on I/Q mixing and filtering, they still heavily rely on multipliers which are usually implemented as expensive DSP slices in FPGA. To overcome this drawback, we demonstrate a more efficient technique to realize real-time frequency translation and channel selection of DSCM channels based on distributed arithmetic (DA) [31], as described in Chapter 4. No digital multipliers are required when using DA, thus completely eliminating the need for DSP slices in the FPGA. In addition, the DA-based DSXC reduces DSP-induced latency down to only a few clock periods, which is independent of the applied digital filter order. DA has been used to implement digital filters for Nyquist pulse generation in fiber-optic transmitter [9, 14], but has not been used for digital subcarrier frequency translation and channel selection. By applying DA algorithms to implement resampling filters, we show that DSXC key functionalities can be implemented in an FPGA platform without requiring any DSP slice. To our best knowledge, this is the first realization of a DA-based DSXC, which is capable of performing bandwidth flexible switching and routing with improved hardware efficiency, low latency, and transparency to signal modulation formats.

#### 1.2 Digital subcarrier cross-connect (DSXC)

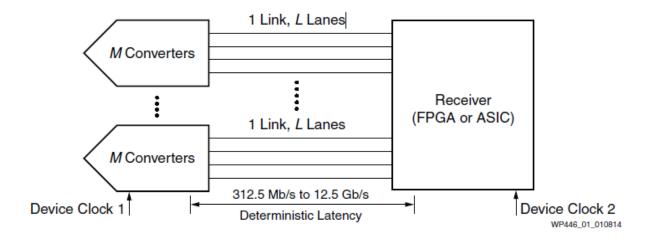

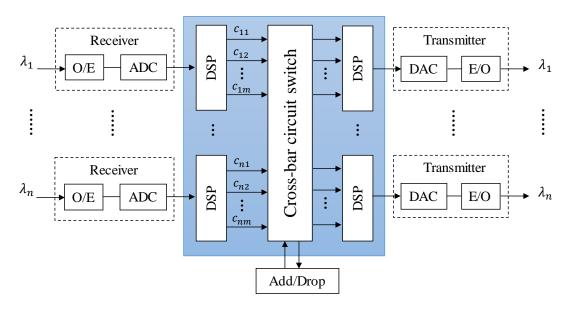

Figure 1.1 Digital subcarrier cross-connect

Figure 1.1 shows the block diagram of a generic DSXC node [30]. Input to the DSXC node are n optical signals, each consisting of m subcarrier channels. Each optical signal is received by a receiver, which performs optical-to-electrical conversion (O/E) through an optical receiver, and analog-to-digital conversion through an ADC. The digitized signal from each receiver is sent to the DSP module for processing. In the DSP module, each multicarrier signal is de-multiplexed into multiple subcarriers and sent into a cross-bar switch to be routed to any output port for multiplexing. The multiplexer aggregates multiple subcarriers and sent them into the targeted transmitter. The transmitter performs digital to analog conversion through a DAC, and electrical to optical (O/E) conversion obtained by an electro-optic modulator. In the shown DSXC node architecture, each digital subcarrier channel  $c_{ij}$ , (i = 1, 2...n, and j = 1, 2...m) in any input wavelength can be routed to any output wavelength  $\lambda_i$  and subcarrier frequency slot through a cross-bar circuit-switch.

The optical system can be either coherent or direct-detection. The multiplexing method can be through either high order Nyquist filters or OFDM. Digital compensation techniques, such as chromatic dispersion compensation and electronic circuit frequency roll-off compensation, can be performed in the digital domain. In the design of this DSXC, we use high order Nyquist filters for DSCM, which provide the flexibility of using unequal spectral bandwidth and distinct modulation formats to be assigned to each subcarrier channel.

In order to be able to route any subcarrier channel of any input wavelength to any subcarrier channel of any output wavelength, frequency translation and channel selection of individual subcarrier are two critical functions in a DSXC. Frequency translation includes frequency down conversion and up conversion of each subcarrier channel. The frequency down conversion can be achieved through decimation filter, in which the decimation factor is the ratio of the input rate to the output rate. The frequency up conversion can be achieved through an interpolation filter, in which the interpolation factor is the ratio of the output rate to the input rate. Since resampling filter includes decimation filter and interpolation filter, both decimation factor and interpolation factor are named as resampling factor. According to Nyquist criterion, the available analog bandwidth of each wavelength channel is limited to half of the ADC's sampling rate. This total bandwidth can be subdivided among many frequency slots (FS). The bandwidth of each FS is given by the total available bandwidth divided by the resampling factor when digital resampling filters are used. In this process, any subcarrier in a FS is first down-converted to the lowest frequency FS through a decimation filter, and then up-converted to any targeted FS through an interpolation filter [23]. During the down-conversion process, a decimation filter, whose frequency response has a passband targeted at a particular FS, selects the subcarrier in this FS and down converts it to the first FS. During the up-conversion process, an interpolation filter,

whose frequency response has a passband targeted at a particular FS, selects the up-sampled copy of subcarrier in this FS and rejects all copies in other FSs. Theoretically, decimation is equivalent to a cascaded process of filtering and down sampling, whereas interpolation is equivalent to a cascaded process of up sampling and filtering. Further information about these two procedures can be found in [30]. Both decimation filter and interpolation filter can be categorized as resampling filters, which are essentially finite impulse response (FIR) filters with the capability of changing sampling rate of its input signal. FIR filter characteristics such as passband ripple, width of transition band, and stopband attenuation are determined by the filter order and coefficients. For a given sampling rate, a low passband ripple, sharp transition band, and large stopband attenuation are desirable features, which usually require a high filter order and take significant DSP resources in hardware. In addition, when supporting high capacity DSXC with fine spectral granularity of subcarrier channels the number of digital filters can be quite high. In summary, an efficient digital filter design is critically important in order to minimize the DSP resource requirement.

#### 1.3 Digital subcarrier multiplexing techniques

DSXC is circuit cross-connect switch that is based on DSCM. Nyquist-FDM and OFDM are the are two major techniques for implementing DSCM.

Figure 1.2 (a) Nyquist pulse in time domain (b) spectrum of a single Nyquist pulse (c) spectrum of Nyquist FDM The basic principle of Nyquist pulse modulation is shown in Figure 1.2. For simplicity, we use OOK modulation format. Modulation formats with high spectral efficiency can also be employed [32]. As it shown in Figure 1.2 (a), a Nyquist pulse in time domain is a sinc-shaped waveform which spreads into adjacent time slots. By taking the Fourier transform of the Nyquist pulse in Figure 1.2 (a), we can get the spectrum of this pulse. As shown in Figure 1.2 (b), the spectrum of Nyquist pulse has a rectangular shape. By shifting the spectrum of Nyquist pulse in Figure 1.2 (b) by  $k\Delta f$  (k = 0, 1, ..., N - 1), we can get N sub-spectra of Nyquist pulse signal. The superposition of the N sub-spectra results in the total Nyquist-FDM spectrum as it illustrated in Figure 1.2 (c). Ideally, there is no guard-band between every two adjacent channels if perfect filtering is performed. However, ideal filtering cannot be realized in practical implementation since the order of digital filter is limited, so a guard-band between every two adjacent channels is required to prevent inter-channel crosstalk. In Nyquist-FDM based DSCM, phase synchronization between different channels is not needed, since every channel is independent from other channels.

The basic principle of OFDM is shown in Figure 1.3, suppose OOK is utilized as the modulation format. A single carrier OFDM signal in time domain is shown in Figure 1.3 (a), it has a rectangular pulse shape and a symbol period of  $T_S$ . By taking the Fourier transform of the signal in Figure 1.3 (a), we can get the spectrum of a single carrier OFDM signal whose bandwidth is  $\Delta f$ . The spectrum of this single carrier OFDM signal spreads to adjacent frequency slots. Shifting the spectrum of OFDM symbol in Figure 1.3 (b) by  $k\Delta f$  (k = 0, 1,..., N-1), we can get N sub-spectra of OFDM signal. The superposition of the N sub-spectra results in the total OFDM spectrum as illustrated in Figure 1.3 (c).

Figure 1.3 Principle of OFDM (a) single pulse shape (b) spectrum of a single OFDM symbol (c) spectrum of OFDM As it shown in Figure 1.3, in OFDM based DSCM, the spectral of each channel spreads to adjacent channels and there is no guard-band between adjacent channels.

The research of real-time DSCM has been actively conducted. The real-time generation and reception of N-FDM have been reported and experimentally demonstrated [9, 14, 33]. Recent years, OFDM has also received a lot of attention in the field of optical communication [34]. The real-time generation of OFDM [9, 14, 35], real-time reception of OFDM [36-38] and the

implementation of real-time OFDM transceivers [39, 40] have been demonstrated. Optical networks based on real-time OFDM with flexible power loading and bandwidth allocation have also been demonstrated [41-43].

#### 1.4 Overview of proposed work

In this dissertation, we aim to investigate and implement real-time DSP-enabled DSXC for optical communication networks. In Chapter 2, we introduced the principle of DSXC and a hardware platform to implement real-time DSP for this DSXC. In Chapter 2 and Chapter 3, we investigate the cost and performance of different techniques, such as resampling filters and DA architecture, to efficiently implement this DSXC on the hardware platform. The implemented real-time DSP-enabled DSXC is demonstrated experimentally.

#### 1.4.1 Real-time DSP hardware platform

We built a hardware platform to implement real-time DSP-enabled DSXC. This platform is based on Virtex7 FPGA, which allows the test of various real-time DSP algorithms for cross-connect switching in optical communication systems and networks. It consists of two ADCs boards, a DAC board, a Virtex 7 FPGA board and a data processing computer. In order to achieve very high data transfers between different parts of this platform, we developed the high-speed interface, such as JESD204B interface between FPGA and converters.

#### 1.4.2 Channel selection and frequency translation in DSXC

In this work, we focus on the study of DSXC based on Nyquist FDM. The essential operation of a DSXC is the switching and routing of subcarrier channels, which is achieved through channel selection and frequency translation. There are multiple techniques to achieve channel selection and frequency translation. We discussed and compared the performance and resource cost of two techniques: (1) mixing and filtering, (2) resampling filters. In the design of real-time DSP

algorithms, considerations must be given to the performance and resource cost because the DSP resource of FPGA is limited.

#### 1.4.3 Implementation of DSXC based on hardware platform

After the development of real-time DSP algorithms and the hardware platform, we implemented the real-time DSP algorithm on this hardware platform. The implemented DSXC can be either based on resampling filters that consumes multipliers or resampling filters that based on DA architecture. In Chapter 3, we discuss and demonstrate the DSXC based on resampling filters that consume multipliers and compared it with traditional technique that is based on I/Q mixing and filtering. In Chapter 4, we describe the principle of DA architecture and introduce a DA-based DSXC, and we compare it with the DSXC based on resampling filters that utilize multipliers. We built the project for FPGA and generated the bitstream to be downloaded onto FPGA board, which results in a real-time DSP-enabled DSXC. We incorporated this cross-connect into optical fiber transmission system and analyzed its performance in experiment.

#### **Chapter 2: Real-time DSP hardware platform**

In this chapter, we introduce the architecture of a real-time DSP hardware platform for implementing DSXC. This platform consists of high-speed ADCs, high-speed DACs, FPGA, and optical transceivers. The development of data interfaces and considerations for FPGA implementation are also discussed in this chapter.

#### 2.1 Hardware Platform

In order to meet the requirements of processing time in a practical application, a real-time DSP is needed. A general-purpose computer lacks the needed resources and is not suitable for real-time DSP. In contrast, an FPGA has the advantage of fast, parallel processing and is programmable, which makes it a good choice for building a platform for the prototype research of a real-time DSP for optical communication.

Our purpose is to establish an optical system testbed capable of generating, detecting, and processing advanced multiplexing techniques such as N-FDM and OFDM, which allows us to investigate various modulation formats and DSP algorithms in real-time optical systems and networks. In order to demonstrate algorithms and capabilities of DSCM, we have developed a flexible FPGA platform that consists of three major parts: an FPGA board (HTG700), two ADC boards (ADC12J4000EVM), and a DAC board (DAC38RF82EVM). The interface between the converters and the FPGA is a JESD204B, and the interface between the FPGA and the computer is a peripheral component interconnect express (PCIe).

Figure 2.1 (a) block diagram and (b) photo of DSCM testbed

As shown in Figure 2.1 (a), the testbed consists of two ADC evaluation boards, a DAC evaluation board, an FPGA board, and a connection with the data collection computer through the PCIe. Two ADCs are used to convert the received electrical signal from the optical receivers into the digital domain and send it to the FPGA board through the FPGA mezzanine card (FMC) connectors. The FPGA has three major tasks: digital down-conversion (DDC)/digital upconversion (DUC), digital filtering, and cross-connect switching of digital subcarrier channels. Digital compensation of transmission impairments and waveform distortion can also be

implemented with DSP algorithms in the FPGA platform. The DAC is used to convert the processed digital signals in the FPGA back to analog waveforms. Figure 2.1 (b) shows the crossconnect platform. This platform uses a Texas Instruments (TI) DAC evaluation board (DAC38RF82EVM), which supports two DAC output channels each with a 2.5GS/s uninterpolated input sampling rate with 16-bit resolution, and two ADC evaluation boards (TI: ADC12J400EVM), each with a 4GS/s sampling rate with 12-bit resolution. The FPGA evaluation board is a HTG700, which is mounted with a Xilinx Virtex7-XC7VX690T FPGA chip and equipped with three FMC connectors. The FPGA board also supports a PCIe-X8-Gen3 with eight lanes operating in parallel, and the maximum data rate is approximately 63 Gb/s.`

Table 2.1 Available FPGA resources on Virtex 5 and Virtex 7 [44, 45]

| Part Number | Slices  | Logic   | CLB Flip- | BRAM    | DSP    |

|-------------|---------|---------|-----------|---------|--------|

| Part Number | Silces  | Cells   | Flops     | (Kbits) | Slices |

| XC5VFX200T  | 30,720  | 196,608 | 122,880   | 16,416  | 384    |

| XC7VX690T   | 108,300 | 693,120 | 866,400   | 52,920  | 3,600  |

Table 2.1 shows the available FPGA resources on a Virtex 5 XC5VFX200T and a Virtex 7 XC7VX690T. A Virtex 7 has many more resources than a Virtex 5. The DSP slices on a Virtex 7 are almost 10 times those of a Virtex 5. With more FPGA resources, a DSP platform with higher performance can be developed and more complex DSP algorithms can be investigated.

Table 2.2 Specifications of ADC12J4000 and DAC38RF82

| Part Number | Bit Resolution | Maximum Sampling Rate | Number of Channels | Interface |

|-------------|----------------|-----------------------|--------------------|-----------|

| ADC12J400   | 12             | 4 GSPS                | 1                  | JESD204B  |

| DAC38RF82   | 16             | 3.33 GSPS             | 2                  | JESD204B  |

Table 2.2 shows the specifications of the ADC and DAC used in the design of this DSXC. The ADC operates in single channel mode with 12-bit resolution, and the DAC operates in dual-channel mode with 16-bit resolution. Both of them have a JESD204B interface. Considering the available resources and timing issues in the FPGA design, we used 1.6 GHz as the sampling rate of both the ADC and DAC.

Table 2.3 Specifications of Optical Tx and Rx

| Part Number | Bandwidth     | Wavelength | Type   | Modulation |

|-------------|---------------|------------|--------|------------|

| OZ510       | 30 MHz ~ 3GHz | 1330nm     | Linear | Intensity  |

|             |               |            |        | modulation |

Table 2.3 shows the specifications of the optical Tx and Rx used in this testbed. Both are linear, have intensity modulation, and have a RF bandwidth from 30 MHz to 3 GHz.

#### 2.2 Data Interfaces

There are a few different data interfaces in our design. Low speed data interfaces include a JTAG (named after the Joint Test Action Group) interface and a universal asynchronous receiver-transmitter (UART) interface. The JTAG is the interface between the FPGA and the PC, through which the bitstream can be downloaded to the FPGA. The UART is also a low speed interface between the FPGA and the PC, which can be used to transfer low rate data between the FPGA board and the computer, such as during debugging and monitoring the status of modules in the

FPGA. The high-speed interfaces include the JESD204B and the PCI Express. The JESD204B is a high-speed serial interface between the data converters and the computer, and the PCI Express is a high-speed serial interface between the FPGA board and the computer. The JESD204B and PCI Express are complicated and are discussed in the following sections.

#### 2.2.1 JESD204B interface

The high throughput rates of these gigabit ADCs and DACs push the limits and timing constraints of the current standard high-speed interface, a serial low-voltage differential signaling (LVDS) interface. In order to address this problem, the Joint Electron Device Engineering Council (JEDEC) committee created a robust wide data converter interface known as the JESD204 interface [46][48]. The latest version of the JESD204 interface is the JESD204B.

[Xilinx WP 446]

Figure 2.2 JESD204B standard

As shown in Figure 2.2, the JESD204B provides deterministic latency with a data rate in each serial lane up to 12.5 Gb/s[46, 47]. Since the data rate of each serial lane is much higher than in the LVDS, the required pin count in the JESD204B can be greatly reduced, which makes the design of a printed circuit board much simpler and more compact. With improvement comes complexity; the JESD204B interface is much more complex than the LVDS interface, which

makes designing with the JESD204B more challenging. The JESD204B has an OSI-type protocol stack, which is very complicated. In order to reduce the complexity of design, Xilinx has provided a configurable FPGA object for implementing the JESD interface, called the JESD204B IP Core. In this design, a JESD204B subclass 1 is used.

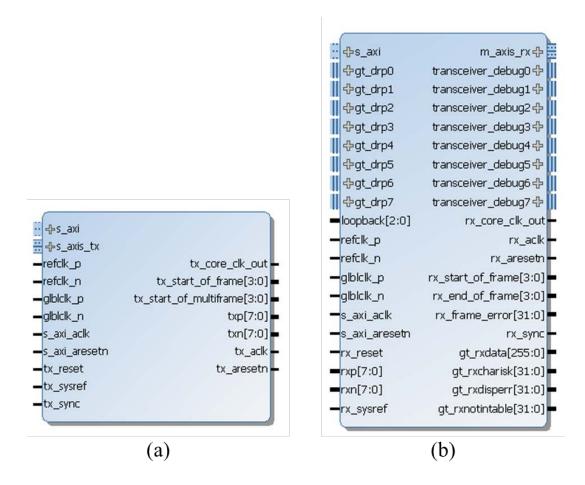

A real-time high-speed transmitter is based on the FPGA board and DAC board. This design is able to generate arbitrary waveforms at the output of the DAC.

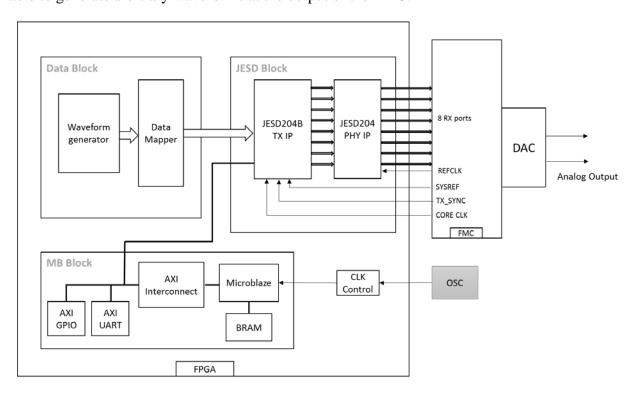

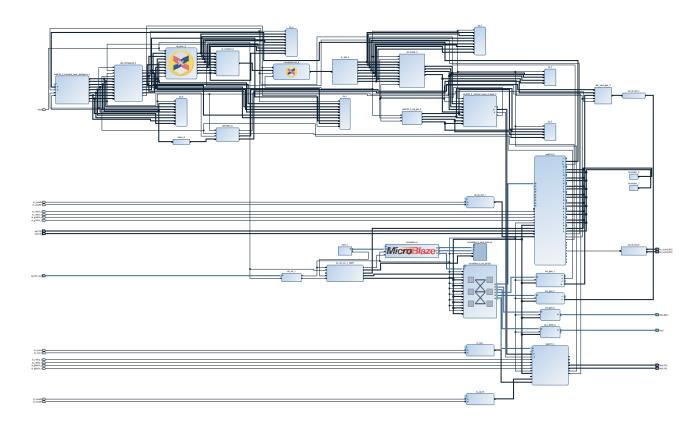

Figure 2.3 Block diagram of a real-time transmitter based on FPGA and DAC

Since the data is transferred from the FPGA to the DAC through the JESD interface, the FPGA board serves as a JESD transmitter, and the DAC board serves as a JESD receiver accordingly. Digital signals are transferred from the FPGA board to the DAC board through eight JESD serial lanes, and the maximum data rate of each JESD lane is 12.5 Gb/s. As shown in Figure 2.3, the block design inside the FPGA mainly consists of three blocks: the data block, the JESD block, and the Microblaze block (MB block).

In the MB block, the Microblaze is a soft-core processor implemented on the FPGA, which can be programmed by C language. With the Microblaze, IP cores can be easily programmed and configured through the advanced extensible interface (AXI). The block random access memory (BRAM) provides local memory for the Microblaze processor. The AXI interconnect serves as the bridge between the Microblaze and other AXI IPs. In the data block, the waveform generator is a user-packaged IP that generates waveforms by using a look-up table (LUT). The data mapper maps the generated waveform into the AXI data stream that fits the data format of the JESD block. In the JESD block, the JESD204B TX block transmits data to the JESD204 PHY once it receives the request from the DAC through the FMC connector. In the JESD block, the JESD TX IP is configured and monitored through an AXI4-Lite management interface. The JESD PHY IP implements the Xilinx GTX transceiver logic and control interface. After receiving the AXI stream data from the data block, the JESD TX IP sends the data to the JESD PHY IP. The source clock for the Microblaze and AXI interfaces is provided by an oscillator (OSC) on the HTG700. The JESD clock, which includes the reference clock (REFCLK) and core clock (CORE CLK) for JESD, are generated by the clock chip (LMK04828) on the DAC board.

A real-time high-speed receiver is based on the FPGA board and ADC board. This allows the ADC to sample and digitize analog signals and send digital signals to the FPGA for real-time processing. The receiver project is intended to build the interface and synchronize between the ADC board and the FPGA board. This is an essential part for a high-speed digital receiver, which enables the DSXC to convert analog signals received from the photodetector to the digital domain and transfer them to the FPGA board for real-time processing.

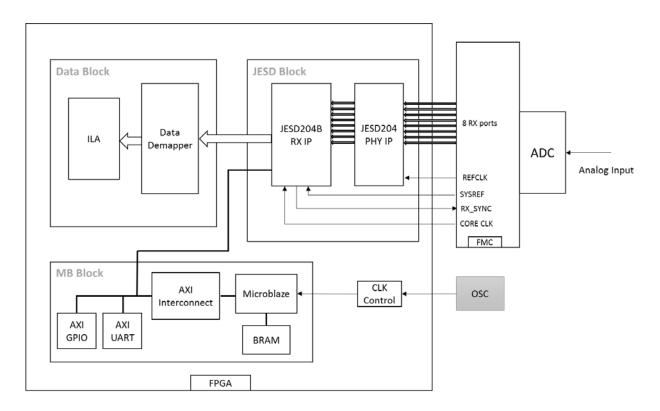

Figure 2.4 Block diagram of high-speed receiver based on FPGA and ADC

As shown in Figure 2.4, the block design of the real-time receiver consists of an MB block, data block, and JESD block. The design of the receiver is similar to the design of the real-time transmitter, except that in this design the FPGA board serves as the JESD receiver while the ADC board serves as the JESD transmitter. The ADC converts analog input signals into digital data and transmits them to the FPGA board.

As shown in Figure 2.3 and 2.4, projects for interfacing ADC and DAC with FPGA have been built in Xilinx Vivado separately. The ADC and DAC have been tested separately to verify if the JESD204B interfaces are working properly.

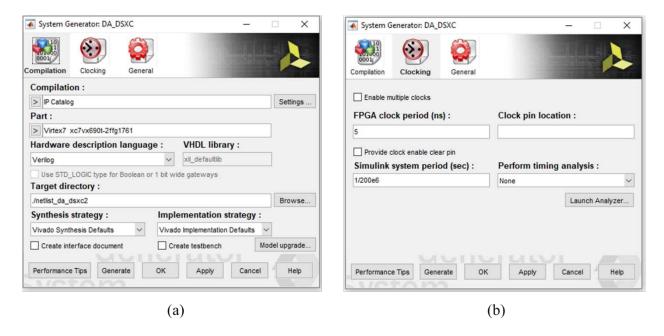

#### 2.2.2 Design in Xilinx Vivado

In the FPGA design of the DSXC, Xilinx Vivado 2015.4 is used as the design tool. The design of the resampling filters is accomplished using the Xilinx System Generator and Filter Design HDL Coder. A more detailed description of the DSXC design process is given in Appendix I.

#### 2.3 Considerations in FPGA Implementation

In implementing an FPGA, there are a few issues that need to be addressed, such as clocking and bit resolution, as they may have a significant impact on the signal quality. Timing is critical during the setup of a real-time DSP hardware platform. In this setup, the ADC and DAC use external clocks generated by signal generators. If the signal generators are running freely, the frequencies of their generated clocks may slightly differ, and this can cause a frequency offset in the digital signal. This frequency offset may cause the degradation of the signal quality at the output of the DAC. In order to avoid frequency offset when transferring a digital signal from the ADC clock domain to the DAC clock domain, it is necessary to lock the clock frequencies. We used the 10 MHz reference signal to lock the clock frequencies of all the signal generators and first in first out (FIFO) IP to transfer large amounts of data between the different clock domains. Bit growth is also a very common issue in real-time DSP implementation, because in FPGA arithmetic, the bit width of a digital signal can rapidly grow, making it impossible to keep full precision during the processing. For example, adding two N bit numbers results in a N + 1 bit number, and multiplying two N bit numbers results in a 2N-1 bit number. If full precision is kept, the bit growth can quickly exceed the computation capability of the FPGA. Thus, it is very important to reduce bit width. The simplest way of reducing bit width is truncation, which can be achieved through dropping the least significant bits (LSB). However, truncation results in undesirable DC bias at the output. The round to even technique can solve the problem of DC bias by rounding up to the nearest even number. Compared with truncation, which does not consume logic resources, this technique costs logic resources but only contributes a negligible resource cost of the DSXC. In the implementation of the DSXC, we use the round to even technique to reduce the bit width while keeping sufficient resolution in the signal quality.

Another issue is that the FPGA has limited maximum clock frequency, on the order of a few hundred MHz. Current GSPS ADCs and DACs can achieve a sampling rate on the order of a few GHz, which is much higher than the maximum clock frequency in FPGA processing. The solutions for this issue are parallel processing and pipelining. Parallel processing means processing the data in parallel channels, so data with high sampling rates can be processed with a relatively low clock frequency. The FPGA architecture makes it very suitable for parallel processing. For example, if the FPGA has a clock frequency of 200 MHz and the data are processed in 20 parallel channels, then logically the total sampling rate is 4 GHz.

Timing is a critical issue in FPGA implementation, because it takes time for a signal to propagate from one flip-flop, through a combinational logic, to the next flip-flop. The more complicated the combinational logic, the longer takes for the signal to propagate. Timing can be a very difficult issue when the combinational logic is large and the FPGA clock frequency is high (above 50 MHz). The simplest technique to fix a timing issue is pipelining. By adding flip-flops into a large combinational logic, pipelining breaks the combinational logic into multiple stages, where the propagation delay in each stage is shorter than the original propagation delay. It is also important to note that pipelining does not decrease the total throughput of this digital design. Pipelining only increases the latency by a few clock periods, which is acceptable in many FPGA designs.

DSP units such as finite impulse response (FIR) filters, mixers, and local oscillators can also be easily implemented in parallel and be pipelined. Fast Fourier transform (FFT) can be implemented in FPGA by using a third-party IP named SpiralFFT, which can be generated in the format of a hardware description language (HDL) as described in [49]. Thus, all the DSP

algorithms described in this thesis can be implemented in FPGA to achieve a very high processing rate.

#### Chapter 3: Real-time DSP-enabled DSXC based on resampling filters

In this chapter, we introduce the design and experimental demonstration of the first real-time DSP-enabled DSXC based on resampling filters. This DSXC is implemented on a Xilinx Virtex-7 FPGA board, and the results have been presented in [30].

#### 3.1 Digital subcarrier cross-connect based on FPGA

Figure 3.1 Block diagram of digital subcarrier cross-connect (DSXC) based on FPGA

Figure 3.1 shows a basic DSXC block diagram based on FPGA. The input signal to the DSXC switch fabric comprises *n* wavelength channels, and each wavelength carries *m* radio frequency (RF) subcarrier channels. The RF subcarriers can support different modulation formats and make use of different spectral bandwidths. Each wavelength channel is detected by an optical receiver performing optical to electrical (O/E) conversion, which is followed by an ADC digitizing the analog waveform delivered by the optical carrier. Then the digitized waveform is sent to a DSP block for subcarrier de-multiplexing. The de-multiplexed subcarriers from all wavelength channels are sent to a cross-bar circuit switch, in which any input subcarrier can be routed to any output port. Subcarrier channel local add/drop can also be performed in this cross-bar switch

unit. The subcarriers switched through the cross-connect are then re-grouped and multiplexed by n DSP units corresponding to n output wavelength channels. Each digitally multiplexed composite signal forms a wavelength channel that is converted from electrical to optical (E/O) through a DAC and an optical transmitter. With this basic DSXC architecture, any subcarrier channel of any input optical carrier can be routed to any subcarrier of any output wavelength channel.

For demonstration purpose, the DSP units and the cross-bar circuit switch can be implemented using a single FPGA module which provides real-time processing. The cost of this implementation choice is proportional to the amount of FPGA resources that is required to implement the DSXC. FPGA resources mainly consist of memory resources and DSP slices. Memory resources include look-up table (LUT), LUT random access memory (LUTRAM), flip-flop (FF) and block RAM (BRAM). DSP slices are used to carry out digital multiplications, which are usually the most expensive operation in a real-time DSP hardware platform. For convenience, in this chapter we use the term *DSP cost* to represent the number of required DSP slices.

Since subcarrier channels in each wavelength are multiplexed in frequency domain, frequency translation (also known as spectral translation) is a critical operation in DSXC. A straightforward and conventional frequency translation technique is based on signal mixing and filtering operations whereby multiple local oscillators (LOs), mixers, and low pass filters are combined to achieve the intended goal. Digital filtering, which is the convolution between the input data sequence and the filter coefficients, is achieved through FIR filters that involve a large number of multiplications and represent the major DSP cost. Because the number of FIR filters increases linearly with the number of subcarriers in the cross-connect switch, the DSP cost for a DSXC

based on this frequency translation technique also increases accordingly, and may become a major limiting factor.

Since DSXC is performed in the digital domain, some inherent properties of digital sequence and DSP algorithms can be utilized to achieve frequency translation at a reduced DSP cost. More specifically, interpolation and decimation are techniques that have been widely used in digital systems to change the sampling rate of a signal [50]. By applying some modifications as described in Section 3.2, interpolation and decimation techniques can be used to perform frequency translation with significantly less DSP cost in comparison to the frequency translation obtained through conventional I/Q/ mixing and filtering. For reader's convenience, we first briefly describe frequency translation through I/Q mixing and filtering. Then, we describe frequency translation through resampling filters.

#### 3.2 Frequency translation techniques

In this section, we briefly introduce two techniques for frequency translation: 1) I/Q mixing and filtering; 2) Resampling filters.

#### 3.2.1 I/O mixing and filtering

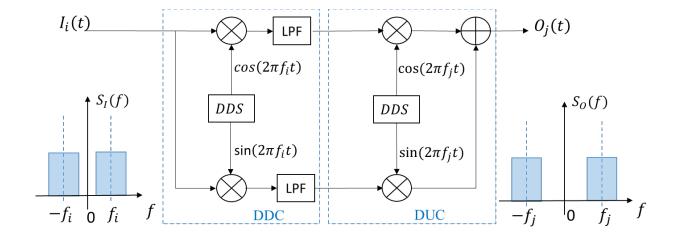

A traditional technique for frequency translation is through I/Q mixing and filtering. As shown in Figure 3.2, traditional frequency translation includes down-conversion and up-conversion, in which LOs are implemented from direct digital synthesizer (DDS). In order to maintain phase synchronization between LO and the RF subcarrier whose frequency needs to be translated, I/Q mixing is usually required. Figure 3.2 shows a standard two-step digital frequency translation process which consists of both digital down-conversion (DDC) and digital up-conversion (DUC).

Figure 3.2 Frequency translation through I/Q mixing and filtering

As shown in Figure 3.2, in the DDC process, a DDS simultaneously generating sine and cosine waveforms is used to provide a pair of LOs. Assume the incoming signal data sequence on the  $i^{th}$ subcarrier channel is  $I_i(t) = A_i(t) \cos(2\pi f_i t + \varphi_i)$ , where  $A_i(t)$  is modulated amplitude,  $f_i$  is the carrier frequency, and  $\varphi_i$  is the carrier phase; and the in-phase (I) and quadrature (Q) components of the LO are  $\cos(2\pi f_i t)$  and  $\sin(2\pi f_i t)$ , respectively. After down-conversion mixing and low pass filtering (LPF), the I and Q components of the baseband signal are  $\frac{1}{2}A_i(t)\cos(\varphi_i)$  and  $-\frac{1}{2}A_i(t)\sin(\varphi_i)$ , respectively. If the subcarrier channel needs to be dropped at this node, the I and Q components are combined together to recover the original baseband signal. Otherwise, the I and Q components are mixed with another pair of LOs,  $\cos(2\pi f_i t)$  and  $\sin(2\pi f_i t)$  , in the DUC module. The frequency up-conversion generates  $\frac{1}{2}A_i(t)\cos(\varphi_i)\cos(2\pi f_j t)$  and  $-\frac{1}{2}A_i(t)\sin(\varphi_i)\sin(2\pi f_j t)$ , and they are combined to form the DUC module output as,

$$O_m(t) = \frac{1}{2} A_i(t) \cos[2\pi f_j t + \varphi_i]$$

(3.1)

Throughout this frequency translation process, the carrier frequency is changed from  $f_i$  to  $f_j$ , while the original carrier phase,  $\varphi_i$ , is automatically maintained.

Note that I/Q mixing requires two separate filters for the I and the Q channels. Alternatively, one can use a single stage frequency translation from  $f_i$  to  $f_j$  using an LO frequency  $|f_j - f_i|$ . However, to avoid spectral overlap with other subcarrier channels, this approach requires the selection of the subcarrier channel at  $f_i$  by a bandpass filter before mixing, and the selection of subcarrier frequency at  $f_j$  by another bandpass filter after mixing, and thus the number of digital filters remains unchanged.

Alternatively, frequency translation may be applied to complex field modulated subcarriers in which the upper and lower sidebands of each subcarrier channel are not redundant. In that case Hilbert transform must be applied to avoid spectral aliasing, which would further increase the DSP cost.

As previously noted, when implementing this frequency translation in FPGA platform, the major DSP cost comes from digital filters, which increases linearly with the number of subcarrier channels.

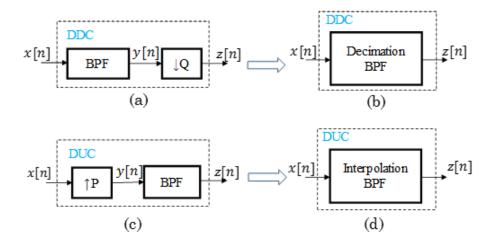

## 3.2.1 Resampling Filters

Alternatively, frequency translation may be achieved through resampling and filtering of each subcarrier channel. Similar to mixing and filtering, the resampling and filtering technique also consists of both DDC and DUC processes. As shown in Figure 3.3(a) and 3.3(c), DDC is usually achieved by cascading a bandpass filter (BPF) with a down sampling unit, while DUC can be achieved with an up-sampling unit followed by a BPF. For simplicity, we refer both down-sampling and up-sampling as *resampling* [50].

Figure 3.3 (a) DDC through BPF and down-sampling, (b) DDC through interpolation BPF, (c) DUC through upsampling and BPF, (d) DUC through decimation BPF

In Figure 3.3(a), a BPF is used to select a specific subcarrier channel, the data sequence after BPF is down sampled by a factor of Q through a down sampling unit.

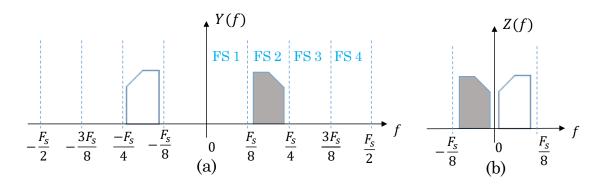

Figure 3.4. (a) DFT of y[n], and (b) DFT of z[n] for down sampling

Figure 3.4 shows an example of discrete Fourier transform (DFT) spectra of the input data sequence y[n] and the output data sequence z[n] of the down sampling unit with an input sampling frequency  $F_s$  and a down-sampling factor Q = 4. Through down sampling, the frequency range is scaled down by a factor of 4 from  $(-F_s/2, F_s/2)$  to  $(-F_s/8, F_s/8)$ . As shown in Figure 3.4(a), the selected subcarrier channel originally located in frequency slot 2 (FS2) is automatically down shifted to the frequency slot  $(0, F_s/8)$ . In general, if the selected subcarrier channel is originally located within an even frequency slot, such as FS2 and FS4 in Figure 3.4(a),

it will be spectrally flipped after down sampling. While if it is located in an odd frequency slot, such as FS1 and FS3, its spectrum will not flip.

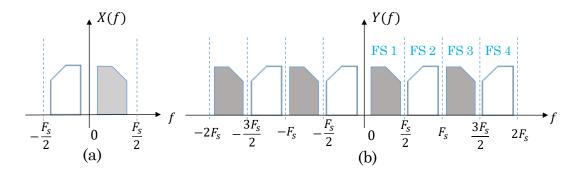

Figure 3.5. (a) DFT of [n], and (b) DFT of y[n] for up-sampling

For the process of DUC shown in Figure 3.3(c), a subcarrier channel at the lowest frequency slot needs to be translated to a higher frequency slot. Figure 3.5 shows an example of DFT spectra of the input data sequence x[n] and the output data sequence y[n] of the up-sampling unit with a sampling rate  $F_s$  and an up-sampling factor of P=4. Through up-sampling, the frequency range is expanded 4 times from  $(-F_s/2, F_s/2)$  to  $(-2F_s, 2F_s)$ . The up-sampled DFT spectrum in this expanded frequency range consists of multiple copies of the original spectrum, and each of them falls into a different frequency slot. By applying a band pass filter on the up-sampled spectrum, a particular copy of spectrum at the desired frequency slot can be selected, which is equivalent to a frequency translation. Again, similar to the down-sampling process the frequency-translated spectra in even frequency slots such as FS2 and FS4 shown in Figure 3.5(b), are flipped in comparison to the original spectrum in FS1. The flipped spectrum, although contains the full information, is a frequency conjugated version of the original signal, and thus another conjugate operation has to be performed when the baseband waveform needs to be recovered.

In comparison to I/Q mixing and filtering, the resampling and filtering technique shown in Figure 3.3(a) and 3.3(c) does not need LOs and mixers, and there is no need for carrier phase synchronization. Since the actual bandwidth of each frequency slot is determined by the sampling frequency and the resampling factor, it can be flexible to accommodate different data rates carried by different subcarriers. Suppose the sampling frequency is  $f_s$  and the resampling factors are  $L_1$ ,  $L_2$  and  $L_3$ , then the bandwidths of the frequency slot after resampling is  $f_s/(2L_1)$ ,  $f_s/(2L_2)$  and  $f_s/(2L_3)$ , respectively. The channel data rate granularity of DSXC can be made fine enough to address network efficiency requirements through the change of resampling factor. However, the major drawback of both DDC and DUC shown in Figure 3.3(a) and 3.3(c) is that the BPF still requires significant DSP resources of FPGA, similar to that based on I/Q mixing and filtering. A novel technique to solve this problem is to combine the resampling and BPF into a single resampling BPF as showing in Figure 3.3(b) and 3.3(d). Resampling BPF is a general term which includes decimation BPF for DDC and interpolation BPF for DUC.

Resampling filters can be implemented as polyphase decimation or interpolation filters on FPGA hardware [51], which was proposed primarily for resampling of data sequences while avoiding spectral aliasing and rejecting spectral images. Although polyphase resampling filters have been previously used in wireless transceivers [52], they have not been used for DSXC switches which require the capability of handling asynchronous subcarrier channels with non-equal bandwidth and independent modulation formats. While the required DSP resources linearly increases with the number of subcarrier channels for both I/Q-mixing-and-filtering and resampling-and-filtering, DSP resources required for resampling BPF is independent of the number of subcarrier channels. This significantly reduces the DSP resources requirement for FPGA implementation.

Digital frequency translation can be accomplished with resampling and filtering. As shown in Figure 3.3(a), DDC can be achieved by applying a band-pass filter (BPF) before a down-sampling unit, so that the subcarrier channel selected by the BPF is down-converted to a lower frequency slot. Let Q be the down-sampling factor indicating that one of every Q output samples from the BPF is retained, while the other Q-1 samples are discarded. The processing of these Q-1 discarded samples is in fact unnecessary and could be avoided to reduce the DSP cost. By combining down-sampling and filtering into a single decimation filter as shown in Figure 3.3(b), only one of every Q sampling operations is actually performed for BPF. Therefore, the total computation is effectively reduced by a factor of Q, and the DSP cost of a decimation BPF is only 1/Q of a conventional BPF with the same number of coefficients.

Similarly, DUC can be achieved by using an up-sampling unit followed by a BPF, as shown in Figure 3.3(c), so that a subcarrier channel at a lower frequency slot is up-converted to a higher frequency slot and be selected by the BPF. For an up-sampling factor of P, P-1 zeros are inserted between every two samples of the input digital sequence in the up-sampling process. As the multiplication of these inserted zeros with filter coefficients always results in zeros in the subsequent digital filtering process, these operations are not necessary. By combining up-sampling and filtering into a single interpolation filter as shown in Figure 3.3(d), unnecessary operations performed on the inserted zeros can be avoided by using only 1/P of the BPF coefficients during each convolution. Thus, the total computation is effectively reduced by a factor of P and the DSP cost of the interpolation BPF is only 1/P that of a traditional BPF with the same number of coefficients.

The frequency translation based on resampling filters and its DSP cost can be analyzed mathematically. In Figure 3(a) the input sequence x[n] represents a digital multi-carrier signal.

Suppose that the BPF is an N-tap FIR filter with coefficients  $h_0, h_1, \dots, h_{N-1}$ , then the filter output is

$$y[n] = \sum_{i=0}^{N-1} h_i \cdot x[n-i]$$

(3.2)

which is the digital sequence of a selected subcarrier channel that needs to be down-converted. After down sampling by a factor of Q, the output is

$$z[n] = y[nQ] \tag{3.3}$$

The Z-transform of z[n] can be calculated as

$$Z(z) = \sum_{n} z[n] \cdot z^{-n}$$

$$= \sum_{n} y[nQ] \cdot z^{-n}$$

$$= \sum_{m} y[m] \cdot \left(\frac{1}{Q} \sum_{p=0}^{Q-1} e^{j\frac{2\pi}{Q}pm}\right) \cdot z^{-\frac{m}{Q}}$$

$$= \frac{1}{Q} \sum_{p=0}^{Q-1} \sum_{m} y[m] \cdot (e^{-j\frac{2\pi}{Q}pm} \cdot z^{1/Q})^{-m}$$

$$= \frac{1}{Q} \sum_{m=0}^{Q-1} Y(e^{-j\frac{2\pi}{Q}p} \cdot z^{1/Q})$$

$$(3.4)$$

By letting  $z = e^{j\Omega}$  in Equation (3.4), the discrete-time Fourier transform (DTFT) of the down-sampled digital sequence z[n] can be calculated as

$$Z(e^{j\Omega}) = \frac{1}{\rho} \sum_{p=0}^{Q-1} Y(e^{j\frac{\Omega - 2\pi p}{Q}})$$

(3.5)

where  $Y(e^{j\Omega})$  is the DTFT of y[n].

According to Equation (3.5),  $Z(e^{j\Omega})$  is an expanded and shifted version of  $Y(e^{j\Omega})$  with an expansion factor Q. Since the DTFT of a digital sequence is periodical with a period of  $2\pi$ , every spectral component with an original bandwidth  $\pi/Q$  will be expanded to  $\pi$ . As a result, the

original spectrum which occupies a frequency slot (FS) with a bandwidth of  $\pi/Q$  will be automatically expanded to  $\pi$ , and frequency shifted by  $2p\pi$  into Q copies with p=0,1,2...Q-1.

Although  $Y(e^{j\Omega})$  is continuous and periodical, the DFT of y[n], is one sampled period of its DTFT, which is sampled at discrete points  $\Omega = 2\pi k/M$ , where  $\Omega$  is a normalized angular frequency, M is the length of DFT, and  $k = 0, 1, 2 \dots M - 1$  is the index of sampling in the frequency domain. Thus,  $\Omega \in (0, 2\pi)$  for M >> 1. If the sampling rate of y[n] is  $F_s$ , the actual frequency range of its DFT, denoted by Y(f), is  $(-F_s/2, F_s/2)$ .

As described previously, it is unnecessary to calculate the values of the samples in y[n] that are not used in the subsequent down-sampling process. The BPF and the down-sampling unit could be more efficiently implemented together as a decimation filter as shown in Figure 3.3(b). Consider Equation (3.2) and Equation (3.3), the output of the decimation BPF is

$$z[n] = \sum_{i=0}^{N-1} h_i \cdot x[nQ - i]$$

(3.6)

Compared with Equation (3.2), the amount of calculations in Equation (3.6) has been reduced by a factor of Q. This is because the number of output samples of the decimation filter is Q times less than that of a traditional digital filter, and thus the DSP cost is reduced by a factor of Q. Similarly, for the conventional up-sampling process shown in Figure 3.3(c), suppose the input

digital sequence is x[n], after up-sampling by a factor of P, the output is,  $(x[n/P] \quad \text{if } n/n \text{ is an integer})$

$$y[n] = \begin{cases} x[n/P] & \text{if } n/p \text{ is an integer} \\ 0, & \text{otherwise} \end{cases}$$

(3.7)

The Z transform of y[n] can be calculated as

$$Y(z) = \sum_{n} y[n] \cdot z^{-n}$$

$$= \sum_{n: \overline{p} \in \mathbb{Z}} x\left[\frac{n}{p}\right] \cdot z^{-n}$$

(3.8)

$$= \sum_{k} x[k] \cdot z^{-kP}$$

$$= X(z^{P})$$

Based on the result of Equation (3.8), the DTFT of the up-sampled digital sequence y[n] can be calculated by letting  $z = e^{j\Omega}$ , we get

$$Y(e^{j\Omega}) = X(e^{j\Omega P}) \tag{3.9}$$

Where  $X(e^{j\Omega P})$  is the DTFT of x[n/P]. In this up-sampling process,  $Y(e^{j\Omega})$  is a compressed version of  $X(e^{j\Omega})$ , and the compression factor is equal to the up-sampling factor P.

This up-sampling process can be explained by the similar scaling rule between DFT and DTFT as described above for down-sampling. An up-sampling by a factor P is equivalent to creating P equally spaced copies of DFT of x[n], denoted by Y(f), in the expanded frequency range of  $(-PF_s/2, PF_s/2)$ .

As shown in Figure 3.3(c), y[n] and z[n] are the input and output of the BPF, respectively. Suppose this BPF is a N-tap FIR filter with coefficients  $h_0, h_1, \dots, h_{N-1}$ , the output of this BPF is

$$z[n] = \sum_{i=0}^{N-1} h_i \cdot y[n-i]$$

(3.10)

As described previously, the up-sampling unit and BPF can be combined into an interpolation BPF to reduce the DSP cost. Consider Equation (3.7) and Equation (3.10), the output of this combined interpolation BPF is

$$z[n] = \sum_{k=0}^{N/P-1} h_{n-kP} \cdot x[k]$$

(3.11)

Compared with Equation (3.10), Equation (3.11) only requires N/P, instead of N, multiplications, so that the DSP cost is reduced accordingly by a factor of P.

# 3.3 Resource utilization of frequency translation

In order to estimate the resource utilization of different frequency translation techniques, a  $4 \times 4$  DSXC is designed in Xilinx System Generator. In this design, the FPGA platform is based on Xilinx Virtex-7 690t [45].

Figure 3.6 (a) spectrum of a[n], (b) DSP block of DSXC, and (c) spectrum of b[n]

Figure 3.6(a) shows an example of input electrical signal spectrum which has 4 subcarrier channels each carrying a different data sequence ( $D1\sim D4$ ). For simplicity, in this example each subcarrier channel has the same bandwidth. Figure 3.6(b) shows the block diagram of DSP used for this  $4\times 4$  DSXC. In this DSP block, the composite digital sequence including all 4 subcarrier channels at the input is first made into 4 equal copies. Each of the 4 DDC blocks down converts a channel from its subcarrier frequency to the baseband. The  $4\times 4$  cross-bar switch routes each down-converted baseband data sequence to a DUC block for frequency up-conversion. Channel add/drop is also possible at this stage before DUC. After up-conversion with each channel assigned a new subcarrier frequency, these subcarrier channels are combined at the output and sent to a DAC. The spectrum of the output electrical signal is illustrated in Figure 3.6(c) with the frequencies of subcarriers switched in comparison to the input spectrum.

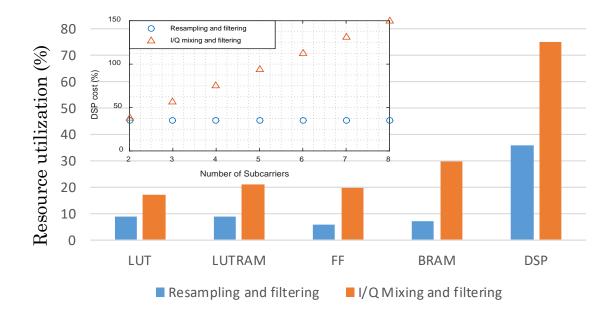

Figure 3.7 FPGA resource cost of a  $4 \times 4$  DSXC

Two frequency translation techniques, one based on resampling BPF, and the other one based on I/Q mixing and filtering, are compared for this example. Both of them use 800MHz total analog bandwidth which is equally divided into 4 frequency slots with 200MHz bandwidth in each slot. 40MHz is reserved as the guard band between adjacent subcarrier channels.  $79^{th}$  order finite impulse response (FIR) filters are used for both techniques with 60dB stopband attenuation. For the resampling-based frequency translation technique, the resampling factor is 4, and bandpass-filtering in each DDC block is accomplished by a decimation BPF. Similarly, each DUC block also performs bandpass-filtering which is implemented as an interpolation BPF. For the frequency translation based on mixing with LO, each DDC is performed by I/Q mixing and filtering by two low-pass FIR filters for the *I* and the *Q* channels, and each DUC also uses a DDS and two mixers, as shown in Figure 3.2. In this configuration, LOs are implemented through DDS by using look-up table (LUT), and mixers are implemented as digital multipliers, they both cost FPGA resources in memories and DSP slices. Figure 3.7 shows the comparison of FPGA resource cost to build this  $4 \times 4$  DSXC based on the two different frequency translation

techniques. In order to achieve the same performance, DSXC based on I/Q mixing and filtering has more than twice DSP cost than that based on resampling filters.

Here we used Xilinx Virtex-7 690t FPGA chip as the DSP hardware platform, and the total number of available DSP slices on this chip is 3600. As indicated by Figure 3.7, the bottleneck of the FPGA available resources in the design of DSXC is the DSP slices, and thus it is very important to minimize the cost of DSP slices in the design of DSP algorithms. The usage of DSP slices is mainly consumed by FIR filters, and the design of FIR filters is a tradeoff between the performance and resources cost. A higher order FIR filter has smaller passband ripple, sharper cutting edges, and higher stopband attenuation, but has higher resources cost. Passband ripple of a FIR filters causes frequency-dependent attenuation of the signal in the passband, which introduces signal waveform distortion.

For a traditional FIR filter to be implemented on a Virtex-7 FPGA, and suppose the length of its coefficients is S and the coefficients are symmetric, if the degree of parallelism is R, then the DSP cost of this FIR filter is  $R \times (S/2)$ . Since a mixer is just a multiplier that supports parallel processing, it simply uses R DSP slices. For the I/Q mixing and filtering technique shown in Figure 3.2, the frequency translation of each subcarrier channel needs 2 filters and 4 mixers, so that it requires (S + 4)R DSP slices. If the number of subcarrier channels is L, the total DSP cost of a DSXC based on I/Q mixing and filtering is

$$C_1 \approx (S+4)LR \tag{3.12}$$

Since usually S >> 4, the resources cost of this DSXC mainly comes from FIR filters. According to Equation (3.12), the total DSP cost increases linearly with the number of subcarriers.

Resampling BPF will cost less resource compared to a traditional FIR filter of the same coefficients. In order to compare with the frequency translation based on I/Q mixing and filtering with the number of subcarrier channels of L, we assume the total available bandwidth is B, and the bandwidths of subcarrier channels are  $B_1, B_2, ..., B_L$ , so that  $\sum_{i=1}^L B_i = B$ . The resampling factor  $M_i$  of subcarrier channel i is inversely proportional to the bandwidth of that channel,  $M_i = B/B_i$ , thus an  $L \times L$  DSXC could be built by using resampling filters with resampling factors  $M_1, M_2, ..., M_L$ . For a resampling FIR filter with a resampling factor  $M_i$  and a length of coefficients S, if the degree of parallelism in the DSP system is R, the number of required DSP slices to build this resampling FIR filter is  $R \times S/M_i$ . Since a DDC block needs a decimation BPF and a DUC block needs an interpolation BPF for each subcarrier channel, all together the DSXC needs L decimation BPF and L interpolation BPF. Therefore, the total DSP cost for building these resampling filters is

$$C_2 \approx \sum_{i=1}^{L} 2 \times R \times S/M_i = 2S \times R \tag{3.13}$$

According to Equation (3.13), the total DSP cost of DSXC based on resampling filters for frequency translation is independent of the number of subcarrier channels. Basically, a higher channel count requires a larger resampling factor for resampling filters which reduces the DSP cost of each filter, and thus the total DSP cost does not increase with the number of channels. In comparison, for frequency translation based on I/Q mixing and filtering technique, each digital filter requires the same amount of DSP slices and thus the overall DSP cost increases linearly with the number of subcarrier channels.

The inset of Figure 3.7, obtained through Equation (3.12) and Equation (3.13), shows the DSP cost of DSXC based on two different methods. Here we assume length of filter coefficients is S = 80 and the degree of parallelism is R = 4. The DSP cost of the DSXC based on

resampling filters remains unchanged when the number of subcarriers increases. Whereas the DSP cost increases linearly with the number of subcarriers for I/Q mixing and filtering, and there will not be enough DSP slices available on a Xilinx Virtex-7 690T FPGA if the number of subcarriers exceeds 5.

Although we used  $4 \times 4$  DSXC as the example with equal subcarrier channel spacing and equal data rate for each channel, unequal channel spacing and different bandwidth for subcarrier channels can also be used because the resampling factor for each channel can be independently set. This has been experimentally demonstrated and will be discussed in the next section.

#### 3.4 Experiments

In order to demonstrate DSXC and test its performance experimentally, an optical system based on digital subcarrier multiplexing has been setup using an FPGA platform for real-time DSP and cross-connect switching.

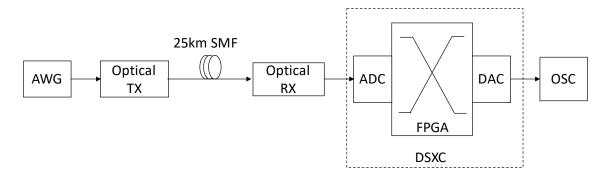

Figure 3.8 Experimental setup

The experimental setup is shown in Figure 3.8, where an AWG generates an electrical waveform which has multiple subcarriers. A linear optical transmitter converts this multicarrier electrical waveform into optical domain through direct intensity modulation. The optical signal is transmitted through 25 km standard single mode fiber (SMF), and detected by an optical receiver which linearly converts the received optical signal into electrical waveform. This detected electrical waveform is then sent into the DSXC for subcarrier level cross-connect switch. The

waveform at the output of the DSXC is sampled by a real-time digital oscilloscope (OSC, DPO72304DX) for analysis.

This DSXC platform consists of three major parts: FPGA board (Hitech-global HTG700), analog-to-digital converter (ADC) (TI ADC12J4000EVM) and digital-to-analog converter (DAC) (TI DAC38RF82EVM). The resolutions of the ADC and the DAC are 12-bit and 16-bit respectively. Because a common clock is required, both the ADC and the DAC are running at an input sampling rate of 1.6 GSPS, so that the available analog bandwidth is 800MHz. The FPGA board is mounted with a Xilinx Virtex-7 690t FPGA chip. The FPGA clock frequency is 200MHz, and thus the sampled data in FPGA is processed in eight parallel channels.

Based on this DSP platform, an 8 × 8 DSXC has been implemented, which switches subcarrier channels with three different data rates. Only resampling filters have been used for frequency translation in the experiment. The available analog bandwidth of 800MHz is divided into 8 frequency slots with three different widths: 200MHz, 100MHz and 50MHz, and 20MHz is reserved for the guard band between adjacent subcarrier channels. Thus, the bandwidth of the corresponding subcarrier channels are 180MHz, 80MHz and 30MHz, respectively, and in principle each can have an independent modulation format. Equiripple 108<sup>th</sup> order FIR filters are used in this experiment for DDC and DUC. The ripple in the filter passband is 0.5dB and the stopband attenuation is 30dB.

Table 3.1 shows an example of the input signal to the 8 × 8 DSXC, in which 8 subcarrier channels, SC1, SC2, ...SC8, are generated by the AWG. Each subcarrier is filtered to have rectangular spectral shape by using the method described in [53]. To demonstrate the capability of working with mixed modulation formats and data rates, Table I shows the bandwidth and modulation format assignment for the 8 subcarrier channels.

Table 3.1 AWG generated input signal to 8×8 DSXC

| Subcarrier # | Bandwidth (MHz) | <b>Modulation Format</b> |  |

|--------------|-----------------|--------------------------|--|

| 1            | 30              | QPSK                     |  |

| 2            | 80              | QPSK                     |  |