# Control Plane Hardware Design for Optical Packet Switched Data Centre Networks

Paris Andreades

A dissertation submitted in partial fulfilment of the requirements for the degree of

**Doctor of Philosophy**

of

**University College London**

Optical Networks Group

Department of Electronic and Electrical Engineering

University College London

November, 2019

I, Paris Andreades, confirm that the work presented in this thesis is my own. Where information has been derived from other sources, I confirm that this has been indicated in the work.

## **Abstract**

Optical packet switching for intra-data centre networks is key to addressing traffic requirements. Photonic integration and wavelength division multiplexing (WDM) can overcome bandwidth limits in switching systems. A promising technology to build a nanosecond-reconfigurable photonic-integrated switch, compatible with WDM, is the semiconductor optical amplifier (SOA). SOAs are typically used as gating elements in a broadcast-and-select (B&S) configuration, to build an optical crossbar switch. For larger-size switching, a three-stage Clos network, based on crossbar nodes, is a viable architecture. However, the design of the switch control plane, is one of the barriers to packet switching; it should run on packet timescales, which becomes increasingly challenging as line rates get higher. The scheduler, used for the allocation of switch paths, limits control clock speed. To this end, the research contribution was the design of highly parallel hardware schedulers for crossbar and Clos network switches. On a field-programmable gate array (FPGA), the minimum scheduler clock period achieved was 5.0 ns and 5.4 ns, for a 32-port crossbar and Clos switch, respectively. By using parallel path allocation modules, one per Clos node, a minimum clock period of 7.0 ns was achieved, for a 256-port switch. For scheduler application-specific integrated circuit (ASIC) synthesis, this reduces to 2.0 ns; a record result enabling scalable packet switching. Furthermore, the control plane was demonstrated experimentally. Moreover, a cycle-accurate network emulator was developed to evaluate switch performance. Results showed a switch saturation throughput at a traffic load 60% of capacity, with sub-microsecond packet latency, for a 256-port Clos switch, outperforming state-of-the-art optical packet switches.

# **Impact Statement**

Optical packet switching is a viable solution to continue increasing the network performance, in response to the traffic requirements inside a data centre. A major challenge is the clock speed of the switch control plane. This has to be on packet timescales, which keep decreasing as line rates keep increasing. The clock speed is typically limited by the scheduler, responsible for the fair allocation of switch paths and resolving any contention.

The impact of the research conducted is the contribution of a collection of scheduler designs, for crossbar and Clos-network switches, optimised for ultra-low clock period, to enable large-size packet switching. The critical path in the designs is identified. The digital design techniques and Clos routing algorithms applied, for highly parallel scheduling and reducing the critical path, were discussed in detail. A record minimum clock period was reported, for a 256-port Clos scheduler.

Although focus is on optical packet switch scheduling, all scheduler designs presented are applicable to electronic crossbar and Clos-network packet switches. From a resource point of view, there is no difference in allocating and activating, for example, an SOA gate in an optical crossbar or a multiplexer in an electronic crossbar. The same scheduler digital design principles and techniques are applicable to both switch types.

The control plane was verified experimentally and it was used to demonstrate optical packet switching with ultra-low end-to-end packet latency. The experiment quantified the control plane delay contributions and identified the critical path. It also revealed the implications of asynchronous operation on the performance of the switch. The significance of the scheduler clock period was highlighted.

A cycle-accurate network emulator, with packet-level detail, was developed. This enables researchers to accurately assess the flow control and routing algorithm of a network of any architecture, under different traffic patterns, as a function of traffic load and network size. Packet latency and network throughput, which are key performance metrics, can be measured with this tool. Also, because the emulator is developed in a hardware description language, key circuits such as network control modules can be directly implemented on a hardware platform, after verification.

# Acknowledgements

First and foremost, I would like to thank my supervisor, Dr Georgios Zervas, for his invaluable advice and generosity. His expertise on computer networks has led to stimulating discussions on the PhD topic. I am also thankful to my previous supervisor, Dr Philip M. Watts, for my digital design knowledge and skills.

I am grateful to fellow Optical Interconnects PhD students and dear friends, Mr Joshua Benjamin and Mr Kari Clark, for the collaborative discussions we had, which have deepened my understanding on the research subject.

Over the years in the Optical Networks research group, I have made some great friends, who helped make my time truly enjoyable and I am thankful for that. In particular, Dr M. Sezer Erkilinç, Dr Gabriel Saavedra Mondaca, Dr Gabriele Liga, Mr Boris Karanov and Mr Hui Yuan.

A special thanks goes to Miss Amna Fareed Asghar, who has always been by my side, throughout my research journey, and made my life in London an incredible experience. Thank you for being there for me during stressful times.

In addition, I would like to acknowledge my younger brother, Mr Christos Andreades, for the numerous motivating conversations we had about the future that lies ahead.

Last but not least, I would like to express my gratitude towards my parents, Mr Antonis Andreades and Mrs Andrie Andreades. You have always been there for me and helped me realise my dreams. Without you, I would not be where I am today.

# **Contents**

| 1 | Intr | oductio  | n                                     | 20 |

|---|------|----------|---------------------------------------|----|

|   | 1.1  | Resear   | rch Problem                           | 23 |

|   | 1.2  | Thesis   | Structure                             | 25 |

|   | 1.3  | Key C    | ontributions                          | 26 |

|   | 1.4  | List of  | Publications                          | 28 |

| 2 | Lite | rature l | Review                                | 30 |

|   | 2.1  | Non-b    | locking Architectures                 | 30 |

|   |      | 2.1.1    | Crossbar                              | 30 |

|   |      | 2.1.2    | Clos Network                          | 31 |

|   | 2.2  | Data C   | Centre Network Architectures          | 34 |

|   |      | 2.2.1    | Hierarchical Tree                     | 34 |

|   |      | 2.2.2    | Leaf-Spine                            | 36 |

|   | 2.3  | Electri  | cal Network Scaling Limitations       | 37 |

|   |      | 2.3.1    | Transmission Distance and Bandwidth   | 37 |

|   |      | 2.3.2    | Bandwidth Density                     | 38 |

|   |      | 2.3.3    | Switch Capacity and Power Consumption | 39 |

|   | 2.4  | Optica   | l Networks for Future Data Centres    | 40 |

|   |      | 2.4.1    | Transmission Distance and Bandwidth   | 40 |

|   |      | 2.4.2    | Bandwidth Density                     | 43 |

|   |      | 2.4.3    | Switch Capacity and Power Consumption | 44 |

|   | 2.5  | Sched    | uling                                 | 44 |

|   |      | 2.5.1    | Arbitration                           | 45 |

| Contents | 8 |

|----------|---|

| Contents | 8 |

|   |             | 2.5.2                                                            | Allocation                                                                                                                                                                                        | 50                                                                        |

|---|-------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|   | 2.6         | Optical                                                          | Switching                                                                                                                                                                                         | 53                                                                        |

|   |             | 2.6.1                                                            | Technologies                                                                                                                                                                                      | 53                                                                        |

|   |             | 2.6.2                                                            | Technologies Review and Comparison                                                                                                                                                                | 61                                                                        |

|   |             | 2.6.3                                                            | Architectures                                                                                                                                                                                     | 63                                                                        |

|   |             | 2.6.4                                                            | Architectures Review and Comparison                                                                                                                                                               | 76                                                                        |

| 3 | Syste       | em Con                                                           | cept                                                                                                                                                                                              | 81                                                                        |

|   | 3.1         | Switch                                                           | Application                                                                                                                                                                                       | 81                                                                        |

|   | 3.2         | Wavele                                                           | ngth-striped Transmission                                                                                                                                                                         | 82                                                                        |

|   | 3.3         | Switch                                                           | Architecture                                                                                                                                                                                      | 83                                                                        |

|   | 3.4         | Switch                                                           | Routing                                                                                                                                                                                           | 85                                                                        |

|   | 3.5         | Flow C                                                           | ontrol                                                                                                                                                                                            | 86                                                                        |

|   | 3.6         | Review                                                           | and Comparison to Related Work                                                                                                                                                                    | 89                                                                        |

|   | 3.7         | Tools a                                                          | nd Methodology                                                                                                                                                                                    | 92                                                                        |

| 4 | Cros        | sbar Sc                                                          | heduler Design                                                                                                                                                                                    | 102                                                                       |

|   | 4.1         | Baselin                                                          | e Scheduler Design                                                                                                                                                                                | 102                                                                       |

|   |             |                                                                  |                                                                                                                                                                                                   |                                                                           |

|   |             | 4.1.1                                                            | Network Emulation Results                                                                                                                                                                         | 106                                                                       |

|   |             | 4.1.1<br>4.1.2                                                   | Network Emulation Results                                                                                                                                                                         |                                                                           |

|   | 4.2         | 4.1.2                                                            |                                                                                                                                                                                                   | 110                                                                       |

|   | 4.2         | 4.1.2<br>Pipeline                                                | Hardware Implementation                                                                                                                                                                           | 110<br>115                                                                |

|   | 4.2         | 4.1.2<br>Pipeline                                                | Hardware Implementation                                                                                                                                                                           | 110<br>115<br>117                                                         |

|   | 4.2         | 4.1.2<br>Pipeline<br>4.2.1                                       | Hardware Implementation                                                                                                                                                                           | 110<br>115<br>117<br>120                                                  |

|   | 4.2         | 4.1.2<br>Pipelino<br>4.2.1<br>4.2.2<br>4.2.3                     | Hardware Implementation                                                                                                                                                                           | 110<br>115<br>117<br>120<br>124                                           |

| 5 | 4.3         | 4.1.2<br>Pipelino<br>4.2.1<br>4.2.2<br>4.2.3<br>Summa            | Hardware Implementation                                                                                                                                                                           | 110<br>115<br>117<br>120<br>124                                           |

| 5 | 4.3         | 4.1.2<br>Pipelino<br>4.2.1<br>4.2.2<br>4.2.3<br>Summa            | Hardware Implementation                                                                                                                                                                           | 110<br>115<br>117<br>120<br>124<br>126<br><b>128</b>                      |

| 5 | 4.3<br>Clos | 4.1.2<br>Pipelino<br>4.2.1<br>4.2.2<br>4.2.3<br>Summa            | Hardware Implementation e Scheduler Design  Network Emulation Results  Hardware Implementation  Crossbar Scheduler Comparison  sry  Scheduler Design                                              | 110<br>115<br>117<br>120<br>124<br>126<br><b>128</b><br>129               |

| 5 | 4.3<br>Clos | 4.1.2 Pipeline 4.2.1 4.2.2 4.2.3 Summa Switch Global             | Hardware Implementation e Scheduler Design  Network Emulation Results  Hardware Implementation  Crossbar Scheduler Comparison  ary  Scheduler Design  Scheduler Design                            | 110<br>115<br>117<br>120<br>124<br>126<br><b>128</b><br>129<br>131        |

| 5 | 4.3<br>Clos | 4.1.2 Pipeline 4.2.1 4.2.2 4.2.3 Summa Switch Global 5.1.1 5.1.2 | Hardware Implementation e Scheduler Design  Network Emulation Results  Hardware Implementation  Crossbar Scheduler Comparison  ary  Scheduler Design  Scheduler Design  Network Emulation Results | 110<br>115<br>117<br>120<br>124<br>126<br><b>128</b><br>129<br>131<br>133 |

| Contents | 9 |

|----------|---|

| Contents |   |

|     |        | 5.2.2   | Scheduler Hardware Modules             | 137 |

|-----|--------|---------|----------------------------------------|-----|

|     |        | 5.2.3   | Network Emulation Results              | 148 |

|     |        | 5.2.4   | Hardware Implementation                | 149 |

|     |        | 5.2.5   | Switch Design Comparison               | 154 |

|     | 5.3    | Summa   | ary                                    | 159 |

| 6   | Expo   | eriment | al Demonstration                       | 162 |

|     | 6.1    | Contro  | l Plane Components                     | 162 |

|     |        | 6.1.1   | Server Network Interface               | 162 |

|     |        | 6.1.2   | Switch Scheduler                       | 163 |

|     | 6.2    | Experi  | mental Setup                           | 166 |

|     | 6.3    | Experi  | mental Demonstration and Results       | 169 |

|     |        | 6.3.1   | Scenario A                             | 169 |

|     |        | 6.3.2   | Scenario B                             | 172 |

|     |        | 6.3.3   | Asynchronous Control Plane Limitations | 175 |

|     | 6.4    | Balanc  | ed Pipeline Scheduler Design           | 175 |

|     | 6.5    | Networ  | rk Emulation Results                   | 177 |

|     | 6.6    | Summa   | ary                                    | 179 |

| 7   | Cone   | clusion | & Future Work                          | 182 |

|     | 7.1    | Conclu  | asion                                  | 182 |

|     | 7.2    | Future  | Work                                   | 190 |

| Bil | bliogr | aphy    |                                        | 194 |

# **List of Figures**

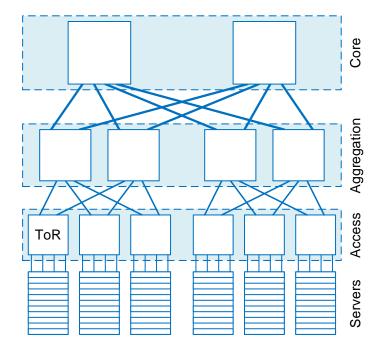

| 1.1  | A hierarchical tree network in traditional data centres                    | 21 |

|------|----------------------------------------------------------------------------|----|

| 1.2  | A leaf-spine network in current data centres                               | 22 |

| 2.1  | An N x N crossbar conceptual model                                         | 31 |

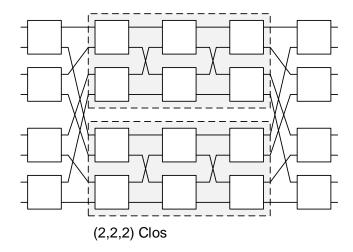

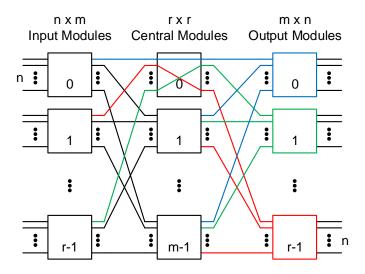

| 2.2  | A three-stage $(m,n,r)$ Clos network                                       | 32 |

| 2.3  | A (2,2,4) Clos network with two (2,2,2) Clos networks used as 4x4          |    |

|      | central modules. This is also referred to as an 8x8 Beneš network          |    |

|      | due to composition using only 2x2 switch modules                           | 34 |

| 2.4  | A traditional multi-rooted three-tier data centre network topology.        |    |

|      | Switch size and port capacity increase from access to core tiers           | 35 |

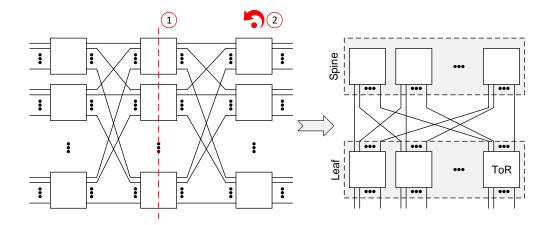

| 2.5  | The Leaf-Spine architecture. It is a Clos network folded along the         |    |

|      | middle and rotated by 90 degrees                                           | 36 |

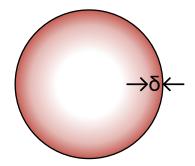

| 2.6  | Electrical link cross-section showing alternating current density dis-     |    |

|      | tribution at high data rates. Current flows mainly within a depth $\delta$ |    |

|      | from the link's outer edge or "skin". This phenomenon is known as          |    |

|      | the skin effect                                                            | 37 |

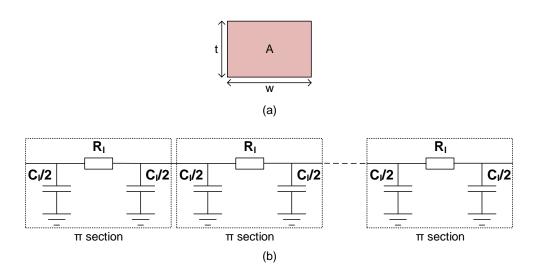

| 2.7  | On-chip wire model: (a) Wire cross-section and (b) The $\pi$ model         |    |

|      | for wire delay estimation                                                  | 39 |

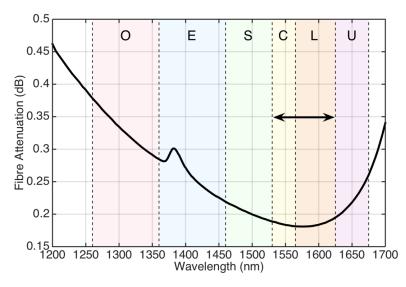

| 2.8  | Optical power loss in silica single-mode fibre for different wave-         |    |

|      | lengths                                                                    | 41 |

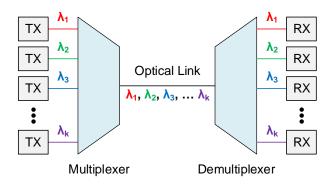

| 2.9  | Wavelength-division multiplexing (WDM)                                     | 42 |

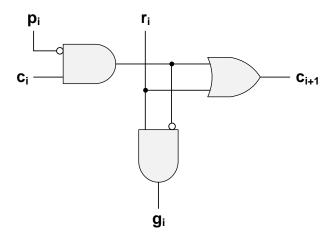

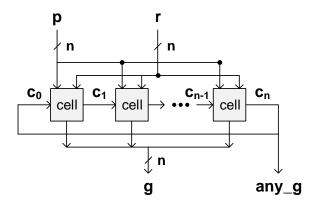

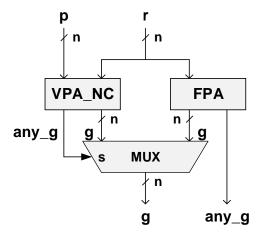

| 2.10 | A bit cell for a variable priority arbiter                                 | 45 |

| 2.11 | A variable priority arbiter.                                               | 46 |

| 2.12 | A variable priority arbiter optimised for hardware implementation          | 47 |

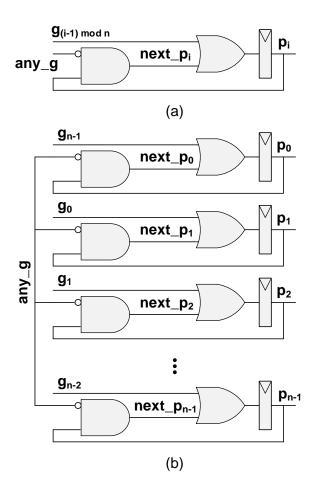

|      |                                                                            |    |

| 2.13 | Round-robin priority generator. (a) A one-bit slice and (b) An <i>n</i> -bit       |    |

|------|------------------------------------------------------------------------------------|----|

|      | priority generator                                                                 | 49 |

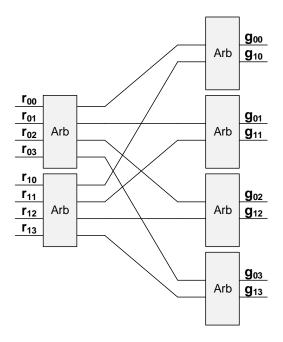

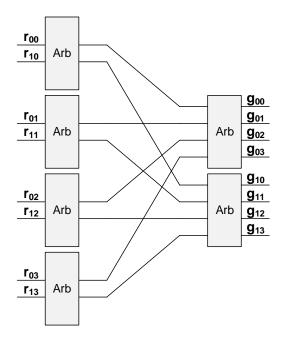

| 2.14 | A $2 \times 4$ input-first separable allocator                                     | 51 |

| 2.15 | A $2 \times 4$ output-first separable allocator                                    | 52 |

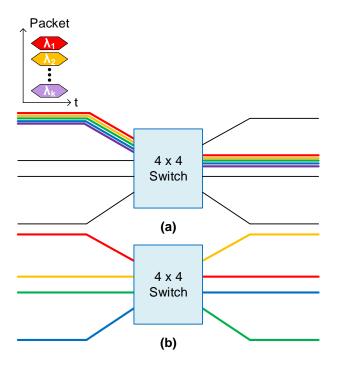

| 2.16 | Optical switch operation: (a) space switching and (b) wavelength                   |    |

|      | routing                                                                            | 54 |

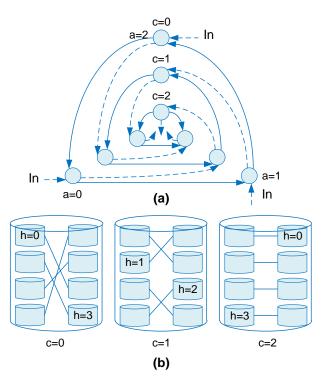

| 2.17 | A $12 \times 12$ Data Vortex with $C = 3$ , $H = 4$ and $A = 3$ . Module           |    |

|      | connectivity shown from (a) top view and (b) side view. Module                     |    |

|      | coordinates are (c,h,a), where $0 \le c \le C - 1$ , $0 \le h \le H - 1$ , $0 \le$ |    |

|      | $a \leq A-1$                                                                       | 66 |

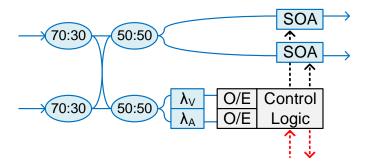

| 2.18 | A $2 \times 2$ Data Vortex SOA-based B&S module. Header valid (V)                  |    |

|      | and address (A) bits are recovered to make routing decisions. Con-                 |    |

|      | trol logic turns SOAs "on"/"off", based on address bit and input                   |    |

|      | deflection signal, and asserts output deflection signal, if necessary.             |    |

|      | Deflection input/output signals shown in red                                       | 67 |

| 2.19 | An $8 \times 8$ binary butterfly network and destination-tag routing from          |    |

|      | source 5 to destination 2. The destination address in binary is $2_{10}$ =         |    |

|      | $010_2$ and selects the route at each network stage as up (0), down (1),           |    |

|      | up (0). Regardless of the source, the pattern 010 always routes to                 |    |

|      | destination 5. This is valid for all possible destinations                         | 68 |

| 2.20 | A $2 \times 2$ SPINet SOA-based B&S module. Header valid (V) and                   |    |

|      | address (A) bits are recovered to make routing decisions. Control                  |    |

|      | logic performs routing-aware output port allocation and turns SOAs                 |    |

|      | "on"/"off"                                                                         | 69 |

| 2.21 | An $N \times N$ OPSquare switch. It is based on a parallel modular archi-          |    |

|      | tecture with distributed control                                                   | 72 |

| 2.22 | An $N \times N$ AWGR-based LION switch. The switch supports                        |    |

|      | all-optical token (AO-TOKEN)-based transmission and all-optical                    |    |

|      | negative acknowledgement (AO-NACK)-based re-transmission to                        |    |

|      | avoid packet loss                                                                  | 74 |

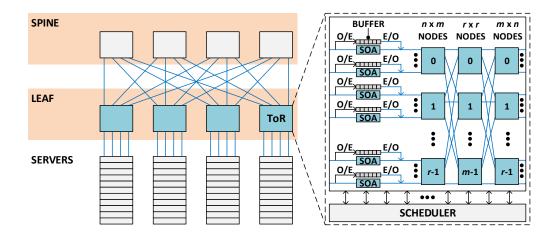

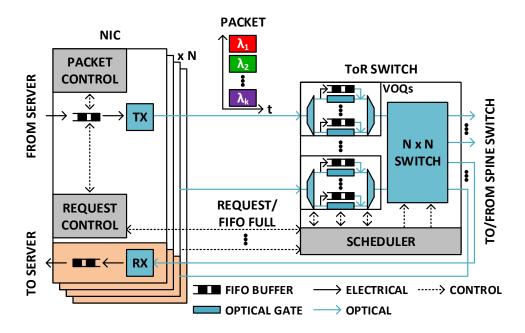

| 3.1 | Proposed data centre network concept. Input-buffered optical top-                          |     |

|-----|--------------------------------------------------------------------------------------------|-----|

|     | of-rack (ToR) switch reduces minimum packet latency and avoids                             |     |

|     | packet loss. A Clos network is a possible switch architecture.                             |     |

|     | A dedicated scheduler reconfigures the switch in nanoseconds.                              |     |

|     | Colour-coded in grey/black for electronic/electrical components                            |     |

|     | and in blue for optical components                                                         | 82  |

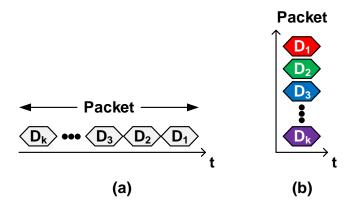

| 3.2 | Packet transmission in (a) serial format and (b) wavelength-parallel                       |     |

|     | format                                                                                     | 83  |

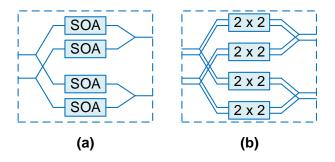

| 3.3 | Clos module architecture using parallel $2 \times 2$ SOA-based B&S                         |     |

|     | switch elements. The fundamental (a) $2 \times 2$ switch element is used                   |     |

|     | to build (b) a $4 \times 4$ module. An $8 \times 8$ module is built using the $4 \times 4$ |     |

|     | module, and every twofold increase in size is implemented as such,                         |     |

|     | recursively around the $2 \times 2$ base element                                           | 84  |

| 3.4 | Switch architecture comparison                                                             | 85  |

| 3.5 | Proposed system concept                                                                    | 86  |

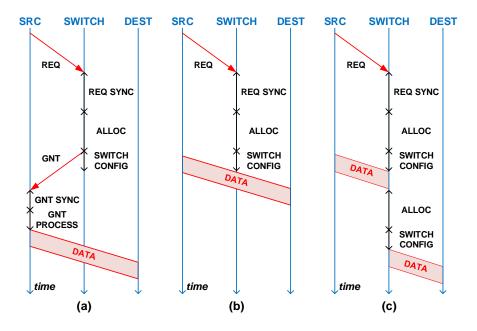

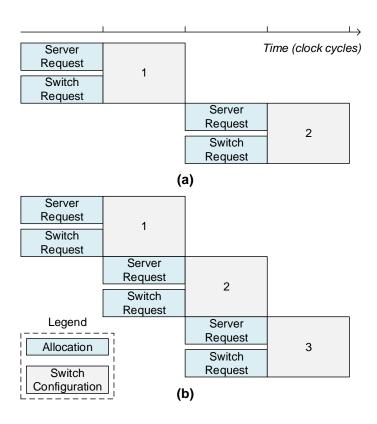

| 3.6 | Control delay comparison for two flow control methods: (a) non-                            |     |

|     | speculative, (b) speculative - successful allocation and (c) specula-                      |     |

|     | tive - failed allocation.                                                                  | 87  |

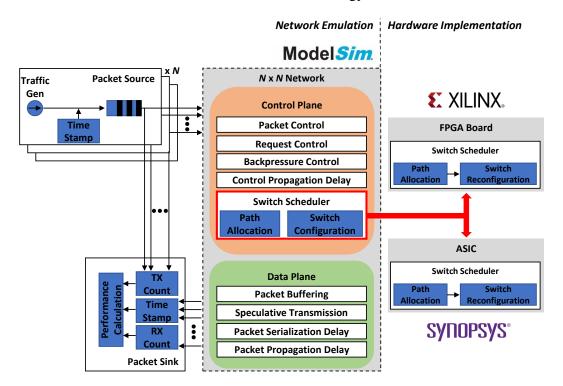

| 3.7 | Network emulation setup includes $N$ packets sources, the $N \times N$                     |     |

|     | network under test and the packet sink. The network module ver-                            |     |

|     | ifies control and data plane functionality and adds delays to accu-                        |     |

|     | rately model the system concept. Once performance is evaluated,                            |     |

|     | the scheduler is either implemented on an FPGA or synthesised as                           |     |

|     | an ASIC.                                                                                   | 94  |

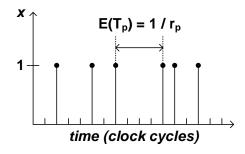

| 3.8 | Behaviour of a Bernoulli process injecting packets at a rate $r_p$ over                    |     |

|     | time. The expected injection period is $E(T_{\rm p})=1/r_{\rm p}.$                         | 96  |

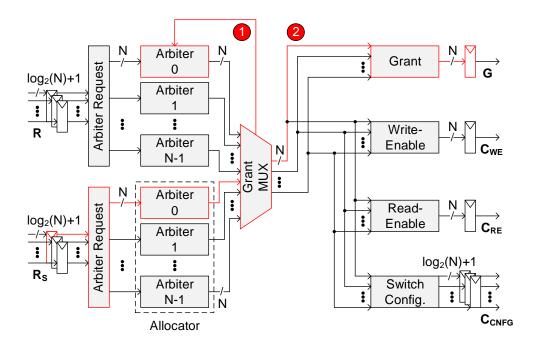

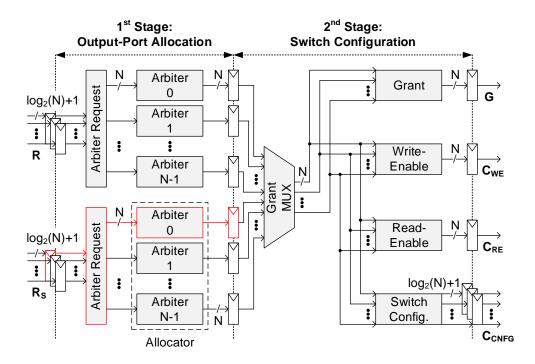

| 4.1 | Scheduler design for an $N \times N$ crossbar. There are two critical paths                |     |

|     | in the design, depending on $N$ , shown in red                                             | 103 |

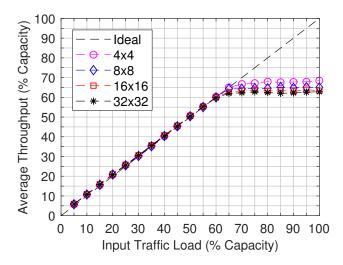

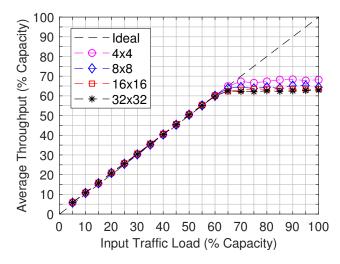

| 4.2 | Average switch throughput vs. input traffic load, under Bernoulli                          |     |

|     | traffic                                                                                    | 106 |

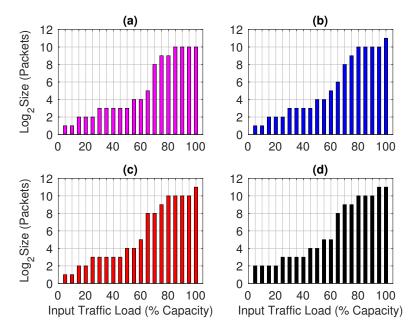

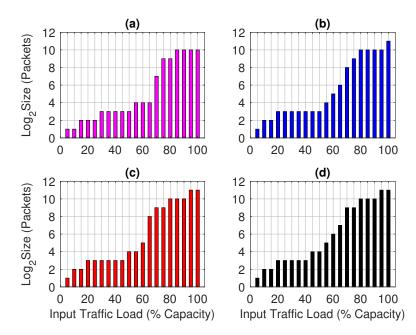

| 4.3  | Minimum switch buffer size vs. input traffic load: (a) $4 \times 4$ crossbar,               |

|------|---------------------------------------------------------------------------------------------|

|      | (b) $8 \times 8$ crossbar, (c) $16 \times 16$ crossbar and (d) $32 \times 32$ crossbar. The |

|      | crossbar is under control of the baseline scheduler                                         |

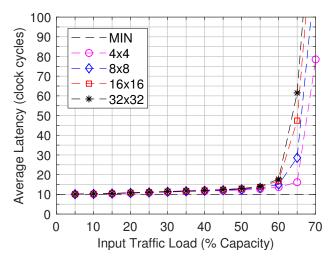

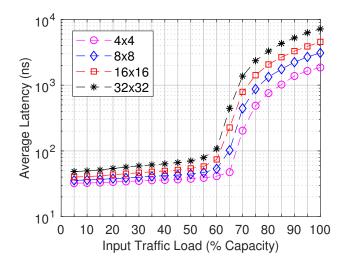

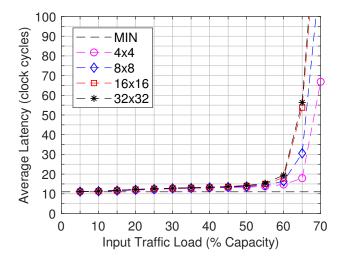

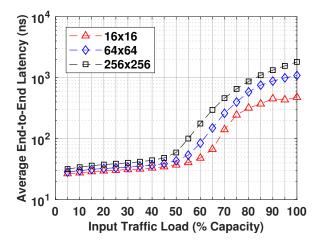

| 4.4  | Average end-to-end packet latency vs. input traffic load, for dif-                          |

|      | ferent switch sizes. Network model assumes 3 clock cycles prop-                             |

|      | agation delay to and from the switch, for both optical and electri-                         |

|      | cal links. Packets are 1 clock cycle long and injected based on a                           |

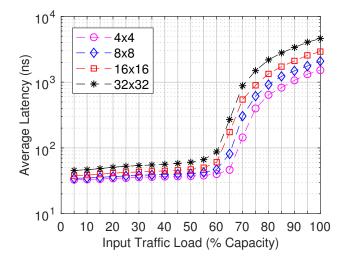

|      | Bernoulli process                                                                           |

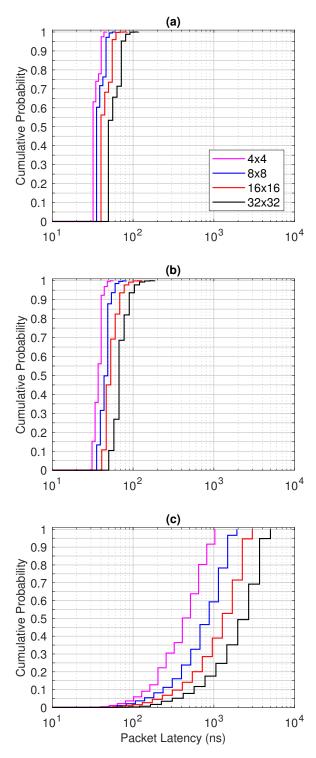

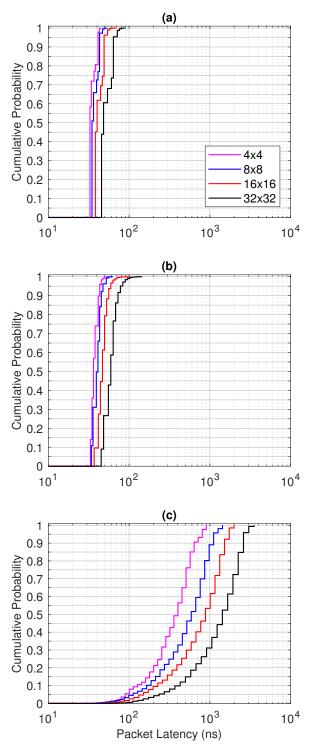

| 4.5  | Cumulative distribution of the packet end-to-end latency at (a) 25%,                        |

|      | (b) 50% and (c) 75% input traffic loads for different switch sizes.                         |

|      | The Network model assumes SOA-based crossbar with a 2 m link                                |

|      | distance to every connected source and destination. Packets are                             |

|      | 64 B, wavelength-striped at $4 \times 100$ Gb/s and injected based on a                     |

|      | Bernoulli process                                                                           |

| 4.6  | Packet end-to-end average latency vs. input traffic load, for dif-                          |

|      | ferent switch sizes. Network model assumes SOA-based crossbar                               |

|      | with a 2 m link distance to every connected source and destination.                         |

|      | Packets are 64 B, wavelength-striped at $4 \times 100$ Gb/s and injected                    |

|      | based on a Bernoulli process                                                                |

| 4.7  | Scheduler design parallelism: (a) spatial and (b) temporal 115                              |

| 4.8  | Scheduler design with 2-stage pipeline for an $N \times N$ crossbar. The                    |

|      | critical path in the design is shown in red                                                 |

| 4.9  | Average switch throughput vs. input traffic load, under Bernoulli                           |

|      | traffic                                                                                     |

| 4.10 | Minimum switch buffer size vs. input traffic load: (a) $4 \times 4$ crossbar,               |

|      | (b) $8 \times 8$ crossbar, (c) $16 \times 16$ crossbar and (d) $32 \times 32$ crossbar. The |

|      | crossbar is under control of the pipeline scheduler                                         |

| 4.11 | Average end-to-end packet latency vs. input traffic load, for dif-           |

|------|------------------------------------------------------------------------------|

|      | ferent switch sizes. Network model assumes 3 clock cycles prop-              |

|      | agation delay to and from the switch, for both optical and electri-          |

|      | cal links. Packets are 1 clock cycle long and injected based on a            |

|      | Bernoulli process                                                            |

| 4.12 | Cumulative distribution of the packet end-to-end latency at (a) 25%,         |

|      | (b) 50% and (c) 75% input traffic loads, for different switch sizes.         |

|      | The network model assumes SOA-based crossbar with a 2 m link                 |

|      | distance to every connected source and destination. Packets are              |

|      | 64 B, wavelength-striped at $4 \times 100$ Gb/s and injected based on a      |

|      | Bernoulli process                                                            |

| 4.13 | Average end-to-end packet latency vs. input traffic load, for differ-        |

|      | ent switch sizes. The network model assumes SOA-based crossbar               |

|      | with a 2 m link distance to every connected source and destination.          |

|      | Packets are 64 B, wavelength-striped at $4 \times 100$ Gb/s and injected     |

|      | based on a Bernoulli process                                                 |

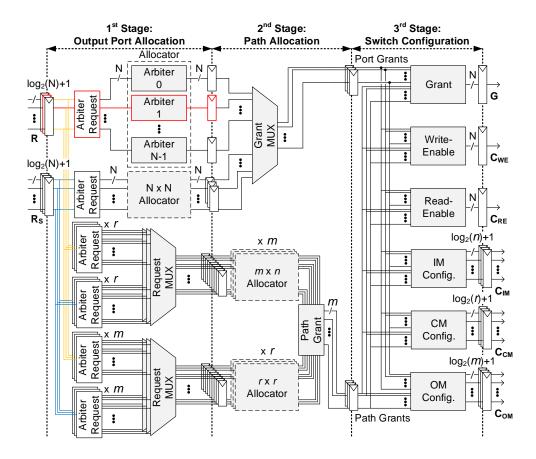

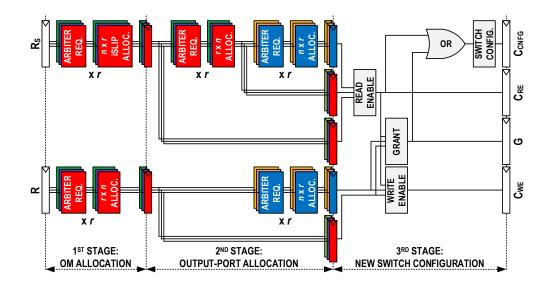

| 5.1  | Scheduler design with 3-stage pipeline for an $N \times N$ Clos switch.      |

|      | The critical path in the design is shown in red                              |

| 5.2  | Average switch throughput vs. input traffic load, for a $32\times32$         |

|      | switch built in different architectures, under Bernoulli traffic 132         |

| 5.3  | Average end-to-end packet latency vs input traffic load, for $32\times$      |

|      | 32 switches in different architecture and scheduler implementation           |

|      | on the Xilinx Virtex-7 XC7VX690T FPGA. The network model                     |

|      | assumes SOA-based Clos switch with a 2 m link distance to every              |

|      | connected source and destination. Packets are 64 B, wavelength-              |

|      | striped at $4 \times 100$ Gb/s and injected based on a Bernoulli process 135 |

| 5.4  | An (m,n,r) Clos network with strictly non-blocking modules. The              |

|      | proposed routing scheme, for $m = n = r$ Clos networks, assigns fixed        |

|      | paths to eliminate routing overhead and avoid contention at the cen-         |

|      | tral modules, simplifying the scheduler design and reducing its delay, 136   |

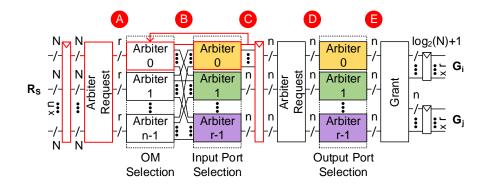

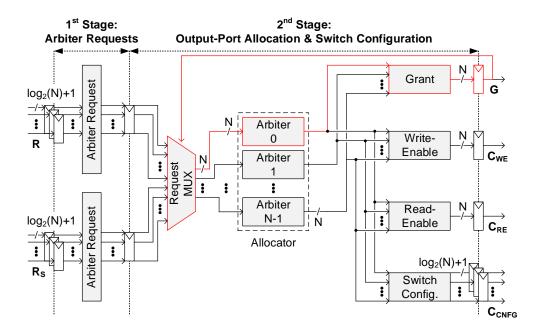

| 5.5  | Scheduler design with 3-stage pipeline for an $N \times N$ Clos switch, in               |

|------|------------------------------------------------------------------------------------------|

|      | which $m = n = r = \sqrt{N}$ . The critical path in the design is in the 1 <sup>st</sup> |

|      | pipeline stage, through the iSLIP allocator                                              |

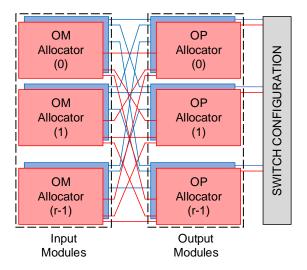

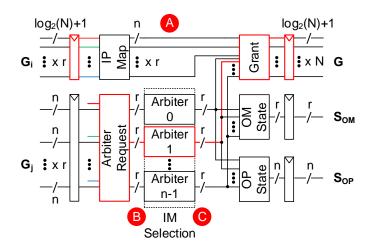

| 5.6  | Clos switch scheduler design in a planar-modular visualisation.                          |

|      | Planes operate independently and in parallel to allocate paths based                     |

|      | on output module (OM) and output port (OP) arbitration for the                           |

|      | Clos input and output modules. The switch configuration module                           |

|      | reconfigures the switch based on the allocation grants from both                         |

|      | planes                                                                                   |

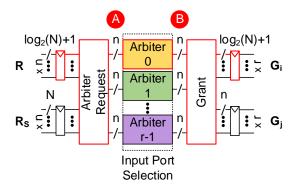

| 5.7  | Output module allocator design for new packets. The critical path                        |

|      | in the design is shown in red. Tags A and B are for cross-reference                      |

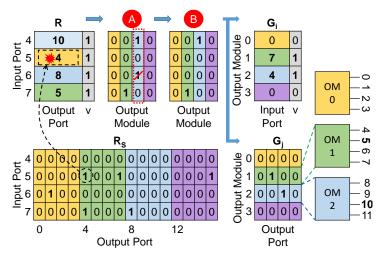

|      | with Fig. 5.8                                                                            |

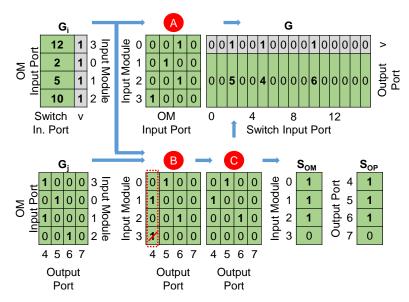

| 5.8  | Example request processing for new packets by the output module                          |

|      | allocator, for the 2 <sup>nd</sup> input module in a (4,4,4) Clos switch. Binary         |

|      | matrices are tagged for cross-reference with the digital design in                       |

|      | Fig. 5.7                                                                                 |

| 5.9  | Output module allocator design for switch VOQ packets. The crit-                         |

|      | ical path in the design is shown in red. Tags A-E are for cross-                         |

|      | reference with Fig. 5.10                                                                 |

| 5.10 | Example request processing for switch VOQ packets by the output                          |

|      | module allocator, for the 2 <sup>nd</sup> input module in a (4,4,4) Clos switch.         |

|      | Binary matrices are tagged for cross-reference with the digital de-                      |

|      | sign in Fig. 5.9                                                                         |

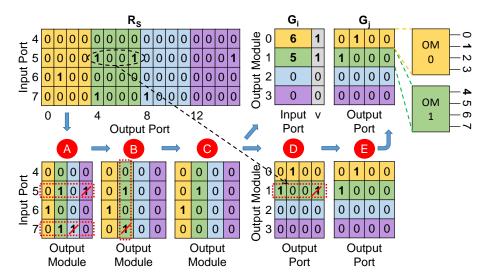

| 5.11 | Output port allocator design. The same design is used for new pack-                      |

|      | ets and for switch VOQ packets. The critical path in the design is                       |

|      | shown in red. Tags A-C are for cross-reference with Fig. 5.12 144                        |

| 5.12 | Example request processing by the output port allocator for the 2 <sup>nd</sup>          |

|      | output module, in a (4,4,4) Clos switch. Binary matrices are tagged                      |

|      | for cross-reference with the digital design in Fig. 5.11 144                             |

| 5.13 | Switch configuration module design. Blue-coded logic blocks are                  |

|------|----------------------------------------------------------------------------------|

|      | for VOQ packets and rest blocks for new packets. The critical path               |

|      | in the design is marked in red                                                   |

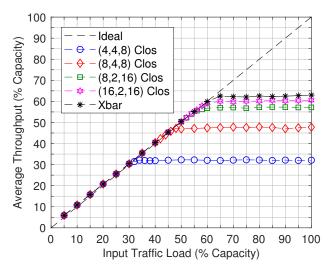

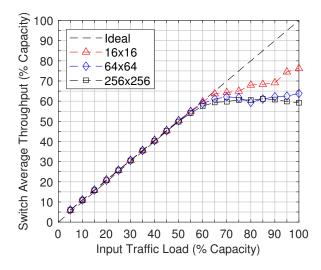

| 5.14 | Average switch throughput vs input traffic load, under Bernoulli                 |

|      | traffic                                                                          |

| 5.15 | Minimum switch virtual output queue (VOQ) size vs. input traf-                   |

|      | fic load: (a) $16 \times 16$ Clos switch, (b) $64 \times 64$ Clos switch and (c) |

|      | $256 \times 256$ Clos switch. All VOQs at every switch input port are            |

|      | considered, to ensure no packet loss                                             |

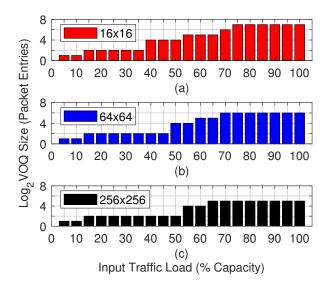

| 5.16 | Cumulative distribution of the packet end-to-end latency at (a) 25%,             |

|      | (b) 50% and (c) 75% input traffic loads, for different size Clos                 |

|      | switches, and ASIC scheduler. Network model assumes SOA-based                    |

|      | Clos switch with a 2 m link distance to every source and destination.            |

|      | Packets are 64 B, wavelength-striped at $8 \times 100$ Gb/s and injected         |

|      | based on a Bernoulli process                                                     |

| 5.17 | Average end-to-end latency vs. input traffic load, for different size            |

|      | Clos switches, and ASIC scheduler. Network model assumes SOA-                    |

|      | based Clos switch with a 2 m link distance to every source and                   |

|      | destination. Packets are 64 B, wavelength-striped at $8 \times 100$ Gb/s         |

|      | and injected based on a Bernoulli process                                        |

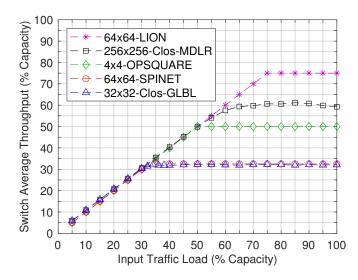

| 5.18 | Switch average throughput vs. input traffic load, for different switch           |

|      | designs, under Bernoulli traffic                                                 |

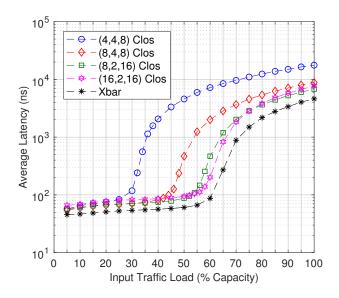

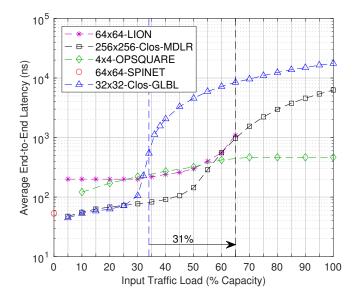

| 5.19 | Average end-to-end packet latency vs. input traffic load, for differ-            |

|      | ent switch designs. Clos-MDLR/GLBL latency is based on sched-                    |

|      | uler implementation on the Virtex-7 XC7V690T FPGA board. The                     |

|      | network model assumes a 2 m link distance to every source and des-               |

|      | tination. Packets are 64 B and injected based on a Bernoulli process. 158        |

| 6.1  | Scheduler design with 2-stage pipeline for an $N \times N$ crossbar              |

|      | switch. Critical path shown in red                                               |

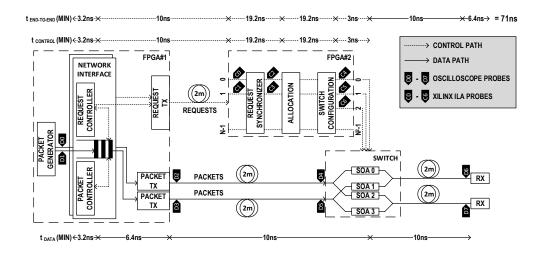

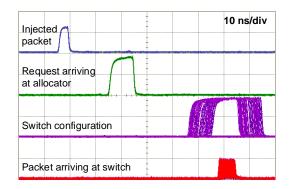

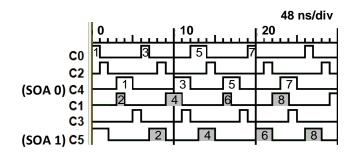

| 6.2 | The experimental setup. Control path and data path latency con-         |

|-----|-------------------------------------------------------------------------|

|     | tributions and the minimum end-to-end latency are marked on the         |

|     | figure. Oscilloscope probes D0-D7 are placed along the data path.       |

|     | Xilinx Integrated Logic Analyzer (ILA) probes C0-C6 are imple-          |

|     | mented onto the scheduler FPGA board                                    |

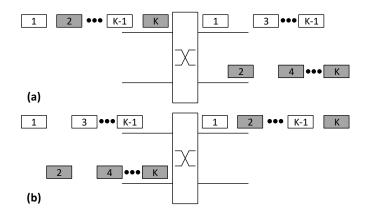

| 6.3 | Experimental scenarios: a) switching packets from an input port to      |

|     | two output ports and b) switching packets from two input ports to       |

|     | an output port                                                          |

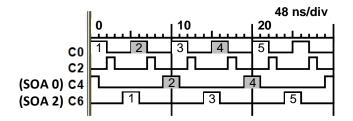

| 6.4 | Scheduler shown allocating the two switch output ports in turn, one     |

|     | at a time, to the requesting server network interface. Traces are       |

|     | labelled according to the probe placement shown in Fig. 6.2. Each       |

|     | subdivision is $1T_{\text{scheduler}}$                                  |

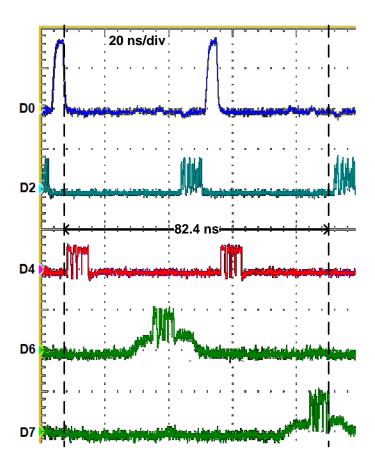

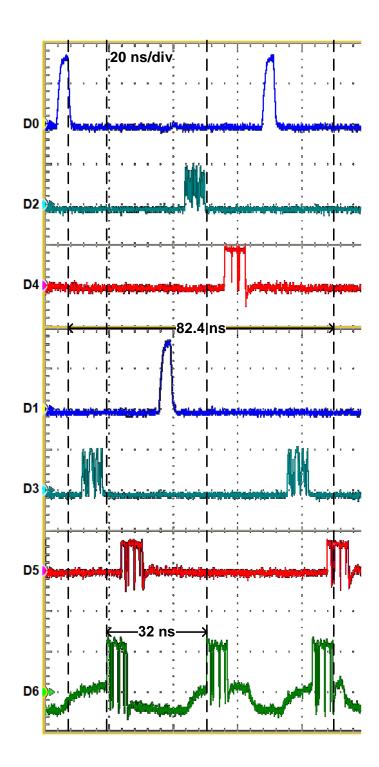

| 6.5 | Data path from a server network interface to the two switch out-        |

|     | put ports. Traces are labelled according to the probe placement         |

|     | shown in Fig. 6.2. The minimum end-to-end latency measurement           |

|     | is marked in this Figure                                                |

| 6.6 | Effect of request synchronisation uncertainty on the switch config-     |

|     | uration. The switch configuration pulse timing is captured using a      |

|     | 5-second persistence on the oscilloscope. The speculatively trans-      |

|     | mitted packet is shown arriving at the switch SOA at the right time 172 |

| 6.7 | Scheduler shown allocating one switch output port to the two re-        |

|     | questing server network interfaces, one at a time. Traces are la-       |

|     | belled according to the probe placement shown in Fig. 6.2. Each         |

|     | subdivision is $1T_{\text{scheduler}}$                                  |

| 6.8 | Data path from the two server network interfaces to the first switch    |

|     | output port. Traces are labelled according to the probe placement       |

|     | shown in Fig. 6.2. The minimum end-to-end latency and packet            |

|     | spacing measurements are marked in this Figure                          |

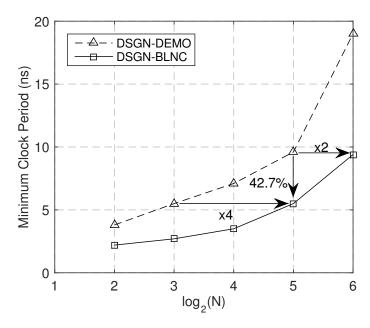

| 6.9 | Minimum clock period vs. switch size, for two crossbar scheduler        |

|     | designs, implemented on the Xilinx Kintex-7 XC7K325T FPGA 176           |

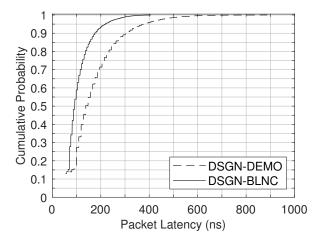

| 6.10 | Cumulative distribution function of packet end-to-end latency, at          |    |

|------|----------------------------------------------------------------------------|----|

|      | 50% input traffic load, for two different scheduler designs imple-         |    |

|      | mented on the Xilinx Kintex-7 XC7K325T FPGA. The network                   |    |

|      | model assumes an SOA-based, $32 \times 32$ crossbar switch with a 2 m      |    |

|      | link distance to every connected source and destination. Packets are       |    |

|      | 64 bytes, wavelength-striped at $8 \times 10$ Gb/s and injected based on a |    |

|      | Bernoulli process                                                          | 79 |

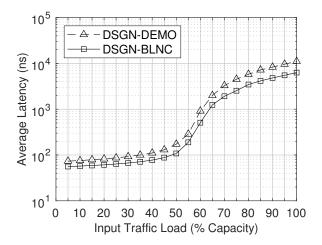

| 6.11 | Average end-to-end packet latency vs. input traffic load, for              |    |

|      | two different scheduler designs, implemented on Xilinx Kintex-7            |    |

|      | XC7K325T FPGA. The network model assumes an SOA-based,                     |    |

|      | $32 \times 32$ crossbar switch with a 2 m link distance to every connected |    |

|      | source and destination. Packets are 64 bytes, wavelength-striped at        |    |

|      | $8 \times 10$ Gb/s and injected based on a Bernoulli process               | 79 |

# **List of Tables**

| 2.1 | Switching Technologies Comparison 61                                           |

|-----|--------------------------------------------------------------------------------|

| 2.2 | Flow Control Comparison for Different Switch Architectures 79                  |

| 3.1 | Parameters for Network Emulation                                               |

| 3.2 | Parameters for Absolute Packet Latency Calculation                             |

| 4.1 | Throughput Saturation Traffic Load vs. Switch Size 107                         |

| 4.2 | Xilinx Virtex-7 XC7VX690T FPGA Timing and Utilisation Results. 110             |

| 4.3 | Minimum End-to-End Packet Latency vs. Switch Size                              |

| 4.4 | Comparison of Throughput Saturation Traffic Load vs. Switch Size. 118          |

| 4.5 | Xilinx Virtex-7 XC7VX690T FPGA Timing and Utilisation Results. 120             |

| 4.6 | Minimum End-to-End Packet Latency vs. Switch Size                              |

| 4.7 | Minimum Clock Period for Different Scheduler Designs 125                       |

| 5.1 | Throughput Saturation Traffic Load vs. $32 \times 32$ Switch Architecture. 133 |

| 5.2 | Xilinx Virtex-7 XC7V690T FPGA Timing and Utilisation Results 133               |

| 5.3 | Minimum Packet Latency vs. $32 \times 32$ Switch Architecture 134              |

| 5.4 | Scheduler Modules Minimum Clock Period for ASIC Synthesis 150                  |

| 5.5 | Scheduler Minimum Clock Period for FPGA Implementation 151                     |

| 5.6 | Minimum End-to-End Packet Latency vs. Switch Size 152                          |

| 5.7 | Scheduling Comparison                                                          |

| 6.1 | Parameters for Network Emulation 178                                           |

## Chapter 1

# Introduction

The ever increasing Internet traffic is dominated by data centre traffic, which is projected to reach 20.6 zettabytes per year by 2021 [1]. Data centre traffic can be divided into three main types: (a) traffic between data centres and users, (b) traffic between data centres and (c) traffic within data centres. The latter accounts for more than 70% of the data centre traffic and it is exchanged between network servers. It is commonly known as *East-West* traffic, as opposed to the *North-South* traffic which enters and exits the network, in traditional data centres. The East-West traffic is driven by a number of technological trends. The growth of cloud computing and virtualisation has led to servers running multiple virtual workloads, which are commonly migrated from one server to another. Storage replication is also used to a great extend, to ensure business continuity, having a significant contribution to the inter-server traffic. Furthermore, new data centre applications rely on multiple workloads distributed to different servers to run in parallel, thus generating traffic between servers [1, 2].

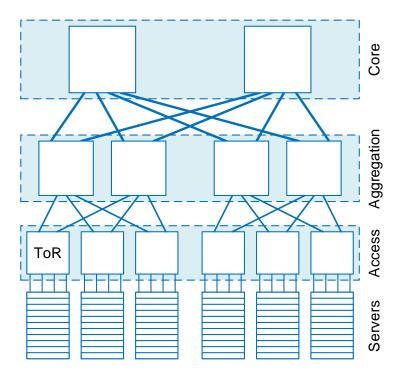

The increasing East-West traffic has caused a shift in the data centre network topology, due to stringent bandwidth and latency requirements. In the traditional data centre, network switches were arranged in a tree topology with a three-layer hierarchy, as illustrated in Fig. 1.1. A rack of servers at the network edge connected to a top-of-rack (ToR) switch in the *access* layer. Switches in the *aggregation* layer would then interconnect the racks. Finally, switches in the *core* layer were used to interconnect aggregation switches, in order to increase the network size and the

Figure 1.1: A hierarchical tree network in traditional data centres.

performance. The switch port count and bit rate would be higher moving from the access to the core layer, to support the higher volume of traffic in the upper layers. To reduce network cost, *over-subscription* was often used at the network layers. This refers to reducing the total uplink bandwidth with respect to the total downlink bandwidth. This architectural model, although it catered to North-South traffic, is not well suited for the East-West traffic exhibited in today's data centres. Traffic routed over different paths may traverse a different number of switches, leading to unpredictable latency. Moreover, the high over-subscription ratios that are typically used, would limit server throughput.

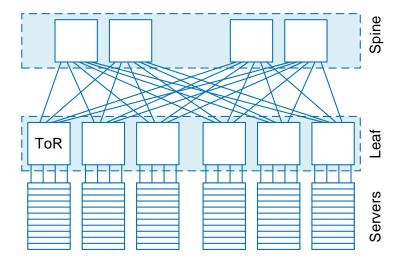

Small-scale data centre networks are now built in the *leaf-spine* topology [1, 3], illustrated in Fig. 1.2. Compared to the traditional hierarchical tree, this topology is flatter as it consists of only two layers; the *leaf* layer, in which the ToR switches lie, and the *spine*, which interconnects the ToR switches [4]. Also, paths are equidistant, in terms of number of hops, with servers in different racks experiencing only a three-hop latency. Therefore, the minimum inter-server latency is low and predictable,

Figure 1.2: A leaf-spine network in current data centres.

which favours East-West traffic [5]. Furthermore, every leaf (or ToR) switch is connected to a spine switch and vice versa. Hence, in theory, no over-subscription is applied, delivering full bisection bandwidth for the server communication. Also, commodity switches can be deployed across the entire architecture, giving a more cost-effective solution than the hierarchical tree model [6].

The electrical data centre interconnect, however, runs into physical limitations, as the requirements on network size and bandwidth continue to increase. Due to frequency-dependent losses, the length of an electrical link is limited as the bit rate increases [7]. At 10 Gb/s, the transmission distance of copper transmission lines is typically no longer than 10 m, to avoid signal distortion [8]. The bandwidth of an electronic switch is also limited. The number of high-speed pins, available on the switch chip, or the number of connectors fitting on a rack unit front panel, limit the switched bandwidth [9]. The electronic switch design, as well as its power consumption, are bit rate-dependent. An electronic switch dissipates energy with every bit transition, thus consumes power proportional to the bit rate [10, 11, 12].

Optical interconnects, for intra-data centre networking, is an inevitable next step for sustainable performance increase. A key optical technology, to significantly increase bit rate, is wavelength-division multiplexing (WDM) [13]. It exploits the

very high bandwidth of an optical waveguide, such as fibre, to multiplex together *k* independent data streams, modulated on dedicated wavelengths, that can propagate simultaneously. The low loss and high bandwidth (through WDM) of an optical fibre, overcomes the bit rate-distance limitation of electrical transmission lines and allows for a low energy per bit to be achieved. In fact, optical fibre is already in use in data centres, for point-to-point connectivity between switches [3, 14]. The switches, however, are still electronic, which creates a bandwidth bottleneck and limits energy efficiency. Optical switching is the sensible way forward. Integrated photonics that use WDM, is a viable solution to overcome the pin and front panel connector count limitations, and continue increasing the switched bandwidth. The building blocks of an optical switch are transparent to the data bit rate. Thus, (a) the switch design does not have to change, as bit rates continue to increase and (b) the power consumed is independent of the switched bandwidth. Optical switching is therefore a key enabler for network scalability.

Depending on the building block technology, the reconfiguration time of an optical switch, varies from milliseconds to nanoseconds. Switches built as *microelectro-mechanical systems* or based on *piezoelectric* beam steering technology, are already commercially available [15, 16]. Their high port count (100s of ports) and low loss allow building a large data centre network, without any signal degradation issues. However, these technologies limit the switch reconfiguration time to 10s of milliseconds, suitable only for *circuit* switching. Several optical circuit-switched network architectures have been proposed, based on such switches applied at the network core, to handle high-volume traffic. Notable examples are the RotorNet [17], Helios [8] and c-Through [18] architectures. Nevertheless, electronic packet switching is still needed to handle small-size traffic or traffic that is bursty and rapidly changing [19].

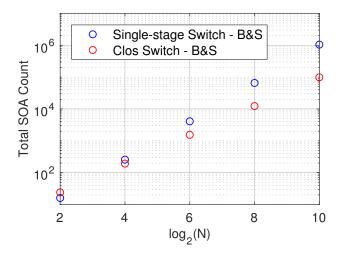

#### 1.1 Research Problem

Optical packet switching is an attractive alternative. The capability of switching on a per packet basis means that this solution can be widely deployed in the network, in any hierarchy layer, without any limitations on the traffic stability or volume. To support packet switching, the switch needs to be reconfigurable in nanoseconds. A suitable technology is the semiconductor optical amplifier (SOA), used as an optical gate, with switching transients of the order of 100 ps [20]. SOA-based optical switch prototypes, such as the OPSquare [21], SPINet [11], OSMOSIS [12] and Data Vortex [22], have been demonstrated experimentally. They all use SOA gates in a broadcast-and-select configuration to build *crossbar* switching modules. The modules are then used in a multi-stage architecture to scale the switch size.

A switch built entirely as a photonic-integrated circuit (PIC), is a practical approach to cost- and energy-effective switching [9, 11]. Photonic-integrated packet switches have been demonstrated based on SOA [23], Mach-Zehnder interferometer (MZI) [24] and micro-ring resonator (MRR) [25] technologies. Network scalability is limited by optical loss, crosstalk and noise accumulated per optical switch. The inherent amplification of an SOA compensates for loss and, when deactivated, it strongly suppresses crosstalk, making it an attractive technology. A switch built by arranging SOA-based crossbar modules in a three-stage *Clos* network [26] topology, has been shown viable at least up to a  $64 \times 64$  size, with a low level of noise [23]. An optical switch of this size can replace the currently electronic ToR switch in the leaf layer (Fig. 1.2), accommodating sufficient optical links to interconnect a rack of servers to the electronic switches in the core layer. In the resulting data centre network, the most distant servers communicate with a minimum latency of two hops; one hop from the source server to a core switch and another hop to the destination server.

Despite the demonstration of nanosecond-reconfigurable photonic-integrated switch architectures, optical packet switching is not yet employed in data centres. The main impediments are the lack of practical random-access memory and limited optical signal processing capabilities. A more pressing challenge, in optical packet switch design, is the speed of the accompanying control plane. The control plane implements the switch's flow control; the allocation of switch resources, such as output ports, also referred to as switch *scheduling*. Scheduling needs to be executed

on packet timescales. However, as the line rate keeps increasing, the packet duration gets smaller which places stringent requirements on scheduling delay. To maintain a low scheduling delay, as the switch size increases, is another challenge.

To this end, the research conducted and described in the thesis addresses the scheduling problem; the design of parallel hardware schedulers for nanosecond crossbar and Clos switch scheduling. The focus is to achieve ultra-low minimum packet latency, which is particularly important for small-size packets, but also to achieve a high switch throughput as the input traffic load is increased. The aim is to deliver scalable optical packet switching to replace electronic switches, at least at the leaf network layer, for future data centres. The scheduler is part of a novel switch system concept that is proposed, which uses electronics for buffering and processing and optics for low latency and high bandwidth packet switching.

#### 1.2 Thesis Structure

The remainder of the thesis is structured as follows:

Chapter 2 reviews the literature to set the foundation on the thesis topic. The target data centre architecture is presented and its performance limitations due to the currently electrical interconnect, are discussed. Optical networking for sustainable performance increase is argued. The significance and design of resource allocation circuits, for packet switch scheduling, is discussed. Optical switch technologies and demonstrated prototypes are compared.

Chapter 3 introduces the proposed system concept, covering the design of the network interface, at every node, and the switch design, which addresses the internal architecture, routing method and flow control. The proposed system is compared to the other switch designs reviewed in Chapter 2. The tools and methodology to implement the switch control plane and assess switch performance, are described. This includes the development details of a cycleaccurate network emulator with packet-level accuracy.

Chapter 4 presents the register-transfer level (RTL) design of a nanosecond scheduler, for crossbar switches. The design has been optimised for clock

speed using digital design techniques for parallelism. The crossbar scheduler is implemented on hardware to measure the minimum clock period and assess control plane scaling. Switch average throughput and packet latency, under scheduler control, are measured in the network emulator.

Chapter 5 focuses on the size scalability of the proposed switching system. The RTL designs of two highly-parallel schedulers, for switches built in a Clos network topology, are presented. Routing algorithms, executable in a single scheduler clock period, are applied. Clock period results for scheduler synthesis as an application-specific integrated circuit (ASIC) are presented, to verify scalability. The Clos switch, under control of either scheduler, is compared to the reviewed designs in Chapter 2, in terms of scheduling delay, average packet latency and throughput. The Clos scheduler designs have been published in [27, 28].

Chapter 6 verifies experimentally the proposed system concept. A proof-of-concept control plane demonstrator is built and used to showcase optical packet switching. The improvement in switch performance, under control of the optimised crossbar scheduler, presented in Chapter 4, is quantified. The performance implications of using an asynchronous control plane are discussed. The experimental demonstration has been published in [29, 30].

*Chapter* 7 draws conclusions based on conducted research and the results obtained. Potential research directions, as part of future work, are suggested.

## 1.3 Key Contributions

As a result of the work conducted, specialised tooling has been developed and a number of contributions to the research field have been made. The key contributions are listed below:

An entire network emulator has been developed for control plane verification and performance evaluation of the network under test, with a packet level of detail. This includes traffic sources, network interfaces, a switch time model and the switch scheduler. All these network components are implemented as hardware modules, developed in *SystemVerilog*; a hardware description and verification language. This allows (a) for cycle-accurate measurements and (b) directly implementing the emulator modules on a hardware platform, such as a field-programmable gate array (FPGA). The emulator adds delays for packet and control propagation and for packet (de)serialisation. A traffic sink collects all packets in the emulation for packet latency and switch throughput measurements. The emulator is fully parameterised, to evaluate performance at different network sizes, and it is transparent to the network topology.

- A highly parallel and scalable scheduler has been designed for crossbar switches. The scheduler allocates switch paths and reconfigures the switch in two clock cycles. Implementation on a commercial FPGA board showed a minimum clock period of 5.0 ns for a 32 × 32 crossbar. That is a total scheduling delay of 10 ns, which enables switching on a per packet basis.

- A routing algorithm for Clos networks has been developed. A Clos network, in certain topological configurations, has been shown to be a viable switch architecture for scalable photonic-integrated switching. Route calculation for a non-blocking Clos network, using the traditional algorithm, is unsuitable for packet switching due to its long delay. A novel routing algorithm is proposed to assign paths in a single hardware clock cycle and also eliminate contention at the central switching nodes in the Clos network. The trade-off is reduced throughput as it makes the Clos network blocking.

- A highly parallel and scalable scheduler has been designed for Clos-network switches. The scheduler is divided into arbitration and switch reconfiguration hardware modules. Each arbitration module corresponds to a switching node in the Clos architecture. This allows for distributed scheduling, to achieve a shorter minimum clock period for a larger switch size. Every hardware module is synthesised as an application-specific integrated circuit (ASIC), in a 45 nm CMOS process, and optimised for clock speed. For a 256 × 256 Clos

switch, a minimum clock period of 2.0 ns is achieved, or 7.0 ns for FPGA implementation. The scheduler allocates switch paths and reconfigures the switch in three clock cycles, one of which is for assigning paths using the routing algorithm discussed above. Therefore, the total scheduling delay is 6.0 ns, for a 256-port Clos switch and an ASIC scheduler, suitable for large-scale packet switching. This is currently the lowest scheduling delay, for a Clos switch of this size, reported in the research field.

• A control plane experimental demonstrator is built to verify the proposed system concept. The control plane, including server network interfaces and switch scheduler, is implemented on FPGAs in an experimental setup, for a 32 × 32 crossbar. As is the case in a real network, the demonstrated control plane is asynchronous; server network interfaces and switch/scheduler are ran from independent crystal oscillators. The clock constraints and scheduler critical path are discussed in detail. The control plane delay components are identified and measured. The implications of asynchronous operation on the switch performance and the significance of the scheduler clock period, are discussed. Using the FPGA-based control plane, switching packets with a minimum end-to-end packet latency of 71.0 ns is demonstrated, for a rack-scale network and 64-byte packets serialised at 8 × 10 Gb/s.

#### 1.4 List of Publications

The research work described in the thesis, has led to a number of publications in journals and conferences, as listed below:

Journal Publications:

- P. Andreades and G. Zervas, "Parallel modular scheduler design for Clos switches in optical data centre networks," to appear in *IEEE/OSA Journal of Lightwave Technology*, April 2020.

- 2. **P. Andreades**, K. Clark, P. M. Watts, and G. Zervas, "Experimental demonstration of an ultra-low latency control plane for optical packet switching in

data center networks," *Optical Switching and Networking*, vol.32, pp. 51-60, November 2019.

#### Conference Publications:

- 1. **P. Andreades** and G. Zervas, "Parallel distributed schedulers for scalable photonic integrated packet switching," in *Proceedings of the IEEE Conference on Photonics in Switching and Computing*, September 2018.

- 2. **P. Andreades** and P. M. Watts, "Low latency parallel schedulers for photonic integrated optical switch architectures in data centre networks," in *Proceedings of the IEEE European Conference on Optical Communication*, September 2017.

- 3. **P. Andreades**, Y. Wang, J. Shen, S. Liu, and P. M. Watts, "Experimental demonstration of 75 ns end-to-end latency in an optical top-of-rack switch," in *Proceedings of the IEEE/OSA Optical Fiber Communications Conference and Exhibition*, March 2015.

## Chapter 2

## **Literature Review**

This chapter introduces the evolution of the data centre architecture and its current limitations, imposed by the electrical interconnect, which motivated the application of optical networking. The main benefits of optical interconnects, in switching in particular, are discussed. Key technologies, upon which an optical switch is built, are reviewed in detail. Renowned optically-switched architectures in the field and their approach to optical packet switch challenges, including scheduling, are also critically reviewed. The fundamentals of resource allocation design, critical for switch scheduling implemented in hardware, are presented.

## 2.1 Non-blocking Architectures

A network is *strictly* non-blocking if a dedicated path can be allocated without any conflicts for any permutation of unused sources (inputs) and destinations (outputs) [31]. If any new permutation is possible, but rearranging existing connections is required, then that network is *rearrangeably* non-blocking. Otherwise, the network is simply blocking. These definitions apply to *unicast* traffic where an input can be connected to at most one output at a time.

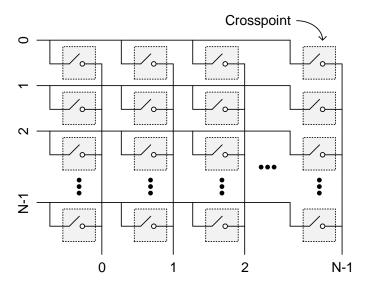

#### 2.1.1 Crossbar

A crossbar architecture implements an array of crosspoints where each crosspoint enables a direct connection between an input port and an output port, when the crosspoint is set. Figure 2.1 illustrates a conceptual model of an  $N \times N$  crossbar. The array consists of  $N^2$  crosspoints which enable switching traffic from an input

**Figure 2.1:** An N x N crossbar conceptual model.

port to an output port. In practice, an electronic crossbar is implemented using N N:1 multiplexers, one for each output. The multiplexer select signal chooses at most one out of N inputs to connect to the output. Optical implementations of a crossbar switch are discussed in section 2.4.

In a crossbar switch every input is directly connected to an output, through a dedicated path, thus the architecture is strictly non-blocking. Connectivity is as simple to establish as setting the appropriate crosspoint. Also, no routing is required which simplifies switch control. At medium sizes, crossbars are commonly used as electronic switches. However, the quadratic growth of crosspoints with the switch size, N, limits the switch scalability, because the implementation complexity and cost increase rapidly. Furthermore, the delay to schedule a crossbar may become prohibitively long, for switching on a per packet basis, as the switch size grows. This topic is extensively covered in section 2.5.

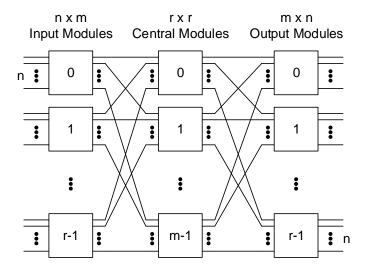

#### 2.1.2 Clos Network

A Clos network is built by arranging switch modules into a 3-stage architecture in which every central module (CM) has one input link from each input module (IM) and one output link to each output module (OM) [26, 31], as illustrated in Fig. 2.2.

**Figure 2.2:** A three-stage (m,n,r) Clos network.

The modules are also non-blocking and can be implemented as crossbar switches. The entire network can be described by the triple (m, n, r) where m is the number of CMs, n is the number of input/output ports on each IM/OM and r is the number of IMs and OMs. Hence, the network has N = nr input and output ports in total. For referencing the input and output ports, we denote input port a on IM a as a in IM a and output port a on OM a as a in IMa and output port a on OM a in IMa as a in IMa and output port a on OM a in IMa as a in IMa and output port a on OM a in IMa as a in IMa and output port a on OM a in IMa i

Unlike in a crossbar, where there is a single path from an input to an output port, in a Clos network there are m possible paths; one through each of the CMs. It is due to this path diversity that the network is non-blocking. For unicast traffic, depending on the number of CMs (m), the Clos network can be either:

- 1. Strictly non-blocking, when  $m \ge 2n 1$

- 2. Rearrangeably non-blocking, when  $m \ge n$

The ratio m/n is known as the *expansion* ratio, referring to the expansion in the input stage. An expansion ratio of 2n - 1/n is the minimum requirement for strictly non-blocking connectivity.

Routing unicast traffic from IM(x,a) to OM(y,b), in a strictly non-blocking Clos network, is simple; a CM is selected whose input and output ports are free

for both IM x and OM y. In a rearrangeable Clos network, however, less paths are available making routing more complex; the path from IM(x,a) to OM(y,b) may have to be changed so that another input-output pair uses that CM. Nevertheless, the rearrangeable Clos network is simpler to implement as it requires (2n-1)/n less CMs. For unicast traffic, the *looping* algorithm loops the current routing matrix re-arranging existing connections to add new ones, resolving any arising conflicts.

It is often desired that the network is constructed using same-size modules. In that case, a Clos network can be scaled up using larger modules or scaled out using more network stages or using both techniques. A rearrangeable Clos network with  $m=n=r=\sqrt{N}$  has  $n^2$  ports using  $n\times n$  modules. If this  $n^2\times n^2$  network is now used as a single central module, and  $n\times n$  modules are still used at the input and output stages, the resulting 5-stage network will have  $n^3$  ports. Figure 2.3 shows a 5-stage (2,2,4) Clos network built entirely out  $2\times 2$  modules where each  $4\times 4$  central module is itself a (2,2,2) Clos network. In general, a Clos network with  $n\times n$  modules in 2x+1 stages provides  $n^{x+1}$  ports. Nevertheless, as the number of stages increases, routing becomes more complex; the looping algorithm needs to be applied multiple times working from outside to inside. Also, for strictly non-blocking connectivity, expansion is required at the input stage of each Clos network. In order to reduce wiring complexity, the symmetry of a multi-stage Clos network can be exploited, by folding it along the middle. In this way, co-located network stages share common packaging.

#### 2.1.2.1 Beneš Network

A Clos network built entirely using only  $2 \times 2$  modules is called a Beneš network. This is illustrated in Fig. 2.3. Such networks are particularly interesting as they require the minimum number of crosspoints to provide rearrangeable non-blocking connectivity between  $N = 2^x$  ports. However, 2x - 1 stages of  $2^{x-1}$  switch modules are required. Assuming 4 crosspoints per module, the total number of crosspoints required in an  $N \times N$  Beneš network is  $(2x - 1)2^{x+1}$ .

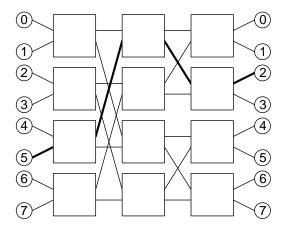

**Figure 2.3:** A (2,2,4) Clos network with two (2,2,2) Clos networks used as 4x4 central modules. This is also referred to as an 8x8 Beneš network due to composition using only 2x2 switch modules.

#### 2.2 Data Centre Network Architectures

The traffic exchanged between data centre servers, places stringent requirements on the network bandwidth and latency [2]. This section first discusses the conventional topology deployed in data centre networks and its limitations, before presenting the topology currently used to address inter-server traffic requirements.

#### 2.2.1 Hierarchical Tree

The traditional data centre network was built in a tree topology with either two or three hierarchy tiers, depending on the required size [6, 32]. Connecting more than 25 thousand servers would require a three-tier tree with the *core* tier at the root of the tree, the *aggregation* tier in the middle and the *access* tier at the leaves of the tree, as illustrated in Fig. 2.4. In a two-tiered tree the core and aggregation layers were combined into one core tier, accommodating 5 to 8 thousand servers [6]. In general, the tree topology was suitable for traffic entering and exiting the data centre, also known as "North-South" traffic, between external clients and data centre servers.

In order to support the injected bandwidth at the edge of the network, more than one core switches were used at the root of a large data centre, resulting in a *multi-rooted* design [6], such as the one shown in Fig. 2.4. Moreover, the switch port

**Figure 2.4:** A traditional multi-rooted three-tier data centre network topology. Switch size and port capacity increase from access to core tiers.

count and bit rate were increased, moving upwards towards the tree root, to provide more bandwidth for the aggregation and core layers [2, 6] where the traffic volume is higher. The top-of-rack (ToR) switches in the access tier would typically have 48 ports running at 10 Gb/s for connections to servers plus 4 more ports running at 40 Gb/s for connections to aggregation switches, while the switches in the aggregation and core tiers would have a size up to 128 ports with speeds ranging from 40 Gb/s to 100 Gb/s. Hence, more expensive switching equipment was used at the higher layers.

Since it is unlikely that links are ran at their full speed, *over-subscription* was typically applied in the network [2]. At a network layer the uplink capacity,  $C_{uplink}$ , is lower than the downlink capacity,  $C_{downlink}$ . This reduces the topology cost by using less switching equipment and fewer high-speed links. In the access layer, for example, assuming 48 x 10 Gb/s downlinks and 4 x 40 Gb/s uplinks at a ToR switch, the over-subscription ratio is  $R = C_{downlink}$ :  $C_{uplink} = 3$ : 1.

In addition to the limited network capacity, the packet end-to-end latency in the

**Figure 2.5:** The Leaf-Spine architecture. It is a Clos network folded along the middle and rotated by 90 degrees.

traditional three-tier architecture could be long and variable, depending on the path taken [32]. A packet could traverse a core switch before reaching its destination, performing multiple hops along the way, while another packet could be switched to its destination through an aggregation switch in fewer hops. The limited bandwidth and unpredictable network latency is not favourable for inter-server traffic currently exchanged in the data centre [2, 32]. The network topology has now shifted to the *leaf-spine* model, as discussed in the next section.

#### 2.2.2 Leaf-Spine

The leaf-spine architecture is a three-stage Clos network folded along the middle and rotated anti-clockwise by 90 degrees, as illustrated in Fig. 2.5. The resulting multi-rooted architecture is flat with only two tiers; the *leaf* which is composed of the ToR switches and the *spine* which interconnects the ToR switches. Every leaf switch connects to every spine switch and vice versa. The network can be constructed entirely out of identical commodity switches, reducing the architecture cost compared to traditional hierarchical trees.

The path-diversity in Clos networks, from which their non-blocking property stems, enables full bisection bandwidth connectivity between the two layers. This means that there is no over-subscription at the leaf layer, i.e. R = 1:1, and hence servers can transmit at full capacity. More importantly, in this flat architecture all

**Figure 2.6:** Electrical link cross-section showing alternating current density distribution at high data rates. Current flows mainly within a depth  $\delta$  from the link's outer edge or "skin". This phenomenon is known as the skin effect.

paths are equidistant; every source and destination server are three hops apart. As a result, the latency is lower and less variable compared to the traditional hierarchical architecture. The aforementioned advantages made the leaf-spine architecture the de facto standard for data centre networks, to efficiently handle the so called "East-West" traffic patterns between servers.

Full bisection bandwidth connectivity may not be practical as the data centre size grows, due to the increasing wiring complexity between the two layers and the implementation cost [8]. In practice over-subscription may be applied to mitigate complexity and cost by trading off bandwidth [4]. It should be noted however that since the architecture becomes blocking, in theory it is no longer a Clos network but rather a partial mesh network interconnecting switches in two layers.

## 2.3 Electrical Network Scaling Limitations

#### 2.3.1 Transmission Distance and Bandwidth

Electrical links face length limitations due to data rate dependent losses [7]. Due to the *skin effect* in alternating current transmission lines, the current density is higher near a conductor's outer edge or "skin" and decreases towards the centre, as depicted in Fig. 2.6. The current flow mainly occurs within a skin depth,  $\delta$ , from the outer edge and the depth decreases as the current frequency increases. Hence, the effective resistance of a conductor increases with signal frequency resulting in

a higher loss, which in turn limits the propagation distance due to signal distortion. At a 10 Gb/s data rate, the length for copper-based point-to-point links is limited to 10 meters [8]. Pre-emphasis and equalisation are signal processing techniques to mitigate the skin effect at the cost of increased latency, power and chip area [12, 11].