# SOFT-SWITCHED STEP-UP MEDIUM VOLTAGE POWER CONVERTERS

#### MEHDI ABBASI

A DISSERTATION SUBMITTED TO

THE FACULTY OF GRADUATE STUDIES

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

GRADUATE PROGRAM IN

ELECTRICAL ENGINEERING AND COMPUTER SCIENCE

YORK UNIVERSITY

TORONTO, ONTARIO

August 2019

© Mehdi Abbasi, 2019

#### **Abstract**

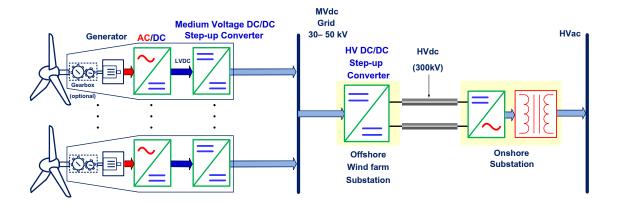

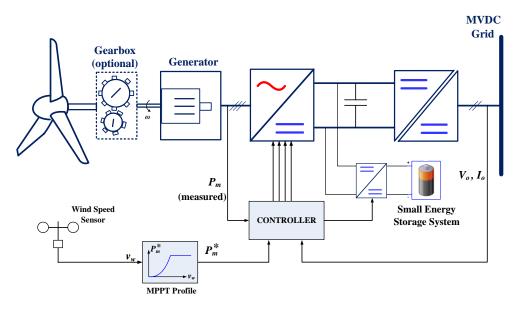

With a ten-year average annual growth rate of 19 percent, wind energy has been the largest source of new electricity generation for the past decade. Typically, an offshore wind farm has a medium voltage ac (MVac) grid that collects power from individual wind turbines. Since the output voltage of a wind turbine is too low (i.e., typically 400 – 690 V) to be connected to the MVac grid (i.e., 20 – 40 kV), a heavy line-frequency transformer is used to step up the individual turbine's output voltage to the MV level. To eliminate the need for bulky MVac transformers, researchers are gravitating towards the idea of replacing the MVac grid with a medium voltage dc (MVdc) grid, so that MV step-up transformers are replaced by MV step-up power electronic converters that operate at the medium frequency range with much lower size and weight.

This dissertation proposes a class of modular step-up transformerless MV SiC-based power converters with soft-switching capability for wind energy conversion systems with MVdc grid. This dissertation consists of two parts: the first part focuses on the development of two novel groups of step-up isolated dc-dc MV converters that utilize various step-up resonant circuits and soft-switched high voltage gain rectifier modules. An integrated magnetic design approach is also presented to combine several magnetic components together in the modular high voltage gain rectifiers. The second part of this dissertation focuses on the development of several three-phase ac-dc step-up converters with integrated active power factor correction. In particular, a bridgeless input ac-dc rectifier is also proposed to combine with the devised step-up transformerless dc-dc converters (presented in the first part) to form the three-phase soft-switched ac-dc step-up voltage conversion unit. In each of the presented modular step-up converter configurations, variable frequency control is used to regulate the output dc voltage of each converter module. The operating principles and characteristics of each presented converter are provided in detail. The feasibility and performance of all the power converter concepts presented in this dissertation are verified through simulation results on megawatts (MW) design examples, as well as experimental results on SiC-based laboratory-scale proofof-concept prototypes.

to my parents,

my lovely wife, Farnaz,

and my sister

#### Acknowledgment

There are no appropriate words to convey my deep gratitude and respect to my supervisor, Dr. John Lam. His invaluable guidance, encouragement and strong technical insights were instrumental in completing this work. I appreciate all his contributions of time, ideas, and financial support to make my Ph.D. experience productive and stimulating.

I also wish to express my thanks to the members of the dissertation examining committee: Dr. Ali Hooshyar, Dr. Hany Farag, Dr. S. Ali Khajehoddin, Dr. Sebastian Magierowski, and Dr. Paul G. O'Brien. I am grateful for their valuable advice and feedback.

I would like to offer my thanks to all graduate students in the Power Electronics Laboratory for Sustainable Energy Research (PELSER) for many productive discussions over the past few years.

I deeply thank my parents for giving me strength, love, and support to reach for the stars and chase my dreams. Words cannot express how grateful I am to my mother and father for the countless sacrifices they have made for me. Without you, I would not be the person I am today. My sister, Maryam, also deserves my wholehearted thanks. Without her supports, love, and encouragement, I would not be able to pursue my studies in the PhD level and begin this journey. Also, I express my gratitude to my parents-in-law for their unconditional support.

Above all, I owe thanks to a very special person, my wife, Farnaz, for her continued and unfailing love, support, and understanding during my pursuit of Ph.D. degree that made the completion of thesis possible. Thank you for your unwavering belief in me to get through the tough times. To have a woman of such infinite talent and dynamism, put her own professional career on hold to be with me, and support me, is my most precious possession. I owe you everything.

# **Table of Contents**

| Abstract                |                                                                     | ii   |

|-------------------------|---------------------------------------------------------------------|------|

| Dedication              |                                                                     |      |

| Acknowle                | dgment                                                              | iv   |

| Table of C              | ontents                                                             | v    |

| List of Tab             | oles                                                                | viii |

| List of Fig             | ures                                                                | ix   |

| List of Abl             | breviations                                                         | XVi  |

| Chapter 1               | Introduction                                                        | 1    |

| 1.1 V                   | Vind Farm Configurations                                            | 3    |

| 1.1.1                   | Parallel AC Configuration with HVac Transmission                    | 3    |

| 1.1.2                   | Parallel AC Configuration with HVdc Transmission                    | 4    |

| 1.1.3                   | Series DC Configuration with HVdc Transmission                      | 5    |

| 1.1.4                   | Parallel DC Configuration with HVdc Transmission                    | 7    |

| 1.2 T                   | echnical Challenges and Possible Solutions                          | 8    |

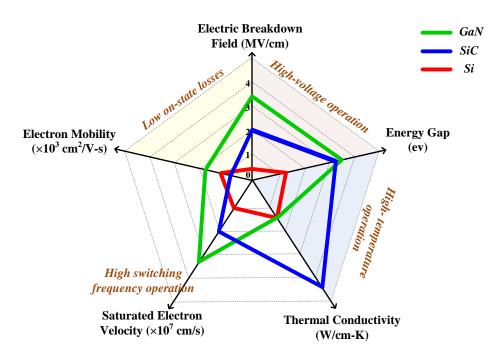

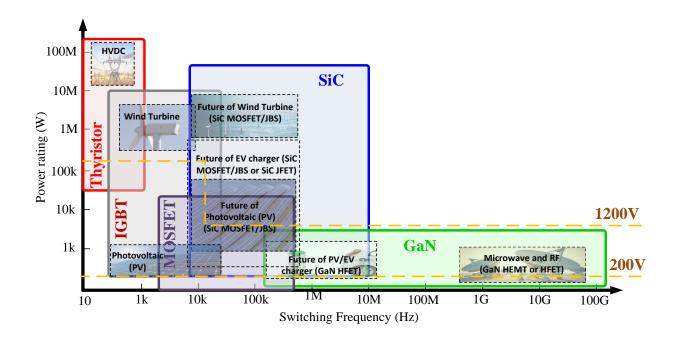

| 1.3 S                   | emiconductor Devices Advancement                                    | 11   |

| 1.4 P                   | ower Converters for Medium Voltage DC (MVdc)                        | 14   |

| 1.4.1                   | Existing MV Step-Up DC-DC Converter                                 | 15   |

| 1.4.2                   | Generator-Side AC-DC Converter                                      | 26   |

| 1.5 R                   | esearch Objectives                                                  | 28   |

| 1.6 D                   | Dissertation Outline                                                | 29   |

| Chapter 2<br>Rectifiers | Proposed DC-DC Converters with Modular Resonant Circuits and High-G |      |

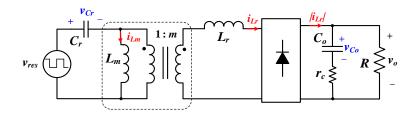

| 2.1 R                   | esonant Converter Topology                                          | 34   |

| 2.2 D                   | OC-DC Converters with Modular Resonant Circuits                     | 36   |

| 2.2.1                   | Multistring Configuration of Semiconductor Devices                  | 38   |

| 2.2.2                   | Proposed Topology with CL Step-Up Resonant Circuits                 | 40   |

| 2.2.3                   | Converter Operating Principles                                      | 41   |

| 2.2.4                     | Analysis of Each Converter Module with <i>CL</i> Resonant Circuit         | 44  |

|---------------------------|---------------------------------------------------------------------------|-----|

|                           | posed DC-DC Converters with Modular Resonant Circuits and High-Gain       |     |

| Rectifiers                |                                                                           |     |

| 2.3.2                     | Different Topologies Employing Modular Resonant Circuits and High-Gai     |     |

|                           |                                                                           |     |

|                           | p-Up Resonant Converter with Internally Coupled High Voltage-Gain Modu    |     |

| 2.4.1                     | Circuit Description of the Proposed Converter                             |     |

| 2.4.2                     | Operating Principles of the Proposed Step-up Converter                    |     |

| 2.4.3                     | Theoretical Analysis of the Proposed Converter (Per Module)               |     |

| 2.4.4                     | Converter Modeling                                                        |     |

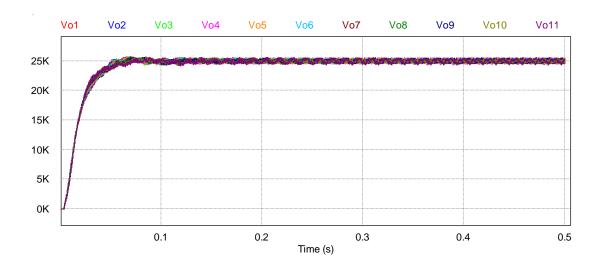

| 2.4.5                     | Simulation Results                                                        |     |

| 2.4.6                     | Controller Design                                                         |     |

| 2.4.7                     | Experimental Results and Design Procedures                                |     |

|                           | apter Summary                                                             |     |

| Chapter 3<br>Gain Rectifi | Proposed DC-DC Converters with Single Isolation Magnetic and Coupled ers  |     |

| 3.1 Ste                   | p-Up Converter Module Configuration with 1:1:1 Transformer                | 109 |

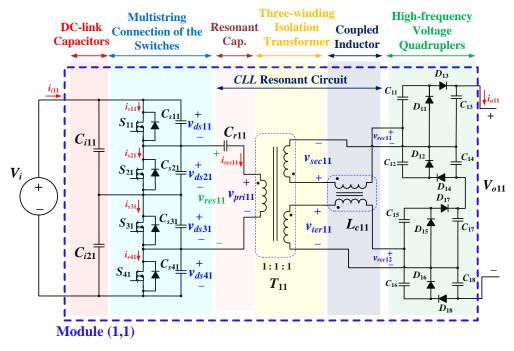

| 3.1.1                     | Circuit Description of the Proposed Converter                             | 110 |

| 3.1.2                     | Operating Principles of the Proposed Step-up Converter                    | 115 |

| 3.1.3                     | Converter Analysis.                                                       | 118 |

| 3.1.4                     | Simulation, Experimental Results and Performance                          | 128 |

|                           | p-Up Converter Module Configuration with a 1:1 Turns-Ratio Multi-Windiner | _   |

| 3.2.1                     | Circuit Descriptions and Operating Principles of the Proposed Converter   |     |

| 3.2.1                     | Proposed Converter Analysis                                               |     |

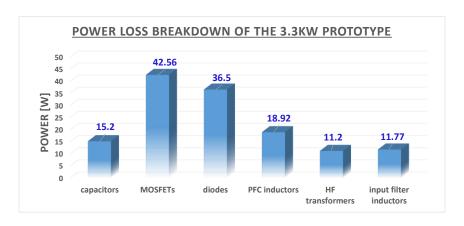

| 3.2.3                     | Power Loss Analysis                                                       |     |

| 3.2.4                     | Simulation, Experimental Results and Performance                          |     |

|                           | apter Summary                                                             |     |

| Chapter 4                 | Proposed Three-Phase AC-DC High Voltage-Gain Converters                   |     |

| •                         | gle-Stage PFC with HGR Approach                                           |     |

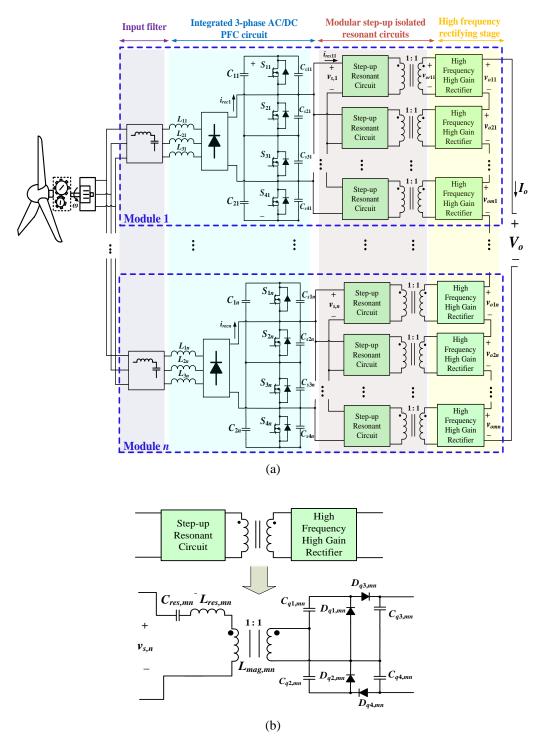

| 4.1.1                     | Circuit Description of the Proposed Converter                             |     |

| 4.1.2                     | Steady-State Analysis of the Proposed Circuit                             |     |

| 4.1.3                     | Simulation, Experimental Results and Performance                          |     |

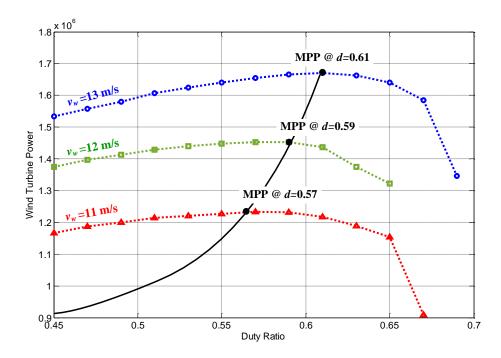

| 4.1.4                     | Maximum Power Point Tracking (MPPT)                                       |     |

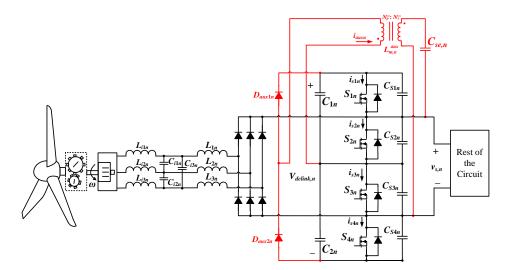

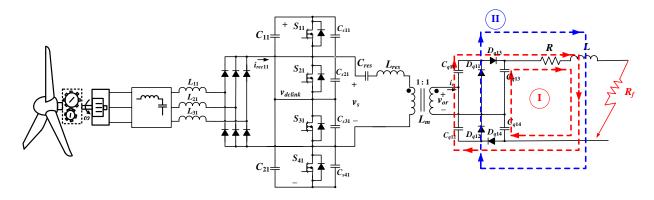

|                           | dgeless PFC with HGR Approach                                             |     |

|                           | MENINUM I I V 11111 I I VII I I VII VII VII VII                           |     |

| 4.2.1      | Circuit Description of the Proposed Converter          | 219 |

|------------|--------------------------------------------------------|-----|

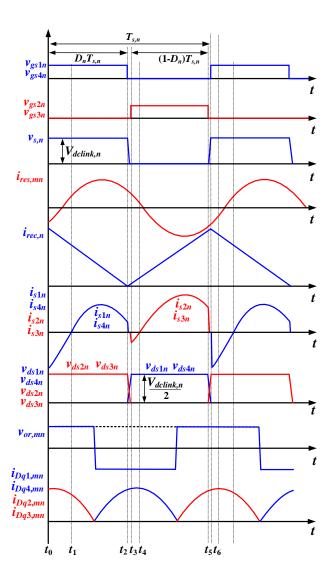

| 4.2.2      | Operating Principles of the Proposed Step-up Converter | 222 |

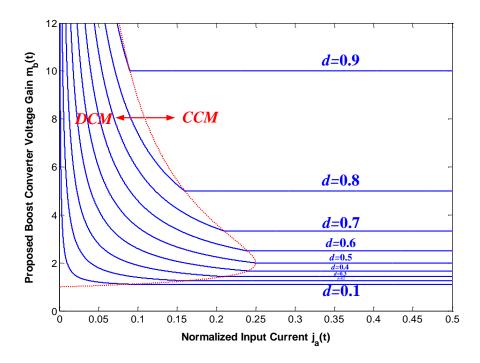

| 4.2.3      | Proposed Converter Analysis                            | 227 |

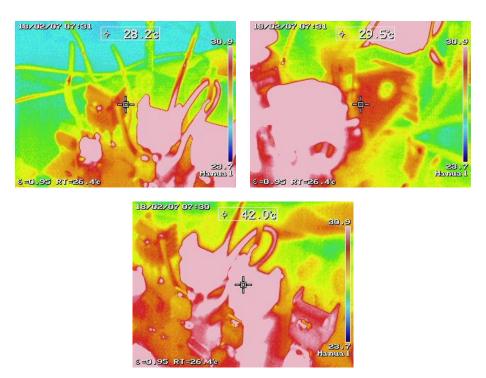

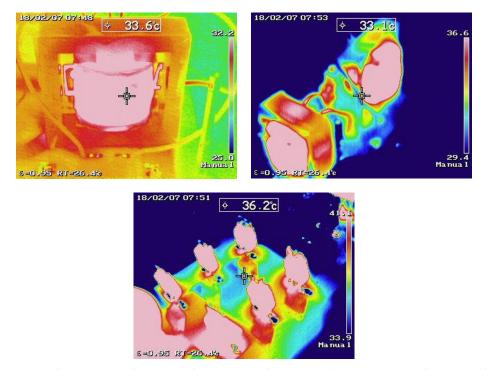

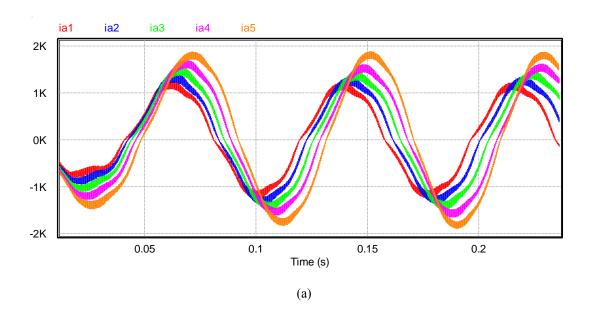

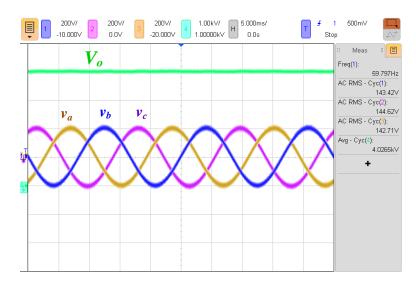

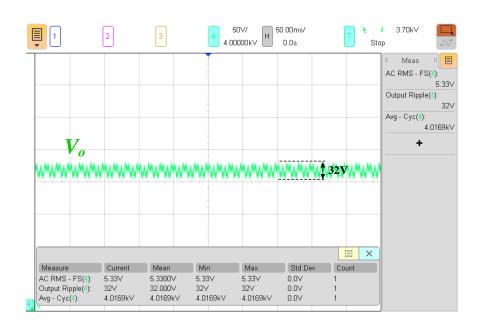

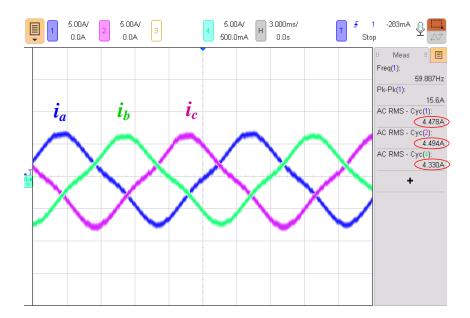

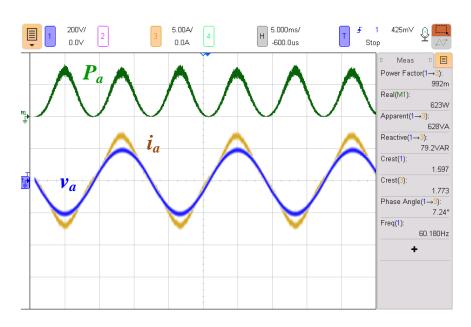

| 4.2.4      | Experimental and Simulation Results                    | 240 |

| 4.3 C      | hapter Summary                                         | 263 |

| Chapter 5  | Conclusions                                            | 264 |

| 5.1 C      | ontributions                                           | 265 |

| 5.2 F      | uture Works                                            | 268 |

| References |                                                        | 269 |

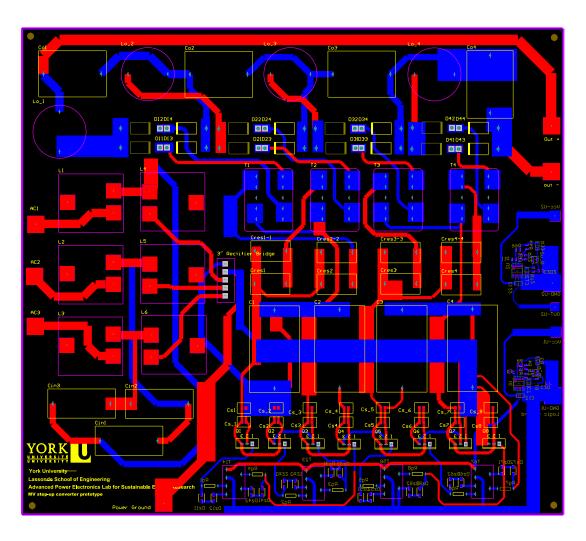

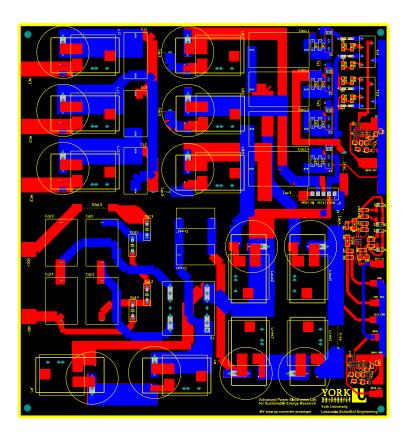

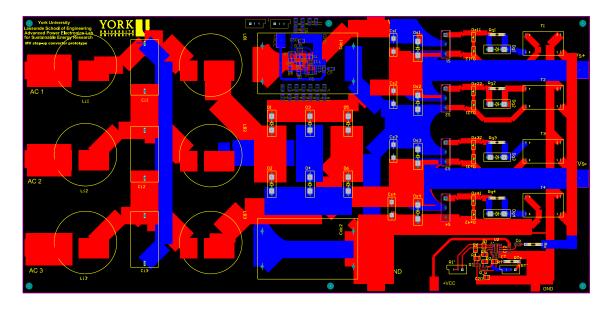

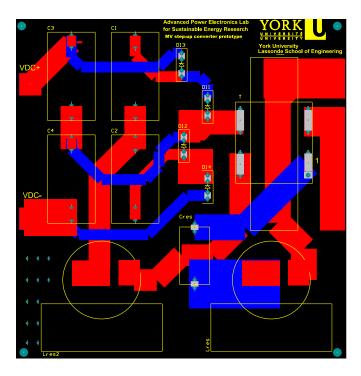

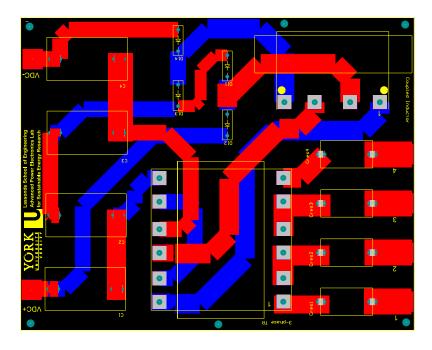

| Appendix . | A Printed Circuit Board (PCB) Layouts                  | A-1 |

| Appendix   | B MVdc Grid Protection for the Proposed Converter      | B-4 |

| Appendix   | C List of Publications                                 |     |

| C.1 R      | efereed Journal Papers                                 | C-6 |

| C.2 R      | efereed Conference Papers                              |     |

## **List of Tables**

| Table 1.1– List of Commercial Type 3 and Type 4 Megawatt Wind Turbines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Table 1.2– Summary of Transformers Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10       |

| Table 1.3- A Comparison Between 1.2kV and 1.7kV SiC Half-bridge Modules [43]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13       |

| Table 1.4– Summary of Boosting Techniques in MVdc Step-Up Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25       |

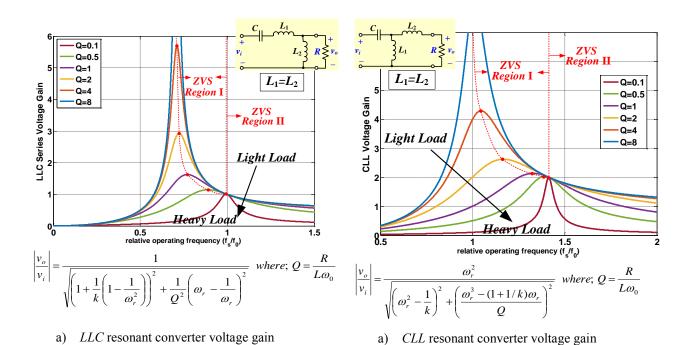

| Table 2.1– Comparison of Different Resonant Topologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 35       |

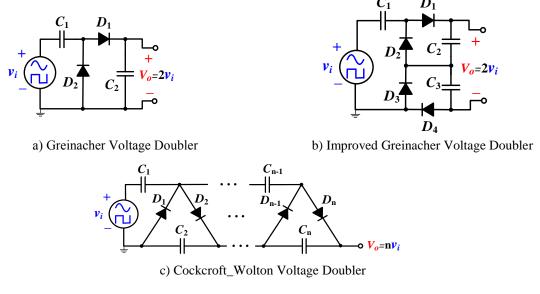

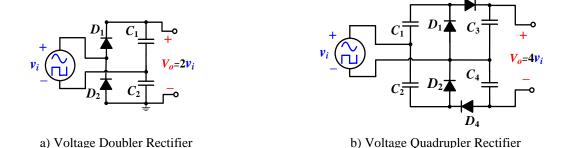

| Table 2.2– Comparison of Different Voltage Multiplier Rectifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 56       |

| Table 2.3- Circuit Components (Per Module) in Simulation and the Experimental Proto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | type95   |

| Table 3.1– Voltage and Current Sharing of Different DC-DC Modular Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 114      |

| Table 3.2– Specifications and Components Used in the Simulation and the Laboratory-Specifications and Components Used in the Simulation and the Laboratory-Specifications and Components Used in the Simulation and the Laboratory-Specifications and Components Used in the Simulation and the Laboratory-Specifications and Components Used in the Simulation and the Laboratory-Specifications and Components Used in the Simulation and the Laboratory-Specifications and Components Used in the Simulation and the Laboratory-Specifications and Components Used in the Simulation and the Laboratory-Specifications and Components Used in the Simulation and the Laboratory-Specifications and Components Used in the Specification and Components Used |          |

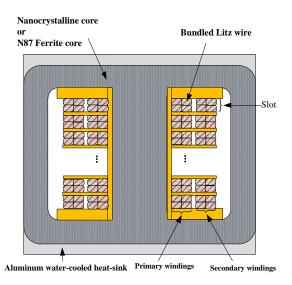

| Table 3.3– Properties of Magnetic Properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 132      |

| Table 3.4– Specifications of the High Frequency Transformer Utilized in the Proposed Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 132      |

| Table 3.5– Specifications of the Coupled Inductor utilized in the Proposed Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 132      |

| Table 3.6– Specifications and Components Used in the Simulation and the Laboratory-S Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| Table 3.7– Line Frequency and High Frequency Transformers Size Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 169      |

| Table 3.8– High Frequency Transformer Specifications Utilized in the Proposed Conver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | rter 169 |

| Table 3.9– Comparison of Existing Step-Up DC-DC Resonant Converters with the Prop Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| Table 4.1- Components Part Numbers and Values in the 1.5MW design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 196      |

| Table 4.2– Specifications and Components for the Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 204      |

| Table 4.3– Specifications and Components for the Proof-of-Concept Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 243      |

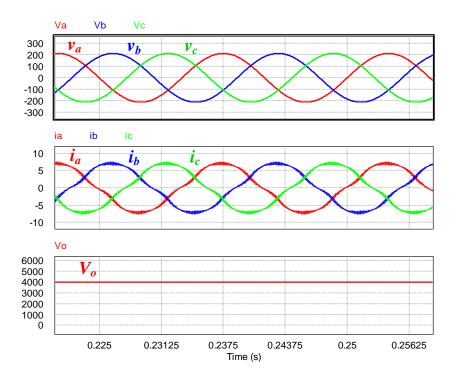

| Table 4.4– Specifications and Components for the Simulated 1 MW Wind Turbine Con                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

# **List of Figures**

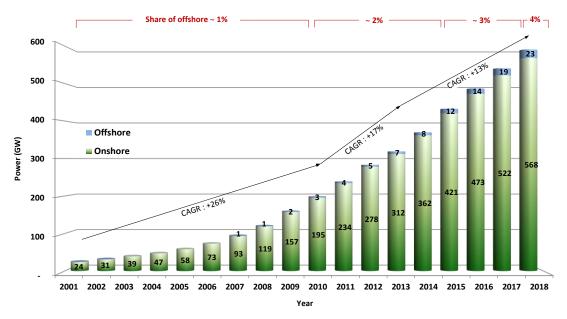

| Figure 1.1– Global cumulative installed wind capacity                                                                                                    | 1   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

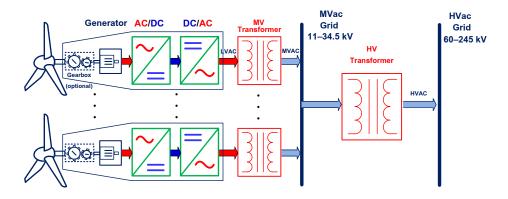

| Figure 1.2– Parallel ac with HVac based onshore wind farm configuration                                                                                  | 4   |

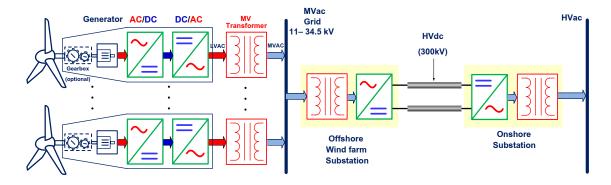

| Figure 1.3– Parallel ac with HVdc based offshore wind farm configuration                                                                                 | 5   |

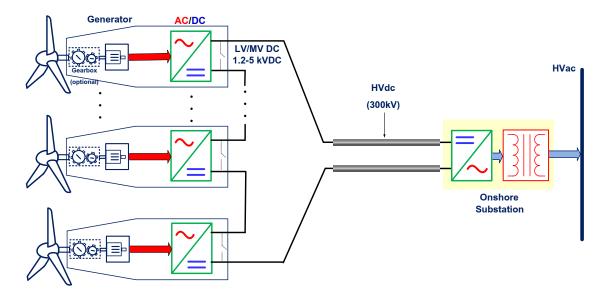

| Figure 1.4– Series dc with HVdc based offshore wind farm configuration                                                                                   | 6   |

| Figure 1.5– Parallel dc with HVdc based offshore wind farm configuration                                                                                 | 7   |

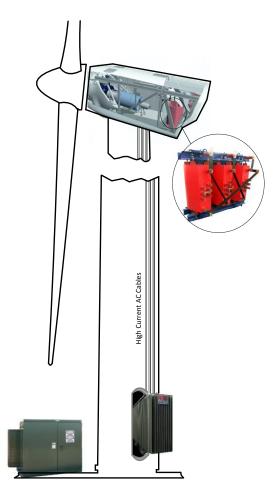

| Figure 1.6– Housing of power transformer in wind turbine                                                                                                 | 9   |

| Figure 1.7– Summary of Si, SiC, and GaN relevant materials properties                                                                                    | 12  |

| Figure 1.8– Summary of Si, SiC and GaN-based applications status [42]                                                                                    | 14  |

| Figure 1.9– Basic switched capacitor                                                                                                                     | 16  |

| Figure 1.10– ZCS resonant switched capacitor converter                                                                                                   | 16  |

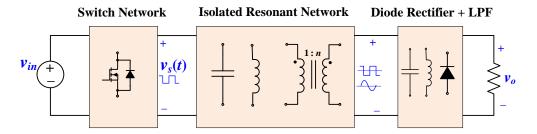

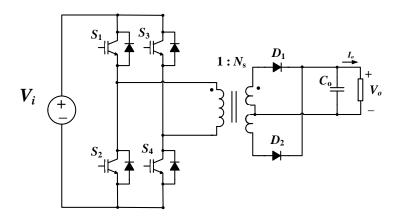

| Figure 1.11– Conventional resonant converter structure                                                                                                   | 18  |

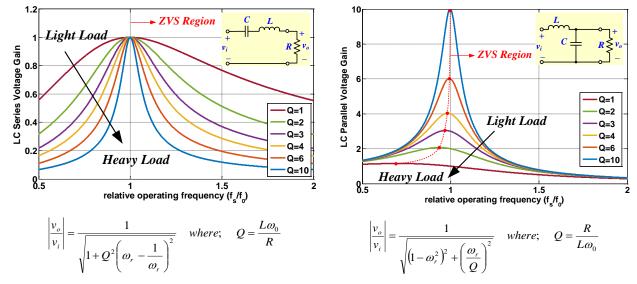

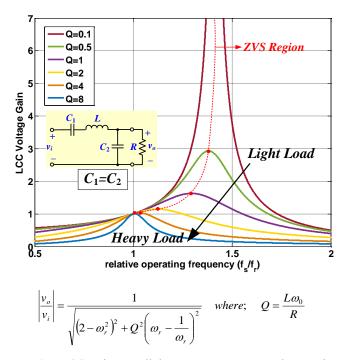

| Figure 1.12- Voltage gain characteristics of the basic resonant circuits                                                                                 | 19  |

| Figure 1.13– Active bridge converter                                                                                                                     | 21  |

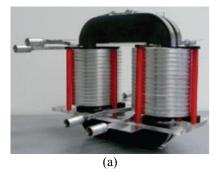

| Figure 1.14– High power medium frequency transformers                                                                                                    | 21  |

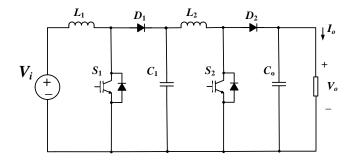

| Figure 1.15– Multiple-module cascaded boost configuration                                                                                                | 24  |

| Figure 1.16– Multiple-module hybrid converter                                                                                                            | 24  |

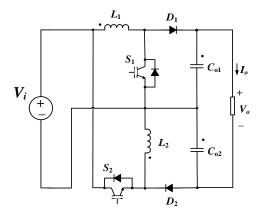

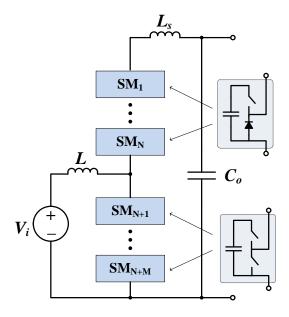

| Figure 1.17– General structure of dc-dc multilevel modular converter (MMC)                                                                               | 24  |

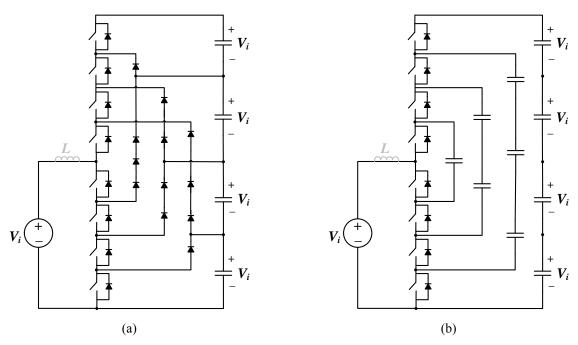

| Figure 1.18– (a) five-level multilevel modular diode clamped converter; (b) five-level multilevel modular capacitor clamped (flying capacitor) converter | 25  |

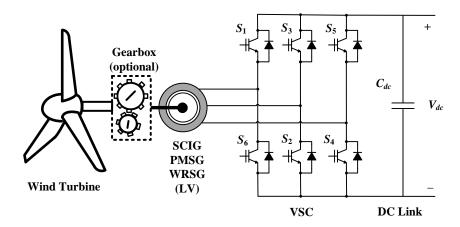

| Figure 1.19– Three-phase ac-dc active rectifier                                                                                                          | 26  |

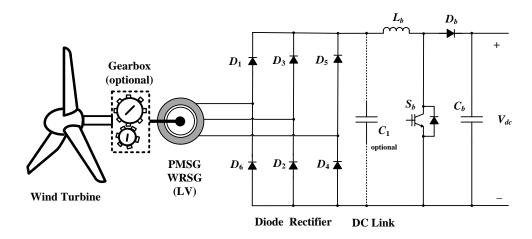

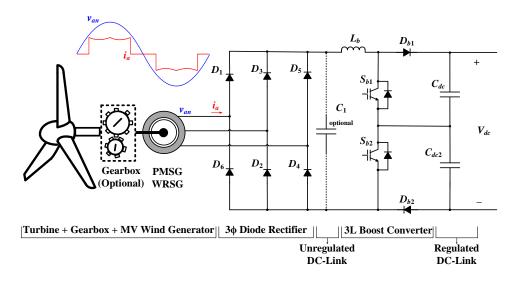

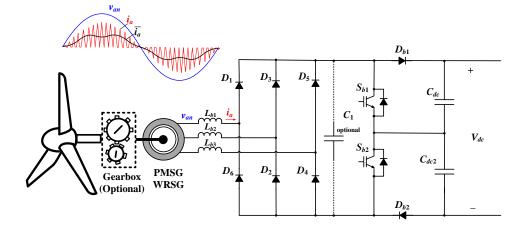

| Figure 1.20– Three-phase ac-dc diode rectifier + boost converter                                                                                         | 27  |

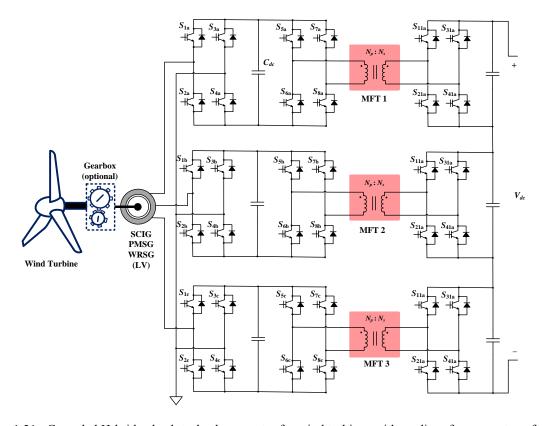

| Figure 1.21– Cascaded H-bridge back-to-back converter for wind turbines with medium frequency transformer                                                | 28  |

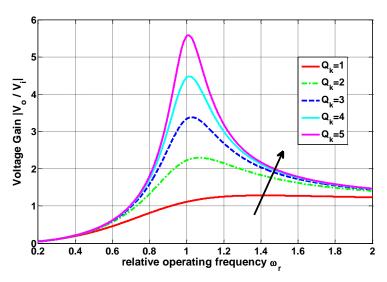

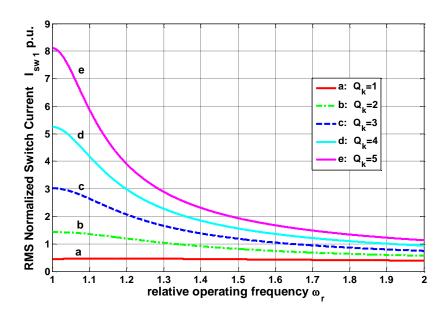

| Figure 2.1- Voltage gain characteristics of most practical resonant circuits                                                                             | 35  |

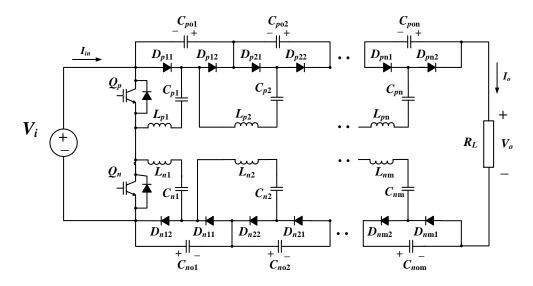

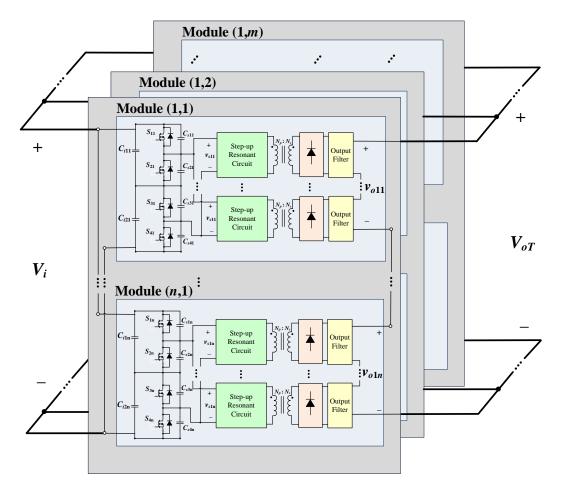

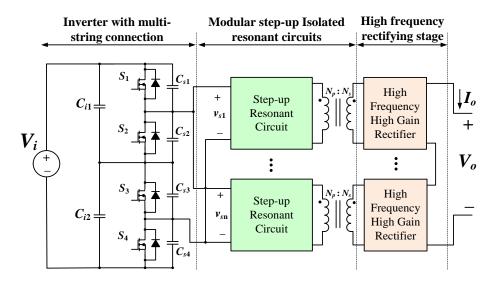

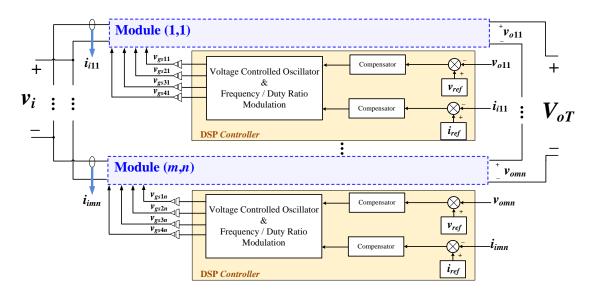

| Figure 2.2– Proposed modular MV step-up dc-dc converter structure                                                                                        | 37  |

| Figure 2.3– One module of proposed MV step-up dc-dc converter                                                                                            | 37  |

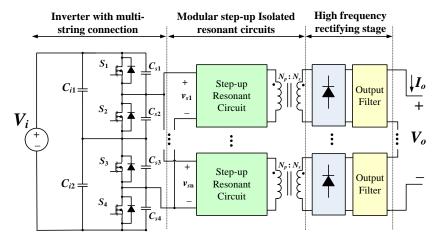

| Figure 2.4- Modular step-up converters, relying on resonant circuits to step-up the voltage                                                              | e38 |

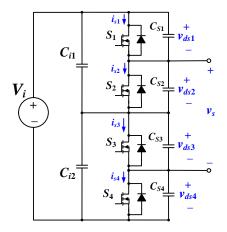

| Figure 2.5– Proposed multistring connection of semiconductor devices                                                                                     | 39  |

| Figure 2.6– Operating states of the proposed multistring connection of semiconductor dev                                                               |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.7– Proposed converter with two modules of resonant circuit                                                                                    |    |

| Figure 2.8– Key operating waveforms of the converter                                                                                                   |    |

| Figure 2.9– Equivalent circuit in each operating stage within a switching period                                                                       |    |

| Figure 2.10– Equivalent circuit of one of the modules in the proposed converter                                                                        | 44 |

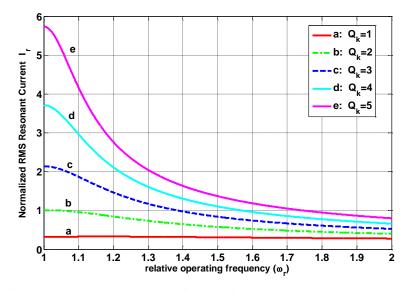

| Figure 2.11– Per unit rms value of the fundamental resonant current at $d_k$ =0.5                                                                      | 46 |

| Figure 2.12– Voltage gain plot of the proposed step-up converter                                                                                       | 48 |

| Figure 2.13– Phase plot of the <i>CL</i> resonant circuit                                                                                              | 48 |

| Figure 2.14– Per unit rms value of the fundamental switching current at $d=0.5$                                                                        | 49 |

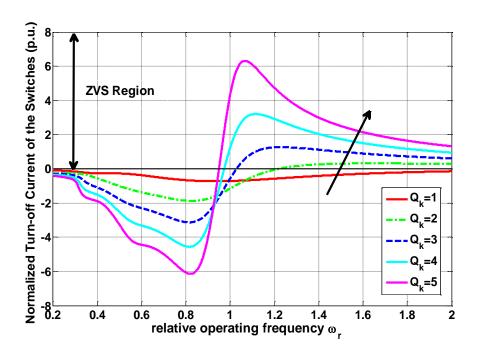

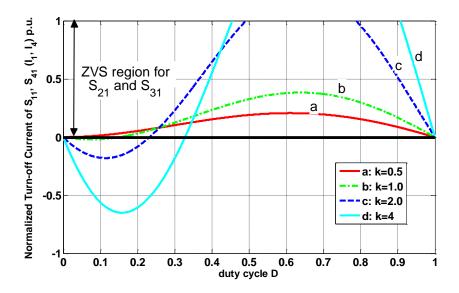

| Figure 2.15– Normalized turn-OFF current of all the switches at $d_k$ =0.5                                                                             | 51 |

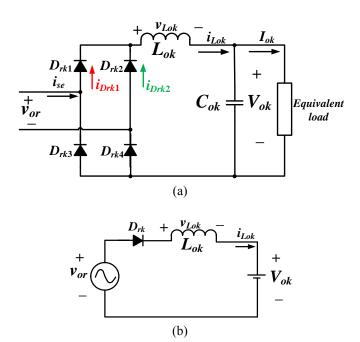

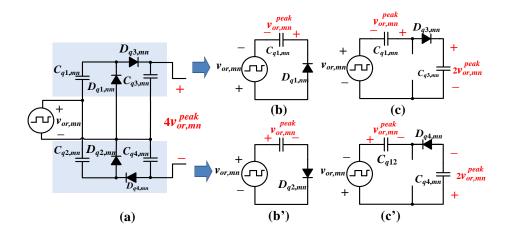

| Figure 2.16– Equivalent circuit of the high frequency rectifier                                                                                        | 52 |

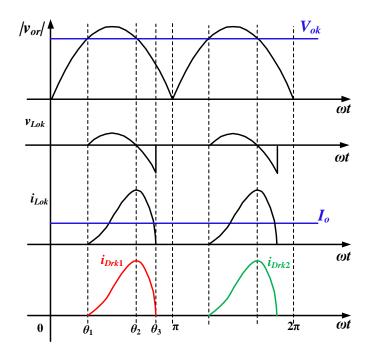

| Figure 2.17– Operating waveforms of the high frequency rectifier                                                                                       | 53 |

| Figure 2.18– Well-known half-wave voltage multiplier rectifiers                                                                                        | 55 |

| Figure 2.19– Well-known full-wave voltage multiplier rectifiers                                                                                        | 55 |

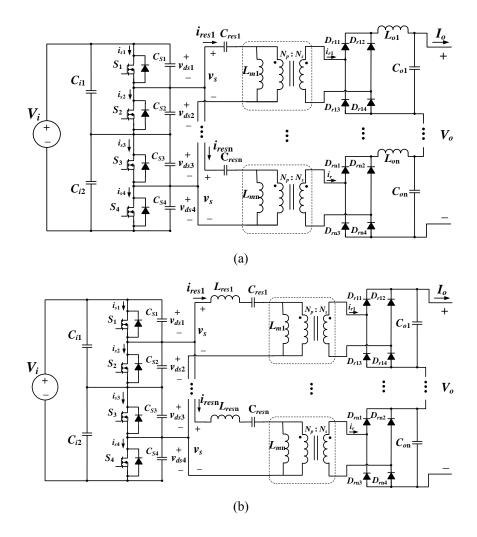

| Figure 2.20– Proposed modular MV step-up dc-dc converter with high-frequency high-garectifiers                                                         |    |

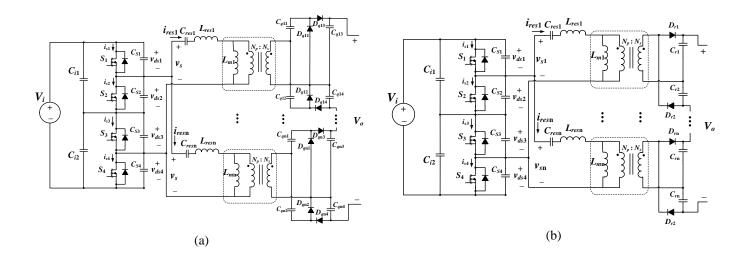

| Figure 2.21– Multiple circuit configurations based on the proposed converter structure                                                                 | 58 |

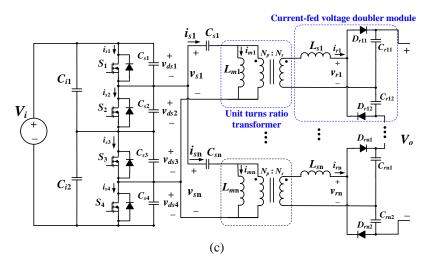

| Figure 2.22– Performance region of the proposed converter                                                                                              | 58 |

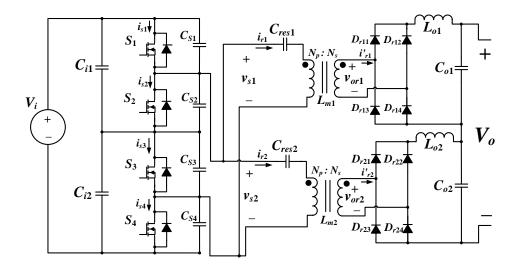

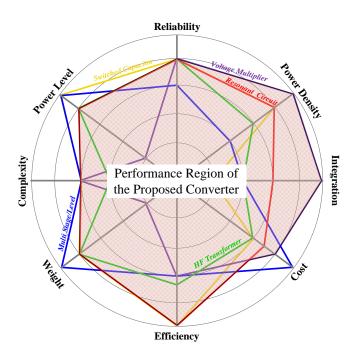

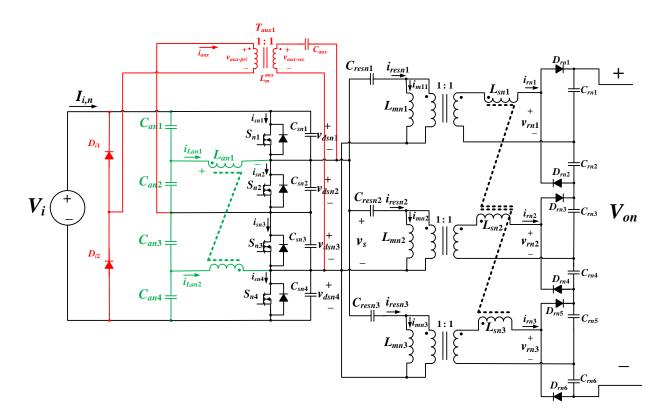

| Figure 2.23– Modular structure of the proposed step-up transformerless dc-dc step-up converter                                                         | 61 |

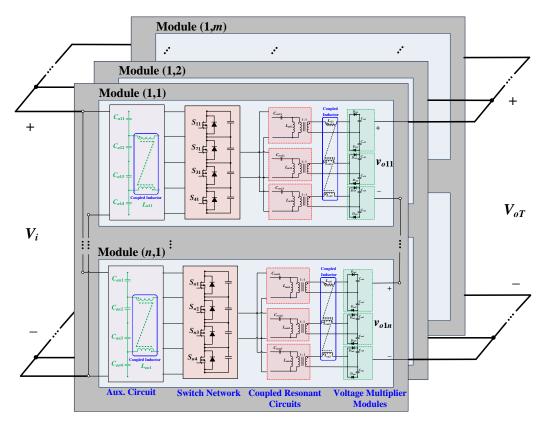

| Figure 2.24– Proposed dc-dc step-up converter configuration with magnetically-integrate voltage doublers (per module)                                  |    |

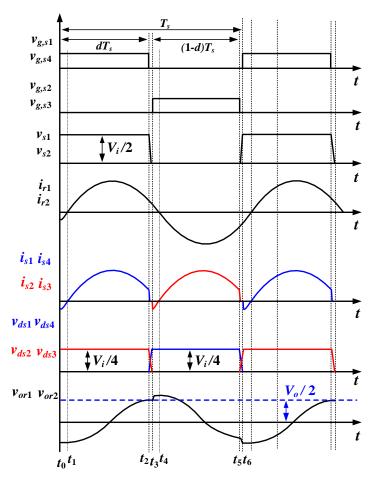

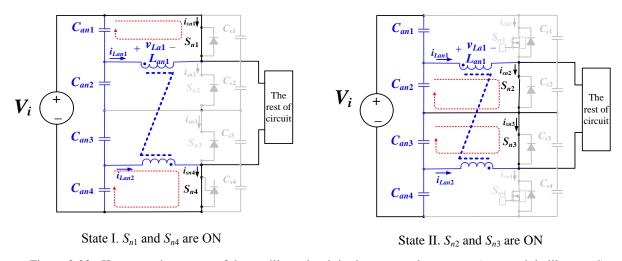

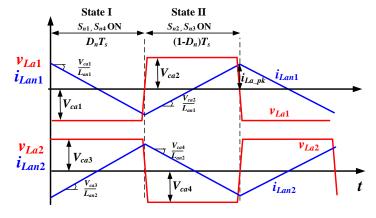

| Figure 2.25– Key operating waveforms of the converter (per module)                                                                                     | 64 |

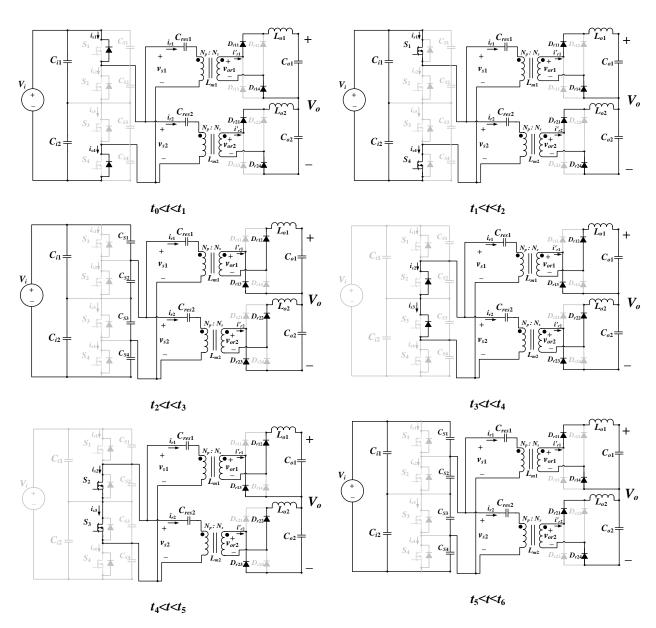

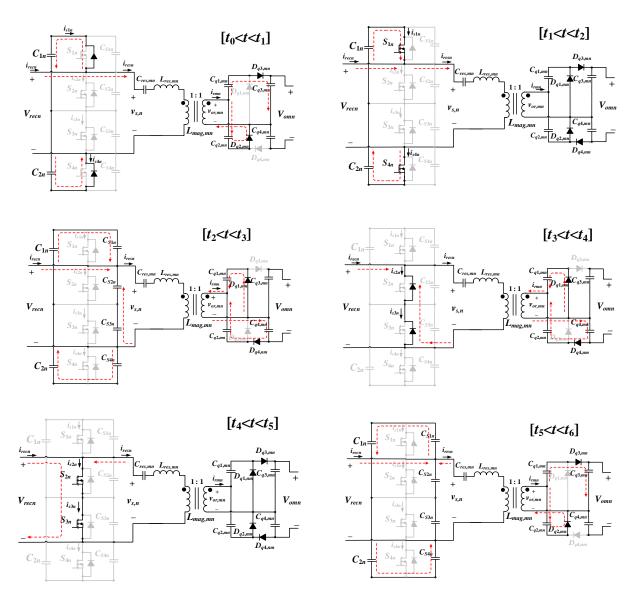

| Figure 2.26– Operating stages of the proposed converter within a switching period                                                                      | 65 |

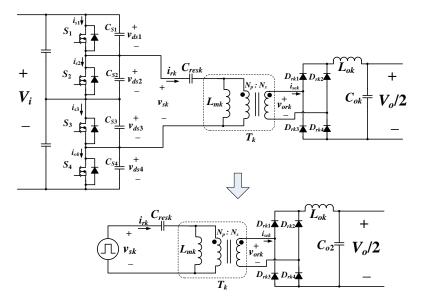

| Figure 2.27– The steady state equivalent circuit of the proposed topology                                                                              | 66 |

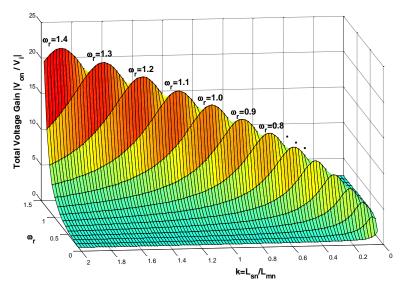

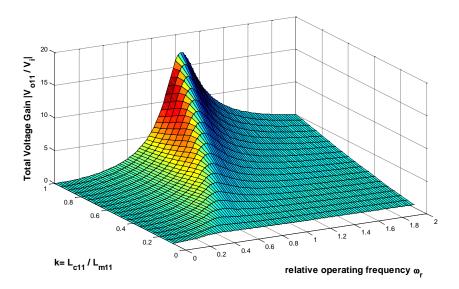

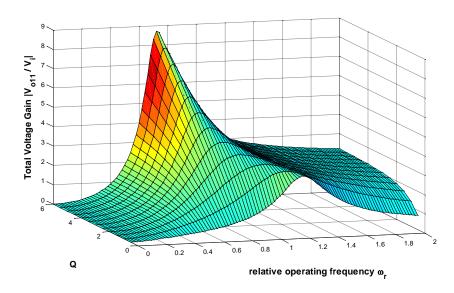

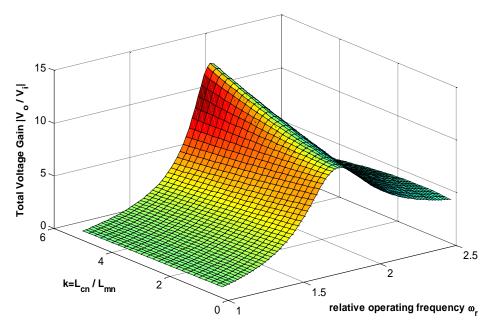

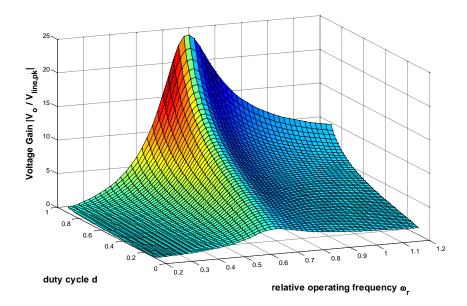

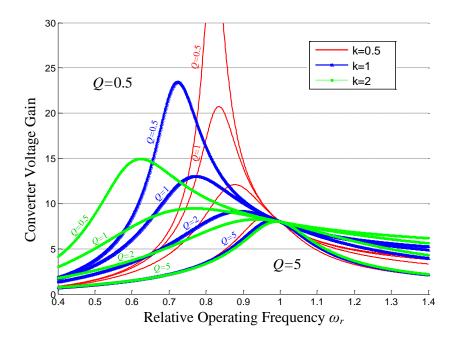

| Figure 2.28– Converter voltage gain as a function of $\omega_r$ and $k$ for $Q=3$                                                                      | 71 |

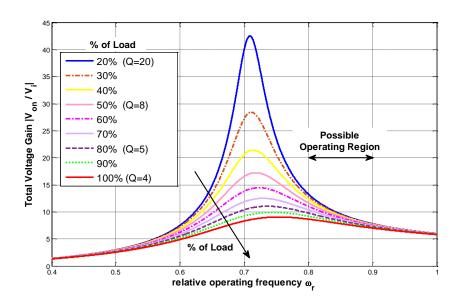

| Figure 2.29– Converter voltage gain as a function of $\omega_r$ for $k=0.5$                                                                            | 71 |

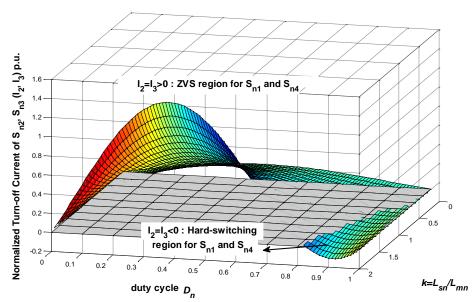

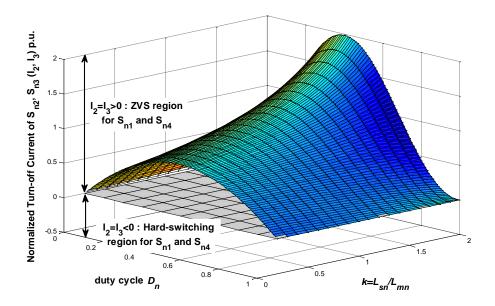

| Figure 2.30– Normalized turn-OFF current of $S_{n1}$ and $S_{n4}$ ( $I_1$ and $I_4$ ) as a function of duty $D_n$ and $k$ for $\omega_r$ =2 and $Q$ =4 |    |

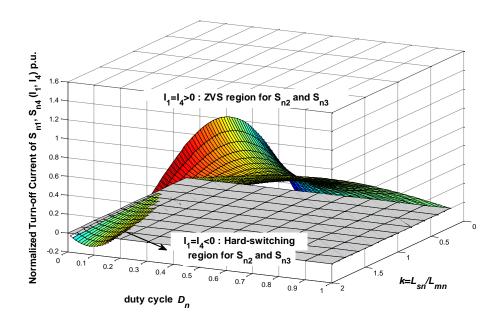

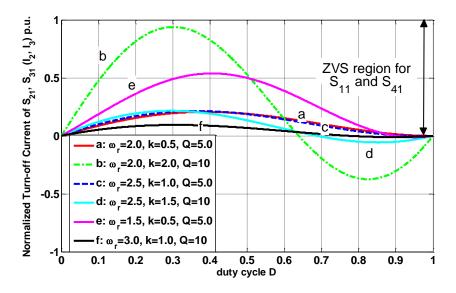

| Figure 2.31– Normalized turn-OFF current of $S_{n2}$ and $S_{n3}$ ( $I_2$ and $I_3$ ) as a function of duty $D_n$ and $k$ for $\omega_r$ =2 and $Q$ =4 |    |

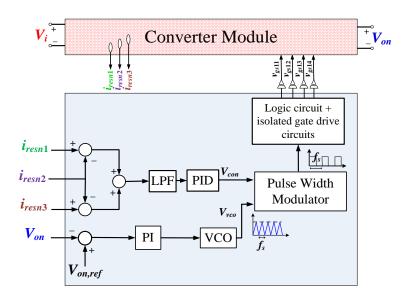

| Figure 2.32- Control block diagram for balancing resonant currents in each converter mo                                                                |    |

| Figure 2.33– Key operating stages of the auxiliary circuit in the proposed converter (one                                                              |    |

| module illustrated)                                                                                                                                    | 77 |

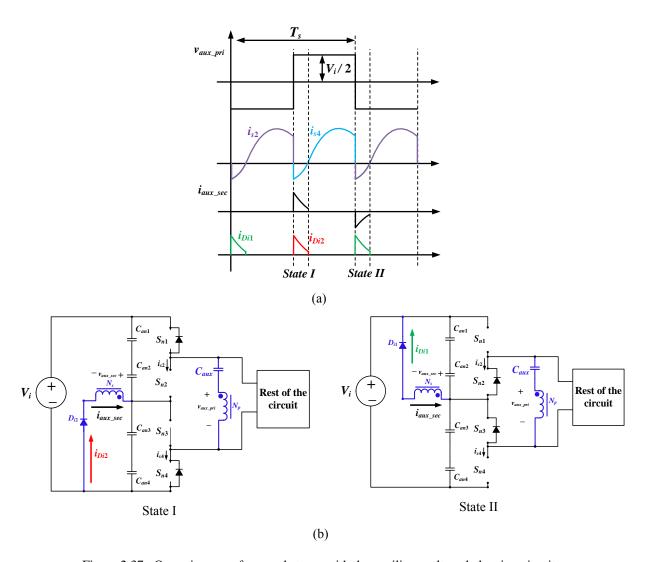

| Figure 2.34– Key operating waveforms of the auxiliary circuit in the proposed converter                                                                                                      | 77    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 2.35– Normalized turn-OFF current of $S_{n2}$ and $S_{n3}$ ( $I_2$ and $I_3$ ) with the auxiliary circ as a function of duty cycle $D_n$ and $k$ for $\omega_r=2$ , $Q=4$ and $m=7$ . |       |

| Figure 2.36– Voltage balancing technique with auxiliary circuit in the proposed converter (with only one module)                                                                             |       |

| Figure 2.37– Operating waveform and stages with the auxiliary voltage balancing circuit                                                                                                      | 80    |

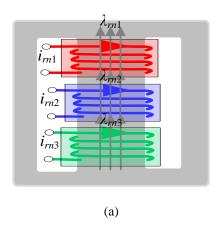

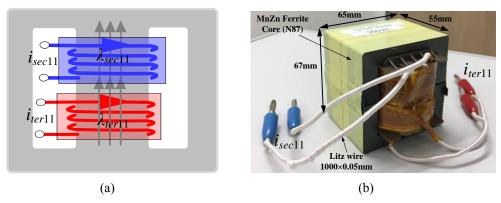

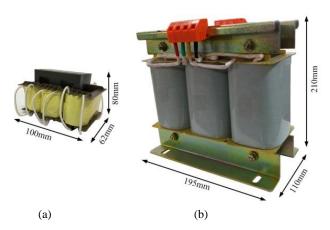

| Figure 2.38– (a) Structural diagram of the coupled inductor, (b) a picture of the implement coupled inductor.                                                                                |       |

| Figure 2.39– Equivalent circuit of the <i>CLL</i> resonant converter for modelling                                                                                                           | 83    |

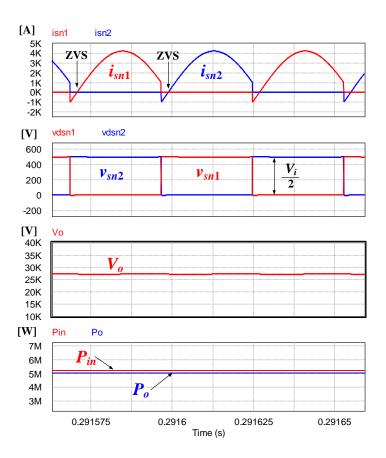

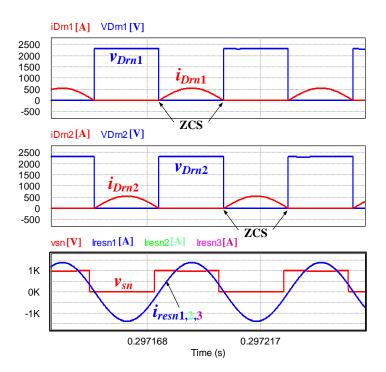

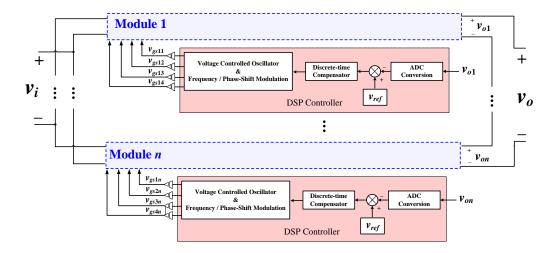

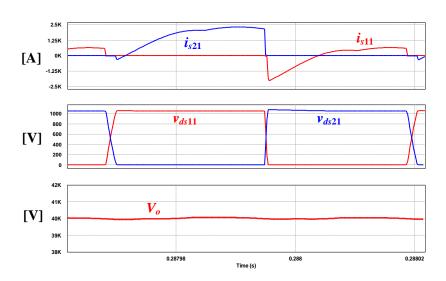

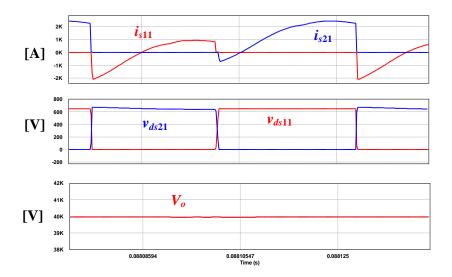

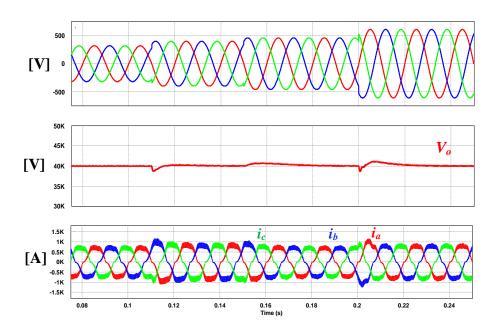

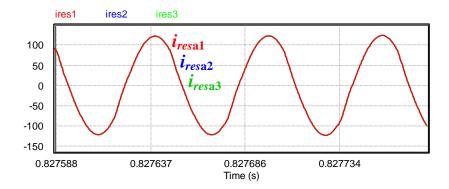

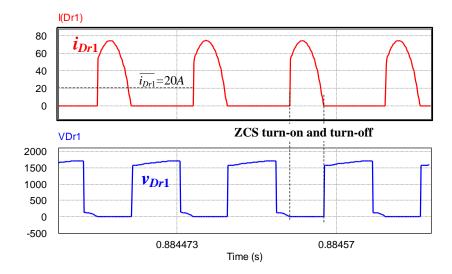

| Figure 2.40– Simulation results for full-load condition                                                                                                                                      | 89    |

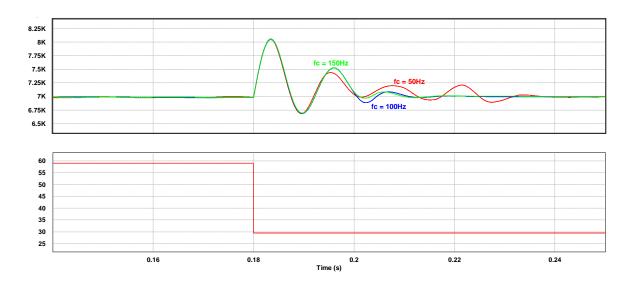

| Figure 2.41– The output voltage response against low-pass filter cut-OFF frequency variat (50Hz, 100Hz, 150Hz)                                                                               |       |

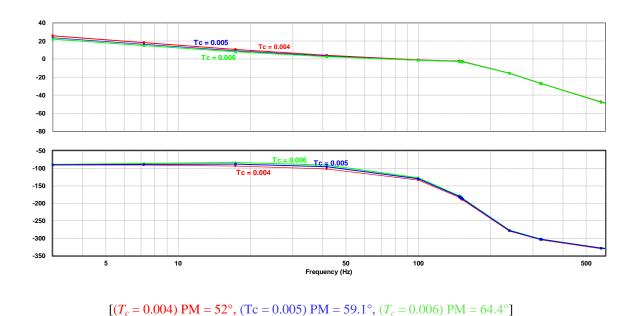

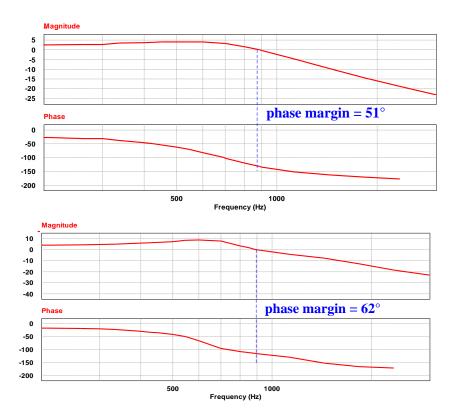

| Figure 2.42– Bode plot with various "Time constant (i.e., $T_c$ )" in the PI transfer function ( $V_i = 1 \text{kV}$ at full-load)                                                           |       |

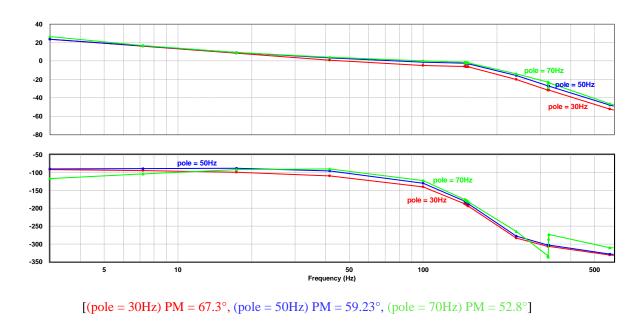

| Figure 2.43– Bode plot with various "pole placements" in the PI transfer function (with $V_i$ 1kV at full-load)                                                                              |       |

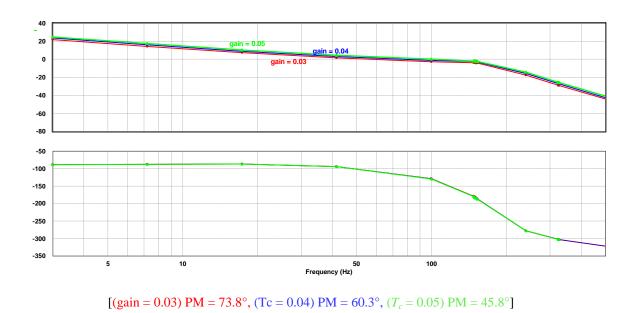

| Figure 2.44– Bode plot with various "gain values (i.e., $K_c$ )" in the PI transfer function (wit = 1kV at full-load)                                                                        |       |

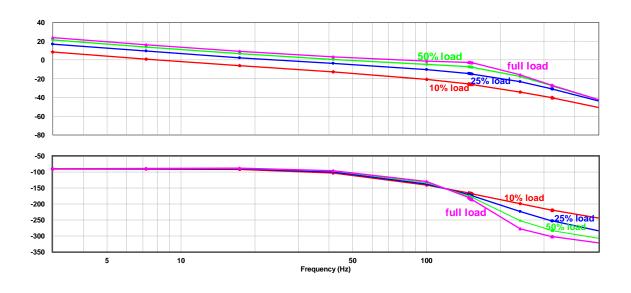

| Figure 2.45– Closed-loop Bode plot performance with different loading (i.e., power) conditions (with $V_i = 1 \text{kV}$ )                                                                   | 93    |

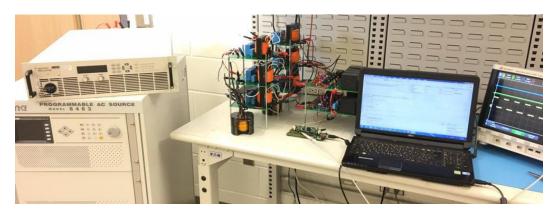

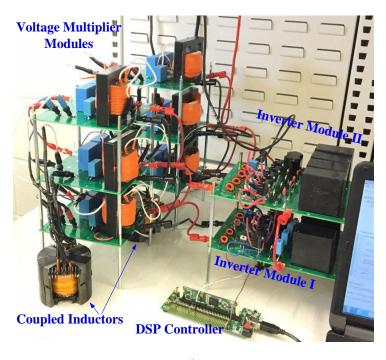

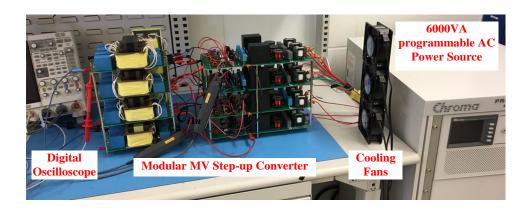

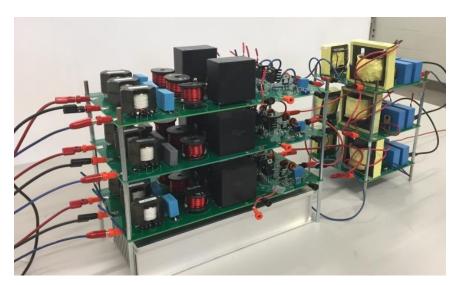

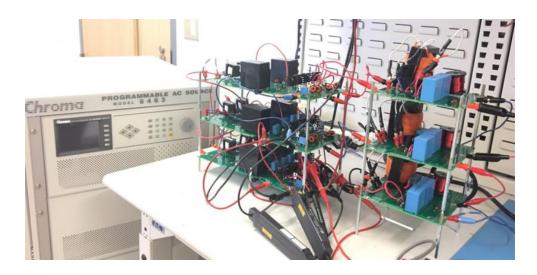

| Figure 2.46– (a) Experimental platform (b) prototype picture                                                                                                                                 | 96    |

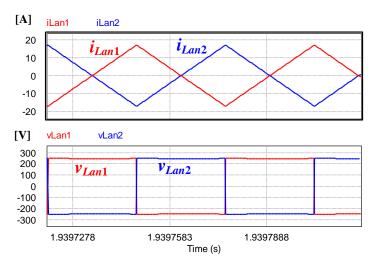

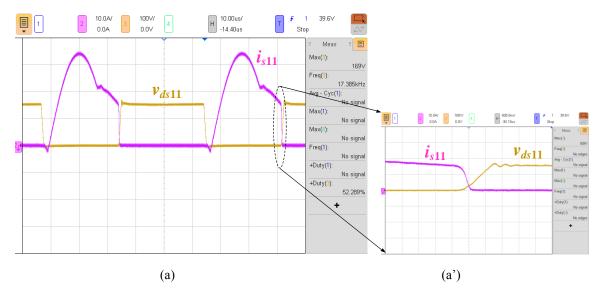

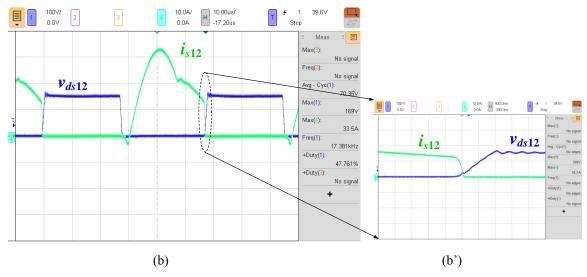

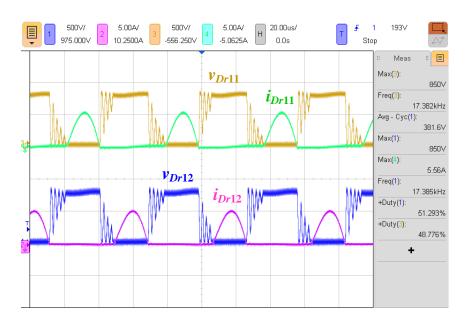

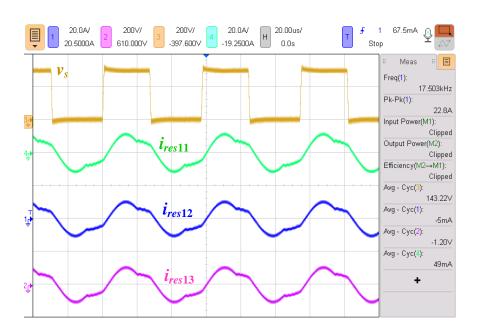

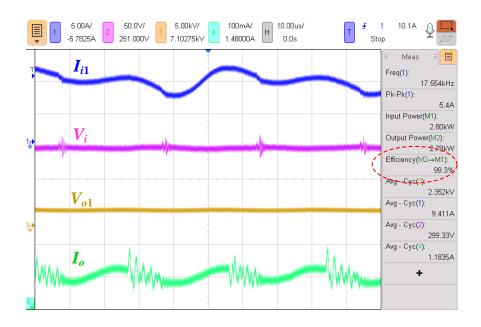

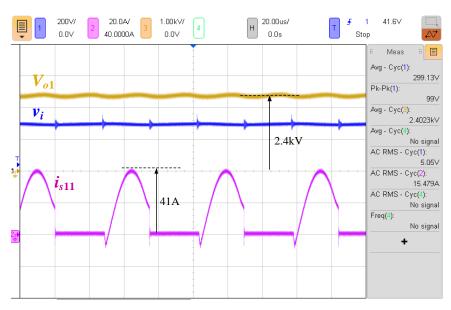

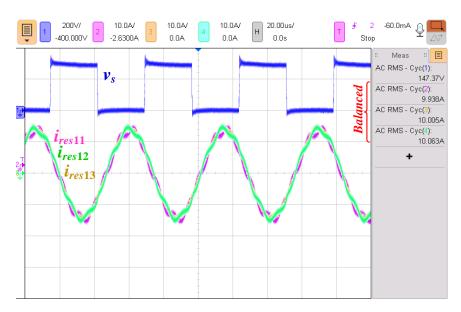

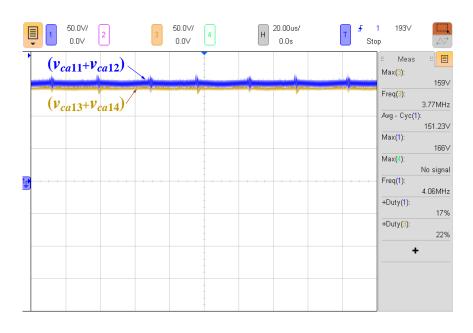

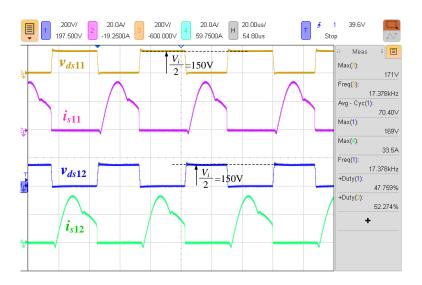

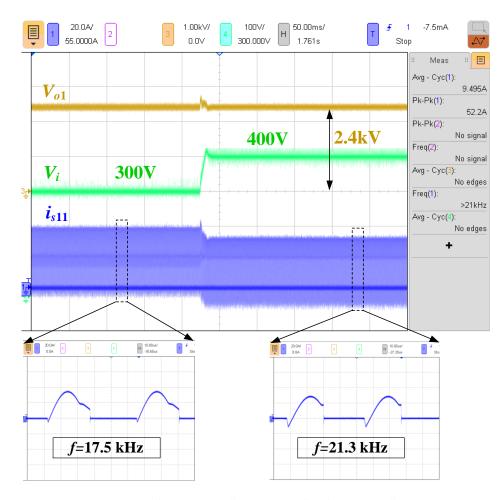

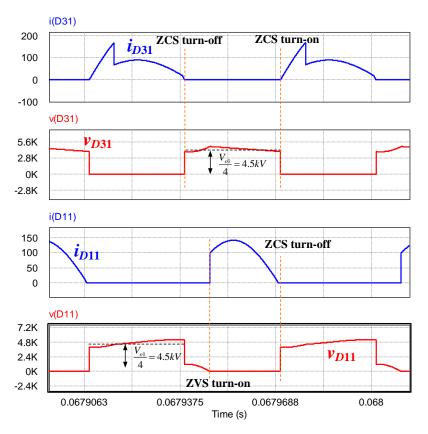

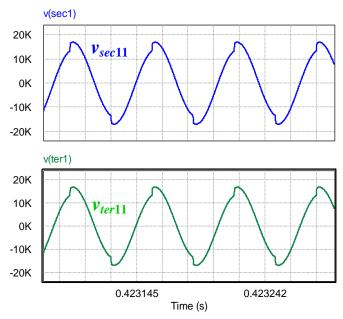

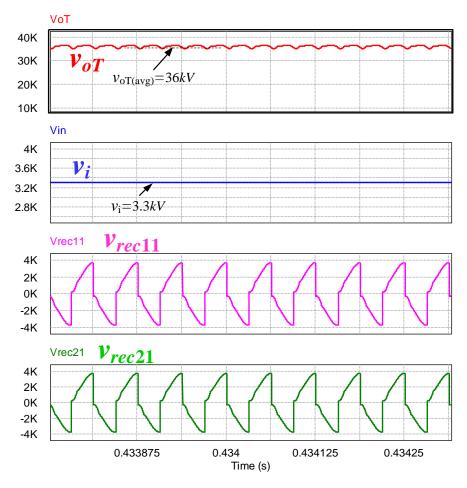

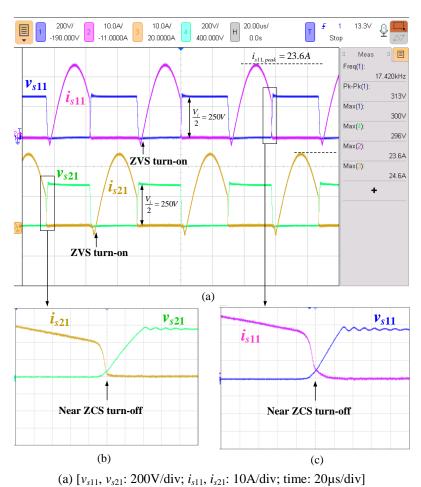

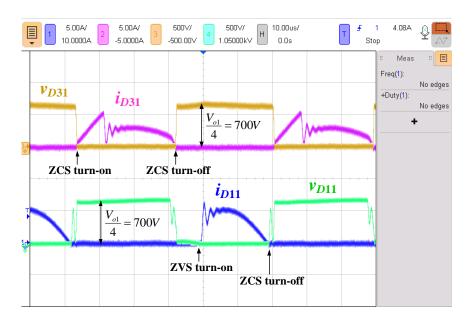

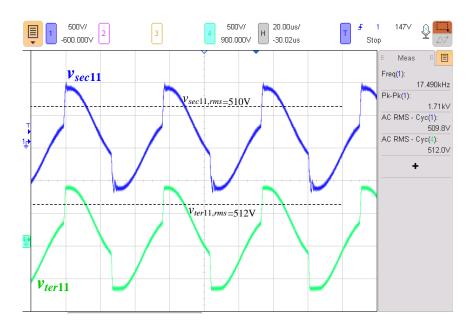

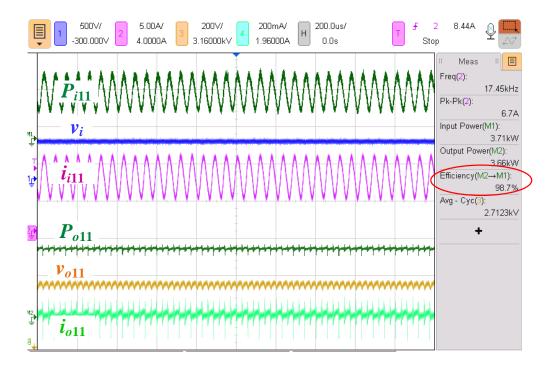

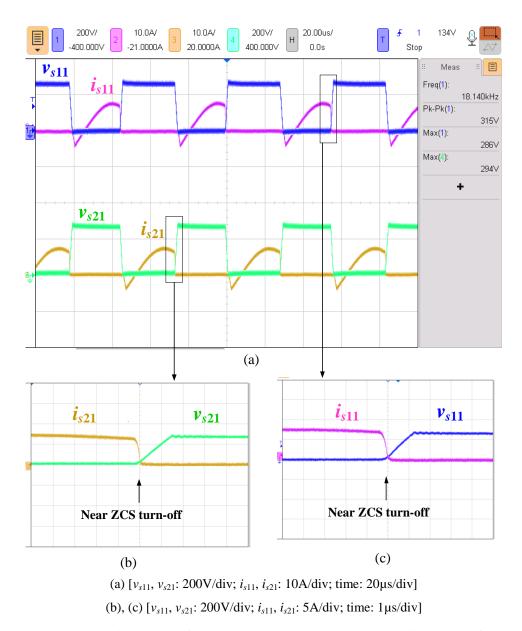

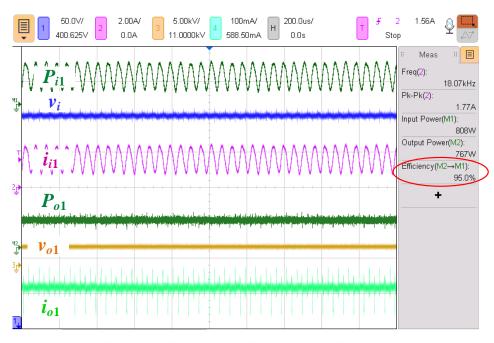

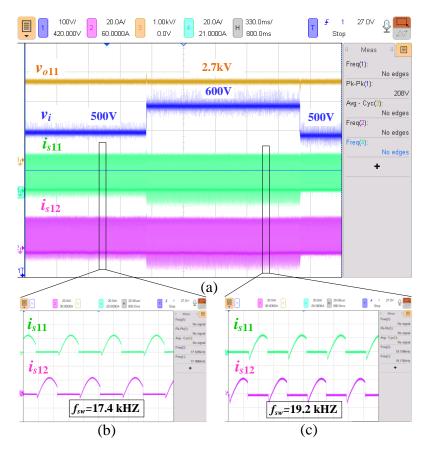

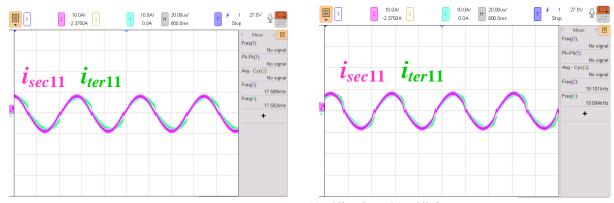

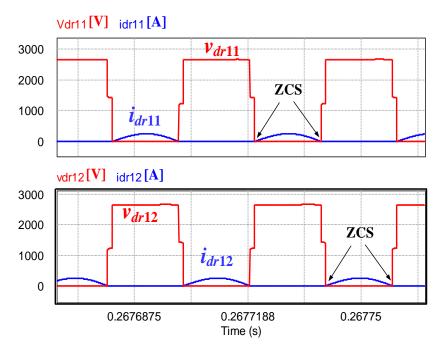

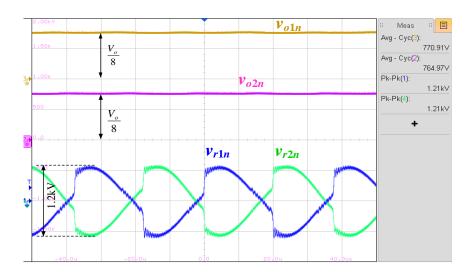

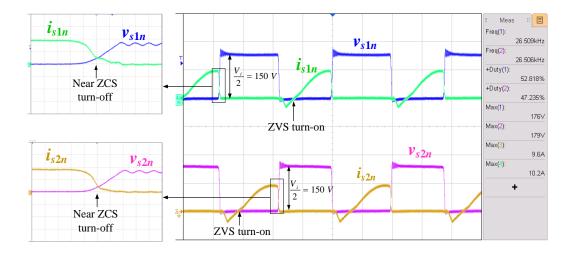

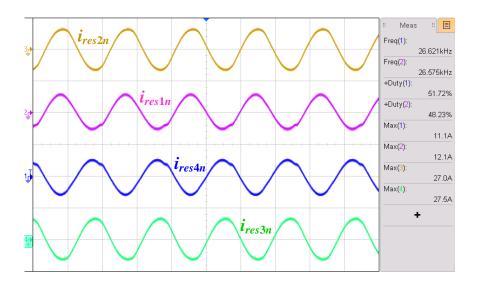

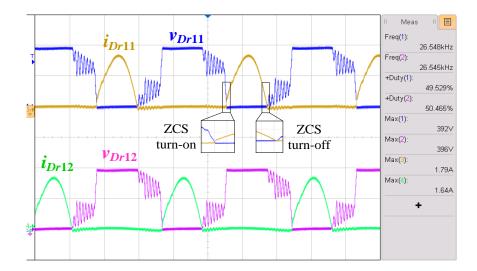

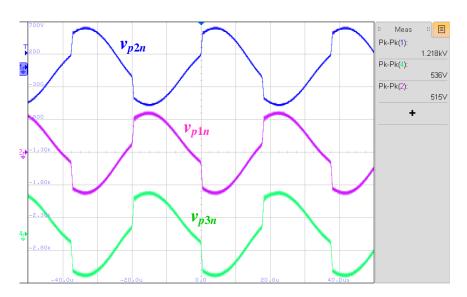

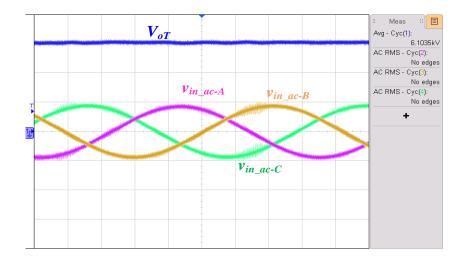

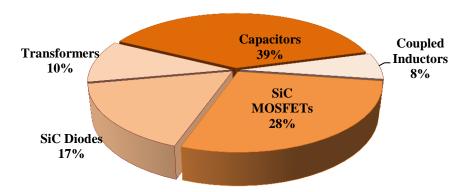

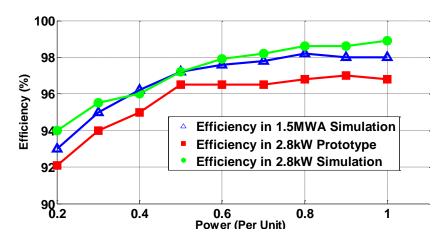

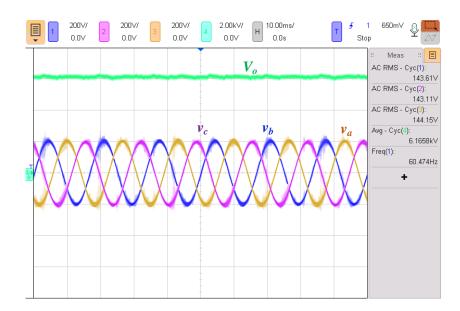

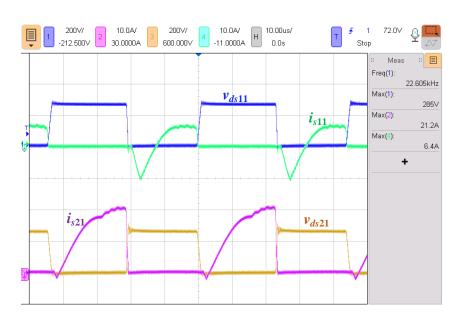

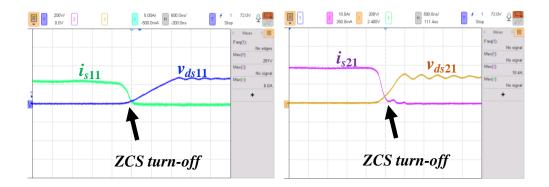

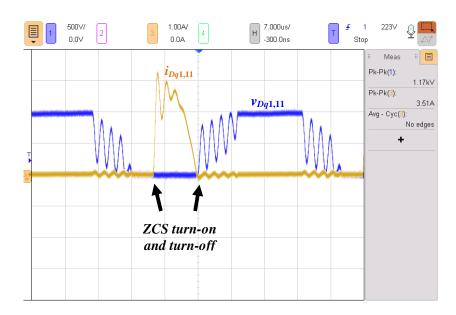

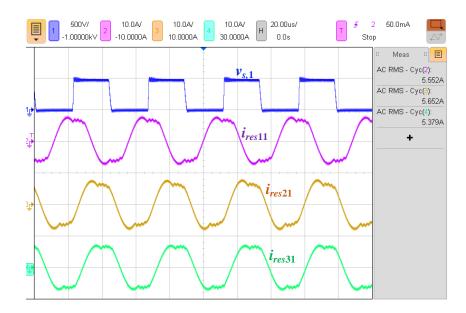

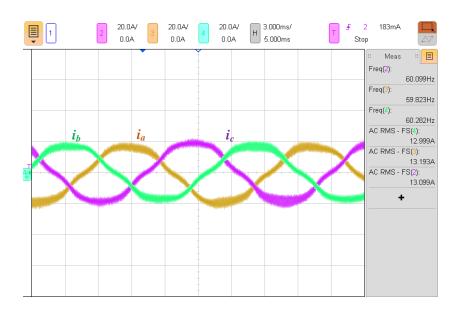

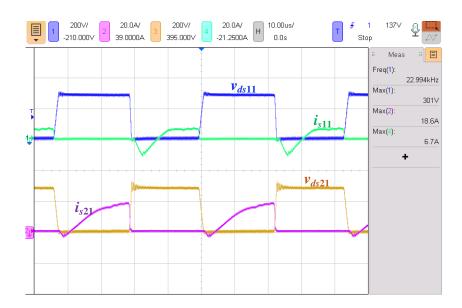

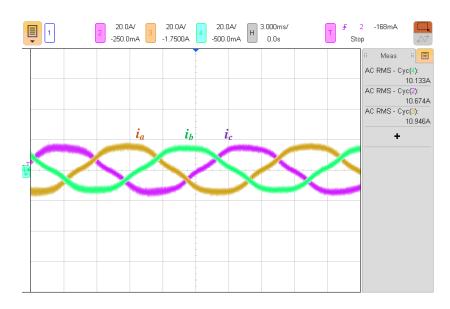

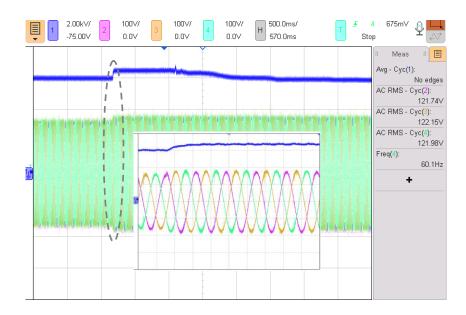

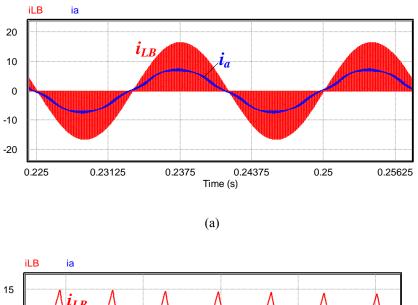

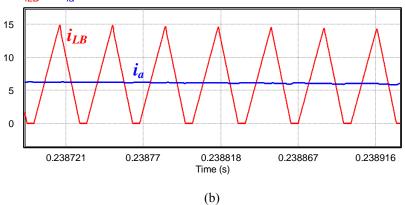

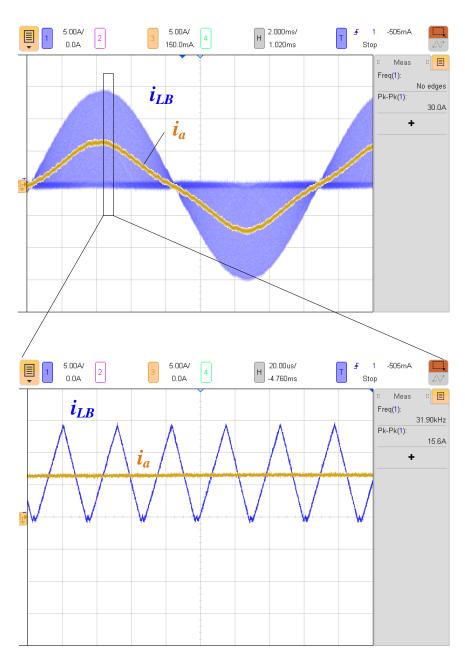

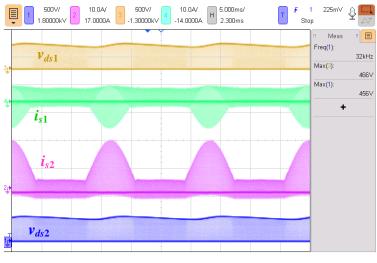

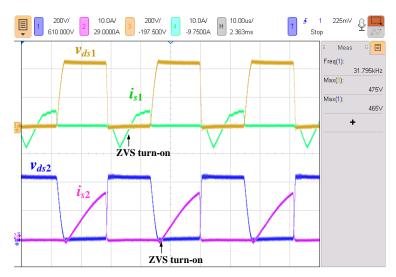

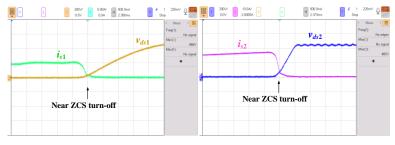

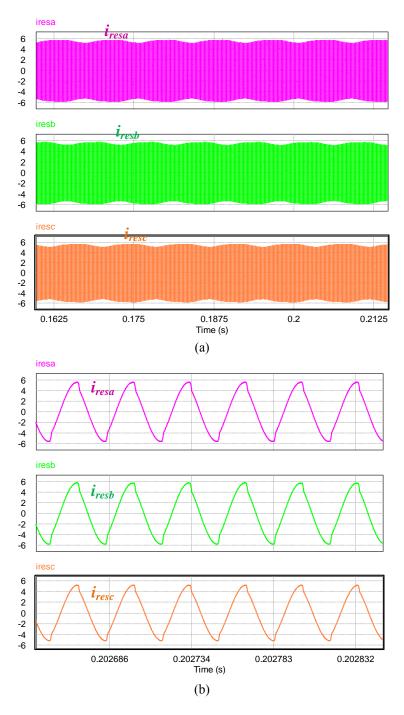

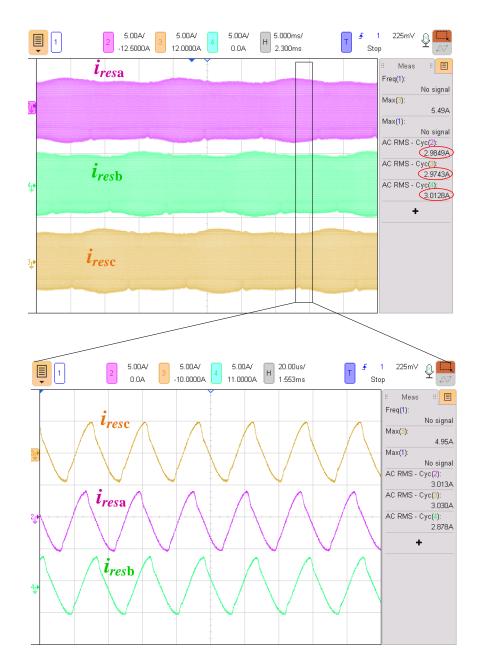

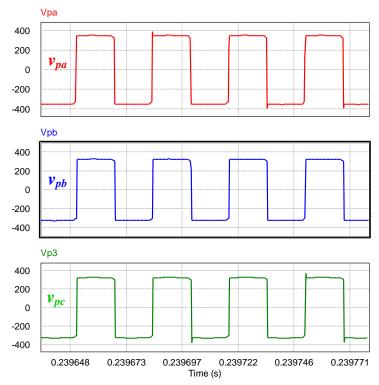

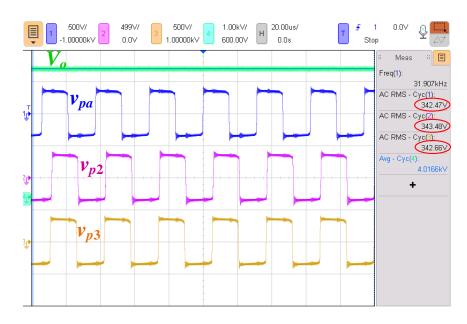

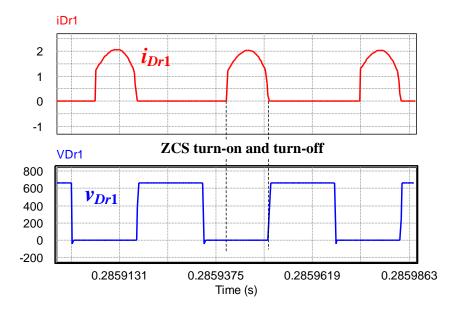

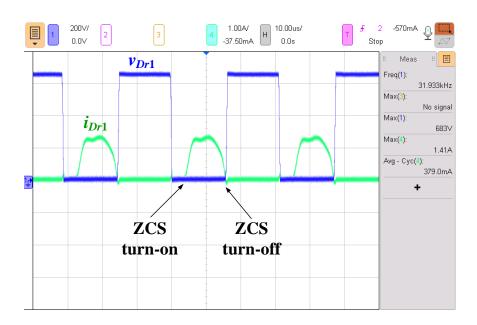

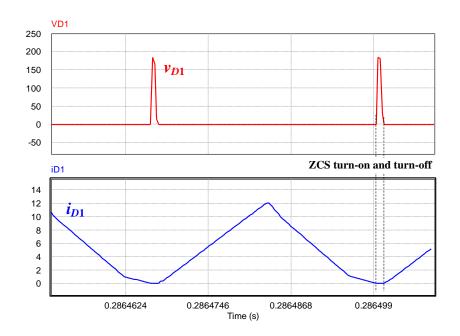

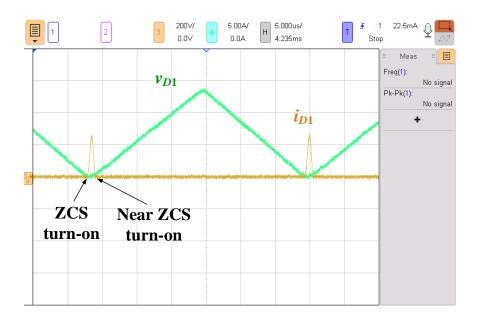

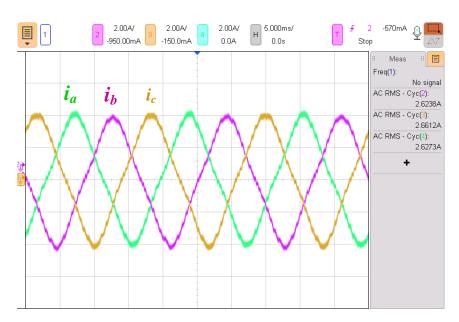

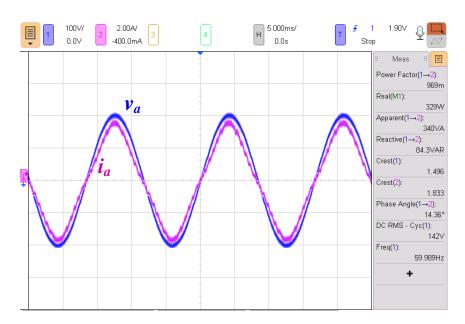

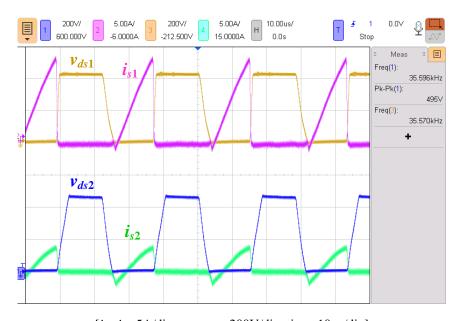

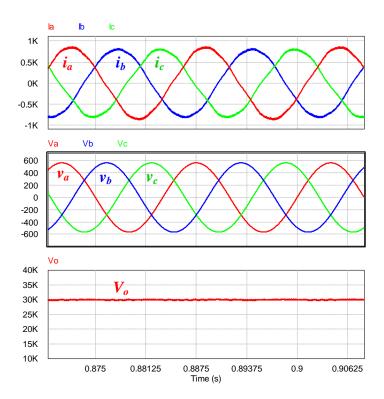

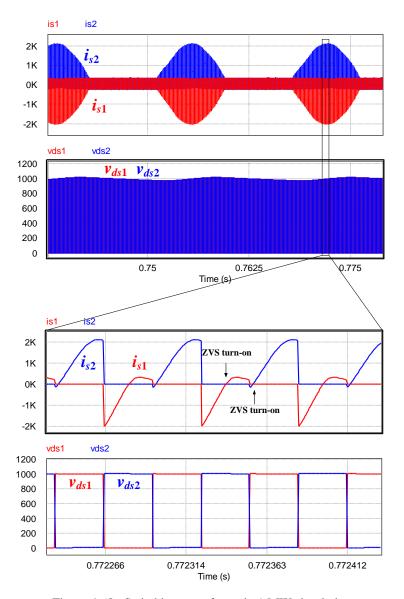

| Figure 2.47– Experimental waveforms at rated power condition with 99.3% measured efficiency per module                                                                                       | 99    |

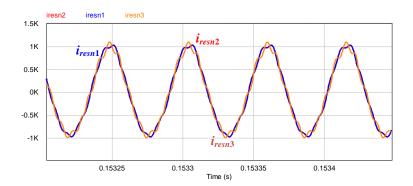

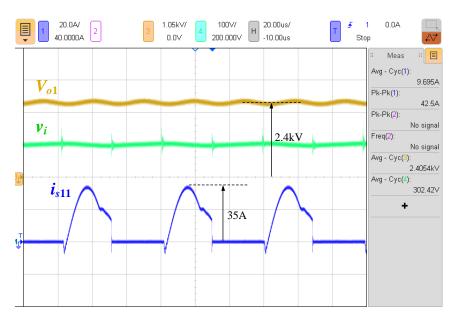

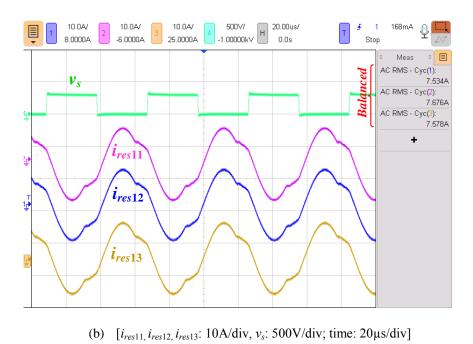

| Figure 2.48– Experimental waveforms at 20% reduction in the coupled inductance $(L_{sn})$                                                                                                    | .101  |

| Figure 2.49– Experimental waveforms at 20% increase in the resonant capacitance ( $C_{resn}$ )                                                                                               | .102  |

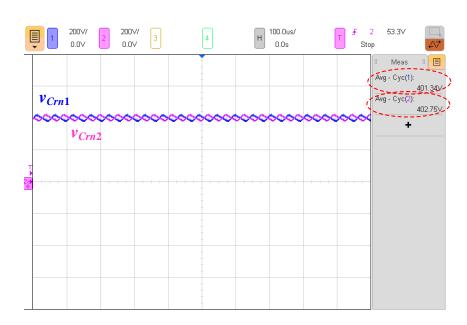

| Figure 2.50—Balanced voltage across the capacitors in the switch network at full-load condition; (a) across the dc-link capacitors; (b) across snubber capacitors                            | .103  |

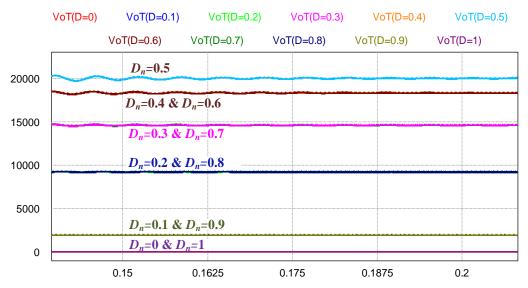

| Figure 2.51– Balanced voltage across the output capacitors                                                                                                                                   | . 103 |

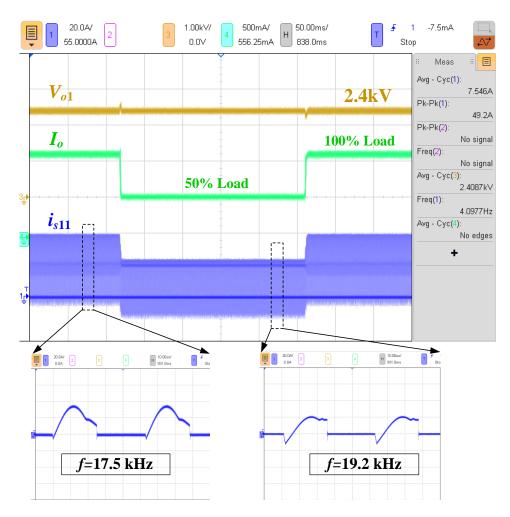

| Figure 2.52– Dynamic response with the step change in the load                                                                                                                               | .104  |

| Figure 2.53– Dynamic response with the step the input voltage                                                                                                                                | . 105 |

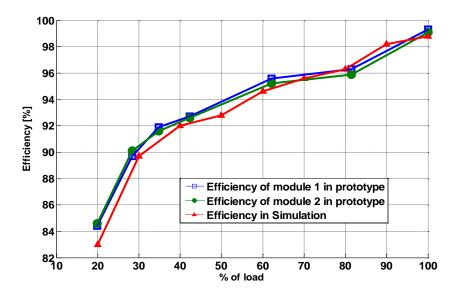

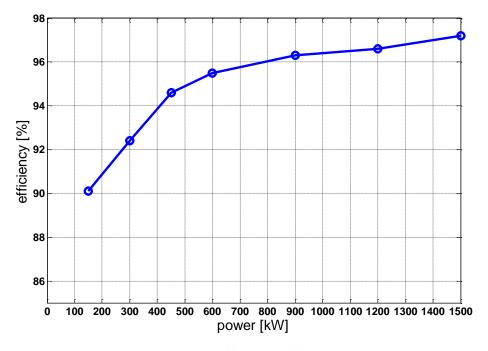

| Figure 2.54 – Measured efficiency of the experimental prototype and simulation results for different power level                                                                             |       |

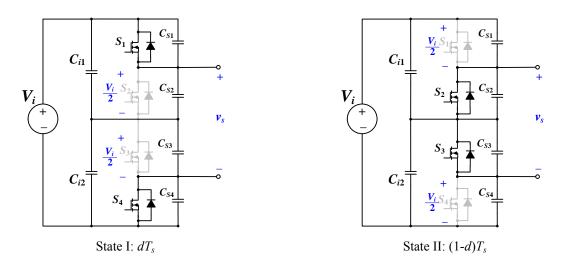

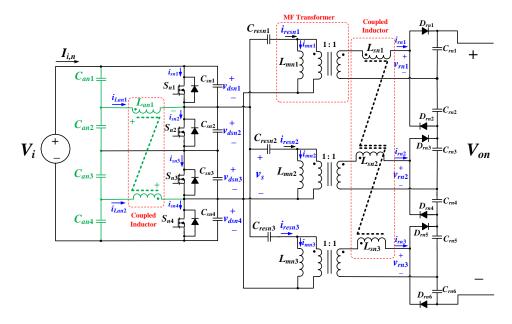

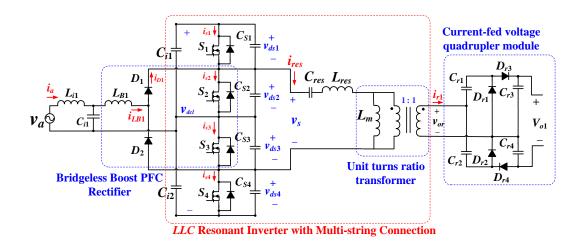

| Figure 3.1– Proposed MV coupled-voltage-quadruplers based step-up converter with 1:1:1 Transformer                                                                                           |       |

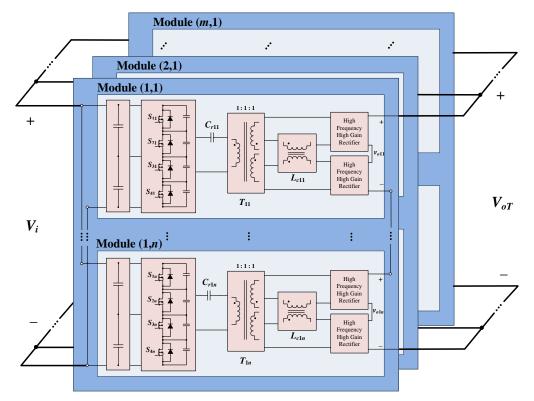

| Figure 3.2– Modular structure of the proposed converter                                                                                                                                      | .112  |

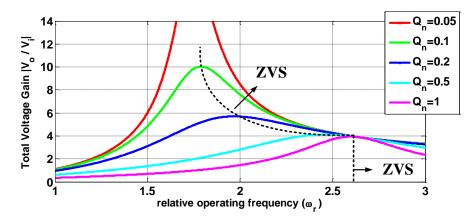

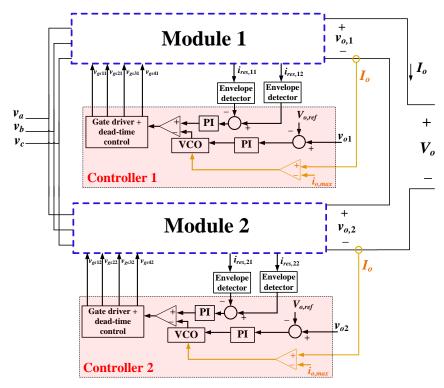

| Figure 3.3– Modular control scheme for the proposed converter                                                                                                                                | .114  |

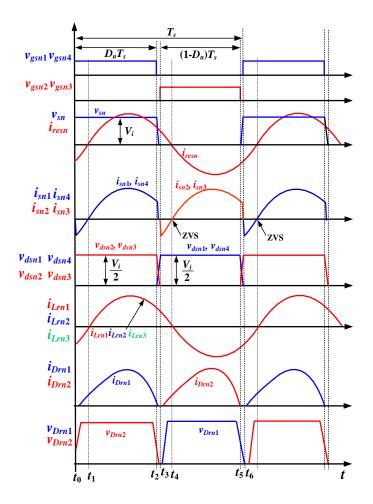

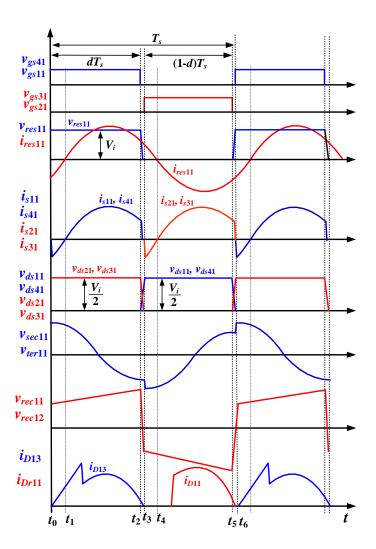

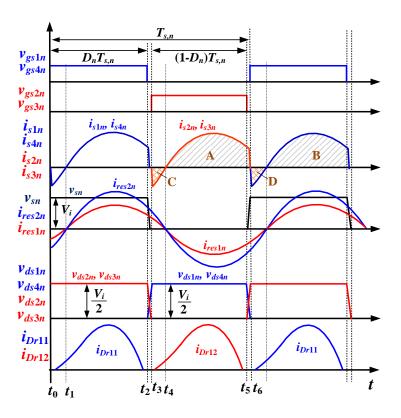

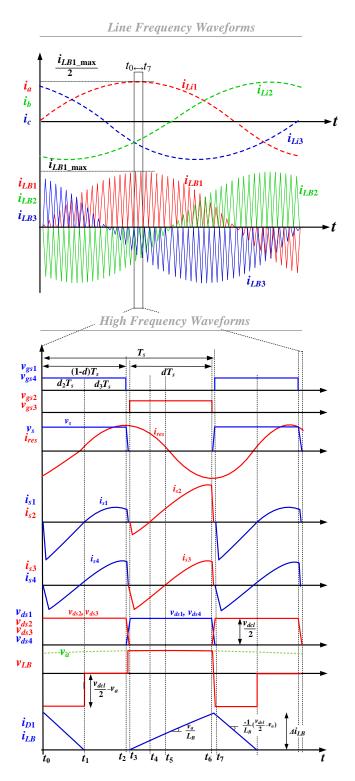

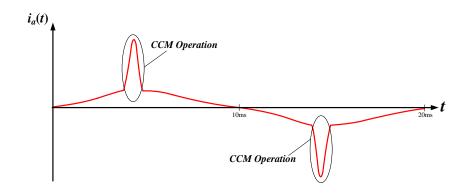

| Figure 3.4– Key operating waveforms of the converter for one module                                                                                                                          | .117  |

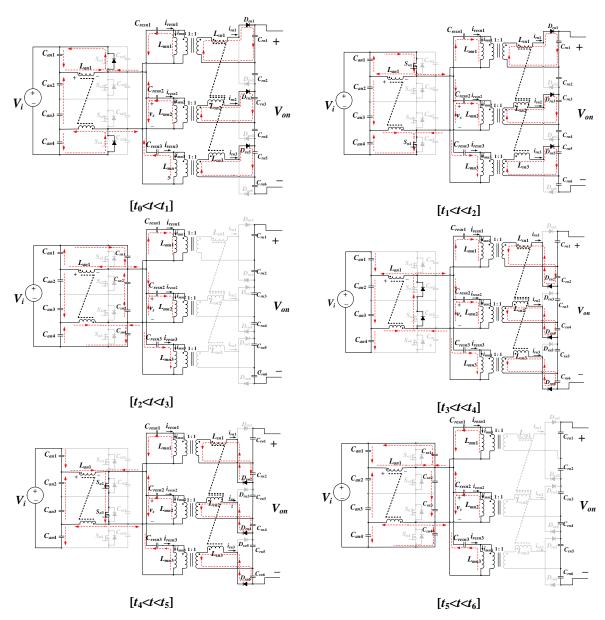

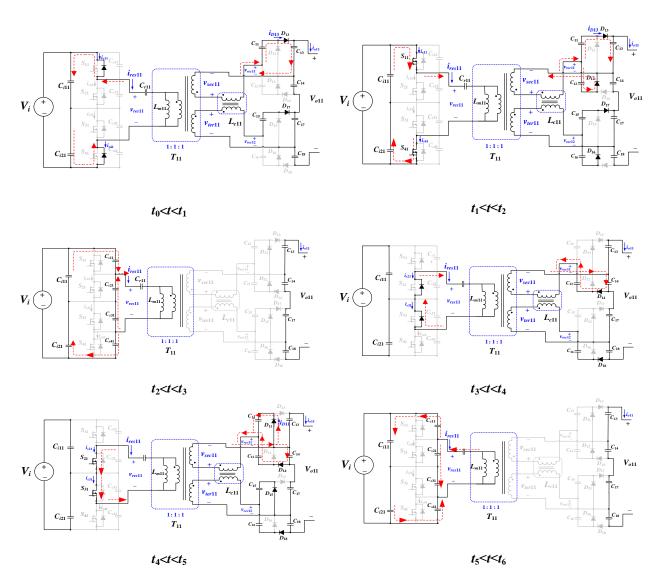

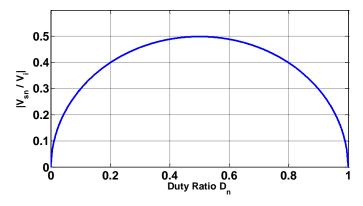

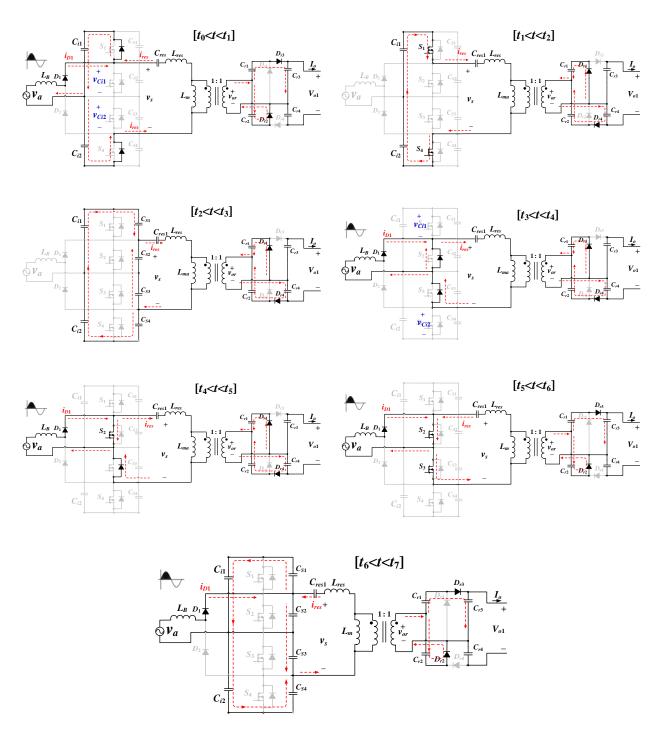

| Figure 3.5– Operating stages of the proposed converter within a switching period (illustrate with one module)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

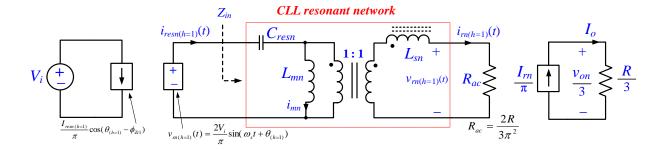

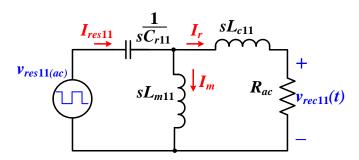

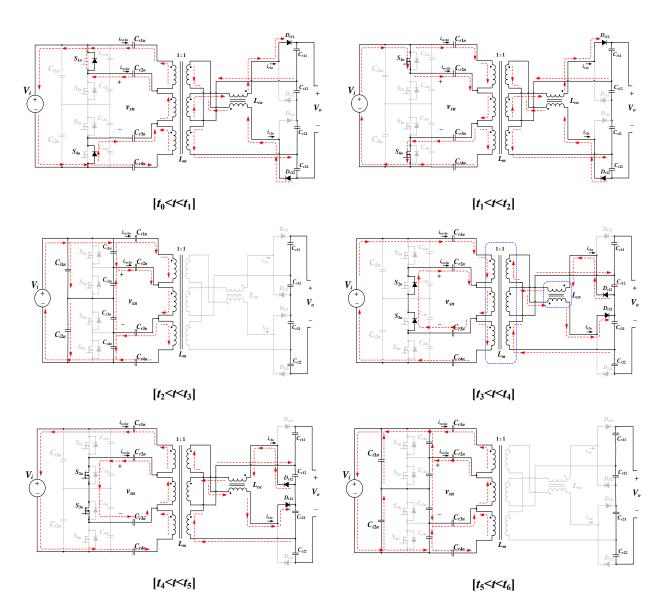

| Figure 3.6– The equivalent circuit of the proposed topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

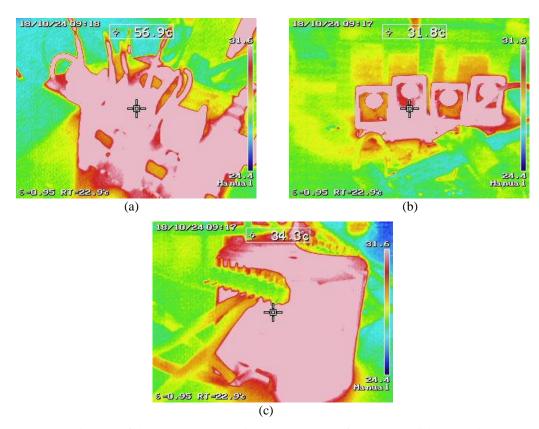

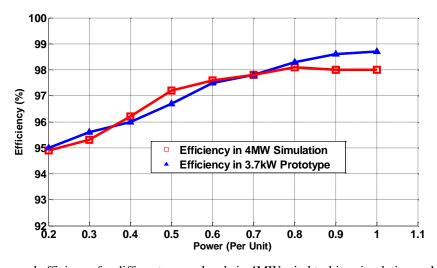

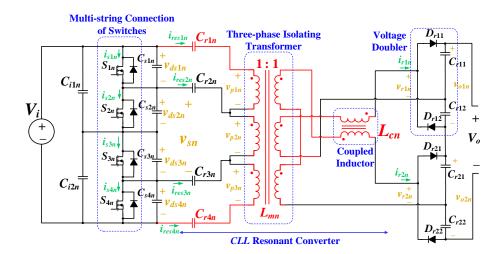

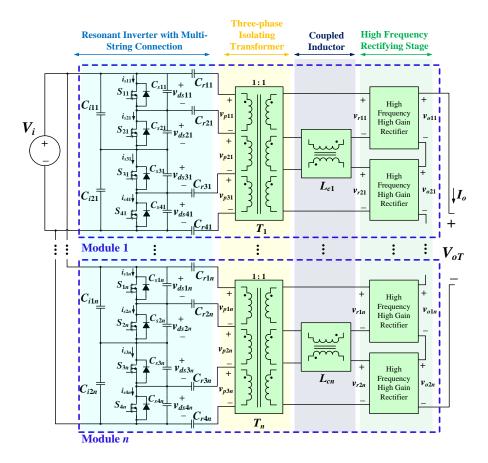

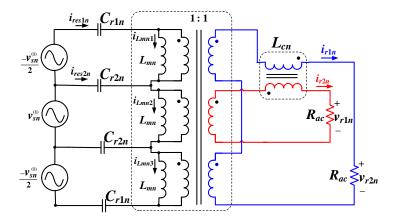

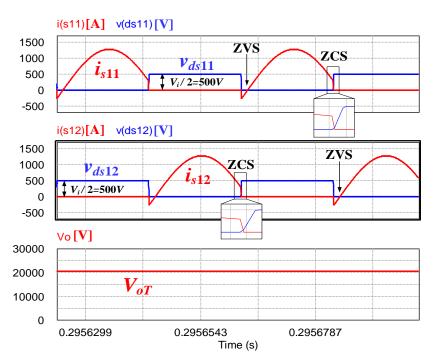

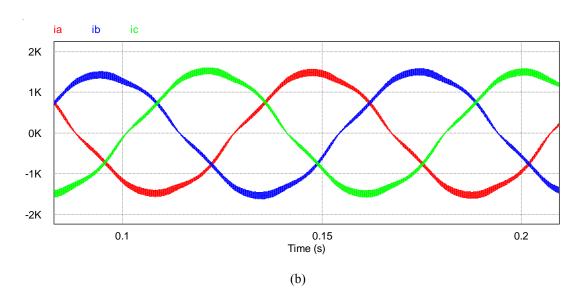

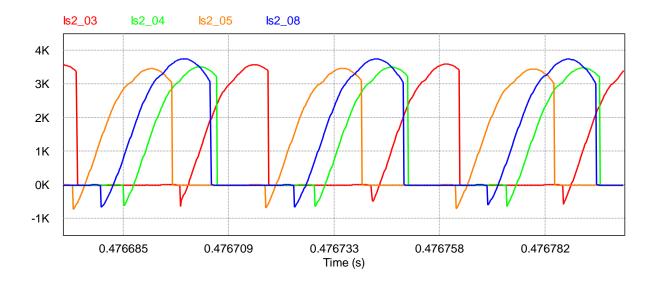

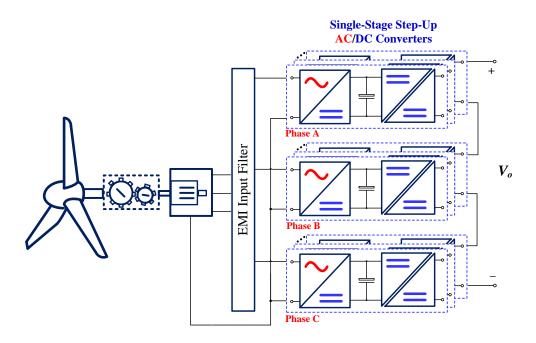

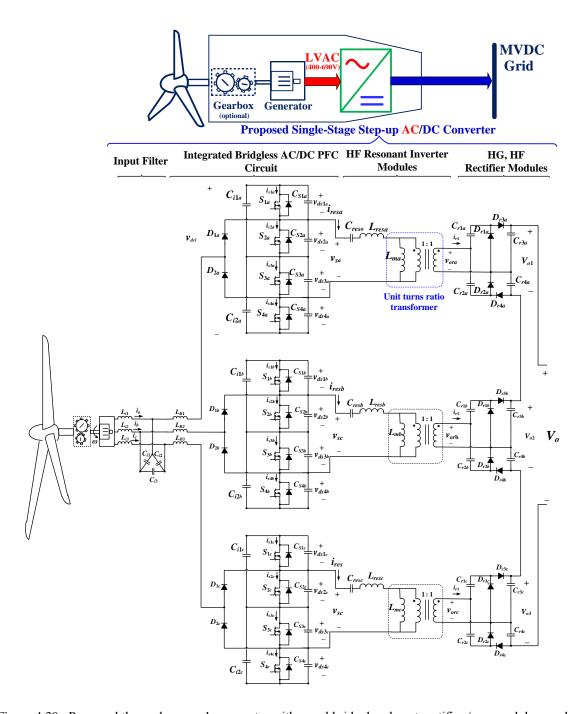

| Figure 3.7– Converter voltage gain as a function of $\omega_r$ and $k$ for $Q=4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |