# Design Techniques of Highly Integrated Hybrid-Switched-Capacitor-Resonant Power Converters for LED Lighting Applications

# Chengrui Le

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

COLUMBIA UNIVERSITY

# **ABSTRACT**

# Design Techniques of Highly Integrated Hybrid-Switched-Capacitor-Resonant Power Converters for LED Lighting Applications

# Chengrui Le

The Light-emitting diodes (LEDs) are rapidly emerging as the dominant light source given their high luminous efficacy, long lift span, and thanks to the newly enacted efficiency standards in favor of the more environmentally-friendly LED technology. The LED lighting market is expected to reach USD 105.66 billion by 2025. As such, the lighting industry requires LED drivers, which essentially are power converters, with high efficiency, wide input/output range, low cost, small form factor, and great performance in power factor, and luminance flicker. These requirements raise new challenges beyond the traditional power converter topologies. On the other hand, the development and improvement of new device technologies such as printed thin-film capacitors and integrated high voltage/power devices opens up many new opportunities for mitigating such challenges using innovative circuit design techniques and solutions.

Almost all electric products needs certain power delivery, regulation or conversion circuits to meet the optimized operation conditions. Designing a high performance power converter is a real challenge given the market's increasing requirements on energy efficiency, size, cost, form factor, EMI performance, human health impact, and so on. The design of a LED driver system covers from high voltage AC/DC and DC/DC power converters, to high frequency low voltage digital controllers, to power factor correction (PFC) and EMI filtering techniques, and to safety solutions such as galvanic isolation. In this thesis, we study design challenges and present corresponding solutions to realize highly integrated and high performance LED drivers combining switched-capacitor and resonant converters, applying re-configurable multi-level circuit topology, utilizing sigma delta modulation, and exploring

capacitive galvanic isolation.

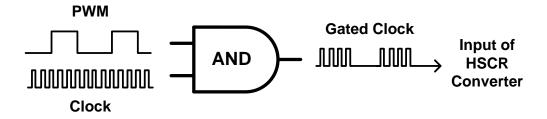

A hybrid switched-capacitor-resonant (HSCR) LED driver based on a stackable switched-capacitor (SC) converter IC rated for 15 to 20 W applications. Bulky transformers have been replaced with a SC ladder to perform high-efficiency voltage step-down conversion; an L-C resonant output network provides almost lossless current regulation and demonstrates the potential of capacitive galvanic isolation. The integrated SC modules can be stacked in the voltage domain to handle a large range of input voltage ranges that largely exceed the voltage limitation of the medium-voltage-rated 120 V silicon technology. The LED driver demonstrates > 91% efficiency over a rectified input DC voltage range from 160  $V_{DC}$  to 180  $V_{DC}$  with two stacked ICs; using a stack of four ICs > 89.6% efficiency is demonstrated over an input range from 320  $V_{DC}$  to 360  $V_{DC}$ . The LED driver can dim its output power to around 10% of the rated power while maintaining > 70% efficiency with a PWM controlled clock gating circuit.

Next, the design of AC main rectifier and inverter front end with sigma delta modulation is described. The proposed circuits features a pair of sigma delta controlled multilevel converters. The first is a multilevel rectifier responsible for PFC and dimming. The second is a bidirectional multilevel inverter used to cancel AC power ripple from the DC bus. The system also contains an output stage that powers the LEDs with DC and provides for galvanic isolation. Its functional performance indicates that integrated multilevel converters are a viable topology for lighting and other similar applications.

# Table of Contents

| 1 | Intr | oducti | $_{ m n}$                                  |

|---|------|--------|--------------------------------------------|

|   | 1.1  | Funda  | nental of Lighting                         |

|   |      | 1.1.1  | Light Basics                               |

|   |      | 1.1.2  | Human Vision                               |

|   |      | 1.1.3  | Luminance Flicker                          |

|   |      | 1.1.4  | History of Artificial Lighting             |

|   | 1.2  | LED-I  | ased Lighting                              |

|   |      | 1.2.1  | Characteristics of LEDs                    |

|   |      | 1.2.2  | Application of LEDs in Lighting            |

|   | 1.3  | Introd | ction of LED Driver                        |

|   |      | 1.3.1  | The Fundamentals of LED Drivers            |

|   |      |        | 1.3.1.1 Current Regulation                 |

|   |      |        | 1.3.1.2 Power Efficiency                   |

|   |      |        | 1.3.1.3 Input and Output Range             |

|   |      |        | 1.3.1.4 Power Factor Correction            |

|   |      |        | 1.3.1.5 Flicker                            |

|   |      |        | 1.3.1.6 Safety                             |

|   |      | 1.3.2  | Types of LED Drivers                       |

|   |      |        | 1.3.2.1 Linear LED Driver                  |

|   |      |        | 1.3.2.2 Switched-Mode LED Driver           |

|   |      |        | 1.3.2.3 Inductor Based LED Driver          |

|   |      |        | 1.3.2.4 Switched-Capacitor Power Converter |

|   |     |         | 1.3.2.5 Resonant Converter based LED Driver            | 22        |

|---|-----|---------|--------------------------------------------------------|-----------|

|   | 1.4 | Integra | ation of Power Converters                              | 23        |

|   | 1.5 | Thesis  | S Organization                                         | 24        |

| 2 | Hyb | orid-Sv | witched-Capacitor-Resonant DC-DC Converter Design      | <b>25</b> |

|   | 2.1 | Introd  | uction                                                 | 25        |

|   | 2.2 | Hybrid  | d-Switched-Capacitor-Resonant DC-DC Converter          | 29        |

|   |     | 2.2.1   | System Architecture                                    | 29        |

|   |     | 2.2.2   | Power Loss of the SC Ladder                            | 31        |

|   |     | 2.2.3   | Multi-level Resonant Output Network                    | 33        |

|   |     | 2.2.4   | Design of the Resonant Tank                            | 35        |

|   |     |         | 2.2.4.1 Circuit Analysis                               | 35        |

|   |     |         | 2.2.4.2 Zero Voltage Switching (ZVS)                   | 38        |

|   |     | 2.2.5   | LED Dimming                                            | 39        |

|   |     | 2.2.6   | Safety Performance                                     | 39        |

|   | 2.3 | HSCR    | LED Driver IC Design and Building Blocks               | 44        |

|   |     | 2.3.1   | Chip-Stacking Topology                                 | 44        |

|   |     | 2.3.2   | Overall Architecture                                   | 44        |

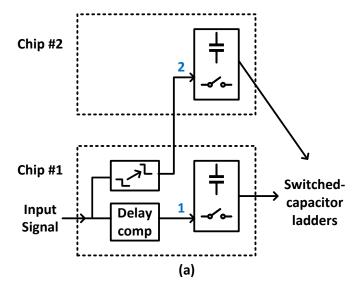

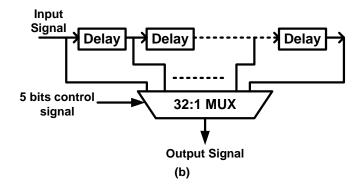

|   |     | 2.3.3   | Signal Path and Delay Compensation                     | 46        |

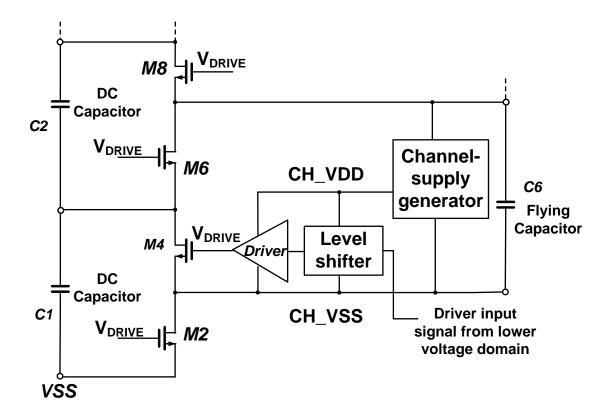

|   |     | 2.3.4   | Gate-Driving Circuits Implementation                   | 48        |

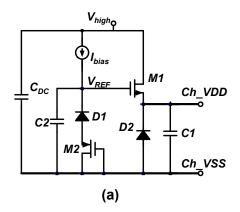

|   |     |         | 2.3.4.1 Channel-Supply Generator                       | 48        |

|   |     |         | 2.3.4.2 Level Shifter                                  | 49        |

|   |     |         | 2.3.4.3 Converter Start-Up                             | 51        |

|   | 2.4 | Exper   | imental Results                                        | 52        |

|   |     | 2.4.1   | Measurement Setup                                      | 52        |

|   |     | 2.4.2   | Converter Performance with Different L-C Output Stages | 54        |

|   |     | 2.4.3   | Four-chip-stacking DC-DC Converter                     | 57        |

|   |     | 2.4.4   | Performance Comparison                                 | 60        |

|   | 2.5 | Metac   | apacitors for LED Drivers                              | 61        |

|   |     | 2.5.1   | Introduction of Metacapacitor                          | 61        |

|   |     | 2.5.2   | Integration of Metacapacitors and the HSCR LED Driver  | 62        |

|    |        | 2.5.3   | Measurement results                                         | 63 |

|----|--------|---------|-------------------------------------------------------------|----|

|    | 2.6    | Conclu  | asions                                                      | 66 |

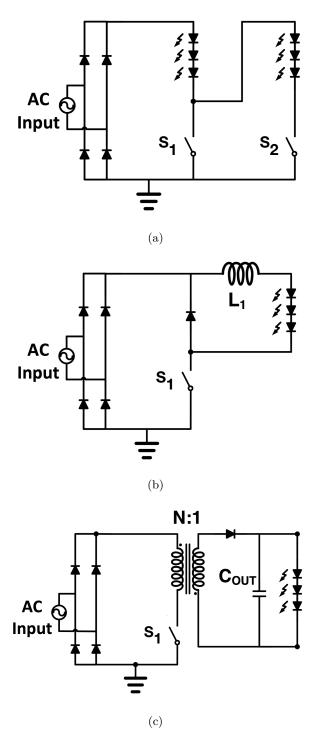

| 3  | Pow    | ver Fac | tor Correction and Ripple Canceling AC-DC Rectifier Design  | 68 |

|    | 3.1    | Introd  | uction                                                      | 68 |

|    |        | 3.1.1   | Power Factor Correction                                     | 69 |

|    |        | 3.1.2   | Flicker Mitigation                                          | 69 |

|    | 3.2    | Multi-  | Level Switched-Capacitor PFC and Ripple Canceling Rectifier | 74 |

|    |        | 3.2.1   | Full System Architecture                                    | 74 |

|    |        | 3.2.2   | Multilevel Topology for PFC and Ripple Cancellation Module  | 74 |

|    | 3.3    | Sigma   | Delta Control                                               | 77 |

|    |        | 3.3.1   | Introduction of the Sigma Delta Control Loop                | 77 |

|    |        | 3.3.2   | Control for the PFC Rectifier                               | 77 |

|    |        | 3.3.3   | Control for the Ripple Cancellation Module                  | 78 |

|    | 3.4    | Multi-  | level Transformer Based Output Stage                        | 79 |

|    | 3.5    | Exper   | imental Results                                             | 81 |

|    |        | 3.5.1   | Integration and Testing                                     | 81 |

|    |        | 3.5.2   | Data and Results                                            | 82 |

|    | 3.6    | Conclu  | asions                                                      | 89 |

| 4  | Con    | nclusio | ns and Future Works                                         | 90 |

|    | 4.1    | Summ    | ary of Proposed LED Driver Solutions                        | 90 |

|    | 4.2    | Possib  | le Directions for Future Studies                            | 92 |

| Bi | ibliog | graphy  |                                                             | 95 |

# List of Figures

| 1.1 | Jablochkoff candle                                                                             | 7  |

|-----|------------------------------------------------------------------------------------------------|----|

| 1.2 | LED device structure and operation physics                                                     | 10 |

| 1.3 | Example I-V curves of red, green, and blue LED devices                                         | 10 |

| 1.4 | Example of commercial LED light bulb with smart color control                                  | 15 |

| 1.5 | Example of (a) linear voltage regulator using an Op-Amp (LM317) and (b)                        |    |

|     | linear current regulator as LED driver                                                         | 18 |

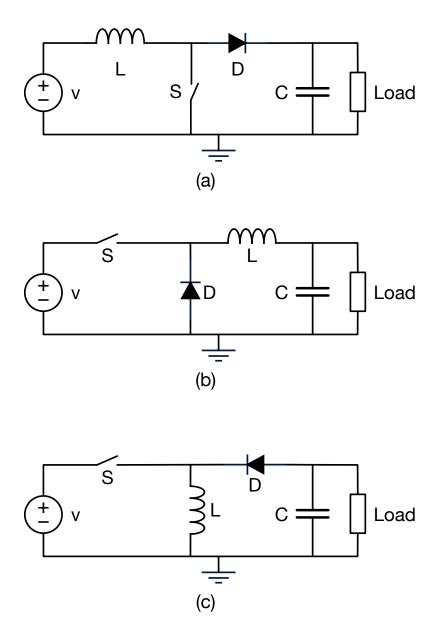

| 1.6 | Basic schematics of (a) a boost converter, (b) a buck converter, and (c) a                     |    |

|     | buck-boost converter                                                                           | 20 |

| 1.7 | Basic schematic of a flyback converter                                                         | 21 |

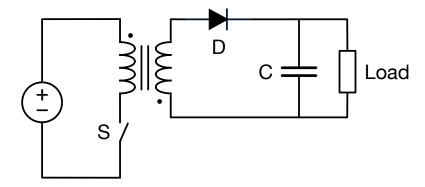

| 1.8 | Basic schematic of a voltage doubler                                                           | 22 |

| 2.1 | Schematics of LED drivers: (a) Simplified circuit of a AC/DC converter free                    |    |

|     | LED driver; (b) Simplified circuit of a conventional Buck LED driver; (c)                      |    |

|     | Simplified circuit of a conventional off-line flyback LED driver                               | 27 |

| 2.2 | Dissembled commercial flyback LED driver circuit                                               | 28 |

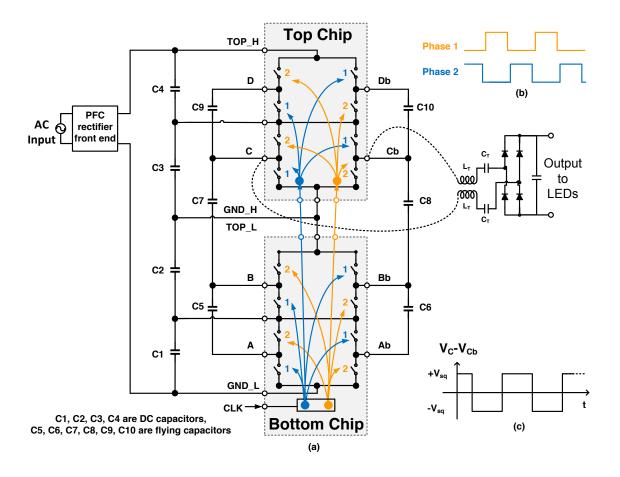

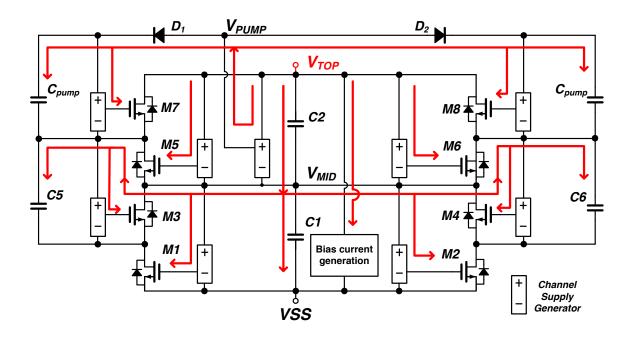

| 2.3 | ${\rm (a)\ System\ architecture\ of\ the\ chip-stacking\ hybrid-switched-capacitor-resonant}}$ |    |

|     | LED driver. (b) Two-phase non-overlapping gate drive signals. (c) Differen-                    |    |

|     | tial output signal between nodes $C$ and $C_b$ of the SC ladder                                | 30 |

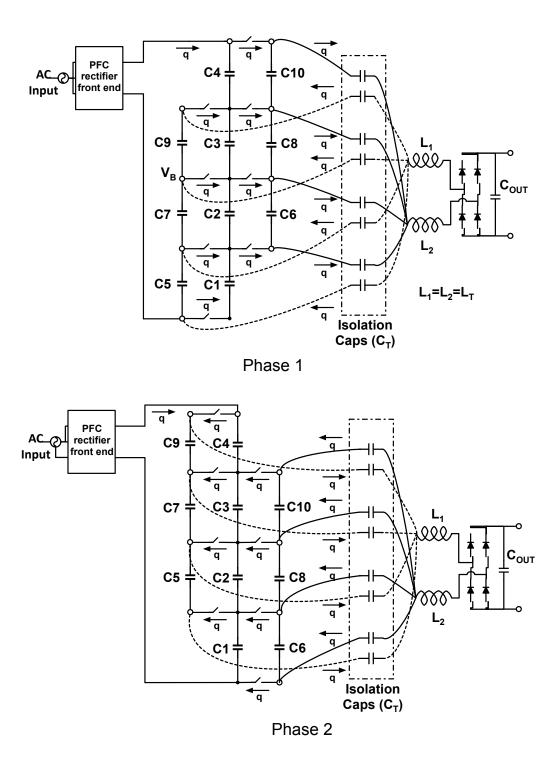

| 2.4 | Charge flow in SC ladder when the L-C resonant bridge is attached to all                       |    |

|     | four pairs of differential notes                                                               | 34 |

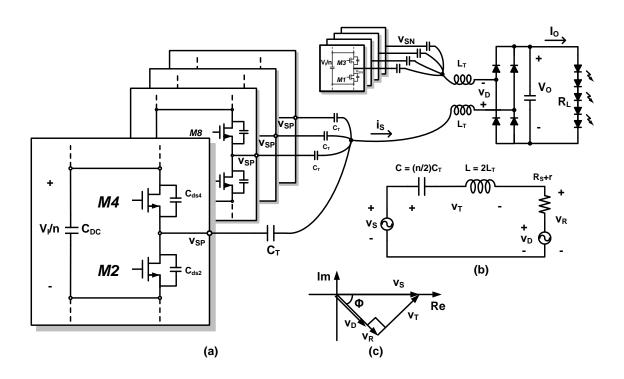

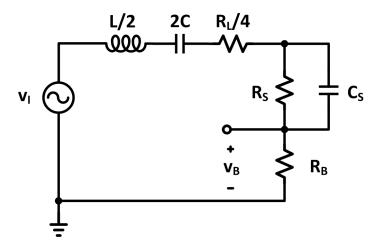

| 2.5 | (a) Equivalent circuit of the HSCR converter for AC analysis. (b) Simpli-                      |    |

|     | fied single-end equivalent circuit of the HSCR DC-DC converter. (c) Phase                      |    |

|     | diagram used to design the resonant tank                                                       | 36 |

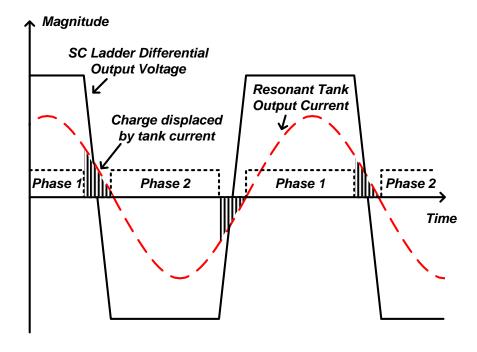

| 2.6  | Example of ideal zero voltage switching waveforms. Solid: SC ladder differ-    |    |

|------|--------------------------------------------------------------------------------|----|

|      | ential output voltage. Dashed: resonant tank current. Dotted: two-phase        |    |

|      | gate-drive voltages                                                            | 38 |

| 2.7  | PWM dimming of the LED driver                                                  | 40 |

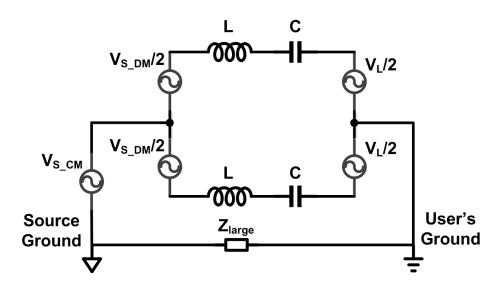

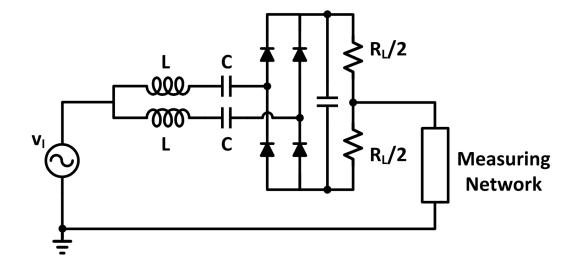

| 2.8  | Simplified HSCR LED driver circuit diagram                                     | 41 |

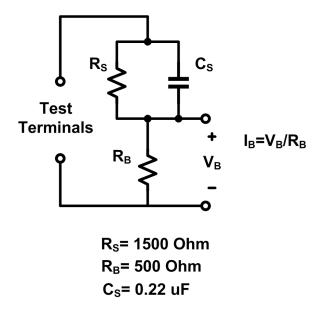

| 2.9  | Equivalent circuit of the HSCR LED driver for common mode signal analysis.     | 41 |

| 2.10 | Circuit configuration to measure the 120 Hz leakage current                    | 42 |

| 2.11 | The human body model for unweighted touch current measurement                  | 43 |

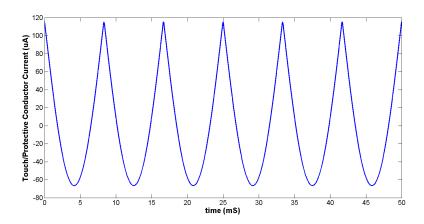

| 2.12 | Half circuit of the 120 Hz leakage current measurement circuit                 | 43 |

| 2.13 | Calculated touch/protective conductor current waveform                         | 44 |

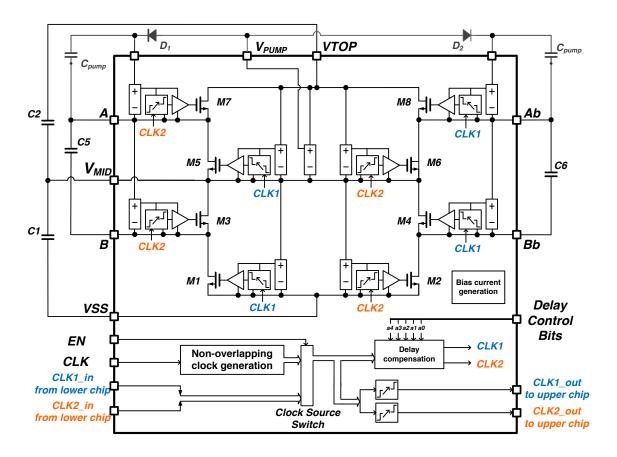

| 2.14 | Architecture of the SC Converter IC                                            | 45 |

| 2.15 | Block diagram of the (a) delay compensation system; and (b) digital con-       |    |

|      | trolled delay generation chain                                                 | 47 |

| 2.16 | Block diagram of the gate driver                                               | 48 |

| 2.17 | Schematic of (a) the channel-supply generator and (b) the level shifter        | 50 |

| 2.18 | Charge flow in the start-up phase of the converter                             | 51 |

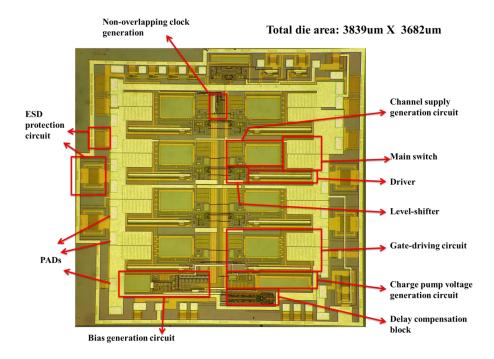

| 2.19 | SC converter die photo                                                         | 53 |

| 2.20 | The two-chip-stacking DC/DC converter for LED driver                           | 53 |

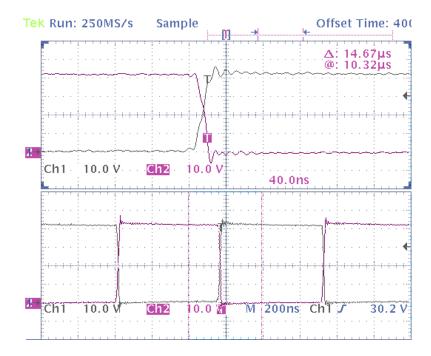

| 2.21 | Voltage waveforms of the differential output nodes of the switched-capacitor   |    |

|      | ladder (nodes A and Ab in Fig. 2.3). The waveform on top (Ch1) is a zoomed     |    |

|      | view of the switching edge of the signals                                      | 55 |

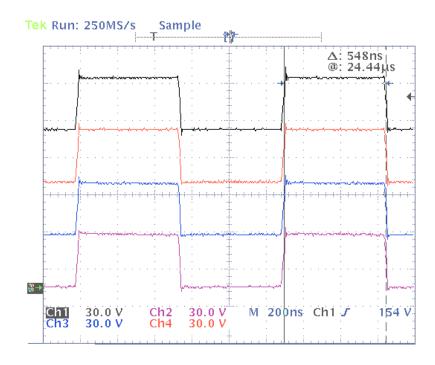

| 2.22 | Voltage waveforms the flying nodes on one side of the switched-capacitor       |    |

|      | ladder (nodes A, B, C, D in Fig. 2.3)                                          | 56 |

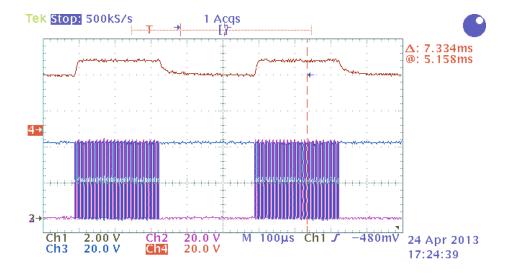

| 2.23 | Voltage across the LED string during dimming (upper waveform) and the          |    |

|      | voltage of the differential output nodes A and Ab in Fig. 2.3 (lower wave-     |    |

|      | form)                                                                          | 56 |

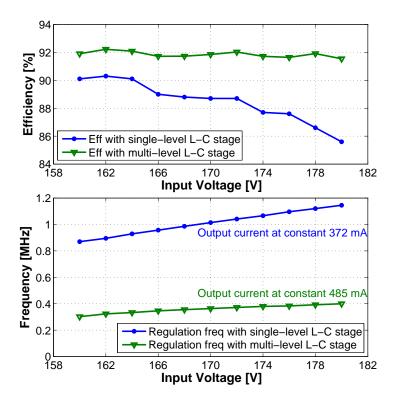

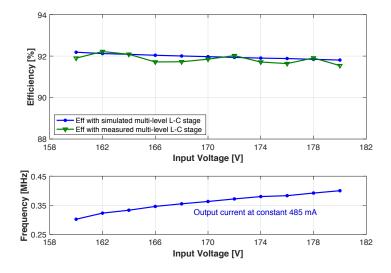

| 2.24 | Measured switching frequencies, output currents, and efficiencies versus input |    |

|      | voltage variation of proposed LED driver with single-level and multi-level     |    |

|      | output L-C stages connected                                                    | 57 |

| 2.25 | Theoretically calculated and measured efficiencies versus input voltage vari-     |    |

|------|-----------------------------------------------------------------------------------|----|

|      | ation of the proposed LED driver with multi-level output L-C stages               | 58 |

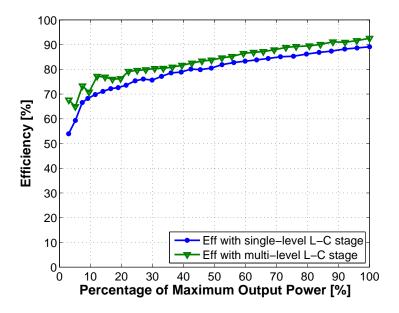

| 2.26 | Measured efficiency versus dimmed output power of proposed LED driver             |    |

|      | with single-level and multi-level output L-C stages connected. The input          |    |

|      | voltage is 170 $V_{DC}$                                                           | 58 |

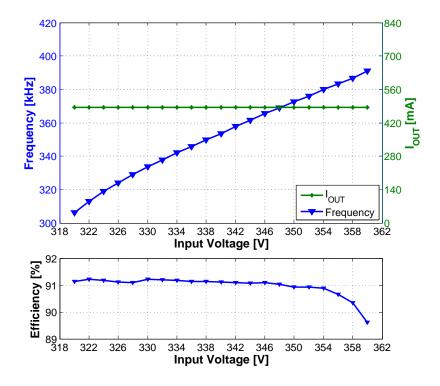

| 2.27 | Measured switching frequency, output current, and efficiency versus input         |    |

|      | voltage variation of proposed LED driver with rectified 240V AC (340V DC)         |    |

|      | input                                                                             | 59 |

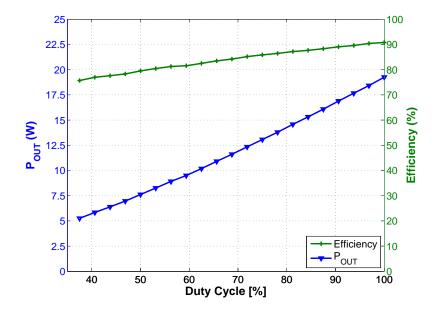

| 2.28 | Measured output power and efficiency versus dimming duty cycle of proposed        |    |

|      | LED driver with rectified 240V AC (340V DC) input                                 | 60 |

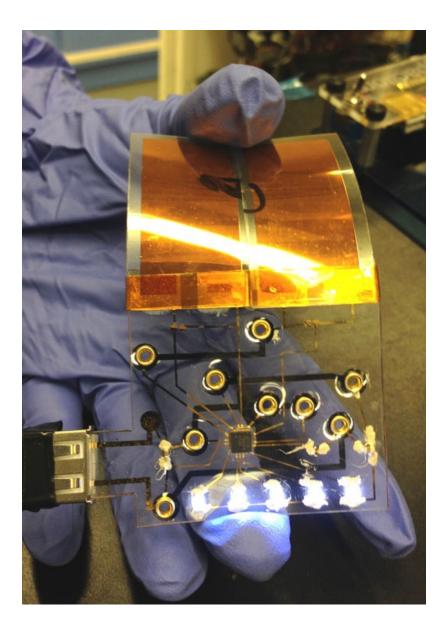

| 2.29 | Two printed thin-film Metacapacitors integrated with a commercial converter       |    |

|      | IC on a flexible substrate                                                        | 64 |

| 2.30 | Single-stack HSCR LED driver integrated with two printed Metacapacitors           |    |

|      | driving a series of LEDs                                                          | 65 |

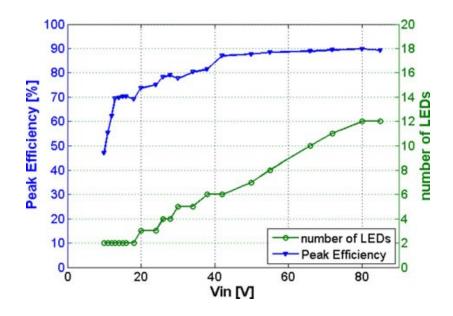

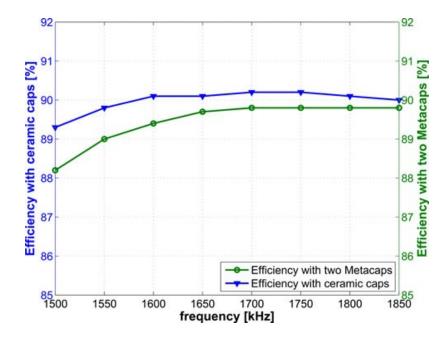

| 2.31 | Peak efficiency of the LED driver with input voltage and load variation           | 65 |

| 2.32 | Measured efficiency of the 2:1 HSCR LED driver using two Metacapacitors           |    |

|      | versus using all ceramic capacitors                                               | 66 |

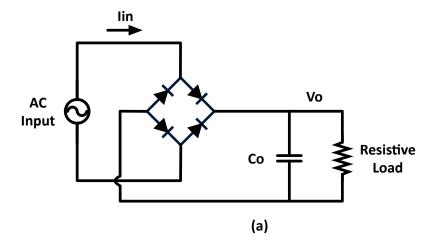

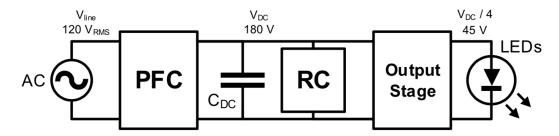

| 3.1  | Conceptual schematic of (a) a non-PFC AC-DC converter and (b) its voltage         |    |

|      | and current waveforms                                                             | 70 |

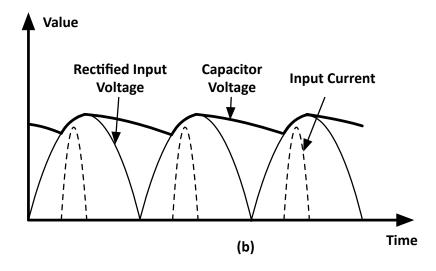

| 3.2  | Conceptual schematic of a active PFC AC-DC buck converter                         | 71 |

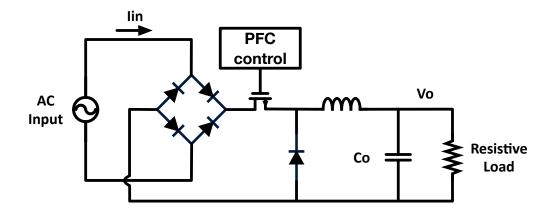

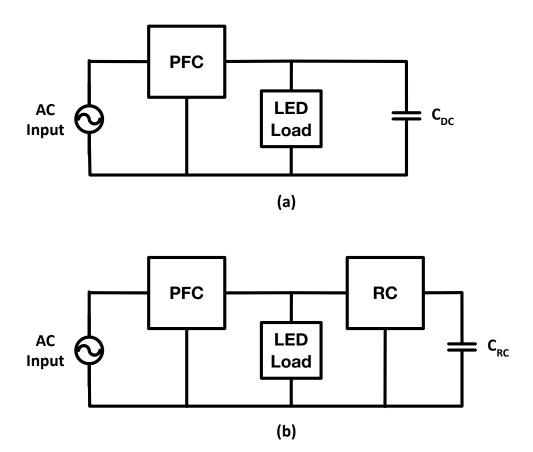

| 3.3  | Conceptual diagram of (a) the passive ripple canceling method with large          |    |

|      | capacitor $C_{DC}$ and (b) an active ripple canceling method involving a separate |    |

|      | ripple canceling (RC) converter and a much smaller capacitor $C_{RC}$             | 73 |

| 3.4  | Block diagram of the multilevel converter with power factor correction (PFC),     |    |

|      | ripple cancellation (RC), and output stage                                        | 74 |

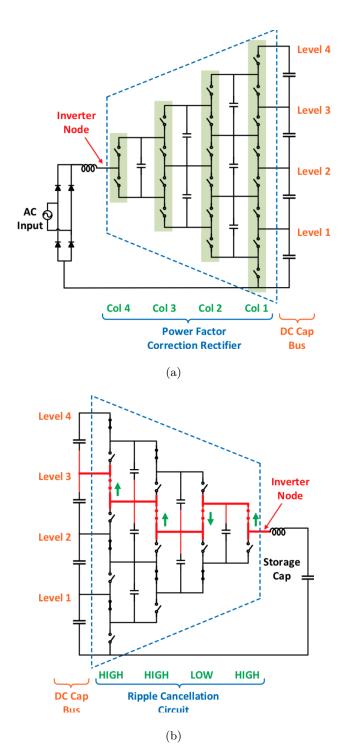

| 3.5  | Generalized multilevel schematic for the PFC rectifier and ripple cancella-       |    |

|      | tion module. The DC capacitor bus creates the DC levels, buffers power            |    |

|      | flow, and connects to the output stage (not shown here). (a) PFC with             |    |

|      | switching columns highlighted in green. (b) Ripple cancellation module with       |    |

|      | an example switch configuration for connecting the inverter node to level 3.      | 76 |

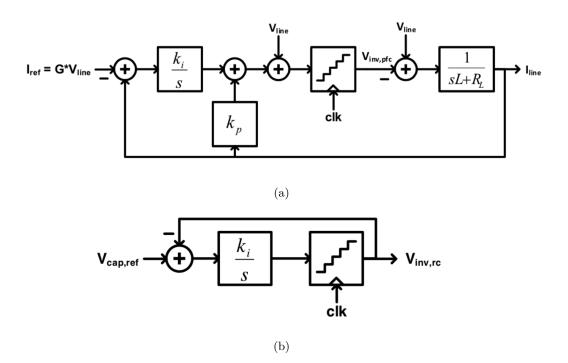

| 3.6  | The sigma delta control loops for the PFC rectifier and ripple cancellation             |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | module. Each loop has an integrator and a quantizer clocked at $400~\mathrm{kHz}$ . (a) |    |

|      | Second order sigma delta loop used for the PFC rectifier, where the second              |    |

|      | pole is obtained from the input inductor. The input current $I_{line}$ relates to       |    |

|      | the voltage across the inductor $V_{inv,pfc} - V_{line}$ . (b) First order sigma delta  |    |

|      | loop used for the ripple cancellation module. This module uses the sigma                |    |

|      | delta loop to set the inverter node of the ripple cancellation circuit $V_{inv,rc}$ to  |    |

|      | approximate a preprogrammed waveform $V_{cap,ref}$                                      | 78 |

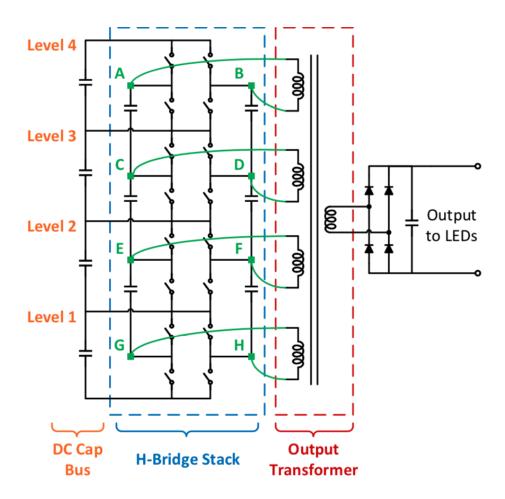

| 3.7  | The output stage is comprised of an integrated H-bridge stack and an output             |    |

|      | transformer                                                                             | 80 |

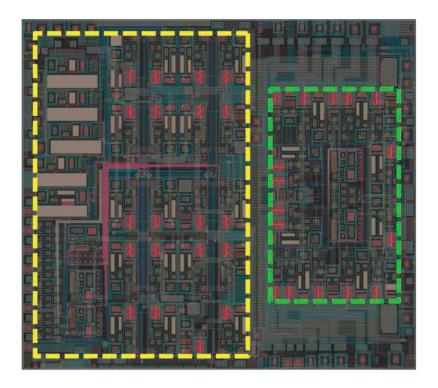

| 3.8  | The prototype IC layout with dimensions of 7.08mm X 6.28mm. The mul-                    |    |

|      | tilevel converter is on the left (yellow). The H-bridge stack is on the right           |    |

|      | (green)                                                                                 | 81 |

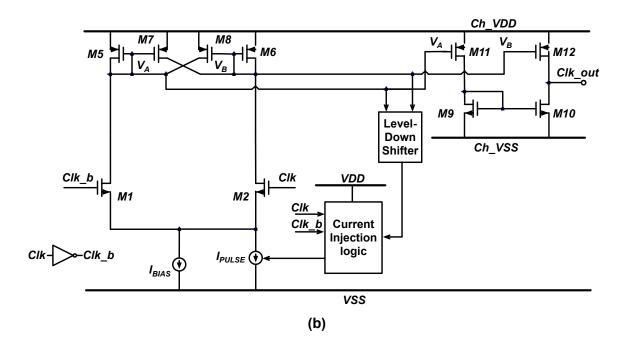

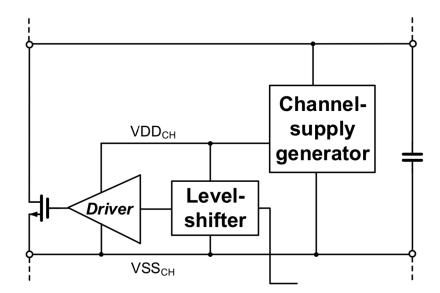

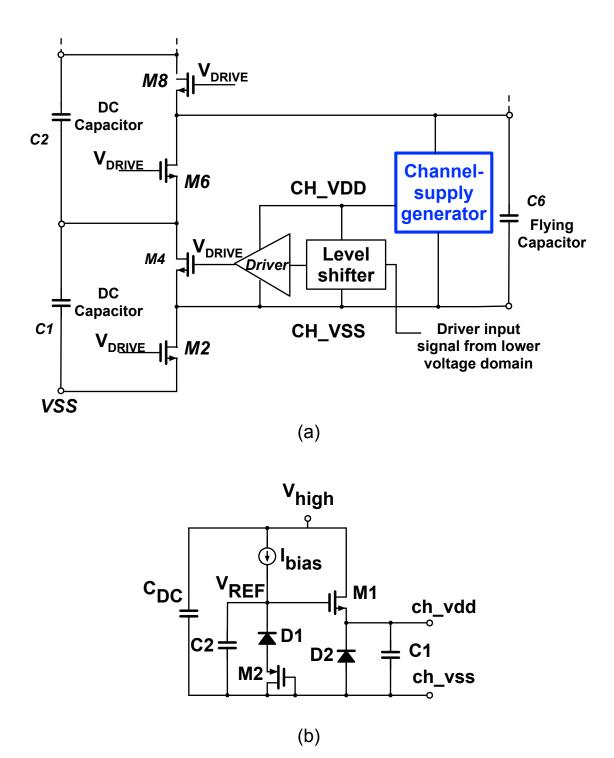

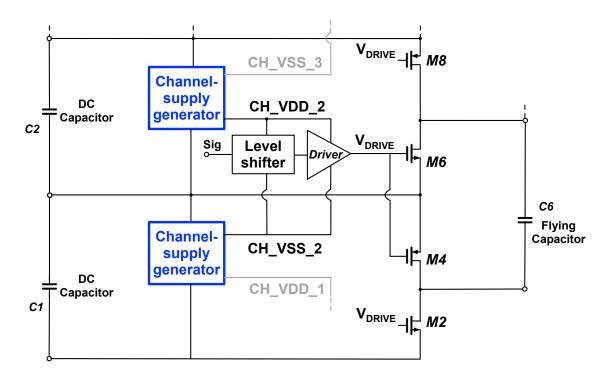

| 3.9  | Several devices in a switching column of the multilevel converter, with the             |    |

|      | full gate driving channel shown for the high power DMOS switch M2. Each                 |    |

|      | gate driving channel consists of a high-side channel supply, a level shifter,           |    |

|      | and a driver (inverter). The channel supply bootstraps off a flying capacitor           |    |

|      | and generates the CH_VDD voltage at 5V above CH_VSS                                     | 82 |

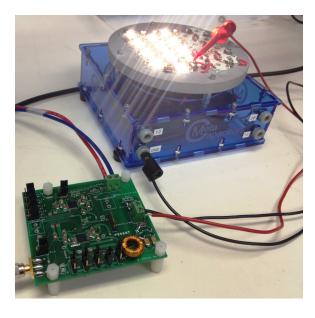

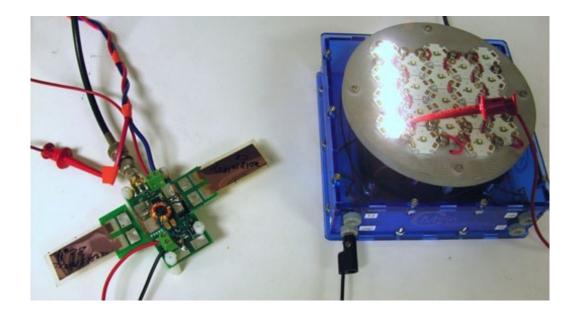

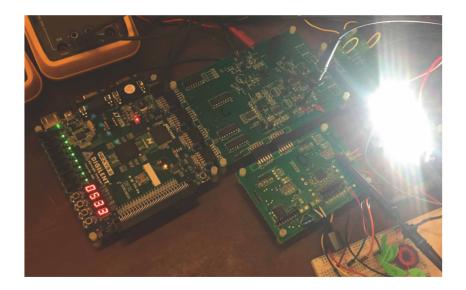

| 3.10 | Board and lab setup. The power board (lower left of the LEDs) contains two              |    |

|      | ICs, one for the PFC rectifier and one for the ripple cancellation module.              |    |

|      | The FPGA board (left) attaches to the control board (top center). All of the            |    |

|      | control logic can be integrated in CMOS on the IC                                       | 83 |

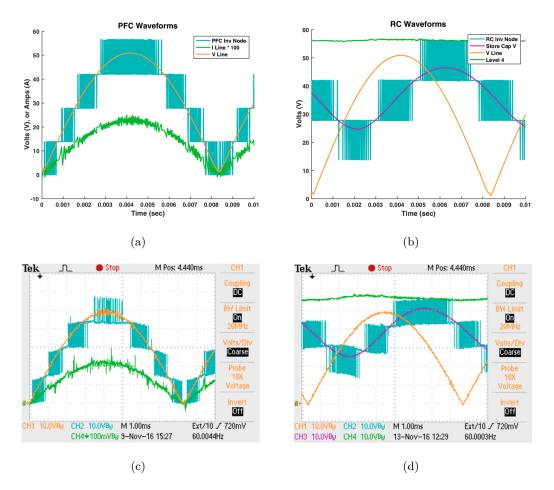

| 3.11 | Simulated and experimental waveforms that demonstrate the functionality             |            |

|------|-------------------------------------------------------------------------------------|------------|

|      | of the power factor correction (PFC) rectifier and ripple cancellation mod-         |            |

|      | ule. (a) Simulated PFC waveforms with the line voltage (yellow), line cur-          |            |

|      | rent (green), and the PFC rectifier inverter node of Fig. 3.5(a) (blue). The        |            |

|      | line current is scaled by 100 for visibility. (b) Simulated ripple cancellation     |            |

|      | module waveforms. Waveforms include the line voltage (yellow), the voltage          |            |

|      | at level 4 of the DC capacitor bus (green), the voltage across the storage          |            |

|      | capacitor (purple), and the ripple cancellation module inverter node from           |            |

|      | Fig. 3.5(b) (blue). (c) Experimental PFC rectifier waveforms from oscillo-          |            |

|      | scope. The line current (green) is measured as the voltage across a 1 ohm           |            |

|      | current sense resistor. (d) Experimental ripple cancellation module waveforms.      | 85         |

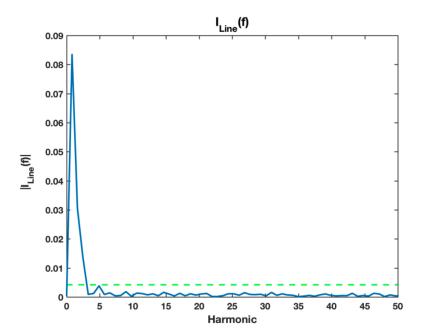

| 3.12 | FFT of the line current input $I_{Line}$ . Line current harmonics are all less than |            |

|      | 5% of the fundamental. Data is obtained at $V_{in,RMS}=36V$ and $I_{in,RMS}=$       |            |

|      | 68.5mA.                                                                             | 86         |

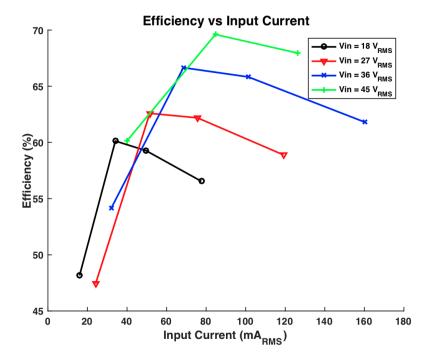

| 3.13 | Efficiency versus input current. The output voltage was set at the optimal          |            |

|      | value using an electronic load. In general, the output voltage and current is       |            |

|      | determined by the total voltage drop of the series LED string                       | 87         |

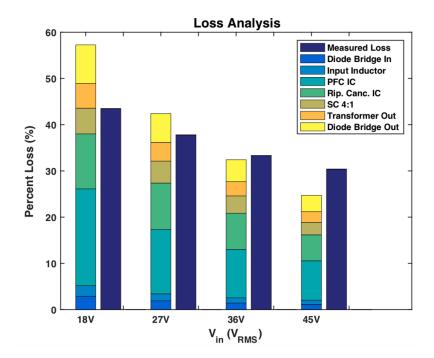

| 3.14 | Loss versus input voltage. The lower voltages each compare a loss model             |            |

|      | (left bar) to the actual measured loss (right dark blue bar). Unfortunately,        |            |

|      | measured loss data doesn't exist for the higher voltages, but the loss model        |            |

|      | can somewhat provide a projection of how the system would perform. The              |            |

|      | model and data correspond to operation at close to 80 mA input current. $$ .        | 88         |

| 4.1  | (a) Block diagram of the gate driver and (b) schematic of the channel-supply        |            |

| 1.1  | generator                                                                           | 93         |

| 4.2  | Block diagram of shared gate driving circuit for both NMOS and PMOS                 | <i>J</i> € |

| 1.4  | power transistors                                                                   | 94         |

|      | bonor arminions                                                                     | J          |

# List of Tables

| 1.1 | Glance at the history of artificial lighting                           | 8  |

|-----|------------------------------------------------------------------------|----|

| 1.2 | Advantages of LED lighting.                                            | 12 |

| 1.3 | Disadvantages of LED lighting                                          | 13 |

|     |                                                                        |    |

| 2.1 | Components Used in Prototype DC-DC converter for LED Driver            | 54 |

| 2.2 | Comparison to State-of-the-Art LED Driver Designs                      | 61 |

| 2.3 | Table showing comparative analysis of the Metacapacitor technology and |    |

|     | current technological alternatives                                     | 62 |

| 3.1 | Components used in the prototype LED driver                            | 84 |

# Acknowledgments

It was a long and challenging journey and luckily, with the accompany of many wise and warmhearted guides and fellows, I was able to sail to the end with extraordinary learning and growth. Before I continue on to my new stage of life, I would love to give my deepest thanks to the people that supported me through this endeavor.

Firstly I must thank my advisor Professor Peter Kinget for his guidance, help, and understanding though out my graduate study. His encourage and trust enabled me to overcome the most difficult times in my research. He is a great model to follow not only in academic but also in life. I also want to thank Professor Seth Sanders for all the inspiration, guidance, and discussion which are the key to the success of my research. I am also thankful to Professor Ioannis Kymissis, and Professor Stephen O'Brien for always being warm and supportive in my research.

A special thanks goes to my research partner Dr. Daniel Gerber, for all the days and nights we spent together to accomplish one milestone after another. It was a great time working with you and wish you a best future.

My research will not be possible without supports from Gianpaolo Lisi, Ali Djabbari, Raj Subramoniam, Glen Wells, Jianyi Wu, Zhenyong Zhang, and many fellows from Texas Instruments-silicon valley. It is a memorable and super happy time working with all of you in the beautiful campus of TI. May our friendship last forever.

Additional thanks goes to my colleagues in Columbia Integrated System Lab (CISL). Your advice and support are invaluable to my research and life in Columbia. I will always remember the pleasant time we spent together in the campus.

Finally I would like to thank my families for your unconditional love and trust. Without them I would have never been able to reach this far in my life. Deepest thank to all of you for your effort to support me. To my lovely wife Bining and our little angle Claire

To my beloved parents Weihong and Yesheng

For their selfless love, trust, and support through my life

# Chapter 1

# Introduction

Power conversion is the process of converting electric energy from one form to another. The goal of modern electronic power converters is to provide highly efficient and reliable power processing with minimum component size and cost. Numerous power converter topologies have been developed for a wide range of applications and power levels. One emerging and important application of high efficiency power converters is in the solid-state lighting market.

Light-emitting diodes (LEDs) have been available for many years since the first LED is created by the Soviet inventor Oleg Losev in 1927 [1]. Although the light output per package and cost of the LEDs have been improved exponentially as described by Haitz's Law during the last few decades, it is not until recently that LEDs are finally on the verge of having the capability to radically alter the entire lighting landscape. The LEDs has shown great promise as an efficient, environmentally friendly, and affordable alternative to incandescent and fluorescent lights. Engineering-economic analysis suggests LED is more cost-effective due to its high luminous efficacy and long life span, which significantly saves electric energy and reduces replacement cost. As yellow/amber, green and finally blue colored LEDs became available, the applications of LEDs have exploded. Given their small form factors, LED bulb can be combined in many shapes to provide various lighting effects.

Since an LED is a current driven device whose light emission intensity is proportional to its forward conduction current, LED drivers are necessary to provide current regulation under different input and load conditions. The core of a LED driver is the power converter, which is expected to have characteristics such as high conversion efficiency, wide input/output adaption range, low component cost, wide dimming range, low electromagnetic interference (EMI), and enough safety protection. Chapter 1.1 will provide a brief introduction of the fundamentals of light, human vision, flicker, and lighting history. Chapter 1.2 will cover the basics of LED devices. Chapter 1.3 will discuss the performance requirements of modern LED drivers for general lighting applications. A few widely used power converter topologies for LED driver will be introduced with their advantages and disadvantages analyzed. Chapter 1.4 will discuss the challenges in the integration of power converters. Chapter 1.5 will introduce the organization of the whole thesis.

# 1.1 Fundamental of Lighting

## 1.1.1 Light Basics

As we know, light is electromagnetic radiation within a certain portion of the spectrum, which has both wave and particle nature, which is known as the wave-particle duality. In propagation, light act as waves. However, the energy transmitted by the wave can be absorbed as a particle, which is called a photon, at a single location. The word photon is used to represent the quanta of light. The absorption of light can be viewed as an instant collapse of the light-wave energy to a single location, which is called the wave function collapse. The energy of a photon can be related to the wavelength of light as:

$$E = hf = \frac{hc}{\lambda},\tag{1.1}$$

where E is the energy in joules, h is Planck's constant, f is the frequency of light in Hz, c is the speed of light, and  $\lambda$  is the wavelength of light in meters.

The main characteristics of light includes intensity, propagation direction, and frequency spectrum. The visible light is usually defined as having wavelength in the range of 400 to 700 nanometers, which corresponds with the frequency range of roughly 430 to 750 terahertz. Like other forms of waves, light exhibits properties such as polarization, superposition, reflection, refraction, diffraction, and interference. The speed of light in vacuum is constant, which approximately equals to  $2.998 \times 10^8$ .

#### 1.1.2 Human Vision

The lighting technology serves human vision. The human vision characteristics determine the requirements of lighting. The human vision system is part of the central nervous system that enables people to interpret the surrounding environment using light in the visible spectrum. Specific wavelengths of light within the spectrum correspond to particular colors based on human perception of light. The long-wavelength side of the spectrum is perceived by human to be red, whereas the short-wavelength end pertains to violet light. Bounded between these two ends, lyes other colors, e.g. orange, yellow, green, and blue. The human vision is not only referring to the light reception process in which human eyes receive light and transform it into electrical neuron signals, but also a series of complex visual processing tasks such as the identification of objects and distance assessment. It all starts from the cornea, pupil, and lens of eye refracting light into a small area and project it onto the retina at the back of the eye ball. The photoreceptor cells, which are called rods and cones, on the retina then transduces the signal into electrical neural impulse. The rods, which concentrated at the outer edges of the retina, functions in lower light intensity conditions and peripheral vision, known as scotopic vision. Being more sensitive to luminance, the rods are the key of night vision, while having little contribution to color vision. The cones (photopic vision), to the contrary, function best in bright light and has different response to light of different frequency, thus is responsible for color vision. The cones contain one of the three types of pigments and are accordingly designated as L-type or long-wavelength cones, M-type or middle-wavelength cones, and S-type or short-wavelength cones. Therefore, they are able to distinguish among the different colors.

The science of the measurement of light, in terms of its perceived brightness to the human eye, is called Photometry. It is different from the measurement of absolute radiation energy, because human eye is not equally sensitive to all wavelengths of visible light. Photometry calculates the perceived light by weighing the measured energy of each wavelength with a factor representing the human-eye sensitivity at that wavelength. The factor is called the luminosity function. The relevant quantity is designated as luminous energy. There are several other measurements and units that are widely used in photometry. The luminous flux with unit lumen is luminous energy per unit time. The luminous intensity with unit

candela (cd) is the luminous flux per unit solid angle. The luminance with unit  $cd/m^2$  or nit is luminous flux per unit solid angle per unit projected source area.

#### 1.1.3 Luminance Flicker

Luminance flicker is a rapid and repeated change over time in the brightness of light. The cause of luminance flicker includes light source fluctuations, power supply ripples, or pulse width density modulation (PWM) of light source driver. Various studies have assessed the potential health, performance and safety-related impacts of temporal light flicker [2], [3], [4]. Studies show that flicker at certain frequencies may induce biological human response thus LED lamp driver designers needs to find mitigations. Adverse effects of flicker include annoyance, reduced task performance, visual fatigue, headache and epileptic attack by photosensitive persons. The luminance flicker that is consciously perceivable by a human viewer is called visible flicker, while invisible flicker cannot be consciously perceived by a human viewer.

Human visual sensitivity to variation of luminance over time is defined by the temporal contrast sensitivity function (TCSF). This function describes visual sensitivity as a function of temporal frequency of luminance modulation [5]. The TCSF falls rapidly at high temporal frequencies, reaching a minimum of 1 at the Critical Fusion Frequency (CFF). The CFF of flicker is defined as the frequency at which an intermittent light stimulus appears to be completely steady to the average human observer and is related to persistence of vision. The TCSF as a function of flicker frequency spectrum is affected by the following parameters:

- 1. The average luminance intensity;

- 2. The position and area on the retina where the stimulation occurs;

- 3. The wavelength of stimulus light;

- 4. The degree of light or dark adaptation;

- 5. Physiology conditions such as age and fatigue;

- 6. Person to person variation.

To estimate the flicker intensity observed by human eye, we can calculate the frequency spectrum of the received luminance at every spacial location on human retina, and multiply with the TCSF with corresponding parameters, then integrate the resulted spectrum energy.

The resulted spacial flicker intensity across the retina can then be weighted and summed together based on the retina spacial sensitivity of flicker. If the resulted overall flicker intensity is below certain threshold, the person cannot observe flicker.

It is reported visible flicker at frequencies within the range 3-70Hz could cause risks of seizures. In addition, a few studies suggests invisible flicker at frequencies below 165Hz could have possible human biological effects including headaches and eye-strain [2]. Thus artificial light source designers needs to be aware and reduce luminance flickering in the frequency ranges of interest.

## 1.1.4 History of Artificial Lighting

Besides natural light source such as sunlight and moonlight, primitive human craved for artificial light source to stay away from darkness. Through out the history of human, several sources of light have been developed as the technology advances. The earliest artificial light starts from the control of fire, discovered approximately  $5 \times 10^5$  years ago such as campfires and torches. The next break-through came about  $3 \times 10^4$  to  $7 \times 10^4$  years ago when people started burning a fiber immersed in molten fat. Later many different kinds of oil were used for this purpose including oil produced from plants, animals (e.g. whale oil), and mineral. A major reduction in the cost of lighting occurred after Abraham Gesner, a Canadian geologist, first refined kerosene in the 1840s. Then came the discovery of crude oil in 1859, and the petroleum industry arose. Around the 1880s another major drop of cost of lighting came with the introduction of electrical lighting in the form of arc lights for large space and street lighting followed by incandescent light bulb for general purpose lighting.

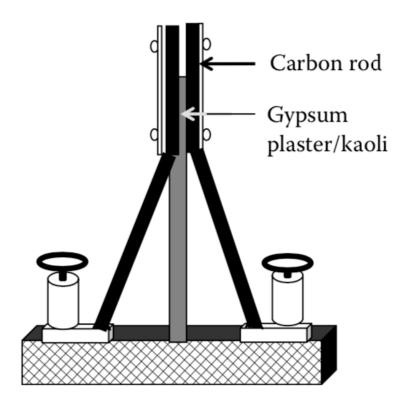

In particular, the first solid-state light device was invented by T. Drummond in 1826 [6]. The device was not electrical and consisted of a calcium oxide cylinder with an oxyhydrogen blowpipe producing a bright flame. This brilliant limelight was used in the theaters. The first practical electrical lighting device was demonstrated in 1876 by a Russian telegraph engineer. It is consisted of two Carbon rods separated by a thin layer of gypsum plaster and was called Jablochkoff's candle as shown in Fig. 1.1. It is the pioneer of modern electrical arc lamp aroused public interest. Later a series of inventors, including Thomas Alve Edison, an American researcher and businessman, and Joseph Wilson Swan, a British

chemist, electrical engineer, and inventor, improved and commercialized the incandescent filament lamp in 1879 [7]. Incandescent bulb works by heating a wire filament to a high temperature such that it glows visible light. The filament is protected from oxidation with a bulb that is filled with inert gas or a vacuum. It was an important milestone of lighting technology enabling humanity to produce long lasting light with extreme low cost. The subsequent lighting devices are vapor lamps. The first mercury vapor lamp to achieve widespread success was invented in 1901 by American engineer Peter Cooper Hewitt. It is a gas discharge lamp that uses an electric arc through vaporized mercury to produce light. The fluorescent lamp is a low-pressure mercury-vapor gas-discharge lamp that uses fluorescence to produce visible light. The mercury vapor lamp and fluorescent lamp converts electrical energy into useful light much more efficiently than incandescent lamps. The typical luminous efficacy of fluorescent lighting system is 50-100 lumens per watt, several times the efficacy of incandescent bulbs with comparable light output. The other advantages are their long life time in the range of 24,00 hours and a high intensity, clear white light output.

A technology revolution of lighting has taken place since the discovery of LED. It has many advantages over incandescent light sources, including lower energy consumption, longer lifetime, improved physical robustness, smaller size, and faster switching. The electro-luminescence phenomenon was discovered in 1907 by the British experimenter H. J. Round of Marconi Labs, and Russian inventor Oleg Losev reported creation of the first LED in 1927. The first visible-spectrum (red) LED was developed in 1962 by Nick Holonyak, Jr. while working at General Electric. The first high-brightness blue LED was demonstrated by Shuji Nakamura of Nichia Corporation in 1994. Table 1.1 shows a brief glance of the history of artificial lighting.

Figure 1.1: Jablochkoff candle.

| No. | Event                                                    | Year                                    |

|-----|----------------------------------------------------------|-----------------------------------------|

| 1.  | Fire torch                                               | $5 \times 10^5$ years ago               |

| 2.  | Wick lamp                                                | $3\times 10^4 - 3\times 10^4$ years ago |

| 3.  | Oil pottery lamp                                         | 600 BC                                  |

| 4.  | Oil reservoir lamp                                       | 500 BC                                  |

| 5.  | Beeswax candle                                           | 400 BC                                  |

| 6.  | Gas lighting                                             | 1772 AD                                 |

| 7.  | Argand oil lamp                                          | 1784 AD                                 |

| 8.  | First solid-state lighting device (limelight)            | 1826 AD                                 |

| 9.  | First solid-state lighting device (Jablochkoff's candle) | 1876 AD                                 |

| 10. | Incandescent filament lamp                               | 1879 AD                                 |

| 11. | Mercury vapor lamp                                       | 1901 AD                                 |

| 12. | Low-pressure sodium vapor lamp                           | 1919 AD                                 |

| 13. | Fluorescent tube                                         | 1927 AD                                 |

| 14. | First WLED                                               | 1994 AD                                 |

Table 1.1: Glance at the history of artificial lighting.

# 1.2 LED-Based Lighting

### 1.2.1 Characteristics of LEDs

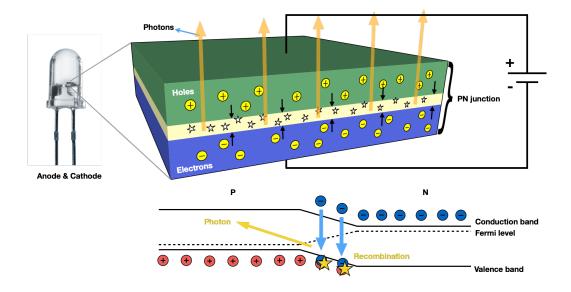

As depicted in Fig. 1.2, an LED is a two-lead semiconductor light source made from a P-N junction diode. The PN junctions are created by doping impurities e.g. indium, gallium and nitrogen to silicon carbide. Once a forward voltage is applied across the LED, electrons jump to the conduction band, resulting in a forward current flow. When an electron loses energy and falls back to the valence band, energy is released in the form of a photon. The wavelength of the light emitted, and thus its color, depends on the band gap energy of the material forming the p-n junction. The materials used for the LED have a direct band gap with energies corresponding to near-infrared, visible, or near-ultraviolet light. LED development began with infrared and red devices made with gallium arsenide. Advances in materials science have enabled making devices with shorter wavelengths, emitting light in a variety of colors.

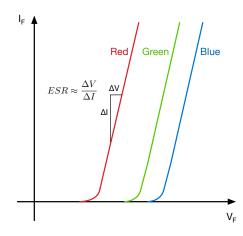

The typical I-V characteristic curves versus different colors of LED devices are depicted in Fig. 1.3. Once the forward bias voltage  $(V_F)$  of a LED passes the turn-on threshold, its forward current  $(I_F)$  increases almost exponentially, then the slope of the I-V curve gradually reduces and eventually the curve becomes linear. This linear region can be modeled by the equivalent series resistance (ESR), which dominates when the forward current is large. Since the ESR is typically designed to be as small as possible to improve power efficiency, a small change in voltage across the LED results in a large variation in the current. In other words, an LED can often be thought of as a constant voltage load. The exact forward voltage drop depends on the exact LED material, manufacturer process, color, aging condition, and environment impacts such as temperature.

LED's efficacy decreases as the driving current increases. This was initially thought to be related to temperature increase but proved to be wrong by later studies. The elevated temperature actually improves LED's efficacy. The true cause of efficiency droop of LED was identified in 2007 as Auger recombination [8]. However, higher temperature can shorten LED's lifetime, by causing light reduction and accelerated chip degradation such as defects. High-brightness LEDs often operate at 350 mA, which is a compromise between light output,

Figure 1.2: LED device structure and operation physics.

Figure 1.3: Example I-V curves of red, green, and blue LED devices.

efficiency, and longevity.

Given the thermal impact on LED's efficiency and lifespan, the heat dissipation performance of LED light bulbs are crucial for many applications. One efficient way to dissipate heat is by attaching a heat sink with large surface area. In the case of household lighting, the good news is that the LED light bulb is often designed to have the same size of the traditional incandescent bulb, ,thus making large heat sink a practical and economical solution. Advanced LED drivers should be able to compensate for the temperature impacts to LED luminance. Such function would require a temperature sensor, larger tuning capability of the LED driver and a digital compensation loop.

## 1.2.2 Application of LEDs in Lighting

The commercial use of LEDs started in the late 1960s. The early LEDs were first used as colored indicator lights in electronic devices. Starting with the introduction of the first transparent-substrate AlGaAs LEDs in the 1980s, hight-luminance LEDs are moving into all applications related to artificial lighting. LED lamps have a lifespan many times longer than equivalent incandescent lamps and significantly more than most fluorescent lamps. The most efficient available LED lamps have efficiencies of 200 lumens per watt [9]. The LED lamp market is projected to grow by more than 12% from \$2 billion in 2014 to \$25 billion in 2023.

Table 1.2 and 1.3 summarizes the pros and cons of LED lighting vs. the traditional methods.

| Advantages |

|------------|

|------------|

- 1. Efficiency LED has higher efficacy than incandescent/florescent lights. The efficiency of LED lighting fixtures are not affected by shape or size. 2. Lifetime One report estimates 35,000 to 50,000 hours of useful life, though time to complete failure may be shorter or longer [10]. Fluorescent tubes typically are rated at about 10,000 to 25,000 hours 3. Size LEDs can be very small, including mini and micro LEDs for display, and are easily attached to printed circuit boards. Response time LEDs can have microseconds of response time and are ideal for high-frequency on-off cycling. 5. Color LEDs can emit light with intended color without color filters as traditional lighting methods need. It is more efficient. Dimming LEDs are ideal for PWM dimming or lowering the forward current. 6. 7. Durability Being solid-state device, LEDs are very durable physically com-

- 8. Directional light The LED lighting is directional which are preferable for certain applications.

pared with fragile incandescent or fluorescent bulbs.

Table 1.2: Advantages of LED lighting.

#### Disadvantages

. Temperature dependence LED performance highly depends on the temperature of the operation environment and thermal management properties.

2. LED driver complexity LEDs are very sensitive to driving voltage. Current and lifetime change greatly with a small voltage delta. Thus LED drivers require current regulation and temperature compensation.

3. Color rendition Most cool-white LED have spectra that differ significantly from a black body radiator. This can make object color look differently under LED illumination.

4. Area light source Single LED doesn't approximate a point source of light giving a spherical light distribution, but rather a lambertian distribution. Thus LEDs need optic lenses or fixtures to provide spherical light field.

Table 1.3: Disadvantages of LED lighting.

## 1.3 Introduction of LED Driver

#### 1.3.1 The Fundamentals of LED Drivers

The concept of LED driver comes from the need to regulate the current through LEDs to achieve high efficiency operation and deliver the right amount of light. The architecture of an LED driver is determined by the characteristics of input power source, output load, available passive and active components, and application-specific requirements.

The LED driver is essentially a power converter. Today, the domestic mains electric power is delivered by an alternative AC voltage source with 50~Hz to 60~Hz frequency. Thus off-line LED drivers needs to convert electric power from a AC voltage source to a DC current through the LEDs. a typical off-line LED driver is required to have both rectification and voltage conversion function with good power efficiency.

The basic LED performance requirements are summarized and listed below.

#### 1.3.1.1 Current Regulation

One of the basic functions of the LED drivers is current regulation. This maintains a desired LED current flow given input voltage and current fluctuation, temperature change, or component performance shift over time. As mentioned in Section 1.2.1, LED luminance is almost proportional to the current passing through and behaves similar to a constant voltage load. Thus by nature, current regulation is advantageous in LED light control over voltage regulation. Applications like LED dimming and color control of LED bulbs [11] as shown in Fig. 1.4 also requires accurate current control with LED drivers.

### 1.3.1.2 Power Efficiency

The U.S. Energy Information Administration (EIA) estimates that in 2018, the U.S. residential sector and the commercial sector used about 232 billion kilowatthours (kWh) of electricity for lighting, which was 6% of total U.S. electricity consumption. One percent of lighting power efficiency improvement means billions of kWh of electricity energy saving. As LED light market is growing rapidly, the power efficiency of LED drivers become more and more critical. In practice, the power efficiency often needs to be traded-off with other

Figure 1.4: Example of commercial LED light bulb with smart color control.

design considerations such as component size, cost, and input/output conditions. LED driver circuit topology, design technique, and component performance are crucial in terms of efficiency optimization.

### 1.3.1.3 Input and Output Range

For off-line LED drivers, the input voltage and frequency varies among different regions of the world. A voltage of (nominally) 230 V and a frequency of 50 Hz is used by most of the world population, including people in Europe, most of Africa, most of Asia, much of South America and Australia. In North America, the most common combination is 120 V and a frequency of 60 Hz. Other voltages exist, and some countries may have, for example, 230 V but 60 Hz. A wide input voltage and frequency range design can benefit LED driver providers to lower design and manufacture cost by covering more regions with the same product.

The output load specifications could also have large variation due to the various LED applications. If LEDs are connected in series the output voltage and power of LED driver is proportional to the number of LED in a string. LED dimming and color control also require output power to be controllable. It is desirable to maintain high power efficiency

and low cost across wide input and output configurations of LED driver. However, it is very challenging to meet this requirement with fixed circuit design parameters and components. Thus re-configurable LED driver could be an optimized solution.

### 1.3.1.4 Power Factor Correction

For the AC main power distribution system, the power factor, which is the ratio of the real power absorbed by the load to the apparent power flowing in the power rails, is required to be above certain levels e.g. 0.9 to improve energy efficiency and reduce power generation and transmittance cost. For example if the load power factor were 0.7, the apparent power would be 1.4 times the real power used by the load. Thus power-factor correction (PFC) technique, which increases the power factor of a load by adding passive or active network of capacitors or inductors, has been widely applied in power substations, distribution networks, and power-consuming devices. The PFC feature is also required for modern LED drivers in the world's main lighting markets.

### 1.3.1.5 Flicker

The LED luminance flicker performance is another important design specification of LED drivers. Flicker is defined as variations of luminance in time [12]. Previous reports suggest both visible and invisible flicker have potential adverse biological effects on human health [13]. Thus it is critical for LED driver designers to consider the light modulation scheme. However, it is very challenging for an electrical light source to maintain constant luminance, given the power main source is typically AC (i.e., 60Hz AC in North America). Thus special power main harmonic energy reduction technique needs to be applied for LED drivers. The human sensitivity to flicker, reported health impact, and driver voltage ripple cancellation circuits will be discussed in more details in Part 3.

## 1.3.1.6 Safety

Beyond normal electrical safety requirements, some LED drivers provides galvanic isolation between the high voltage AC input and the low voltage DC output to the LED string. Galvanic isolation prevents direct conduction path between functional sections of electrical systems thus protects the users from electric shock by accidents. The isolation also prevents any disturbance on the primary side of the driver circuit from passing onto the output side. Thus the LEDs are protected against transients and surges occurring on the primary side.

Various electrical safety standards also specify the isolation requirements on the touch current and protective conductor current. Touch current is the current that flows when a human body touches the equipment. Protective conductor current is the current appearing in a protective conductor, such as leakage current or electric current resulting from an insulation fault.

## 1.3.2 Types of LED Drivers

There are many circuits that can provide a relative constant current through the LEDs and thus serves as a LED driver. However, in order to meet the performance requirements and standards discussed in Section 1.3.1, the LED driver circuits needs to be carefully designed and optimized. A few widely used design of LED drivers are introduced below:

### 1.3.2.1 Linear LED Driver

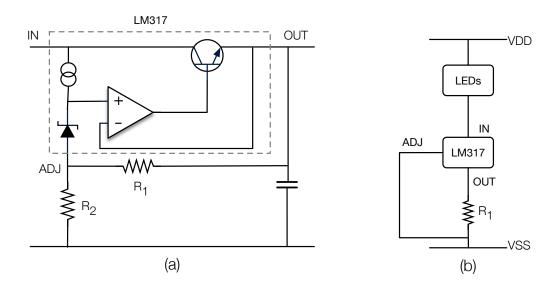

One of the simplest ways to drive LEDs is through a linear LED driver. It is preferred for a few reasons. One of them is its simplicity which leads to a lower cost for manufacturers. Another important engineer concern is the obscene of electromagnetic interference (EMI). The EMI specifications could require extra shielding or filtering which adds to the cost. However, the disadvantages are also obvious. The linear power converters usually have lower power efficiency which become worse with a wide output range. For off-line LED drivers, the efficiency would be extremely low for linear regulators since the mains voltage is high and with 50Hz to 60Hz ripple. In addition, the introduced thermal issue by low efficiency could lead to bulkier heat dissipation solution which is problematic for certain applications. Fig. 1.5 shows a linear voltage regulator and a constant current regulator using Op-Amps.

Figure 1.5: Example of (a) linear voltage regulator using an Op-Amp (LM317) and (b) linear current regulator as LED driver.

#### 1.3.2.2 Switched-Mode LED Driver

A switched-mode LED driver incorporates a switching regulator to convert electric power efficiently and driver LEDs. The two key ideas of the switched-mode regulator are switching and filtering. The switching operation is important so that the across a wide input/output range the regulator circuit only operates at high-efficiency full-on and full-off states while reducing the time of the transitions between the two states when power efficiency is low. If the transition time is reduced to zero then ideally the switched-mode power regulator consumes no power. However, the switching operation generates electromagnetic signal at the switching frequency and thus power filters, usually low-pass filters, are required for most applications to filter out the EMI signals. Usually only passive filters are applied to power converters, since passive filters scale better to large signals and consume little power. For low-pass passive filter, the higher the switching frequency, the smaller and lighter the reactive components and thus the less cost and space is required. In addition, increasing operating frequencies improves the dynamic characteristics of converters. The bandwidth of a control loop is often determined by the characteristics of the output filter. Thus high operating frequencies can allow converters to achieve faster dynamic response, for example,

to rapid changes in the load current and/or the input voltage. In LED driver design, such benefits from higher switching frequency need to be traded-off with the increased switching power and device bandwidth limit. Another important factor that designers need to take into consideration is the device power rating limits. A lot of time the designer needs to trade-off other device performance to withstand the required power ratings.

#### 1.3.2.3 Inductor Based LED Driver

Inductor based switched-mode LED drivers are widely applied in the lighting industry. The most common switched-mode regulators topologies include buck, boost, buck-boost, and flyback converters. Fig. 1.6 shows the basic schematics of the buck, boost and buck-boost power converters. They all utilize single inductor as energy storage elements. Take the boost converter as an example, the inductor stores energy by transforming electric potential energy into magnetic potential energy when the power switch is turned on and is then used to supply current by transforming magnetic potential energy into magnetic energy when the power switch is off. The power diode guarantees that the power flow is single direction and will not bounce between the source and load causing extra energy loss.

The buck, boost, and buck–boost topologies are all strongly related. Input, output and ground are connected through three loops. Two of the three passes through an inductor, while the other one passes through only switches. One of the two switches must be active such as a transistor, while the other one can be a diode.

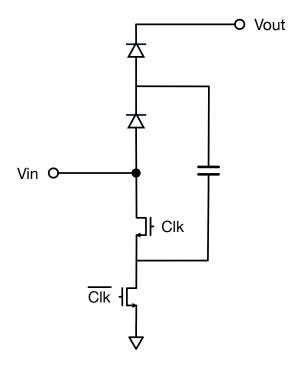

The flyback converter is shown in Fig. 1.7, which is essentially a buck-boost converter with the inductor split to form a transformer, providing the advantage of galvanic isolation. The operation principle of the flyback converter is very similar to the buck-boost converter, with the difference that the magnetic energy is now stored in the transformer. Another advantage of transformer based power converter is that the converter can easily supply multiple outputs by making small circuitry modifications. The drawback of transformers is their large size.

Figure 1.6: Basic schematics of (a) a boost converter, (b) a buck converter, and (c) a buck-boost converter.

Figure 1.7: Basic schematic of a flyback converter.

## 1.3.2.4 Switched-Capacitor Power Converter

Switched-capacitor (SC) circuits utilizing capacitors and switches to transfer charge and regulate voltage or current. The SC converters can achieve high power efficiency (>90%) and are more friendly to integration compared with inductor or transformer based power converters.

One of the intrinsic advantage of SC converts is that existing capacitors have significantly higher energy density than inductors [14]. The energy density of surface mounted capacitors can easily achieve 1000 times of the shielded inductors. This can lead to significant Printed Circuit Board (PCB) area and cost reduction in electrical products.

The second intrinsic advantage of SC converter is that the voltage rating of the passive and active circuit components can be significantly reduced to only a small portion of the overall voltage rating of the converter. Fig. 1.8 shows a simple voltage doubler based on switched capacitor topology. There are 5 circuit elements in this schematic, and a non-overlapping clock signal controls the two switches. One can analyze and find that the voltage rating of all 5 elements are all below  $\frac{V_{OUT}}{2}$ , in which  $V_{OUT}$  is the overall voltage rating of the converter. By relaxing the voltage rating requirements, the other characteristics of the components can be significantly improved, such as size, cost, energy density, frequency bandwidth, and non-ideal parasitics. The end result of such improvements on overall converter performance can be dramatic. The lowered voltage ratings of electronic components also makes integration solution more viable.

Figure 1.8: Basic schematic of a voltage doubler.

One limitation of traditional SC converters is that the voltage conversion ratio needs to be integer number, fractionally multiply or scale voltages (such as 3/2, 4/3, 2/3, etc.) when highest efficiency can be achieved. Otherwise the efficiency drops linearly like linear regulator. In certain topologies other voltage ratios can be generated by alternating between modes frequently, at the cost of topology and control complexity, which also impacts the robustness and cost of products.

#### 1.3.2.5 Resonant Converter based LED Driver

As described above, switched mode power converters or LED drivers are widely used in various applications. However, the rectangular voltage and current waveforms cause turnon and turn-off energy loss from circuit parasitics which limits the operating frequency and

thus its benefits to the converter designs. For example, the reactive component size cannot

be further reduced with limited switching frequencies. The rectangular voltage and current

waveforms also generate broad-band electromagnetic energy and can pose a higher risk to

the EMI issues. In order to allow converters to operate at higher frequencies, topologies that

shape either a sinusoidal current or voltage waveform have been developed by engineers to reduce switching losses. The fundamental idea of resonant converters is to utilize a resonant tank with sufficiently high quality factor to store and transfer charge. A common method to achieve loss and EMI reduction in resonant converters is the soft-switching technique, which means operating the switches or diodes under zero-voltage switching (ZVS) or zero-current switching (ZCS) conditions. The resonant LED driver consists of a high-frequency resonant DC-AC inverter and a high-frequency rectifier. The low frequency or DC input power is first converted into high frequency AC power by the inverter, then converted back to DC output power by the rectifier. Galvanic isolation can be achieved in the AC phase by inserting isolation transformers or capacitors.

# 1.4 Integration of Power Converters

The global Power Management IC market is expected reach 38.4 billion US dollars by the year 2023, reflecting a coefficient of annual growth rate (CAGR) of 8.8% during the forecast period (2018-2023). Integration in power systems plays an essential role in achieving higher power efficiency, reducing product size and cost, improving reliability and EMI performance, as well as realizing various innovative features to meet the customer's need. Power ICs are widely used in applications such as switch-mode power supplies, electric motors, displays, lighting and telecommunication.

The most common power ICs are known as bipolar CMOS DMOS (BCDs), which combines the strengths of three different process technologies in a single IC: Bipolar for precise analog functions, Complementary Metal Oxide Semiconductor (CMOS) for digital design and Double Diffused Metal Oxide Semiconductor (DMOS) for high power and high-voltage devices. BCD technology can employ vertical and/or lateral power devices. The lateral BCDs have laterally-DMOS (LDMOS) devices or insulated gate bipolar transistor (LIGBT) as the power device, whereas the vertical BCDs are based on quasi-vertical DMOSs or IGBTs.

Other than BCDs, other technologies such as trench and silicon on insulator (SOI) also play increasingly more significant roles in power ICs [15]. The use of SOI technology

allows a higher device density and better vertical and lateral isolation. It can suppress the latch-up, offers considerably reduced cross-talk, decrease leakage current by two to three orders of magnitude, and allows for the integration of bipolar devices and body diode of LDMOSs. On the other hand, the trench technology can improve the current capability and cut dramatically the on-state resistance of the power device.

The performance specs for integrated high voltage and high power devices includes higher breakdown voltage, lower on-resistance, wider bandwidth and smaller size. These performance requests need to be traded-off against each other in most designs. In order to provide the optimized performance for different applications most power IC process provide a range of power device selections.

# 1.5 Thesis Organization

The thesis is organized as follows. In chapter 2, a hybrid switched-capacitor-resonant (HSCR) LED driver based on a stackable switched-capacitor (SC) DC-DC converter IC is introduced to demonstrate the idea of combining SC converter with resonant converter and capacitive isolation to replace the bulky transformers in traditional LED driver designs and improve the LED driver performance allowing higher efficiency, wider input and output range, and smaller component size. In chapter 3, the LED driver issues of power factor correction (PFC) and luminance flicker reduction is further addressed and the AC-DC rectifier front end for the HSCR DC-DC LED driver is discussed. To demonstrate the proposed solution, a highly integrated LED driver based on multilevel converters with sigma delta modulation is introduced and analyzed. In chapter 4, the conclusion of this thesis is made, and some possible work to extend the study of the topics in this thesis are proposed.

# Chapter 2

# Hybrid-Switched-Capacitor-Resonant DC-DC Converter Design

# 2.1 Introduction

Since an LED is a current driven device whose light emission intensity is proportional to its forward conduction current, LED drivers are necessary to provide current regulation over a range of input and load conditions. A simple way to drive LEDs is to use a linear regulator. Compared to other topologies, linear regulators are often smaller in size without bulky magnetics, easier to design, and they emit little electromagnetic interference (EMI). However, the efficiency of linear regulators is inversely proportional to the conversion ratio and thus too low for most applications requiring high energy efficiency. Fig. 2.1(a) shows a linear LED driver that efficiently performs current regulation and power factor correction (PFC) by alternating the average load impedance with switches and multi-channel LED strings [16]. Disadvantages of such a topology include difficulties in performing LED dimming and adapting to applications with various input or output specifications. Switched-mode LED drivers can achieve much higher power transfer efficiency than linear regulators by using passive energy storage devices and keeping the switch transistors in full-on and full-off states

most of the time. The buck-based LED driver, as shown in Fig. 2.1(b), is a widely used topology that can achieve higher efficiency (> 90%) and handle a wide range of input and loading conditions with a simple architecture. In [17], with a 5.5 mH inductor and a peak current controlled PWM method the driver achieves > 80% efficiency and > 0.9 power factor with large input and LED load variations. Despite its simple topology and good performance, the buck-based driver is not isolated from the AC mains, which can be a safety hazard in certain applications. In addition, the 5.5 mH inductor is large in size. To provide galvanic isolation, the most common solution is to use transformers. Fig. 2.1(c) shows the flyback converter based LED driver which is popular in low to moderate power applications [18]. The major drawback of the transformer-based LED driver is relatively large size and high cost due to the transformer, whose power handling capability is related to its volume. One example of commercial flyback LED driver is shown in Fig. 2.2 [19], where the magnetic transformer takes up significant space on board and cost around 2 dollars.

Switched-capacitor (SC) DC/DC converters provide another solution for high performance and highly integrated LED drivers. In comparison to magnetic-based converters, the SC topologies have a few fundamental advantages. As concluded in [20], any DC/DC converter must have at least two time-varying and/or nonlinear resistors (e.g. switches) and one reactance. The effectiveness of utilizing these two kinds of basic elements in a power converter decides its intrinsic performance-to-cost ratio. For integrated switching transistors, the cost of a device is proportional to its voltage-current (V-A) product. Larger transistors are typically required in order to stand higher voltage stress or to handle larger current while keeping resistive loss small. Likewise, in order to reduce the size of reactive components one must minimize their required energy storage or V-A stress. Thus switching converters should be designed in a way that reduces the total V-A stress over the components. Reference [20] gives two fundamental limits on the minimal V-A stress of the switches and reactive parts of a converter. Through a detailed first-order analysis in [21], it is concluded that SC converters can be superior to the inductor-based buck converter in terms of switch and reactive element utilization, approaching the given fundamental limits.

One of the noted advantages of the SC converter topologies is that their main reactive components are capacitors, which exhibit a substantially higher energy and power density

Figure 2.1: Schematics of LED drivers: (a) Simplified circuit of a AC/DC converter free LED driver; (b) Simplified circuit of a conventional Buck LED driver; (c) Simplified circuit of a conventional off-line flyback LED driver.

Flyback transformer for voltage down conversion as well as galvanic isolation.

Figure 2.2: Dissembled commercial flyback LED driver circuit.

than magnetics. Such is true for both integrated and discrete components. Typical surface mount capacitors can easily have an energy density three orders of magnitude larger than that of inductors [22]. The significantly higher energy density of capacitors allows for greater potential for integration. In addition, since most of the SC converter topologies (e.g. the ladder type or series-parallel type) arrange the power elements in series to interface the high input/output voltage level, the voltage stress on each individual component is only a fraction of the total rating. This allows the SC converters to use devices with lower voltage rating for "high" voltage applications. In magnetic-based converters, the main switches and reactive elements usually need to stand the whole input voltage or even higher.

However, SC DC/DC converters typically have a fixed input to output-voltage ratio. This behavior can be a disadvantage since LED devices are more conveniently controlled by a regulated forward current. Because of the PVT variation in an LED's I-V characteristic, it is impractical to control the LED's output by voltage regulation. A highly efficient current regulation scheme is required to take advantage of the SC converter topology for use in an LED driver. To achieve this goal, a hybrid switched-capacitor resonant (HSCR) strategy has been developed to combine the SC ladder topology with the series resonant converter [23]. The proposed HSCR converter leverages the advantages of the SC topology, while offering nearly lossless regulation of the output current and a soft-switching configuration

to handle the parasitic capacitance of the switching transistors. The series resonant stage can potentially provide a capacitive galvanic isolation barrier for the LED driver application as well.

We improved the HSCR architecture and implemented a highly integrated LED driver for a wide range of mains voltage standards [24]. To assist in integration our design takes advantage of the multilevel architecture of the SC ladder topology and the lowered individual device stress. As such, we use a medium-voltage-rated Analog-Bipolar-CMOS-DMOS (ABCD) technology to integrate the power transistors, gate drivers, level shifters, and internal DC-DC converters into a standard SC module. These modules can then be stacked in the voltage domain to interface with various mains voltages. This paper analyzes the proposed HSCR DC/DC converter topology [24] and describes the modularized IC implementation in detail. The paper also provides detailed analysis of the power loss of the SC ladder, design of the resonant network, and the performance of the HSCR converter under two different output stage configurations. The measurement results of both two-chips stacking and four-chip stacking HSCR converters are reported. The paper is organized as follows: Section 2.2 introduces the proposed HSCR DC/DC converter. Section 2.3 describes the implementation details of the HSCR converter module IC and Section 2.4 discusses the measurement results. Finally, Section 2.6 concludes the paper.

# 2.2 Hybrid-Switched-Capacitor-Resonant DC-DC Converter

## 2.2.1 System Architecture

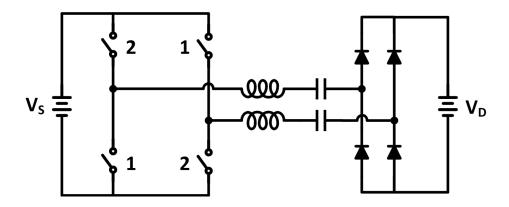

Fig. 2.3 shows the simplified system architecture of the proposed HSCR LED driver [24]. A power factor correction (PFC) rectifier interfaces the 120  $V_{AC}$  line voltage to the input of the HSCR converter, converting the AC source voltage to about 170  $V_{DC}$ . One example of the PFC rectifier front-end implementation that works with the proposed HSCR converter can be found in [25]. The HSCR converter consists of two main building blocks: a two-phase balanced 4:1 step-down power train, and a L-C resonant output stage. Capacitors  $C_{1,2,3,4}$  in the power train are DC capacitors, which ideally distribute the input DC link voltage evenly. In order to balance the charge across each capacitor, flying capacitors  $C_5$

Figure 2.3: (a) System architecture of the chip-stacking hybrid-switched-capacitor-resonant LED driver. (b) Two-phase non-overlapping gate drive signals. (c) Differential output signal between nodes C and  $C_b$  of the SC ladder.

to  $C_{10}$  are switched in a pair of non-overlapping phases with 50% duty cycle, as shown in Fig. 2.3(b). All of the switches and their driving circuits are integrated on chip. As described in Section 2.1, a chip-stacking configuration is implemented in order to overcome the breakdown voltage limit of the silicon technology. The SC ladder shown in Fig. 2.3 is split into two identical parts each with two DC voltage levels and eight main switches. This eight-switch part is designed as a standard SC module which can be stacked in series in the voltage domain and configured to stand a range of input DC voltage levels. The balanced topology of the SC ladder creates a differential AC square waveform across any two of the symmetrical flying nodes (e.g. node C and Cb in Fig. 2.3(a)). This differential

AC signal is then fed through the L-C resonant tank and rectified to drive the output LEDs. The differential topology helps in minimizing the common-mode signal feed-through to the output. With high voltage (e.g.  $5 \ kV$ ) MLCC capacitors, the resonant bridge can provide DC galvanic isolation between the LED heat spreader assembly and the power train. Since the resonant capacitors are rated for high voltage, the input of the L-C bridge can be attached to any of the symmetrical flying nodes. By varying the switching frequency of the SC ladder, the imaginary impedance of the L-C tank can be altered, thus allowing for output current regulation. Another L-C output network that utilizes all the differential nodes in the SC ladder is shown in Fig. 2.4 and will be analyzed in Section 2.2.2. The modified topology reduces the required capacitance of the DC and flying capacitors and boosts the power efficiency.

#### 2.2.2 Power Loss of the SC Ladder

Proper design of the HSCR DC-DC converter requires insights in analyzing and minimizing its power loss. There are three major contributions of power loss from the SC ladder in steady state: (1) charge sharing loss between the power capacitors during the two-phase operation; (2) resistive conduction loss due to the resonant output current flowing through the power switches; and (3) gate drive loss. The other switching losses, shoot-through current losses, and other parasitic losses are relatively small thus are not discussed in this paper. The efficiency of the output resonant stage and the overall converter will be discussed in Section 2.2.4. We can model the steady state behavior of the SC ladder as an ideal transformer with a series output impedance  $R_S$  [26], which represents the power losses and the requisite output voltage drop to transfer charge from input to the load.