## High-Performance Multi-Antenna Wireless for 5G and Beyond

## Mahmood Baraani Dastjerdi

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

### COLUMBIA UNIVERSITY

2020

©2020 Mahmood Baraani Dastjerdi All Rights Reserved

## ABSTRACT

### High-Performance Multi-Antenna Wireless for 5G and Beyond

### Mahmood Baraani Dastjerdi

Over the next decade, multi-antenna radios, including phased array and multiple-inputmultiple-output (MIMO) radios, are expected to play an essential role in the next-generation of wireless networks. Phased arrays can reject spatial interferences and provide coherent beamforming gain, and MIMO technology promises to significantly enhance the system performance in the coverage, capacity, and user data rate through the beamforming or diversity/capacity gain which can substantially increase the range in wireless links, that are challenged from the transmitter (TX) power handling, receiver (RX) noise perspectives and a multi-path environment. Furthermore, the multi-user MIMO (MU-MIMO) can simultaneously serve multiple users which is vital for femtocell base stations and access points (AP).

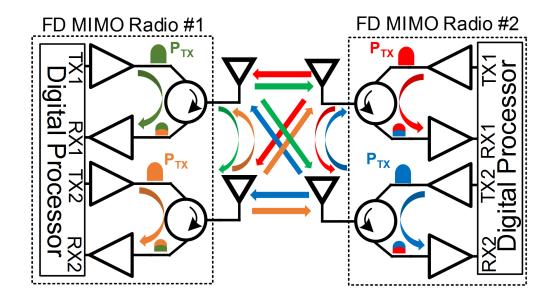

Full-duplex (FD) wireless, namely simultaneous transmission and reception at the same frequency, is an emerging technology that has gained attention due to its potential to double the data throughput, as well as provide other benefits in the higher layers such as better spectral efficiency, reducing network and feedback signaling delays, and resolving hiddennode problems to avoid collisions. However, several challenges remain in the quest for the high-performance integrated FD radios. Transmitter power handling remains an open problem, particularly in FD radios that integrate a shared antenna interface. Secondly, FD operation must be achieved across antenna VSWR variations and a changing EM environment. Finally, FD must be extended to multi-antenna radios, including phased array and multi-input multi-output (MIMO) radios, as over the next decade, they are expected to play an essential role in the next generation of wireless networks. Multi-antenna FD operation, however, is challenged not only by the self-interference (SI) from each TX to its own RX but also cross-talk SI (CT-SI) between antennas. In this dissertation, first, a full-duplex phased array circulator-RX (circ.-RX) is proposed that achieves self-interference cancellation (SIC) through repurposing beamforming degrees of freedom (DoF) on TX and RX. Then, an FD MIMO circ.-RX is proposed that achieves SI and CT-SI cancellation (CT-SIC) through passive RF and shared-delay baseband (BB) canceller that addresses challenges associated with FD MIMO operation.

Wireless radios at millimeter-wave (mm-wave) frequencies enable the high-speed link for portable devices due to the wide-band spectrum available. Large-scale arrays are required to compensate for high path loss to form an mm-wave link. Mm-wave MIMO systems with digitization enable virtual arrays for radar, digital beamforming (DBF) for high mobility scenarios and spatial multiplexing. To preserve MIMO information, the received signal from each element in MIMO RX should be transported to ADC/DSP IC for DBF, and vice versa on the TX side. A large-scale array can be formed by tiling multiple mm-wave IC front-ends, and thus, a single-wire interface is desired between DSP IC and mm-wave ICs to reduce board routing complexity. Per-element digitization poses the challenge of handling high data-rate I/O in large-scale tiled MIMO mm-wave arrays. SERializer – DESerializer (SERDES) is traditionally being used as a high-speed link in computing systems and networks. However, SERDES results in a large area and power consumption. In this dissertation, a 60 GHz 4element MIMO TX with a single-wire interface is presented that de-multiplexes the baseband signal of all elements and LO reference that are frequency-domain multiplexed on a singlewire coax cable.

# **Table of Contents**

| Li       | st of             | Figure | es                                                          | $\mathbf{v}$ |

|----------|-------------------|--------|-------------------------------------------------------------|--------------|

| Li       | List of Tables xi |        |                                                             |              |

| A        | cknov             | wledge | ments                                                       | xiii         |

| D        | edica             | tion   |                                                             | xiii         |

| 1        | Intr              | oducti | on                                                          | 1            |

|          | 1.1               | Full-D | uplex Multi-Antenna Wireless                                | 3            |

|          |                   | 1.1.1  | Full-Duplex Wireless                                        | 3            |

|          |                   | 1.1.2  | Why Multi-Antenna Full-Duplex?                              | 4            |

|          |                   | 1.1.3  | Challenges                                                  | 4            |

|          |                   | 1.1.4  | Prior Works                                                 | 7            |

|          | 1.2               | A 60 C | GHz 4-Element MIMO TX With A Single-Wire Interface          | 7            |

|          |                   | 1.2.1  | Motivation                                                  | 7            |

|          |                   | 1.2.2  | Prior Works                                                 | 9            |

|          |                   | 1.2.3  | Single-Wire Interface Using Frequency-Division Multiplexing | 10           |

|          | 1.3               | Organ  | ization                                                     | 11           |

| <b>2</b> | Full              | -Duple | ex Phased Array Wireless                                    | 13           |

|          | 2.1               | FD Pł  | nased Array System Requirements                             | 14           |

|          |                   | 2.1.1  | Array SIC                                                   | 14           |

|   |      | 2.1.2  | Link Budget Calculations and FD operation                 | 15 |

|---|------|--------|-----------------------------------------------------------|----|

|   | 2.2  | SIC vi | a Beamforming                                             | 17 |

|   | 2.3  | Circui | t Implementation                                          | 22 |

|   |      | 2.3.1  | Integrated CircRX Phased Array RX                         | 22 |

|   |      | 2.3.2  | Phased Array TX                                           | 29 |

|   |      | 2.3.3  | Slot Loop Antenna                                         | 29 |

|   | 2.4  | Exper  | imental Results                                           | 29 |

|   |      | 2.4.1  | Single-Element CircRX Measurements                        | 30 |

|   |      | 2.4.2  | 8-Element FD Phased-array TRX Measurements                | 32 |

|   |      | 2.4.3  | FD Demonstration                                          | 37 |

|   | 2.5  | Summ   | ary                                                       | 39 |

| 3 | Full | -Duple | ex MIMO Wireless                                          | 41 |

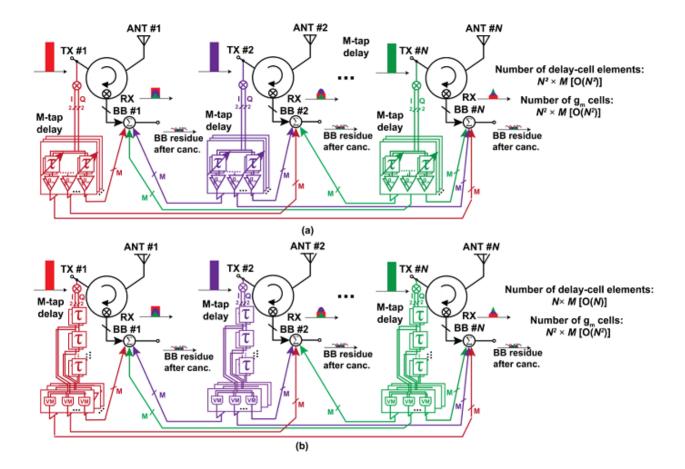

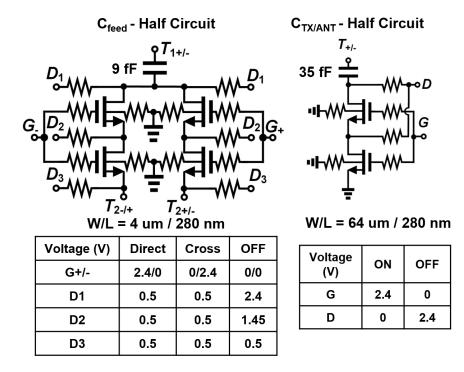

|   | 3.1  | FD M   | IMO Cancellation: Complexity, Trade-offs and Architecture | 42 |

|   |      | 3.1.1  | Dual Injection MIMO Canceller                             | 43 |

|   |      | 3.1.2  | Shared-Delay Baseband Canceller Architecture              | 43 |

|   |      | 3.1.3  | Baseband Canceller Noise Penalty                          | 46 |

|   | 3.2  | Circui | t Implementation                                          | 48 |

|   |      | 3.2.1  | Circulator-Receiver as a Shared MIMO FD Antenna Interface | 50 |

|   |      | 3.2.2  | MIMO Passive RF Cancellers                                | 51 |

|   |      | 3.2.3  | MIMO Baseband Canceller with Shared Delay-Cells           | 54 |

|   |      | 3.2.4  | Output Buffer                                             | 59 |

|   |      | 3.2.5  | Clock Generation and Bootstrapping circuitry              | 59 |

|   | 3.3  | Exper  | imental Results                                           | 62 |

|   |      | 3.3.1  | Circulator-Receiver Measurements                          | 62 |

|   |      | 3.3.2  | Linearity Measurements                                    | 64 |

|   |      | 3.3.3  | RF MIMO Passive Canceller Measurements                    | 64 |

|   |      | 3.3.4  | Wireless Full-Duplex MIMO SIC and CT-SIC Measurements     | 66 |

|   | 3.4  | Summ   | ary                                                       | 70 |

| 4  | A 6   | 0 GHz  | 4-Element MIMO TX with a Single-Wire Interface                      | 72  |

|----|-------|--------|---------------------------------------------------------------------|-----|

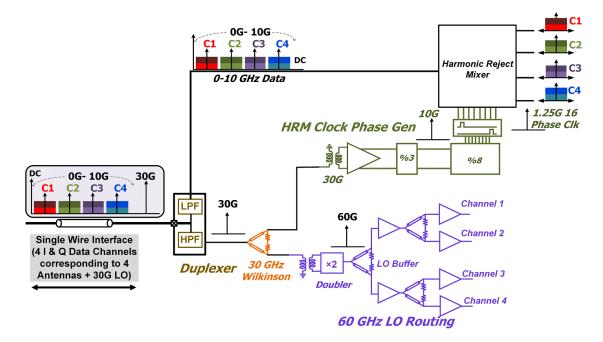

|    | 4.1   | Single | Wire Interface                                                      | 73  |

|    |       | 4.1.1  | Challenge                                                           | 73  |

|    |       | 4.1.2  | Signal Flow                                                         | 75  |

|    |       | 4.1.3  | Harmonic Rejection Mixer                                            | 76  |

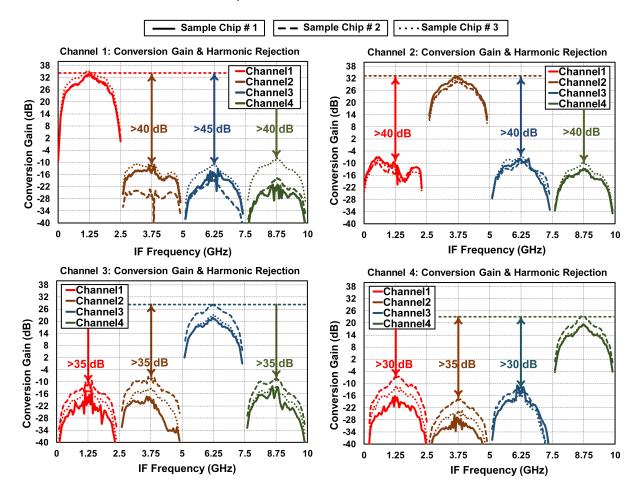

|    | 4.2   | Circui | t Implementation                                                    | 77  |

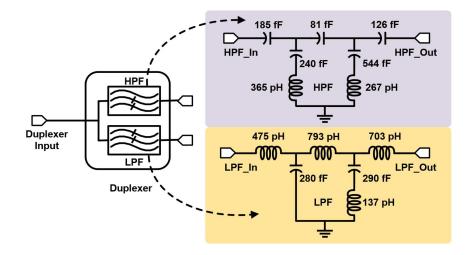

|    |       | 4.2.1  | Duplexer                                                            | 78  |

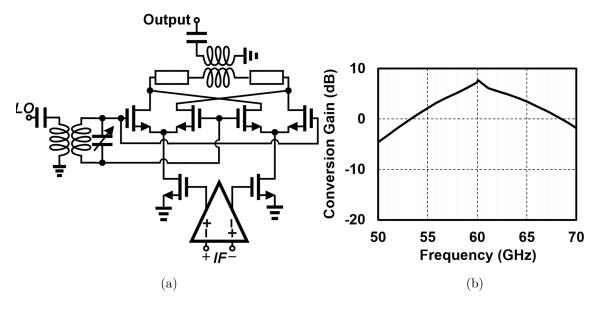

|    |       | 4.2.2  | Two-Stage Harmonic Rejection Mixer                                  | 80  |

|    |       | 4.2.3  | Low-Pass Filter                                                     | 80  |

|    |       | 4.2.4  | Upcoversion Gilbert-Cell Mixer                                      | 82  |

|    |       | 4.2.5  | Pre-Driver and Power Amplifier                                      | 83  |

|    | 4.3   | Measu  | rement Results                                                      | 84  |

|    | 4.4   | Summ   | ary                                                                 | 87  |

| 5  | Con   | clusio | n                                                                   | 89  |

| Ι  | Bi    | bliogr | aphy                                                                | 94  |

| Bi | bliog | graphy |                                                                     | 95  |

| II | А     | ppen   | dix 1                                                               | 108 |

| A  | A C   | ircuit | Simulation Technique for Inter-modulation Simulations and Lin-      | -   |

|    | eari  | ty Ana | alysis of N-path Filters and Passive-Mixer-Like Circuits            | 109 |

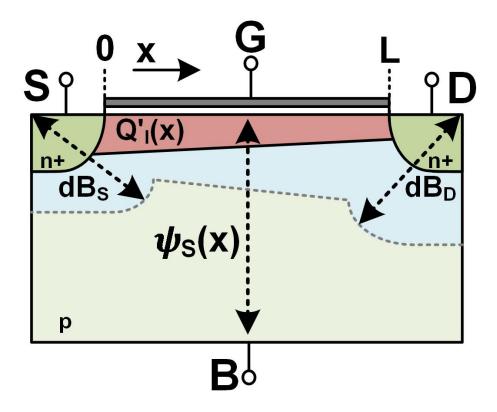

|    | A.1   | Circui | t simulation technique using SP equations and short channel effects | 111 |

|    |       | A.1.1  | Long-Channel Transistor Surface Potential Equations                 | 112 |

|    |       | A.1.2  | Effective Mobility                                                  | 114 |

|    |       | A.1.3  | Charge Sharing                                                      | 115 |

|    |       | A.1.4  | Velocity Saturation                                                 | 116 |

|     | A.1.5 Channel Length Modulation                                             | 117 |

|-----|-----------------------------------------------------------------------------|-----|

|     | A.1.6 Parameter Extraction                                                  | 118 |

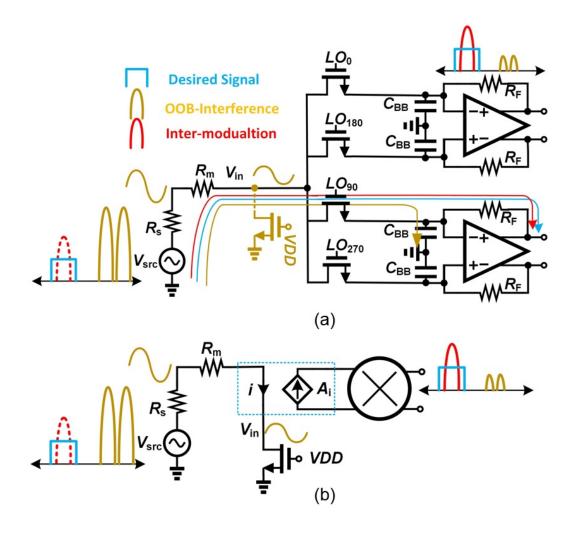

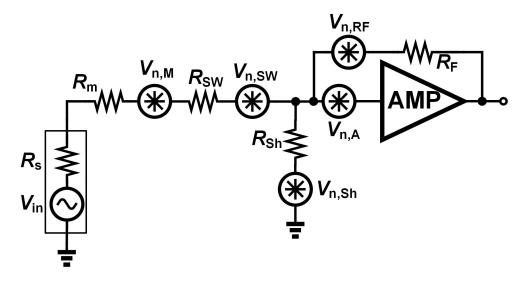

| A.2 | Mixer-First Receiver/N-Path-Filter Linearity Analysis and Design Trade-Offs | 119 |

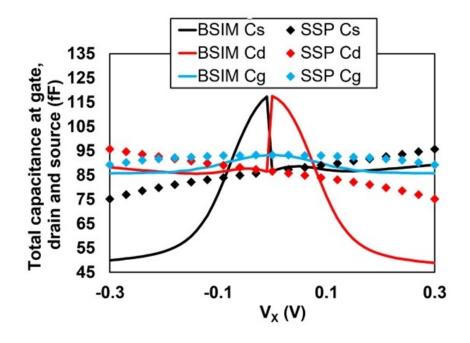

| A.3 | Simulation and Measurement Results                                          | 126 |

| A.4 | Summary                                                                     | 130 |

# List of Figures

| 1.1 | Evolving speed of wireless networks [1]. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$               | 1  |

|-----|-----------------------------------------------------------------------------------------------------|----|

| 1.2 | (a) Beamforming antenna array scenario at BS and UE [2] and (b) the antenna                         |    |

|     | array configuration for 5G cellular mobile [3].                                                     | 2  |

| 1.3 | Different multiplexing access methods: (a) time-division (b) frequency-division                     |    |

|     | (c) full-duplex [4]                                                                                 | 3  |

| 1.4 | Integrating FD operation with MIMO technology can result in higher data                             |    |

|     | rate and spectrum efficiency for the next generation of wireless communication.                     | 5  |

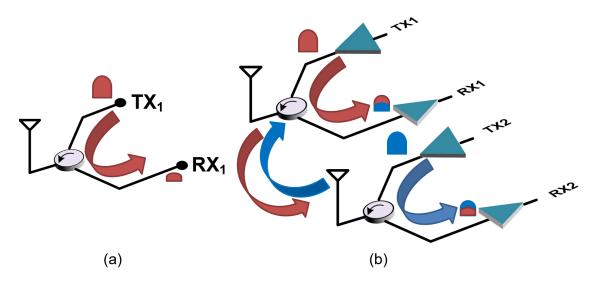

| 1.5 | SI and CT-SI in full duplex (a) single-antenna (b) and multi-antenna wireless.                      | 5  |

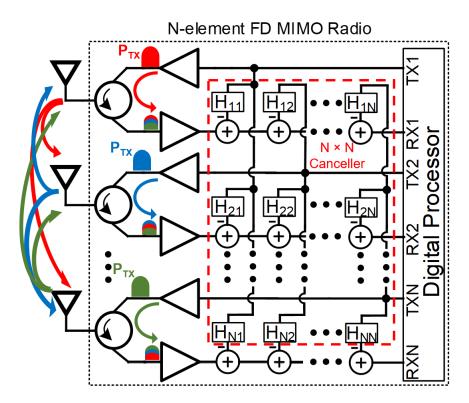

| 1.6 | In an $N$ -element FD MIMO radio, a cancellation path for each TX-RX pair                           |    |

|     | is required, and so the canceller complexity grows as $\mathcal{O}(N^2)$                            | 6  |

| 1.7 | Prior system level FD MIMO transceivers using discrete components: (a) FD                           |    |

|     | $3{\times}3$ MIMO with shared delay structure to reduce the canceller complexity                    |    |

|     | (b) FD MIMO using DBF only on the TX side, and (c) FD 2-element MIMO                                |    |

|     | radio for LTE applications using 4 RF bulky multi-tap cancellers to suppress                        |    |

|     | the SI and CT-SI                                                                                    | 8  |

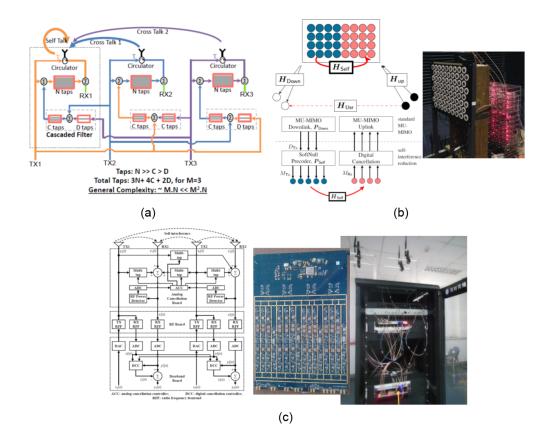

| 1.8 | Prior transceivers with single-wire interface: (a)<br>A $60\mathrm{GHz}~\mathrm{TX/RX}$ with single |    |

|     | coaxial interface for low-cost integration in PC platform $[5]$ (b)A 4-element                      |    |

|     | 28 GHz mm-wave MIMO array with single-wire interface using code-domain                              |    |

|     | multiplexing $[6]$                                                                                  | 10 |

| 1.9 | Single-Wire interface between DSP unit and mm-wave unit using frequency-                            |    |

|     | division multiplexing                                                                               | 11 |

|     |                                                                                                     |    |

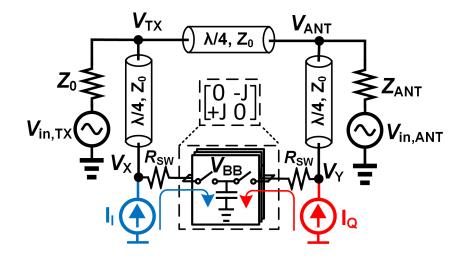

| 2.1  | FD N-path-filter-based circulator-receiver conceptual architecture and block         |    |

|------|--------------------------------------------------------------------------------------|----|

|      | diagram                                                                              | 14 |

| 2.2  | FD phased array link budget.                                                         | 15 |

| 2.3  | (a) A 2×4 8-element antenna array at 730 MHz with $\lambda/2$ spacing, (b) the       |    |

|      | measured SI channel magnitudes at 730 MHz, and (c)–(d) examples of mea-              |    |

|      | sured SI channel magnitudes across frequency from antenna elements $(1,1)$           |    |

|      | and $(1,2)$ to the adjacent elements, respectively                                   | 18 |

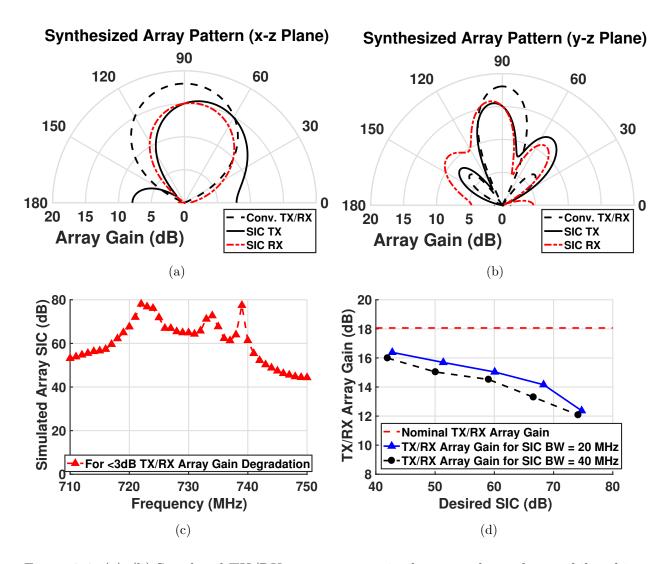

| 2.4  | (a)–(b) Simulated TX/RX array patterns in the $x$ - $z$ and $y$ - $z$ planes while   |    |

|      | achieving 60 dB array SIC across 20 MHz with 3 dB array gain degradation             |    |

|      | in the TX/RX broadside beam-pointing directions, (c) simulated array SIC             |    |

|      | where at least 60 dB SIC is guaranteed to be achieved across 720–740 MHz,            |    |

|      | (d) simulated TX/RX array gain for a desired array SIC based on solving an           |    |

|      | optimization problem using the measured SI channels depicted in Fig. 2.3. $$ .       | 19 |

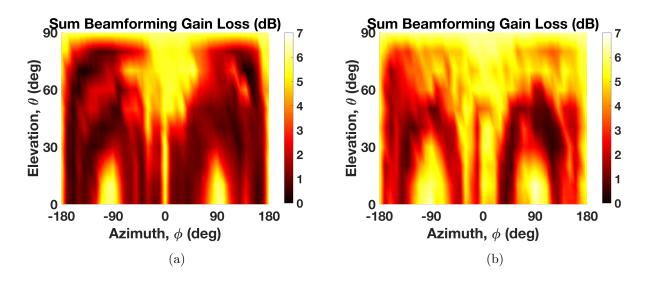

| 2.5  | (a)–(b) spatial distribution of the simulated sum TX and RX beamforming              |    |

|      | gain loss for achieving the desired RF SIC across 20 MHz and 40 MHz band- $$         |    |

|      | width                                                                                | 20 |

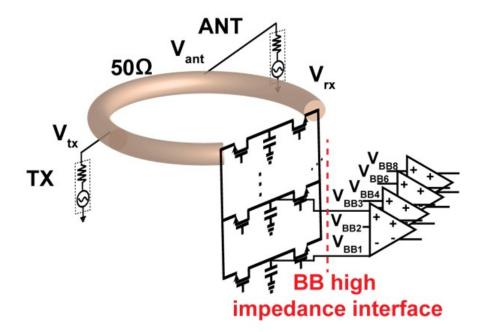

| 2.6  | Combined non-magnetic non-reciprocal circulator-receiver deployed as inte-           |    |

|      | grated shared antenna interface                                                      | 23 |

| 2.7  | Block/Circuit Diagram of scalable 4-element FD circRX phased array                   | 24 |

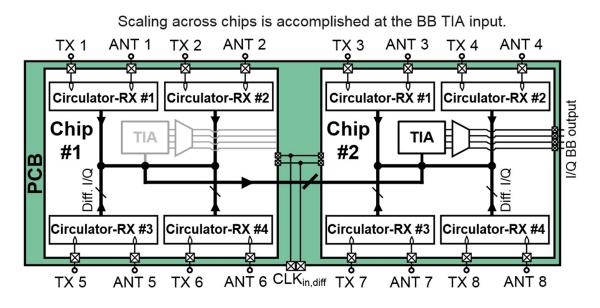

| 2.8  | Tiling two circRX phased array to form 8-element FD circRX phased array.             | 24 |

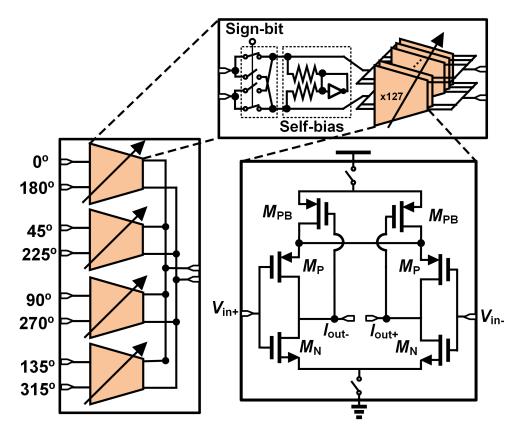

| 2.9  | Beamforming using 3-bit vector modulator: (a) 4-phase (b) 8-phase                    | 25 |

| 2.10 | Inverter-based output buffer with common-mode feedback                               | 26 |

| 2.11 | CircRX phased array clock distribution and synchronize and reset circuitry.          | 27 |

| 2.12 | Circuit details of programmable $\mathrm{g}_m\text{-cells}$ deployed for beamforming | 28 |

| 2.13 | A custom-designed 8-element transmitter phased array: (a) Block diagram,             |    |

|      | and (b) PCB implementation                                                           | 30 |

| 2.14 | Slot loop antenna simulated radiation pattern                                        | 31 |

| 2.15 | FD N-path-filter-based circulator-receiver conceptual architecture and block   |    |

|------|--------------------------------------------------------------------------------|----|

|      | diagram                                                                        | 31 |

| 2.16 | Custom designed antenna tuner: (a) circuit diagram (b) PCB                     | 32 |

| 2.17 | Single-element circRX measurements: (a) TX-ANT S-parameters demon-             |    |

|      | strating non-reciprocity, (b) TX-ANT IIP3.                                     | 33 |

| 2.18 | Single-element circRX measurements: (a) TX-ANT S-parameters demon-             |    |

|      | strating nonreciprocity, (b) TX-ANT IIP3 and (c) NF                            | 34 |

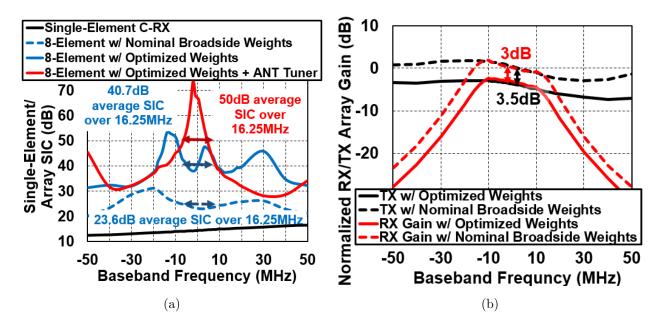

| 2.19 | Measured full-duplex phased-array performance across 8-elements (tiling of $2$ |    |

|      | ICs): (a) array SIC, (b) impact of optimized weights to achieve SIC on the     |    |

|      | TX/RX array gain.                                                              | 35 |

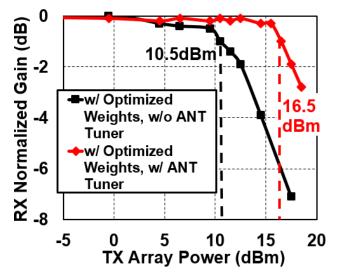

| 2.20 | Gain compression of a small received signal under the influence of TX power    |    |

|      | with optimized weights with and without the antenna tuner                      | 35 |

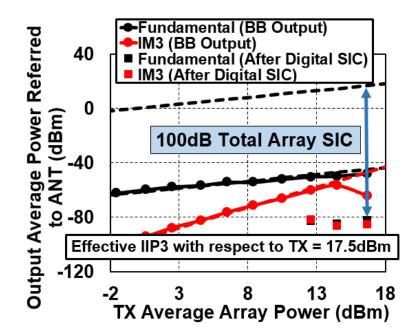

| 2.21 | Two-tone TX test tracking the TX total SI and its IM3 products at the receiver |    |

|      | output with additional digital SIC.                                            | 36 |

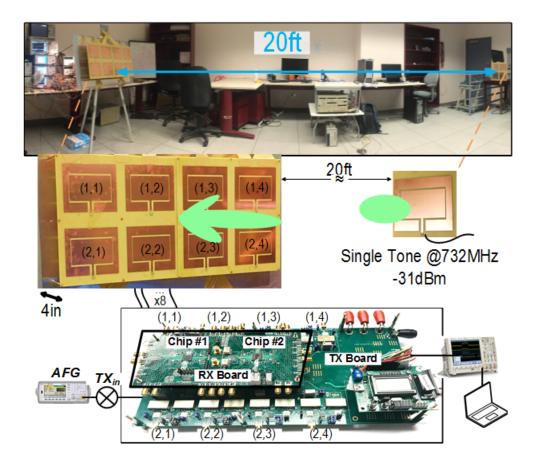

| 2.22 | Wireless FD demonstration setup                                                | 37 |

| 2.23 | Demo results: A -31dBm desired signal radiated from 20ft away from a sin-      |    |

|      | gle antenna is recovered while transmitting a 5MHz OFDM-like signal with       |    |

|      | +8.7dBm TX array power                                                         | 38 |

| 3.1  | FD MIMO links benefits from MIMO diversity/capacity gain as well as FD         |    |

|      | spectrum efficiency. However, CT-SI must be addressed in addition to SI        | 42 |

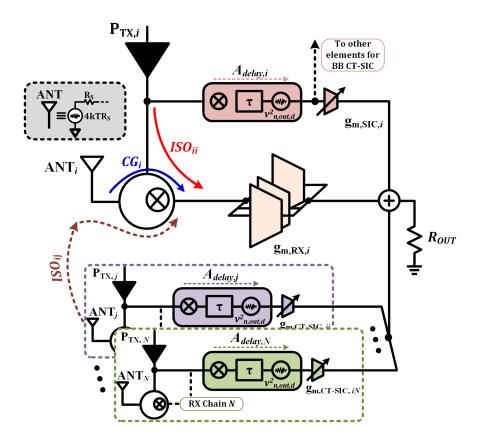

| 3.2  | Proposed dual injection MIMO RF and BB canceller to address power han-         |    |

|      | dling and complexity challenges of FD MIMO implementation                      | 44 |

| 3.3  | MIMO baseband canceller structure and power consumption distribution: (a)      |    |

|      | typical MIMO canceller (b) proposed shared-delay BB canceller architecture.    | 45 |

| 3.4  | Model for the analysis of noise degradation due to active delay-based baseband |    |

|      | cancellation.                                                                  | 47 |

| 3.5  | Impact of the baseband active delay cells on NF as a function of RF SIC and    |    |

|      | CT-SIC                                                                         | 48 |

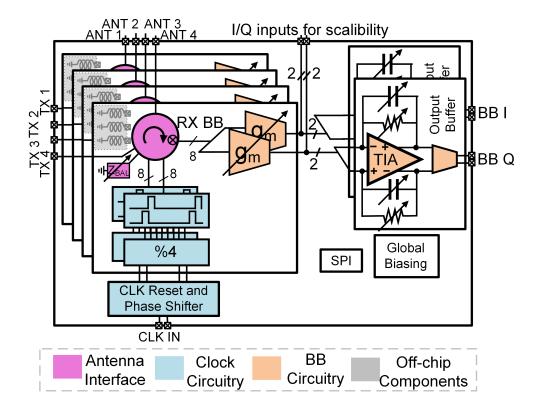

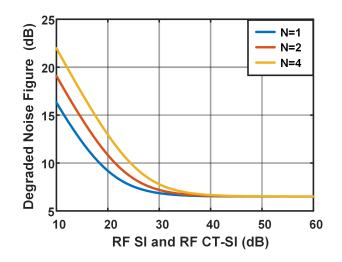

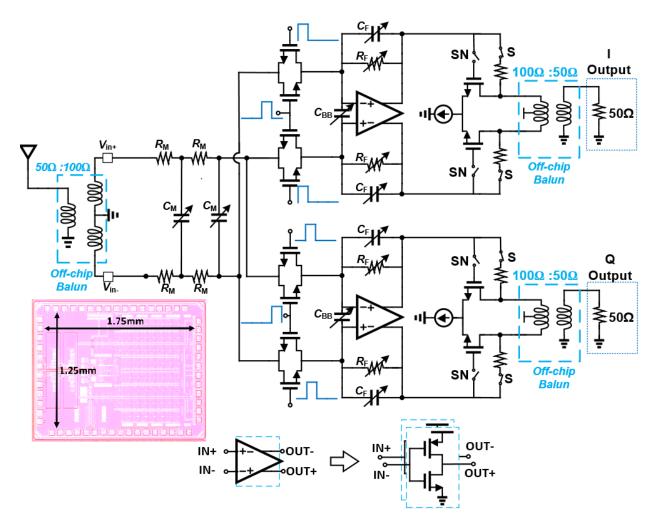

| 3.6  | Block and circuit diagram of the 65nm CMOS 2.2GHz full-duplex 2-element                        |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | MIMO circRX with high TX power handling exploiting MIMO RF and                                 |    |

|      | shared-delay baseband self-interference cancellation                                           | 49 |

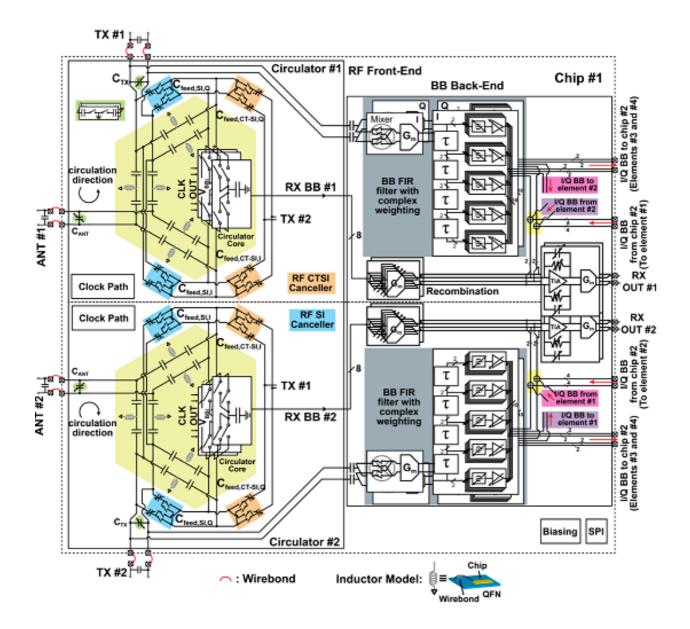

| 3.7  | Two thick-oxide devices stacked to implement the feed capacitor and $\mathrm{TX}/\mathrm{ANT}$ |    |

|      | capacitor banks.                                                                               | 51 |

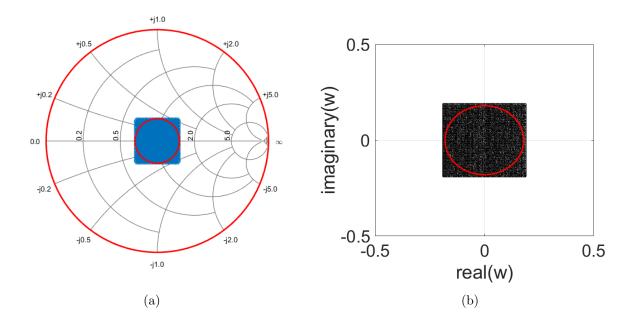

| 3.8  | Circulator model for feed-capacitor-based RF SIC and CT-SIC analysis                           | 52 |

| 3.9  | Calculated antenna (a) VSWR and (b) cross-talk coupling coverage, which                        |    |

|      | shows that a VSWR of 1.5 (red circle) or up to -14.8 dB of antenna coupling                    |    |

|      | (red circle) can be covered                                                                    | 55 |

| 3.10 | Passive mixer along with programmable capacitor bank used to tap from the                      |    |

|      | TX for BB SIC and CT-SIC                                                                       | 56 |

| 3.11 | Complimentary delay cell architecture based on [7]                                             | 56 |

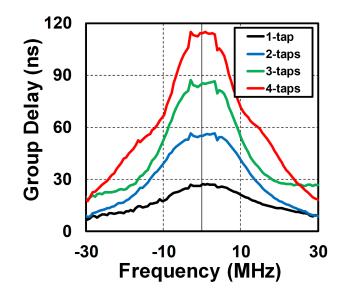

| 3.12 | Measured delays across the 4 taps of the delay element                                         | 57 |

| 3.13 | BB canceller vector modulator.                                                                 | 58 |

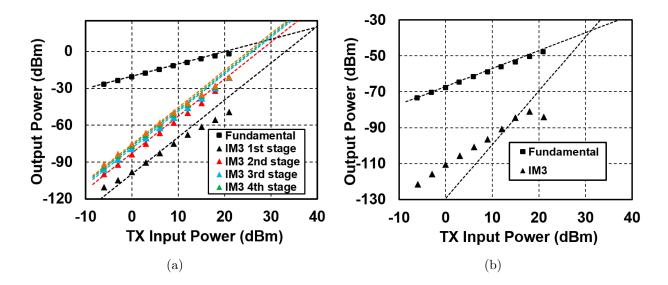

| 3.14 | Baseband canceller IIP3 simulations: (a) TX to the output of each stage of                     |    |

|      | the delay line, and (b) TX to output current of the baseband canceller when                    |    |

|      | the cancellation weight is programmed                                                          | 59 |

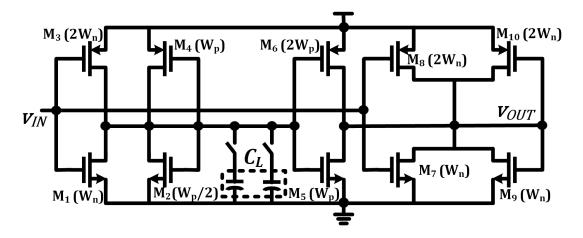

| 3.15 | Inverter-based output buffer with common-mode feedback                                         | 60 |

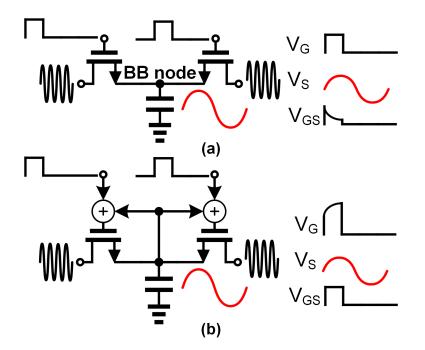

| 3.16 | Clock bootstrapping in N-path filters can improve the linearity by keeping                     |    |

|      | the gate-source voltage constant. N-path filter and FET terminal voltages (a)                  |    |

|      | without and (b) with clock bootstrapping.                                                      | 60 |

| 3.17 | Clock generation and bootstrapping circuitry.                                                  | 61 |

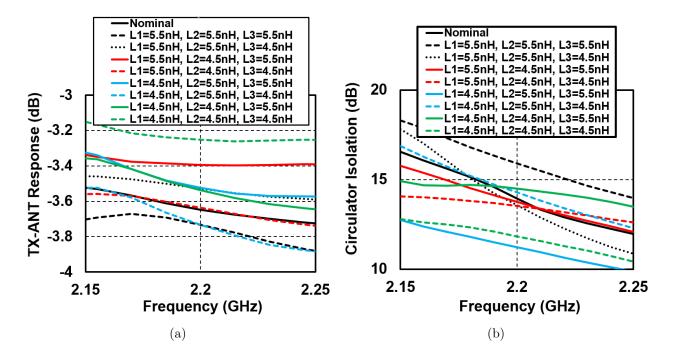

| 3.18 | Simulation results of the circRX performance across 10% variation in wire-                     |    |

|      | bond inductance, where L1, L2 and L3 are the wirebond inductances in the                       |    |

|      | CLC sections between the ANT-RX, TX-RX and TX-ANT ports, respectively:                         |    |

|      | (a) TX-ANT response, and (b) TX-RX isolation.                                                  | 63 |

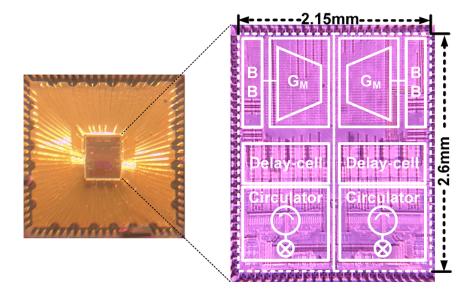

| 3.19 | Chip microphotograph of the 65 nm CMOS FD 2-element MIMO circRX in                             |    |

|      | an 80-pin QFN package.                                                                         | 64 |

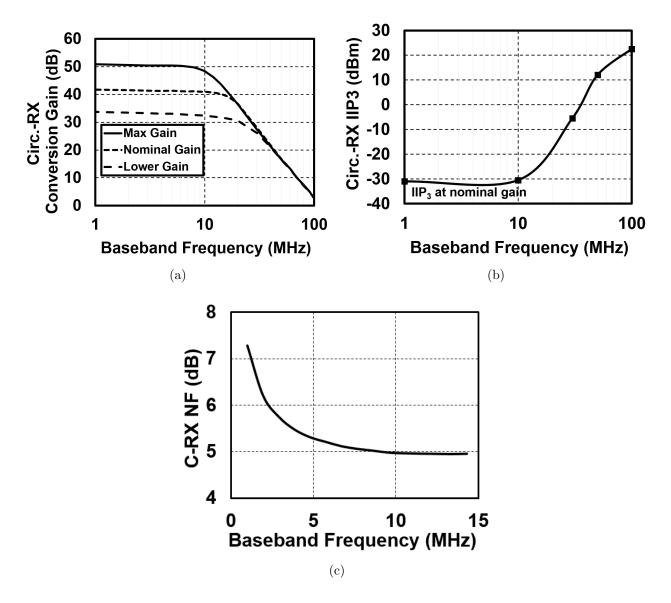

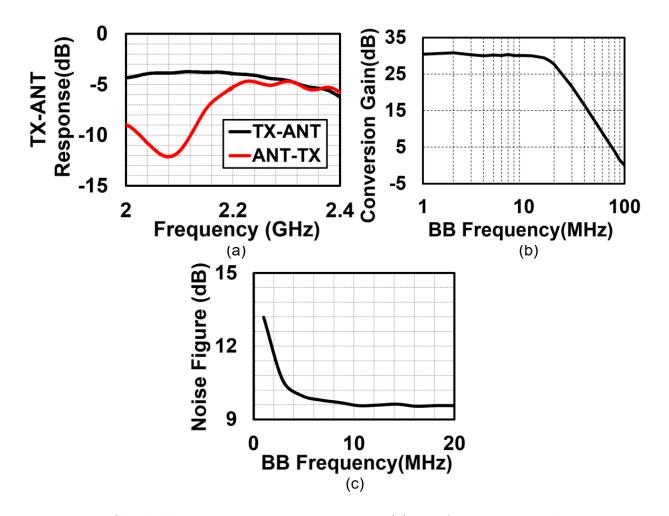

| 3.20 | Single-element circRX measurements: (a) TX-ANT response demonstrating        |    |

|------|------------------------------------------------------------------------------|----|

|      | nonreciprocity, (b) ANT-BB conversion gain, and (c) NF                       | 65 |

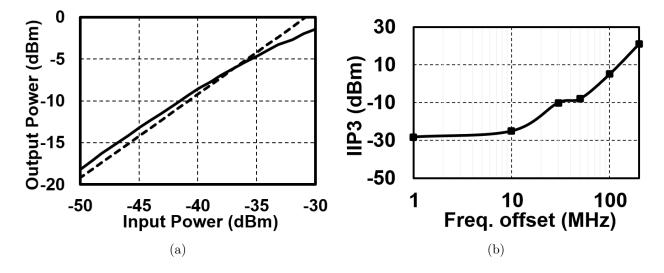

| 3.21 | Single-element circRX ANT-BB linearity measurements: (a) in-band 1dB         |    |

|      | compression point, (b) IIP3 versus offset frequency                          | 66 |

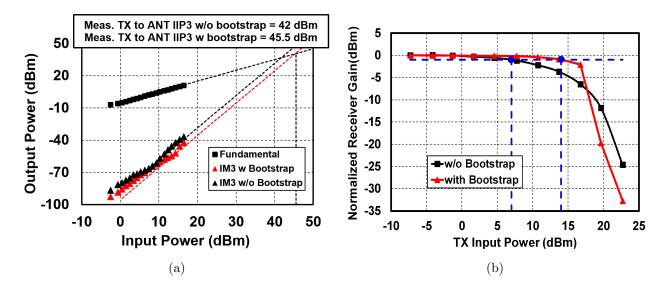

| 3.22 | Linearity measurements with and without bootstrapping: (a) TX-ANT IIP3       |    |

|      | and (b) TX-induced RX gain compression.                                      | 66 |

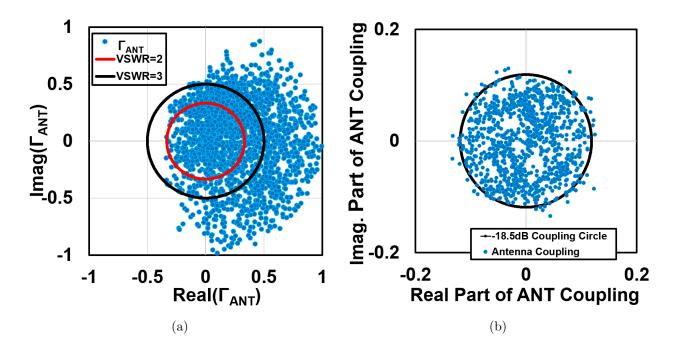

| 3.23 | Measured RF SIC/CT-SIC performance: (a) SIC antenna VSWR coverage            |    |

|      | and (b) CT-SIC antenna coupling coverage.                                    | 67 |

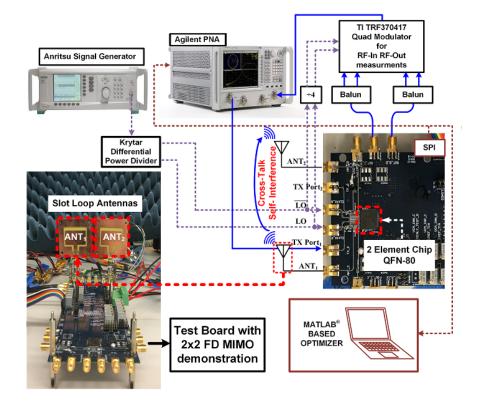

| 3.24 | FD MIMO wireless SIC and CT-SIC measurement setup                            | 68 |

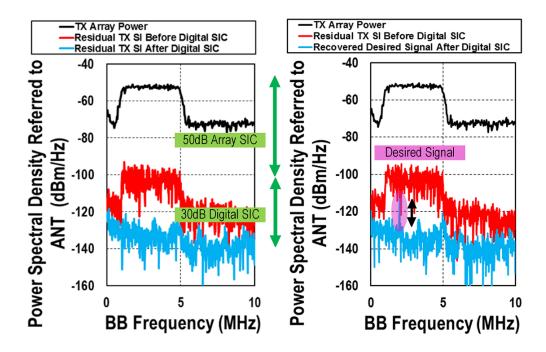

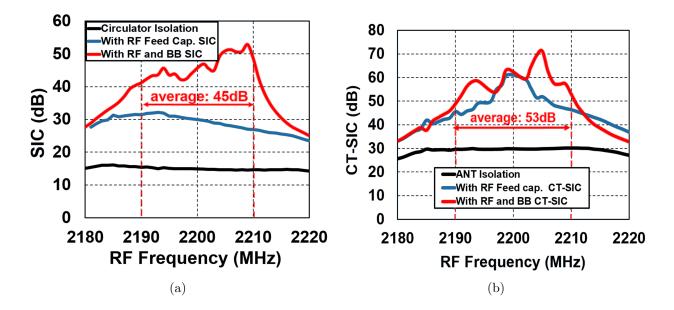

| 3.25 | Wireless FD measurements: (a) single-element FD SIC measurement results,     |    |

|      | and (b) two-element FD CT-SIC measurement results.                           | 69 |

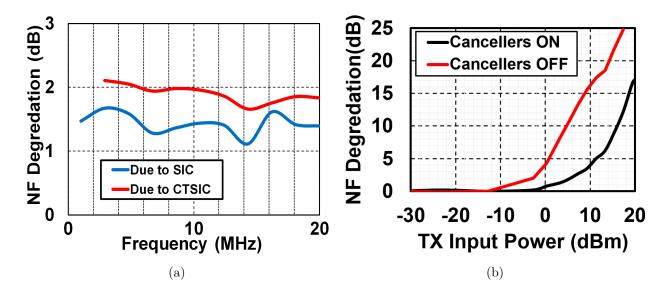

| 3.26 | (a) NF degradation due to SIC and CT-SIC, and (b) NF degradation in the      |    |

|      | presence of TX signal.                                                       | 70 |

| 4.1  | A scalable MIMO TX architecture with a single-wire interface based on CDMA   |    |

|      | and FDMA.                                                                    | 74 |

| 4.2  | Single-wire interface signal flow breakdown.                                 | 75 |

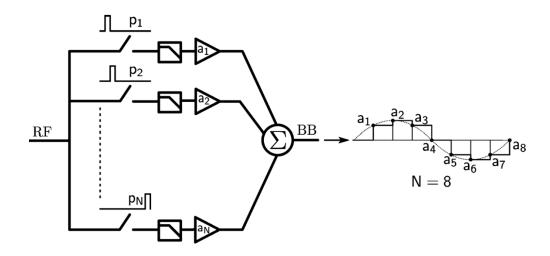

| 4.3  | HRM using $1/N$ duty cycle clocks and baseband gain coefficients [8]         | 77 |

| 4.4  | HR is limited due to gain quantization and mismatch. Multi-stage HRM         |    |

|      | reduces the degradation in HR due to gain and phase mismatch                 | 77 |

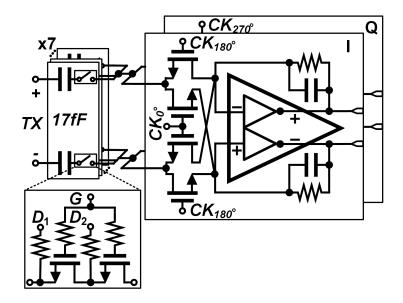

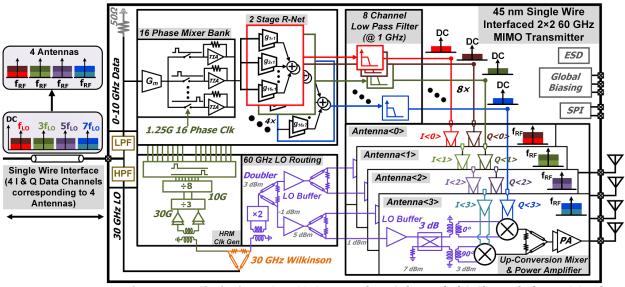

| 4.5  | Block diagram of a 45 nm RFSOI 60 GHz 4-element MIMO TX with a               |    |

|      | frequency-division-multiplexed 10 GHz single-wire interface.                 | 78 |

| 4.6  | Circuit Implementation of the duplexer that includes high pass and low pass  |    |

|      | filters to divide 0-10 GHz IF data and 30 GHz LO signal from the single wire |    |

|      | input                                                                        | 79 |

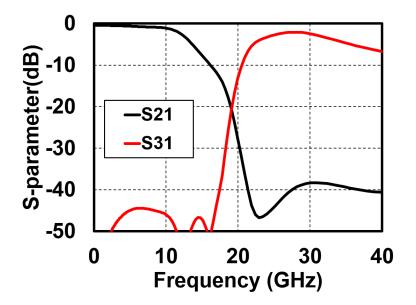

| 4.7  | S-parameter simulation of the duplexer which divides IF signals and 30 GHz   |    |

|      | reference with around 40 dB isolation.                                       | 79 |

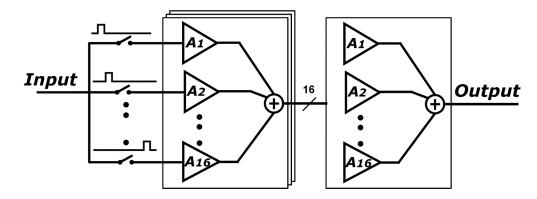

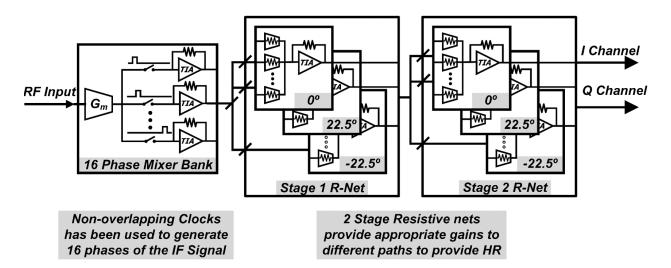

| 4.8  | Circuit Implementation of the 2-stage harmonic rejection mixer with minimum  |    |

|      | area and power consumption.                                                  | 80 |

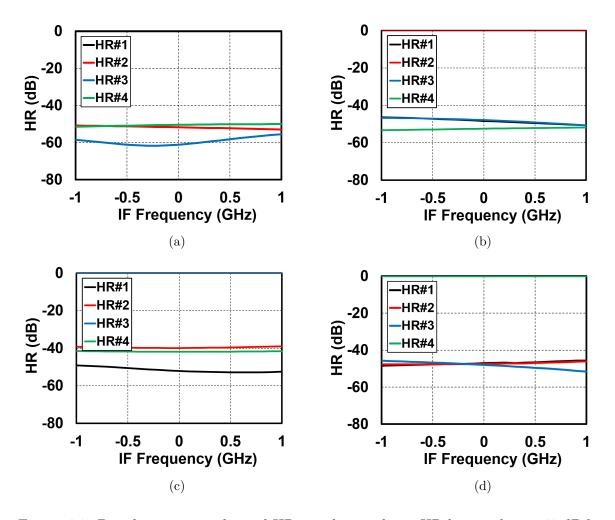

| 4.9  | Post-layout inter-channel HR simulation shows HR better than $>40$ dB be-                          |     |

|------|----------------------------------------------------------------------------------------------------|-----|

|      | tween all channels.                                                                                | 81  |

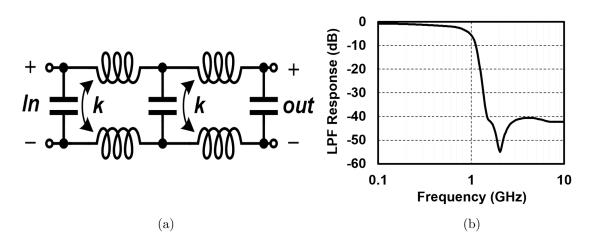

| 4.10 | The 5th order differential elliptic low pass filter using passive components.                      | 82  |

| 4.11 | Doubly-balanced Gilbert cell mixer used as upconversion mixer with BB am-                          |     |

|      | plifier (a) circuit diagram and (b) simulation results.                                            | 82  |

| 4.12 | Two-stage stacked class-E PA (a) circuit diagram, and (b) simulation results.                      | 83  |

| 4.13 | Chip microphotograph of the 45 nm CMOS RF-SOI 60 GHz 4-element MIMO $$                             |     |

|      | ΤΧ                                                                                                 | 84  |

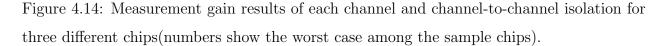

| 4.14 | Measurement gain results of each channel and channel-to-channel isolation for                      |     |

|      | three different chips (numbers show the worst case among the sample chips).                        | 85  |

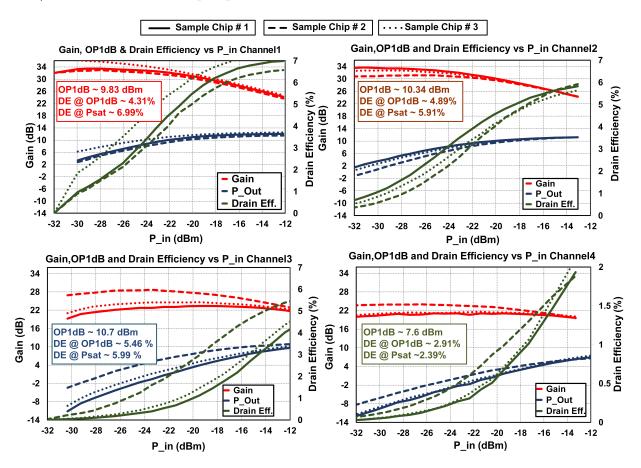

| 4.15 | Measured gain, output power and drain efficiency as a function of input power                      |     |

|      | for all channels for three different chips. The inset in each figure shows the                     |     |

|      | Psat, OP1dB and drain efficiency at OP1dB for the 3rd sample                                       | 86  |

| 4.16 | Measurement setup to demonstrate simultaneous formation of multiple beams                          |     |

|      | carrying independent signals: antenna pattern measured for two simultaneously-                     |     |

|      | transmitted frequencies, 59.9GHz and 60.05GHz                                                      | 87  |

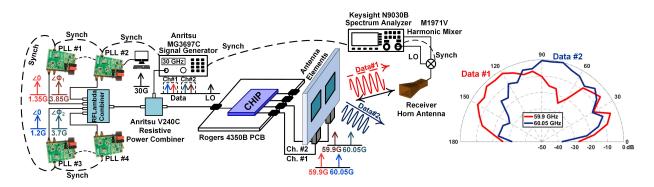

| A.1  | Proposed circuit simulation technique based on surface potential equations                         | 110 |

| A.2  | Simulation of total capacitance at the transistor terminals of $24 \times \frac{4\mu m}{60nm}$ de- |     |

|      | vice in 65nm CMOS using foundry BSIM4 models and the proposed circuit                              |     |

|      | simulation technique.                                                                              | 112 |

| A.3  | Cross section of the MOS transistor.                                                               | 114 |

| A.4  | (a) Single-ended 4-path mixer-first receiver (MFRx), and (b) MFRx/N-path                           |     |

|      | filter equivalent circuit for the analysis of OOB linearity                                        | 119 |

| A.5  | Simplifed model to analyze the MFRx noise performance [9]                                          | 121 |

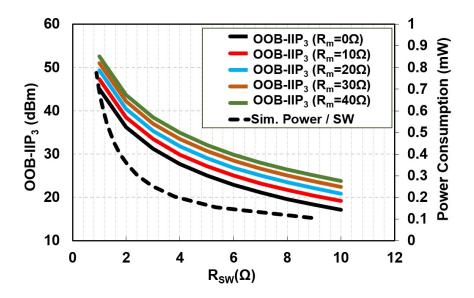

| A.6  | Trade-off of between OOB-IIP3 and power consumption at 1GHz ( $R_s = 50\Omega$ ).                  | 122 |

| A.7  | Trade-off of between OOB-IIP3 and NF vs. $R_t$ for different values of the                         |     |

|      | amplifier gain $(R_{SW} = 3\Omega, R_s = 50\Omega)$ .                                              | 123 |

|      |                                                                                                    |     |

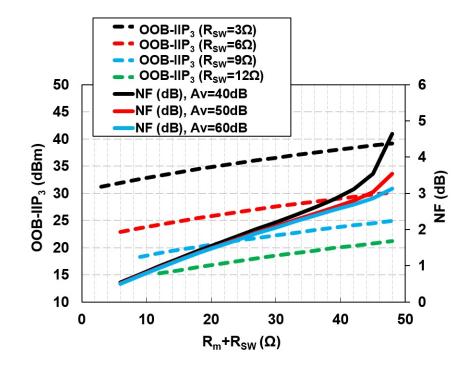

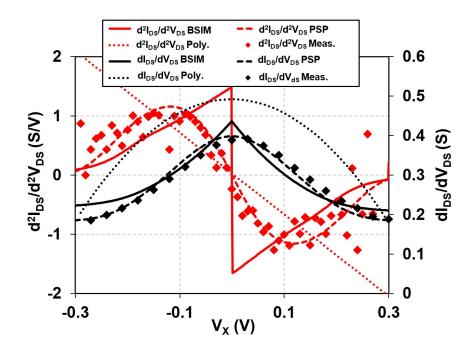

| A.8  | Simulated $I_{DS}$ vs. $V_{DS}$ of a $24 \times \frac{4\mu m}{60nm}$ device for different values of the $V_{GS}$ |     |

|------|------------------------------------------------------------------------------------------------------------------|-----|

|      | using factory-provided BSIM4 models and our circuit simulation technique. $\ .$                                  | 124 |

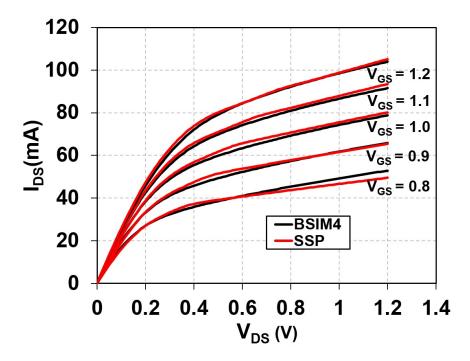

| A.9  | Gummel test on a $24 \times \frac{4\mu m}{60nm}$ device using BSIM4 models, the proposed circuit                 |     |

|      | simulation technique, 3rd order polynominal curve-fit and measured data                                          | 125 |

| A.10 | Simulation and measurement results from a harmonic test on a single $24 \times \frac{4\mu m}{60nm}$              |     |

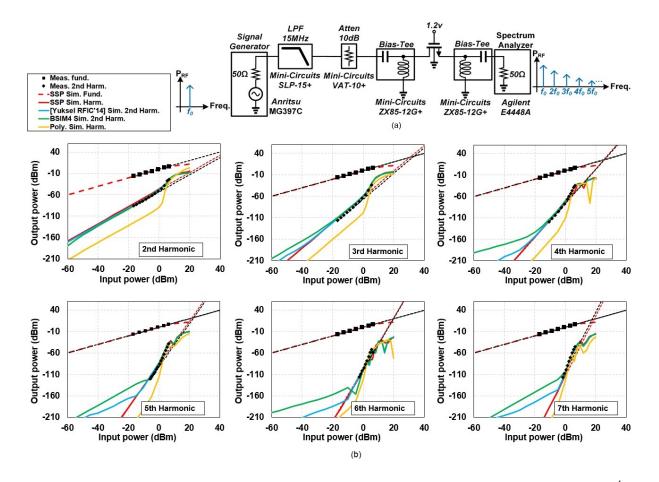

|      | transistor switch: (a) test setup, and (b) results                                                               | 127 |

| A.11 | IIP3 simulations of a single $24 \times \frac{4\mu m}{60nm}$ switch to ground - BSIM4, the modeling              |     |

|      | approach in [10], and our proposed circuit technique. $\ldots$ $\ldots$ $\ldots$ $\ldots$                        | 128 |

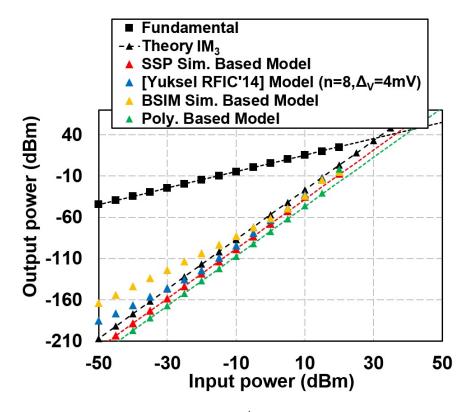

| A.12 | Block and circuit diagram and chip micrograph of the 65nm CMOS $0.15\text{-}2\mathrm{GHz}$                       |     |

|      | mixer-first receiver.                                                                                            | 129 |

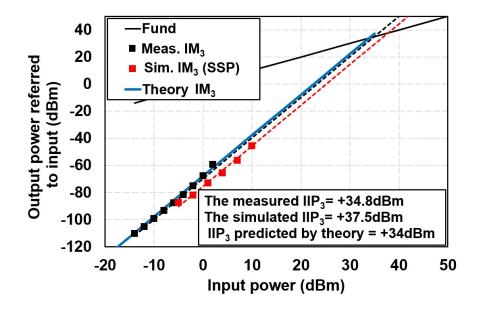

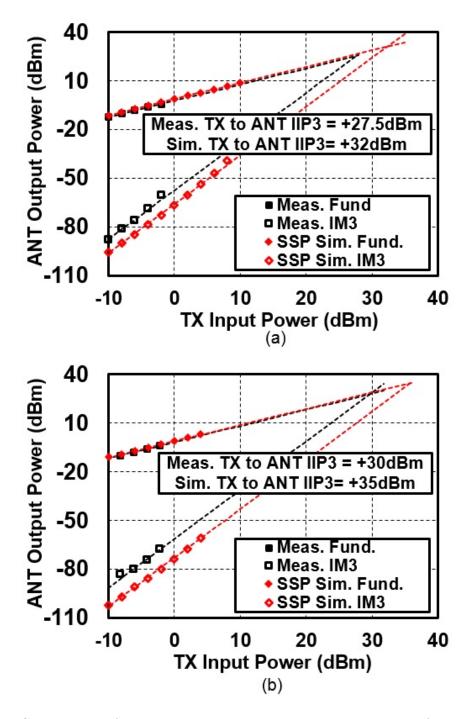

| A.13 | Comparison of measured MFRx out-of-band (OOB) IIP3 with the simulated                                            |     |

|      | OOB IIP3 using the proposed circuit simulation technique                                                         | 130 |

| A.14 | Comparison of transmitter-to-antenna $\mathrm{IIP}_3$ measurements of our 750MHz non-                            |     |

|      | magnetic non-reciprocal integrated N-path-filter-based circulators fabricated                                    |     |

|      | in 65nm CMOS with new simulations based on our circuit simulation tech-                                          |     |

|      | nique: (a) [11],and (b) [12]                                                                                     | 131 |

|      |                                                                                                                  |     |

# List of Tables

| 2.1 | FD phased array link budget.                                                                                        | 16 |

|-----|---------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Comparison of the proposed FD phased array circRX with the state-of-the-                                            |    |

|     | art FD RXs with an integrated shared antenna interface                                                              | 39 |

| 3.1 | Comparison of the proposed FD MIMO circRX with state-of-the-art FD RXs with an integrated shared antenna interface. | 71 |

| 4.1 | Comparison with state-of-the-art mm-wave transceivers with and without                                              |    |

|     | single-wire interface.                                                                                              | 88 |

To my parents, grandparents and dear friends...

## Chapter 1

## Introduction

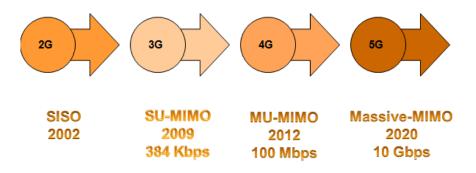

By 2020, according to CISCO, more people (5.4 B) will have mobile phones than have electricity (5.3 B), running water (3.5 B) and cars (2.8 B). While 75% of the mobile data is bandwidth-hungry video, users expect a higher data rate and more reliable wireless communication [1]. The use of a large number of antennas in base station (BS), access point and user equipment (UE), called phased array or MIMO is a key technology promised to increase the capacity of network and beyond [1,3,13–16]. Wireless network speed has improved over the years starting from single-input single-output (SISO) systems, single-userand multi-user-MIMO networks. MU-MIMO systems already provide a significant advantage over earlier systems, and massive MIMO (mMIMO) aims to further enhance data throughput to >10 Gbps (Fig.1.1).

Figure 1.1: Evolving speed of wireless networks [1].

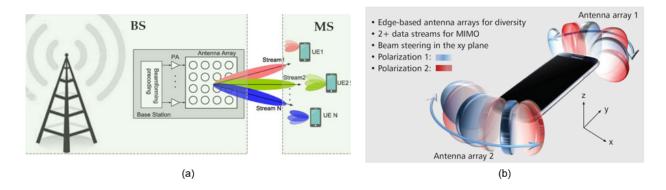

Mm-wave communication is considered in fifth-generation (5G) of the wireless system as it promises tremendous available bandwidth for high data rate communication. However, it is important to understand the channel dynamics with respect to time and space to form a robust communication system as mm-wave signals are highly susceptible to blocking, and they have communication limits. High-gain directional antennas can be used at both the transmitting and receiving ends, resulting in a significantly enhanced signal-to-noise ratio (SNR), and improved data security for long-range mm-wave point-to-point (P2P) communications with a line of sight link [2]. However, directional antennas with narrow beam are not viable for multi-user communication as they only provide very limited spatial coverage. Phased array transceivers are promising a robust reliable wireless link at mm-wave. However, user mobility and environmental variations are essential factors that need to be considered. Although many works deploy analog beamforming, DBF is desired for user discovery and tracking which poses significant input/output (I/O) challenge.

Multi-antenna radios are emerging in BS, AP as well as space-constraint femtocells and UE (Fig.1.2), and thus designing a compact power-efficient multi-antenna radio is a high-impact interesting research topic. This dissertation proposes high-performance multiantenna wireless by adding FD feature to phased array/MIMO technologies and introducing an mm-wave TX array with a single-wire interface that addresses I/O challenge for DBF.

Figure 1.2: (a) Beamforming antenna array scenario at BS and UE [2] and (b) the antenna array configuration for 5G cellular mobile [3].

### 1.1 Full-Duplex Multi-Antenna Wireless

#### 1.1.1 Full-Duplex Wireless

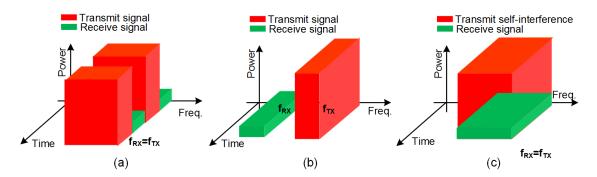

Current Wireless systems rely on duplexing to avoid SI. Bluetooth and WiFi are examples of transceivers that use time-division duplexing (TDD) by sending and receiving at nonoverlapping time slots (Fig.1.3(a)). Majority of today cellular bands use frequency-division duplexing (FDD) to separate the transmission and reception in the frequency domain [17] (Fig.1.3(b)). Full-duplex wireless, namely simultaneous transmission and reception at the same frequency, is an emerging technology that has gained attention due to its potential to double data throughput [18, 19], as well as provide other benefits in the higher layers such as better spectral efficiency, reducing network and feedback signaling delays, and resolving hidden-node problems to avoid collisions [19-22]. However, several challenges remain in the quest for high-performance integrated FD radios. TX power handling remains an open problem, particularly in FD radios that integrate a shared antenna interface. Recent integrated shared antenna interfaces that exhibit high power handling exploit SOI CMOS technologies and occupy substantial area [23]. Secondly, FD operation must be achieved across antenna VSWR variations and a changing EM environment. Finally, FD must be extended to multiantenna radios, including phased array and MIMO radios, as over the next decade, they are expected to play an essential role in the next generation of wireless networks.

Figure 1.3: Different multiplexing access methods: (a) time-division (b) frequency-division (c) full-duplex [4].

The main challenge that single-input-single-output (SISO) FD radios face is the tremendous amount of SI from the TX to its own RX. The SI can be mitigated through the magnetic-free integrated circulators at RF [11, 12, 23–25] and mm-wave frequencies [26, 27] as the shared antenna interface, reciprocal electrical-balance duplexers [28–31], polarizationbased antenna interfaces [32, 33], active antenna duplexers [34], and analog RF/baseband cancellers [35–41]. Finally, to form an FD link, digital cancellers are also required in addition to analog ones to meet stringent SIC requirements [20, 35, 42, 43].

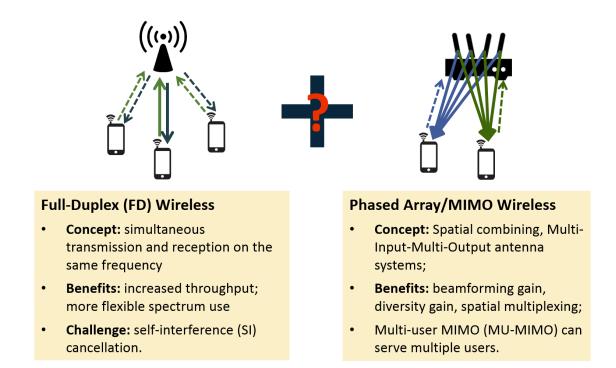

#### 1.1.2 Why Multi-Antenna Full-Duplex?

Integrating FD operation with multi-antenna technologies is an important research challenge. Fig. 1.4 depicts the concept of FD multi-antenna radios where FD wireless is a key to spectrum efficient wireless communication and Phased Array/MIMO wireless is vital to form a high data rate link using beamforming and diversity/capacity gain. Combination of these two technologies can result in higher data rate and spectrum efficiency, while substantially enhancing the link range.

#### 1.1.3 Challenges

#### 1.1.3.1 Power Handling

Integrating FD operation is challenged not only by the SI from each TX to its own RX, but also CT-SI between antennas (Fig. 1.5). In an N-element FD phased array transceiver, in the worst case in each RX channel, the SI and CTSI can add up constructively to increase by an amount equal to the TX array gain  $(N^2)$ , and then add up constructively after RX beamforming to increase by an amount equal to the RX array gain  $(N^2)$ , resulting in a total increase of  $N^4$  relative to a single-element transceiver. Similarly, in an N-element FD MIMO transceiver, assuming orthogonal coding, the total SI and CT-SI power can be N times larger than the single-element case (assuming similar power level for the SI and CT-SI across all elements). This can substantially limit the FD phased array/MIMO transceiver power

Figure 1.4: Integrating FD operation with MIMO technology can result in higher data rate and spectrum efficiency for the next generation of wireless communication.

handling compared to the single-element case and alleviate benefits gained from deploying a multi-antenna system.

Figure 1.5: SI and CT-SI in full duplex (a) single-antenna (b) and multi-antenna wireless.

#### 1.1.3.2 Canceller Complexity

In an FD MIMO transceiver, CT-SI between each TX-RX pair needs to be suppressed. As depicted in Fig.1.6, a cancellation path,  $H_{ij}$ , is required from each TX to all other RXs. Therefore, an N-element FD MIMO transceiver requires  $N^2$  cancellation paths, which means the complexity of canceller in terms of associated area, power dissipation and noise penalties grow as  $O(N^2)$ . This is both area- and power-hungry, and not feasible for radios with a large number of elements. Furthermore, the noise from SI and CT-SI cancellation paths can accumulate and further degrades the radio sensitivity level.

Figure 1.6: In an N-element FD MIMO radio, a cancellation path for each TX-RX pair is required, and so the canceller complexity grows as  $O(N^2)$ .

#### 1.1.4 Prior Works

To our best of knowledge, there is no prior integrated FD phased array/MIMO transceiver. However, there have been a few works on the system level using off-the-shelf discrete components shown in Fig. 1.7. In [44], correlation between SI and CT-SI is exploited to share cancellation delay taps between SI and CT-SI cancellation paths (Fig. 1.7(a)). This is based on a simple idea that cross-talk signal experiences slightly higher delay compared to the SI. This enables FD MIMO canceller complexity to increase linearly with the number of elements. However, this radio uses bulky delay lines and there is no phase control on the delay taps. SoftNull [45] is another technique that divides number of available antennas between TX and RX and sacrifices MIMO degree of freedom (DoF) on TX side DBF to achieve SIC (1.7b). However, this work does not employ a shared antenna interface for TX/RX which relaxes the SI and CT-SI levels that must be cancelled and does not feature analog TX or RX cancellers, with SI and CT-SI cancellation only achieved through DBF. In [46], an FD 2-element MIMO radio is presented for LTE applications using 4 multi-tap cancellers to suppress the SI and CT-SI in the RF domain 1.7c). However, this radio does not address the  $N^2$  challenge, requires bulky delay cells, and also does not use a shared antenna interface between TX and RX.

## 1.2 A 60 GHz 4-Element MIMO TX With A Single-Wire Interface

#### 1.2.1 Motivation

Wireless radios at mm-wave frequencies enable the high-speed link for portable devices due to the wide-band spectrum available. However, the high path loss is the main challenge that hinders forming an mm-wave link. Large-scale mm-wave phased arrays with hundreds of elements have been demonstrated with analog beamforming [47, 48] resulting in one IF signal, but MIMO array enables

Figure 1.7: Prior system level FD MIMO transceivers using discrete components: (a) FD  $3\times3$  MIMO with shared delay structure to reduce the canceller complexity (b) FD MIMO using DBF only on the TX side, and (c) FD 2-element MIMO radio for LTE applications using 4 RF bulky multi-tap cancellers to suppress the SI and CT-SI.

- Multiple user or data stream using spatial multiplexing [49];

- Enhanced radar resolution through the virtual array concept [50];

- DBF for user discovery and tracking in highly mobile scenarios.

However, DBF needs per-element digitization which results in a significant I/O challenge at mm-wave with large signal bandwidth.

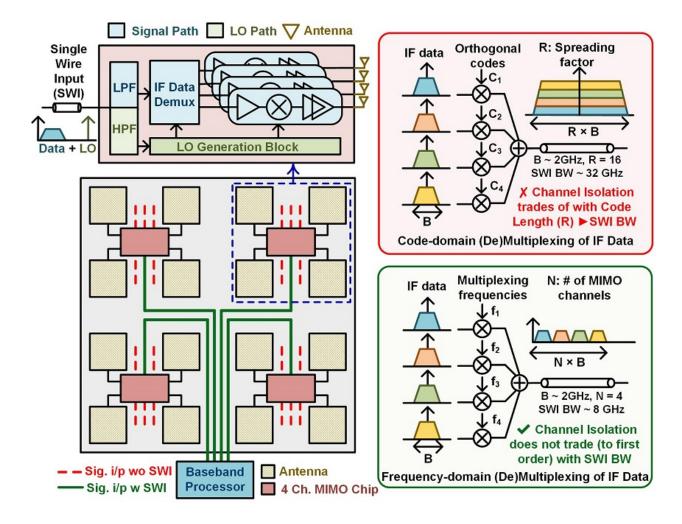

Large-scale mm-wave arrays can be formed by tiling integrated phased array ICs with single or multi-beam I/O. Since practical implementation challenges lead to separate ICs as mm-wave RF radio part and ADC/DSP, a single coaxial interface for scalable phased arrays/MIMO mm-wave unit is desired. To preserve MIMO information, the received signal from each element in a MIMO RX/TX should be transported to ADC/DSP IC for DBF and vice versa, and thus, signals from each element should co-exist on a single-wire interface through serializing the data or multiplexing in time, frequency or code-domain.

SERDES are traditionally being used in computing systems and networks to serialize multiple streams of data on a single connection. However, these circuits along with required clock data recovery are power- and area-hungry. In addition to data, the clock signal is also required to be routed to mm-wave RF front-end ICs, as the mixers in all the elements in a MIMO radio need to be synchronized.

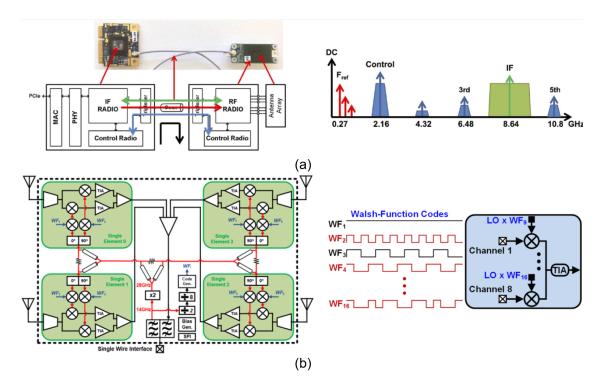

### 1.2.2 Prior Works

In [5], a 16-element TX/RX 60 GHz transceiver that achieves high throughput and enables simple integration into laptops and other consumer electronic devices. The transceiver is a dual-chip split-IF architecture and uses a single coaxial cable interface (Fig. 1.8). A fixed-IF architecture is employed, and the 8.64 GHz IF signal is passed over the coaxial cable along with a 270 MHz reference signal for a front-end phase-locked loop (PLL), a 2.64 GHz control signal and DC power. Although this work simplifies the interface for phased arrays, due to analog beamforming prior to the digitization its impossible to have multi-beam and spatial information is lost.

A 28 GHz 4-element MIMO RX in 65 nm CMOS with a single-wire interface that multiplexes the BB signals of all elements and the LO reference through code-domain multiplexing is demonstrated in [6]. Walsh-function is used which spread each element received IF signal with low cross-code leakage. The approach is validated through DBF after de-multiplexing of the BB signals from the single-wire. However, the high spreading ratio of 16 used in this work results in high occupation of the spectrum and requires power-consuming digitization, and thus this solution is not suitable for transceivers with multi-GHz of IF data bandwidth.

Figure 1.8: Prior transceivers with single-wire interface: (a)A 60GHz TX/RX with single coaxial interface for low-cost integration in PC platform [5] (b)A 4-element 28 GHz mm-wave MIMO array with single-wire interface using code-domain multiplexing [6].

### 1.2.3 Single-Wire Interface Using Frequency-Division Multiplexing

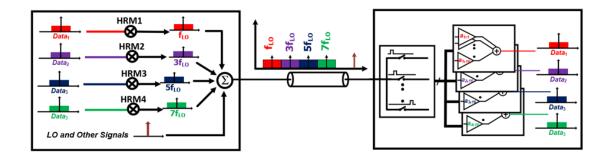

In this dissertation, a 4-element MIMO TX mm-wave IC with a single-wire interface is proposed which receives the IF signals that are frequency-division multiplexed on harmonics of each other shown in Fig. 1.9 along with 30 GHz reference. A harmonic rejection mixer is deployed to downconvert and separate each element IF signal from the single-wire interface to zero-IF frequencies and finally upconvert to 60 GHz and amplify on each element. The 60 GHz WiGig is a potential application in which each channel bandwidth is around 2 GHz which makes code-domain multiplexing similar to [6], not a viable solution as that results in 32 GHz spreaded data bandwidth which requires high-speed power-hungry ADC and digital processing.

Figure 1.9: Single-Wire interface between DSP unit and mm-wave unit using frequencydivision multiplexing

### **1.3** Organization

This thesis is organized as follows. To demonstrate high-performance multi-antenna radios, first, FD phased-array is discussed. Then, FD MIMO is presented and finally, an mm-wave MIMO TX with a single-wire interface is discussed and the dissertation is concluded.

Chapter.2 presents how phased array beamforming can be combined with FD operation to achieve wideband SI suppression with minimal link budget penalty in terms of TX and RX array gains. The detailed analysis of system-level requirements for FD phased-array wireless links and circuit implementation is presented. Furthermore, an optimization problem to jointly maximize the TX and RX beamforming gains subject to the constraint on the amount of achieved wideband RF SIC is formulated. A 65 nm CMOS scalable 4-element FD phased array circ.-RX which utilizes the multiple phases naturally available in the N-pathfilter circulators to perform beamforming and SI cancellation is implemented. An 8-element FD phased-array based on the described ICs achieves (i) 50 dB overall RF array SIC over 16.25 MHz, WiFi-like, bandwidth with less than 3.5/3 dB penalty in TX/RX array gains, and (ii) 100 dB overall array SIC including digital SIC, supporting +16.5 dBm TX array power handling.

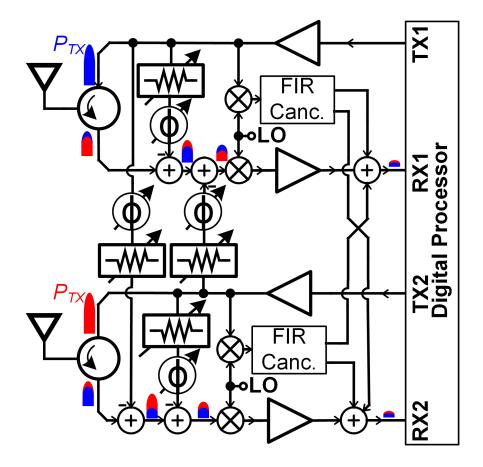

Chapter.3 presents an integrated FD 2-element MIMO circ.-RX array exploiting MIMO RF and BB SIC which address the complexity associated with FD MIMO operation by sharing delay cells and enhance power handling using bootstrapping technique. In this chapter, first, challenges and proposed solutions associated with implementing FD MIMO radios are illuminated. Then, implementation details are described and finally measurement results are discussed. The 65 nm CMOS prototype exhibits (i) up to 35/45 dB average SIC across 40/20 MHz BW, (ii) more than 42/53 dB average CT-SIC across 40/20 MHz BW with <2.1 dB degradation in RX NF, and (iii) overall TX power handling of +14 dBm enabled by clock bootstrapping.

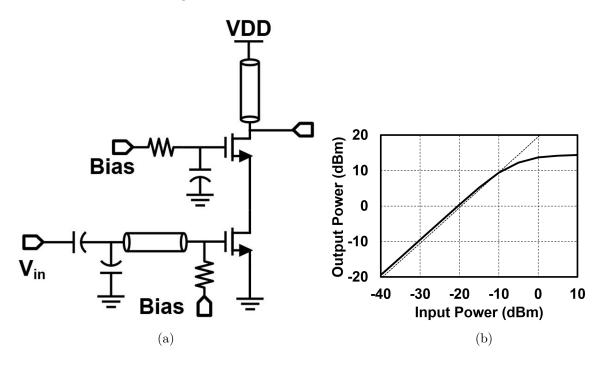

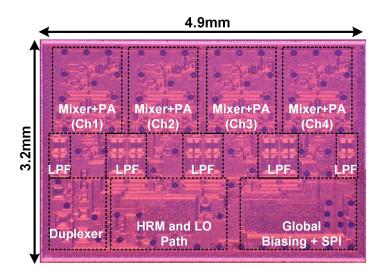

Chapter.4 presents a 60 GHz 4-element MIMO TX with a single-wire interface that receives the BB signals multiplexed on a single-wire and LO reference through frequencydivision multiplexing. A two-stage 16-phase harmonic rejection mixer is deployed to downconvert IF signals of each element to zero-IF frequencies. Then, a fifth-order low-pass filter is used to reject the higher harmonics and clean the spectrum mask. Finally, each IF signal is upconverted to 60 GHz using a Gilbert-cell based mixer and amplified using a two-stage stacked PA structure. The proposed structure is designed and taped-out in 45 nm RFSOI CMOS. Measurement results demonstrate (i) >20 dB gain in each channel with (ii) >30 dB inter-channel isolation, (iii) >8.8 dBm output -1 dB compression point and >9.1 dBm output saturation power.

Chapter.5, finally, concludes the dissertation with a summary of the key technical contribution and suggestion for future research directions.

## Chapter 2

## **Full-Duplex Phased Array Wireless**

The phased array can reject spatial interference and provide coherent beamforming gain which can substantially increase the range in silicon-based radios that are limited in TX power handling and RX noise perspective. Furthermore, FD wireless can potentially double the data throughput by simultaneously transmitting and receiving at the same frequency, and can provide benefits on higher layers such as better spectral efficiency, reducing network, feedback signaling delays, and resolving hidden-node problems to avoid the collision.

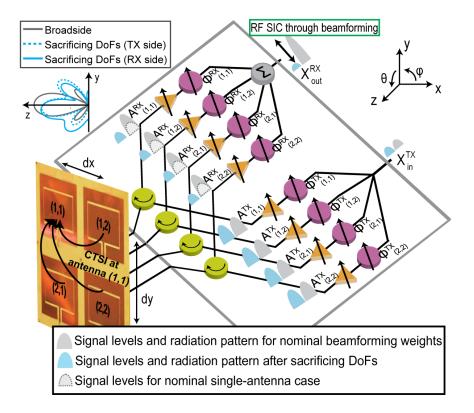

In this chapter, we present how phased array beamforming can be combined with FD operation to achieve wideband SI suppression with minimal link budget penalty in terms of TX and RX array gains [51]. FD phased array operation is extremely challenging as not only the SI from each TX to its own RX needs to be cancelled, but also CT-SI between each TX-RX pair need to suppressed, as shown in Fig. 2.1. Beamforming DoF are re-purposed to achieve SIC without any explicit cancellation circuitry. We present a detailed analysis of system-level requirements for the FD phased array wireless links and circuit implementation. We then formulate an optimization problem with an objective to jointly maximize the TX and RX beamforming gains subject to the constraint on the amount of achieved RF SIC across wideband. A 65 nm CMOS scalable 4-element FD phased array circ.-RX is proposed which utilizes the multiple phases naturally available in the N-path-filter circulators to perform beamforming and SI cancellation. Finally, the concept is validated through measurements

Figure 2.1: FD N-path-filter-based circulator-receiver conceptual architecture and block diagram.

performed on an 8-element FD phased array transceiver by tiling two of the described circ.-RX ICs and a TX beamformer implemented using off-the-shelf discrete components.

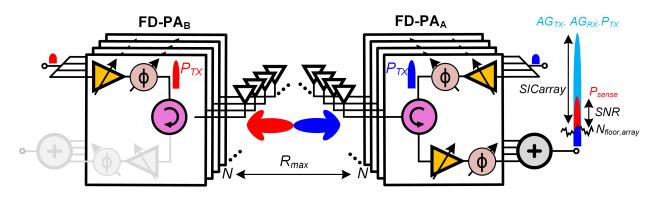

### 2.1 FD Phased Array System Requirements

### 2.1.1 Array SIC

Two N-element FD phased array circ.-RXs forming an FD link are depicted in Fig. 2.2. Although the SIC after beamforming depends heavily on the antenna response, in the worst case in each RX channel, the SI and CT-SI can add up constructively to increase by an amount equal to the TX array gain  $(N^2)$ , and then add up constructively after RX beamforming to increase by an amount equal to the RX array gain  $(N^2)$ , resulting in a total increase of  $N^4$  relative to a single-element transceiver. Hence, while phased array beam-

Figure 2.2: FD phased array link budget.

forming provides  $N^2$  increase in the array gain on both TX/RX sides, it can also increase the total SI at the RX output after beamforming by the same amount. Therefore, we define the array SIC similar to the single-element counterpart with the addition of TX/RX array gain:

$$SIC_{array,dB} = P_{TX} \cdot AG_{TX} \cdot AG_{RX}/SI,$$

(2.1)

where  $P_{\text{TX}}$  is the TX power level at each element, SI is the residual SI power level and  $AG_{\text{TX/RX}}$  are TX/RX array gains.

In single-input-single-output (SISO) transceivers, the required SIC to suppress the SI level down to the noise level is equal to  $SIC_{SISO} = P_{TX}/N_{floor,SISO}$  where  $N_{floor,SISO} = kT \cdot BW \cdot NF$ . In an N-element phased array, the required SIC is given by  $SIC_{array} = P_{TX} \cdot AG_{TX} \cdot AG_{RX}/N_{floor,array}$ , where  $N_{floor,array} = kT \cdot BW \cdot NF \cdot N$ . Hence, the challenging required SIC in the array scenario is  $AG_{TX} \cdot AG_{RX}/N$  (as high as  $N^3$ ) times larger than the SISO case.

#### 2.1.2 Link Budget Calculations and FD operation

The desired received signal in an N-element FD phased array TRX link after the beamforming is:

$$P_{\rm RX,array} = \frac{P_{\rm TX} \cdot AG_{\rm TX} \cdot G_{\rm TX} \cdot AG_{\rm RX} \cdot G_{\rm RX}}{FSPL \cdot IL},$$

(2.2)

| Metric                                                                            | Calculation                                                          | Value    |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------|----------|

| Frequency (f)                                                                     |                                                                      | 730MHz   |

| # of ANT Elements (N)                                                             |                                                                      | 8        |

| TX power per Elements ( $P_{TX}$ )                                                |                                                                      | 1dBm     |

| TX/RX Array Gain (AG <sub>TX/RX</sub> )                                           | 20.Log <sub>10</sub> (N)-3dB                                         | 15dB     |

| TX/RX ANT Gain (G <sub>TX/RX</sub> )                                              |                                                                      | 6dBi     |

| Bandwidth (BW)                                                                    |                                                                      | 16.26MHz |

| RX Noise Figure (NF)                                                              |                                                                      | 5dB      |

| RX Array Noise Floor referred<br>to ANT Input ( <i>N</i> <sub>floor,array</sub> ) | kT.BW.NF.N                                                           | -88dBm   |

| Required SNR                                                                      |                                                                      | 20dB     |

| RX Array Sensitivity referred<br>to ANT Input (P <sub>sense</sub> )               | 2 . SNR . N <sub>floor,array</sub>                                   | -65dBm   |

| Implementation Losses (IL)                                                        |                                                                      | 10dB     |

| Supported Range (R <sub>max</sub> )                                               | $\frac{\lambda}{4\pi}\sqrt{P_{TX}AG_{TX}G_{TX}AGRXGRX.IL/P_{sense}}$ | 2.6km    |

| Required Array SIC (SIC <sub>array</sub> )                                        | $P_{TX}AG_{TX}AG_{RX}/N_{floor,array}$                               | 119dB    |

Table 2.1: FD phased array link budget.

where  $G_{\text{TX/RX}}$  are TX/RX antenna gains, FSPL is the free space propagation loss equal to  $(4\pi \cdot R \cdot f/c)^2$  and IL is a margin considered for practical implementation losses  $(R, f, \text{ and } c \text{ are the range, the operation frequency, and the light speed, respectively).$

Minimum required signal to noise ratio (SNR) determines the radio sensitivity level  $(P_{\text{sense}} = 2 \cdot SNR \cdot N_{\text{floor}, \text{array}})$  where the factor of 2 covers the SNR degradation because of the residual SI. The maximum range that the link can support  $(R_{\text{max}})$  can be calculated as:

$$R_{\rm max} = \frac{\lambda}{4\pi} \sqrt{P_{\rm TX} A G_{\rm TX} G_{\rm TX} \cdot A G_{\rm RX} G_{\rm RX} \cdot I L / P_{\rm sense}},$$

(2.3)

This clearly shows benefit of array gain in increasing link range. Table. 2.1 summarizes link budget calculation. Based on our calculations, for an 8-element 730 MHz array with +1 dBm TX power per element ( $P_{\text{TX}}$ ), 6 dBi antenna gain, 15 dB TX and RX array gains ( $AG_{\text{TX}}$  and  $AG_{\text{RX}}$ , 3 dB degraded from the ideal 18 dB array gain due to the need to achieve SIC), 16.25 MHz bandwidth (BW), 5 dB RX noise figure (NF), 20 dB required Signal-to-Noise Ratio (SNR) and 10 dB implementation losses, one can establish an FD link over a distance of 2.6 km. This shows that phased arrays can substantially enhance range in silicon-based FD transceivers which are limited in power handling, make them suitable for both space-constrained WiFi access points and small cell base stations.

### 2.2 SIC via Beamforming

An N-element phased array transceiver with a shared antenna interface, and amplitude and phase controls on each TX and RX element features overall 2(N-1) complex-valued DoF on TX and RX sides ((N-1) DoF on each side). These DoF are a representation of the complexvalued weights (amplitudes and phases) of each element relative to that of the first element. Typically, these DoF are employed to form the beams toward desired signal directions, and to minimize interference to/from nearby radios by pointing nulls towards them or suppressing the side-lobes of the radiation pattern. Alternatively, a few beamforming DoF at the TX and RX can be repurposed so that total SI is suppressed after RX beamforming at the expense of some TX and RX beam characteristics, such as a few nulls and/or some gain loss in the beam-pointing direction(s).

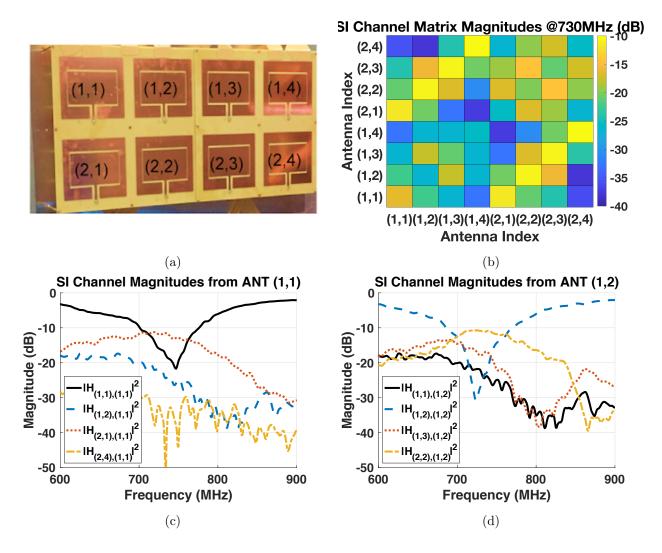

Fig. 2.3 depicts our implementation of a 2×4 rectangular array of slot loop antennas at 730 MHz with  $\lambda/2$  spacing, whose SI channel matrix in the frequency domain is denoted by  $\mathbf{H}^{\mathrm{SI}}(f) = [H^{\mathrm{SI}}_{(m',n'),(m,n)}(f)] \in \mathbb{C}^{8\times8}$ , where  $H^{\mathrm{SI}}_{(m',n'),(m,n)}(f)$  is the frequency response of the (CT-)SI channel from the  $(m, n)^{\mathrm{th}}$ -element to the  $(m', n')^{\mathrm{th}}$ -element. As Fig. 2.3 shows, the antenna matching is around -20 dB at the center frequency of 730 MHz (which would be the SI channel for each element if the circulators were ideal), while the magnitude of the SI channel from the closest element can be as high as -10 dB (e.g.,  $|H_{(2,1),(1,1)}|$ ). Moreover, a vertical pair of elements have higher SI channel magnitude than a horizontal pair of elements (e.g.,  $|H_{(2,1),(1,1)}| > |H_{(1,2),(1,1)}|$  at 730 MHz).

Let x(f) be the transmit signal in the frequency domain, and  $\mathbf{w}^{\text{TX}} = [w_{(m,n)}^{\text{TX}}]$  and  $\mathbf{w}^{\text{RX}} = [w_{(m,n)}^{\text{RX}}]$  be the complex-valued TX and RX beamforming weight vectors, respectively. Then, the phased array SI after TX and RX beamforming, denoted by  $x^{\text{SI}}(f)$ , is given by

$$x^{\mathrm{SI}}(f) = (\mathbf{w}^{\mathrm{RX}})^{\top} \mathbf{H}^{\mathrm{SI}} \mathbf{w}^{\mathrm{TX}} \cdot x(f), \qquad (2.4)$$

where  $(\cdot)^{\top}$  denotes the transpose of a vector.

Consider a 3D coordinate system where the  $2 \times 4$  rectangular array is located on the x-y plane. We denote the TX and RX beamforming directions by the azimuth and elevation an-

Figure 2.3: (a) A 2×4 8-element antenna array at 730 MHz with  $\lambda/2$  spacing, (b) the measured SI channel magnitudes at 730 MHz, and (c)–(d) examples of measured SI channel magnitudes across frequency from antenna elements (1,1) and (1,2) to the adjacent elements, respectively.

gles  $(\phi, \theta)$  in a horizontal coordinate system. Then, the *far-field* array TX/RX beamforming pattern is given by

$$E^{\mathrm{TX/RX}}(\phi,\theta) = (\mathbf{s}^{\mathrm{TX/RX}}(\phi,\theta))^{\top} \cdot \mathbf{w}^{\mathrm{TX/RX}}$$

$$= \sum_{m} \sum_{n} w_{(m,n)}^{\mathrm{TX/RX}} \cdot e^{j\pi[(m-1)\cos\phi\cos\theta + (n-1)\sin\phi\cos\theta)]},$$

(2.5)

Figure 2.4: (a)–(b) Simulated TX/RX array patterns in the x-z and y-z planes while achieving 60 dB array SIC across 20 MHz with 3 dB array gain degradation in the TX/RX broadside beam-pointing directions, (c) simulated array SIC where at least 60 dB SIC is guaranteed to be achieved across 720–740 MHz, (d) simulated TX/RX array gain for a desired array SIC based on solving an optimization problem using the measured SI channels depicted in Fig. 2.3.

where the TX/RX beam steering vector in the spatial direction of  $(\phi, \theta)$  is given by

$$\mathbf{s}^{\mathrm{TX/RX}}(\phi,\theta) = \left[s_{(m,n)}^{\mathrm{TX/RX}}(\phi,\theta)\right]$$

$$= \left[e^{j\pi\left[(m-1)\cos\phi\cos\theta + (n-1)\sin\phi\cos\theta\right]}\right].$$

Figure 2.5: (a)–(b) spatial distribution of the simulated sum TX and RX beamforming gain loss for achieving the desired RF SIC across 20 MHz and 40 MHz bandwidth.

The goal is to achieve wideband SIC in the *near-field* (2.4) with minimal penalty in the TX/RX beamforming gains in the *far-field* (2.5).

Denote by  $(\phi^{\text{TX/RX}}, \theta^{\text{TX/RX}})$  the main TX/RX beam-pointing direction in which the TX/RX beamforming gain needs to be maximized. We formulate an optimization problem where the objective is to maximize the TX and RX array gains, subject to the constraint that a desired amount of array SIC is achieved after TX and RX beamforming, i.e.,

$$\max_{\mathbf{w}^{\mathrm{TX}},\mathbf{w}^{\mathrm{RX}}} : AG_{\mathrm{TX/RX}},$$

(2.6)

subject to :  $|(\mathbf{s}^{\mathrm{TX/RX}}(\phi^{\mathrm{TX/RX}}, \theta^{\mathrm{TX/RX}}))^{\top} \cdot \mathbf{w}^{\mathrm{TX/RX}}|^{2} \ge AG_{\mathrm{TX/RX}} |(\mathbf{w}^{\mathrm{RX}})^{\top} \mathbf{H}^{\mathrm{SI}}(f) \mathbf{w}^{\mathrm{TX}}|^{2} \le \chi, \forall f,$  $|w_{m,n}^{\mathrm{TX/RX}}|^{2} \le 1, \forall m, n.$

Specifically, the first constraint ensures minimal degradation in both the TX/RX array gains in the desired TX/RX beam-pointing direction (compared to the maximal TX/RX array gains without sacrificing any DoFs). The second constraint guarantees at least  $\chi_{dB} = 10 \log_{10}(\chi)$  dB SIC across the desired bandwidth so that the total RF SIC is ( $\chi_{dB} + AG_{TX} + AG_{TX}$ )

$AG_{RX}$ ) dB. The last inequality sets the normalization constraint on each TX/RX beamforming weight.

We evaluated this idea through simulations using the measured array SI channel (see Fig. 2.3), where the optimization problem is solved using the MATLAB nonlinear optimization solver. We set  $\chi = 10^{-3}$  so that the total array SIC is given by  $(30 + AG_{TX} + AG_{RX})$  dB. The results are summarized in Fig. 2.4 and 2.5. In the simulation, the TX/RX array gains are maximized for broadside beamforming (i.e.,  $\theta = 90^{\circ}$ ) subject to the constraint that at least 60 dB array SIC is achieved between 720–740 MHz. Figs. 2.4(a) and 2.4(b) show that an array gain degradation of only 3 dB compared with the maximal array gain of  $N^2 = 18$  dB can be maintained while achieving 60 dB array SIC across 20 MHz. Moreover, Fig. 2.4(d) shows the trade-off between the maximum achievable TX/RX array gain and different amounts of desired array SIC across 20 MHz and 40 MHz, respectively.

To further investigate the performance of our proposed approach for different TX/RX beam-pointing directions, Figs. 2.5(a) and 2.5(b) show the distribution of the sum of TX and RX beamforming gain loss with varying TX/RX beamforming in the spatial direction of  $(\phi, \theta)$  (i.e., both the TX and RX beam-pointing directions are  $(\phi, \theta)$ ). The results show that the sum beamforming gain loss never exceeds 6.0 dB and 6.6 dB for achieving an array SIC of 60.0 dB and 59.4 dB over 20 MHz and 40 MHz bandwidth, respectively. Moreover, when beamforming in the directions with stronger SI (e.g., in the array broadside due to higher circulator TX-RX leakage or in the direction of adjacent antenna elements due to strong couplings), a higher of TX and RX beamforming gains need to be sacrificed to achieve the desired performance. Similar approaches can also be applied to explore the scenarios with different TX and RX beam-pointing directions and is a subject of our future work.

In general, four important features must be highlighted: (i) SI suppression is essentially achieved in the *spatial domain* through a trade-off between near-field SI nulling and farfield beamforming without any explicit cancellers and associated power consumption, since the RX/TX beamformers are repurposed, (ii) the SI suppression is *wideband* since different antenna coupling paths are cancelling each other, as opposed to having an IC canceller duplicate the frequency characteristics of an antenna coupling path, (iii) the beamforming-FD trade-off can be *dynamically adapted* in the field, with the number of DoF sacrificed dependent on the required SI cancellation, bandwidth, external interferers that need to be nulled, etc., and (iv) the trade-off between FD and beamforming will become more favorable for larger arrays. In [52], we further investigate this problem and develop efficient algorithms for cases with large-scale arrays (e.g., N = 36/72).

# 2.3 Circuit Implementation

## 2.3.1 Integrated Circ.-RX Phased Array RX

#### 2.3.1.1 Shared Antenna Interface

This work deploys the N-path-filter-based combined-circ.-RX described in [53] as a sharedantenna interface that merges a commutation-based linear periodically time-varying (LPTV) non-magnetic circulator with down-converting mixer and directly provides the BB signals (Fig. 2.6). The availability of 8-phase at the BB node of N-path-filter further simplifies the beamforming. The 50  $\Omega$  quarter wavelength transmission lines are implemented using one capacitor-inductor-capacitor section with off-chip inductors. Each circ.-RX requires two sets of 8-phase non-overlap clock with 90° phase shift to drive the switches on each side of N-path-filter. The N-path-filter deploys 8-path to increase the ANT-RX BB recombination gain and achieve harmonic cancellation for the 3rd and 5th harmonic. The resistance of transistor used as a switch is around 3.5  $\Omega$ , and the source/drain of the FETs are biased at 0.6 V and DC coupled to BB gm-cells. The gate of the switches are AC coupled to buffers and are biased at 0.75 V (DC level of 12.5% pulse swinging from 0.6 V to 1.8 V). An input clock at 4 times the operating frequency ( $f_{clk}$ ) provides eight output phases in the Johnson-counter-based divide-by-4 in each circulator.

Figure 2.6: Combined non-magnetic non-reciprocal circulator-receiver deployed as integrated shared antenna interface.

### 2.3.1.2 Phased Array RX

A scalable 65 nm CMOS 730 MHz 4-element circ.-RX phased array is implemented (Fig. 2.7). The circ.-RX as described before provides 8-phase BB nodes which simplifies the RX beamforming, four 8-bit (1-bit sign and 7-bit amplitude) programmable differential  $g_m$ -cells are connected to each BB node of each element circ.-RX and then combined in the current domain across all 4 elements into low-input impedance IQ TIAs enabling Cartesian beamforming. The TIAs are implemented using two-stage op-amps. Therefore, the complex-valued weight (phase and gain) applied to each element and summation across all the elements are performed simultaneously while maintaining low noise and high linearity. Besides, scalability across multiple chips is feasible using the low input impedance combining point at the TIA input. By connecting a second chip's low impedance node to the first one, and turning off the second chip's TIA, and the current from the  $g_m$  cells of the second chip can be combined into the TIAs of the first chip in the current domain (Fig. 2.8). Thanks to the low impedance

Figure 2.7: Block/Circuit Diagram of scalable 4-element FD circ.-RX phased array.

node provided by the TIA of the main chip, board trace capacitance does not degrade BW performance.

Figure 2.8: Tiling two circ.-RX phased array to form 8-element FD circ.-RX phased array.

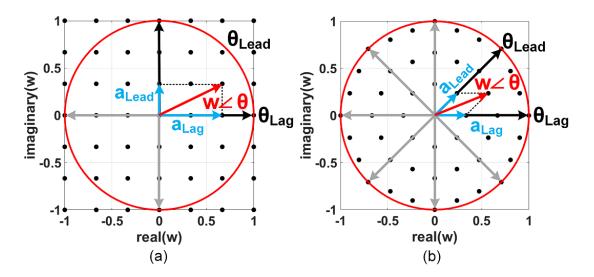

Although typical Cartesian vector modulator covers full 360° using 0°, 90°, 180°, and 270° phases, this work deploys oversampling vector modulator using 8-phases (0°, 45°, ..., 315°) provided by BB nodes of N-path filter. Fig.2.9 shows vector modulation using 3-bit resolution (1-bit sign and 2-bit amplitude) where oversampled vector modulation (8 phases rather than 4 phases) is beneficial in terms of complex-gain accuracy [54], noise and power, but increases the circuit complexity and the associated area consumption. If the desired weight on an element is vector  $w \angle \theta$ , the amplitude and phase can be generated using two adjacent phases (lag and lead),  $a_{\text{lag}} \angle \theta_{\text{lag}}$  and  $a_{\text{lead}} \angle \theta_{\text{lead}}$  shown in Fig. 2.9, and solving for real and imaginary part of  $a_{\text{lag}} \angle \theta_{\text{lag}} + a_{\text{lead}} \angle \theta_{\text{lead}} = w \angle \theta$ , we can find amplitudes for lag and lead vectors equal to:

$$a_{\text{lag}} = w \left| \frac{\cos(\theta) \cdot tg(\theta_{\text{lead}}) - \sin(\theta)}{\cos(\theta_{\text{lag}}) \cdot tg(\theta_{\text{lead}}) - \sin(\theta_{\text{lag}})} \right|,$$

(2.7)

$$a_{\text{lead}} = w \left| \frac{\cos(\theta) \cdot tg(\theta_{\text{lag}}) - \sin(\theta)}{\cos(\theta_{\text{lead}}) \cdot tg(\theta_{\text{lag}}) - \sin(\theta_{\text{lead}})} \right|.$$

(2.8)

The calculated amplitude is rounded to nearest integer to program the  $g_m$ -cells. If only the two adjacent vectors are not used, vectors are not orthogonal and mapping from desired vector to each phase amplitude is not straight forward and can be found using exhaustive search or  $\Sigma\Delta$  algorithm [54].

Figure 2.9: Beamforming using 3-bit vector modulator: (a) 4-phase (b) 8-phase.

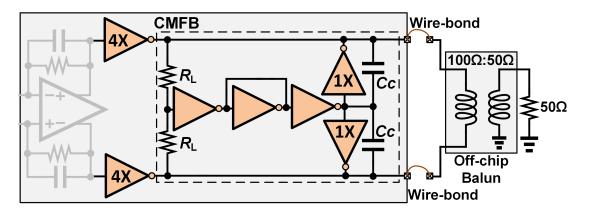

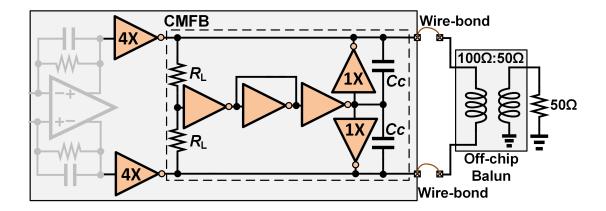

An inverter-based amplifier is used to buffer output of TIA from off-chip IF balun (Fig. 2.10) due to their proper linearity performance at low-voltage supplies. Commonmode feedback circuitry similar to [55] is deployed to ensure proper output DC value. Buffer FETs are sized to provide unity gain with 100  $\Omega$  differential load. The buffer needs to be loaded with 100  $\Omega$  all the time due to its high intrinsic gain to avoid instability. The 2.5 pF compensation capacitors ( $C_c$ ) are used to ensure common-mode stability and large 7.8 k $\Omega$ resistors ( $R_L$ ) are used to extract output DC voltage value.

Figure 2.10: Inverter-based output buffer with common-mode feedback.

#### 2.3.1.3 Clock Distribution

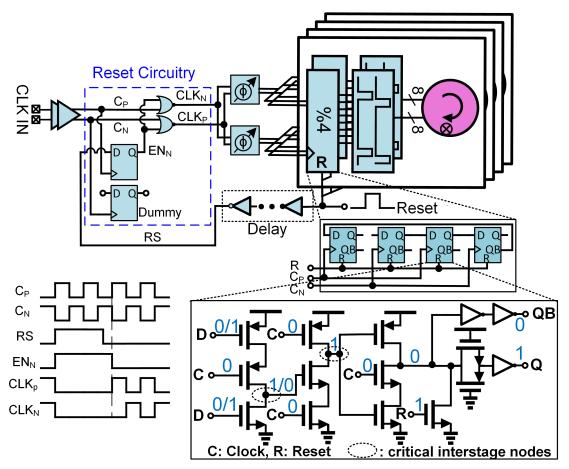

Clock distribution is challenging in any multi-antenna system due to the phase uncertainty that can cause between the elements. Fig. 2.11 presents the clock distribution between 4element and divider circuit detail and it's node voltage at the reset state. To ease the clock distribution two differential clock signal with  $4 \cdot f_{clk}$  frequency, is distributed on the chip between the 4-element symmetrically. These two clocks are phase-shifted through multiplexed digital delay cells with analog varactor-based fine-tuning to cover a range of  $\pm$  70° around the nominal phase setting at 730 MHz based on schematic simulations. To synchronize elements and remove the phase ambiguity upon restart, the divide-by-4 in all the elements should reset by the same signal and then triggered at the same rising edge of the clock. The dividers are implemented using TSPC flip-flops [17] and a pull-down NMOS is used at their output for reset purpose. Note flip-flop should not have any interstage node with unknown voltage ar reset state. When the reset signal is high, it resets the divide-by-4 in elements asynchronously and also keeps clock signals at the low level. When the reset signal toggle to the low value, the reset circuitry keeps clock signals level low until the first rising edge of the clock. This avoids undesirable clock edge and reset signal edge signal collision and passing skewed clock shapes to trigger the dividers. This makes sure that all of the elements dividers are exactly triggered with the same clock edge and are synchronized.

Figure 2.11: Circ.-RX phased array clock distribution and synchronize and reset circuitry.

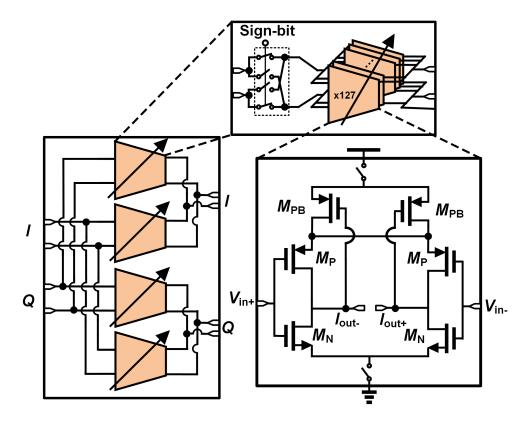

### 2.3.1.4 Programmable $g_m$ -cell

The implementation details of programmable  $g_m$ -cell is shown in Fig. 2.12. Each element eight BB phases are connected to four 8-bit programmable differential  $g_m$ -cells, a1-bit sign,and a 7-bit amplitude control. Each programmable  $g_m$ -cell consists of a cross switch circuit using complementary skim to flip differential phases and 127 switchable identical inverter-based  $g_m$ -cell in parallel to vary the amplitude. An inverter with shorted inputoutput is used to self-bias the input side of each phase  $g_m$ -cells. Inverter-based  $g_m$ -cell proposed in [56] is deployed which provides common-mode rejection and output self-bias using  $M_{PB}$  transistors. High/low threshold voltage (HVT/LVT) FETs are used for proper circuit bias.  $M_{PB}$  and  $M_P$  devices are respectively PMOS HVT and LVT devices with W/L= 800 nm/250 nm and  $M_N$  is HVT NMOS sized to W/L = 400 nm/250 nm. All  $g_m$ -cell outputs are connected to the summation point (TIA input) which is connected to pads and can see different impedance depending on the package and PCB parasitics making it hard to implement common-mode feedback around  $g_m$ -cells. Hence, using output self-bias  $g_m$ -cells is critical.

Figure 2.12: Circuit details of programmable g<sub>m</sub>-cells deployed for beamforming.

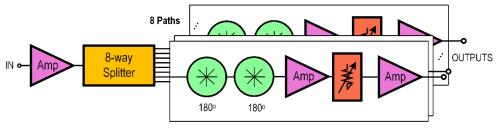

### 2.3.2 Phased Array TX

A custom-designed TX phased array is implemented using off-the-shelf discrete components (Fig. 2.13). The signal is divided into 8 channels after one stage of amplification. Each channel contains a cascade of two 180° phase shifters (Mini-circuits JSPHS-1000+) to cover the full 360° range, in series with two-stage of a high-linear low-noise amplifier (Mini-circuits HXG-122+) and programmable attenuator. This structure obtains amplitude control while maintaining good noise performance while a 7-bit attenuator (Skyworks SKY2343-364LF) can provide maximum attenuation of 31.75 dB with 0.25 dB resolution. Based on system calculation, the design can achieve up to 30 dB gain with an out-referred IP<sub>3</sub> as high as +31 dBm while the noise figure (NF) is less than 3.3 dB.

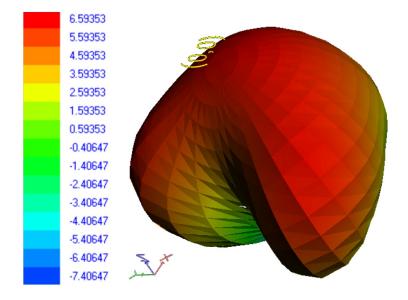

### 2.3.3 Slot Loop Antenna

The slot loop antenna structure is used due to their inherent wideband operation. The antenna is fabricated on the FR-4 PCB and can radiate on both frontside and backside direction. A metal sheet is used as a reflector at the back of the antenna array with quarter wavelength distance to redirect the radiation to the front side. The EM simulations using the Mentor Graphics IE3D shows antenna gain of 6.6 dB (see Fig. 2.14).

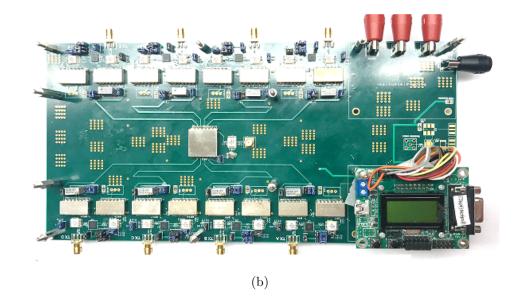

## 2.4 Experimental Results

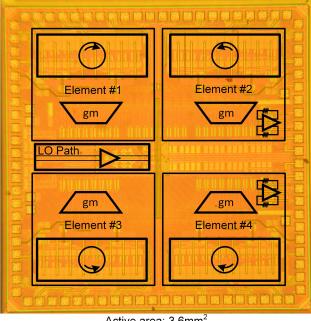

The chip microphotograph of the 65 nm CMOS 4-element FD circ.-RX phased array is shown in Fig. 2.15. It has a total active area of 3.6 mm<sup>2</sup> and is mounted in an 88-pin QFN package, and two chips are mounted on FR-4 PCB to realize an 8-element array for all the measurements.

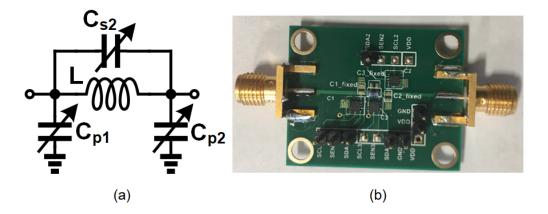

A custom programmable antenna tuner board using discrete components is implemented using a capacitor-(inductor/capacitor)-capacitor section shown in Fig. 2.16. Peregrine PE64906 digitally tunable caps are used which provide 0.9 pF to 4.6 pF capacitor with discrete 119 fF steps and Coilcraft 5.1 nH 0603HP is used as a fixed inductor. Simulation using ADS in-

Two 180 degrees phase-shifters has been used to provide full-360 degrees of phase-shift.

(a)

Figure 2.13: A custom-designed 8-element transmitter phased array: (a) Block diagram, and (b) PCB implementation.

cluding PCB parasitics shows that it can translate all antenna impedances inside the VSWR circle of 2 (return loss >10 dB) to an impedance inside the VSWR circle of 1.2 (return loss >20 dB).

## 2.4.1 Single-Element Circ.-RX Measurements

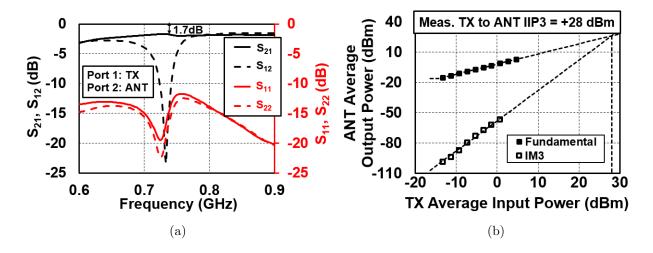

The measured two-port TX-to-ANT S-parameter of the circulator for a clock frequency of 730 MHz are shown in Fig. 2.17. Note that the RX is not available as a separate RF port, and

Figure 2.14: Slot loop antenna simulated radiation pattern.

Active area: 3.6mm<sup>2</sup>

Figure 2.15: FD N-path-filter-based circulator-receiver conceptual architecture and block diagram.

hence the circulator's ANT-to-RX and TX-to-RX performance cannot be measured directly using S-parameters. The circ.-RXs exhibit 1.7 dB TX-ANT loss, +28 dBm TX-ANT IIP3. Since the circulator is based on an 8-path filter, the signals have to be recombined to provide

Figure 2.16: Custom designed antenna tuner: (a) circuit diagram (b) PCB