# North Carolina Agricultural and Technical State University Aggie Digital Collections and Scholarship

Dissertations

**Electronic Theses and Dissertations**

2012

# Ultra-Low Power Wake Up Receiver For Medical Implant Communications Service Transceiver

James Griggs North Carolina Agricultural and Technical State University

Follow this and additional works at: https://digital.library.ncat.edu/dissertations

#### **Recommended Citation**

Griggs, James, "Ultra-Low Power Wake Up Receiver For Medical Implant Communications Service Transceiver" (2012). *Dissertations*. 19. https://digital.library.ncat.edu/dissertations/19

This Dissertation is brought to you for free and open access by the Electronic Theses and Dissertations at Aggie Digital Collections and Scholarship. It has been accepted for inclusion in Dissertations by an authorized administrator of Aggie Digital Collections and Scholarship. For more information, please contact iyanna@ncat.edu.

### ULTRA-LOW POWER WAKE UP RECEIVER FOR MEDICAL IMPLANT COMMUNICATIONS SERVICE TRANSCEIVER

by

James D. Griggs

A dissertation submitted to the graduate faculty in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY

### Department: Electrical and Computer Engineering Major: Electrical Engineering Major Professor: Dr. Numan S. Dogan Co-Advisor: Dr. Huseyin S. Savci

North Carolina A&T State University Greensboro, North Carolina 2012

## ABSTRACT

### **Griggs, James.** ULTRA-LOW POWER WAKE UP RECEIVER FOR MEDICAL IMPLANT COMMUNICATIONS SERVICE TRANSCEIVER. (Major **Professor: Numan Dogan),** North Carolina Agricultural & Technical State University.

The Medical Implant Communications Service (MICS) is an ultra-low power, unlicensed, mobile radio service for transmitting data in support of diagnostic or therapeutic functions associated with implanted medical devices. Medical devices that are implanted in the human body have limited size and battery capacity thus requires ultralow power circuitry. Due to the power consumed by the radio transceiver when the system is active, system level power saving techniques such as "sleep mode" is very essential to achieve "low-power". A wake up receiver (WuRx) is used to detect wireless traffic directed to a node's receiver and activate it upon detection, without compromising latency and energy dissipation by maximizing data transceiver sleep time.

However, the WuRx power consumption must be small compared to the node's main transceiver because it remains active at all times. Due to the always on nature on the WuRx, it sets a power dissipation floor for the entire system, which requires the receiver design to utilize low-power mixed-signal circuits in the RF front-end and baseband circuit blocks. The WuRx employs various architectural and circuit techniques to minimize power while maintaining an acceptable sensitivity to detect the wake-up signal and preserving data throughput.

This thesis explores the specific requirements and challenges for the design of a dedicated wake-up receiver for medical implant communication services equipped with a novel "uncertain-IF" architecture combined with a high – Q filtering MEMS resonator and a free running CMOS ring oscillator as the RF LO. The receiver prototype, implements an IBM 0.18 $\mu$ m mixed-signal 7ML RF CMOS technology and achieves a sensitivity of -62 dBm at 404MHz while consuming <100  $\mu$ W from a 1 V supply.

School of Graduate Studies North Carolina Agricultural and Technical State University

This is to certify that the Doctoral Dissertation of

James D. Griggs

has met the dissertation requirements of North Carolina Agricultural and Technical State University

Greensboro, North Carolina 2012

Approved by:

Dr. Numan. S. Dogan Major Professor Dr. Huseyin S. Savci Co-Advisor

Dr. Zhijian Xie Committee Member Dr. Alvernon Walker Committee Member

Dr. M. U. Bikdash Committee Member Dr. John Kelly Department Chairperson

Dr. Sanjiv Sarin Associate Vice Chancellor of Research and Graduate Dean © James Derrick Griggs 2012 All Rights Reserved

# **DEDICATION**

To My Heavenly Father. May you receive all the glory.

## **BIOGRAPHICAL SKETCH**

James Griggs, a native of Dothan, Alabama, a doctoral candidate in the Department of Electrical and Computer Engineering at North Carolina A&T State University. His research focuses on analog circuit/MEMS design for RF communication. In 2001 James graduated with honors from Tuskegee University, with a B.S. in Electrical Engineering. While attending Tuskegee, James was involved in many activities and was recognized as an Eminent Scholar as well as University Scholar for the College of Engineering, Architectural and Physical Sciences, which honors the top ranking exemplary students from each college.

After Tuskegee, James went to graduate school at the University of Michigan, Ann Arbor where he received his Master's degree in Electrical Engineering in 2004. During his graduate studies at Michigan, James was awarded a scholarship through The National GEM Consortium, a competitive fellowship geared towards identifying highly qualified graduate students within the STEM fields. James is passionate about science and technology and decided to complete his doctoral studies in electrical engineering at North Carolina A&T State University as a Title III fellow.

Throughout his academic career James has been involved in professional and social organizations including Eta Kappa Nu (Electrical Engineering Honor Society), IEEE, and Golden Key International Honor Society.

### ACKNOWLEDGEMENTS

First giving thanks to my Lord and Savior Jesus Christ who has sustained me all of my life.

As for my research I first would like to thank many individuals for their assistance and support. First I would like to thank my advisor, mentor and friend Dr. Numan S. Dogan for his support and guidance throughout my time at North Carolina A&T State University. From the development of the RF Micro Lab and the work that we have done together, I am honored to be apart. In addition I would like to express my gratitude to Dr. Huseyin Savci for his passion and direction. Your passion for engineering, research and discovery has been poured into me as and I look forward to carrying that passion on to my next endeavor. Dr. Xie, thank you for staying late nights to help me work through the testing of my work and always being accessible, it is greatly appreciated. Also I like to thank Dr. Albert Pisano and Ernest Ting-Ta Yen with the Berkeley Sensor and Actuator Center for sharing their resource with the MEMS resonator.

To the RFMicro Lab Marvin Aidoo, Johnathan Matson and Melaka Senadeera thanks for all support and I hope that you have much success with your academic and professional endeavors. Micah Colon for maintaining the CAD systems without which we would not be able to do work, your expertise was essential. Also I like to thank Analog Devices, particularly Natalie Shore and Brenda Rhome. A special thanks to my office mates Ms. Tanina Bradley and Mr. Adam Bowen whom we shared many lunches and dinners together and great conversations, you guys help keep me sane, all the best and I look forward us doing it again soon.

V

Furthermore I would like say a very special thank you to the most professional and dedicated ladies who work in the Title III office especially Ms. Willetta Stamp without whom none of this would have been possible not only did you provide support but you served as an encourager, a nurturer and acted as a North Carolina Mom. You have touched my life in a profound way that will carry with me forever.

Most importantly to my family, Thank you to my parents who continuously encourage me, and imparted into me the vision to soar and then gave me the wings to fly. My Father for his strength and my Mother for her patience and perseverance, anywhere I go you are never far from me, I love you... To my Sister who continues to inspire me, you will always be my dearest love and I look forward to creating more memories together. Wow! Look how far we have come. Finally to the best story written within the chapters of my life, Ms. Dondra S. Bailey your presence has been a blessing and the constant support and encouragement you freely give is a precious treasure. You are truly one of God's most beautiful and cherished gifts and I am humbled to have you in my life. I love you.

# **TABLE OF CONTENTS**

| LIST OF FIGURES                                 | ix   |

|-------------------------------------------------|------|

| LIST OF TABLES                                  | xii  |

| KEY TO SYMBOLS AND ABBREVIATIONS                | xiii |

| CHAPTER 1. INTRODUCTION                         | 1    |

| 1.1 Body Area Network                           | 1    |

| 1.2 Medical Implants Communication Service Band | 2    |

| 1.3 WHY MICS was established                    | 4    |

| 1.4 Wake-up Receiver Design Considerations      | 7    |

| 1.5 Duty Cycle Control for Sensors              | 9    |

| 1.6 Functional Specifications                   | 16   |

| 1.7 System Integration                          | 18   |

| 1.8 Network Environment                         | 19   |

| CHAPTER 2. DESIGN SPACE CONSIDERATIONS          | 21   |

| 2.1 Architecture Consideration                  | 21   |

| 2.2 TRADTIONAL RECEIVER:                        | 24   |

| 2.3 Technology Considerations                   | 29   |

| 2.4 Limitations of Integrated Inductors         | 30   |

| 2.5 Micromechanical Resonators                  | 36   |

| 2.6 SAW Structure                               | 37   |

| 2.7 SAW Circuit Model                           |      |

| 2.8 Circuit and SAW Integration                 | 44   |

| CHAPTER 3. UNCERTAIN-IF RECEIVER                | 46   |

| 3.1 Design of the Ultra Low-Power Wake-Up Receiver | 46 |

|----------------------------------------------------|----|

| 3.1.1 Oscillator Power Limitations                 | 47 |

| 3.1.2 Uncertain IF Architecture                    | 48 |

| 3.2 CIRCUIT DESIGN                                 | 52 |

| 3.2.1 Input Matching Network                       | 53 |

| 3.2.2 Dual Gate Mixer                              | 56 |

| 3.2.3 IF Amplifier                                 | 62 |

| 3.2.3.1 IF Bias Circuit                            | 65 |

| 3.2.4 Differential Envelope Detector               | 66 |

| 3.2.5 Digitally Controlled Oscillator              | 69 |

| 3.2.6 Constant Gm-Bias Circuit                     | 71 |

| 3.2.7 Complete Sensitivity Analysis                | 73 |

| CHAPTER 4. MEASUREMENT RESULTS                     | 81 |

| 4.1 Introduction                                   | 81 |

| 4.2 Floorplan                                      | 81 |

| 4.3 TestBoard and Measurement Setup                |    |

| 4.4 Ring Oscillator LO Measurement                 |    |

| 4.5 Performance Summary                            | 94 |

| CHAPTER 5. CONCLUSION                              | 95 |

| REFERENCES                                         | 97 |

# LIST OF FIGURES

## FIGURE

## PAGE

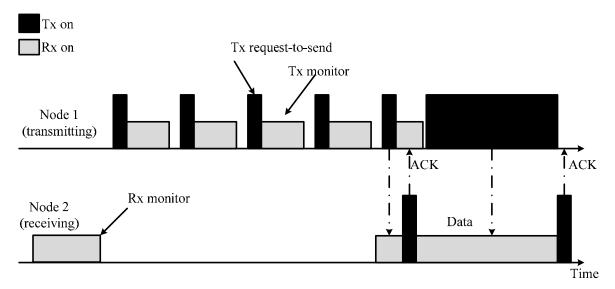

| 1.1  | Protocol-based duty cycle control: transmitter initiated   | . 12 |

|------|------------------------------------------------------------|------|

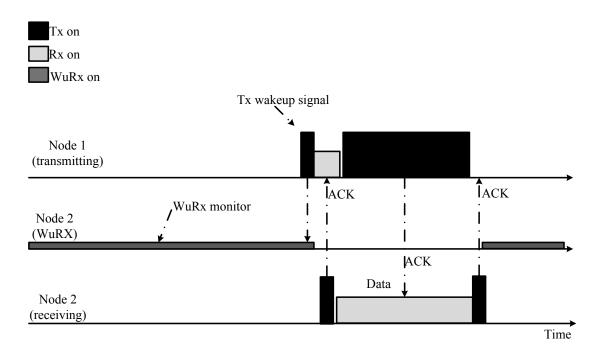

| 1.2  | Duty-Cycle control with wake-up receiver                   | . 13 |

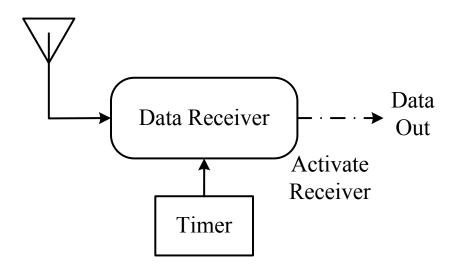

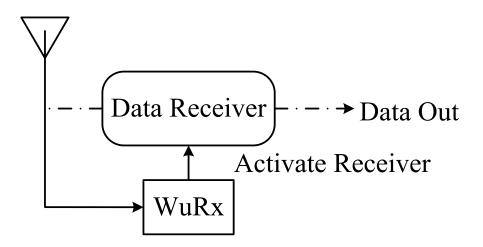

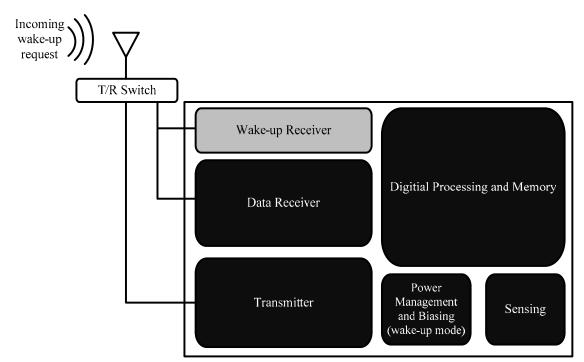

| 1.3  | Block Diagram of sensor node electronics in sleep mode     | . 19 |

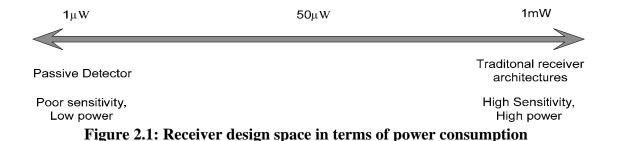

| 2.1  | Receiver design space in terms of power consumption        | . 22 |

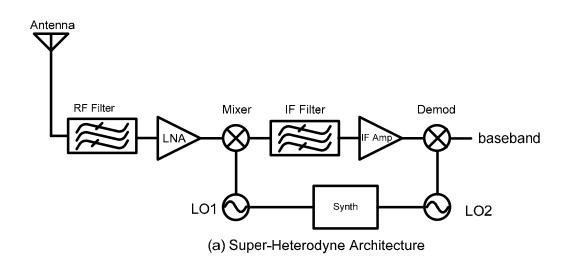

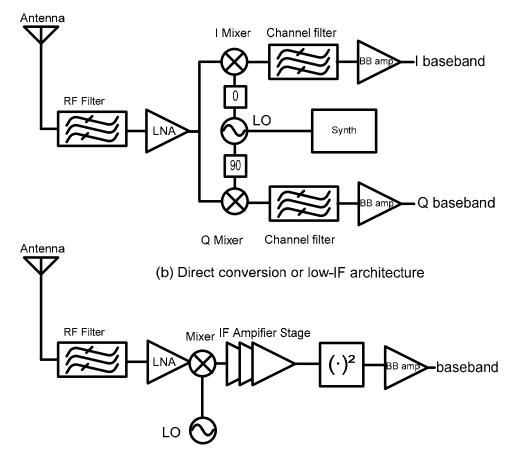

| 2.2  | Block comparison of popular receiver architectures         | . 25 |

| 2.3  | Real Model for a parallel LC                               | . 31 |

| 2.4  | Inductor impedance at resonance                            | . 33 |

| 2.5  | Low Noise Amplifier with Source Degeneration               | . 33 |

| 2.6  | Classic LC tank                                            | . 35 |

| 2.7  | Cross-section and top view of SAW resonator (not to scale) | . 38 |

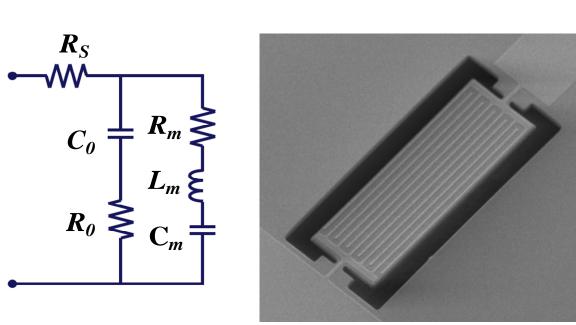

| 2.8  | Circuit Model and photo of SAW resonator                   | 41   |

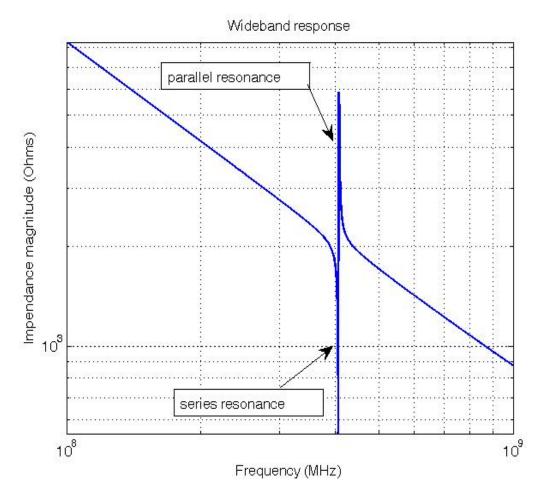

| 2.9  | Simulated SAW resonator response (Wideband response)       | . 42 |

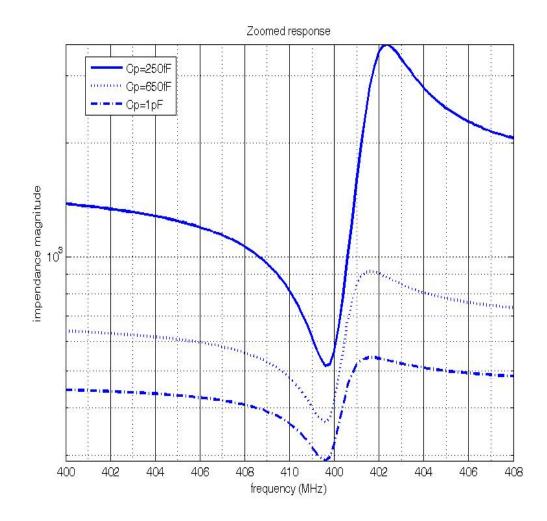

| 2.10 | Simulated SAW resonator (Zoomed response for varying C0)   | . 43 |

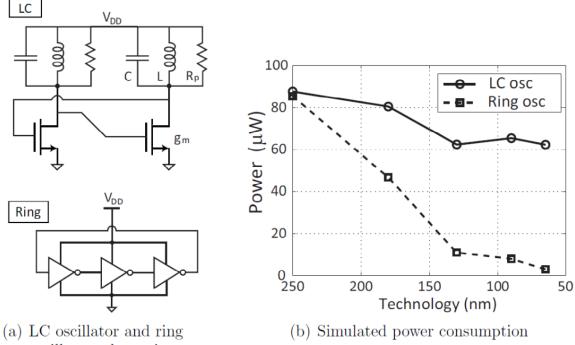

| 3.1  | Effect of technology scaling on oscillator power           | . 47 |

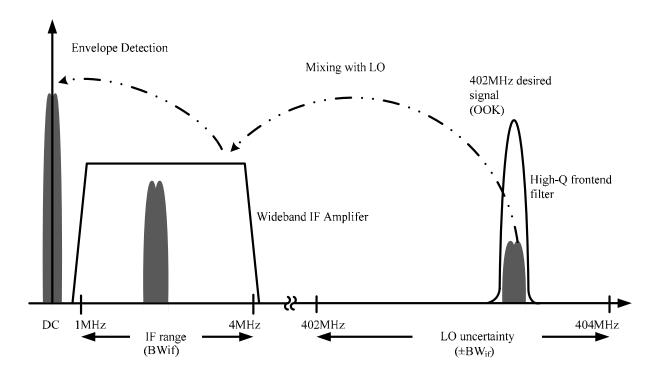

| 3.2  | Uncertain- IF frequency plan and method of operation       | . 49 |

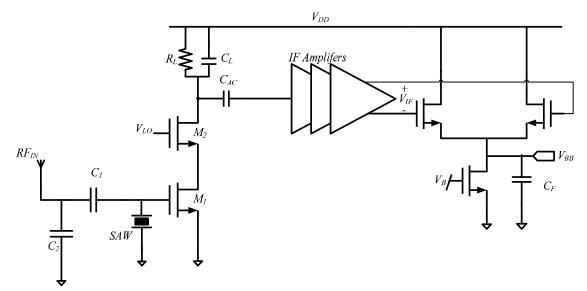

| 3.3  | Simplified schematic of complete receiver                  | . 52 |

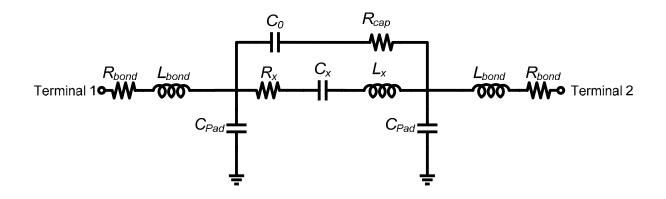

| 3.4  | Complete resonator model including parasitics              | 53   |

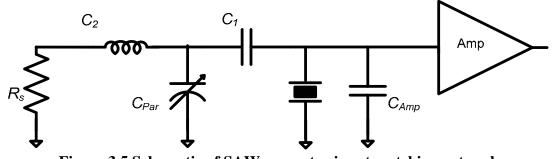

| 3.5  | Schematic of SAW resonator input matching network          | . 54 |

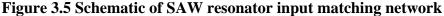

| 3.6  | Simulated input match and voltage gain                     | . 55 |

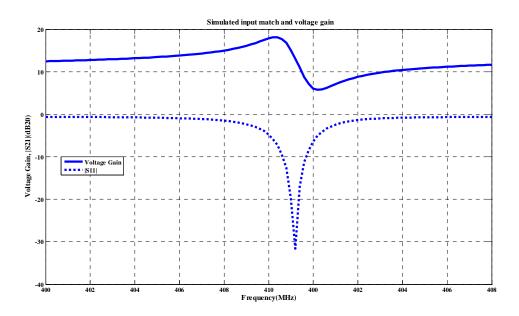

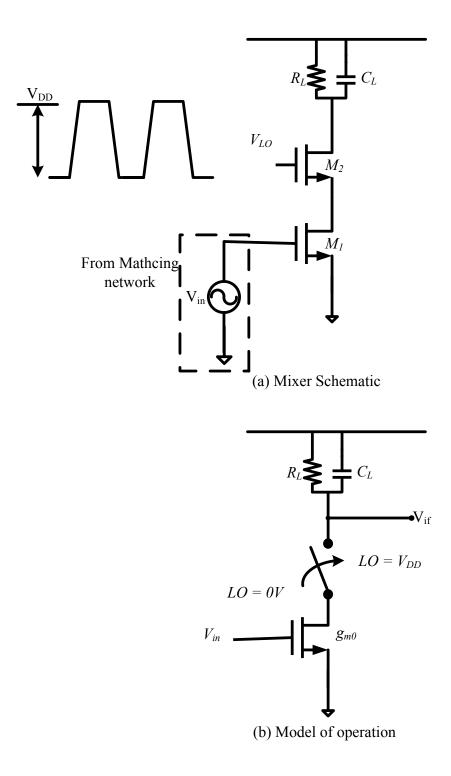

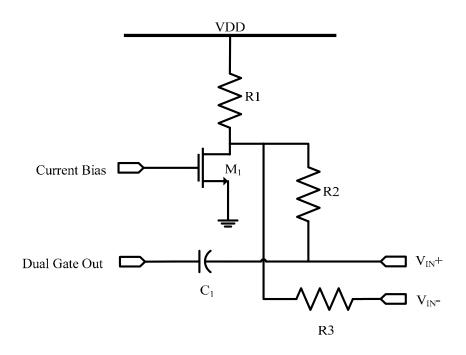

| 3.7 Schematic for Dual gate Mixer                                                | 57   |

|----------------------------------------------------------------------------------|------|

| 3.8 Dual Gate Mixer Operation                                                    | . 59 |

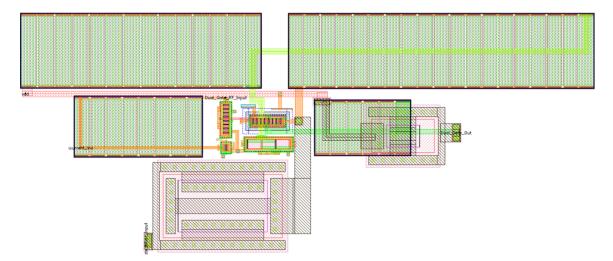

| 3.9 Layout Design for Dual-Gate Mixer                                            | 60   |

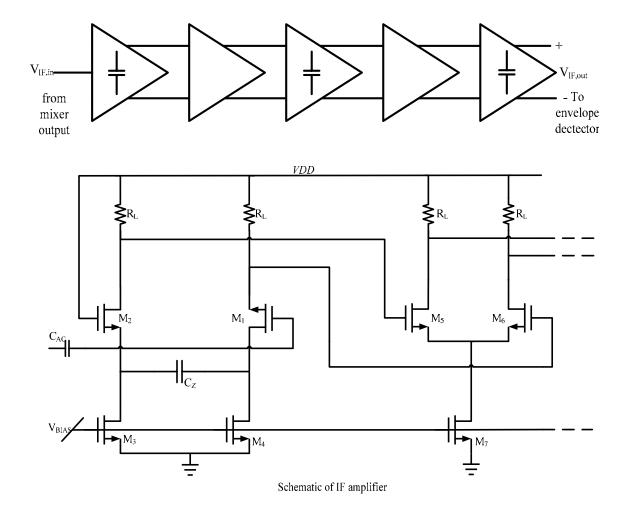

| 3.10 Schematic of IF amplifier                                                   | 61   |

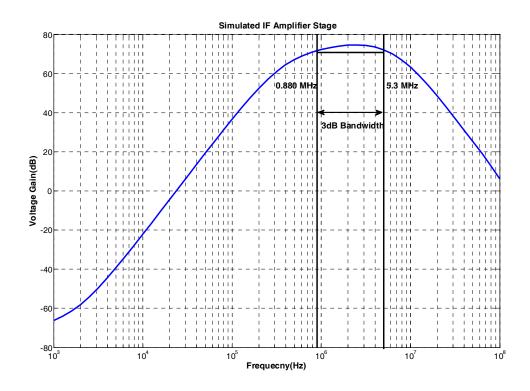

| 3.11 Simulated IF amplifier frequency response                                   | 62   |

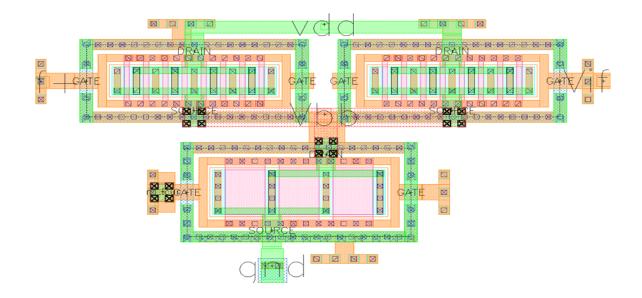

| 3.12 Layout for IF Amplifier                                                     | 64   |

| 3.13 IF Bias Circuit Schematics                                                  | 65   |

| 3.14 Differential Envelope Detector                                              | 66   |

| 3.15 Layout for the Differential Envelope Detector                               | 69   |

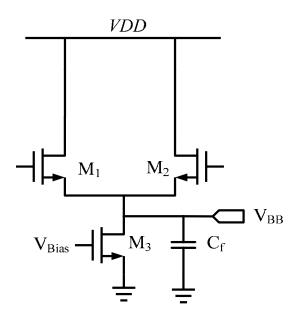

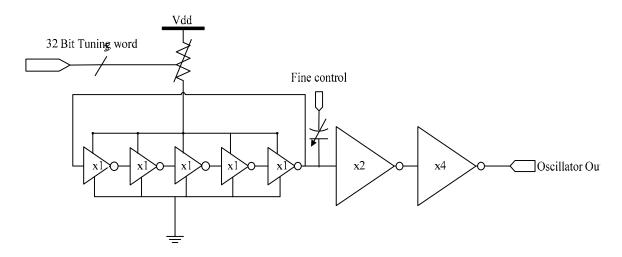

| 3.16 Digitally-controlled oscillator (DCO) schematic                             | 70   |

| 3.17 Layout for Digitally Controlled Oscillator                                  | 70   |

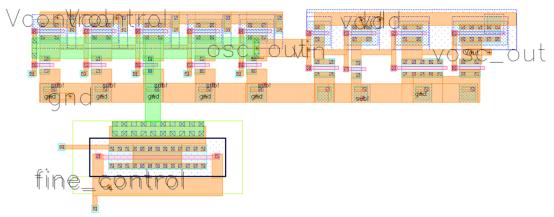

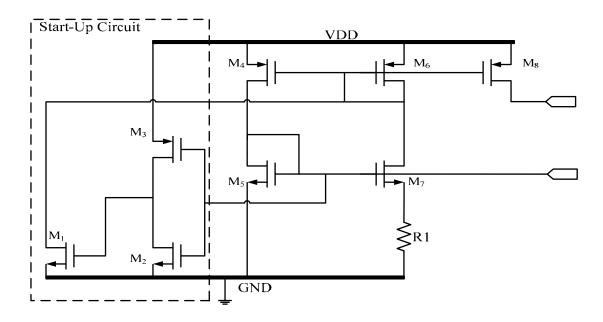

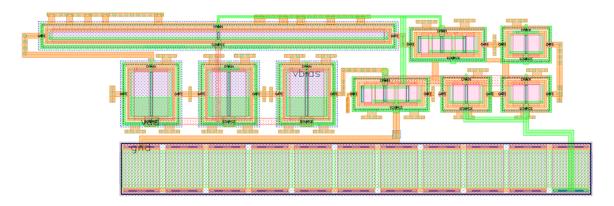

| 3.18 Constant Gm-Bias Circuit                                                    | 71   |

| 3.19 Layout for Constant-Gm bias circuit                                         | . 72 |

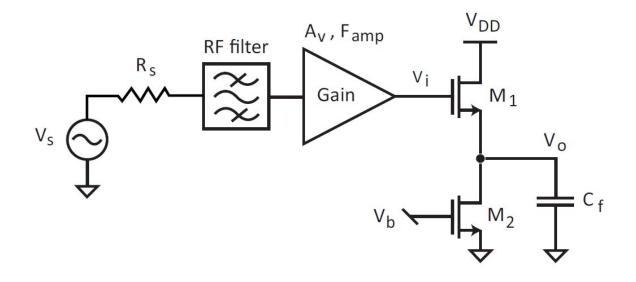

| 3.20 Generic receiver with envelope detector                                     | . 74 |

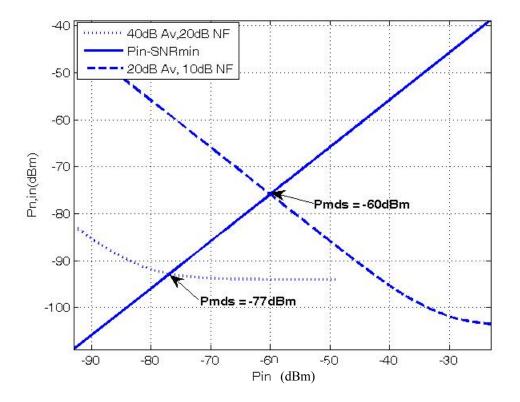

| 3.21 Effect of amplifier gain and NF on envelope detection receiver sensitivity. | .76  |

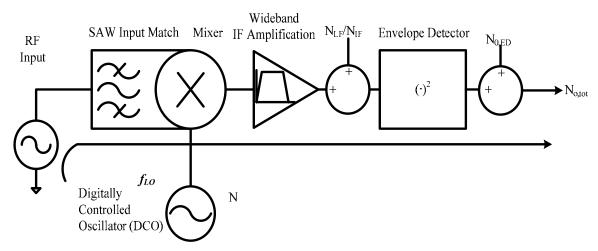

| 3.22 Noise sources for the uncertain-IF receiver                                 | 77   |

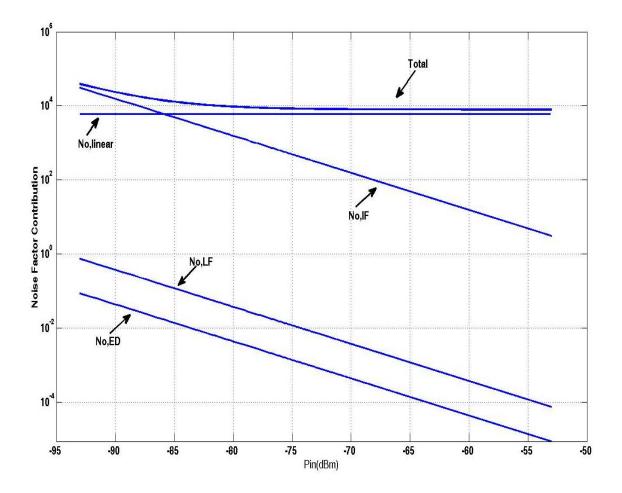

| 3.23 Noise Factor Contribution                                                   | . 79 |

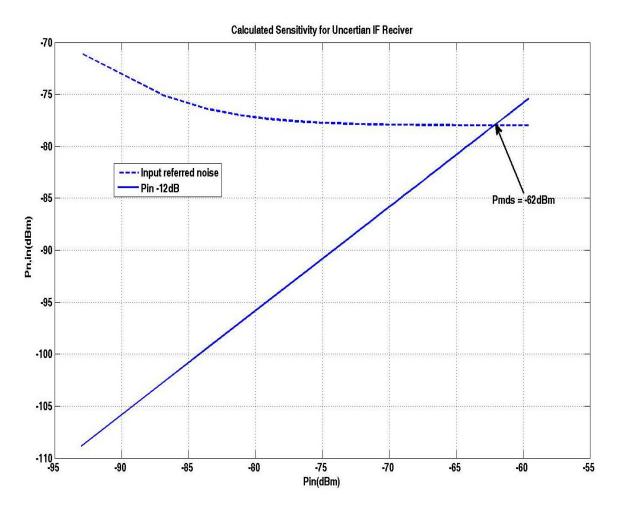

| 3.24 Calculated Sensitivity for Uncertain IF Receiver                            | 80   |

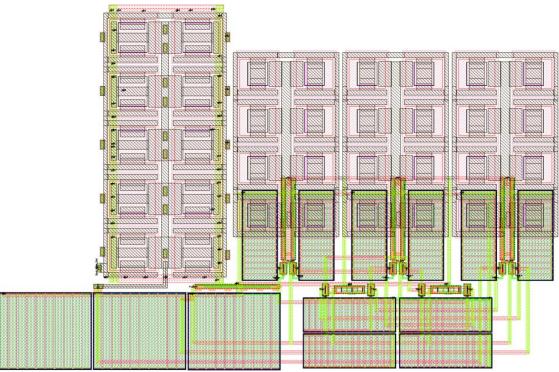

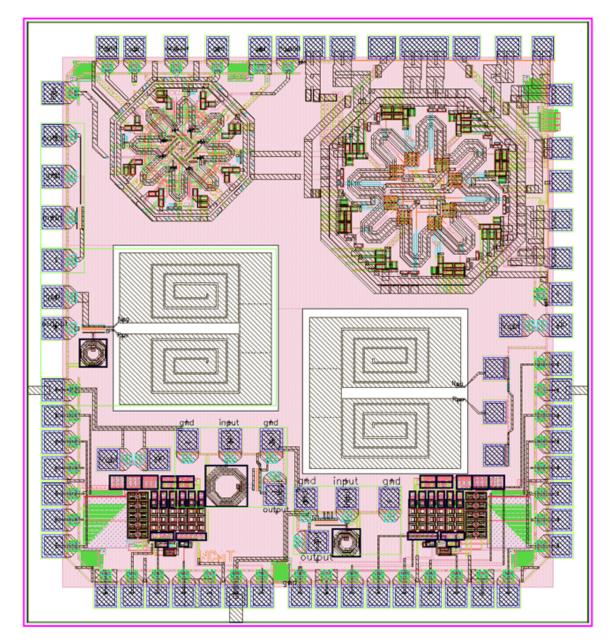

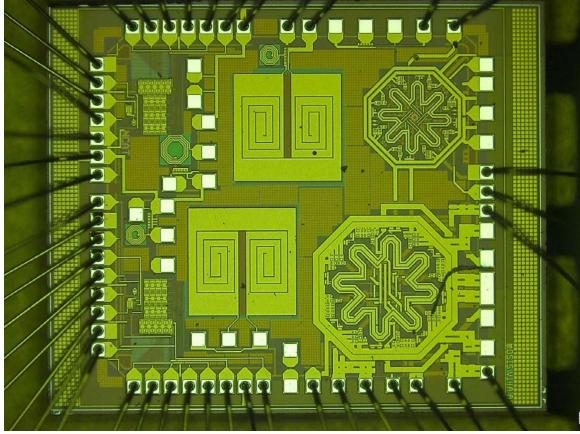

| 4.1 Cadence Virtuoso Layout Design Floorplan                                     | 82   |

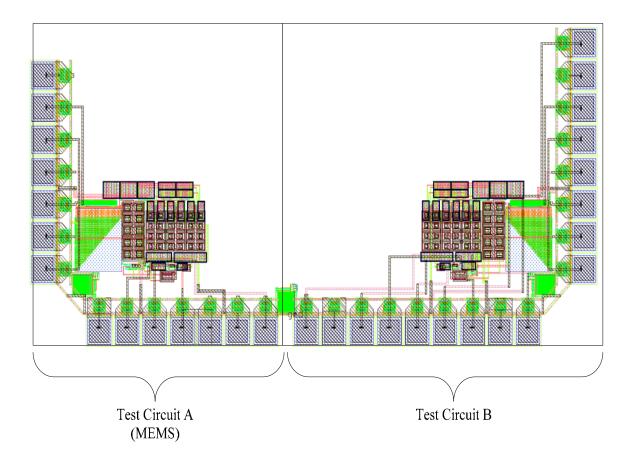

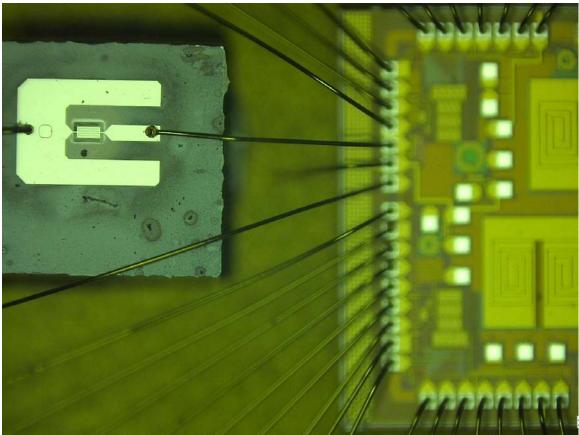

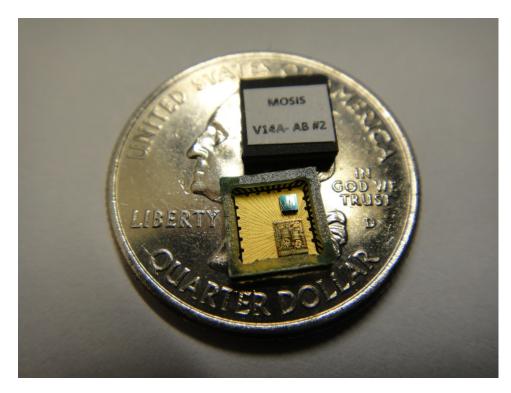

| 4.2 Test circuit A with MEMS device and Test Circuit B beak-out testing          | 83   |

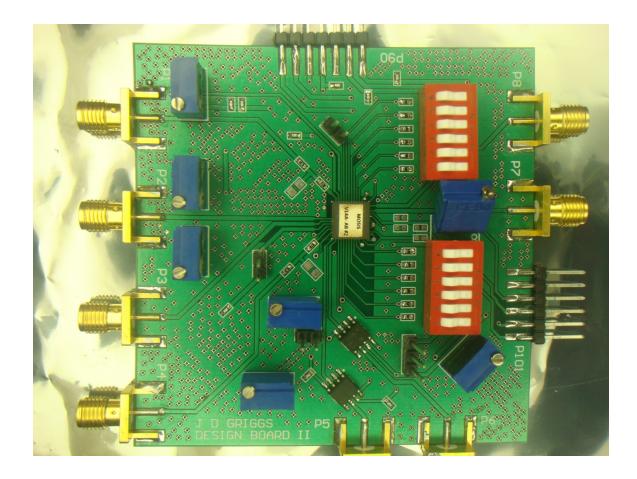

| 4.3 Photograph of the test board for characterization and measurement of MIC     | S    |

| Receiver                                                                         | 84   |

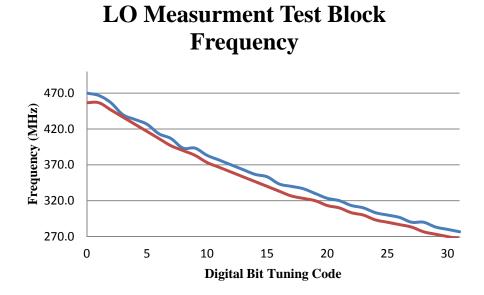

| 4.4  | LO Tuning Range                                    | 88   |

|------|----------------------------------------------------|------|

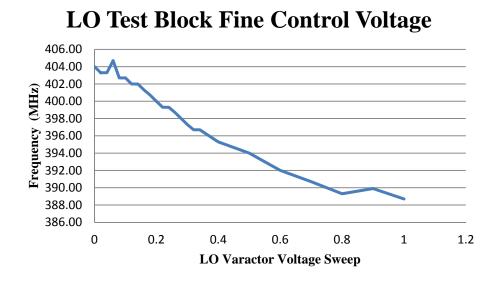

| 4.5  | Varactor (fine tuning frequency range)             | . 89 |

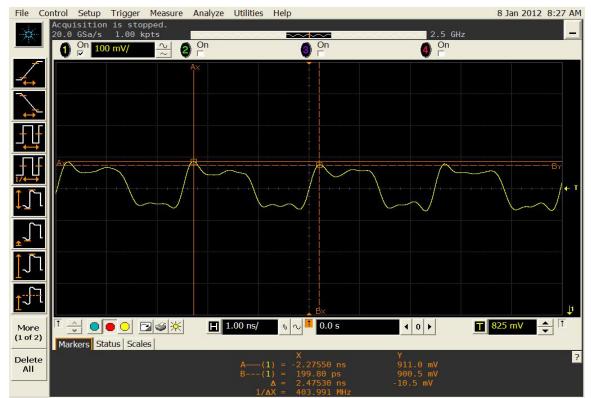

| 4.6  | LO waveform output                                 | . 89 |

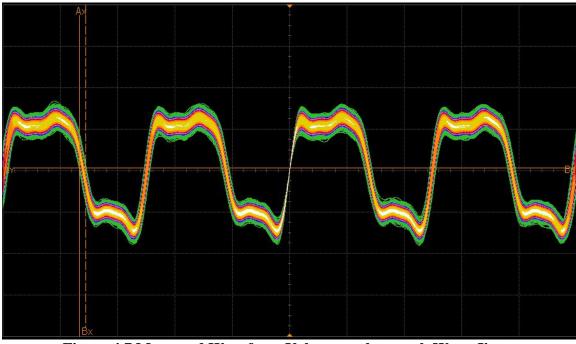

| 4.7  | Measured Waveform Voltage Peak to Peak Wave Jitter | . 90 |

| 4.8  | Full-Chip with wirebonding                         | 91   |

| 4.9  | Chip with wire bonding with MEMS resonator         | 92   |

| 4.10 | Wake-up Receiver and MEMS resonator                | . 93 |

# LIST OF TABLES

## TABLE

# PAGE

| 1.1 Characteristics of Wireless Network Technologies Coverage        | 3    |

|----------------------------------------------------------------------|------|

| 1.2 Characteristics of Wireless Network Technologies                 | 6    |

| 1.3 Wake-up Receiver Comparisons                                     | . 15 |

| 1.4 Wake Up Receiver Design Specifications                           | . 18 |

| 2.1 Performance Comparison of RFIC Technologies                      | . 30 |

| 2.2 Saw Resonator Parameter Value for 406MHz                         | . 41 |

| 3.1 Transistor Sizes and Element Values for Dual Gate Mixer          | . 57 |

| 3.2 Transistor Sizes and Element Values for IF Amplifier             | . 61 |

| 3.3 Transistor Sizes and Element Values for IF Bias Stage            | . 65 |

| 3.4 Transistor Size for Differential Envelope Detector               | . 66 |

| 3.5 Transistor Sizes and Element Values for Constant Gm Bias Circuit | . 71 |

| 3.6 Performance Metrics for Constant Gm Bias Circuit                 | . 71 |

| 4.1 Measurement Equipment                                            | .86  |

| 4.2 Device Performance                                               | . 94 |

# **KEY TO SYMBOLS AND ABBREVIATIONS**

| AC    | Alternative Current                     |  |

|-------|-----------------------------------------|--|

| AM    | Amplitude Modulation                    |  |

| BER   | Bit Error Rate                          |  |

| BW    | Band-Width                              |  |

| CMOS  | Complementary Metal Oxide Semiconductor |  |

| DC    | Direct Current                          |  |

| DR    | Dynamic Range                           |  |

| DSB   | Double Side Band                        |  |

| DUT   | Device Under-Test                       |  |

| EIRP  | Effective Isotropic Radiated Power      |  |

| EMI   | Electromagnetic Interference            |  |

| ESD   | Electro-Static Discharge                |  |

| FCC   | Federal Communication Commission        |  |

| FET   | Field Effect Transistor                 |  |

| FM    | Frequency Modulation                    |  |

| FSK   | Frequency Shift Keying                  |  |

| I/Q   | In-phase/Quadrature-phase               |  |

| IC    | Integrated Circuit                      |  |

| IF    | Intermediate Frequency                  |  |

| IGFET | Insulated-Gate Field-Effect Transistor  |  |

| ISM   | Industrial, Scientific and Military     |  |

|       |                                         |  |

| IMD     | Implantable Medical Devices                                  |  |  |

|---------|--------------------------------------------------------------|--|--|

| ITU-R   | International Telecommunication Union – Radio-communications |  |  |

| KCL     | Kirchhoff's Current Law                                      |  |  |

| KVL     | Kirchhoff's Voltage Law                                      |  |  |

| LNA     | Low Noise Amplifier                                          |  |  |

| LO      | Local Oscillator                                             |  |  |

| LP      | Loop Filter                                                  |  |  |

| LPF     | Low Pass Filter                                              |  |  |

| MICS    | Medical Implant Communication Service                        |  |  |

| MiM     | Metal-Insulator-Metal                                        |  |  |

| MOS     | Metal Oxide Semiconductor                                    |  |  |

| PLL     | Phase Lock Loop                                              |  |  |

| SoC     | System on Chip                                               |  |  |

| TRX     | Transceiver                                                  |  |  |

| TTL     | Transistor-Transistor Logic                                  |  |  |

| TX      | Transmitter                                                  |  |  |

| UHF     | Ultra High Frequency                                         |  |  |

| VCO     | Voltage Controlled Oscillator                                |  |  |

| WuRx    | Wake-Up Receiver                                             |  |  |

| WB      | Wire-Bond                                                    |  |  |

| WiseNet | Wireless Sensor Network                                      |  |  |

| WTMS    | Wireless Telemetry Service                                   |  |  |

# CHAPTER 1 INTRODUCTION

#### **1.1 Body Area Network**

As the design and development of integrated circuit technology has evolved, so has the design of medical implantable devices. The evolution of circuit technology has facilitated highly complex embedded systems and smaller medical device sizes. Current advancements for implantable medical devices (IMD) are now exploiting wireless communication technologies. These strategically placed devices can gather real time data or alert of significant changes within the human environment. These embedded systems include low power radio frequency circuits, energy harvesting techniques, system on chip design, and incorporating Micro-Electro-Mechanical Systems (MEMS) devices. The combination of these advances has contributed to the creation of Wireless Body Area Networks (WBANs). WBAN was first presented in 1996 as a viable wireless communication protocol for medical applications to improve utilization of medical devices such as pacemakers, neuromuscular stimulators, micro-drug delivery devices, cochlear implants and visual prosthesis [1]. All next generation medical devices will have the capability to be controlled remotely through a wireless network. WBAN provides a proactive approach creating a healthcare revolution that allows prevention, early detection or outpatient therapeutic treatments for diseases.

As IMD's become more prevalent there is an increasing need for these devices to support the formation of body area networks. A WBAN is a collection of miniaturized, invasive and non-invasive wireless sensor nodes that monitor the human body functions

and external environment. Each device is configured to continuous, automated and unobtrusively monitor physiological signs which can be collected and processed. The information can be relayed to a base station or PDA for diagnosis and prescription. WBAN would allow physician to monitor patients within their natural physiological state, with the ability to maintain their normal daily activities without restriction. In addition, it can be used to implement an affordable health care system that can diagnose procedures, provide maintenance for a chronic condition, allow supervised recovery from a surgical procedure and handle emergency events.

### **1.2 Medical Implants Communication Service Band**

Use of wireless communications for some of these applications has been approved by the U.S. Federal Communications Commission (FCC). In 1999 the FCC established the Medical Implant Communications Service band that specifically applied to transmitters that support the diagnostic and/or therapeutic functions associated the implantable medical devices to enable individuals and medical practitioners to utilize potential life-saving medical technology without causing interference to other users in the spectrum[2]. The Commission set aside 402-405MHz band specifically for several reasons. 402-405MHz allows development of low-power transmitters and antennas designed for the MICS band that can be made small enough and still have reasonable performance range typically having a communication link ~3-10 meters. With 300 KHz channels spread across the MICS spectrum, enables the wireless communication of

| Network | Coverage | Data Rate  | Applications                    | Technologies               |

|---------|----------|------------|---------------------------------|----------------------------|

| WWAN    | > 10 km  | <10 Mbps   | Mobile Internet, telephony      | Satellite,<br>GSM, UMTS    |

| WMAN    | < 10 km  | < 100 Mbps | Broadband                       | IEEE 802.16                |

| WLAN    | < 1 km   | < 100 Mbps | Hot spots, Ethernet replacement | IEEE802.11                 |

| WPAN    | < 10 m   | < 10 Mbps  | Data Transfer                   | Bluetooth,<br>IEEE802.15.4 |

| WBAN    | < 2-5 m  | < 1 Mbps   | Health Monitoring               | Proprietary                |

Table 1.1 Characteristics of Wireless Network Technologies Coverage

medical devices to achieve sufficient transmission rates. The MICS band has signal propagation characteristics that are particularly well suited for implantable applications due to the signal propagation characteristics for the transmission of radio waves within the human body. Because the human body is not a good media through which electromagnetic waves transmit due to the body's high electric conductivity, this results in a large path loss in the transmission of energy from the implant to free air space. This characteristic is also a challenge for continuously monitoring applications; the signal may go across several access points into multiple networks such as Bluetooth, Zigbee, and WLAN. Table 1.1 shows the classification of wireless networks according to their coverage.

The MICS band does not possess a significant risk of interference to other radio operating within the band and is recognized internationally for medical device applications. MICS transceivers are expected to be used in medical implant devices such as cardiac pacemakers, implantable cardio-verter defibrillator, neurostimulators, hearing aids, and automated drug delivery systems. Recent progress in CMOS IC technology allows wireless transceiver designs that are high reliable, cost effective, and ultra low in power consumption. The MICS band is already compatible with devices governed by European Telecommunication Standards Institute (ETSI) thus implantable medical devices can be maintained wherever they are in the world.

#### **1.3 WHY MICS was established?**

Before the implantable medical devices could communicate wirelessly, communication with the device is often done through magnetic (inductive) coupling methods. Magnetic coupling systems have data rates ~1-10 Mbps and transmission ranges of only a few inches. Also a magnetic system requires the external monitor, which consumes a lot of power, needs to be placed close to the patient, usually in contact with the skin and/or directly over the implant in order for the data communication to occur. The device using inductive coupling within the body can only support one way communication from within the body. Another limitation of medical implanted devices is that since they are magnetically coupled to an external unit, they could easily be affected by electromagnetic interference (EMI). EMI represents a major risk to patient safety and medical effectiveness due to the increasing usage of electromagnetic energy radiating devices such as cell phones and security systems. According to the reports of the Center for Devices and Radiological Health under the US Food and Drug Administration (FDA), it was estimated that about 500 incidents were suspected to be attributable to EMI affecting cardiac devices. More than 80 of these reports involved cardiac and other medical device interactions with electronic security systems. EMI represents a major risk

to patient safety and medical effectiveness due to the increasing usage of electromagnetic energy radiating devices such as cell phones and security systems [3]. WBAN technology overcome these limitations by exploiting the MICS bandwidth which offers a faster data transfer rate and longer link range. The physician can extract information quickly, and the patient benefits greatly from the expanded freedom of movement.

#### **General Transceiver Characteristics**

ITU-R Recommendation SA.1346 (7) sets out recommended characteristics for MICS devices to facilitate sharing with stations operating in the Meteorological Aids service in the band 401-406 MHz[4]. The recommendations include:

- A. limiting MICS devices to a maximum of -16dBm equivalent isotropically radiated power (EIRP) in a reference bandwidth of 300 kHz to prevent interference to meteorological aids; and

- B. that MICS utilizes a range of interference mitigation techniques to minimize the impact of meteorological aids on their operation.

The recommendation identifies a number of possible interference mitigation

techniques that MICS devices might use including:

- A. avoiding a false activation; the implanted device should use techniques such as requiring activation by a strong magnetic field;

- B. when the system is used for home monitoring, the system could poll at long intervals;

- C. the use of multiple error correction codes and automatic repeat requests to avoid impulsive interference and ensure sent and received data is accurate; and

| Controller Unit                     | 0                              |

|-------------------------------------|--------------------------------|

| Receiver noise bandwidth            | 200 kHz                        |

| Antenna Gain Tx/Rx                  | 2 dBi                          |

| Power Into Antenna                  | -22 dBm                        |

| Tx Power                            | -20 dBm EIRP                   |

| Required SNR                        | 14 dB                          |

| Noise Floor                         | -101 dBm                       |

| Ambient noise at receiver input     | 20 dB above kTB                |

| Receiver noise figure               | 4 dB                           |

| Implanted Unit                      |                                |

| Receiver noise bandwidth            | 25 kHz                         |

| Antenna Gain Tx/Rx                  | -31.5 dBi                      |

| Power Into Antenna                  | -2 dBm                         |

| Tx Power at the surface of the skin | -33.5 dBm EIRP                 |

| Required SNR                        | 14 dB                          |

| Noise Floor                         | -121 dBm                       |

| Ambient noise at receiver input     | About kTB (due to tissue loss) |

| Receiver noise figure               | 9 dB                           |

| Transmission Losses                 |                                |

| Free space loss at 2 meters         | 30.5 dB                        |

| Fade margin (with diversity)        | 10 dB                          |

| Excess loss (polarization, etc.)    | 15 dB                          |

| Building penetration loss           | 20 dB                          |

### **Table 1.2 Characteristics of Wireless Network Technologies**

D. avoiding narrow band interference using frequency agility and techniques where the MICS equipment chooses a channel based upon the lowest ambient noise level.

This last technique also reduces the possibility of MICS equipment causing interference to other services by avoiding channels known to be in use. MICS communications sessions are required to be initiated by a programmer/control transmitter, except for a communications session resulting from a "Medical Implant Event". A medical implant event is one that requires the medical implant device to transmit data immediately in order to protect the safety of the person in whom the medical implant device has been placed.

The key technical and operational conditions proposed for the use of MICS transmitters are:

- Band of operation: 402-405 MHz.

- Maximum EIRP:  $25\mu$ W this limit to apply in any 300 kHz bandwidth.

- Operation on a non-interference basis.

- Transmitters in implanted devices to transmit only when commanded to do so by external programmers/controllers, except for medical implant events.

- Programmer/controller devices to operate on a listen-before-transmit basis to identify and use the communication channel of lowest ambient noise.

- Frequency agility to enable communication to occur on the lowest ambient noise channel determined to be available.

Based on the recommendations, a MICS transceiver should have the characteristics listed in Tables 1.2 [5]. They are the specifications for the MICS programmer unit and the MICS implant unit respectively and lists the transmission losses for overall MICS transceiver[5].

### **1.4 Wake-up Receiver Design Considerations**

The implementation and specification for the WuRx depends on the application for which it is design for. Candidate applications of WuRx may include wireless networks such as WSN, radio frequency identification (RFID) technology, Zigbee, Bluetooth, Bluetooth Low Energy (also known as Wibree), and wireless personal area network (WPAN), wireless local area network (WLAN). There are several factors that should be considered when designing a WuRx for a WBAN device.

Low power consumption: IMDs are either battery-less and needs to have continuous power from an external portable battery, or use miniature rechargeable batteries that inductively charges on a regular basis [6]. Regardless of the method the power transmission should be highly efficient to maximize the battery lifetime. This not only preserves the power supply but also minimize the size of the battery and overall IMD thus protecting internal tissue from heat dissipating from the device and limiting the exposure to the electromagnetic field. Ultra-low power and efficient designs must be used because the power capacity is directly proportional to device size.

**High Reliability:** Reliability must be a very high priority, as if any failure of the WBAN device occurs it can result to inconvenience, pain, damage organs or even death. Maintenance is also high risk to the patient and costly.

**Small size and cost:** the size of medical devices must be as small as possible so that the device is unobtrusive and maximized portability, especially constrained depending on anatomical region in which the devices will reside. In order to make a

practical implementation using few external small-sized components will also reduce the cost of parts as well.

**Minimize false wake up signals:** Each WuRx must to be able to determine the difference between an unwanted signal and the wake up signal. Also should have the capability to distinguish between wake-up signals in the form of wake-up packets. This will give WBAN devices addressing abilities in order to interrogate a specific device.

### **1.5 Duty Cycle Control for Sensors**

Power consumption reduction is a primary goal when designing WBAN systems. IMD must perform such functions as computation, sensing and actuation. However when these components have been integrated into the system, the wireless communication energy is still dominant [7]. Thus the goal of this research is to reduce the energy dedicated to communicate to WBAN devices. Within WBAN networks packet traffic rates are generally low with small bits of data exchanged. Packets themselves are short; data packets with 200 bits or less of information is typical. The amount of data to be transferred depends highly on the network traffic and network application. Typically within WBAN application most of the sensing and monitoring application follow a general form that incorporates sparse communications with long periods of idle time.

The Physical layer protocol (PHY) design requires minimizing power consumption without degradation in terms of latency, data loss and throughput. In order to reduce power consumption within medical implantable devices they are heavy duty cycled, meaning the device spends majority of its time in a low power sleep mode. For communication to begin there has to be some way for the devices to activate simultaneously, the communication event is referred to as rendezvous. There are two main ways for overcoming this challenge a synchronous protocol can be implemented which uses a global clock as a reference and is shared between devices that allow the communication channel to come alive only for a certain time period. By limiting the period of time the electronic device needs to perform a given function can reduce the average power consumption by orders of magnitude. The difficulty with this protocol is that to maintain a distributed clock signal within each individual WBAN device is challenging. Moreover the energy needed to maintain a global synchronization can be significant because the device will wake up even if there is no packet to transmit or receive. This results in idle listening and overhearing.

Alternatively a pseudo-asynchronous duty cycle method can be utilized; this avoids/removes the need for a remote synchronization by using a request based protocol to control duty cycle and set-up communication between devices. As shown in Figure 1.2, this request can be initiated by either the transmitting or the receiving device. With this protocol based duty cycle the receiver is set on a timer to limit the time that it is active, while active the receiver monitors the channel for communication. If there is no communication signal received then the receiver returns to sleep. For the transmitting device to communicate it sends repeated requests until the receiver is active and detects the request. When these two events coincide, then data can be exchanged, though the asynchronous protocol eliminates the need for a global clock (synchronization), a significant amount of energy has been expended by both the receiver and the transmitter; the receiver by monitoring the channel and the transmitter by sending out requests or

beacons. Both methods synchronous and asynchronous show a trade-off between power consumption and latency. Latency is the measure of time delay experienced in a system.

To create a bridge between these two tradeoffs an alternative method can be implemented by employing an addition auxiliary receiver called a wake-up receiver (WuRx) for each device thus employing a pure asynchronous rendezvous protocol. The wake-up receiver is totally dedicated to monitor the channel it is tuned for, monitoring communication requests and wake-up signals. Because the WuRx is listening continuously, the WuRx can respond more quickly thus significantly reducing latency. The power that was expended by the repeated beaconing on the transmit side and the periodic monitoring on the receiver side is replaced by the power consumption of the WuRx. Because the WuRx is not duty-cycled, its active power consumption needs to be very low to ensure that the power used does not dominate the overall power of the link. The WuRx would reduce the turnaround time from transmit state to a receive state and create a faster wakeup from sleep mode which would help with power savings.

The most elementary and lowest power consumption wake up circuit is presented in [8]. Gu et al. presents and simulates a zero-power radio-triggered hardware that uses a multiple-stage charge pump that receives energy from radio signals that initiates a wakeup signal to the network node without using an internal power supply. This approach is realized using Schottky diodes. However, it is not capable of RF filtering nor selectivity of the wake-up signals. Without this function whenever there is a RF activity event within communication proximity of the node, it can trigger a wake up interrupt for the receiver. This result would lead to a higher overall power consumption since the micro-

Figure 1.1 Protocol-based duty cycle control: transmitter initiated

Figure 1.2 Duty-Cycle control with wake-up receiver

circuitry and the regular receiver has been awaken to decide if the wake up was intended for the sensor every time it occurs. Therefore, for each wake-up signal event, the sensor nodes in the vicinity switches on the transceiver, consuming energy to test if the signal is meant for it. Another approach similar to is based on a MOSFET with a sensitivity of -29dBm and a current consumption of 2.6 µA this work is presented in [9]. Also, a battery assisted semi-passive RFID wakeup solution also falls within this group as well. Another design with a "power on" circuit based on a multi stage charged pump is presented in [10]. A wake up circuit with static power consumption of 4.8  $\mu$ W and with high sensitivity (-65dBm), is presented in[11]. Marinkovic et. al presents a WuRx that has a power consumption of 8nW with a sensitivity of -51 dBm. Within the WBAN radio spectrum, IMD are susceptible to significant interference from other various wireless network devices found in the vicinity, and as WBAN technologies grow there will be an increasing number of sensors that require wireless interlinking. Therefore, a more sophisticated WuRx, with addressing capabilities and high interference rejection is needed. A low power wake up receiver that has addressing capabilities and is closest to our implementation regarding the power consumption is presented in [12]. A different solution based on an envelope detector and a programmable amplifier is shown in [13]. It has a dedicated FPGA for digital decoding and preamble detection. The data is transmitted serially and it has no standardized connection. The static power consumption of 12.5  $\mu$ W and sensitivity/data rate of -57 dBm and 100 kb/s are reported. A similar solution with an envelope detector and amplifier is reported in[13]. It has a power consumption of 96  $\mu$ W, but it does not have wake up signal decoding. The design

|                                        | Detector          | Decoder           | Operating    | Data       | G           | Interference |

|----------------------------------------|-------------------|-------------------|--------------|------------|-------------|--------------|

|                                        | power†            | power†            | Frequency    | Rate       | Sensitivity | filtering    |

| This                                   |                   |                   |              |            |             |              |

| work                                   | 60µW@1.0V         | 60µW              | 405Mhz       | 100kbs     | -62dBm      | resonator    |

|                                        | . 0               | •                 |              | 2 to 80    |             | Preamble     |

| Marinkovic[11]                         | 0.27 μW@1.5V      | 8 nW              | 433.92 MHz   | kb/s       | -51 dBm     | detector     |

|                                        | 0.27 µ (1.0 1.0 1 | 0 11 ()           | 100.02 11112 | NO/ 5      | or upin     | Microcontro  |

| Ansari [14]                            | 2.6 μW@3V         | $\mu C$ dependent | 869 MHz      | 0.75 kb/s  | N/A         | ler          |

| Allsall [14]                           | $2.0 \mu W @ 3 V$ | $\mu C$ dependent | 809 IVII IZ  | 0.75 KU/S  | 1N/A        |              |

| Dumente [15]                           | 125W@15V          | 5                 | 2 4 CH-      | 100 l-h /a | 57 dDm      | EDCA         |

| Durante[15]                            | 12.5 μW@1.5V      | 5 μW              | 2.4 GHz      | 100 kb/s   | −57 dBm     | FPGA         |

|                                        |                   |                   |              | 100 to     |             | BAW          |

| Pletcher[16]                           | 52 μW@0.5V        | N/A               | 2 GHz        | 200 kb/s   | −72 dBm     | resonator    |

|                                        |                   |                   |              | 0.862      |             |              |

| Doorn [13]                             | 96 μW@1.5V        | 50 μW             | 868 MHz      | kb/s       | -51 dBm     | SAW          |

|                                        |                   | ·                 |              |            |             |              |

| Le-Huy[17]                             | 17.8 µW @ 3V      | $0.8 \mu W$       | 2.4 GHz      | 50 kb/s    | -53 dBm     | None         |

| /[1/]                                  |                   | F?                |              | 2 2 -10/0  |             |              |

| Takiguchi[18]                          | 12.4 μW           | N/A               | 950 MHz*     | 40 kb/s*   | N/A         | Bloom Filter |

| * - Simulated values: † - Static power |                   |                   |              |            |             |              |

**Table 1.3 Wake-Up Receiver Comparisons**

\* - Simulated values; † - Static power consumption (When in listening mode)

requires an active microcontroller with constant analog to digital conversion (ADC) to do the signal decoding, which further increases the power consumption. Finally, [16] presents a high sensitivity solution (-72 dBm) and good (0.5nJ/bit) dynamic power consumption, but it has a static power consumption of 52  $\mu$ W. It is mainly targeted for Wireless Sensor Networks with higher ranges than WBAN, and higher power consumption requirements. Table I presents a comparison of our receiver with low power wake up receivers with addressing mechanism both realized and tested [14],[15],[13] and [16] or simulated in detail [17] and [18].

All values in the table are extracted from the referenced papers, and no assumptions were made. These wake-up receivers have higher power consumption than our WuRx. Some of them have better sensitivity or data rate, but none of them is as wellsuited for WBAN as the WuRx presented here. We compared only the static power consumption, since most of the compared works do not have a detailed analysis of dynamic power consumption and energy per bit.

### **1.6 Functional Specifications**

A WBAN wake-up receiver must be able to communicate over the same range as the data receiver. If the transmitter and receiver are not within the communication distance then it would be impossible to wake up the node to receive data otherwise. As stated earlier for the WBAN Pico-network the data link range should be  $\sim 2m - 10m$  with a transmitter output data of about -16dBm.

The power consumption specification relies heavily on the maid data transceiver power, but also the on the network traffic conditions and desired latency. Different type of duty cycle rendezvous strategies are compared on the basis of average power and network latency.

$$L_{FS} = \left(\frac{\lambda}{4\pi}\right)^2 \left(\frac{1}{d}\right)^n \tag{1.1}$$

Where  $\lambda$  is the wavelength of the carrier frequency, *d* is the link distance, and *n* is the empirical path loss exponent. Assuming transmitter output power of -16 dBm (25µW),  $\lambda$ = 74.5cm and *n* = 2, Equation 1.1 gives a link distance of about ~4 meters for a receiver with an -34 dBm sensitivity. For effective WBAN channel conditions, the receiver sensitivity should be at least -51 dBm.

A wake-up receiver essentially functions as a single bit receiver that detects an event and then activates the data receiver. At its most fundamental level the wake-up event could simply detect the RF energy. For security and reliability implementation, the WuRx should be more than just a simple energy detector. The transmitted signal would most likely be sent as a packet with a particular bit sequence, which allows selective wake-up among WBAN devices to avoid false alarm triggers by regular data communication between neighboring devices.

It is important to understand the link budget for the desired carrier frequency. A link budget is the account of the gains and losses from the transmitter through the medium (free space, body tissue, bone, etc.), to the receiver. For IMD the general link budget formula is [19].

$$P_{RX} = P_{TX} + G_{TX} + L_{FS} + L_B + G_{RX}$$

(1.2)

Where  $P_{RX}$  is received power (dBm);  $P_{TX}$  is transmitter output power (dBm);  $G_{TX}$  is transmitter antenna gain (dBi);  $L_{FS}$  is free space loss or path loss (dBm); power L<sub>B</sub> is losses within body tissues (dBm); and  $G_{RX}$  is the receiver antenna gain (dBi). Assuming an MICS channel of 402.5MHz and a transmit and receive distance of 4 – 5 meters and typical implants are about 1cm below the fat layer, using [20] we can estimate the power loss within body tissue to be approximately -8dBm. Combining antenna transmitter and receiver gains which are reported to be in the range of 7-10dBm. The power for the receiver antenna can be approximated.

$$P_{RX} = (-16) + (-34) + (-8) + (7) = -51 \, dBm.$$

The approximated received power level can be used as a design input for the sensitivity of the WuRx. A sensitive receiver permits communication over a longer

|                      | ±                 |  |  |

|----------------------|-------------------|--|--|

| Parameter            | Value             |  |  |

| Network architecture | Narrowband        |  |  |

| Carrier frequency    | ~402.5 MHz        |  |  |

| Modulation scheme    | OOK               |  |  |

| Data Rate            | 100 kbs           |  |  |

| Sensitivity          | ~-51 dBm          |  |  |

| Power consumption    | Minimize (≤100µW) |  |  |

**Table 1.4 Wake-up Receiver Target Design Specifications**

range. However it may consume more power and hence decrease battery lifetime. Therefore the ideal wireless medical system design should balance between longer communication ranges with respect to battery longevity of the implantable devices. Therefore the goal of this research is to implement a WuRx with less that 100μW active power. The specifications are summarized in Table 1.4 Battery life can be saved by employing an optimal wake-up protocol.

### **1.7 System Integration**

At the system level, the wake-up receiver must seamlessly integrate with the rest of the WBAN's electronics. A conceptual diagram of a WBAN device in sleep mode is shown in Figure 1.3. During sleep mode, most of the electronics may be powered off, with the exception of the WuRx and any required power management circuitry. For a system device integration perspective, it is preferred for the WuRx to share the same antenna with the other wireless blocks. To reduce hardware requirements and minimize size, the WuRx must be able to receive signals from the same transmitter used for data communications, without requiring a separate wake-up transmitter antenna. Therefore,

Figure 1.3 Block diagram of sensor node electronics in sleep mode

any practical WuRx implementation will use the carrier frequency and modulation scheme as the main data transceiver.

#### **1.8 Network Environment**

In a dense network environment such as the human body, the wake-up receiver is expected to operate as shown in Figure 1.4. At any given moment a wireless device will be communicating, but many will be in deep sleep mode, only monitoring the channel for wake-up requests from other nodes. In this environment, the wake-up receiver must be robust to ambient traffic in the network and avoid waking up on signals intended for neighboring nodes. From a functional perspective, the WuRx design is not concerned with bit error rate performance as in standard receiver. Instead, the performance metrics of interest are probability of detection and conversely, probability of false alarms (FA). A missed detection means that the transmitter must re-transmit the wake-up request, increasing power and latency. A false alarm is also costly from a power perspective because the main data receiver is activated needlessly.

The two main objectives of this research are; (i) to design a general-purpose ultralow-power Medical Implant Communication Service wake-up receiver; (ii), to explore novel design techniques provided by low supply voltages for power reduction in RF integrated circuits.

# CHAPTER 2 DESIGN SPACE CONSIDERATIONS

#### **2.1 Architecture Consideration**

From the previous chapter, specifications were outlined on the functionality and power consumption for a dedicated wake-up receiver. Given that the power specification are very stringent, in the range of micro to nano-watts, in order for the WuRx to have any practical implementation both creative and novel methods have to be utilize. To move forward, one must first consider the fundamental limitations of contemporary integrated circuits while exploring other available design space. Outlined in this chapter are wireless receivers architectures available, which are used for wake-up receiver implementation, highlighting the factors limiting the power consumption for each design. With the rapid advancement of integrated circuits (ICs) fabrication technology, these developments are not limited to this specific area alone. Recent progress in the area of microelectromechanical systems (MEMS), has developed in such a way that by exploiting this design space, along with combining the two, allows one to explore new opportunities to reduce power, and bypass the limitations poised by integrated inductors in designed to be used in RF circuits.

There are two groups of RF wake up systems and depending on the intricacies of the design determines power consumption with respect to channel sensitivity. The more complex the receiver is the higher its sensitivity to detect RF activity, but these designs suffer from high power consumption. While the more simplistic design such as an RFID

system like the one in[8] which is realized using Schottky diodes uses no power but poor sensitivity and response to and RF event. Figure 2.1 shows this trade-off of power consumption versus performance.

Passive detectors are at the low end of the continuum, devices such as RFID tags are the simplest and are the lowest power receivers. These passive tags derive their power from the incoming RF waveform, and then store the energy which it uses to power up its electronics to decode the incoming signal and transmit back to the reader. However in this approach there is no RF filtering nor an addressing mechanism nor any channel selectivity for the wake-up signal. This device would activate every time there is a nearby RF event which can trigger the receiver. This unintentional wake-up event would active all the devices within its vicinity, the device activate theirs transceivers and consume energy attempting to test to see if the signal received was meant for them. The false alarm (FA) event wastes power.

For most WBAN systems the sensor network links are infrastructure nodes where all communication traffic is feed-through an access point or a base station which forwards the signal to the intended recipient. The sender and the receiver must be in range of each other thus the power of the transmitter cannot be ignored. To quantify the effective power needed for the transmitter in an RFID system let us examine the work

used in[21] as an example for an RFID tag design. The active power consumption for a RFID tag is ~1 $\mu$ W and this power is below the WuRx power budget. However the tradeoff is poor RF sensitivity, reported at -25.7 dBm on a 300  $\Omega$  antenna. In order to overcome the poor sensitivity one can simply raise the transmitting power from the reader antenna. To communicate with a tag over a distance of 10 meters, the reader must transmit 34.5 dBm output power (Pout) at the tune 2.4GHz. The average power  $P_{tx}$  is expressed as:

$$P_{tx} = \frac{P_{out}}{\eta} \frac{N}{R} \frac{1}{T_{wu}},\tag{2.1}$$

where  $\eta$  is the transmitter efficiency, and R is the data rate in bits per second,  $T_{wu}$  is the duty cycle for the reader sending a wake-up signal and N is bit sequence length. Assuming that the average power on the transmit side is 425µW with an BER=100kbs. For a peer to peer network this scenario where the transmitter is power-constrained, this power level is much too high. Poor sensitivity for the receiver tag is the primary cause for the high transmit power requirement. RFID receiver tags are appealing due to their low power consumption however a practical WuRX design will require a better sensitivity in order to avoid shifting the burden of power consumption to the transmitter and cause inference with neighboring bands.

#### **2.2 Traditional Receiver**

Traditional wireless receiver development is placed on the other side of the spectrum and they employ active devices that increase sensitivity and data throughput which surpasses what is possible with passive detectors. Receivers architectures can be grouped into three main categories and these architectures are marked as "traditional" or "conventional" architectures due to the fact that their basic structure have not changed substantially even though the implementation has become more complex over the years. A brief overview will be presented on narrowband receivers: To start, ultra wide band architectures are not the best fit for requirements that implements a wake-up application due to the high power consumption and long synchronization times. The most common types of receiver implement a frequency conversion, where the input signal is shifted to a lower frequency, to ease design constraints for signal processing blocks such as gain and filtering. The super-heterodyne architecture shown in Figure 2.3(a) utilizes two separate down conversion operations. First, the input RF signal is amplified by a low noise amplifier (LNA) in order to ease the noise requirements of the rest of the receiver chain. Afterwards the RF signal is converted to the intermediate frequency (IF) with a highaccuracy, tunable local oscillator (LO). This IF signal is amplified and filtered with a low pass filter to remove the image.

(c) Envelope Dectector (uncertain-RF) architecture

Figure 2.2 Block comparison of popular receiver architectures

band and interferers signals. The second mixer converts the signal to DC using a fixed frequency oscillator at the IF frequency.

To avoid the image problem when using Zero-IF and low-IF receivers shown in (Figure 2.2(b)) the RF signal is mixed directly to baseband using quadrature downconversion because in general the two side bands of the RF spectrum are different. The homodyne architecture advantage over the heterodyne is the intermediary IF stages are removed and the need for the IR filter is eliminated. The removal of the IR filter removes the LNA requirement to drive a low impedance load. Similar to the super-heterodyne architecture, an RF LO with high spectral purity and stability is required to drive the mixer. The main drawback of these architectures is their power consumption, along with super-heterodyne, each architecture is fundamentally limited by the RF oscillator and synthesizer. Due to strict frequency accuracy and phase noise performance, each structure requires a resonant LC oscillator which is usually embedded in the phase-locked loop (PLL) circuitry. Because of the limited quality factor (Q) of integrated passives this leads to a power floor of a few milliwatts.

To explore this further, a low-IF receiver implementation described in [7] is considered. To save power, the design eliminated the typical LNA and feeds the RF input directly to the quadrature down-conversion mixers. The mixer consumes DC current due to the mixing circuitry using MOSFET switches as a passive switching network. Following the mixer, the receiver circuits processes the baseband signal at the lower IF frequency (less than 1 MHz), thus these amplifiers consume little power. The last remaining system block is the oscillator which is used to drive the LO port of the mixers.

The oscillator operates near the RF channel frequency with high accuracy and stability, while simultaneously driving the gates of the mixer switches with a large amplitude signal (ideally a square wave). For quadrature operation, the voltage-controlled oscillator (VCO) must provide both in-phase and quadrature outputs. Because of all the responsibility for the LO, the LO results in more than 80% of the overall power consumption in the receiver. Despite the use of a large modulation index to eliminate the need for a complete PLL, the VCO itself still consumes more than 300  $\mu$ W in single-phase, non-quadrature mode. This figure is several times higher than the power budget for the entire WuRx. For the receiver to be implemented for WBAN devices the power devoted to the RF oscillator must be drastically reduced. As an alternative to frequency conversion architectures, the simplest receiver can be implemented with just RF amplification and an energy detector, similar to the first AM receivers. This architecture, also called envelope detection receiver, reduces the power requirement for the LO and moves it to the RF front end (Figure 2.2(c)).

There are two main limitations with the envelope detection architecture, one factor is that the self-mixing operation will be insensitive to phase and frequency, selectivity must be provided through narrowband filtering directly at RF. Second, a high RF gain is necessary to overcome the sensitivity limitations of the envelope detector, usually implemented with a nonlinear element like passive devices or a diode. The envelope receiver is essentially an enhanced implementation of the simple diode rectifiers used in RFID tags, as shown they tend to have poor sensitivity and not adequate for WBAN application. The additional high frequency gain requires too much power, so the

envelope detector receivers usually exhibit inferior sensitivity compared to heterodyne mixing architectures for the equal power consumption. In [22], the authors take advantage of the simplicity of the envelope detector architecture to implement a two-channel receiver at 2 GHz for wireless sensor networks, consuming about 3.5mW. However, more than 80% of the total receiver power is dedicated to the RF gain stages, divided between the LNA at the antenna and the channel-select amplifiers. The journal paper shows the power breakdown and illustrates the critical problem with the architectures: that providing adequate gain at RF usually requires large amounts of power.

One option to enhance gain and improve sensitivity is the use of positive feedback, or regeneration, in the amplifier. This technique was used in the early days of wireless communication to increase the gain available from the vacuum tubes used at the time. A drawback of the technique is that the amount of feedback must be tuned and carefully controlled to enhance the gain without triggering oscillation. The superregenerative architecture circumvents the need for feedback tuning by allowing the amplifier to oscillate at RF, achieving a large amount of gain from a single stage. The resulting high gain preceding the detector improves sensitivity substantially, to better than -100 dBm [23]. The super-regenerative receiver at its core is an envelope detection architecture using a super-regenerative amplifier as an RF gain stage, achieving high performance. The implementation drawback is that a high accuracy LO is now required, with performance requirements similar to those of the frequency conversion architectures described above.

In summary, simple RFID receivers are not sensitive enough for peer-to-peer links, while traditional frequency conversion architectures are inherently limited by LO power consumption. In order to significantly reduce the power of the wake-up receiver, the power contribution of the LO must be reduced.

### 2.3 Technology Considerations

The power and performance of any circuit is influenced by the process technology used for implementation. Choosing the proper technology is always one of the main issues before starting to design a new application. RF CMOS and SiGe BiCMOS are the two promising technologies used in RF/mixed-signal applications. The quality factor of the passives integrated on a Si BJT or CMOS processes are poor compared to the integrated SiGe or GaAs ones. SiGe and BiCMOS process, also have a relatively higher cut-off frequency, fr, and has been preferred over the RFCMOS process for highperformance and low-noise designs most of the time.

However the recent advances in RFCMOS, especially the further shrinking of the FETs, makes conventional CMOS process a rival to previous SiGe generation as far as cut-off frequencies are concerned. Lower power consumption, shorter fabrication time and lower wafer costs further promote the RF CMOS process as the technology of choice for medical implant devices. For sensor network applications, standard digital CMOS integrated circuit (IC) is the only feasible choice for the active circuitry designed. Single-chip integration of digital, analog, and communication circuitry is mandatory to reduce the hardware cost and scaled CMOS is proven to be a good platform for RF circuits as well as digital. For analog and RF design, however, the performance of the active devices

|                         |        | Si     | SiGe   | GaAs    | InGaAs  |

|-------------------------|--------|--------|--------|---------|---------|

|                         | CMOS   | BiCMOS | BiCMOS | MESFET  | НВТ     |

| Feature size            | 0.18µm | 0.4µm  | 0.25µm | 0.5µm   | 3µm     |

| f <sub>T</sub> (GHz)    | 40     | 25     | 75     | 40      | 60      |

| f <sub>max</sub> (GHz)  | 45     | 40     | 75     | 40      | 60      |

| NF <sub>min</sub> @2GHz | 1.2    | 1.1    | 0.9    | 0.5     | 1       |

| Substrate               | 1      | 0      | 10     | × 10000 | > 10000 |

| resistivity<br>(Ohm-cm) | 1      | 8      | 18     | >10000  | >10000  |

| Metal layer             | 6      | 3      | 3      |         |         |

| Inductor(Q)             | 7      | 8      | 15     | 25      | 25      |

**Table 2.1 Performance Comparison of RFIC Technologies**

Performance comparison of RFIC technologies [24]

does not give a complete picture. The quality and implementation of passive devices play an integral role in determining the ultimate limits of gain and power consumption.

# 2.4 Limitations of Integrated Inductors

One of the major limitations of RF integrated circuits is the lack of high Q on chip inductors. Figure 2.3 shows an example of a basic LC tank. For this network the impedance is:

$$Z = \frac{1}{j\omega C + \frac{1}{j\omega L}}$$

(2.2)

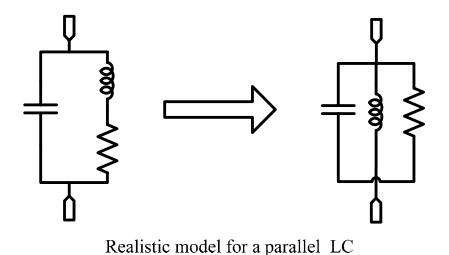

## Figure 2.3 Real Model for a parallel LC

The equation shows that the impedance goes to zero both at DC, the inductor acts as a short and at high frequency the capacitor acts like a short. At low frequencies the networks impedances' is dominated by the inductor and the capacitor dominates at high frequencies. The resonance frequency incurs when the inductive and capacitive parts cancel and this is given by equation 2.3:

$$\omega_0 = \frac{1}{\sqrt{L \cdot C}} \tag{2.3}$$

However pure parallel LC networks are ideal. The inductors tend to be more "lossy" than capacitors and thus the figure shown below presents a more realistic model of an LC tank.

By replacing the LR series section with a parallel one, equating the parallel and series impedance of the LR section:

$$R_{s} + j\omega L_{s} = (R_{p} \parallel j\omega L_{p}) = \frac{(\omega_{0}L_{p})^{2}R_{p} + j\omega_{0}L_{p}R_{p}^{2}}{R_{2}^{p} + (\omega_{0}L_{p})^{2}}$$

(2.4)

By equating the real parts given that  $Q = R_p / \omega_0 L_p = \omega_0 L_s / R_s$  Solving for R<sub>p</sub>:

$$R_p = R_s(Q^2 + 1) (2.5)$$

Equating the imaginary part and solve for  $L_p$ :

$$L_p = L_s \left(\frac{Q^2 + 1}{Q^2}\right) \tag{2.6}$$

For equation 2.4 dominant factor for the frequency of resonance is determined by the series resistance of the inductor and its quality factor Q.

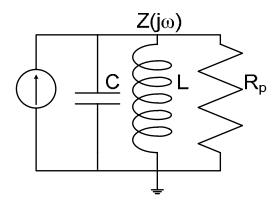

Therefore, in order to maximize gain, the load should be optimized for high impedance. For RF circuits, the load itself is typically implemented with a resonant LC network, where the impedance at resonance is given by:

$$R_p = \omega_0 L Q_L \tag{2.7}$$

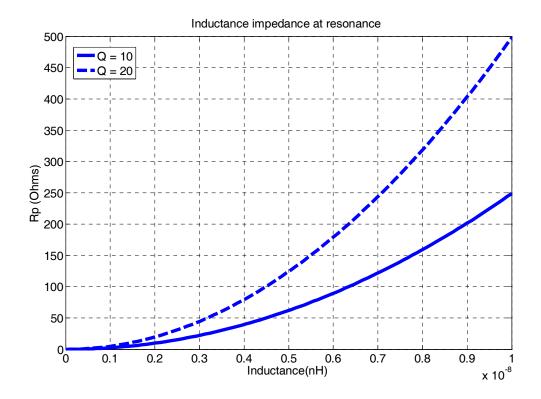

where  $\omega_0$  is the resonant frequency and it is assumed that the network Q is limited by the inductor  $Q_L$ . For on-chip inductors in the low GHz regime,  $R_p$  is practically limited to a few ohms by the size and quality of integrated passives. Figure 2.5 shows the calculated  $R_p$  at 400MHz using Equation 2.2 for inductor quality factors of 10 and 20. Large inductors (10 nH) with quality factors of 10 on chip are considered outstanding, with Q of 15 or 25 possible for smaller inductors [25]. Achieving impedance greater than 1 k $\Omega$  is difficult with integrated inductors especially at UHF frequencies which limits amplifier gain.

Figure 2.4 Inductor impedance at resonance

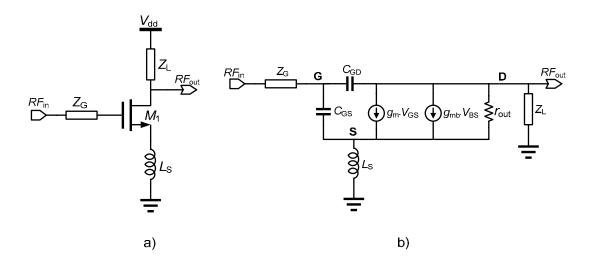

Figure 2.5 Low Noise Amplifier with Source Degeneration

From inspection of the circuit of Figure 2.5 and not considering the effect of  $L_s$  we can obtain that the gain of the low noise amplifier at the frequency of interest, the frequency of resonance, is determined by the impedance of the LC tank and the transconductance  $g_m$  of the input transistor. The obtained gain is expressed by equation:

$$G_{LNA} \propto g_m R_{Load} \tag{2.8}$$

Where  $g_m$  is the transconductance of the transistor  $M_1$  and  $R_{Load}$  is the total parallel resistance of the equivalent circuit. The impedance at resonance is given by

$$R_{LOAD} = R_p = R_s \cdot (Q^2 + 1) = \omega_0 L Q_L$$

(2.9)

$R_{LOAD}$  is practically limited by the size and quality of integrated passives.

As an example, consider a single stage amplifier with source degeneration using 100  $\mu$ A of bias current. The maximum transconductance is then about 2 mS, which yields a gain of 2 with 1 k $\Omega$  load. Much higher gain will be needed to implement an RF receiver, re-enforcing the role of passives components in low power design. However with the advance of technology, scaling has little impact on the limitations of passive components because CMOS processes are optimized for digital performance and low cost, so the metallization used for the inductors must use relatively thin layers, increasing the loss and lowering Q. One of the few benefits of scaling is the continuing trend to add more interconnect layers, which helps move inductors further from the substrate and reduce loss. The logical extension of this concept is to post-process additional thick metal layers, specifically optimized for high quality inductors, on top of completed CMOS wafers. Because the additional layers do not require precision lithography, minimal cost is added to the fabrication process. An example of an "above-IC" inductor was presented

Figure 2.6 Classic LC tank

in[26], using a 5  $\mu$ m thick layer of copper above the CMOS. The combination of thick copper interconnects and larger distance between the coil and substrate results in a measured quality factor of 25 for a2.5nH inductor. Although this is almost a factor of two improvements over standard on-chip inductors, the oscillator using this coil still consumed 400  $\mu$ W of power. This figure is still several times higher than the power consumption target for the entire WuRx, even with the extra processing steps and thick metals. It is therefore unlikely that the  $R_p$  available from LC networks will be improved significantly in future IC technologies.

As an alternative to resonant networks, the load impedance can also be implemented as a wideband resistive load (Figure 2.4). In this case the bandwidth is determined by the load capacitance, which is usually the input device capacitance  $C_d$  of the subsequent stage. In contrast to resonant networks, scaled CMOS technologies excel at reducing device size and capacitance. The result is that, for fixed frequencies, the impedance magnitude attainable from a wideband network is increasing rapidly with technology scaling, far surpassing resonant networks in 90 nm CMOS. Figure 2.6 illustrates this trend, comparing the impedance magnitude of an LC tank with that of transistor input capacitance at 2 GHz. For the LC tank, a very high quality inductor (L=20 nH, Q=15) is assumed to represent a best-case scenario, and as mentioned above, the impedance stays roughly constant as technology scales. In the wideband case, devices in each technology are sized and biased around moderate inversion to provide a transconductance equal to 1 mS, intended to mimic the loading due to a subsequent circuit stage. The impedance magnitude due to device capacitance in modern technologies has exceeded that of high quality resonant tank. To maximize gain, then, wideband amplifiers and active loads are a promising choice in modern CMOS technology.

#### **2.5 Micromechanical Resonators**

The field of wireless communication has dictated the need for new micromechanical RF components capable of multi-frequency low loss filtering and frequency synthesis on the same silicon chip. Because of these advancements as an alternative to on-chip passives and traditional off-chip passive components mounted on the printed circuit board (PCB), radio-frequency micro-electromechanical systems (RF-MEMS) are emerging as a viable option to break the trade-off between integration and quality of passive components. RF-MEMS take advantage of thin-film IC processing techniques to implement high quality resonant structures on the micro scale. Researchers have demonstrated structures with Q factors higher than 10,000 and resonant frequencies up to the low GHz, fabricated using a variety of materials from bulk silicon to diamond and others [27, 28].

Fortunately, the reliability and stability of these research structures are ideal for use in circuit prototypes. For that purpose, this research focuses on a type of MEMS resonator that is already ubiquitous in communication and other electronic applications. However, having a MEMS device that can simultaneously deliver monolithic, post CMOS integration for IF and RF components that can readily interface with 50 Ohm systems is challenging. Thin film piezoelectric aluminum nitride (AIN) based processing technology for RF applications is an emerging technology for realizing mulit-frequency per silicon chip, CMOS-compatible, low-loss filter, reaching to GHz frequencies. The ability to scale the lateral dimension for the structural material, allows for more mechanically robust devices that are capable of attaining lower fundamental resonant (406 MHz) frequencies with reduced motional resistance ( $260\Omega$ ) while maintaining a high Q (1,420). The circuit design techniques developed here to incorporate MEMS resonators will also be applicable to future MEMS devices.

### 2.6 SAW Structure

One common off-chip high quality resonator is the surface acoustic wave (SAW) resonator. It has long provided high performance RF filters with small form factors while showing a continuously declining cost structure. The SAW chip is a piezoelectric single crystal (e.g. quartz, lithium tantalate, lithium niobate), polished on the surface and coated with one or more comb-like, interlocking electrode fingers, so-called interdigital transducers. These usually consist of aluminum and are deposited by photolithographic means. When an electric signal is applied to an electrical transducer, an electrical field is produced between the polarized transducer fingers and, because of the (reverse)

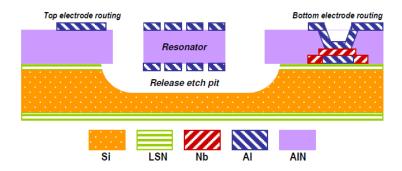

**Figure 2.7 Cross-section and top view of SAW resonator (not to scale)** piezoelectric effect, the chip surface is deformed mechanically. Like tiny seismic waves, a surface acoustic wave spreads out from both sides of the transducer. The reflectors on both sides of the transducer reflect these acoustic waves and thus create a standing wave, which is converted back into an electrical signal at an output transducer (piezoelectric effect). An input piezoelectric transducer uses electrical signals to generate a longitudinal acoustic wave traveling on the surface of the piezoelectric substrate. The basic SAW structure is a thin layer of piezoelectric aluminum nitride (AIN) sandwiched between two metal electrodes and fabricated on a silicon substrate. The whole structure must also be acoustically isolated from the substrate to allow free movement.

There are several variations of SAW resonators, depending mainly on the acoustic isolation method. For this research, we utilize a piezoelectric contour mode MEMS plate resonators which uses an etch pit under the resonator. Figure 2.7 shows the structure of an AlN MEMS resonator, where the resonator is fabricated on a silicon wafer using standard IC processing techniques. The bulk silicon under the resonator is etched away, allowing the structure to vibrate. Because of the novelty of this SAW resonators, its resonant frequency depends on the lateral spacing of the transducer electrodes, the

resonance design effectively uncouples the resonant frequency of the device from their overall dimensions by selectively patterning the transduction electrodes and routing the excitation wave form. Quality factors on the order of several hundred to a few thousand are typical, with resonance frequencies in the low GHz range. The standard IC batch fabrication method also results in low manufacturing cost. The combination of small size and low cost of AlN MEMS technology makes it a good fit for wireless micro-systems where, this technology permits a monolithic integration of post-CMOS compatible, with low-loss filters spanning IF to RF that can readily be interfaced with existing 50 $\Omega$  RF systems [29]. Tolerances can be improved with better manufacturing methods or addressed through laser trimming.

### 2.7 SAW Circuit Model