brought to you by **CORE**

ISSN **2321-807X** Volume 12 Number21 Journal of Advances in chemistry

# AN EFFICIENT ERROR DETECTION AND CORRECTION METHOD FOR TIMING ERRORS

#### M.Revathy, T.Evangeline Santhia

Assistant Professor, Department of Electronics and Communication Engineering, PSNA College of Engineering and Technology, Dindigul-624622, India

#### revathim@psnacet.edu.in

PG scholar, Department of Electronics and Communication Engineering, PSNA College of Engineering and

Technology, Dindigul-624622, India

#### evangelinesanthia2606@gmail.com

### ABSTRACT

Timing errors are an important concern in nanometer CMOS technologies. A promising way to overcome the timing errors is the development of error detection and correction techniques. A local error detection and correction technique is done in this work. It is based on a new bit flipping flip flop. Whenever a timing error is detected, it is corrected by complementing the output of the corresponding flip flop. No extra circuitry is inserted in the design. Timing errors are identified and corrected within a single cycle and hence design complexity is reduced which results in reduced power consumption and low silicon area when compared to the earlier designs.

#### Indexing terms/Keywords

Timing errors, Error detection, Error correction, Bit flipping flip flop.

### **1.INTRODUCTION**

CMOS technology scale down, increase in process variation, the complexness of integrated circuits, many performance degradation mechanisms and reduction in the power supply affect the reliability and set error values[11],[12].

Circuits' noise margins and reliability are affected by the device size scaling, increase in operating frequency and the power supply reduction, Thereby probability of transient fault generation increases. Many times it is hard to achieve error rate specification levels. Timing error generation are mainly due to various mechanisms like crosstalk, power supply disturbance or ground bounce. The increased path delay deviations, due to process variations, and the manufacturing defects that affect circuit speed may also result in timing errors that are not easily detectable in high frequency and high device count ICs. The already complex testing process can not sufficiently use the huge number of paths in modern circuit designs, and thus it cannot effectively find out all timing related defective ICs. A considerable part of defective ICs may escape the fabrication tests. In addition and for similar reasons, timing verification turns to be a tough task escalating the likelihood of timing failures in a design. Furthermore, modern systems running at multiple frequency and voltage levels could suffer from an enhanced timing error rate due to various environmental and method related as well as data dependent variabilities that may have an effect on circuit performance. Besides, dynamic voltage scaling (DVS) techniques for low power operation which reduces power supply voltage with marginal performance degradation have been proposed in the literature. These exploit timing error detection and correction mechanisms to overcome increased timing error rates. In addition, transistor aging problems cosiderably impact the performance of nanometer circuits resulting in the appearance of timing errors during their normal lifetime[13],[14]. Such an example is the Negative Bias Temperature Instability (NBTI) induced aging of PMOS transistors that degrades their threshold voltage in time enhancing path delays [15]. From the on top, it's evident that concurrent on-line testing techniques for timing error detection and correction have become necessary so as to attain acceptable levels of error robustness and meet reliability necessities [16].

In a combinational logic, timing failures are responsible for delayed responses. A delayed response. After the edge triggering of the clock signal that drive the memory elements at the outputs of the combinational block, can result to the generation of timing errors on the information stored within the memory elements. A number of error detection techniques have been proposed in the literature[2],[3],[4],[5],[9],[18][19]. These techniques detect the delayed circuit response and provide error tolerance using time redundancy approach. A well known error detection scheme is based on the use of a comparator which is realized by a simple XOR gate. The monitoring circuitry consists of mux, an XOR gate and a NOT gate for every memory element (flip-flop) in the design. At recent times, transition detectors [8] are used to avail timing error tolerance.

This work presents a reliability aware design technique that provides low power and cost efficient timing error tolerance in nanometer technology small cores designs that are the building blocks for many core system-on-a-chip (SoC) applications. Two error detection techniques to latch based designs are worked out in [10]. A bit flipping flip-flop topology is introduced in this work along with a proper error handling mechanism that provides timing error detection and correction in flip-flop based cores. A pririor version of this process has been presented in [6].

## 2. RELATED WORKS

Timing error detection and correction techniques may be divided into two general categories, they are targeting flip-flop based designs and targeting latch based designs.

## 2.1 Razor technique

A pipeline architecture named razor [1] contains error detection and correction capabilities. It consists of main system flip flop plus an assistant shadow latch, a mux and an XOR gate. The xor gate performs as a comparator and compares the outputs of the main flip flop and the shadow latch. The xor output will rise to high indicating the detection of an error and to low indicating the absence of error. The main advantage in this paper is efficient error detection and correction of errors with energy reduction. Disadvantage is that razor technique suffers from increased silicon area, for every main flip flop an extra latch, a mux and xor gate are required. In addition an extra clock signal is used.

### 2.2 Timber technique

This paper presents TIMBER [20], a technique for online timing error resilience that finds timing errors by borrowing time from successive pipeline stages. TIMBER-based error masking will recover timing margins while ,not instruction replay or roll-back support is used. Two sequential circuit elements—TIMBER flip-flop and TIMBER latch—that implement error masking based on time borrowing are described.

It utilizes an additional latch per main system flip flop. The main advantage of this paper is that it recovers the time margins and improves the performance and power consumption of the circuit design and the drawback is, it requires three extra clock signals plus two control signals for its operation.

### 2.3 Time dilation technique

In this paper, the Time Dilation [7] design technique is proposed that provides error detection and correction technique and also supports off-line manufacturing scan testing. By using a new scan Flip-Flop, the Time Dilation technique is capable to detect and correct many errors at the minimum of one clock cycle delay. The area overhead and the power consumption are reduced, since no additional memory elements are required.

The stage registers are constructed by using the time dilation flip flop, that consists of scan flip flop, a mux and an XOR gate. At the same time, this technique introduces only negligible performance degradation since no extra circuitry is inserted in the critical paths of a design. The main advantage is that it reduces the silicon area overhead and the disadvantage is that number of buffers is increased and consequently silicon area penalty and error tolerance is reduced.

## 2.4 Razor II technique

In this paper, a Razor II [9] design is explained which implements a flip-flop with detection and architectural correction. Error detection is based on flagging spurious transitions in the state-holding latch node. The RazorII based DVS allows removal of safety margins and operation at the first failure of the processor, which exploits a transition detector for error detection while error correction is performed through architectural replay. The main advantage is, it Provides energy efficiency and error tolerance. Disadvantage is its Conflicting power and less performance.

### 2.5 Timing error tolerance in soc applications

Timing error is an increasing reliability concern in nanometer technology, high complexness and multi voltage/ frequency integrated circuits, which is given in the literature [17]. A local error detection and correction system is presented in this paper. It is based on a new bit flipping flip flop. Whenever a timing error is detected, by complementing the output of the flip-flop it is corrected. The proposed solution is characterized by very low silicon area and power requirements compared to previous design. Apart from the original flip flop (Main Flip-Flop), the system consists of two XOR gates and a Latch. The first XOR gate compares the input and output of the Main Flip-Flop and provides the result to the Latch.

The Latch sends the second XOR gate at the output of the Main Flip-Flop. Depending on the comparison result within a particular time interval, either the output of the Main Flip-Flop or its complement is propagated to the final output of the EDC Flip Flop.

### 2.6 Summary

The above discussed papers fail to detect and correct the timing errors more efficiently, also the power consumption, silicon area overhead of the existing systems is more compared to the proposed method .In addition speed of the circuit operation is slow.

### 3.PROPOSED SYSTEM

A new soft and timing error detection circuit delivers fast response times with the use of a MUX and inverter. The proposed flip-flop detects late-arriving data by comparing the input and output of the flip-flop using XOR gate as a comparator. Mux uses the xor output as a selection line and choose either flip flop normal correct output or inverted output.

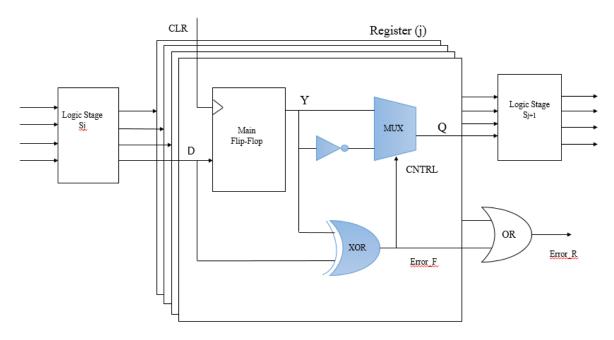

#### Figure 1: Proposed Circuit

That is when the xor gate output is "0" then the comparison output is "low" indicating timing error free condition and so the output of the flip flop is given directly to the next stage of combinational circuit through the 2\*1 MUX. But when the XOR gate output is "1" then the comparison output is high indicating timing error, hence in this condition the output of the flip flop is inverted using NOT gate and gives the corrected output to the next combinational stage. A main characteristic and an advantage of the proposed circuit is that no extra circuitry is inserted in the critical path from the *D* input to the Q output of the Flip-Flop or in the distribution path of the clock signal *CLK*. The additional MUX is inserted in the path which is not critical. The main advantage of the proposed method is that the speed is increased, area is reduced, and the power consumption is decreased. In addition the error tolerance is better when compared to the previous schemes and it is implemented using Xilinx 12.1

## 4.OUTPUT OF THE PROPOSED METHOD

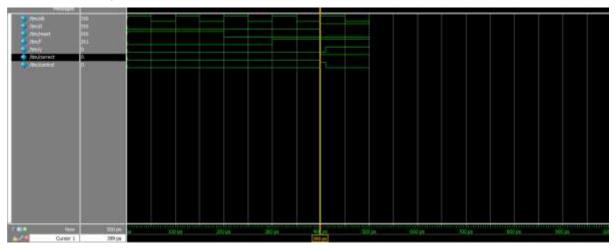

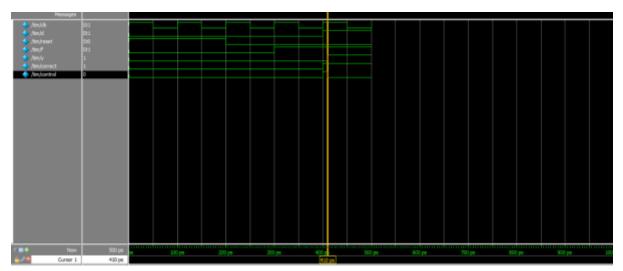

At first *clk*, *d*, *reset and f* are the inputs where *y*, *cntrl* are the intermediate output, *correct* is the final output of the flipflop which is given to the next combinational logic stage. Initially clock is given as positive edge triggering, *d* is the input of the flip flop where it can be given either zero or one here "0" is given first, reset is given "1" for resetting and then "0", fault is initially given as "0" that is fault free condition then checked for faulty condition that is "1"the figure 2 shown below is error detection and the next figure 3 shows the correction of error in the proposed system. When control is "0" there is no detection of error so the output of the flipflop "y"is given to the next combinational stage through MUX and when the control is "1" fault is detected and so the output of the flip flop is inverted through the NOT gate and then given to the the next combinational stage through MUX. Below graph shows the clearly that the error detection and correction is more efficient than the existing methods.

Figure 2: Error detection of the proposed method

#### Figure 3:Error correction of the proposed method

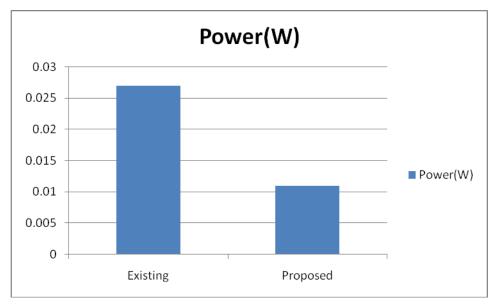

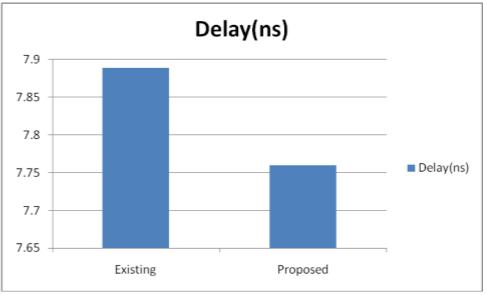

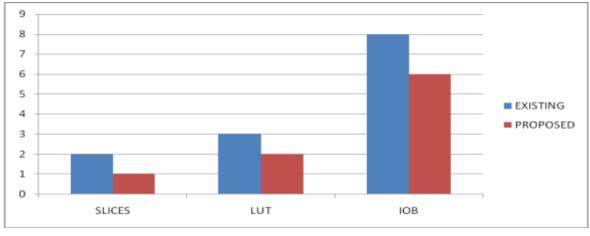

| S.No. | Parameters | Existing method | Proposed method |

|-------|------------|-----------------|-----------------|

| 1.    | Power      | 0.027 watt      | 0.011 watt      |

| 2.    | Area       | 17              | 12              |

| 3.    | Delay      | 7.889 ns        | 7.760 ns        |

#### Table 1:Comparision table

### 4.1 Performance analysis

The graphs given below shows that there is a considerable reduction in time and area based on the implementation results which have been done by using Xilinx ISE 12.1, spartan 6 family. The proposed technique significantly reduces power consumption when compared to the existing system. The power comparison of the existing and proposed is shown in the figure 4 and the comparison chart for area and delay is shown in the figure 5 and figure 6 respectively.

Figure 5:Comparison chart for area

### Figure 6:Comparison chart for delay

The comparison of device utilization summary between existing and proposed method is shown in the figure 7

**5289 |** Page December 2016

## **5.CONCLUSION**

Timing errors are a real concern in modern nanometer CMOS technologies. A promising way to cope with them is the development of error detection and correction techniques. A timing error tolerance technique is presented in this work for enhanced reliability in flip-flop based nanometer technology cores. It exploits a new bit flipping flip-flop, which provides the ability to detect and correct timing errors in a circuit, with a time penalty of a single clock cycle. The proposed approach is characterized by low silicon area requirements and reduced design complexity that also result in reduced power consumption with respect to earlier design schemes.

### **6.FUTURE WORK**

The router is characterised by its design having four directions (North, South, East, West) suitable for a 2-D mesh NOC. The PEs and IPs are connected to any facet of the router. Thus there's no specific connection port for a PE or IP. The proposed detection mechanism can even be applied to NoCs 5 port routers with a port dedicated to an IP. Our proposed efficient error detection and correction technique is employed in router to reduce the timing errors.

#### REFERENCES

- 1. T. Austin, D. Blaauw, T. Mudge, and K. Flautner, "Making typical silicon matter with razor," IEEE Comput., vol. 37, no. 3, pp. 57–65, Mar. 2004.

- 2. Y. Tsiatouhas and Th. Haniotakis, "A zero aliasing built-in self test technique for delay fault testing," in Proc. IEEE Symp. Des.Tes-tability of VLSI Syst., 1999, pp. 95–100.

- 3. L. Anghel and M. Nicolaidis, "Cost reduction and evaluation of temporary faults detecting technique," in Proc. ACM/IEEE Des.Autom. Test Eur. Conf., 2000, pp. 591–598.

- 4. S. Matakias, Y. Tsiatouhas, A. Arapoyanni, and T. H. Haniotakis, "A circuit for concurrent detection of soft and timing errors in digital CMOS ICs," J. Electron. Testing: Theory Appl., vol. 20, no. 5,pp. 523–531, 2004.

- 5. K. Kang, S. P. Park, K. Kim, and K. Roy, "On-chip variability sen-sor using phase-locked loop for detecting and correcting paramet-ric timing failures," IEEE Trans. VLSI Syst., vol. 18, no. 2, pp. 270– 280, Feb. 2010.

- 6. S. Valadimas, Y. Tsiatouhas, and A. Arapoyanni, "Timing error tolerance in nanometer ICs," in Proc. IEEE Int. On-Line Testing Symp., 2010, pp. 283–288.

- 7. A. Floros, Y. Tsiatouhas, and X. Kavousianos, "The time dilation scan architecture for timing error detection and correction," in Proc. IFIP/IEEE Int. Conf. Very Large Scale Integr., 2008, pp. 569–574.

- 8. S. Valadimas, Y. Tsiatouhas, and A. Arapoyanni, "Cost and power efficient timing error tolerance in flip-flop based microprocessor cores," in Proc. IEEE Eur. Test Symp., 2012, pp. 8–13

- S. Das, C. Tokunaga, S. Pant, W-H. Ma, S. Kalaiselvan, K. Lai, D. M. Bull, and D. T. Blaauw, "Razor II: In situ error detection and correction for PVT and SER tolerance," IEEE J. Solid-State Circuits, vol. 44, no. 1, pp. 32–48, Jan. 2009

- 10. K. Bowman, J. W. Tschanz, N.-S.Kim, J. C. Lee, C. B. Wilkerson, S.-L. Lu, T. Karnik, and V. K. De, "Energyefficient and metastability-immune resilient circuits for dynamic variation tolerance," IEEE J. Solid-State Circuits, vol. 44, no. 1, pp. 49–63, Jan. 2009.

- 11. J. W. McPherson, "Reliability challenges for 45 nm and beyond,"in Proc. ACM/IEEE Des. Autom. Conf., 2006, pp. 176–181.

- 12. S. Mitra, N. Seifert, M. Zhang, Q. Shi, and K. S. Kim, "Robust system design with built-in soft-error resilience," IEEE Comput.,vol. 38, no. 2, pp. 43–52, Feb. 2005.

- 13. M. Agarwal, B. C. Paul, M. Zhang, and S. Mitra, "Circuit failure prediction and its application to transistor aging," in Proc. IEEE VLSI Test Symp., 2007, pp. 277–284.

- 14. M. Agarwal, V. Balakrishnan, A. Bhuyan, K. Kim, B. C. Paul, W.Wang, B. Yang, Y. Cao, and S. Mitra, "Optimized circuit failure prediction for aging: Practicality and promise," in Proc. IEEE Int.Test Conf., 2008, pp. 1–10.

- 15. S.P.Park, K. Roy, and K. Kang, "Reliability implications of bias temperature instability in digital ICs," IEEE Des.TestComput.,vol.23,no.6,pp.8–17,Nov.2009.

- 16. Y. Makris, I. Bayraktaroglou, and A. Orailoglou, "Enhancing reliability of RTL controller-data path circuits via invariant-based concurrent test," IEEE Trans. Rel., vol. 53, no. 2, pp. 269–278, Jun. 2004.

- M. Nicolaidis and Y. Zorian, "On-Line Testing for VLSI—A compendium of approaches," J. Electron. Testing: Theory Appl., vol. 12, no. 1/2, pp. 7–20, 1998.

- 18. C. Metra, R. Degiampietro, M. Favalli, and B. Ricco, "Concurrent detection and diagnosis scheme for transient, delay and crosstalk faults," in Proc. IEEE Int. On-Line Testing Workshop, 1999,pp. 66–70.

- M. Nicolaidis, "Time redundancy based soft-error tolerance to rescue nanometer technologies," in Proc. IEEE VLSI Test Symp., 1999, pp. 86–94.

- 20. H. Yu, M. Nicolaidis, L. Anghel, and N-E. Zergainoh, "Efficient fault detection architecture design of latch-based low power DSP/MCU processor," in Proc. IEEE Eur. Test Symp., 2011,pp. 177–183.

## Author' biography with Photo

**M.Revathy** working as an Assistant Professor in the department of Electronics and Communication Engineering at PSNA College of Engineering and Technology has a working experience of about ten years. She had graduated from Madurai Kamaraj University in 1996 and had completed her master's degree in VLSI design from Anna University, Chennai in 2007.She had obtained her doctoral degree from Anna University, Chennai in 2015.She had published papers in many referred journals and has guided around 15 M.E. Scholars. Her research interests include VLSI architectures, Error detection and Error correction codes, Low power VLSI etc.

**T.Evangeline santhia** received her B.E in Electronics and Communication Engineering degree from PSNA College of Engineering and Technology, Dindigul in 2015 and pursuing M.E (VLSI Design) in PSNA College of Engineering and Technology, Dindigul.