# Asynchronous Sequential Symbol Synchronizers based on Pulse Comparison by Both Transitions at Half Bit Rate

Antonio D. Reis, Jose F. Rocha, A. S. Gameiro and Jose P. Carvalho

*Abstract*— This work studies the asynchronous sequential symbol synchronizers based on pulse comparison by both transitions at half bit rate. Their performance will be compared with the reference asynchronous symbol synchronizers based on pulse comparison by both transitions at bit rate.

For the reference and proposed variants, we consider two versions which are the manual (m) and the automatic (a).

The objective is to study the four synchronizers and evaluate their output jitter UIRMS (Unit Interval Root Mean Square) versus input SNR (Signal Noise Ratio).

Index Terms—Synchronism, Digital Communications

## I. INTRODUCTION

This work studies the asynchronous sequential symbol synchronizer based on pulse comparison operating by both transitions at half bit rate (ab/2). Their jitter is compared with the reference asynchronous synchronizers operating by both transitions at bit rate (ab) [1, 2].

For both, reference and proposed variant, we consider the versions manual (m) and automatic (a) [3, 4, 5, 6, 7].

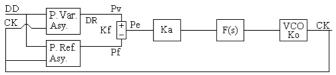

The difference between the reference and proposed synchronizer is in the symbol phase comparator since the others blocks are similar. The phase comparator compares the input variable pulse duration Pv with the intern reference fixed pulse duration Pf and the error pulse Pe synchronizes the VCO (Voltage Controlled Oscillator) [8, 9].

The synchronizer regenerates the data, recovering a clock (VCO) that samples and retimes the data [10, 11, 12, 13].

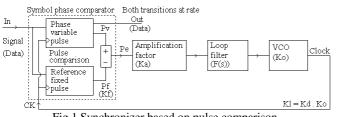

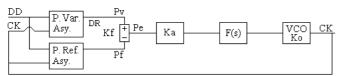

Fig.1 shows the blocks of the general symbol synchronizer.

Fig.1 Synchronizer based on pulse comparison

Kf is the phase comparator gain, F(s) is the loop filter, Ko is the VCO gain and Ka is the loop amplification factor that controls the root locus and then the loop characteristics.

Manuscript received March 21, 2014; Supports from UBI and FCT.

A. D. Reis is with the University of Beira Interior Covilha and Remote Detection Unit, Portugal (e-mail: adreis@ ubi.pt).

J. F. Rocha is with the University of Aveiro and Institute of Telecommunications, Portugal (e-mail: frocha@ ua.pt).

A. S. Gameiro is with the University of Aveiro and Institute of Telecommunications, Portugal (e-mail: amg@ ua.pt).

J. P. Carvalho is with the University of Beira Interior Covilha and Remote Detection Unit, Portugal (e-mail: pacheco@ ubi.pt).

In priori and actual-art state was developed various synchronizers, now is necessary to know their performance.

The motivation of this work is to create new synchronizers and to evaluate their performance with noise. This contribution increases the knowledge about synchronizers.

Following, we present the reference variant, asynchronous sequential symbol synchronizers based on pulse comparison by both transitions at bit rate, with versions manual (ab-m) and automatic (ab-a). Next, we present the proposed variant, asynchronous sequential symbol synchronizer based on pulse comparison by both transitions at half bit rate, with versions manual (ab-m/2) and automatic (ab-a/2).

After, we present the design and tests. Then, we present the results. Finally, we present the conclusions.

# II. REFERENCE BY BOTH AT BIT RATE

The standard reference, asynchronous sequential symbol synchronizers based on pulse comparison operating by both transitions at bit rate has two versions, which are the manual (ab-m) and the automatic (ab-a) [1, 2].

The versions difference is in the phase comparator, the variable pulse Pv is common but the fixed Pf is different.

## A. Reference by both at rate manual (ab-m)

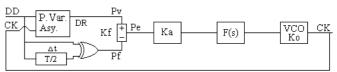

The block Pv, shown below, produces a variable pulse Pv between the input bits and VCO. The manual adjustment delay with Exor produces a manual fixed pulse Pf (Fig.2).

Fig.2 Asynchronous by both at rate and manual (ab-m)

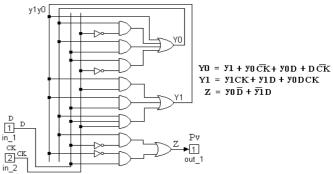

The comparison between the pulses Pv and Pf provides the error pulse Pe that forces the VCO to synchronize the input. The block Pv is an asynchronous circuit (Fig.3).

Fig.3 Intern aspect of the block Pv

Proceedings of the World Congress on Engineering 2014 Vol I, WCE 2014, July 2 - 4, 2014, London, U.K.

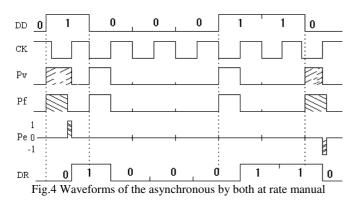

Fig.4 shows the waveforms of the reference manual (equal to the corresponding synchronous version) [3].

The error pulse Pe diminishes during the synchronization time and disappear at the equilibrium point.

#### B. Reference by both at rate automatic (ab-a)

The block Pv, common with anterior, produces the variable pulse Pv between input and VCO. The block Pf, shown below, produces the comparison fixed pulse Pf (Fig.5).

Fig.5 Asynchronous by both at rate and automatic (ab-a)

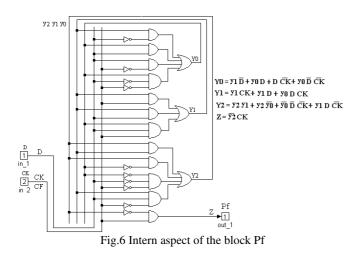

The comparison between the pulses Pv and Pf provides the error pulse Pe that forces the VCO to follow the input. The block Pf is an asynchronous circuit (Fig.6).

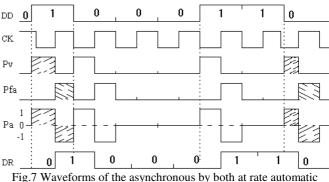

Fig.7 shows the waveforms of the reference automatic (equal to the corresponding synchronous version) [3].

The error pulse Pe don't disappear, but the variable area Pv is equal to the fixed Pf at the equilibrium point.

#### III. PROPOSED BY BOTH AT HALF BIT RATE

The proposed, asynchronous sequential symbol synchronizers based on pulse comparison operating by both transitions at half bit rate has also two versions namely the manual (ab-m/2) and the automatic (ab-a/2) [3, 4].

The versions difference is in the phase comparator, the variable pulse Pv is common but the fixed Pf is different.

## A. Proposed by both at half rate manual (ab-m/2)

The block Pv produces the variable pulse Pv between input transitions and VCO. The manual adjustment delay T/2 with Exor produces a fixed pulse Pf (Fig.8).

Fig.8 Asynchronous by both at half rate and manual (ab-m/2)

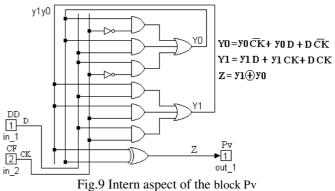

The comparison between pulses Pv and Pf provides the error pulse Pe that forces the VCO to synchronize the input. The block Pv is an asynchronous circuit (Fig.9).

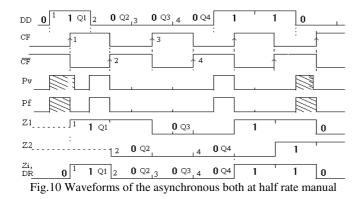

Fig.10 shows the waveforms of the proposed manual (equal to the corresponding synchronous version) [3].

Proceedings of the World Congress on Engineering 2014 Vol I, WCE 2014, July 2 - 4, 2014, London, U.K.

The error pulse Pe diminishes during the synchronization time and disappear at the equilibrium point.

#### B. Proposed by both at half rate automatic (ab-a/2)

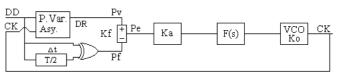

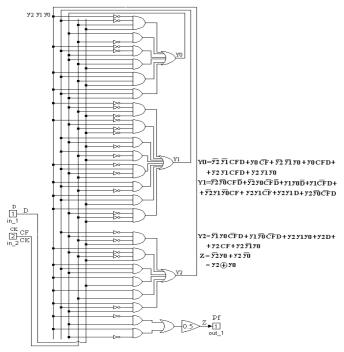

The block Pv, common, produces the variable pulse Pv between input and VCO. The block Pf, shown below, produces the comparison fixed pulse Pf (Fig.11).

Fig.11 Asynchronous by both at half rate and automatic (ab-a/2)

The comparison between the pulses Pv and Pf provides the error pulse Pe that forces the VCO to follow the input. The block Pf is an asynchronous circuit (Fig.12).

Fig.12 Intern aspect of the block Pf

Fig.13 shows the waveforms of the proposed automatic (equal to the corresponding synchronous version) [3].

Fig.13 Waveforms of the asynchronous both at half rate automatic

The error pulse Pe don't disappear, but the variable area Pv is equal to the fixed Pf at the equilibrium point.

#### IV. DESIGN, TESTS AND RESULTS

We present the design, tests and results of the various synchronizers [5].

#### A. Design

To have guaranteed results, is necessary to dimension all the synchronizers with equal conditions. Then, the loop gain Kl=KdKo=KaKfKo must be equal in all the synchronizers. The phase detector gain Kf and the VCO gain Ko are fixed. Then, the loop gain amplification Ka controls the root locus and consequently the loop characteristics.

For analysis facilities, we use normalized values for the transmission rate tx=1baud, clock frequency fCK=1Hz, extern noise bandwidth Bn=5Hz and loop noise bandwidth Bl=0.02Hz. Then, we apply a signal power Ps=  $A_{ef}^2$  and a noise power Pn= No=  $2\sigma n^2 \Delta \tau$ , where  $\sigma n$  is the noise standard deviation and  $\Delta \tau = 1/f$ Samp is the sampling period. The relation between SNR and noise variance  $\sigma n^2$  is

$SNR = A_{ef}^{2} / (No.Bn) = 0.5^{2} / (2\sigma n^{2} * 10^{-3} * 5) = 25/\sigma n^{2}$ (1) Now, for each synchronizer, is necessary to measure the output jitter UIRMS versus the input SNR

We use a cutoff loop filter F(s)=0.5Hz, which is 25 times greater than Bl=0.02Hz, what eliminates the high frequency, but maintains the loop characteristics. The transfer function is  $C(s) = \frac{K_2 K_2 E(s)}{K_2 E(s)} = \frac{K_2 K_2 E(s)}{K_2 E(s)}$

$$H(s) = \frac{G(s)}{1 + G(s)} = \frac{KaKoF(s)}{s + KdKoF(s)} = \frac{KaKo}{s + KdKo}$$

(2)

the loop noise bandwidth is

Bl =

$$\frac{KaKo}{4} = Ka \frac{KJKo}{4} = 0.02Hz$$

(3)

So, with (Km=1, A=1/2, B=1/2, Ko= $2\pi$ ) and loop bandwidth Bl=0.02, we obtain respectively the Ka, for analog, hybrid, combinational and sequential synchronizers, then

$$Bl = (Ka.Kf.Ko)/4 = (Ka.Km.A.B.Ko)/4 \rightarrow Ka = 0.08*2/\pi$$

(4)

$$Bl = (Ka.Kf.Ko)/4 = (Ka.Km.A.B.Ko)/4 -> Ka = 0.08 * 2.2/\pi$$

(5)

$$Bl = (Ka.Kf.Ko)/4 - (Ka*1/\pi*2\pi)/4 -> Ka = 0.04$$

(6)

$$Bl = (Ka.Kf.Ko)/4 = (Ka^{*1}/\pi^{*2}\pi)/4 -> Ka = 0.04$$

(6)

$$Bl = (Ka.Kf.Ko)/4 = (Ka^{*1}/2\pi^{*2}\pi)/4 -> Ka = 0.08$$

(7)

$\sigma_{\phi}^2 = Bl.No/Aef^2 = 0.02*10^{-3}*2\sigma n^2/0.5^2 = 16*10^{-5}.\sigma n^2$  (8) For the others PLLs, the jitter formula is more complicated.

## - 2<sup>nd</sup> order loop:

Is not used here, but provides similar results.

Proceedings of the World Congress on Engineering 2014 Vol I, WCE 2014, July 2 - 4, 2014, London, U.K.

#### B. Tests

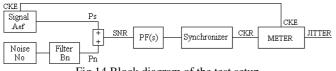

We used the following setup to test synchronizers (Fig.14)

Fig.14 Block diagram of the test setup

The receiver recovered clock with jitter is compared with the emitter original clock, the difference is the jitter.

#### C. Results

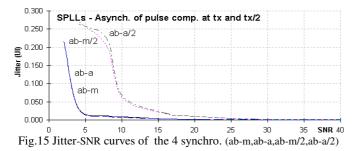

We present the results in terms of output jitter UIRMS versus input SNR. Fig.15 shows the jitter - SNR curves of the four synchronizers which are the both rate manual (ab-m), the both rate automatic (ab-a), the both half rate manual (ab-m/2) and the both half rate automatic (ab-a/2).

We observe that, in general, the output jitter UIRMS decreases gradually with the input SNR increasing.

We verify that, for high SNR, the four jitter curves tend to be similar. However, for low SNR, the variant asynchronous both at rate manual (ab-m) and automatic (ab-a) are better than the variant asynchronous both at half rate manual (ab-m/2) and automatic (ab-a/2).

#### V. CONCLUSIONS

We studied four synchronizers involving the reference variant asynchronous by both transitions at bit rate with versions manual (ab-m) and automatic (ab-a) and the proposed variant asynchronous by both transitions at half bit rate with versions manual (ab-m/2) and automatic (ab-a/2). Then, we tested and compared their jitter - SNR curves.

We observed that, in general, the output UIRMS jitter curves decrease gradually with the input SNR increasing.

We verified that, for high SNR, the four synchronizers jitter curves tend to be similar, this is comprehensible since all the synchronizers are digital, with equal noise margin. However, for low SNR, the variant asynchronous by both at rate with their versions manual (ab-m) and automatic (ab-a) are better than the variant asynchronous by both at half rate with their versions manual (ab-m/2) and automatic (ab-a/2), this is comprehensible because the variant by both transitions at rate has minus states than the variant by both transitions at half rate, and then, the time to pass from the error state to the correct state is lesser.

In the future, we are planning to extend the present study to other types of synchronizers.

## ACKNOWLEDGMENTS

The authors are grateful to the program FCT (Foundation for sCience and Technology) / POCI2010.

## REFERENCES

- J. C. Imbeaux, "performance of the delay-line multiplier circuit for clock and carrier synchronization", IEEE Jou. on Selected Areas in Communications p.82 Jan. 1983.

- [2] Werner Rosenkranz, "Phase Locked Loops with limiter phase detectors in the presence of noise", IEEE Trans. on Communications com-30 N°10 pp.2297-2304. Oct 1982.

- [3] H. H. Witte, "A Simple Clock Extraction Circuit Using a Self Sustaining Monostable Multivibrat. Output Signal", Electronics Letters, Vol.19, Is.21, pp.897-898, Oct 1983.

- [4] Charles R. Hogge, "A Self Correcting Clock Recovery Circuit", IEEE Tran. Electron Devices p.2704 Dec 1985.

- [5] A. D. Reis, J. F. Rocha, A. S. Gameiro, J. P. Carvalho "A New Technique to Measure the Jitter", Proc. III Conf. on Telecommunications pp.64-67 FFoz-PT 23-24 Apr 2001.

- [6] Marvin K. Simon, William C. Lindsey, "Tracking Performance of Symbol Synchronizers for Manchester Coded Data", IEEE Transactions on Communications Vol. com-2.5 N°4, pp.393-408, April 1977.

- [7] J. Carruthers, D. Falconer, H. Sandler, L. Strawczynski, "Bit Synchronization in the Presence of Co-Channel Interference", Proc. Conf. on Electrical and Computer Engineering pp.4.1.1-4.1.7, Ottawa-CA 3-6 Sep. 1990.

- [8] Johannes Huber, W. Liu "Data-Aided Synchronization of Coherent CPM-Receivers" IEEE Transactions on Communications Vol.40 N°1, pp.178-189, Jan. 1992.

- [9] Antonio D'Amico, A. D'Andrea, Reggianni, "Efficient Non-Data-Aided Carrier and Clock Recovery for Satellite DVB at Very Low SNR", IEEE Jou. on Sattelite Areas in Comm. Vol.19 N°12 pp.2320-2330, Dec. 2001.

- [10] Rostislav Dobkin, Ran Ginosar, Christos P. Sotiriou "Data Synchronization Issues in GALS SoCs", Proc. 10th International Symposium on Asynchronous Circuits and Systems, pp.CD-Ed., Crete-Greece 19-23 Apr. 2004.

- [11] N. Noels, H. Steendam, M. Moeneclaey, "Effectiveness Study of Code-Aided and Non-Code-Aided ML-Based Feedback Phase Synchronizers", Proc. IEEE Int Conf. on Comm.(ICC'06) pp.2946-2951, Ist.-TK, 11-15 Jun 2006.

- [12] A. D. Reis, J. F. Rocha, A. S. Gameiro, J. P. Carvalho "Sequential Symbol Synchronizers based on Clock Sampling of Discrete Pulses", Proc. VIII Symposium on Enabling Optical Network and Sensors (SEONs) p.CD-Edited, Porto-PT 25-25 June 2010.

- [13] A. D. Reis, J. F. Rocha, A. S. Gameiro, J. P. Carvalho "Optical Digital Communication Systems and Synchronism", Proc. 7th UBI International Conference on Engeneering (for Economic Development) - ICEUBI 2013, pp. CT8-11.7, Covilhã-PT 27-29 November 2013.