#### Tiago Emanuel Urze Afonso

FPGA e sistemas embutidos multi-core para processamento de vídeo

FPGA and multi-core embedded systems for video processing

#### Tiago Emanuel Urze Afonso

# FPGA e sistemas embutidos multi-core para processamento de vídeo

# FPGA and multi-core embedded systems for video processing

Dissertação apresentada à Universidade de Aveiro para cumprimento dos requesitos necessários à obtenção do grau de Mestre em Engenharia Eletrónica e Telecomunicações, realizada sob a orientação científica do Doutor Pedro Nicolau Faria Fonseca (orientador), professor auxiliar do departamento de Eletrónica, Telecomunicações e Informática da Universidade de Aveiro, e do Doutor Manuel Bernardo Salvador Cunha (coorientador), professor assistente do Departamento de Eletrónica, Telecomunicações e Informática da Universidade de Aveiro.

#### o júri / the jury

| presidente / president       | <b>Prof. Doutor Arnaldo Silva Rodrigues de Oliveira</b><br>Professor Auxiliar da Universidade de Aveiro (por delegação da Reitora da Univer-<br>sidade de Aveiro)                                                    |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vogais / examiners committee | <b>Prof. Doutor Hélio Mendes de Sousa Mendonça</b><br>Professor Auxiliar do Departamento de Engenharia Eletrotécnica e de Computa-<br>dores da Faculdade de Engenharia da Universidade do Porto (Arguente Principal) |

|                              | Prof. Doutor Manuel Bernardo Salvador Cunha                                                                                                                                                                          |

Professora Auxiliar do Departamento de Eletrónica, Telecomunicações e Informática da Universidade de Aveiro (Co-orientador)

# agradecimentos / acknowledgements

Gostava de agradecer em primeiro lugar aos meus pais e irmão, que me apoiaram incondicionalmente ao longo de todo este processo de formação no ensino superior e que constituiram um pilar muito importante na minha educação, acreditando sempre nas minhas capacidades. À Natasa, por toda a paciência que teve nas horas sem fio que me ouviu a falar do tema, e por todo o apoio, incentivo e confiança que sempre depositou em mim. Aos meus colegas e amigos em geral que me acompanharam ao longo deste percurso académico e comigo partilharam horas a fio de trabalho. Ao meu orientador, co-orientador e colaborador pela ajuda na escrita deste documento, nomeadamente pela sua contribuição científica, demonstrando sempre disponibilidade para ajudar. Por fim, a todos os outros a quem a memória me esteja a falhar.

palavras-Chave FPGA, visão artificial, deteção de contornos, Canny, análise morfológica de imagem, VHDL, CAMBADA, dispositivos lógicos programáveis, lógica reprogramável, vídeo, processamento em paralelo, ipCores O presente trabalho apresenta técnicas de processamento digital de sinal, resumo nomeadamente em processamento de vídeo, recorrendo à tecnologia FPGA. Consiste numa introdução teórica sobre tópicos tais como o papel da visão artifical nos dias de hoje, reconhecimento de imagem, e técnicas matemáticas de processamento e análise morfológica de imagem. Aborda o tema do papel das FPGAs na tecnologia actual, e as suas vantagens quando utilizadas no processamento digital de sinal. Finalmente é demonstrado e explicado o algoritmo implementado na FPGA para deteção de contornos no processamento de vídeo, concluindo com uma análise a nível da sua eficiência, e discussão de melhorias a fazer num possível trabalho futuro em termos de otimização de recursos utilizados e velocidade de processamento.

| Keywords | FPGA, artificial vision, Canny, morphological image analysis, VHDL, CAM-<br>BADA, programmable logic devices, reprogrammable logic, video, parallel<br>processing, ipCores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Abstract | The present work presents techniques of digital signal processing, namely<br>in video processing, using FPGA technology. It consists of a theoretical in-<br>troduction about topics such as the role of artificial vision nowadays, image<br>recognition and mathematical techniques of image processing and morpho-<br>logical analysis. It discusses the role of an FPGA in today's technology and<br>its advantages when used in digital signal processing. Finally, it is demon-<br>strated and explained the algorithm that was implemented in the FPGA for<br>edge detection in video processing, concluding with an analysis in terms of<br>efficiency, and discussion of improvements to do in a possible future work<br>regarding the optimization of used resources and also of its processing speed. |

# Contents

| $\mathbf{C}$ | onter | nts    |                                                                                                             | i  |

|--------------|-------|--------|-------------------------------------------------------------------------------------------------------------|----|

| Li           | st of | Figure | es                                                                                                          | v  |

| A            | crony | yms    |                                                                                                             | ix |

| 1            | Intr  | oducti | on                                                                                                          | 1  |

|              | 1.1   | Comp   | uter Vision: A modern reality                                                                               | 1  |

|              | 1.2   | Goals  |                                                                                                             | 2  |

| <b>2</b>     | Rec   | onfigu | rable Computing                                                                                             | 4  |

|              | 2.1   | Introd | uction                                                                                                      | 4  |

|              | 2.2   | Progra | ammable Logic vs Fixed Logic                                                                                | 5  |

|              | 2.3   | FPGA   | vs CPLDs                                                                                                    | 6  |

|              | 2.4   | FPGA   | state-of-art                                                                                                | 6  |

|              |       | 2.4.1  | Programmable Logic blocks                                                                                   | 7  |

|              |       | 2.4.2  | Programmable Interconnect                                                                                   | 7  |

|              |       | 2.4.3  | Programmable I/O                                                                                            | 8  |

|              |       | 2.4.4  | Block RAM vs Distributed RAM $\ldots$                                                                       | 8  |

|              |       | 2.4.5  | Modern market of FPGA                                                                                       | 13 |

|              | 2.5   | FPGA   | Design Flow and Design methods / approaches $\ldots \ldots \ldots \ldots$                                   | 18 |

|              |       | 2.5.1  | Methods                                                                                                     | 18 |

|              |       | 2.5.2  | Design Flow                                                                                                 | 18 |

|              |       | 2.5.3  | Design Entry / Synthesis                                                                                    | 19 |

|              |       | 2.5.4  | Design Implementation $\ldots \ldots \ldots$ | 21 |

|              |       | 2.5.5  | Device downloading / programming $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                  | 22 |

|              |       | 2.5.6  | Programming approaches                                                                                      | 22 |

|          |     | 2.5.7 IP (Intellectual Property) Cores                                  | 23 |

|----------|-----|-------------------------------------------------------------------------|----|

|          | 2.6 | Development board (Genesys Virtex-5 LX50T FPGA Development Board) $~$ . | 25 |

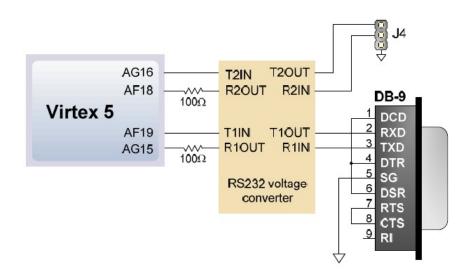

|          |     | 2.6.1 Adept System Serial Port                                          | 26 |

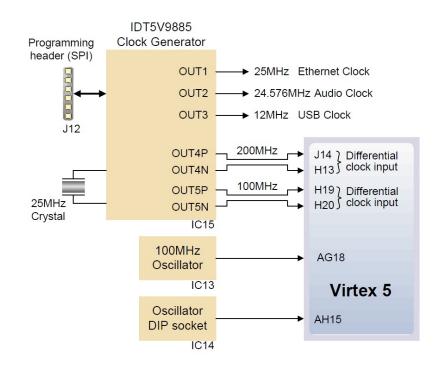

|          |     | 2.6.2 Oscillators/Clocks                                                | 26 |

|          | 2.7 | VHDL                                                                    | 27 |

|          |     | 2.7.1 History                                                           | 27 |

|          |     | 2.7.2 Design Cycle                                                      | 28 |

|          |     | 2.7.3 The Standardisation Process                                       | 30 |

|          |     | 2.7.4 Portability                                                       | 31 |

|          | 2.8 | Conclusions                                                             | 31 |

| 3        | Cor | puter Vision                                                            | 33 |

|          | 3.1 | Introduction                                                            | 33 |

|          |     | 3.1.1 Image - The base of vision                                        | 33 |

|          |     | 3.1.2 Computer vision backbone – image processing                       | 34 |

|          | 3.2 | Image Enhancement                                                       | 35 |

|          |     | 3.2.1 Anisotropic diffusion                                             | 35 |

|          | 3.3 | Image Segmentation and Edge detection                                   | 38 |

|          |     | 3.3.1 Edge Detection                                                    | 40 |

|          |     | 3.3.2 Canny Edge Algorithm                                              | 43 |

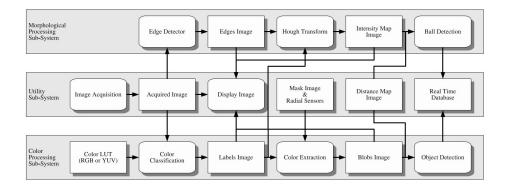

|          | 3.4 | CAMBADA Vision System Software Architecture                             | 52 |

| 4        | FPO | A Circuit Design and Development                                        | 54 |

|          | 4.1 | Introduction                                                            | 54 |

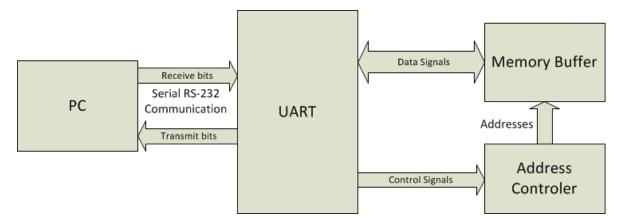

|          | 4.2 | Serial Communication                                                    | 55 |

|          | 4.3 | Canny's Circuit Design                                                  | 58 |

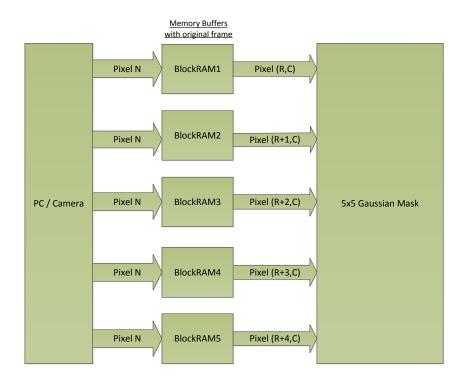

|          |     | 4.3.1 Smoothing Filter                                                  | 59 |

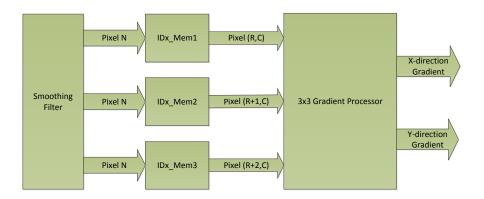

|          |     | 4.3.2 Finding Gradients                                                 | 63 |

|          |     | 4.3.3 Non-Maximum Suppression                                           | 66 |

|          |     | 4.3.4 Double Thresholding and Edge Linking                              | 69 |

|          | 4.4 | FPGA Statistics and Design optimization techniques                      | 72 |

|          |     | 4.4.1 Optimization Techniques                                           | 72 |

| <b>5</b> | Cor | clusions and Future Work                                                | 77 |

|          | 5.1 | Future Work                                                             | 78 |

#### Bibliography

# List of Figures

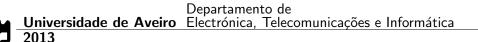

| 2.1  | Built-in overview of an <i>Field-Programmable Gate Array</i> (FPGA)           | 7  |

|------|-------------------------------------------------------------------------------|----|

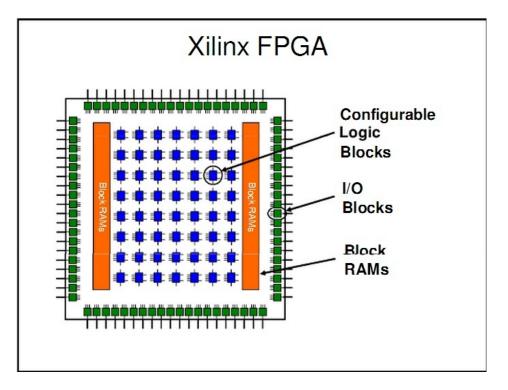

| 2.2  | Dual-port Random Access Memory (RAM) scheme                                   | 8  |

| 2.3  | Arrangement of a slice within the CLB [13]                                    | 10 |

| 2.4  | Diagram of a SLICEM [13]                                                      | 11 |

| 2.5  | Diagram of a SLICEL [13]                                                      | 12 |

| 2.6  | VirteX-5 FPGA Feature Summary [13]                                            | 14 |

| 2.7  | FPGA Market (July 2011) [6]                                                   | 15 |

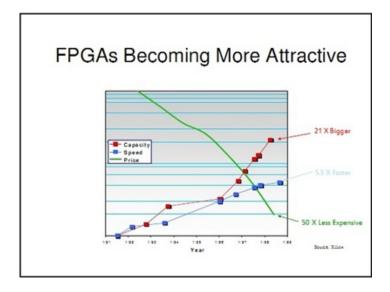

| 2.8  | Evolution of price (green line), capacity (red line) and speed (blue line) of |    |

|      | FPGAs from 1991 to 1999                                                       | 17 |

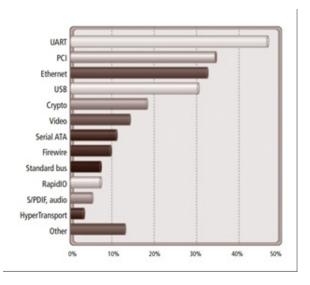

| 2.9  | Most usual applications in 2005, where embedded processors were required [21] | 17 |

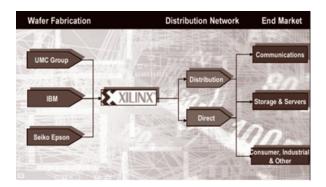

| 2.10 | XILINXMarket [21]                                                             | 18 |

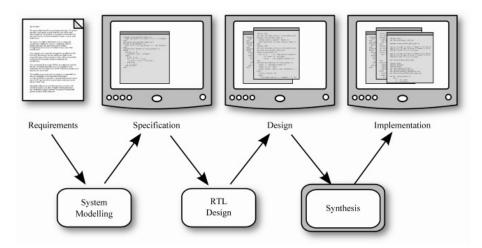

| 2.11 | FPGA graphic design flow[15]                                                  | 19 |

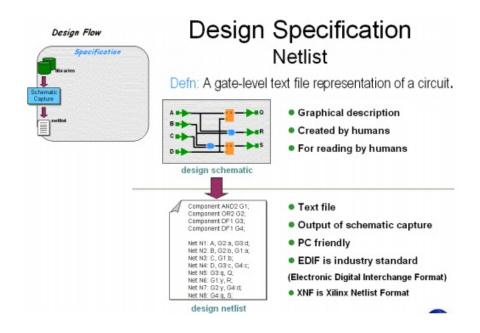

| 2.12 | Design Specification netlist [15]                                             | 20 |

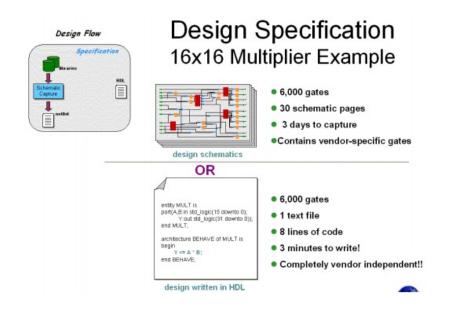

| 2.13 | Design Specification 16x16 multiplexer - HDL vs Schematics [15] $\ldots$      | 21 |

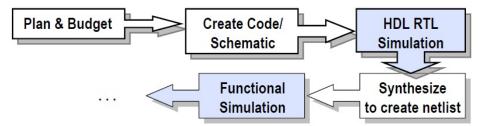

| 2.14 | FPGA Design Entry flow [15]                                                   | 21 |

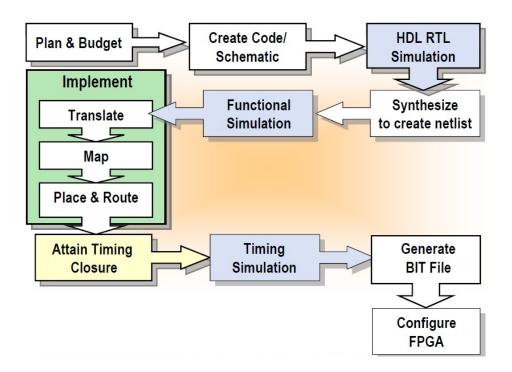

| 2.15 | Xilinx FPGA Design Flow                                                       | 23 |

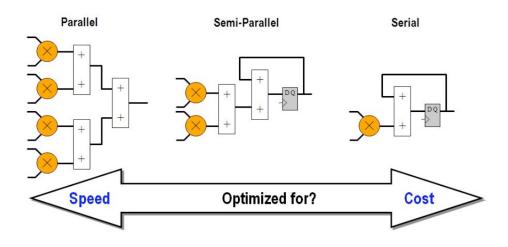

| 2.16 | Illustration of the speed/area trade-off in FPGAs                             | 24 |

| 2.17 | Genesys Virtex-5 FPGA Development board [17]                                  | 25 |

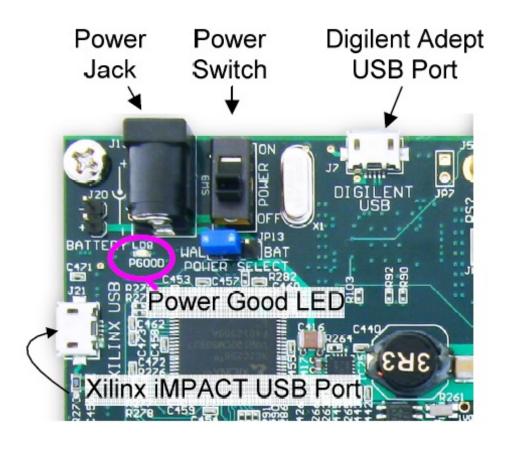

| 2.18 | Digilent Power plug-in, on button and USB programming port $[17]$             | 27 |

| 2.19 | Adept system Serial port                                                      | 28 |

| 2.20 | Genesys Clock System [17]                                                     | 29 |

| 2.21 | The Very High-Speed Integrated Circuits Hardware Description Language (VHDL)  | -  |

|      | based hardware design cycle                                                   | 30 |

|      |                                                                               |    |

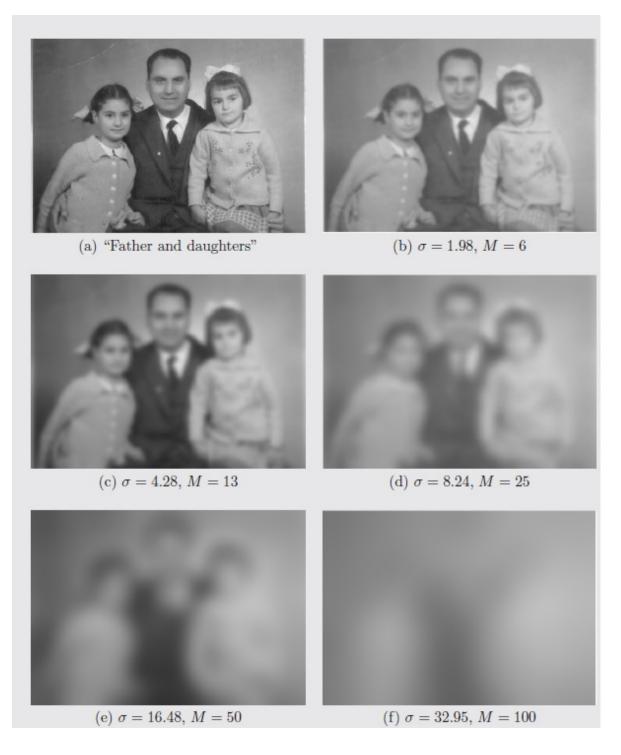

<sup>3.1</sup> As filter scale increases, less information remains. Filter used has size (2M+1)x(2M+1) 36

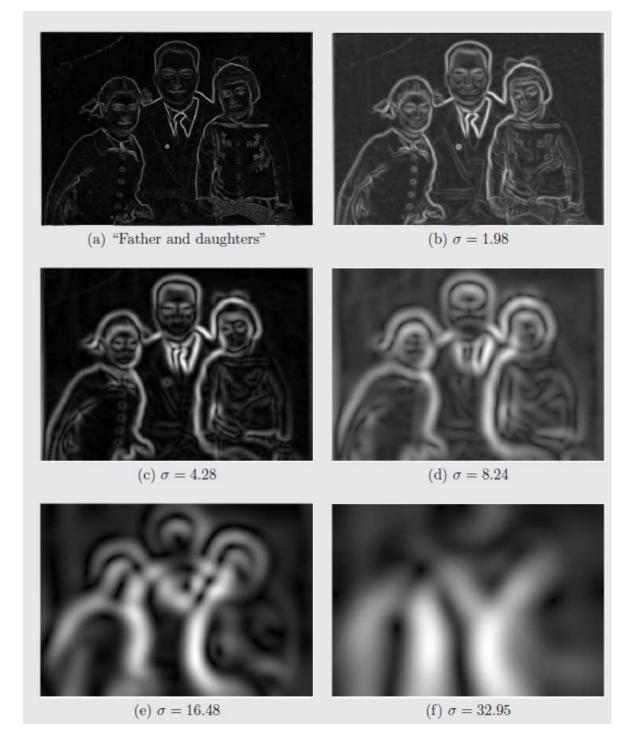

| 3.2  | As the scale of the filter increases, transition between regions becomes less and      |    |

|------|----------------------------------------------------------------------------------------|----|

|      | less sharp                                                                             | 37 |

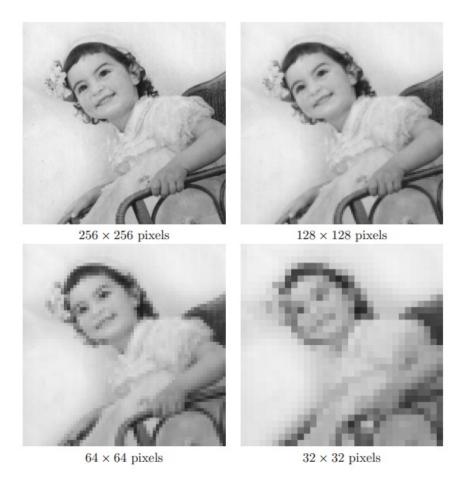

| 3.3  | Graphical result of keeping the number of grey levels while decreasing the             |    |

|      | number of pixel of an image                                                            | 38 |

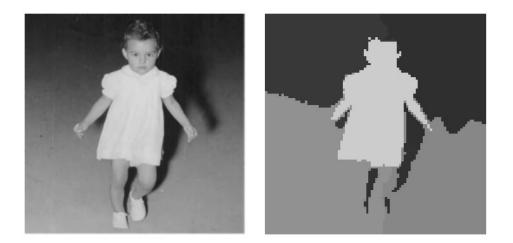

| 3.4  | Example of Image Segmentation                                                          | 39 |

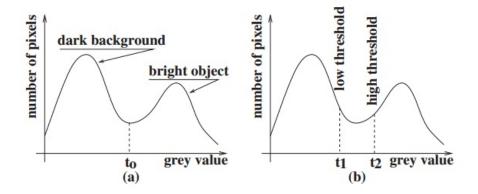

| 3.5  | Image segmentation histogram with a) one threshold level and b) with hystere-          |    |

|      | sis threshold                                                                          | 40 |

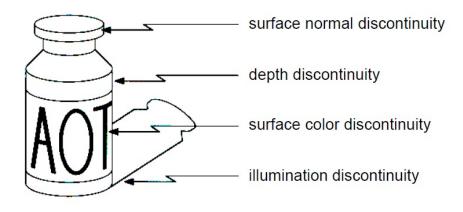

| 3.6  | Origin of Edges                                                                        | 41 |

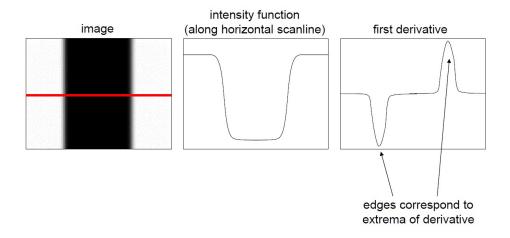

| 3.7  | Edges characterization. Edges are detected in sudden contrast changes, and             |    |

|      | through first derivative we can mathematically detect this sudden discontinu-          |    |

|      | ities with its local maxima and minima.                                                | 42 |

| 3.8  | Dimensional signal with different intensity pixels                                     | 42 |

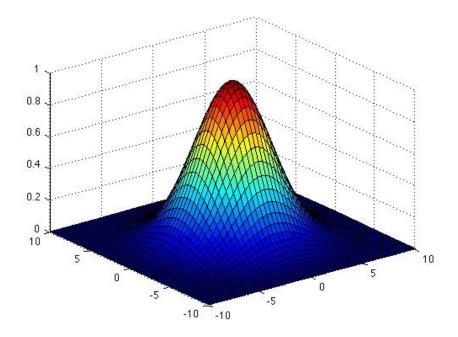

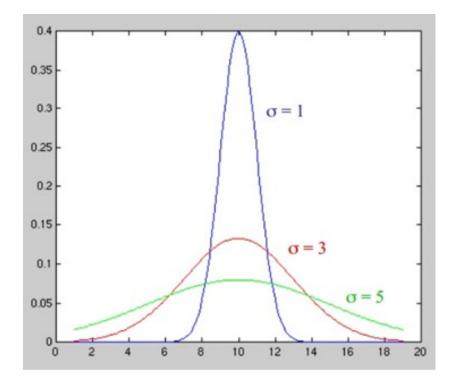

| 3.9  | Gaussian Curve in 3D domain                                                            | 45 |

| 3.10 | Gaussian curve as a function of variance                                               | 45 |

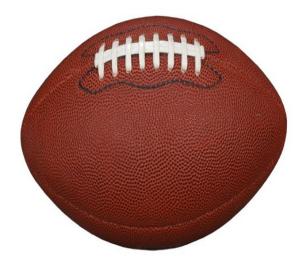

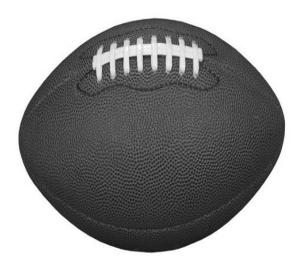

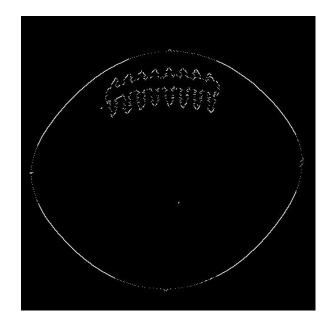

| 3.11 | Rugby Ball                                                                             | 46 |

| 3.12 | Monochromatic representation of the Rugby Ball                                         | 46 |

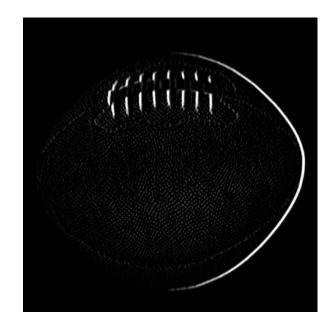

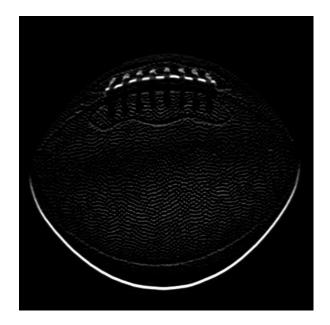

| 3.13 | Gaussian Smoothed representation of the Rugby Ball                                     | 47 |

| 3.14 | Output image from X-direction gradient operator                                        | 48 |

| 3.15 | Output image from Y-direction gradient operator                                        | 49 |

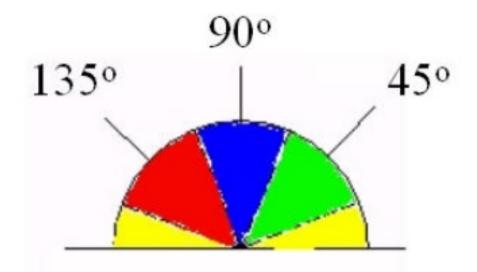

| 3.16 | Gradient orientation                                                                   | 50 |

| 3.17 | Illustration of non-maximum suppression. Edge strengths are marked with                |    |

|      | numbers and colors, and gradient directions are shown as arrows $\ldots \ldots \ldots$ | 50 |

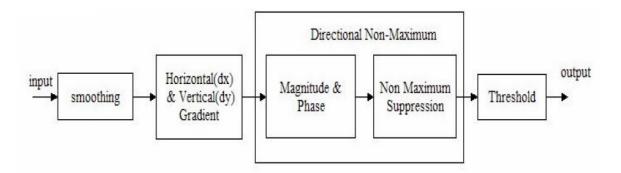

| 3.18 | Canny Algorithm Design Flow                                                            | 51 |

| 3.19 | Final Output of the Canny Edge Algorithm                                               | 52 |

| 3.20 | Software architecture of the vision system developed by CAMBADA robotic                |    |

|      | football team                                                                          | 53 |

| 4.1  | Serial Communication algorithm                                                         | 55 |

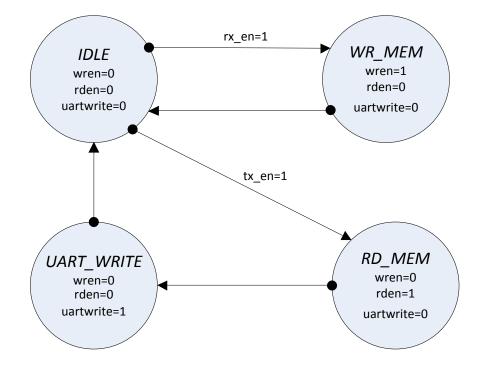

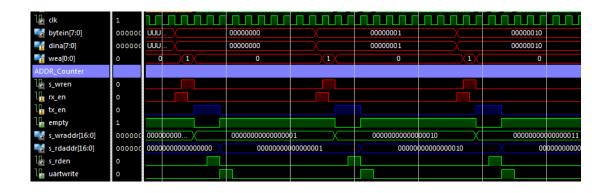

| 4.2  | Serial Communication State Diagram                                                     | 57 |

| 4.3  | Serial communication timing diagram                                                    | 57 |

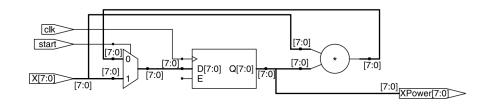

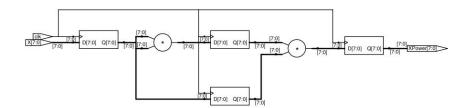

| 4.4  | Iterative Implementation                                                               | 58 |

| 4.5  | Pipelined Implementation                                                               | 59 |

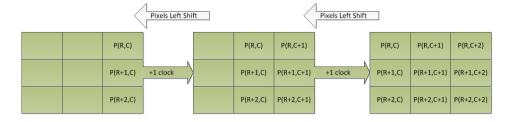

| 4.6  | First two calculations of the moving window (in light green) over the original                                      |    |

|------|---------------------------------------------------------------------------------------------------------------------|----|

|      | frame. Pixels in light blue, $P(2,2)$ and $P(2,3)$ , are the pixels under calculation                               |    |

|      | in each clock                                                                                                       | 61 |

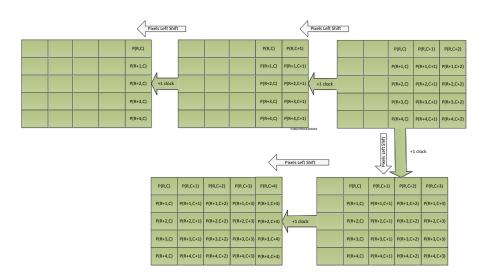

| 4.7  | Algorithm of the Smoothing Filter step                                                                              | 62 |

| 4.8  | Mask shift process in the Gaussian Operator. $P = pixel$ , $R = row$ and $C =$                                      |    |

|      | column                                                                                                              | 62 |

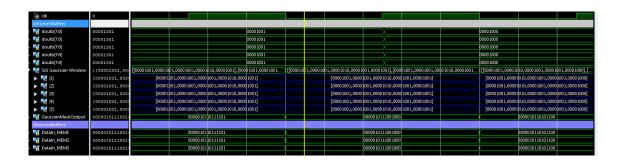

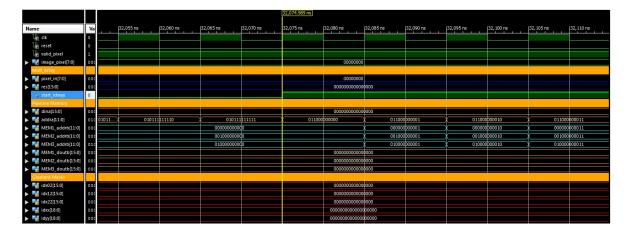

| 4.9  | Smoothing Filter Timing Diagram                                                                                     | 63 |

| 4.10 | Finding Gradients algorithm                                                                                         | 64 |

| 4.11 | Mask shift process in Gradient 3x3 Mask. $\mathbf{P}$ = pixel, $\mathbf{R}$ = row and $\mathbf{C}$ = Column         | 64 |

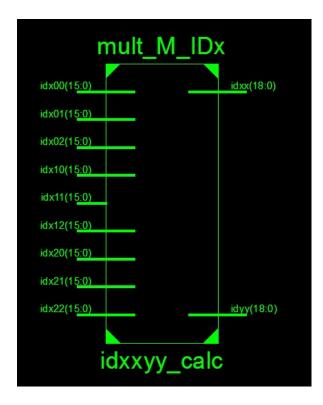

| 4.12 | 3x3 Moving Window with corresponding signals                                                                        | 64 |

| 4.13 | Mask multipliers structure                                                                                          | 65 |

| 4.14 | Finding Gradients Step Diagram                                                                                      | 65 |

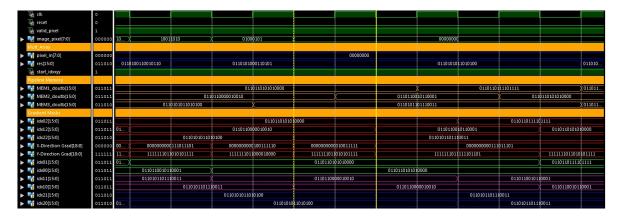

| 4.15 | "Finding Gradients" step timing diagram 2                                                                           | 66 |

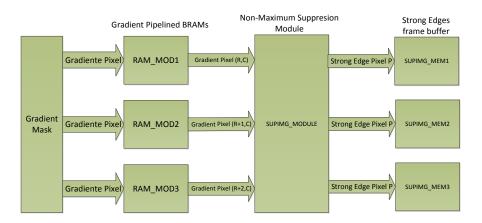

| 4.16 | Non-Maximum suppression algorithm                                                                                   | 67 |

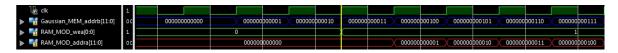

| 4.17 | Non-Maximum suppression (memory) timing diagram                                                                     | 67 |

| 4.18 | Non-Maximum suppression (memory) timing diagram                                                                     | 67 |

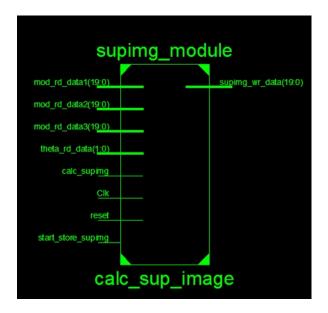

| 4.19 | "Supimg_module" structure $\ldots$ | 68 |

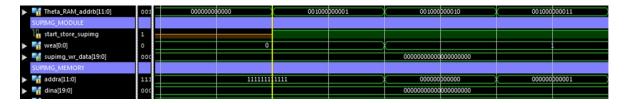

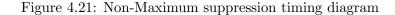

| 4.20 | Non-Maximum suppression timing diagram                                                                              | 68 |

| 4.21 | Non-Maximum suppression timing diagram                                                                              | 69 |

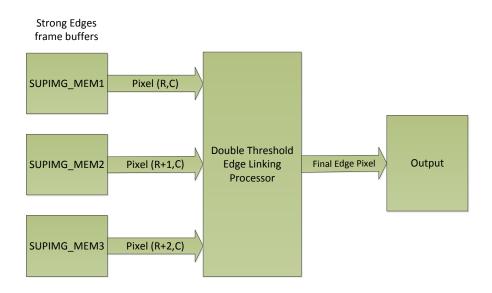

| 4.22 | Algorithm of the Edge Linking with double threshold stage                                                           | 70 |

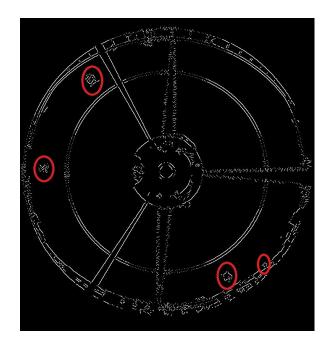

| 4.23 | Image obtained from Cooperative Autonomous Mobile roBots with Advanced                                              |    |

|      | Distributed Architecture (CAMBADA) omnidirectional camera                                                           | 70 |

| 4.24 | Previous image processed by the designed Canny Edge Algorithm                                                       | 71 |

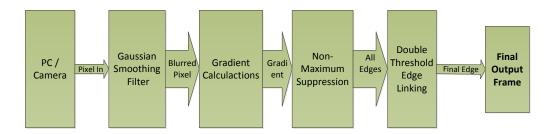

| 4.25 | Canny Edge complete algorithm, step-by-step                                                                         | 71 |

| 4.26 | Edge Hysteresis Processor timing diagram                                                                            | 71 |

| 4.27 | FPGA Resources Utilization Statistics                                                                               | 72 |

### Acronyms

ALU Arithmetic Logic Unit

ASIC Application-specific Integrated Circuit

**BRAM** Block Random Access Memory

CAD Computer-Aided Design

CAGR Compound Annual Growth Rate

**CAMBADA** Cooperative Autonomous Mobile roBots with Advanced Distributed Architecture

**CLB** Configurable Logic Block

**CPLD** Complex Programmable Logic Device

**CPU** Central Processing Unit

**DSP** Digital Signal Processor

**FF** *Flip-Flop*

FPGA Field-Programmable Gate Array

HDL Hardware Description Language

$\mathbf{IC} \ \textit{Integrated} \ \textit{Circuit}$

LTE Long-Term Evolution

LUT Look-Up Table

**NRE** Non-recurring engineering

**PLD** Programmable Logic Device

**RAM** Random Access Memory

**SMD** Surface Mounted Device

**SRAM** Static Random Access Memory

**UART** Universal Asynchronous Receiver/Transmitter

${\bf USB} \ \ Universal \ Synchronous \ Bus$

**VHDL** Very High-Speed Integrated Circuits Hardware Description Language

### Chapter 1

## Introduction

#### 1.1 Computer Vision: A modern reality

As artificial intelligence technology advances, computer vision is becoming more and more important and present in our everyday life. Nowadays we have plenty of applications on this area embracing various markets, namely health, personal security and robotics. Besides those areas, computer vision also plays an important role in all the industrial sectors which aim the optimization of quality standards. This optimization is provided through the inspection at nano-level in various sectors like mechanical, textile, electronics, pharmaceutical, plastic packaging and more, detecting problems which the human eye is oblivious to. Examples of real case situations are the following: monitoring of urban areas, *Surface Mounted Device* (SMD) pins inspection of its positioning, fast and precise evaluation of food color/shape/condition, inspection of leaks in liquid barrels, among other applications.

When we talk about this technology, we have to talk about a common computer system which allows to implement it, performing dedicated functions: the embedded systems. The heart of this computer systems are the processing cores, which in the case of video processing are named *Digital Signal Processors* (DSPs) and enable the processing of individual or a sequence of frames on-the-fly.

CAMBADA is a middle-size robotic football team project developed in the University of Aveiro, which was created aiming the participation in the RoboCup middle-size league - an international initiative with the goal of promoting the development of artificial intelligence in the robotics area and related fields. CAMBADA project, among other technologies, has adopted an embedded computer vision system to provide their robots with the ability to see, being a great example of successful use of this technology. In this competition, during a game in the playing field, besides the obstacles and the points-of-reference, there is also a very fast-changing scenery with the teammates, opponents and the ball itself moving quickly and unpredictably, requiring a fast processing system to operate heavy quantities of information on-the-fly, through an omnidirectional camera.

#### 1.2 Goals

This is a very good situation to study the advantage of relegating the processing of heavy information to the power of reconfigurable hardware, through its parallel processing capacity, integrated in an embedded system. In this case we will be using an FPGA to process on-the-fly data. But real-time processing is not the only challenge we have to face.

Year after year, RoboCup competition has been changing in some aspects, namely on its environment. Initially, this environment was robot friendly, where conditions such as controlled lighting or easy to recognize color coded objects were taken for granted. Today, with the advance of the technology, this environment has become increasingly more difficult with all these conditions being relaxed or completely suppressed. This implies an important step on the evolution of the robots vision system which has to adapt to the strong lightning changes and also to the change of ball-type colour from game to game. One solution to this problem is to make a vision system not color based but, instead, able to recognize boundaries and consequently geometric forms. This systems, based on edge detection, becomes independent from the light and colour conditions, detecting object by its form, regardless of its colour.

Edge detection is in fact, one of the most common operations in the world of image analysis, and as a consequence with various applications and big relevance in the computer vision field of study. According to CAMBADA experiments, among several edge detection algorithms, Canny Edge algorithm was the one chosen for the role of edge detection because, despite of being the most demanding regarding processing time, it was fast enough for realtime processing, also providing the most effective contours [12].

In this project, we will test and evaluate the power and possible advantages of the use of reconfigurable hardware parallel processing, in the step of "Edge Detection" using the Canny algorithm, within the vision system of CAMBADA. This will involve the following points:

- The study of reconfigurable hardware technology, namely FPGA technology and its different phases of the project;

- The study of a computer vision algorithm within the scope of CAMBADA vision system,

for the purpose of boundary detection and its inherent steps;

- The study of the versatility of hardware description languages, VHDL, namely for arithmetic operations purposes;

- Test, optimization of size and performance, and validation of a DSP embedded in an FPGA;

### Chapter 2

## **Reconfigurable Computing**

#### 2.1 Introduction

The concept of reconfigurable computing has existed since the 1960s [37], when the concept of a computer constituted of a standard processor and an array of "reconfigurable" hardware was proposed. The idea was to have the processor controlling the reconfigurable hardware, which would be tailored to do a specific task - such as image processing - as quickly as a dedicated piece of hardware. Once the task was done, the hardware could be reconfigured to do some other task, resulting in a hybrid computer structure which combined the flexibility of software with the speed of hardware. However, in that time, this idea was far ahead of its needed state-of-art electronic technology.

Today's computationally intensive applications, such as video streaming, image recognition and processing, and highly interactive services, are placing new demands on the computation units that implement these applications, requiring a higher processing power than ever before. Facing these performance requirements, the power consumption targets, the acceptable packaging and manufacturing costs, and the time-to-market requirements of these computation units are all decreasing rapidly, especially in the embedded devices market. In fact, in 2004, studies already reported that moving critical software loops to reconfigurable hardware were resulting in average energy savings of 35% to 70% with an average speed up of 3 to 7 times, depending on the particular device used [5].

Hence, and thanks to the advance of technology, reconfigurable computing finally came up and is rapidly establishing itself as a major discipline. Indeed, there is evidence that embedded systems developers show a growing interest in reconfigurable computing systems [6], especially with the introduction of soft cores which can contain one or more instruction processors [7, 8, 9, 10, 11, 20].

#### 2.2 Programmable Logic vs Fixed Logic

The vast world of digital electronics can be divided in three categories, memory devices, microprocessors and logic devices, where the latter can be classified in two different categories: fixed and programmable. It is very important to clarify the difference between them. As the name suggests, the circuits in a fixed logic device are permanent and they are customized to perform a set of functions, can't be changed once manufactured (for eg., *Application-specific Integrated Circuit* (ASIC)). The time required to go from design, to prototypes, to a final manufacturing run, can take from several months to more than a year, depending on the complexity of the device, and if the requirements change there is no flexibility at all so a new design must be developed [2].

On the other hand, programmable logic devices, as already mentioned, offer users a wide range of logic capacity, features and speed, and they can be changed and configured at any time. With this technology, designers appeal to inexpensive tools being able to quickly program it into a device, and immediately test it in a live circuit. Another key benefit of using programmable logic devices is that in some of them, circuit can be reconfigured as many times we want, whenever we want, until we are satisfied with the optimization, due to the fact they are based on re-writable memory technology.

So let us resume the main advantages of each technology. Fixed logic devices is better shapped for big volume applications since their mass productions is cheaper, and when high performance is required. However, programmable logic devices provide us with:

- More flexibility during the design cycle we can change the programming file and the results of the design changes can be seen immediately in working parts;

- Faster prototype building;

- The chance to add new features from time to time, upgrading it with the upload of a programming file, directly via the internet or from a hard-drive, creating new hardware logic in the system;

- Customers don't have to pay for large *Non-recurring engineering* (NRE) costs since these costs will be amortized over the multi-year lifespan of a given line of the *Programmable Logic Device* (PLD).

#### 2.3 FPGA vs CPLDs

The two major types of programmable logic devices are FPGAs and *Complex Programmable Logic Devices* (CPLDs), each having different characteristics. CPLDs, whilst offering much smaller amounts of logic than FPGAs, provide predictable timing characteristics which make it ideal for critical control applications, and also require extremely low amounts of power becoming an optimal choice for cost-sensitive, battery-operated, portable applications like digital phones. On the other hand, FPGAs offer the highest amount of logic density, highest performance and several features, providing substantial amounts of memory, built-in hard-wired processors, and other means. These devices are used mostly for data processing and storage, telecommunications, digital signal processing, among other applications. But how did they emerge? How do they function? These are questions we'll be discussing in the next topic.

#### 2.4 FPGA state-of-art

FPGAs were introduced in the market in 1984 by Xilinx with a central idea: the capacity to produce a personalized integrated circuit, without the economic risk usually associated to other technologies. Today FPGAs are present in fields as diverse as automation, consumer electronics, biomedicine, night vision, telecommunications, security, special investigation, among others. This technology is basically a device with an application in all the industries which require high-speed and/or heavy processing computation. Since the emergence of integrated circuits, there are two alternatives to carry out a digital hardware: algorithm codification in a microprocessor or direct mapping of the algorithm in the hardware. Microprocessor together with microcontrollers and DSPs allow to successfully solve most of the electronic challenges.

But what is an FPGA and why is it such a great device? As mentioned earlier in this chapter, an FPGA is a structure of logic cells and connections, which is under the control of the user/costumer, being able to design and program it, and make changes to the circuit whenever necessary. Basically, they are prefabricated silicon chips that can be programmed electrically to implement any digital design.

The elementary architecture of FPGA consists of three major components: programmable logic blocks (which implement the logic functions), programmable routing (interconnects) to implement the functions and I/O blocks to make off-chip connections, while they may also integrate extra blocks like dedicated memories (BlockRAM). An illustration of a typical FPGA architecture is shown in figure 2.1.

Figure 2.1: Built-in overview of an FPGA

#### 2.4.1 Programmable Logic blocks

Logic blocks can be named the main elements of an FPGA because its purpose is to provide the basic computation and storage elements used in digital systems. Each basic logic element is composed by programmable combinational logic, *Flip-Flops* (FFs) or latches and fast carry logic to reduce area and delay cost (detailed information will be provided in other topics regarding the FPGA model in use). Furthermore, FPGA has as well other *Configurable Logic Blocks* (CLBs) with specific functions like dedicated memory blocks or multipliers.

#### 2.4.2 Programmable Interconnect

For communication to be feasible within the FPGA, through programmable routing connections are established among logic blocks and I/O blocks to construct the design defined by the user. This is provided by several multiplexers, pass transistors and tri-state buffers, which together form the desired connection. Logic elements are connected by the combination of pass transistors and multiplexers whilst these latter two with the tri-state buffers form global routing structures.

#### 2.4.3 Programmable I/O

FPGA dispose of I/O pads which provide the interface between its logic blocks and routing architectures and the several external components. These I/O pads along with surrounding supporting logic circuitry form I/O cells which are important components consuming approximately 40% of FPGAs area [3].

#### 2.4.4 Block RAM vs Distributed RAM

Regarding the storing capability of the FPGA, usually, depending on the amount of RAM required for a specific function, we're working with one of two types of this memory. *Block Random Access Memorys* (BRAMs) are located in specific areas of the FPGA and they are dedicated, hence they cannot be used for anything but RAM functions. For small amounts of memory, FPGA logic-cells are used as tiny RAMs providing a very flexible RAM distribution (although inefficient in terms of area), which is called Distributed RAM.

RAM operation is affected by many parameters, where the main one is the number of agents that can access it simultaneously. While in a Single-Port RAM only one agent can read/write the RAM, in a "dual-port" RAM two agents can read/write. In fig.2.2 is illustrated a simplified scheme of a dual-port RAM.

Figure 2.2: Dual-port RAM scheme

Eventually, technology improves and FPGA architecture has not been an exception to that. Nowadays, more specialized programmable functional blocks were added, namely embedded memory (BlockRAMs), *Arithmetic Logic Units* (ALUs), multiplexers and even microprocessors, due to a frequent need of such resources for application in a wide variety of areas. A good example of this fact is the FPGA used in this project, Virtex 5 by Xilinx, which provides various resources, as we can see below.

FPGA Virtex-5 XC5VLX50T typical blocks and its corresponding logic resources: [13]

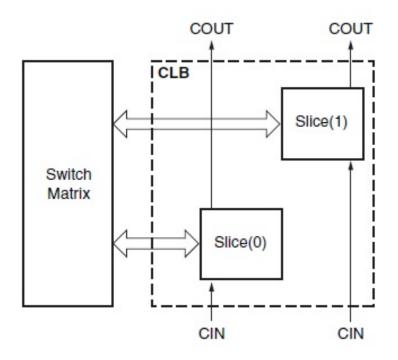

- 120 x 30 CLB, each with two slices (figure 2.3) with 4 *Look-Up Tables* (LUTs), 4 storage elements (FFs), wide-function multiplexers and carry-logic;

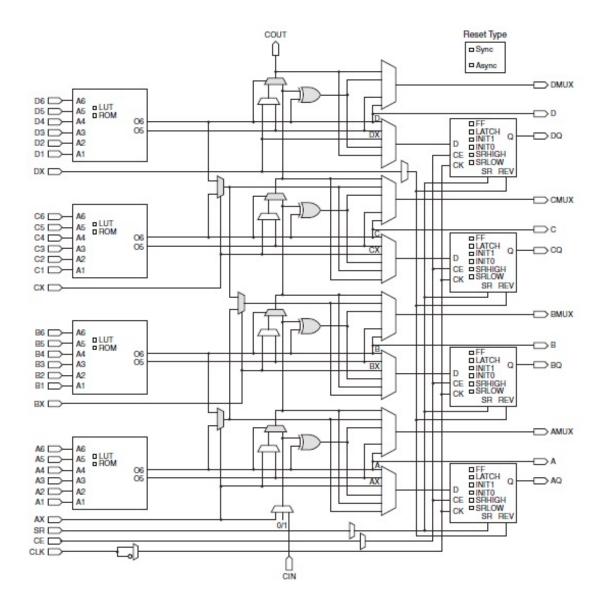

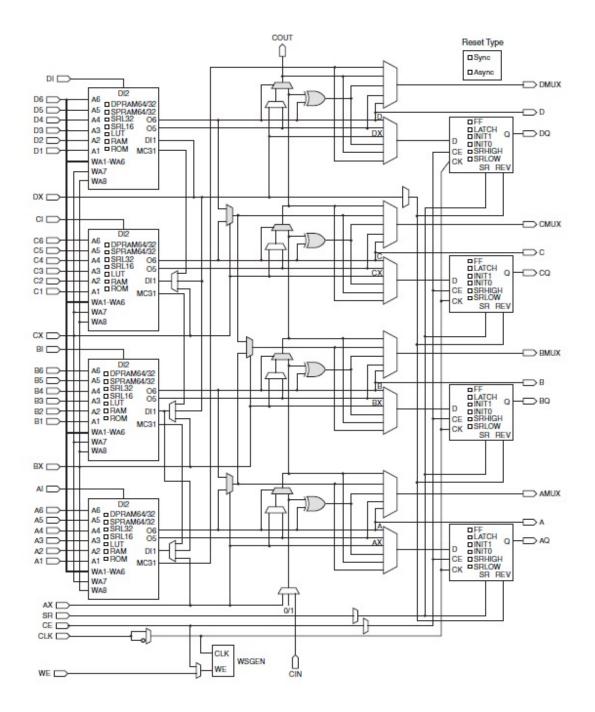

- Some slices support two additional functions: storing data using distributed RAM and shifting data with 32-bit registers. These slices are called SLICEM (fig. 2.4). Others are named SLICEL (fig. 2.5);

- CLBs which have SCLICEMs contain 256 bits of distributed RAMs and 128 bits of Shift Registers;

- Total of 2160 Kb True dual-port RAM blocks [14];

- Clock control units;

- 550 MHz Clock technology;

- 48 x 550 MHz DSP48 Slices, each containing 25x18 multiplier, an adder and an accumulator;

- Ethernet MACs;

- Flexible and high performance I/O interface standards (up to Gbps);

- Hardwired PowerPCs, PCI Express modules;

Figure 2.3: Arrangement of a slice within the CLB [13]

Figure 2.4: Diagram of a SLICEM [13]

Figure 2.5: Diagram of a SLICEL [13]

But what are the advantages of FPGAs when supporting embedded systems processing power?

We have several, namely:

• Low cost of development despite of its high complexity (for small and medium markets);

- Easy to debug;

- Error tolerant;

- Reduced size;

- High reliability;

- Dedicated and reconfigurable system;

- They are recommended for the processing of parallel operations thanks to its density of logic cells, more precisely Look-up Tables and multiplexers (for non-high transfer rates), being able to run multiple channels simultaneously;

- Fast prototyping;

- Faster cycles, lower risk;

- Dynamic upgrades of the system.

However, there are also some **limitations:** which are important to have in mind when we pretend to use this technology, namely:

- Overhead due to reconfiguration time and/or additional hardware circuit delays;

- Long software compiling times due to its complexity;

Figure 2.6 presents the characteristics of some Virtex-5 family FPGA devices.

#### 2.4.5 Modern market of FPGA

FPGA companies are no longer just trying to architect the best logic module, interconnect, and place-and-route algorithm, but they continue refining it over time, whilst their main core competency is to expand this technology to new markets. These markets have been segmented, based on application, into consumer electronics, automotive, industrial, data processing, military and aerospace, telecommunications, and others. The telecommunications field is expected to present the fastest growth, with an estimated *Compound Annual Growth Rate* (CAGR) of 9.0% from 2013 to 2019 [2], mostly due to the usage of FPGA in base stations in the updates from 2G to 3G and from 3G to *Long-Term Evolution* (LTE), and high demand of bandwidth in wireless networks. Big usage of this technology in imaging equipment, high performance computing in vehicular communications and flat panel displays, is also a growing reality, and consequently FPGAs will have a significant popularity in smartphones, tablets Virtex-5 Family Overview

| Device     | Configurable Logic Blocks (CLBs) |                                   |                                | 1                               | Block RAM Blocks     |       |             |                     | PowerPC             | Endpoint                     |                                 | Max RocketlO<br>Transceivers <sup>(6)</sup> |     | Total | Max                        |

|------------|----------------------------------|-----------------------------------|--------------------------------|---------------------------------|----------------------|-------|-------------|---------------------|---------------------|------------------------------|---------------------------------|---------------------------------------------|-----|-------|----------------------------|

|            | Array<br>(Row x Col)             | Virtex-5<br>Slices <sup>(1)</sup> | Max<br>Distributed<br>RAM (Kb) | DSP48E<br>Slices <sup>(2)</sup> | 18 Kb <sup>(3)</sup> | 36 Kb | Max<br>(Kb) | CMTs <sup>(4)</sup> | Processor<br>Blocks | Blocks for<br>PCI<br>Express | Ethernet<br>MACs <sup>(5)</sup> | GTP                                         | GTX | VO    | User<br>I/O <sup>(7)</sup> |

| XC5VLX30   | 80 x 30                          | 4,800                             | 320                            | 32                              | 64                   | 32    | 1,152       | 2                   | N/A                 | N/A                          | N/A                             | N/A                                         | N/A | 13    | 400                        |

| XC5VLX50   | 120 x 30                         | 7,200                             | 480                            | 48                              | 96                   | 48    | 1,728       | 6                   | N/A                 | N/A                          | N/A                             | N/A                                         | N/A | 17    | 560                        |

| XC5VLX85   | 120 x 54                         | 12,960                            | 840                            | 48                              | 192                  | 96    | 3,456       | 6                   | N/A                 | N/A                          | N/A                             | N/A                                         | N/A | 17    | 560                        |

| XC5VLX110  | 160 x 54                         | 17,280                            | 1,120                          | 64                              | 256                  | 128   | 4,608       | 6                   | N/A                 | N/A                          | N/A                             | N/A                                         | N/A | 23    | 800                        |

| XC5VLX155  | 160 x 76                         | 24,320                            | 1,640                          | 128                             | 384                  | 192   | 6,912       | 6                   | N/A                 | N/A                          | N/A                             | N/A                                         | N/A | 23    | 800                        |

| XC5VLX220  | 160 x 108                        | 34,560                            | 2,280                          | 128                             | 384                  | 192   | 6,912       | 6                   | N/A                 | N/A                          | N/A                             | N/A                                         | N/A | 23    | 800                        |

| XC5VLX330  | 240 x 108                        | 51,840                            | 3,420                          | 192                             | 576                  | 288   | 10,368      | 6                   | N/A                 | N/A                          | N/A                             | N/A                                         | N/A | 33    | 1,200                      |

| XC5VLX20T  | 60 x 26                          | 3,120                             | 210                            | 24                              | 52                   | 26    | 936         | 1                   | N/A                 | 1                            | 2                               | 4                                           | N/A | 7     | 172                        |

| XC5VLX30T  | 80 x 30                          | 4,800                             | 320                            | 32                              | 72                   | 36    | 1,296       | 2                   | N/A                 | 1                            | 4                               | 8                                           | N/A | 12    | 360                        |

| XC5VLX50T  | 120 x 30                         | 7,200                             | 480                            | 48                              | 120                  | 60    | 2,160       | 6                   | N/A                 | 1                            | 4                               | 12                                          | N/A | 15    | 480                        |

| XC5VLX85T  | 120 x 54                         | 12,960                            | 840                            | 48                              | 216                  | 108   | 3,888       | 6                   | N/A                 | 1                            | 4                               | 12                                          | N/A | 15    | 480                        |

| XC5VLX110T | 160 x 54                         | 17,280                            | 1,120                          | 64                              | 296                  | 148   | 5,328       | 6                   | N/A                 | 1                            | 4                               | 16                                          | N/A | 20    | 680                        |

| XC5VLX155T | 160 x 76                         | 24,320                            | 1,640                          | 128                             | 424                  | 212   | 7,632       | 6                   | N/A                 | 1                            | 4                               | 16                                          | N/A | 20    | 680                        |

| XC5VLX220T | 160 x 108                        | 34,560                            | 2,280                          | 128                             | 424                  | 212   | 7,632       | 6                   | N/A                 | 1                            | 4                               | 16                                          | N/A | 20    | 680                        |

| XC5VLX330T | 240 x 108                        | 51,840                            | 3,420                          | 192                             | 648                  | 324   | 11,664      | 6                   | N/A                 | 1                            | 4                               | 24                                          | N/A | 27    | 960                        |

| XC5VSX35T  | 80 x 34                          | 5,440                             | 520                            | 192                             | 168                  | 84    | 3,024       | 2                   | N/A                 | 1                            | 4                               | 8                                           | N/A | 12    | 360                        |

| XC5VSX50T  | 120 x 34                         | 8,160                             | 780                            | 288                             | 264                  | 132   | 4,752       | 6                   | N/A                 | 1                            | 4                               | 12                                          | N/A | 15    | 480                        |

| XC5VSX95T  | 160 x 46                         | 14,720                            | 1,520                          | 640                             | 488                  | 244   | 8,784       | 6                   | N/A                 | 1                            | 4                               | 16                                          | N/A | 19    | 640                        |

| XC5VSX240T | 240 x 78                         | 37,440                            | 4,200                          | 1,056                           | 1,032                | 516   | 18,576      | 6                   | N/A                 | 1                            | 4                               | 24                                          | N/A | 27    | 960                        |

| XC5VTX150T | 200 x 58                         | 23,200                            | 1,500                          | 80                              | 456                  | 228   | 8,208       | 6                   | N/A                 | 1                            | 4                               | N/A                                         | 40  | 20    | 680                        |

| XC5VTX240T | 240 x 78                         | 37,440                            | 2,400                          | 96                              | 648                  | 324   | 11,664      | 6                   | N/A                 | 1                            | 4                               | N/A                                         | 48  | 20    | 680                        |

| XC5VFX30T  | 80 x 38                          | 5,120                             | 380                            | 64                              | 136                  | 68    | 2,448       | 2                   | 1                   | 1                            | 4                               | N/A                                         | 8   | 12    | 360                        |

| XC5VFX70T  | 160 x 38                         | 11,200                            | 820                            | 128                             | 296                  | 148   | 5,328       | 6                   | 1                   | 3                            | 4                               | N/A                                         | 16  | 19    | 640                        |

| XC5VFX100T | 160 x 56                         | 16,000                            | 1,240                          | 256                             | 456                  | 228   | 8,208       | 6                   | 2                   | 3                            | 4                               | N/A                                         | 16  | 20    | 680                        |

| XC5VFX130T | 200 x 56                         | 20,480                            | 1,580                          | 320                             | 596                  | 298   | 10,728      | 6                   | 2                   | 3                            | 6                               | N/A                                         | 20  | 24    | 840                        |

| XC5VFX200T | 240 x 68                         | 30,720                            | 2,280                          | 384                             | 912                  | 456   | 16,416      | 6                   | 2                   | 4                            | 8                               | N/A                                         | 24  | 27    | 960                        |

**∑** XILINX°

Figure 2.6: VirteX-5 FPGA Feature Summary [13]

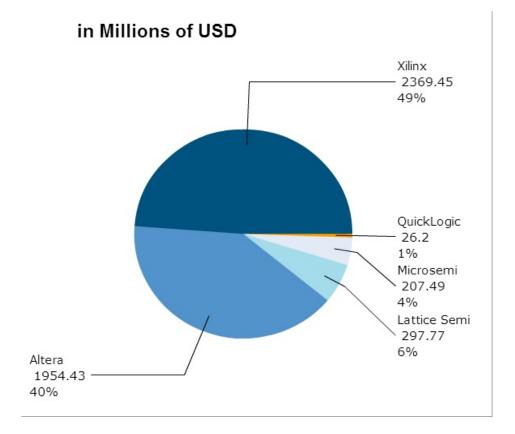

and phablets with advanced touchscreen functionality, within the same period. Besides, integrating 3D acpIC with FPGAs, processor, SerDes (Serializer or Deserializer), and memory controllers are expected to act as an opportunity for market growth in the near future. Among the different FPGA technologies - SRAM, flash, and antifuse - SRAM is expected to be the largest and fastest growing technology dominating the market over the next few years, accounting for 76.1% of the overall revenue in 2012 [2, 3, 4]. In terms of value and according to a new market report published by Transparency Market Research, "Field-Programmable Gate Array (FPGA) Market - Global Industry Analysis, Size, Share, Growth, Trends and Forecast, 2013 - 2019", the market was valued at USD 5.08 billion in 2012 (EUR 3.68 billion), which is expected to reach USD 8.95 billion by 2019 (EUR 6.48 billion), growing at a CAGR of 8.5%from 2013 to 2019 [3]. Asia Pacific industry, which dominated the global market in 2012, was valued at USD 2.04 billion in that year (EUR 1.48 billion)[4], occupying 40.2% of the overall market share [2], and is expected to remain the largest market in the coming years. Growing opportunities in this segment were driven by countries such as Japan, India, South Korea, and of course, China. However, North America also occupied significant market share thanks to technological advancements coupled with sophisticated equipment across target applications. The industry is highly consolidated, where Xilinx and Altera have been the biggest competitors in the marketing game for years, dominating the programmable logic field since the 1980s, and holding together about 90% of the overall market share in 2012 with combined revenues in excess of USD 4.5 billion (EUR 3.26 billion) [3, 4, 5]. In fact, for each company, the other is the only real competition, since other key participants such as Lattice Semiconductor, Achronix, e2v, Tabula, Microsemi and others [5], represent a much smaller slice of the market, with the strategy of producing specific applications to sub-markets.

Figure 2.7: FPGA Market (July 2011) [6]

The leader in FPGAs for many years, Xilinx, has the largest programmable logic portfolio in the industry and a good variety of FPGAs in terms of cost and performance. In recent years, the popular Spartan series has covered the low-to-mid-end market (oriented to servers and medium complexity systems) while the Virtex series has covered the high-end (oriented to communications)[6]. Also, Xilinx released the Series-7 family of FPGAs (Artix-7, Kintex-7, Virtex-7) built on 28-nm process, winning the "Highly Commended Prize" Semiconductor of the year award for 2011, and the next most recent Series-6 device family (Virtex-6, Spartan-6). However, most recently they announced their next generation SoC – the "Zynq-7000" – claiming that developers can use this platform to design smarter systems with tightly coupled software based control and analytics with real time hardware based processing and optimized system interfaces.

Achronix, a company founded in 2004, is one of the emerging suppliers for specialized, high end programmable logic and its parts are built with Intel foundry services using Intel's 22nm 3-D Tri-Gate FinFET process. They have a family of SRAM based FPGAs called "Speedster22i", which have peak performance up to 1.5GHz and densities up to 1.7 million effective acpLUT [38].

Altera has a wide and deep portfolio of programmable logic, with its FPGAs covering the low, mid and upper end markets. For the upper end markets they present the "Stratix" series of FPGAs, for the mid-range market is their "Aria" series, and covering their low cost offer is the "Cyclone" series, all of them build on 28-nm process technology. Altera has made great progress in winning market share in recent years. Many people would say that their software tools are better than those of Xilinx which has likely been an important factor in their success [38].

Lattice Semiconductor tackles the low-power and low-cost market for FPGAs. They commercialize their products as the "high-value FPGAs" of the industry, providing best performance per cost. Lattice claims to have the industry's lowest power and price SERDES-capable FPGA: LatticeECP3.

Microsemi specializes in low-power and mixed-signal FPGAs. Here are some of Microsemi's claims: The industry's lowest power FPGA, the IGLOO, and the industry's only FPGA with hard 32-bit ARM Cortex-M3 microcontroller: the SmartFusion. In 2005 this technology constituted 60% of the technology used on video processing industry being easily integrated in the embedded processors market due to the fact that the FPGA free silicon areas allow to integrate in one chip, together with FPGA logic, core processors that are usually located outside of the chip [21]. Despite the higher cost, its design flexibility is very important. In the next picture we can observe the significant growth of the FPGAs already noticeable in the market of the 90's, from 1991 until 1999 specifically. Although being old statistics, this graphic gives us an idea about the strong growth this technology already had in about two decades ago.

Today, and within the focus of this dissertation, XILINX offers new Hardwired PowerPC's devices, DSP cells, PCI Express modules and Ethernet MACs, and hence we start talking not about a FPGA but the concept of a platform/development board (Atlys/Genesys).

Figure 2.8: Evolution of price (green line), capacity (red line) and speed (blue line) of FPGAs from 1991 to 1999

Graph in figure 2.9 demonstrates the most usual applications. In the scheme presented

Figure 2.9: Most usual applications in 2005, where embedded processors were required [21]

on figure 2.10 we can have an idea of the steps taken in the market by Xilinx, from the wafer fabrication till the End Market, centered on communications, servers and general consume:

Figure 2.10: XILINXMarket [21]

## 2.5 FPGA Design Flow and Design methods / approaches

### 2.5.1 Methods

When we want to design a circuit in an FPGA we can opt between two styles of designing: using a schematic, or using a *Hardware Description Language* (HDL). Basically, when we use the schematic method, we draw our design using various elements among gates and wires, which is very practical for small designs because it is an easily readable format, despite of the difficulty in migrating between vendors and technologies. On the other hand, HDL design entry is the most common for big designs, while requiring learning and understanding at least one of the two main HDL languages, VHDL and Verilog. The first will be used along this entire project and will be discussed further in another section.

## 2.5.2 Design Flow

The project of an FPGA is constituted by 3 main steps:

- Design entry/synthesis;

- Design implementation;

- Device programming;

The achievement of these 3 main steps is possible due to tools called CAD (Computer-Aided Design). Here, design entry can be done either by schematic diagram method, by HDL system to describe the behavior of the circuit, or with a mixture of design entry methods. In this project, the CAD tool we'll use is named Xilinx ISE, appealing to HDL method. This software allows users to design an FPGA, gathering all these steps in the same tool, both using schematics and HDL method.

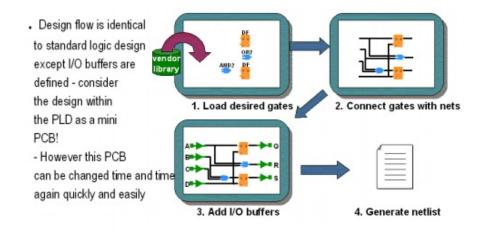

### 2.5.3 Design Entry / Synthesis

Using the first method, i.e. schematics, we can draw the structure of the device. This is a traditional method that is supported by a graphical tool where we can specify the required gates and how they are interconnected. This method consists in four main steps:

- Select a specific schematic tool, a device library and build the circuit. The user must choose a specific vendor and a device family at this time;

- Connect the gates using nets or wires, configuring it the way we want or that best fits the application;

- Define the I/O package pins for the device, adding and labeling the input and output buffers;

- Generate the netlist.

Figure 2.11: FPGA graphic design flow[15]

The netlist will be the text equivalent of the circuit allowing other programs to understand what gates are in the circuit and how they will be connected, and the names of the I/O pins. In fig. 2.12 we can see an example of the design specification netlist. Now let's imagine we need to design (draw) a circuit with approximately 10,000 equivalent gates. If a typical schematic page contains around 200 gates, we would need around 50 pages to create the design, adding all the components with its interconnections, I/Os, and generating a netlist. This would be heavily time-consuming, not to talk about 30k or 50k gate designs which would take a lifetime. This big disadvantage together with the (already mentioned) problem regarding migration between vendors and technologies, makes most of the reconfigurable

Figure 2.12: Design Specification netlist [15]

hardware designers opt for high-level design. HDL is indeed much simpler, as we can see in the example of fig. 2.13, where the design of a  $16 \times 16$  multiplier is made by both methods and compared [15]. In this case, the design software Xilinx ISE WebPACK, based on the high-level description file, has to figure out what gates to use and how to interconnect it, also providing the specification of the optimization criteria, i.e. we can optimize the design for the least number of gates, optimize a certain section of the design for fastest speed and use the best gate configuration to minimize power. In opposition to schematic approach, the user can explore different solutions trying it with different vendors, device families and optimization constraints. In the final, synthesis tool automatically generates netlist file which uses the primitives proposed by the vendor in order to satisfy the logic behavior specified in the HDL file. This file is the text equivalent of the circuit with the hardware components and interconnections optimized, implementing the modeled behavior and/or structure. At this point, a behavioral/functional simulation can be made using tools provided by this Computer-Aided Design (CAD) software. This simulation tool verifies the functionality or timing of a circuit, allowing the user to identify functional errors and correct them before stepping to a next phase, although not providing a timing simulation, which will be done a little later in the design flow. If there are in fact any problems, it is possible to go back to the HDL file, making changes, regenerating the netlist and rerunning the simulation. Usually, until the design fulfils the desired requirements, designers spend approximately 50% of their

Figure 2.13: Design Specification 16x16 multiplexer - HDL vs Schematics [15]

development time going through this loop.

This method is so flexible that we can change to a different vendor or technology, whilst just a new library selection is required, and we can also try different design tools from different vendors and select the best option depending on the results.

In the final of the synthesis step, besides the netlist, resource usage and performance estimation reports are also outputted. In fig. 2.14 we can see a diagram of the design entry flow.

Figure 2.14: FPGA Design Entry flow [15]

### 2.5.4 Design Implementation

After the netlist is created fulfilling our requirements, it is time to implement this in a chip, which is referred to as device implementation. This step is constituted itself by

3 phases: Translation, Mapping and Place & Routing. In the translation phase, various programs (which can vary among vendors) are used so the designed netlist is imported and prepared for layout. During this process, it is accomplished the optimization and verification of the device associated rules, whilst a verification is made to ensure that the choice of the device was the best, depending on the device itself and the required I/O utilization. After this, comes the phase where logical symbols from the netlist are grouped into physical components (slices and IO Blocks). To finish the implementation the netlist is mapped into the FPGA primitives, i.e. a selection is made of specific modules or logic blocks where the design gates will reside. This process is called "Place", and is complemented by other process named "Route", which is the physical routing of the interconnect between the logic blocks. This is the phase that requires the longest time to successfully be completed since it is a very complex task to, mostly on large designs, determine its locations and ensure that everything is correctly connected while, at the same time, meeting the desired performance. Despite of this being an automatic tool, some vendors provide tools to manually place and route the most critical parts when we aim to achieve better performance than that obtained by automatic tools.

### 2.5.5 Device downloading / programming

This step consists in the download of a bitstream file which contains all the information to define the logic and interconnect of the design into the device memory of the FPGA. Since we will be working with a *Static Random Access Memory* (SRAM) based FPGA device which loses its configuration when the device is turned off, the bitstream file has to be stored somewhere, for example, in a serial PROM. When programming is applied with all nonvolatile PLD, it performs the same function as the download does, with the difference that information is retained in the device even after power is removed from it. In the case of antifuse devices, programming is done once per device. In figure 2.15 [15] we can see the Xilinx FPGA typical design flow.

### 2.5.6 Programming approaches

When we are up to program the FPGA, we can think about three main types of architecture approaches, depending upon our time and resource requirements of the application.

When minimum resource utilization (lower cost) is demanded and long execution time is possible, serial approach is preferred being a minimalist implementation which takes more

Figure 2.15: Xilinx FPGA Design Flow

clock cycle to generate a result.

On the other hand, if faster computation is the most important issue, regardless of the hardware resource utilization, then parallel approach is the best option, also called systolic approach. This style is better suited for example in the case of DSP industries where parallelism capability should be exploited, i.e., replication of hardware functions that operate concurrently in different parts of the chip. Hence this approach will naturally be the one under study in this project.

Besides these two, we also have an approach which covers both of the styles previously mentioned, suiting all applications which demand optimization of both resource utilization and execution time, and improvement of area/speed metric.

In figure 2.16 [16] we can see a scheme of all the three approaches illustrating the speed/area trade-off in FPGAs.

## 2.5.7 IP (Intellectual Property) Cores

IP core is basically a complex pre-tested system-level function. It simplifies the design specification step by abstracting designers from gate-level details and it also helps reducing development time. In fact, we take advantage of various benefits when using ipCores, such

Figure 2.16: Illustration of the speed/area trade-off in FPGAs

#### as:

- Faster time to market;

- Simple development process;

- Minimal design risk;

- Reduced software compile time;

- Reduced verification time;

- Predictable performance/functionality.

IP Cores can have several uses namely DSP filters, Block RAMs, PCI bus interface, Universal Asynchronous Receiver/Transmitters (UARTs), Central Processing Units (CPUs), Ethernet controllers, among others. They are very reliable due to the fact they are extensively tested before launched to the market, and are part of the growing electronic design automation industry trend towards repeated use of previously designed components.

They can be subdivided in 3 main categories: Hard cores, firm cores and soft cores. Hard cores are physical units based in IP design and are more commonly used for plug-and-play applications, hence not as flexible and portable as the others two types. Firm cores are similar to hard cores but configurable to various applications. Soft cores are the most flexible, and exist as a list of logic gates and its interconnections featuring an integrated circuit (netlist) or as HDL code. The latter will be used in this project integrated in the FPGA and provided by Xilinx technology, and will be discussed further with more detail.

## 2.6 Development board (Genesys Virtex-5 LX50T FPGA Development Board)

Genesys Virtex-5 FPGA circuit board (figure 2.17) is a complete digital circuit development platform based on a Xilinx Virtex-5 LX50T FPGA [17] already discussed in earlier sections. It includes various resources, namely Gbit Ethernet, HDMI Video, 64-bit DDR2 memory array, audio ports and *Universal Synchronous Bus* (USB) ports. This platform is compatible with all Xilinx CAD tools, including ChipScope, EDK and the free Webpack. It includes Digilent's Adept USB2 system, which offers device programming, real-time power supply monitoring, automated board tests, virtual I/O, and simplified user-data transfer facilities. There is also built into the board, a second USB programming port, based on the Xilinx programmable cable.

Figure 2.17: Genesys Virtex-5 FPGA Development board [17]

The Virtex5-LX50T is optimized for high-performance logic and offers [17]

- 7200 slices, each containing four 6-input LUTs and eight FFs;

- 1.7 Mbits of fast block RAM;

- 12 digital clock managers;

- Six phase-locked loops;

- 48 DSP slices;

- 500 MHz+ clock speeds.

It has also the following features:

- Xilinx Virtex 5 LX50T FPGA, 1136-pin BGA package;

- 256Mbyte DDR2 SODIMM with 64-bit wide data;

- 10/100/1000 Ethernet PHY and RS-232 serial port;

- Multiple USB2 ports for programming, data, and hosting;

- HDMI video up to 1600x1200 and 24-bit colour;

- AC-97 Codec with line-in, mic, and headphone;

- Real-time power monitors on all power rails;

- 16Mbyte StrataFlash for configuration and data storage;

- Programmable clocks up to 400MHz;

- 112 I/O's routed to expansion connectors;

- GPIO includes eight LEDs, two buttons, two-axis navigation switch, eight slide switches, and a 16x2 character LCD;

- Ships with a 20W power supply and USB cable;

### 2.6.1 Adept System Serial Port

Genesys board host two 2-wire RS-232 Serial ports (figure 2.19), one with a DB9F connector (for DTE connection), and one with a three-pin 100-mil header connector (including TX, RX and GND). A ST3232 level-shifting buffer is used to provide RS-232 signal levels on both ports. The former is the one that will be used initially, for serial communication between the computer and the FPGA.

### 2.6.2 Oscillators/Clocks

Genesys development board includes several clock sources available (fig. 2.20), including a 3.3V 100 MHz crystal oscillator, a socket for a user-supplied half-size DIP oscillator, and two high-speed and highly stable differential clocks sources produced by a programmable clock

Figure 2.18: Digilent Power plug-in, on button and USB programming port [17]

generator (IDT 5V9885). This clock generator is programmed by origin to produce several clocks required by the Genesys platform, including a 25MHz clock for the Ethernet PHY, a 24.576MHz clock for the Audio codec, a 12MHz clock for the USB circuit, and two differential clocks (100MHz and 200MHz) for use by user circuits in the FPGA.

## 2.7 VHDL

## 2.7.1 History

VHDL is the acronym for Very-High Speed Integrated Circuits Hardware Description Language and is one of the two most important HDL languages of the Programmable Logic Devices world industry, together with Verilog HDL, also common in PLD design projects. This behavioral language was developed in the 80s by the defense department of USA to substitute the complex manuals which used to describe ASICs operation, an important technology which constituted some equipments sold to the american military forces. By that time, the adopted

Figure 2.19: Adept system Serial port

methodology for projecting circuits was based on diagram schematics, and the department of defense aimed to develop a language that, regardless, of the original format of the circuit, could work as an efficient description of the circuit, allowing different vendors and participants to understand the overall operation, standardizing the communication. Also, in order to avoid re-inventing concepts that had been already thoroughly tested in the development of Ada programming language, the Department of Defense wanted this new language to have as much as of the syntax as possible based on Ada.

In that time, there was a big need for a language with the capability to produce a circuit without having to explicitly specify connections between components, from a textual description. Consequently, VHDL was a success and, by 1987, when its definition came to the public domain, it was standardized by IEEE, amplifying even more its utilization. This initial version of VHDL included a wide range of data types, including numerical (integer and real), logical (bit and Boolean), character and time, plus arrays of bit called bit\_vector and character called string. However, VHDL naturally suffered a review, being upgraded several times during the last few years, with the last upgrade happening in 2008[18].

### 2.7.2 Design Cycle

VHDL is a HDL that covers all levels of the circuit design cycle, as it is confirmed in the following quote, taken from the preface of the Language Reference Manual (IEEE-1076, 2008):

Figure 2.20: Genesys Clock System [17]

"VHDL is a formal notation intended for use in all phases of the creation of electronic systems. Because it is both machine readable and human readable, it supports the development, verification, synthesis, and testing of hardware designs; the communication of hardware design data; and the maintenance, modification, and procurement of hardware."

Notice in the keywords of this quote, "all phases", which means that VHDL is indeed intended to cover every level of the design cycle, from the system specification to the netlist, resulting in a language rather large and puzzling, although not necessarily difficult to learn. In fact, we can think in VHDL as a hybrid language which contains features that fit better one or more stages of the design cycle. Basically each stage is covered by one of the three subsets of the whole language, one for system modeling (specification phase), one for register-transfer level (RTL) modeling (design phase), and another for netlist (implementation phase). The first two stages are carried out by human designers, while the last stage is largely performed by synthesis. In figure 2.21 we can see the illustration of the idealized design cycle. [19]

In the first stage, the purpose of the VHDL system model is to be used as a formal specification of the design which can be simulated to check its functionality, and also can be used to confirm with a customer that the requirements have been fully understood, which is a very important market-oriented feature of this language. In the second phase of the design

Figure 2.21: The VHDL-based hardware design cycle

cycle, this system model is converted into a RTL design in preparation for synthesis. At this stage of the design, there is a specification of the timing at the clock cycle level, and of the particular hardware resources to be used at the block level. The third and last stage of the design constitutes the synthesis of the RTL design to produce a netlist, which should meet the area constraints and timing requirements of the implementation. Of course this is in theory since, in practice, as we'll see in this project, this may not be the case and most of the times modifications are required, which will impact on the earlier stages of the design process.

### 2.7.3 The Standardisation Process

Part of this process requires the language to be upgraded periodically, which was established to happen each 5 years. However, in practice, and due to the industry demand, updates have been happening irregularly and hence, it is important to differentiate between the changed versions over the years. For example, the original standard created in 1987, is usually referred to VHDL-1987, making subsequent versions to be referred in a similar way, i.e., according to their year of ratification.

Below we can see a summary of the different versions and changed features of the language, for synthesis [19]

- VHDL-1987 The original standard;

- VHDL-1993 Added extended identifiers, xnor and shift operators, direct instantiation of components, improved I/O for writing test benches. Most of the synthesis subset of

VHDL is based on VHDL-1993;

- VHDL-2000/2002 Nothing of relevance to synthesis;

- VHDL-2008 Added fixed-point and floating-point packages. Added generic types and packages, enabling the use of generics to define reusable packages and subprograms. Enhanced versions of conditionals. Reading of out ports. Improved I/O for writing test benches. Unification of VHDL standards.