# We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

4,800

122,000

International authors and editors

135M

Downloads

154

Countries delivered to

Our authors are among the

TOP 1%

most cited scientists

12.2%

Contributors from top 500 universities

#### WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected.

For more information visit www.intechopen.com

# The Finite Element Analysis of Weak Spots in Interconnects and Packages

Kirsten Weide-Zaage

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/50779

#### 1. Introduction

Concerning the mechanical stress and the electrical-mechanical behavior ULSI multilevel metallization systems are more and more sensitive against influences of geometrical and material changes. The mechanical and electrical reliability of these metallization systems is influenced by this. The reliability of such metallization systems is investigated by thermal and thermal-electrical accelerated stress tests under high temperature load. This leads to degradation due to electro-, thermo- and stress migration. This is one major concern in reliability investigations. Generally measurements are time consuming, expensive and the time-to-market cycle is in the focus of interest too. The prediction of local weak spots in interconnects, vias and solder bumps by finite element simulations are a helpful procedure. Beside this the modern 3-d integration leads to more complex material compositions in the systems concerning the coefficient of thermal expansion (CTE) and other material properties. Higher applied currents on the interconnects and bumps result in Joule heating, high temperature gradients and mechanical stress gradients in the bump and metallization systems. The temperature gradients are much higher compared to systems with wide interconnect lines and bumps with large diameters like in conventional packages. Due to this in ball grid array (BGA) bumps as well as μ-bumps and small through silicon via (TSV) connections current induced migration effects as electromigration (EM) and as result of the high temperature gradients thermomigration (TM) can occur. In interconnects consisting of copper caused by stress gradients due to the different material properties under high temperature load also stress migration (SM) occurs.

In this chapter the degradation phenomena in dual damascene copper metallization structures as well as degradation in bumps,  $\mu$ -bumps and TSV are presented. The degradation is current, temperature and mechanical stress induced under a high applied current and temperature load. The finite element analyses and the mass flux divergence

calculation of these phenomena will show the suitability of the method in comparison with experimental results. For a prediction of the weakest spot the suitability of the finite element mesh as well as the modeling concerning the structure shape has to be investigated. Especially edges in the model can influence the quality of the results. The geometrical data of the different metallization or package structures can be taken from the layout as well as optical, scanning microscope or other analytical techniques. Especially for the prediction of the electromigration induced weakest spot in the system, the location of the maximum current density is a major indicator for the fault location. Due to this the maximum current density at localizations of structure inhomogeneity must be checked up. Out of this the maximum current density is calculated by conformal mapping to predict an optimized modeling concerning the shape of the edges and the use of a radius instead of edges. Geometrical variations like the thickness of the first and second metallization and a comparison of the different migration mechanisms will be presented. Concerning the mechanical stress of the DD-Cu metallization the process induced stress will be considered with different processing temperatures of the copper metallization. The influence of different dielectrics on the mechanical stress is also determined. Compared to DDmetallizations and the traces, the bumps are only exposed by electro- and thermomigration. The thermal-electrical-mechanical behavior of μ-bumps and TSV will be shown for a Waferon-Wafer (WoW) structure.

# 2. Calculation of the migration mechanism

To figure out the possibilities of determining the effects of migration in solder bumps, interconnects, via and conductive pathways shall be shown here. Migration, particularly in copper or aluminum metallization or migration of solder bumps of a flip-chip package, are presented in [Banas, Hou, Liu 2007, Liu2008, Tan, Wang]. Simulation algorithms are based on analogies and allow only partly- or no material or sizing variations.

Basically, migration processes are described in the metallization on the consideration of diffusion processes. These diffusion processes can lead to a change in dimension or change of geometries of the metallization [Wever]. On one side material loss or the hole formation at these locations leads to tensile stress, while it comes in places of material accumulation to a compressive stress. This leads to a reflux, also called the back stress in the material. There is a critical length existing, which compensates the electromigration related flux and the reflux. The migration of atoms leads to a change of the expansion in the metal, which then in turn changes the chemical potential. Since the chemical potential is very often influenced by a stress term, this leads to stress gradients and a reflux. In microelectronic applications the current flux pathways are subject to large thermal strain before any current load applies. This thermal strain, along with the strain caused by the electromigration can lead to a nonlinear reflux. Also, in the interconnects local self-heating take place, providing a contribution to the migration of the thermal gradients due to the local temperature increases. The components of the electrical, thermal and stress migration flux are added by superposition.

The diffusion coefficient with the activation enthalpy of  $\Delta H$  is defined as follows:

$$D = D_0 e^{-\Delta H/k_B T}$$

(1)

The change of place takes place at cubic (fcc) metals such as Cu, Au and Ag across the holes. The activation enthalpy is additively composed of the enthalpy of formation and the activation energy for the hole formation. Both are nearly the same size. With equation (1) and Do as temperature independent diffusion constant as well as the melting temperature Tm [Heumann, Philibert] applies:

$$5 \cdot 10^{-6} < D_0 < 5 \cdot 10^{-4} [m^2/s], \quad dH \cong 1.5 \cdot 10^{-3} T_m [eV]$$

(2)

Due to this a diffusion coefficient of D(T<sub>m</sub>)≈10<sup>-8</sup> cm<sup>2</sup>/s [Heumann] is resulting.

| Parameter |                   | Al       | Al Cu |         |

|-----------|-------------------|----------|-------|---------|

|           | Tm                | 660      | 1083  | 960     |

|           | $\Delta V/\Omega$ | 0.71-1.3 | 0.9   | 0.7-0.9 |

|           | E [eV]            | 1.234    | 2.15  | 1.921   |

**Table 1.** Melting Temperature, Active Volume and Activation Energy [Philibert].

In the case of multiple components, for example solder bumps, all main materials must be involved in the material transport. In the example of a material of two components A and B, and the chemical or interdiffusion coefficients, there are the partial diffusion coefficients DA and D<sub>B</sub> [Wilkenson]. Using the Darken equation, the diffusion results as follows:

$$v = (D_A - D_B) \frac{\delta N_A}{\delta x} \quad with \quad \tilde{D} = D_B x_A + D_A x_B$$

(3)

From the migration velocity v, the chemical diffusion coefficient  $\widetilde{D}$  and the mole fraction,  $x_A$ and x<sub>B</sub> of the considered components the partial diffusion coefficients D<sub>A</sub> and D<sub>B</sub> can be determined.

The direction of electrical transport in alloys such as leaded solder materials based on Sn, goes, depending on the proportion of Pb to the anode or the cathode. In terms of thermotransport moves the Pb in Sn to the cold part of the sample.

There are different diffusion paths in the material. These are the grain boundaries, surfaces to adjacent materials and the volume or bulk. In the aluminum as a metallization material primarily grain boundary diffusion occurs. In contrary in copper as metallization material predominantly interface or surface migration is occurring.

In the calculation of grain boundaries, the surface diffusion as well as the intermediate phase diffusion must be considered in thin layers. Atomistic transport along a grain boundary or phase boundary has a low activation energy and is therefore by orders of magnitude faster than in the crystal itself. The analytical models for the grain boundary diffusion  $\delta$  D<sub>GB</sub> are only valid for the self diffusion in pure metals [Kaur]. The part of electromigration at grain boundaries depends also on the effective width of the grain  $\delta$  (d) concerning the mass transportation in relation to the average grain size.

A composition of the interconnect from almost poly crystalline parts and parts where bamboo structured grains occur, leads to the predominant grain diffusion on one hand and on the other to volume diffusion and thus to high gradients in the mass flux. If the mass flux is blocked by a large grain, then the material accumulates relating to direction of the electron or material flux, in front of the blocking grain, while it comes behind the blocking grain to a material loss. For grain boundaries in the area of 280nm the diffusion coefficient of the grain boundary diffusion is in the range of the bulk material  $D_{GB} \cong D_{Bulk}$  [Kaur].

Only above a defined threshold current density  $\vec{j}$ th, resulting from the Blech effect and denoted as 'short-length effect', it comes to effective place change and thus to the mass transportation or material flux [Blech]. The mass flux is dependent on the atomic particle density N, the Boltzmann constant  $k_B$ , the local temperature T, the current density  $\vec{j}$ , the specific resistance  $\varrho$ , the diffusion process relating activation energy  $E_A$ , the diffusion coefficient  $D_0$ , and the effective charge eZ.

$$\overrightarrow{J_{EM}} = \frac{N}{k_B T} e Z^* \left( \vec{j} - \vec{j}_{th} \right) \rho D_0 \exp \left( -\frac{E_A}{k_B T} \right)$$

(4)

The thermotransport denoted as Soret-effect is a phenomenon of overlay of diffusion and heat conduction. They closely resemble the electrotransport with the difference that the considered system is not isothermal [Wever]. There is a flux of soluted atoms and the heat flux. These fluxes are described about the chemical potential and the thermal gradients. Without the occurrence of concentration gradients the equation for thermal flux is:

$$\overrightarrow{J_{TM}} = -\frac{NQ^*}{k_B T^2} D_0 \exp\left(-\frac{E_A}{k_B T}\right) grad T$$

(5)

$Q^*$  represents here the transported energy at a constant temperature and is commonly referred to as reduced heat of transport or transfer. The ratio  $Q^*$  /  $k_BT^2$  is referred as Soret coefficient. The heat of transport is the heat flux per unit of material without temperature gradients. Is the value of  $Q^* > 0$  a heat flux is generated to keep the soluted atoms isothermal, which takes place towards the dissolved flux. Is  $Q^* < 0$  the flux of dissolved particles and the heat flux are counter set. It follows that in an isothermal system, a density gradient produces a thermal flux and vice versa a temperature gradient leads to a material flux [Shewman]. The heat of transport is approximately equal to the activation energy for the material flux [Jaffe].

The differences of the coefficient of thermal expansion (CTE) between the metallization material and surrounding materials produce, depending on the ambient temperature a mechanical stress. This in turn leads to a material flux within the metallization. Under strain the enthalpy for example of tensile-stress formation in a grain boundary is reduced, which increases the concentration of holes [Heumann].

$$\overrightarrow{J_{SM}} = -\frac{N\Omega}{k_B T} D_0 \exp\left(-\frac{E_A}{k_B T}\right) \operatorname{grad} \sigma_H$$

(6)

The  $\Omega$  represents the atomic volume and  $\sigma_H$  the hydrostatic stress. Out of the components of the electrical, thermal, and stress migration, the total mass flux in the metallization structure emerges through superposition from the equations (4, 5 and 6).

The formation of material accumulation or void formation requires a divergence in the flux of the total mass flux. Only divergences lead to a change in the density of the material. The calculation of the mass flux and mass flux divergence in metallization, traces and bumps in the past were done using analogies between the electrical and thermal and the thermal mechanical behavior or a variation of the materials or dimension were not possible [Banas, Hou, Liu 2007, Liu 2008, Tan, Wang]. This lead to an overestimation of the temperature gradients and current density like proposed in [Ogurtani]. Without any applied current and temperature gradients the calculation of the stress migration is not possible.

With the new program code the divgrad of T and  $\sigma$  are calculated directly based on the simulation results. The calculation of the mass flux is done for each element under consideration of the neighbor elements. Out of this the stress gradients are calculated. The divgrad terms are calculated on base of the super elements under consideration of an Ansatzfunction. The calculated values for the different migration mechanisms are reloaded into ANSYS for graphic display. Out of this the stress migration can be calculated under SM stress test conditions without any applied current or temperature gradients. The simplified equations neglecting concentration gradients for the different migration mechanism are:

$$\operatorname{div} \overrightarrow{J_{EM}} = \left(\frac{E_A}{k_B T^2} + \frac{\alpha_\rho}{1 + \alpha_\rho (T - T_0)} - \frac{1}{T}\right) \cdot \overrightarrow{J_{EM}} \cdot \operatorname{grad} T \tag{7}$$

$$div \overrightarrow{J_{TM}} = \left(\frac{E_A}{k_B T^2} - \frac{2}{T}\right) \cdot \overrightarrow{J_{TM}} \cdot grad \ T - \frac{QND}{k_B T^2} \cdot \Delta T \tag{8}$$

$$div \overrightarrow{J_{SM}} = \left(\frac{E_A}{k_B T^2} - \frac{1}{T}\right) \cdot \overrightarrow{J_{SM}} \cdot grad \ T - \frac{\Omega ND}{k_B T} \cdot \Delta \sigma_H \tag{9}$$

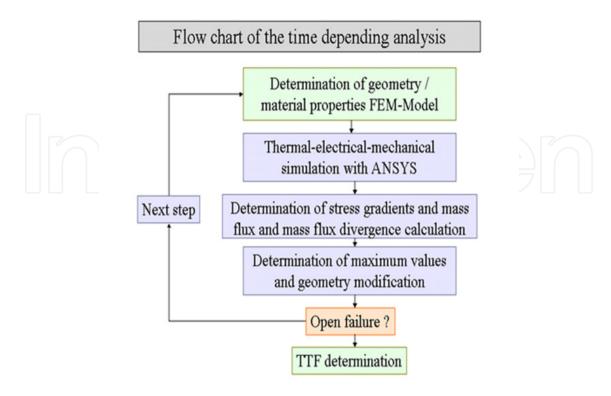

In equation (7-9) N is the atomic concentration, the Boltzmann constant kB, the local temperature T, the resistivity  $\varrho$ , the atomic volume  $\Omega$ ,  $Q^*$  the heat of transport, the activation energy EA (taken from grain boundary and interface migration as strongest influence) and σ<sub>H</sub> is the hydrostatic stress. The simulation and calculation sequence is shown in figure 1.

# 3. Modeling and simulation improvements

The numbers of elements, which are determining the mesh and due to this the density of the nodes have a strong influence on the accuracy of the simulation. Out of this the mesh of the investigated metallization or metallic material as main interesting point in the simulation plays a major rule. In the metallization itself the potential as well as the temperature is calculated. The metallization is surrounded by dielectric material and the traces by FR-4 or PCB. The bumps can be surrounded by underfillers made of different plastic materials.

Figure 1. Simulation and calculation sequence for one cycle (static) and more cycle (dynamic).

Concerning the mechanical stress calculation the interfaces play also an important rule. Due to the different materials and their material properties the stress in the structures can be high and can therefore have a strong influence on the reliability of the structures. The calculation of the stress gradients and stress migration mass flux divergence is strongly affected by the accuracy of the mesh.

## 3.1. Advantages of FEM compared with other applicable methods

Simulation methods like finite difference, finite element and Monte Carlo method are common in the electrical engineering. Monte Carlo method is described for the calculation of time to failure (TTF) distributions induced by electromigration [Huang]. Also in the scope of semiconductor simulation it is widely used [Jacoboni]. The complexity of the metallization and bump structures in combination with the question of multiphysic investigations makes this approach inconvenient in use. The application of the finite difference method is described in investigations of the intermetallic phase growth for instance [Chao]. A model for electromigration calculated by concentration gradients is described in [Joo] and the void evolution and motion was investigated by [Averbuch]. The mass transport along interface caused by electromigration using the level-set method is described in [Li]. All these approaches consider only a part of the thermal-electrical and mechanical behavior.

Calculations in the scope of the coupled thermal-electrical-mechanical behavior of metallization structures and bumps can be sufficiently carried out by commercial programs

like ANSYS®, ABAQUS or COMSOL using the finite element analyses. In the following investigation ANSYS® is used as simulation tool.

# 3.2. Mesh density and singularities

In the thermal electrical calculation the degree of freedom is only the temperature. The mesh of the surrounding material depends in the investigated case of the metallization and due to this of the metallization mesh. A coarse mesh of the metallization can lead to an insufficient determination of the temperature in the isolation materials. Out of this the mesh of the metallization should be investigated with regard of an optimization.

The mesh can be easily refined by varying the count of the nodes. If a convergence concerning the change of the potential voltage is found the mesh is sufficient. A predication concerning the convergence of the current density at inhomogeneities like vias or edges in the metallization cannot be done. At these positions a strong dependence of the maximum current density due to current crowding in relation to the model of this inhomogeneity occurs. The layout from the EDA tools give at such positions rectangular edges or edges with a defined angle. Taking into account such an angle in the model may lead to insufficient calculation of the local current density at this position. Due to this the relation of the current crowding and angle of the edge will be investigated here.

Considering the two-dimensional case, choosing a right angle at the edge of a metallization a singularity will occur. In this case the current density can be calculated analytical with an infinity value [Betz]. The result of the numerical analysis of the current density at this position converges to a defined value due to the fact that the neighbor elements are taken into account for the calculation. If the right angle is replaced by a radius, the calculated current density depends on the selected shape of the radius, the element size and the element shape itself. For a determination of the real current density in the structure and the optimized radius, the edge of a simplified metallization consisting of aluminum, is investigated for the 2-dimensional and 3-dimensional case in sub-models. The boundaries in the calculations were taken of the coarse model.

In the 2-dimensional as well as in the 3-dimensional case the current crowding jmax/jin increases with increasing element count cubically and the relation of the maximum current density to the applied current density jmax/jin increases with decreasing element size exponentially. Out of this the numerical solution converges in the case of infinite small elements to the theoretical expected value. In the case of a curvature of the edges, the current crowding jmax/jin has for increasing element counts as well as decreasing element size for every taken radius a constant value. Due to this the element count used in the simulations depends on the element size as well as the used radius in the model. A decreasing radius down to the range of an rectangular angle with constant element count leads to an increase of jmax/jin.

Not in every case optical or scanning electron microscopy pictures are available for a determination of the structure shapes after the production process. Due to this for a

384

determination of the optimized radius two dimensional simulations can be compared with results from the calculation of the maximum current density out of conformal mapping. The maximum current density and details about the homogeneity of the current density and resistance behavior at the investigated places can be achieved by the conformal mapping.

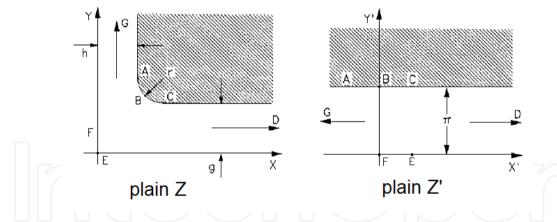

The calculation of the maximum current density is done by the following approach. In general for the analytical calculation of the current density distribution at the edge of an interconnection, a bent metallization with different width g and h and a radius r can be converted by two times conformal mapping into a flat conducting band with width  $\pi$  in the Z' plane. In this flat conducting band a homogenous current density distribution can be assumed (figure 2). With the back transformation of this homogenous current density distribution into the Z plane the current density distribution along the path A-B-C can be achieved and due to this the maximum current density. With the parameters S=g/h as ratio of the metallization width and P=r/h as ratio of the radius r to the smaller metallization width h and the applied current density  $j_{in}$  in the vertical part of the metallization shall apply under the condition the P << 1 [Hagedorn]:

$$j_{\text{max}} = 1.04^{\left[\frac{S^2+1}{PS^2}\right]^{\frac{1}{3}}} j_{\text{in}}$$

(10)

With equation 10 the current crowding  $j_{max}/j_{in}$  can be determined depending on the metallization width and the radius.

**Figure 2.** Original figure of a two dimensional edge of an metallization in the Z-plane (left). Metallization after two times of conformal mapping in the Z' plane (right).

In the 2-dimensional case a good correlation between the analytical solution and the maximum current density determined by the simulations can be found. In the 3-dimensional case the analytical solution is valid under the assumption of a homogenous current density distribution in the via, which means that the current density distribution can be mapped on the 2-dimensional case.

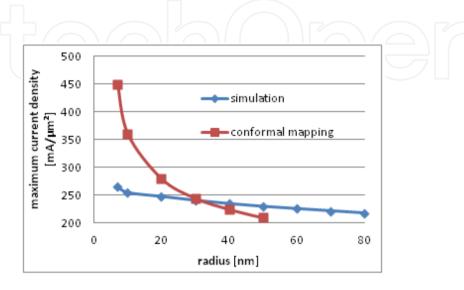

The maximum current density depending on the radius for a fixed element count is compared to the simulated values. The results are shown in figure 3. For a radius of  $0.03\mu m$

a good correspondence between simulation and analytical solution is found. For a radius above 30nm the simulated values are caused by the increased element size above the analytical values. A radius below 30nm has an insufficient mesh and due to this the simulated values are beneath the analytical values. To get compliance between simulation and analytical solution the mesh has to be refined. This leads to an increase of the calculation time and is therefore not useful.

Figure 3. Max. current density depending on the radius for the interconnect/via edge. Analytical solution done by conformal mapping and simulation.

## 3.3. Mechanical stress and stress gradients

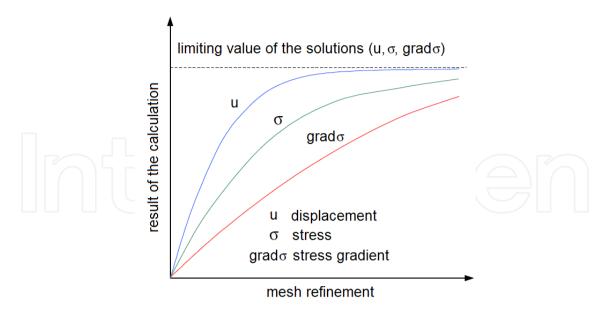

In the finite element method simulation of the mechanical stress, the calculated unknown parameters are the displacement of the nodes. The different forces are calculated by the derivation of the displacements. The form function is continuously but not smoothed between the elements. Due to this the values at the nodes have to be averaged. Due to this and caused by the simplified form function and the limited element expansion the FEM is an approximation method. This can lead to failures in the calculation of the dilatations. When the results of an inaccurate mesh are derived the inaccuracy concerning a second derivation will be intensified. The correlation of the accuracy and mesh refinement is shown in figure 4 [Eichelseder]. From this knowledge it is clear that the distribution of the dilatation of the components S1 to S3 is more accurate than the strain distribution resp. the Von Mises Stress (VMS). This fact also implies that a simplified mesh or a coarse mesh can deliver accurate results concerning the dilatation. The derivate strain shows accurate values only after a refinement. After an additional refinement the gradient of the strain and out of this the hydrostatic stress (HS) can be calculated with a good accuracy. The calculation of the mass flux divergence due to stress migration includes also a derivation of the stress gradients, which will affect the accuracy additional. The accuracy of the finite element mesh has to be investigated before the mass flux divergence calculation is done. And the results have to be handled with care if the mesh is not adequate tested.

**Figure 4.** Correlation of the accuracy and mesh refinement [Eichelseder].

# 4. Metallization

#### 4.1. Metallization variation in the 90nm node

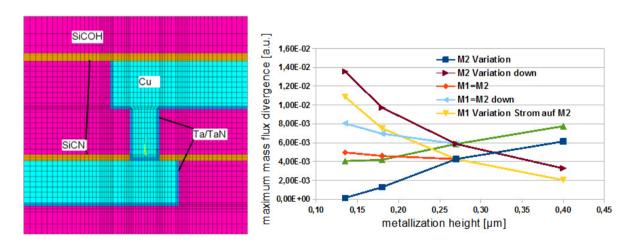

The investigated DD copper structure based on the dimension of the 90nm scaled down to the 65nm process technology. The model consists of SiCN as cap layer, Ta/TaN as barrier layer and different dielectrics like Silk™, Black Diamond II™ and SiCOH. In the mechanical calculations the process temperature using the birth and die algorithm in ANSYS are included, caused by the fact that the use of a reference temperature for the stress free state is not sufficient [Weide-Zaage 2008].

Figure 5. Mesh of the investigated structure (left) and mass flux divergence vs metallization height for a variation of M1 and M2 (right).

The mesh of the investigated structure is shown in figure 5 (left). For simplification one via with two metal links right and left hand was generated. As one example for this proposal the metallization height here was varied. In the investigated cases for electromigration the current flux direction was calculated downstream from the second metallization M2 to the first metallization M1 and in the opposite direction upstream. The mass flux divergence of the variation is shown in figure 5 (right). It was found that the variation of the first metallization M1 and the variation of the second metallization M2 show a big influence on the mass flux divergence and out of this on the reliability of the structure. The weakest location found here is in and beneath the via.

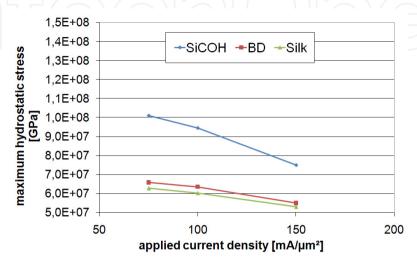

**Figure 6.** Maximum hydrostatic Stress for BDII<sup>TM</sup>, Silk und SiCOH.

For technology nodes in the range of 500nm and below SiO<sub>2</sub> or combinations of USG (undoped-silicate-glass), PSG (phosphosilicated-glass) or FSG (fluorine-doped-silicate-glass) as a customary dielectric (IMD) is used. For products produced in nowadays low-к dielectrics, with a low dielectric constant such as Silk TM, SiCOH, Black Diamond, or MSQ TM II are used.

Figure 6 shows the maximum hydrostatic stress as a function of the applied current density for the different dielectric materials. The greatest mechanical stress occurs at a SiCOH dielectric and the lowest at Silk TM.

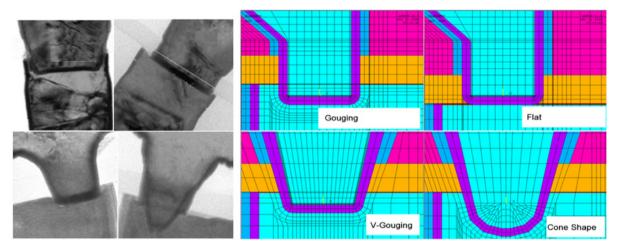

# 4.2. Separated migration mechanism with different via shape

A second model is based on dimensions of the 65nm technology node with a wide line and different via bottom geometries. The model is shown in figure 7 based on SEM pictures from the literature [Delsol, Lee]. Tantalum and TaN were chosen as barrier material, SiCN as capping material and SiCOH was chosen as dielectric material. The structures were investigated under test conditions with an applied current density of 1.5MA/cm<sup>2</sup> taken from [Lin2006a, Lin2006b]. The thermo-mechanical investigations were carried out considering the process-induced stress. The process temperatures are given in table 2.

The stress state in the copper metallization is strongly related to the process temperature of the copper. A high process temperature leads to a higher nearly stress free state of the whole structure compared to structures with lower temperatures [Matsuyama]. The nearly stress free state determined by investigating of the process induced stress is approx. 200°C. The calculation of the stress migration in the structures is described in [Weide-Zaage 2010].

Figure 7. SEM pictures from [Lin2006, Lin2006(2)] (left) and Finite Element Mesh of the via region of the four different bottom geometries (right).

|       | Young Modul (GPa) | Poisson | CTE (300K) | Process Temperature (°C) |

|-------|-------------------|---------|------------|--------------------------|

| Cu    | 125               | 0.34    | 16.7 10-6  | 200                      |

| TaN   | 185               | 0.33    | 6.6 10-6   | 40                       |

| SiCN  | 100               | 0.17    | 3 10-6     | 300                      |

| SiCOH | 15                | 0.3     | 11.6 10-6  | 350                      |

| Si    | 98                | 0.45    | 2.64 10-6  | 25                       |

**Table 2.** Mechanical properties and process temperatures used in the simulations

# 4.2.1. Electromigration test temperature 325°C

The electromigration behavior of the four models was investigated with current (flux in both directions) and an activation energy of 0.9eV. The different via bottom geometries were verified by comparison with investigations from literature. The calculated maximum mass flux divergences as well as the reciprocal values which are related to the MTF are given in table 3. Comparing a Gouging and a Flat via and a Cone Shape and a V-Gouging via the Gouging via is more reliable than the Flat via and the Cone shape via more reliable than the V-Gouging via. The simulated models show that the Cone Shape via has the best results concerning the electromigration behavior.

| Via-Shape     | div em     | (div em)-1 |

|---------------|------------|------------|

| Gouging Via   | 1.143 10-3 | 875        |

| Flat Via      | 0.917 10-3 | 1091       |

| V-Gouging Via | 0.939 10-3 | 1065       |

| Cone Via      | 0.672 10-3 | 1488       |

**Table 3.** Mass flux divergence and reciprocal mass flux divergence.

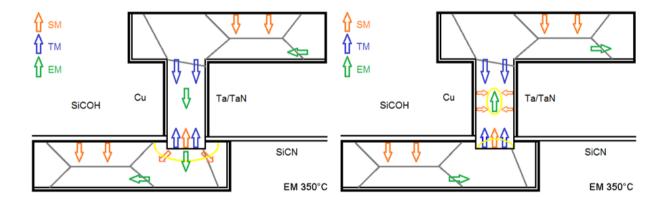

The failure locations due to the void formation after the electromigration test in the literature are found downstream at the bottom of the via and upstream in and over the via at the interface metallization cap layer. A schematically overview of the different migration effects like electro-, thermo- and stress migration mass flux electron flux upstream and downstream and supposed void formation (yellow) is drawn in the via structure shown in figure 6. The electromigration mass flux is depending on the current flux direction and temperature gradients, the thermomigration mass flux depend on the temperature gradients and the stress migration on the stress gradients, which occur at tensile regions also under electromigration test conditions. An arbitrary assumed grain distribution is grey colored in this graphic. Thermomigration mass flux (blue) in the investigated structures proceeds independent of the current flux direction from first as well as the second metallization into the via. The electromigration mass flux (green) is at the upper part of the via downstream in the same direction and at the via bottom in opposite direction of the temperature gradients and thermomigration mass flux. In the upstream case it is vice versa. Due to the process induced stress distribution in the metallization, under electromigration test conditions, the metallization is mostly compressive with some tensile regions. The stress gradients in the tensile regions may lead to a current direction independent migration. High stress migration (orange) is found at the bottom and beneath the via above and below the barrier. The stress gradients show above the barrier upwards and below the barrier downwards. At the interface of the cap layer and the metallization they show down. Only the occurrence of a migration pathway leads to voiding. For interface migration the stress gradients have to have a component into the direction of the interface. Also the existence of a grain boundary pathway supports the voiding. Out of this foot voiding as well as voids in the via itself, both indicated in yellow can be explained by this (figure 8).

Figure 8. Schematically electro-, thermo- and stress migration mass flux electron flux upstream and downstream and supposed void formation (yellow) in the via structure EM>SM>TM.

## 4.2.2. Thermomigration stress temperature 325°C

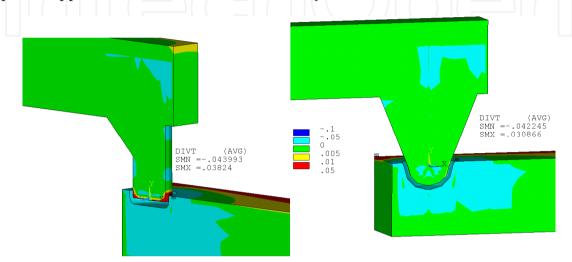

The thermomigration (Soret-Effect) was investigated under electromigration test conditions of 325°C. The calculation of the thermomigration shows high, values for the mass flux divergence. With temperature gradients of 50K/µm the gradients are high but not high enough to induce thermomigration. Gradients of 100K/µm are supposed to be an acceleration factor for the thermomigration. In figure 9 the mass flux divergence distribution due to thermomigration is shown. High values in the Gouging model are found at the via bottom in the via and at the corner of the metallization, barrier- and cap-layer. For the Cone Shape via high values are found only at the corner of the corner the metallization, barrier- and cap-layer. The activation energy for the thermomigration calculation is supposed to be too small and should be >1.2eV. Measurements of thermomigration activation energies of copper in copper are not known until now to verify this.

**Figure 9.** Thermomigration mass flux divergence distribution for the Gouging and the Cone Shape model.

# 5. μ-Bump, CuSn-pillar and TSV

# 5.1. µ-Bump in comparison with BGA-PoP

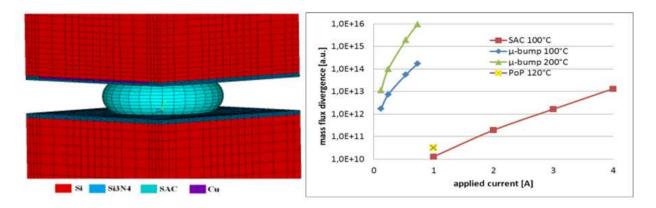

A variation of the applied current in a Package-on-Package (PoP) bumps [Meinshausen 2010 (a)] and µ-bump [Meinshausen 2011] was carried out and the mass flux divergence distribution was determined. The bumps in the FE model of the PoP device with one bump chain consist of SAC305 (SnAgCu). For the under-bump metallization (UBM) and the surface finishes 6µm thick Ni layers were used. As mold compound (MC) around the upper contact surfaces "Stycast 1090" was chosen. The simulations were carried out with anisotropic and temperature depending material parameters. In the FR-4 substrates five layers of Cu traces and Cu vias between the top and the bottom package are placed to connect the top and the bottom bumps. The height of the upper, the middle and the lower copper layers is 20μm, 18μm and 36μm. The width of all layers is 250μm. The model of a μbump between two ICs is shown in figure 10 (left). The dimensions of the μ-bumps are similar to the test structures used in [Labie]. The diameter of the μ- bump is 25μm and the height is 10μm. Over and under the μ-bump a 100μm silicon layer resp. a 50μm thick silicon layer is representing the ICs of a CoC (Chip-on-Chip) structure. The ICs are covered with a 1µm thick Si<sub>3</sub>N<sub>4</sub> passivation layer. The copper traces at the upper and the lower contact surface have a height of 0.5μm and a width of 32μm. The pitch is 40μm.

**Figure 10.** Model of the μ-bump (left). The different materials are indicated by colors. The mass flux divergence vs. the applied current for SAC bump and  $\mu$ -bump (right).

In figure 10 (right) the mass flux divergence depending on the applied current for the SAC PoP bump and the μ-bump is shown. Under the same applied current the mass flux divergence of µ-bumps is compared to PoP bumps about four orders of magnitude higher. Due to this fact the reliability of the μ-bump has a high electromigration risk. The weakest point of the u-bump was found at the top of the bump due to current crowding combined with high temperature gradients.

Figure 11. Temperature distribution in a BGA PoP Package with ICs (left) and maximum temperature in the bumps vs applied IC's power loss (right).

[Meinshausen 2010(b), Meinshausen 2012] investigated in previous simulations the heat flux density of IC stacks with a constant surface load. The heat loss of the ICs is one reason for the existence of an inhomogeneous temperature distribution in packages. An applied power of 2-8W for all ICs in the IC stack was investigated as boundary condition for the simulations. The temperature distribution in the package for a power loss of 8W is shown in figure 11, left side. The maximum temperature occurs in the IC stack. The bump temperature is much lower (figure11, right). This leads to a strong inhomogeneous temperature distribution. On the other hand the temperature gradients in the bumps are not as high compared to the EM simulation. Due to this in this investigated case thermomigration will not occur.

# 5.2. TSV with μ-bump

Through silicon vias (TSV) have a wide range of applications in the modern packaging. Three different kinds of TSV can be identified which are common under the topic of 3D IC packaging, 3D IC integration and 3D Si integration. Due to this the processing as well as the size of the TSV is completely different. The application can be divided into three topics.

- Package on Package stacking with TSV as connections between them

- Chip to Chip, Chip to Wafer or Wafer to Wafer stacking with SiO2 to Sio2 and Cu to Cu bonding.

- Wafer to Wafer stacking; Memory chip stacking TSV are used as connection between the chips; active or passive interposer.

In the case of the 3D IC integration the TSVs are necessary. Due to the fact that the data width is limited, the use of TSV with small sizes in the range of 5-10µm with a pitch in the range of 20-40µm a much wider I/O width is possible. The TSV shortens the way of the connections compared to the common wire bonding. Using the wire bonding the chip size has to be increased and due to this the costs increase. TSV as solution will solve this problem in future. For future 3D integration Cu-TSV as well as tungsten W-TSV will be used [Murugesan] caused by the fact that W is a capable material for sub μ-vias but not usable for power and ground applications due to its high specific resistance. Therefore Cu with a Ta barrier will be used.

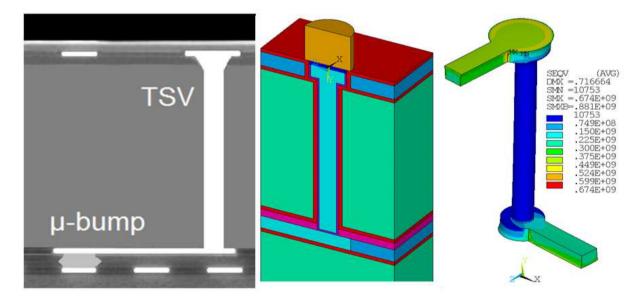

**Figure 12.** Schematic picture of a TSV and  $\mu$ -bump (left) and FE-Model (right).

As an example in figure 12 (right) the mesh of a TSV with a SAC pillar is shown. The right side of figure 12 shows schematically a TSV with a μ-bump [Leduc]. The geometrical data for the simulations are taken from [Kitada, Lo]. The diameter of the TSV was set to 9µm and the height was set to 80µm. The copper barrier in the TSV consists of SiN and TiN. The thickness of the interconnections is 7µm. The passivation consists of SiN.

On top of the TSV high VMS was found caused by the fact that the copper in the TSV is under pressure and the material is pressed out of the TSV. Concerning the EM high mass fluxes were found at the bottom of the TSV to the metal trace. At this position also high thermal mass flux occurs. High hydrostatic stress occurs at the bottom of the TSV to the metal trace. The stress increases about 10% for an increase of the applied current from 0.1 to 0.3A.

# 5.3. CuSn-pillar

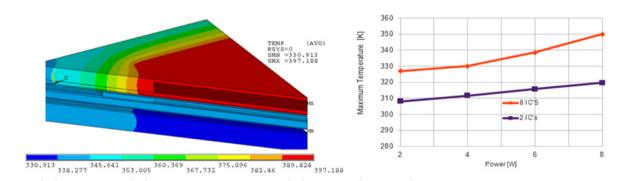

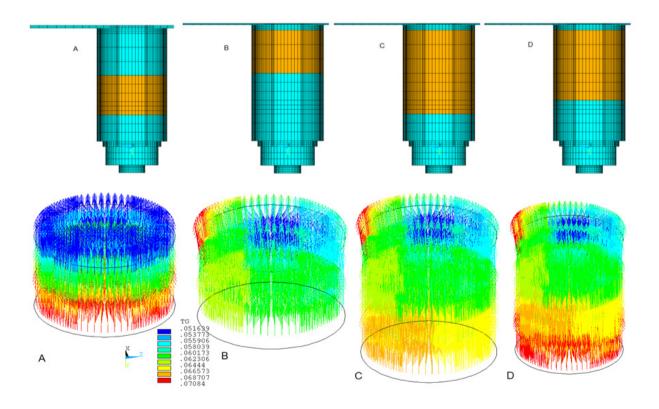

For a simplified assembly, a smaller pitch between the bumps and a low interconnect inductance CuSn-pillars can be used. Copper pillars are copper bumps with a thin layer of Sn on the top. These layer thicknesses can vary [Huffman, Syed]. The CuSn-pillars can be formed under pressure and a temperature load. This leads to the formation of Cu<sub>3</sub>Sn and Cu<sub>6</sub>Sn<sub>5</sub> phases. Due to this CuSn pillars with different Sn thickness and location in the bump were investigated. The bumps had a diameter of 24μm and a complete high of 45μm. Above the bumps a Cu trace and below the bumps a TSV (figure 12) were placed in the model. The applied current was set to 175 mA, the substrate temperature was varied from -50 to 150°C and the stress free temperature was set to 135°C. In figure 13 a part of the mesh and the temperature gradient distribution in the different bumps is shown.

Figure 13. Mesh of the CuSn Pillar with Cu in magenta and Sn in yellow (above) and temperature gradient distribution for the different models (below).

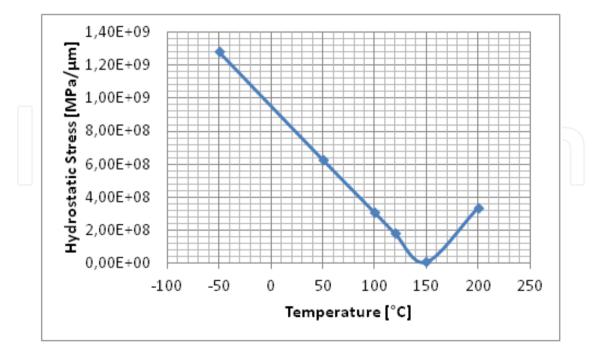

The homogenous temperature distribution the bumps can be achieved by a placement of the Sn in the middle (model A). In the case of model B-C high temperature gradients occur above the Sn near the copper trace. At this position also current crowding occurs. Both can lead to a weak link at this position. Depending on the current flow direction the flux will be increased or decreased. In figure 14 the hydrostatic stress depending of the substrate temperature is shown for model A the highest stress occurs for temperatures about -50°C near the reference temperature of the stress free state the stress is the lowest. The processing temperatures should be included in the model.

|   | HS [MPa] | Tmax [K] | Div J <sub>max</sub> [a.u.] |

|---|----------|----------|-----------------------------|

| В | 174      | 396,86   | 0,486e12                    |

| С | 175      | 396,54   | 0,459e12                    |

| D | 172      | 397,02   | 0,512e12                    |

**Table 4.** Hydrostatic Stress, Maximum Temperature and Maximum Mass flux Divergence.

**Figure 14.** Hydrostatic stress depending of the substrate temperature (model A).

## 6. Conclusion

The finite element analysis of metallization structures or packages and bumps provide an insight into local temperatures, current density and stress gradient distributions with the possibility of mass flux divergence calculation. A prediction of weak links in the structures helps to increase the reliability during the design phase. Also the costs will be decreased and redesigns avoided.

In future phase separation in the CuSn bumps by IMC growth as well as the influence of special placed grain boundaries and concentration gradients should be included in the model. The process induced stress should be also included in the package modeling.

# **Author details**

Kirsten Weide-Zaage Gottfried Wilhelm Leibniz Universität Hannover, Information Technology Laboratory, Germany

# 7. References

- Averbuch, A.; Israeli, M.; Ravve, I.: "Electromigration of intergranular voids in metal films for microelectronic interconnects", Journal of Computational Physics 186, 2, 2003, pp. 281-304.

- Banas, L.; Nürnberg, R.: "Finite Element Approximation of a Three Dimensional Phase Field Model for Void Electromigration", Springer, J. Sci. Computation, DOI 10.1007/s10915-008-9203-y.

- Betz, A.: "Konforme Abbildungen", Berlin, Springer Verlag, 1964, pp.22-33.

- Blech, I.A.: "Electromigration in thin aluminum films on titanium nitride", J. Appl. Phys. 47, 1976, p. 1203.

- Delsol, J. R.; Jacquemin, J.-P.; et. al.: "Improved electrical and reliability performance of 65 nm interconnects with new barrier integration schemes", Microelectronic Engineering 83 (2006) pp. 2377-2380.

- Chao, B; Chae, S.H.; et.al: "Electromigration enhanced intermetallic growth and void formation in Pb-free solder joints", J. App. Phys. 100, 084909 (2006)

- Eichelseder, W.; Unger, B.; Dannbauer, H.: "Neue Aspekte der Submodelltechnik in der finite Elemente Methode zur Beschleunigung des Entwicklungsprozesses", FEM-Konferenz Baden Baden, 1998.

- Hagedorn, F.B.; Hall, P.M.: "Right-Angle Bends in Thin Film Conductors", Journal Appl. Phys., Vol. 34, No.1, 1963, pp. 128-131.

- Heumann, T.: "Diffusion in Metallen", Springer Verlag, WFT 10, ISBN 3-540-55379-7, 1992.

- Hou, Y; Tan, C.M.: "Comparison of stress-induced voiding phenomena in copper line-via structures with different dielectric materials", Semiconductor Sci. Technology, 2009, pp.1-8.

- Huang, J.S.; Oates, T.S.: "Monte-Carlo simulation of electromigration failure distributions of submicron contacts and vias: a new extrapolation methodology for reliability estimate", Proceedings of the IEEE Interconnect Technology Conference 2000, pp. 208-210.

- Huffman, A.; Lueck, M.; et.al: "Effects of Assembly Process Parameters on the Structure and Thermal Stability of Sn-Capped Cu Bump Bonds", ECTC Conf. 2007, pp. 1589-1596.

- Jacoboni, C; Lugli, P.: "The Monte Carlo Method for Semiconductor Device Simulation", Computional Microelectronics", Edited by S. Selberherr, Vienna, Springer 1989, ISBN: 978-3-211-82110-7.

- Jaffe, D.; Shewman, P.G.: "Termal Diffusion of Substitutional Impurities in Copper, Gold and Silver", Acta Metallurgica, Vol.12, 1964, pp.515-527.

- Joo, Y.C.; Yang, T.Y.; et.al.: "Driving forces of mass transport in phase change materials and their effect on device failures", EPCOS 2011.

- Kaur, I.; Mishin, Y.; Gust, W.;: "Fundamentals of Grain and Interphase Boundary and Diffusion", John Wiley & Sons Ltd., 1995.

- Kitada, H.; Maeda, N.; et.al.: Development of Low Temperature Dielectrics down to 150°C for Multiple TSVs Structure with Wafer-on Wafer (WOW) Technology, IEEE, CMPT Tokyo 2010.

- Labie, R.; Limaye, P.; et.al: "Reliability testing of Cu-Sn intermetallic micro-bump 3D-device stacking", IEEE/Electronics-System-Integrationinterconnections for Conference (ESTC), Berlin, September 2010.

- Leduc, P.; Assous, M.; et.al: "First integration of Cu TSV using die-to-wafer direct bonding and planarization", IEEE Int. Conf. on 3D System Integration, 3DIC, 2009, pp. 1-5.

- Lee, K.-D.; Park, Y.-J.; Kim, T.: "Via Processing Effects on Electromigration in 65nm Technology, IEEE 06CH37728 44th Annual IRPS, 2006, pp.:103-106.

- Li, Z; Zhao, H.; Gao, H.: "A Numerical Study of Electro-migration Voiding by Evolving Level Set Functions on a fixed Cartesian Grid", Journal of Computational Physics 152, 2, 1999, pp. 281-304.

- Lin, M.H.(a); Chang, K.P.; et.al: 'Effects of Width Scaling, Length Scaling, and Layout Variation on Electromigration in Dual Damascene Copper Interconnects', IEEE RPSP, 2006, pp. 671-672.

- Lin, M.H.(b); Lin, M.T.; et.al: "Copper Interconnect Electromigration Behavior in Various Structures and Precise Bimodal Fitting", Jap. J. Appl. Phys. Vol. 45, No. 2A, 2006, pp.

- Liu, Y.; Irving, S.; et.al: "3-D Modelling of Elec-tromigration Combined with Thermal-Mechanical Effect for IC Device Package", 8th Int. Conf. EuroSimE 2007, pp.1-13.

- Liu, Y.; Liang, L.; et al.: "3D Modeling of electromigration combined with thermalmechanical effect for IC device and package", Microelectronics Reliability, Vol.48 (2008), pp. 811-824.

- Lo, W.-C.; Chen, Y.-H.; et.al: TSV and 3D Wafer Bonding Technologies For Advanced Stacking System and Application at ITRI, Symp. on VLSI Tech. Digest of Technical Papers, 2009, pp. 70-71.

- Matsuyama, H.; et al.: "Investigation of stress-induced voiding inside and under vias in copper interconnects with "wing" pattern", Proc. Conf. International Reliability Physics Symposium, IEEE/IRPS 2008, pp. 683-684.

- Meinshausen, L.(a); Weide-Zaage, K.; et.al: "; Virtual prototyping of PoP interconnections regarding electrically activated mechanisms" IEEE Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Micro-Systems, EuroSimE 2010, p. 1-4.

- Meinshausen, L. (b); Weide-Zaage, K.: "Exploration of Migration and Stress Effects in PoPs Considering Inhomogeneous Temperature Distribution", International Wafer-Level Packaging Conference (IWLPC), October 2010, pp. 137-145.

- Meinshausen, L.; Weide-Zaage, K.; et.al: "Electro- and Thermomigration in Microbump Interconnects for 3D Integration", IEEE Electronic Components and Technology Conf., June 2011, pp. 1444-1451.

- Meinshausen, L.; Weide-Zaage, K.; et.al:,,Thermal Management for stackable package with stacked ICs", EuroSimE 2012, p. 1-4.

- Murugesan, M; Kino, H.; et.al: High Density §D LSI Technology using W/CU Hybrid TSVs, IEEE/IEDM, 2011

- Ogurtani, T.O.; Akyildiz, O.: "Morphological evolution of voids by surface drift diffusion driven by capillary, electromigration, and thermal-stress gradients induced by steadystate heat flow in passivated metallic thin films and flip chip solder joints. I. Theory, Journal of applied Physics 104, 023521, 2008

- Philibert, J.: "Atom Movements Diffusion and Mass Transport in Solids", Monographies de Physique, 1991.

- Shewman, P. G.: "Diffusion in Solids", Mac Graw-Hill Series in Materials Science and Engineering, 1963/1989.

- Syed, A.; Dhandapani, K. et.al: "Cu Pillar and µ-bump Electromigration Reliability and Comparison with High Pb, SnPb, and SnAg bumps, IEEE Electronic Components and Technology Conf. 2011, pp. 332-339.

- Tan, C.M.; Roy, A.; et.al: "Current Crowding Effect on Copper Dual Damascene Via Bottom Failure for ULSI Applications" IEEE Transactions Dev. Materials Reliability 2005; Vol. 5,198.

- Wang, S.N.; Liang, L; et.al.;" Solder Joint Reliability under Electromigration and Thermal-Mechanical Load ", Elec. Comp. & Tec. Conf, 2007 pp1074-1083.

- Wever, H.: "Stofftransport im metallischen Festkörper", Angewandte Chemie, Nr.7, 1963, pp.309-352.

- Weide-Zaage, K.; Zhao, J.; et.al: "Determination of Migration Effects in Cu-Via Structures with Respect to Process Induced Stress", Microelectronic Reliability 48, 2008, pp. 1393-1397.

Wilkenson, D.S.: "Mass Transport in Solids and Fluids", Cambridge University Press, ISBN 0521624096, 2000.