# the world's leading publisher of Open Access books Built by scientists, for scientists

4,800

Open access books available

122,000

International authors and editors

135M

Downloads

154

**TOP 1%**

Our authors are among the

most cited scientists

12.2%

Contributors from top 500 universities

WEB OF SCIENCE™

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected.

For more information visit www.intechopen.com

# Materials Assessment and Process Characterization for Lead-Free Soldering

Chien-Yi Huang, Chen-Liang Ku, Hao-Chun Hsieh, Ming-Shu Li, Chia-Hsien Lee and Cheng-I Chang

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/51392

# 1. Introduction

Trends in the packaging of semiconductors are towards miniaturization and high functionality. Increased functional density and reduced I/O (Input/Output) spacing are the market trends. In the assembly process with surface mount technology (SMT), a solder paste consisting of solder particles and flux is deposited onto the PCB's bonding pads through stencil printing. The electronic components are then placed onto the printed circuit board (PCB) by a pick-andplacement machine. During reflow soldering, the solder paste melts and solidifies to form reliable solder joints. With the continuously increasing demands of electronic appliances, energy consumption and the use of hazardous substances, such as heavy metals and chemical ingredients, have become of serious concern. Traditionally used tin-lead solder is known to be harmful to human life and not compatible with an eco-environment. Environmental protection has become an international issue, and on July 1, 2006, the. European Union (EU) implemented a directive restricting hazardous substances (RoHS). One lead-free solder candidate, SAC305 (Sn96.5/Ag3.0/Cu0.5), has been widely used as a replacement for traditional tin-lead solder (Sn63/Pb37). Industry reports indicate that approximately 50-70% of soldering defects are attributed to the solder paste printing process. A sufficient amount of paste and the desired reflow soldering profile are mandatory for reliable interconnections. Solderability analysis is one of the major approaches in characterizing PCB assembly, quality control and reliability.

First, the procedure of solder paste evaluation is illustrated. In the lead-free process, the flux and solder alloy play important roles in the effectiveness of electrical resistance and the strength of the solder joints. Test items include wettability, spread, solder balls, slump, tackiness, viscosity, copper minor, silver chromate, assembly test and reliability tests. This study demonstrates the use of measuring tools combined with statistical methods to investi-

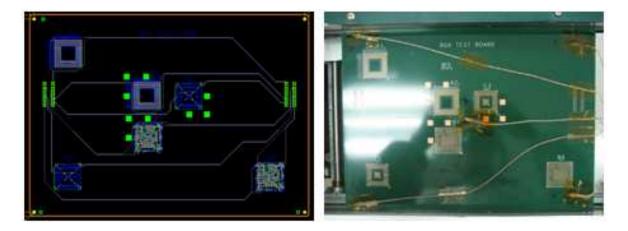

gate the effects of the laser cutting taper angle and speed on the stencil quality for the fine pitch solder paste printing process. The stencil quality is defined by the amount of stainless steel residue after laser cutting and the roundness of the stencil aperture for a circular aperture design. The solder paste inspection data is analyzed to investigate the influences of electropolishing and the stencil area ratio on the transfer ratio during solder paste deposition. The aim of this study is to determine the optimal parameters for stencil fabrication and the corresponding performance in solder paste deposition. The temperature profiles on the critical locations of the PCB during reflow soldering are also important to achieve the desired solder joint quality. This study establishes a procedure to predict the temperature profile based on given information about the PCB design and component loading. Critical factors, such as the conveyor speed and temperature settings of adjacent zones, that can influence the heating process are identified and investigated. A regression model and artificial neural network are constructed to more accurately predict the temperature profile. Results of this study will help improve the efficiency of the temperature setting process, especially in the pilot run stage. Finally, the analytical techniques used for soldering properties, including visual inspection, side-view microscopy, x-ray inspection and dye staining analysis, are also discussed. The crack size and percentage are classified according to the crack area. In this study, the solderability analysis is carried out to determine whether any cracks in the solder joints occur in the CPU and RAM of the ball grid arrays (BGAs) components. It may cause the failure symptom of no display to appear on an ultrabook while the power is on.

# 2. Stencil evaluation of ultra-fine pitch solder paste printing process

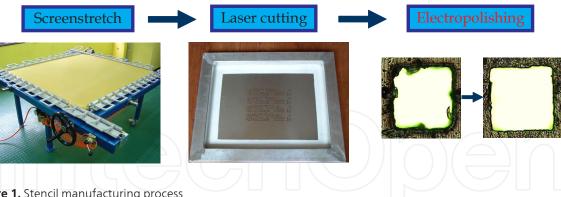

The surface mount technology (SMT) is commonly used in electronics industry to assemble the components onto the PCB. It (SMT) enables the production with relatively low cost. Stencil printing is known to significantly influence the process quality in Surface Mount Technology (SMT). For ultra-fine pitch applications, solder paste printing acts as one of the most critical steps in the SMT assembly process. A review of the literature indicates that solder paste printing is responsible for around 60% of the total process defects. One of the key factors for the performance of solder paste deposition is the stencil fabrication quality. Other important factors include the stencil aperture design, paste printing parameters and stainless steel raw material. The incoming inspection of the stencil typically includes a frame appearance examination and tension force measurement. Inspection of individual apertures under a microscope is not feasible due to the large size of the stencil. Related research also shows that stencil aperture and wall roughness impact the solder paste deposition quality. Laser cutting is widely used due to its advantageous performance with respect to cost and aperture quality. While electroformed stencils are typically considered for the assembly of 01005 passives, evaluations of the laser cut stencil manufacturing process through solder paste printing optimization are lacking. The stencil manufacturing process generally includes three stages, namely, screen stretching, laser cutting and electropolishing/deburring (Fig. 1).

Figure 1. Stencil manufacturing process

Measuring tools combined with statistical methods were used to investigate the effects of the laser cutting taper angle and speed on the stencil quality. The stencil quality is defined by the amount of stainless steel residue after laser cutting and the roundness of the stencil aperture for a circular aperture design. The solder paste inspection data was analyzed to investigate the influence of electropolishing and stencil area ratio on the transfer ratio during solder paste deposition. Weighted ranking was adopted to indicate the variation in solder paste deposits for 01005 and 0.4/0.3mm pitch CSP pads due to the stencil fabrication process. The aim was to determine the optimal parameters for stencil fabrication and corresponding performance in solder paste deposition.

The laser machine and materials used for stencil aperture cutting and stencil materials were evaluated. Experiments included: (1) material properties assessment – to test the durability of the screen; (2) stencil quality inspection - to evaluate the occurrence of clogging, aperture roundness and taper angle; (3) electropolishing process inspection – to determine the optimal process parameters for laser cutting for various taper angles; and (4) printing process assessment – to evaluate the stencil printing performance for 01005/0201 RLC and 0.4/0.3mm pitch CSP applications.

# 2.1. Experiments

# 2.1.1. Material properties assessment

The durability of various raw materials against IPA cleaning solvent was evaluated. The test samples were 736 mm square and 0.1 mm thick. The stencils (without aperture) were cleaned by the cleaning machine. After cleaning for 90 min, the samples were dried for 10 min. As the cleaning time is 10 min in the process currently in use, 90 min of cleaning was equivalent to 9 times the cleaning cycle. The criteria for acceptance were readings above -0.22 mm at the stencil center and above -0.22 mm on the other locations.

# 2.1.2. Stencil quality inspection

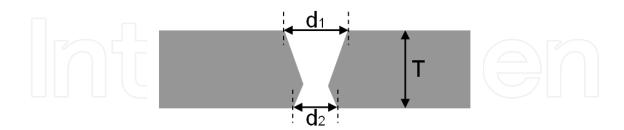

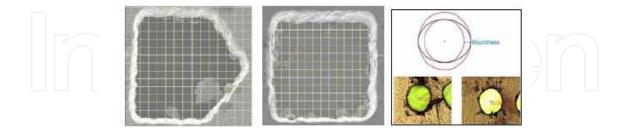

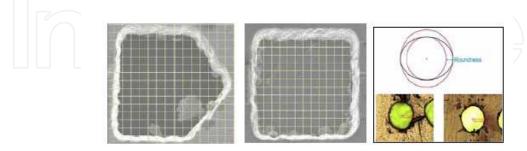

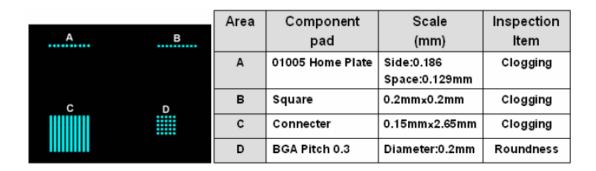

The two-factor three-level full factorial experimental design was used. The factors considered were taper angle and laser cutting speed. Details of the experimental design are shown in Table 1. The taper angle (Fig. 2.) was determined by Equation (1). Quality characteristics included the occurrence of clogging and aperture roundness, as in Fig. 3. Clogging was defined as the percentage of aperture area covered by the steel scrap, while roundness was determined by image measurement software. The stencil aperture design is shown in Fig. 4.

Figure 2. Taper angle

$$\alpha = \tan^{-1}((d1-d2)/2*T)$$

(1)

The d1 and d2 are the aperture sizes at the entrance side and exit side, respectively; T is the stencil thickness.

| Factors      |    | Levels |    |

|--------------|----|--------|----|

| Taper Angle  | 2° | 4°     | 7° |

| Speed (mm/s) | 12 | 10     | 8  |

Table 1. Laser cutting experimental design

# 2.1.3. *Electropolishing process*

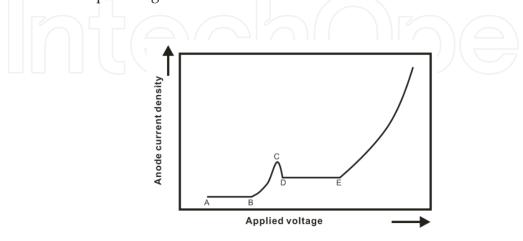

The anodic polarization chart (Fig. 5) shows the relationship between the applied voltage and the anode current density. When the voltage reached the polishing region (DE), further

| Factors      |    | Levels |    |

|--------------|----|--------|----|

| Taper Angle  | 2° | 4°     | 7° |

| Speed (mm/s) | 12 | 10     | 8  |

Figure 3. Clogging and aperture roundness

Figure 4. Stencil design for stencil cutting evaluation

increases in voltage did not have a significant effect. The stencil aperture logging scenario considered three polishing times.

Figure 5. Anodic polarization chart

### 2.1.4. Printing process assessment

Three stencil thicknesses (0.08mm, 0.1mm, 0.12mm), three post treatment methods (CP: chemical polishing, EP: electropolishing, NP: no polishing) and three taper angles (2°, 4°, 7°) were considered. Details of the experimental design are shown in Table 2. Ten stencils in total were used for the printing experiments. The squeegee printing angle remained at 60°. Stencils were cleaned after every printing. The separation velocity was 0.5 mm/sec, the printing pressure was 12 Kg and the printing velocity was 40 mm/sec. The sample size was forty, i.e., there were forty identical apertures on the stencil for each treatment. The printing was duplicated 15 times. The transfer ratio of printing was used as quality performance.

| Stencil<br>thickness | 0.08 |           |    |    |    | 0.1 |    |    |             |    |

|----------------------|------|-----------|----|----|----|-----|----|----|-------------|----|

| Machine              |      | Machine A |    |    |    |     |    |    | Machin<br>B |    |

| Taper<br>Angle       | 2°   | 4°        | 7° | 4° | 2° | 4°  | 7° | 4° | 4°          | 4° |

| Polishing            | EP   | EP        | EP | CP | EP | EP  | EP | CP | NP          | NP |

| Stencil ID           | A    | В         | С  | D  | Е  | F   | G  | Н  | I           | J  |

Table 2. Experimental design for printing performance evaluation

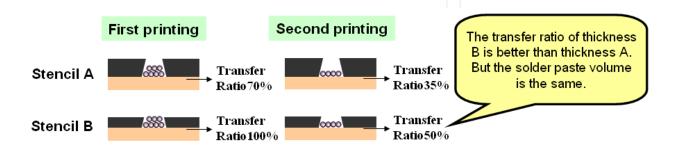

The test board was a bare board without a solder mask in order to minimize the potential printing variation. It is not reasonable to compare the transfer ratio when evaluating the printing performance of stencils with different thicknesses. While the amount of solder paste printed is a major factor influencing the solder joint reliability, a thick stencil with a smaller transfer ratio may still have a greater amount of solder paste deposition. Therefore, a 0.1 mm stencil was used as the standard thickness (Fig. 6). The printing performance was normalized and evaluated through the steps below.

The equation used to calculate the transfer ratio is shown below:

$$volume transfer ratio = \frac{solder paste volume}{stencil thickness*aperture area}$$

(2)

After ten printings, the average and standard deviation are calculated.

The stencil with the highest average printing volume is assigned a score of 10, and the second highest is assigned a score of 9....

The performance of printing variation is considered for an extra score. The top three stencils with the least printing variation (standard deviation) are assigned a score of 3, 2, 1, respectively. The results of printing for a 0.3 mm BGA are shown below.

| Stencil            | F  | Ι  | D | A | C | J | Н | Е | G | В |

|--------------------|----|----|---|---|---|---|---|---|---|---|

| Mean               | 10 | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

| Standard deviation |    | 3  |   |   |   | 1 |   |   | 2 |   |

| Total              | 10 | 12 | 8 | 7 | 6 | 6 | 4 | 3 | 4 | 1 |

Table 3. The results of printing for a 0.3 mm BGA

**Figure 6.** Plot showing difference in transfer ratio for various stencil thicknesses even with similar solder volume deposition

### 2.2. Results

# 2.2.1. Material properties assessment

After a total of 30 hours IPA cleaning (180 cleaning cycles), separation occurred to one of screen model. It showed that the test method can be an effective evaluation of the durability of raw materials.

# 2.2.2. Stencil quality inspection

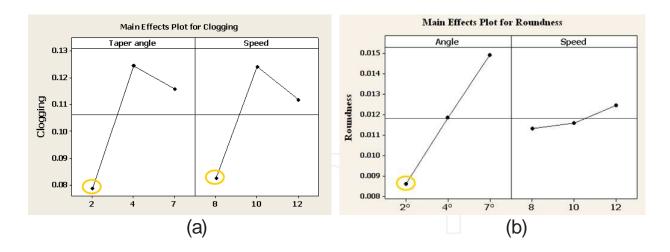

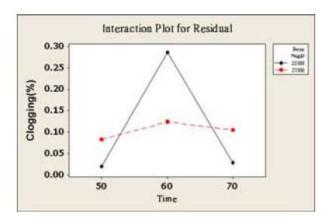

Results show that a taper angle of 2° and a laser speed of 8 mm/s resulted in minimal stencil aperture clogging (Fig. 7(a)). A slower laser speed was preferred for better aperture roundness (Fig. 7(b)).

# 2.2.3. Electropolishing process

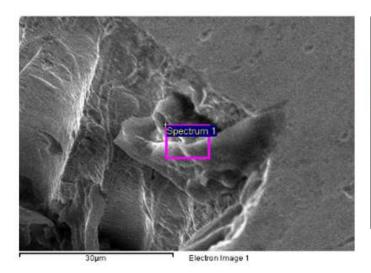

Results showed that clogging was minimized by increasing the polishing time (Fig. 8). The residue was found to be carbon and oxide through scanning electron microscope/energy dispersive X-ray spectroscopy (SEM/EDS) analysis (Fig. 9). Therefore, the electropolishing process did not seem to be effective in removing the non-metal contamination and improving solder deposition. Also, chloride was detected and this may have introduced additional concerns.

Figure 7. Main effects of taper angle and laser speed on (a) clogging and (b) aperture roundness

Figure 8. Main effect of polishing time on aperture clogging

| Element | Weight% | Atomic% |

|---------|---------|---------|

| СК      | 52.48   | 62.64   |

| ок      | 37.08   | 33.22   |

| Na K    | 2.79    | 1.74    |

| CI K    | 2.94    | 1.19    |

| Fe K    | 4.72    | 1.21    |

| Totals  | 100.00  |         |

Figure 9. Residue compound SEM/EDS analysis

# 2.2.4. Printing process assessment

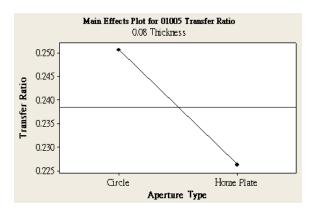

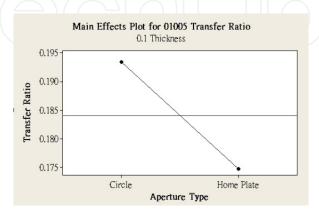

The effect of the stencil aperture shape was evaluated. For both 0.08 mm and 0.1 mm stencils, the circular aperture design was superior to the home plate shape aperture design for 01005 solder paste printing with respect to the transfer ratio (Figs. 10 and 11). For the 0.08 mm stencil, a chemical polished stencil was superior to an electropolished stencil. However, for the 0.1 mm stencil, the electropolished stencil and the stencil with no polishing performed better than the chemical polished stencil. This result was consistent with SEM/EDS analysis in that post treatment did not remove steel scraps and improve solder deposition.

The solder paste transfer ratio scores for various components are shown in Table 4. The transfer ratio for the 0201, 0.5mm BGA and 0.4mm connector were all above 100%. The stencil performance was evaluated for miniaturization applications. The components with a transfer ratio above 100% were excluded. The top three scenarios with the highest scores were (1) the electropolished stencil with a 0.1 mm thickness and a 40° taper angle; (2) the stencil with no polishing, 0.1 mm thick and a 2° taper angle; and (3) the stencil with no polishing stencil, 0.12 mm thick and a 2° taper angle.

Figure 10. Influence of aperture shape on transfer ratio for stencil with thickness 0.08 mm

Figure 11. Influence of aperture shape on transfer ratio with thickness 0.1 mm

Also, the 0.1 mm stencil performed better than the 0.08 mm stencil with respect to the transfer ratio. The stencil with no polishing performed better than the electropolished or chemical polished stencils.

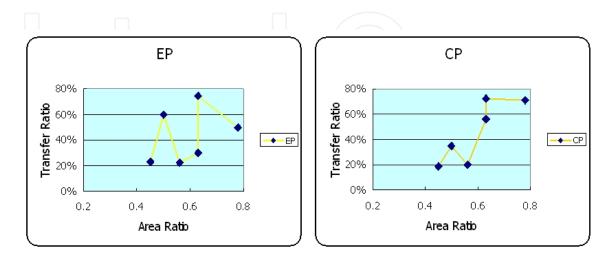

The correlations between the transfer ratio and area ratio were investigated for the stencils with three different post treatment technologies (Figs. 12 and 13). No correlation was found for either the electropolished or chemical polished stencils. The process variation of laser machine A was more severe than that of machine B. While the industry standard IPC-7525 (IPC-7525 3.2.1.1, 2000) suggests an area ratio above 0.66, stencils with an area ratio of 0.5 still achieved a 60% transfer ratio for machine B. Also, as regards stencil manufacturing, stencils with no polishing performed better than stencils that were either electropolished or chemical polished. Significant variations in the stencil manufacturing machine were observed, which may have affected the effectiveness of the stencil evaluation. The area ratio could be used to verify the process variations of stencil manufacturing in future stencil quality assessment studies. The development of printing capability contributes to the miniaturization of electronic products with greater functionality.

| Stencil ID | F    | I    | J  | G  | Α    | Ε  | D  | С   | Н    | В |

|------------|------|------|----|----|------|----|----|-----|------|---|

| 01005      | 12.5 | 10.5 | 9  | 4  | 8    | 3  | 6  | 5   | 1    | 2 |

| BGA0.4     | 10   | 10   | 10 | 6  | 4    | 3  | 5  | 4   | 8    | 1 |

| BGA0.3     | 10   | 12   | 6  | 4  | 7    | 3  | 8  | 6   | 4    | 1 |

| CN 0.3P    | 9    | 11   | 10 | 6  | 4.5  | 7  | 4  | 5.5 | 3    | 1 |

| CN 0.3V    | 10   | 6    | 8  | 10 | 5    | 11 | 2  | 3.5 | 3.5  | 1 |

| Total      | 51.5 | 49.5 | 43 | 30 | 28.5 | 27 | 25 | 24  | 19.5 | 6 |

Table 4. Solder paste transfer ratio score for various components

Figure 12. Correlation between the transfer ratio and area ratio for laser machine A

Figure 13. Correlation between the transfer ratio and area ratio for laser machine B

# 3. Characterization of reflow temperature profile

During reflow soldering, the solder paste melts and solidifies to form reliable solder joints. In the reflow soldering process, the PCBs are transported by the conveyor and go through the various heating zones. Prior to mass production, the process engineer has to ensure that the desired temperature is achieved by using a profile board with the same characteristics as the real product to be assembled. This is critical to ensure that the desired solder joint is formed, while at the same time taking into consideration the heat resistibility of the PCB and the electronic components. The trial and error approach is commonly used, which involves adjusting the temperature setups at various heating zones and the conveyor speed to achieve the temperature profiles on important locations of the PCB so that all comply with the process specifications [Su 1997]. The process to determine the appropriate temperature setups is time consuming as it includes the time to measure the PCB temperature, time for the thermal tracker to cool down to room temperature and the time for the reflow chamber to reach a stabilized temperature. Therefore, the schedule for production could be detained. Characterization of the reflow heating process helps to reduce setup time and the number of trials while ensuring the quality of the solder interconnections.

Temperature simulation using finite difference (FD) and computational fluid dynamics (CFD) modeling tools can achieve a high degree of accuracy, but they are complex to generate and analysis times are unacceptably long. Whalley (2004) developed a less complex approach using simplified representations of both the product and the process. Sarva and Conway (1998) abandoned mathematical modeling and utilized the concept of What-If to forecast temperature profiles. This approach, however, is appropriate primarily at the phase of product design and process planning. Su (1997) proposed a knowledge-based approach to design and implement a profile identification decision support system. Inferences through an expert system usually apply only to certain categories of products. Gao (2008) offered a convenient method to develop an oven recipe for a specific soldering profile. The method was devised to quickly achieve the

proper profile shape, but the accuracy of the profiling was constrained, especially for complicated products in real applications.

Our research considered real PCBs of server applications, usually having six to eight copper layers, but sometimes up to a total of eighteen layers, which are loaded with complicated components with a large heat capacity. The algorithm suggested by Gao (2008) was used in this study as a baseline model for prediction. Data (real temperature setups) of a total of twelve server models collected from production environments were then employed to make the needed modifications to the baseline model. A 'correction value' for the baseline model was the 'response', and the temperature setting of the heating zone, conveyor speed and the total PCBA heat capacity were the independent variables. Stepwise regression analysis (SRA) was used to effectively express the relationship between the response variable and the independent variables (for each heating zone).

# 3.1. Preliminary experiments

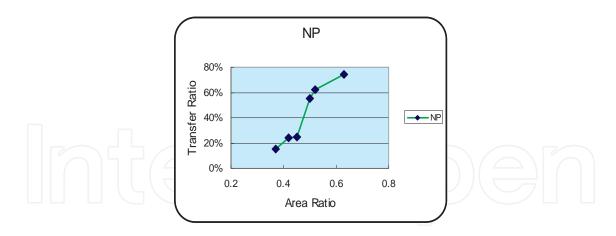

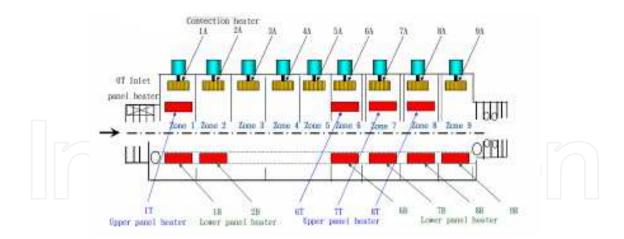

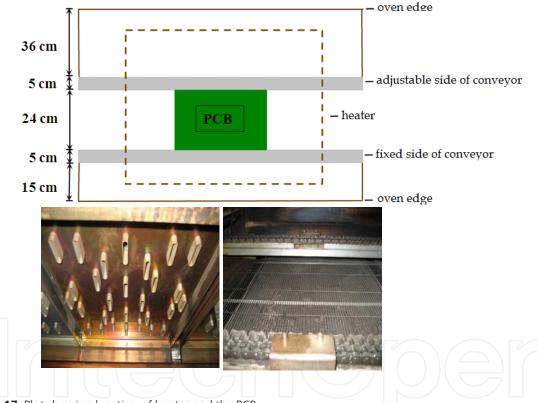

Preliminary experiments were conducted to assess the stability of the reflow oven under study and the influence of the heating zone setup on the resulting temperature profile. The effect of the PCB carrier was also considered. The three preliminary experiments considered a total of five heating zone setups (Table 5). The oven used in these experiments had nine heating zones and natural cooling (Fig. 14). The test vehicle was a bare board with eight stacking layers (Fig. 15). The length, width and thickness were 241 mm, 335 mm and 1 mm, respectively. The thickness of the copper layers on the PCB surface was 0.5 oz, and 1 oz for the inner layers. Six thermal couples were attached at four corners on the top side and center locations of both the top and bottom sides. The fixture used in this study is shown in Fig. 16.

| Heati                          | ng zone          | Z1  | <b>Z</b> 2 | Z3  | Z4  | <b>Z</b> 5 | Z6  | <b>Z</b> 7 | Z8  | Z9  |

|--------------------------------|------------------|-----|------------|-----|-----|------------|-----|------------|-----|-----|

| The 1st preliminary experiment |                  |     | 180        | 180 | 180 | 180        | 180 | 180        | 180 | 180 |

| The 2nd prelim                 | inary experiment | 180 | 180        | 180 | 200 | 200        | 200 | 180        | 180 | 180 |

| The 3rd                        | Temp setting (1) | 180 | 180        | 180 | 180 | 200        | 200 | 240        | 240 | 240 |

| preliminary Temp setting (2)   |                  | 180 | 180        | 180 | 180 | 200        | 200 | 250        | 245 | 240 |

| experiment                     | Temp setting (3) | 180 | 180        | 180 | 180 | 200        | 200 | 260        | 240 | 220 |

Table 5. Heating zone setups considered in the preliminary experiments

In the first experiment, the temperature setting for all heating zones was maintained at  $180^{\circ}$ C. The measured preheating and cooling temperature slopes for the PCB samples with a carrier were smaller than those for PCB samples without a carrier. The peak temperature ( $T_p$ ) during the reflow zone for the PCB samples with a carrier was also lower than that for PCB samples without a carrier and with less variation ( $\Delta T$ ). The above mentioned observations showed the inconsistency in heating phenomena due to the carrier's heat capacity. Secondly, the measured

Figure 14. Reflow oven used in the preliminary experiments

Figure 15. PCB used in the preliminary experiments

Figure 16. Fixture used in this study

temperatures near the adjustable side of the conveyor were higher than those near the fixed side of the conveyor. This was because the adjustable side of the conveyor was close to the center of the heater and the heating source was more stable and effective (Fig. 17). In the second experiment, the temperature setting at  $Z4\sim Z6$  was  $200^{\circ}C$  and all the other zones maintained at

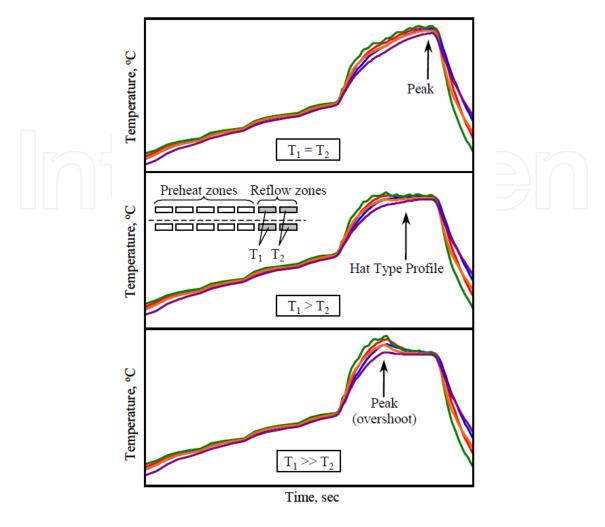

180°C. The results showed that the PCB temperature also increased by approximately 20°C when the temperature setting at the heating zone increased by 20°C. This indicated that the heating zone was stabilized and that the heat transfer was effective. The third experiment, in reference to Cho (2008) (Fig. 18), considered three temperature settings: (1) reflow heating zones Z7-Z9 maintained at 240°C; (2) reflow zone Z7 at 250°C and the remaining zones (Z8 and Z9) decreasing 5°C progressively; and (3) reflow zone Z7 at 260°C and the remaining zones decreasing 20°C progressively. The purpose was to investigate the effect of the temperature setting at the reflow zones on the reflow time (time above 217°C) and the peak temperature. Temperature setting (2) resulted in a higher reflow peak temperature, a longer reflow time and the least variation in peak temperature for the various PCB locations (Table 6), i.e., the reflow temperature setting decreasing 5°C progressively resulted in the desired stable (hat type) temperature profile.

Figure 17. Plot showing location of heater and the PCB

# 3.2. Reflow process specification

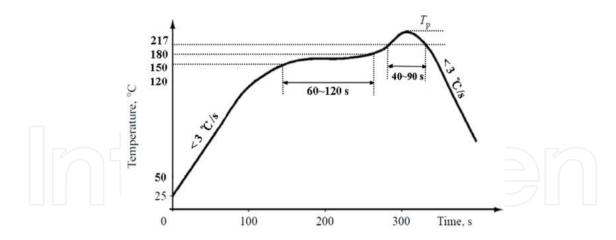

The specifications used in this study are shown in Fig. 19 and described below: (1) the temperature slope increase from 50°C to 120°C during the preheat stage should be less than 3°C/s to prevent damaging the PCB/component due to thermal shock; (2) a slow temperature rise at the soak stage reduces temperature variation across the PCB before the reflow soldering commences. A temperature rise from 150°C to 180°C should be within 60s to 120s; (3) the time above soldering material SAC305's melting point 217°C should be within 40s to 90s; and (4)

Figure 18. Temperature setting at reflow zone from Cho (2008)

|                 | Temper<br>setting  |                 | Tempe<br>settin    |                 | Temperature<br>setting (3) |                 |  |

|-----------------|--------------------|-----------------|--------------------|-----------------|----------------------------|-----------------|--|

|                 | without<br>carrier | with<br>carrier | without<br>carrier | with<br>carrier | without<br>carrier         | with<br>carrier |  |

| Average Tp(℃)   | 227                | 222             | 230                | 224             | 228                        | 220             |  |

| Reflow time (s) | 60                 | 41              | 71                 | 52              | 68                         | 44              |  |

| ∆T(°C)          | 6.3                | 7.8             | 5.7                | 6               | 6.5                        | 10.4            |  |

**Table 6.** Results of the third experiment

rapid cooling is preferred to achieve the desired solder joint metallurgy. The temperature slope from 210°C to 170°C should not exceed 3°C/s to reduce thermal shock.

Figure 19. Reflow temperature profile process specifications

# 3.3. Basic model suggested temperature settings

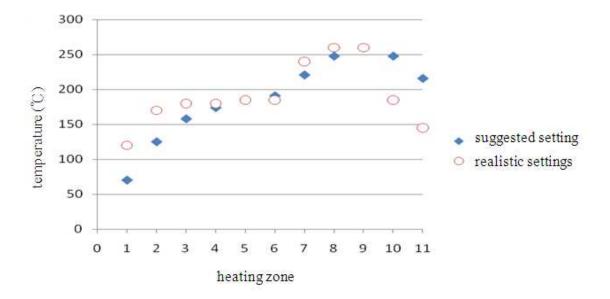

This study started with calculations of the suggested temperature settings based on the reflow profile prediction algorithm proposed by Gao (2008). The results were compared with the real temperature settings in the manufacturing process so that the measured PCB temperature complied with the process specifications. The result of a sample product is shown in Table 7. This task was then duplicated for a total of twelve server products.

| heating zone    | ZI  | <b>Z</b> 2 | <b>Z</b> 3 | Z4  | <b>Z</b> 5 | <b>Z</b> 6 | <b>Z</b> 7 | Z8  | <b>Z</b> 9 | Z10 | Z11 |

|-----------------|-----|------------|------------|-----|------------|------------|------------|-----|------------|-----|-----|

| basic algorithm | 70  | 125        | 158        | 174 | 185        | 191        | 221        | 248 | 260        | 248 | 216 |

| real settings   | 120 | 170        | 180        | 180 | 185        | 185        | 240        | 260 | 260        | 185 | 145 |

| difference      | 50  | 45         | 22         | 6   | 0          | -6         | 19         | 12  | 0          | -63 | -71 |

Table 7. Basic algorithm suggested temperature settings versus real settings

# 3.4. Constructing the function of the correction value through stepwise regression analysis

The temperature settings of twelve server products used in real manufacturing environments were collected. It is noted that the settings were determined by experienced process engineers through trial and error. This was time consuming and iterative modification efforts were required to ensure that the temperatures at critical locations of the PCB were within process specifications. This was essential before the mass-production commenced. Table 7 and Fig. 20 show the basic algorithm suggested temperature settings compared to the real settings. Real temperature settings exhibited longer soak times (in a temperature range of 150°C~180°C) and reflow times (above 217°C). Apparently, PCBs with a higher layer count and loaded with complicated electronic components were more suitable. In contrast, the basic model was only appropriate for the experimental bare board and/or low-end products. Therefore, the aim of

this study was to determine the 'correction value' used to modify the suggested settings proposed by the basic algorithm and feasible for high-end products, such as a high-layer count server.

Figure 20. Basic algorithm suggested temperature settings compared to the real settings

The correction value is considered as a function, f(x), of the product and process-related factors, namely, the total PCB assembly's (PCBA's) heat capacity,  $H_{total}(m)$ ; the temperature setting at zone i,  $x_1$ ; the temperature setting at the previous zone (zone i-1),  $x_2$ ; the temperature setting at the following zone (zone i+1),  $x_3$ ; and the conveyor speed,  $x_4$ . The PCBA consisted of FR4 (flame retardant-4) material, copper layer and components. The total PCBA heat capacity (J/k) is the product of the materials' mass (g) and corresponding specific heat capacities (J/g-k) (Equation 3). In this study, the mass of PCBA was measured with a digital balance. While CAD Gerber file provided information on the total volume of copper, the mass of copper was determined by multiplying the copper density (1.9 g/cm3). The components mass could thus be determined by deducting the mass of PCBA by the masses of copper and components.

$$H_{total}(m) = m_1 c_1 + m_2 c_2 + m_3 c_3 \tag{3}$$

where m1, m2 and m3 are the masses of FR4, copper and components of a given product;  $c_1$ ,  $c_2$  and  $c_3$  are 0.6 J/g-k, 0.38 J/g-k and 0.1 J/g-k, respectively, which are the specific heat capacities of FR4, copper and components, respectively.

The function of the correction value was constructed through the data of eleven server products. Data of the other server product was then used for model verification. SRA integrates the forward regression and the backward regression. First, the forward regression brings in the item with the most prediction ability; the backward regression then removes the item(s) that are not significant (expected explanation ability) from the model. The test criteria, partial

F value and type I error,  $\alpha$ , used in this study were 4 and 0.15, respectively. The cross validation continued until all the items in the complete function were tested. Statistics software Minitab was used to analyze data of the eleven server products and construct the correction value function for each heating zone. The tenth heating zone, Z10, was used for illustration (Table 8). The complete function included first power items, second power items and two way interaction items (Equation 4). The twenty items were tested for their significance, and the results showed that only item  $x_1^2$  was brought into the function model.

$$f(x) = \beta_0 + \beta_1 g(m) + \beta_2 X_1 + \beta_3 X_2 + \beta_4 X_3 + \beta_5 X_4 + \beta_6 H(m)^2 + \beta_7 X_1^2 + \beta_8 X_2^2 + \beta_9 X_3^2 + \beta_{10} X_4^2 + \beta_{11} H(m) X_1 + \beta_{12} H(m) X_2 + \beta_{13} H(m) X_3 + \beta_{14} H(m) X_4 + \beta_{15} X_1 X_2 + \beta_{17} X_2 X_3 + \beta_{19} X_2 X_4 + \beta_{20} X_3 X_4$$

$$(4)$$

| 1 .     | difference | total heat capacity | Z10 set temp | Z9 set temp | Z11 set temp | conveyor speed |

|---------|------------|---------------------|--------------|-------------|--------------|----------------|

| product | (°C)       | (J / k)             | (°C)         | (℃)         | (°C)         | (cm/min)       |

| 1       | 0          | 286.20              | 260          | 260         | 180          | 80             |

| 2       | -13        | 485.54              | 240          | 265         | 160          | 75             |

| 3       | -21        | 411.48              | 240          | 275         | 160          | 75             |

| 4       | 16         | 386.06              | 265          | 270         | 180          | 82             |

| 5       | -7         | 401.34              | 250          | 270         | 180          | 75             |

| 6       | -3         | 242.58              | 250          | 260         | 180          | 87             |

| 7       | -2         | 316.65              | 250          | 260         | 150          | 70             |

| 8       | 0          | 191.45              | 260          | 255         | 180          | 80             |

| 9       | -63        | 864.21              | 185          | 260         | 145          | 68             |

| 10      | -62        | 403.69              | 190          | 265         | 145          | 80             |

| 11      | 11         | 219.52              | 260          | 260         | 180          | 73             |

Table 8. Data to construct correction value function for Z10

The correction value functions for all heating zones determined by SRA are shown in Table 9. Firstly, the setting at Z1 was at  $120^{\circ}\text{C}$  for an efficient temperature rise and to prevent thermal shock to the PCBA during the preheat stage. The setting at Z9 was in the range of  $260^{\circ}\text{C}\sim275^{\circ}\text{C}$  for the desired wetting performance and to limit the exposure of the PCBA in the elevated temperature environment during the reflow stage. Secondly, the effectiveness of the regression functions were determined by the index of model explanation ability, R-sq(adj), and model prediction ability index, R-sq(pred). The R-sq(pred) of the prediction function for the Z11 temperature setting was only 13%, and thus considered an invalid model. For heating zones Z4-Z8, no item was brought into the function with  $\alpha$  equal to 0.15. On the other hand, prediction functions for the Z2, Z3 and Z10 temperature settings were valid. Both prediction functions

for Z2 and Z3 included the interaction item of 'total heat capacity', H<sub>total</sub>(m), and 'temperature setting'. The reason for this was as follows. Z2 and Z3 corresponded to the preheat stage of the temperature profile. PCBA at this stage had a significant heat absorption which resulted in a rapid rise in temperature. The efficiency of the heat absorption and the rise in temperature depended on the heat capacity of the PCBA; therefore, the interaction item (between 'heat capacity' and 'temperature setting') appeared as a critical item. Also, the prediction function for Z10 included only the 'temperature setting', x<sub>1</sub>. This was because Z9-Z11 corresponded to the reflow stage of the temperature profile. The purpose of Z10 was not to raise the PCBA temperature, but to extend the reflow time duration to ensure the complete wetting of the soldering material onto the bonding pads. The PCBA's heat absorption and rise in temperature were slow; therefore, 'total heat capacity' did not play a critical role in the prediction function. Another server product was used for the verification test. The PCB temperatures were measured with the settings suggested by the baseline model and the SRA model (Table 10). The resulting temperature profiles were then compared to the process specifications. As shown in Table 11 and Fig. 21, the temperature profile resulting from the settings suggested that the SRA model was close to the target.

| Heating zone | Function model                                                 | R2(adj.) | R <sup>2</sup> (pred.) |

|--------------|----------------------------------------------------------------|----------|------------------------|

| Z1           | temperature setting at 120℃                                    | -        | -                      |

| Z2           | $y = -37.75 + 0.0023H(m)x_1 - 0.00457H(m)x_3 + 0.00739H(m)x_4$ | 96%      | 91%                    |

| Z3           | $y = -27.04 - 0.00235H(m)x_3 + 0.00645H(m)x_4$                 | 78%      | 61%                    |

| Z4~ Z8       | no item brought into the function                              | -        | -                      |

| <b>Z</b> 9   | setting in the range of 260°C~275°C                            | -        | -                      |

| Z10          | $y = -155.7 + 0.00241x_1^2$                                    | 86%      | 77%                    |

| Z11          | invalid model                                                  | 40%      | 13%                    |

Table 9. Correction value functions by SRA

| Heating zone   | Z1    | Z2  | Z3  | Z4  | <b>Z</b> 5 | Z6  | <b>Z</b> 7 | Z8  | <b>Z</b> 9 | Z10 | Z11 |

|----------------|-------|-----|-----|-----|------------|-----|------------|-----|------------|-----|-----|

| baseline model | 92    | 135 | 164 | 182 | 194        | 205 | 230        | 252 | 265        | 252 | 243 |

| SRA model      | (120) | 162 | 167 | 182 | 194        | 205 | 230        | 252 | 265        | 250 | 243 |

| ANN model      | (120) | 180 | 183 | 185 | 187        | 192 | 238        | 250 | 265        | 255 | 245 |

Table 10. PCB temperatures measured with settings suggested by the baseline model and the SRA model

| Temperature<br>profile | Temp rising slope (°C/s) 50°C ~120°C | Soak time<br>(s)<br>150°C ~180°C | Peak<br>temp<br>(°C) | Reflow time (time above 217°C) (sec) | Cooling rate $210^{\circ}\text{C} \sim 170$ $^{\circ}\text{C} (^{\circ}\text{C}/\text{s})$ |

|------------------------|--------------------------------------|----------------------------------|----------------------|--------------------------------------|--------------------------------------------------------------------------------------------|

| spec requirement       | 0~3                                  | 60~120                           | 230~25               | 40~90                                | 0~3                                                                                        |

| baseline model         | 1.38                                 | 40                               | 234                  | 45                                   | 1.06                                                                                       |

| SRA model              | 1.53                                 | 45                               | 235                  | 46                                   | 1.07                                                                                       |

| ANN model              | 1.85                                 | 72                               | 240                  | 62                                   | 1.51                                                                                       |

Table 11. Temperature profiles versus process specs

Figure 21. Temperature profiles versus process specs

# 3.5. Summary

This research characterized the IR-based reflow oven and calculated the desired temperature setting through a baseline algorithm proposed in reference to twelve server samples. Correction values were as suggested by the SRA model. The results of the SRA analysis indicated that the regression functions of heating zones Z2, Z3 and Z10 were valid models with significant prediction ability. Functions of Z2 and Z3 included the item of interaction between 'total heat capacity' and 'temperature setting', while functions of Z10 included only 'temperature setting'. The results of the confirmation tests indicated that the temperature profile resulting from the settings suggested that the SRA model was close to the target.

# 4. Solderability analysis

Solderability analysis is one of the most important characterizations for PCB assembly (PCBA), quality control and reliability (Huang et al., 2009 and 2011). The analytical techniques used for

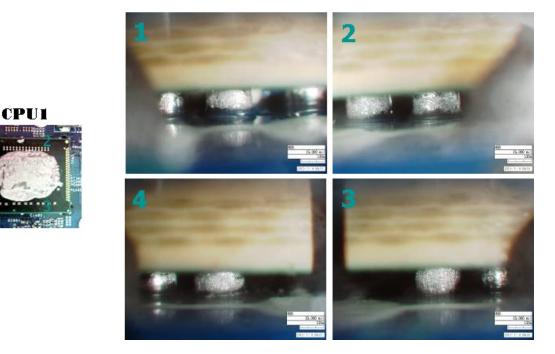

Figure 22. Side-view inspection results from the CPU1 BGA

soldering properties, including visual inspection, side-view microscopy, x-ray inspection and dye staining analysis, were conducted (Huang et al., 2011 and Castello et al., 2006). The crack size percentage was classified according to the crack area. In this case, the solderability analysis was carried out to determine whether any cracks in the solder joints occurred in the CPU and RAM BGAs. The one CPU and eight RAM chips were examined to clarify the suspect ones. It may cause the failure symptom of no display to appear on an ultrabook while the power is on.

# 4.1. Side-view inspection

Side-view is mainly executed to observe the surface mount components, especially the exterior row BGA solder joints in detail, non-destructively, such as foreign matter, solder joint cracks, BGA shift, missing balls and soldering related defects.

However, for an interior analysis or inspection of BGAs or PCBA components, side-view microscopy has blind spots and should be combined with other analysis methods, such as x-ray, dye staining and cross section, for further confirmation and judgment. In this study, from the side view inspection results, no abnormalities were found for the CPU1 and RAM1~8 BGAs. An illustration of the CPU1 inspection results is shown in Fig. 22. The corresponding and complementary analyses were characterized and are presented in the next sections.

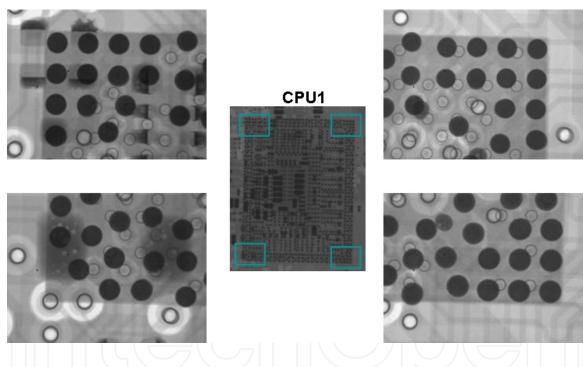

### 4.2. X-ray inspection

X-ray is mainly executed to examine soldering related defects for BGA, CSP and QFN, etc. X-ray inspection is regarded as a non-destructive method and is used when a high proportion of BGA solder joints is hidden under the IC package. As the internal material of BGA package shows different levels of absorbency, x-rays can determine the solder joint related defects, for

example, solder bridges, missing balls, solder voids, insufficient solder or excessive solder volume. The presence and location of solder joint defects under these types of IC package may be determined by conventional 2-D X-ray in a production environment. X-ray inspection has become a common tool for soldering characterization analysis performed to verify product quality (Harrison et al., 2001).

In this study, from the x-ray inspection results, no soldering defects (short, missing balls, etc.) were observed for the CPU1 and RAM1~8 BGAs. An illustration of the CPU1 inspection results is shown in Fig. 23. Voids may exist in the solder joints and make surface mount area arrays risky. According to IPC-A-610E (IPC-A-610E 8.3.12.4, 2010), the acceptance criterion for voids in solder joints is 25% or less voiding of the ball x-ray image area. In this case, void percentages were all within the inspection criterion (<25% ball x-ray image area). While some critical defects in BGA solder joints were not readily detectable by the side-view microscope and/or the x-ray inspections, dye staining analysis was carried out for more accurate soldering analysis.

Figure 23. X-ray inspection results from the CPU1 BGA

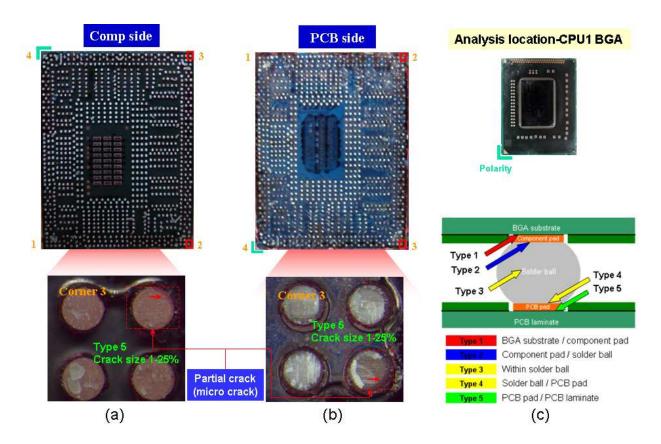

# 4.3. Dye staining analysis

The dye staining analysis is commonly applied to verify whether solder joint cracks have occurred under BGA packages (Liu et al., 2010 and Lau et al., 2004). The dye staining technology, which is a destructive test method used to reveal defects on the solder balls, relies on a liquid dye that penetrates existing micro cracks or under open solder balls. After the dyeing process, a heating process is used to dry the dye followed by prying off the BGA. The presence of the dye on solder balls shows the location of the failure within the solder joint and the degree

of crack propagation. It is a commonplace method applied to grid array soldering problems (Huang et al., 2011).

Since RD can not identify the failure locations, dye staining analysis is performed to determine the possible causes for the no display issue when the ultrabook power is on. If the failure locations can be identified, cross section analysis is suggested to obtain more failure symptom information from other aspects.

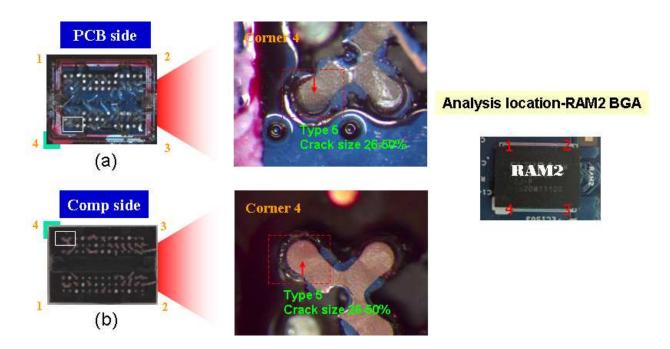

In this study, from the dye staining analysis, solder joint cracks were found in the CPU1 (corners 2 and 3) and RAM2 (corner 4) BGAs (Figs. 24 and 25). For CPU1, the failure mode was located between PCB pad/PCB laminate (Type 5) and the crack size percentage was between 1-25%. For RAM2, the failure mode was also Type 5 and the crack size percentage was 26-50%. Cracks are one of the most important reasons for the failure symptom showing no display for the integrated chips and board in an ultrabook product.

Figure 24. Dye staining analysis results from the CPU1 BGA (a) component and (b) PCB side (corner 3), (c) failure mode

# 4.4. Summary

In this study, visual inspection, side-view microscopy, x-ray inspection and dye staining analysis were successfully used to characterize the soldering quality associated with microelectronics assembly. Side-view microscopy and x-ray inspection were used for a preliminary screening for failure symptoms. Consequently, dye staining analysis was used to identify the

Figure 25. Dye staining analysis results from the RAM2 BGA (a) PCB and (b) component side (corner 4)

failure mode and crack size accurately. This method facilitated determining the failure causes for most soldering problems.

# **Author details**

Chien-Yi Huang<sup>1</sup>, Chen-Liang Ku<sup>2</sup>, Hao-Chun Hsieh<sup>2</sup>, Ming-Shu Li<sup>2</sup>, Chia-Hsien Lee<sup>2</sup> and Cheng-I Chang<sup>2</sup>

- 1 Department of Industrial Engineering and Management, National Taipei University of Technology, Taipei, Taiwan, R.O.C.

- 2 Process Technology Enabling & Materials Characterization Div., Global Operations, Wistron Corporation, Hsinchu, Taiwan, R.O.C.

# References

- [1] Castello, T., Rooney, D. & Shangguan, D. (2006). Failure analysis techniques for leadfree solder joints. Soldering & Surface Mount Technology, Vol. 18, No. 4, pp. 21-27.

- [2] Clark, D. & Rohrer, D. (2003). Specification and qualification of machine vision technology in the SMT process, Technical Paper, GSI Lumonics. pp.1-8.

- [3] Gangue, Z. & Wang, C. (2009). Shape and fatigue life prediction of chip resistor solder joints, *International Conference on Electronic Packaging Technology & High Density Packaging (ICEPT-HDP)*.

- [4] Gao, J.G., Wu, Y. P., Ding H. & Wan, N.H. (2008). Thermal profiling: a reflow process based on the heating factor. *Soldering & Surface Mount Technology*, Vol. 20, No. 4, pp. 20-27.

- [5] Harrison, M.R., Vincent, J.H., Steen, H.A.H. (2001). Lead-free reflow soldering for electronics assembly. *Soldering & Surface Mount Technology*, Vol. 13 Iss: 3, pp. 21–38.

- [6] Huang, C.Y., Li, M.S., Ku, C.L., Hsieh, H.C. & Li, K.C. (2009). Chemical characterization of failures and process materials for microelectronics assembly. *Microelectronics International*, Vol. 26, No. 3, pp. 41-48.

- [7] Huang, C.Y., Li, M.S., Huang, S.Y., Chang, C.I. & Huang, M.H. (2011). *Material Characterization and Failure Analysis for Microelectronics Assembly Processes*. Wide Spectra of Quality Control, InTech publication, ISBN 978-953-307-683-6, Chapter 26, pp. 509-532.

- [8] Huang, C.Y., Lin, C.T., & Tsai, H.L. (2004). Study of Process Capability for The Stencil Printing in PCB Assembly. *Fifth Asia-Pacific Industrial Engineering and Management Systems Conference*, Gold Coast, Australia.

- [9] IPC-7525 3.2.1.1 (2000). Area Ratio/Aspect Ratio, pp. 3.

- [10] IPC-A-610E 8.3.12.4 (2010). Surface Mount Area Array Voids, pp. 8-89.

- [11] Jianbiao, P., Tonkay, G.L., Storer, R.H., Sallade, R.M. & Leandri, D.J. (2004). Critical variables of solder paste stencil printing for micro-BGA and fine-pitch QFP. *IEEE Transactions on Electronics Packaging Manufacturing*, Vol. 27, No. 2.

- [12] Lau, J., Shangguan, D., Castello, T., Horsley, R., Smetana, J., Hoo, N., Dauksher, W., Love, D., Menis, I. & Sullivan, B. (2004). Failure analysis of lead-free solder joints for high-density packages. *Soldering & Surface Mount Technology*, Vol. 16, No. 2, pp. 69-76.

- [13] Liu, F., Meng, G. & Zhao, M. (2010). Experimental investigation on the failure of lead-free solder joints under drop impact. *Soldering & Surface Mount Technology*, Vol. 22, No. 3, pp. 36-41.

- [14] Rumelhart, D.E. & McClelland, J.L. (1986). *Parallel Distributed Processing: Explorations in the Micro-structure of Cognition*. Cambridge: MIT Press, Vol. 1.

- [15] Sarvar, F. & Conway, P.P. (1998). A modeling tool for the thermal optimization of the reflow soldering of printed circuit assemblies. *Finite Elements in Analysis and Design*, Vol. 30, pp. 47-63

- [16] Su, Y.Y., Srihari, K. & Emerson, C.R. (1997). A profile identification system for surface mount printed circuit board assembly. *Computers and Industrial Engineering*, Vol. 33, pp.377-380.

- [17] Tsai, T.N. (2008). Modeling and optimization of stencil printing operations A comparison study. *Computers & Industrial Engineering*, Vol. 54, pp. 374–389.

- [18] Whalley, D.C. (2004). A simplified reflow soldering process model. *Journal of Materials Processing Technology*, Vol. 150, pp. 134-144.

- [19] Yeh, I.C. (2009). Taguchi method based on neural networks and cross validation methodology. *Journal of Quality*, Vol. 14, No. 4.