# we are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

122,000

135M

Our authors are among the

TOP 1%

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

# Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

# All-Optical Quaternary Logic Based Information Processing: Challenges and Opportunities

Jitendra Nath Roy and Tanay Chattopadhyay

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/51559

# 1. Introduction:

Science and Technology is providing people all over the world with much better ways of communicating than ever before, and the winds of change have whipped up the desire to exchange more of everything from messages to movies. The field of computation and signal processing is growing day by day [1-7]. In last three to four decades, the philosophy, science and technical prospects enriched the scientific communities a lot. Massive parallelism, speed of operation, increased spatial density attracts in many ways the scientists, researchers and technologists. Very Large Scale Integration (VLSI) technology has revolutionized the electronics industry and established the 20th century as the computer age. But, VLSI technology is approaching its fundamental limits in the sub-micron miniaturization process. Therefore an alternative technological solution to the problem of high speed information processing is needed, and unless we gear our thoughts toward a totally different pathway, we will not be able to further improve our information processing performance for the future. Conservative and reversible logic gates are widely known to be compatible with revolutionary computing paradigms. At the same time the Multi-valued logic (MVL) is also positioned as a coming generation technology that can execute arithmetic functions faster and with less interconnect than binary logic [8-48].

In order to overcome the electronic bottlenecks and fully exploit the advantages of optics, it is necessary to move towards networks, where the transmitted data will remain exclusively in all optical domains without optical electrical optical (OEO) conversions. Ultra high-speed optical network is developing rapidly as growing capacity demand in telecommunication system is increasing. In these networks, it is desired to carry out switching, routing and processing in optical domain to avoid bottlenecks of optoelectronic conversions. The dream of photonics is to have a completely all-optical technology. All-optical

© 2013 Roy and Chattopadhyay; licensee InTech. This is an open access article distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

switching is an essential technology for transparent fiber optic networks and for all forms of optical signal processing as the optical interconnections and optical integrated circuits is immune to electromagnetic interference, and free from electrical short circuits. In a pursuit to probe into cutting-edge research areas, the development of different ultra-fast alloptical switches has received considerable interest in recent years all over the world for future optical information processing [49-59]. As photon is the ultimate unit of information with unmatched speed and with data package in a signal of zero mass, the techniques of computing with light may provide a way out of the limitations of computational speed and complexity inherent in electronics computing.

The fundamentals of digital signal processing are straightforward. To send something as simple as a phone message or as complicated as a picture, we digitize it by breaking it up into a series of binary bits, transmit the bits, and decode them at the other end to re-create the message or picture. The ones or zeroes in the bits are encoded by turning some signal on or off. In the past, the signal has been electrical, but increasingly it is composed of light pulses. We use a laser to produce the light, and then add information to it with a modulator, transmit it through optical fibers, amplify it if needed, receive it with a photo detector and re-create the message with a demodulator. An optical signal is better than an electrical one, with less attenuation, faster switching, and more signals traveling together. In everyday we have to handle enormous and ever increasing, amounts of information. Binary number (0 and 1) is insufficient in respect to the demand of the coming generation. The application of multi-valued (non-binary) signals can provide a considerable relief in transmission, storage and processing of large amount of information in digital signal processing. Quaternary logic (4-valued) is one type of MVL [60-82].

In this chapter, all-optical scheme for designing some polarization encoded quaternary logic gates (quaternary min and quaternary delta literal) with the help of nonlinear material based interferometric switches have been discussed. Design of all-optical quaternary multivalued multiplexer and demultiplexer circuits have also been described with the help of these basic gates. For the quaternary data processing in optics, the quaternary number (0, 1, 2, 3) have been represented by four discrete polarized state of light. In optical implementation we can consider the set of Quaternary logic states {0, 1, 2, 3} as : 0= No light, 1 = vertically polarized light ( $\uparrow$ ), 2 = horizontally polarized light (•), 3 = partially polarized light  $(\leftrightarrow)$ . This chapter is organized as follows. Section-1.1 to 1.3 gives a brief overview of multivalued logic (MVL) i.e. What is MVL? Why do we need it? How it can be implemented and where MVL can be applied? Section-2.1 describes the basic principle of all-optical interferometric switches which is the cornerstone of all logic based signal processing. Section-2.2 and section 2.3 describes the design and operational principle of some basic all-optical quaternary logic circuits (QMIN, Delta Literal). All-optical circuit for quaternary multiplexer and demultiplexer are described in section-2.4 and section 2.5. Also quaternary T-gate is discussed in section 3. Challenges in design issues that is to be considered for experimentally achieve result from the proposed scheme is mentioned in section section-4. Chapter ends with Conclusions and Future Scopes given in section-5.

All-Optical Quaternary Logic Based Information Processing: Challenges and Opportunities 83 http://dx.doi.org/10.5772/51559

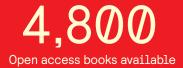

Multi-valued logic (MVL) is a non binary logic with radix >2. Binary logic is limited to only two states 'True' (1) and 'False' (0), MVL replaces these with finite and infinite number of values. MVL system is defined as system operating on higher radix than two. In the base-*R* number system, a numerical value of *N*-bit data $(a_{N-1}a_{N-2} \cdots a_2a_1a_0)_R$ ; [where  $0 \le a \le (R-1)$ ] can be written as [56] :

$$(a_{N-1}.R^{N-1} + a_{N-2}.R^{N-2} + \dots + a_1.R^1 + a_0.R^0) = \sum_{i=0}^{N-1} a_i.R^i$$

(1)

For example Ternary logic (*R*=3) has three logical states {0, 1, 2} or { $\overline{1}$ , 0, 1} [18]. These are known as ordinary ternary and symmetric ternary logic respectively. Quaternary logic (*R* = 4) has four logical states {0, 1, 2, 3}. Like binary world there are also numbers of basic gates in multi-valued logic world. Depending on the radix and number of variables used, different logic functions can be generated. The numbers of possible functions are [37].

$$f(R,n) = R^{\binom{R^n}{2}}$$

(2)

Where  $R = \text{radix}, n = \text{number of variables}$ . In ternary logic of two variable  $(R = 3, n = 2)$  there are  $f(A, 2) = 2^{3^2} = 10(82)$  massible functions. For support  $(R = 4, n = 2)$  there are  $f(A, 2) = 2^{3^2} = 10(82)$  massible functions.

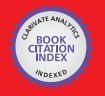

are  $f(3, 2) = 3^{3^2} = 19683$  possible functions. For quaternary (R = 4, n = 2) there are  $f(4, 2) = 4^{4^2} = 4294967296$  logical operations. Hence, huge numbers of logical operation can be possible for higher radix (Fig. 1). Among them, some basic gates are the MAX, MIN, Complement, Cycle or successor, Literals etc [6, 7, 38-41], which is indicated in Fig. 2.

#### 1.2. Why do we need All-optical Quaternary Logic based signal processing?

The most pressing problems in present-day binary systems are interconnection problems, both on-chip and between chip. On chip the difficulties of placement and routing of the digital logic elements which go to make up the complete chip are escalating with increase in capability per chip, and the silicon area used for interconnections may be greater than that used for the active logic elements. Similarly, the difficulties of bringing an increasing number of connections offchip is promoting -a new consideration of packaging concepts in an attempt to overcome problems which are becoming mechanically, thermally, and electrically extreme. All these factors point to the attraction of raising the information content per interconnection from the present lowest-possible (binary) level. Multiple-valued logic, in which the number of discreet logic levels is not confined to two, has been the subject of much research over many years. The practical objective of this work is to increase the information content of the digital signals in a system to a higher value than that provided by binary operation. To increase the transmission capacity of future communication the present binary system is becoming very critical. A more formal approach would be an *n*-valued logic which has *n* different states, each state having a unique identifier. Multi-valued logic (MVL) is defined as a non-binary logic and involves the switching between more than two states. Multi-valued logic can be viewed as an alternative approach to solve many problems in transmission, storage and processing of large amount of information in digital signal processing [22]. The main advantages of multi-valued logic systems and circuits are greater speed of arithmetic operations realization, greater density of memorized information, better usage of transmission paths, decreasing of interconnections complexity and interconnections area, decreasing of pin number of integrated circuits and printed boards, possibilities for easier testing.

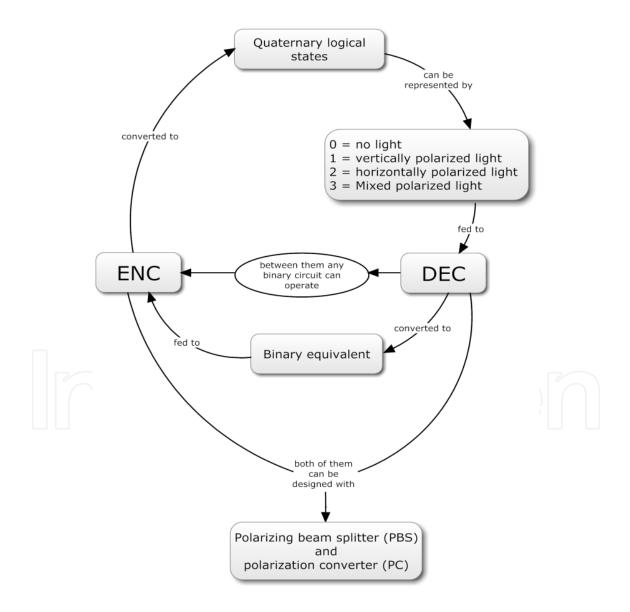

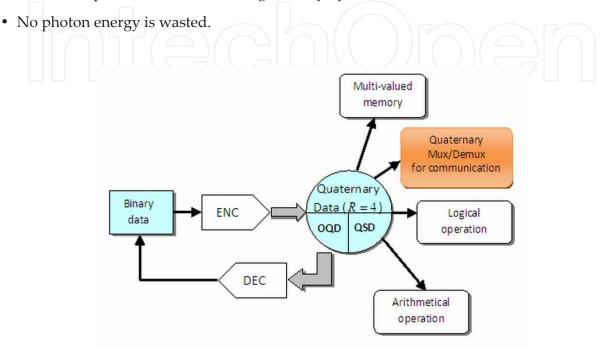

In the field of data communication, the quaternary codes are preferred because four-valued (i.e. quaternary) logic signals easily interface with the binary world. They may be decoded directly into their two binary-digit equivalent. Quaternary logic world can easily be interfaced with binary logic in all-optical domain with the help of our suggested DEC and ENC

schemes [57, 59]. The block diagram of this interfacing circuit is shown in the Fig. 3. Here input & outputs are 4-valued and the internal circuitry is binary (radix=2). Decoder circuit converts quaternary input into its binary equivalent. After performing the logical operation in binary system, it is then encoded to its quaternary equivalent by encoder circuit. Hence, it can be said that this scheme requires no major modifications of the existing transmitter, receiver, or transmission link. Quaternary digits are two major types: ordinary quaternary digit (OQD) and quaternary signed digit (QSD) [75-76]. QSD is useful for carry free arithmetic operations [19, 31-35]. Fig. 4 indicates how quaternary and binary are interfaced.

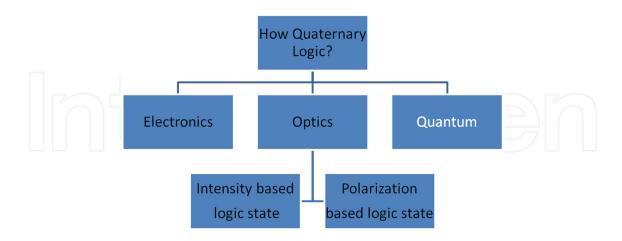

#### 1.3. How All-optical Quaternary Logic can be implemented?

Consideration of different logical states is a challenge. It can be done in different ways and given in Fig. 5. In electronics, efforts have already been made to design four-valued logic

[37-48] with charge couple device (CCD). In I<sup>2</sup>L circuits 0mA, 10mA, 20mA and 30mAg are four different logical states, in  $\nu$ MOS (neuron-MOS) have the logic levels 0.0V, 1.1V, 2.2V and 3.3V [39], also in CMOS MVL have the logic levels 0 V, 1V, 2V, 3V respectively [37]. Quantum computation and information is the study of the information processing tasks that can be accomplished using quantum mechanical systems. Just as the classical computation is built upon bits, quantum computation also has an analogous concept called qubits. Analogous to classical computation, the operations on qubits are carried out using quantum logic gates. Of late, renewed interest in optical computing has been witnessed due to the emergence of novel photonics structures that includes nano-photonics, silicon photonics, biophotonics and plasmonics etc. Optical quaternary logical operation is an interesting and challenging field of research for future optical signal processing where we can expect much innovation [58-82]. Polarization properties of light can play significant role here.

Figure 3. Binary-to-quaternary Encoder and Quaternary-to-binary decoder.

Polarization may be a good choice for representing different logical states in all-optical quaternary (4-valued) logic operations because [7, 15],

- Nature of polarization does not change due to absorption of light like intensity. Therefore the strength or weakness of the beam plays no role in the operation of the devices.

- The sate of polarization can be changed easily by Polarization converter.

Figure 4. Interfacing Binary and Quaternary world by the help of ENC and DEC.

Figure 5. Quaternary (4-valued) logic implementation.

For the quaternary data processing in optics, the quaternary logic states {0, 1, 2, 3} can be represented by four discrete polarized state of light as mentioned below:

0 = No light.

1 = vertically polarized light (1)

2 = horizontally polarized light  $(\bullet)$

3 = mixed polarized light or un-polarized light ( $\leftrightarrow$ ).

# 2. Designing of Polarization encoded all-optical Quaternary multiplexer / De-multiplexer

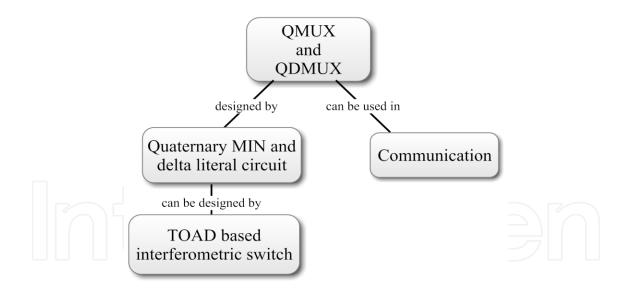

Multiplexing and de-multiplexing are two essential features in almost all the signal communication systems, where a lot of information is being handled without any mutual disturbances. The principles and possibilities of designing of all-optical quaternary multi-valued multiplexer and de-multiplexer circuits are described with the help of quaternary MIN and quaternary delta literal gates (Fig. 6). Nonlinear material based interferometric switches can take an important role here. Working principle of Terahertz Optical Asymmetric Demultiplexer (TOAD) based all-optical switch is discussed in Section-2.1. Section-2.2 and Sec-2.3 describes the design and operational principle of some basic all-optical quaternary logic circuits (QMIN, Delta Literal). All-optical circuit for quaternary multiplexer and demultiplexer are proposed and described in Sec-2.4 and sec-2.5 respectively.

Figure 6. Overview of Quaternary Mux/Demux.

#### 2.1. Interferometer based optical switch:

Interferometric devices for optical processing have been of great interest in the recent years [50-55]. Optical switch using a nonlinear interferometer makes it possible for one optical signal to control and switch another optical signal through the nonlinear interaction in a material. The incoming signal to be switched is split between the arms of the interferometer. The

interferometer is balanced so that, in the absence of a control signal, the incoming signal emerges from one output port. The presence of a strong control pulse changes the refractive index of the medium given by

$$\Delta n = n_2 I \tag{3}$$

Where  $\Delta n$  is the change in the refractive index of the medium,  $n_2$  is the nonlinear refractive coefficient and I is the intensity of the light incident on the medium. A change in the index adds a phase shift between the two arms of the interferometer, so that the incoming signal is switched over to another output port. This method of switching is based on cross phase modulation (XPM). In much resent years, Semiconductor optical amplifier (SOA) makes a revolution in designing high speed (>100 Gb/s) interferometric switches in all-optical information processing system. The technology of SOA has been evolving rapidly during the resent years and has become mature enough so that it is now key factor in implementation of modern optical communication networks. SOA are commercially available device and have different important properties. Such as, fast and strong nonlinearities, short latency, thermal stability, low power consumption, large dynamic range, short response time, broadband and versatile operation and capability of large scale integration with chip level design.

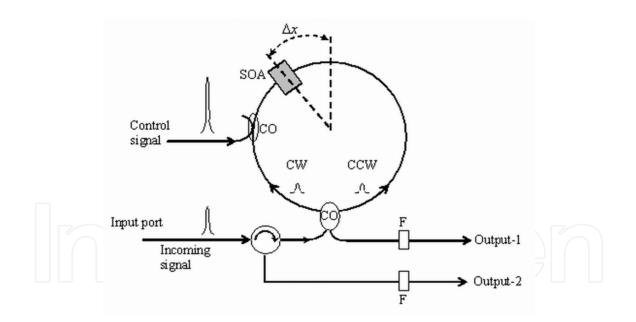

**Figure 7.** A TOAD based optical switch, where SOA: Semiconductor optical amplifier, CW: Clockwise pulse, CCW: Counter clockwise pulse, CO: coupler, F: Filter which blocks control pulse.

The Fig. 7 is a Sagnac interferometer that uses an SOA offset from the midpoint of the loop and is known as a terahertz optical asymmetric demultiplexer (TOAD). It can operate at frequencies in terahertz range [50-51]. There are two couplers; 1) the control coupler provides an input path for the control pulses to enter the fiber loop in order to saturate the SOA, and 2) the input coupler (50:50) where the incoming pulse signal train entering the loop splits equally into

clockwise (CW) and counter clockwise (CCW) pulses. CW and CCW pulses arrive at the SOA at slightly different times as determined by the offset  $\Delta x$  of the SOA from the midpoint of the loop. Another strong light pulse is also injected to the loop. It is called control signal (CS). When *CS=ON*, then SOA changes its index of refraction. As a result, the two counter-propagation data signal will experience a differential gain saturation profiles. Therefore cross phase modulation (XPM) take place when they recombine at the input coupler. Then relative phase difference between CW and CCW pulse become  $\sim \pi$  and the data will exit from the transmitted port / T-port (output-1 according to the Fig. 7). In the absence of a control signal (*CS=OFF*), the incoming signal enters the fiber loop, pass through the SOA at different times as they counter-propagate around the loop, and experience the nearly same unsaturated amplifier gain of SOA, recombine at the input coupler. Then, relative phase difference between CW and CCW is zero (0). Then no data is found at the T-port. Then data is reflected back toward the source and isolated by optical circulator (CR). The port through which it comes is called reflected port /R-port (output-2 according to the Fig. 7). A filter (F) may be used at the output to reject the control and pass the incoming pulse. 'F' can be polarization filter of band pass filter.

The output power of transmitted port (T-port) and reflected port (R-port) of a TOAD based switch can be expressed as [52-53],

$$P_T(t) = \frac{P_{in}(t)}{4} \cdot \left\{ G_{cw}(t) + G_{ccw}(t) - 2\sqrt{G_{cw}(t) \cdot G_{ccw}(t)} \cdot \cos(\Delta\varphi) \right\}$$

(4)

$$P_{R}(t) = \frac{P_{in}(t)}{4} \cdot \left\{ G_{cw}(t) + G_{ccw}(t) + 2\sqrt{G_{cw}(t) \cdot G_{ccw}(t)} \cdot \cos(\Delta\varphi) \right\}$$

(5)

where,  $G_{cw}(t)$ ,  $G_{ccw}(t)$  are the power gain of CW and CCW pulse,  $\Delta \varphi = (\varphi_{cw} - \varphi_{ccw})$  is the difference CW and CCW pulse, between can be expressed phase as  $\Delta \varphi = -\alpha / 2 \cdot \ln(G_{cw} / G_{ccw})$ . The temporal duration of the switching window  $(\tau_{win})$  that depends on the offset position of the SOA in the loop ( $\Delta x$ ) is given by  $T_{off} = 2\Delta x / c_{fiber}$ , where  $c_{fiber}$  is the velocity of light inside the optical fiber. More specifically eccentricity of the loop must be less than half the bit period, otherwise the two counter-propagating halves of incoming signal (IS) being processed will not experience the gain dynamics caused by their synchronized control pulses but instead by others resulting in incomplete switching. T <sub>FWHM</sub> of the control pulse must be as short as possible and ideally less than the switching window so that when CCW pulse is inserted in the SOA the CW pulse already passed through and the SOA gain has started to recover after saturation by the control pulse or else the two components of IS will overlap inside the SOA perceiving its nonlinear properties only partially altered, thus obstructing the creation of the required differential phase shift [52-53].

$$\sigma < T < 0.5\xi < \tau_e < 1.5\xi \tag{6}$$

$\xi$  is bit period. For low switching window eccentricity of the loop (*T*) should be small. One data when transmit through the switching window, next data cannot pass until the gain recovery of the SOA takes place.

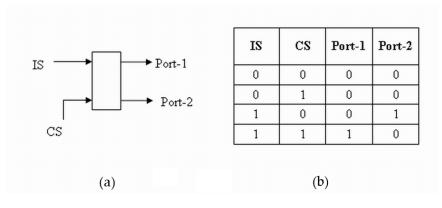

In summary we can say, in the absence of control signal, the incoming signal exits through input port of TOAD and reaches to the output port-2 as shown in Fig. 8(a). In this case no light is present in the output port-1. But in the presence of control signal, the incoming signal exits through output port of TOAD and reaches to the output port-1 as shown in Fig. 8(a). In this case no light is present in the output port-2. In the absence of incoming signal, port-1 and port-2 receives no light as the filter blocks the control signal. Only incoming signal is passed through filter. Truth table is given in Fig. 8(b). The above principle of the switch is used to design basic quaternary logic circuits.

Figure 8. (a) Schematic block diagram TOAD based switch (b) the corresponding truth table.

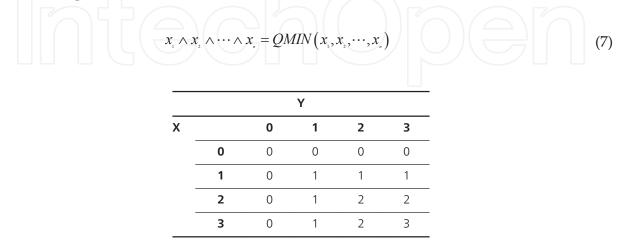

#### 2.2. All-optical two input Quaternary MIN Gate

Quaternary MIN gate is equivalent AND gate in binary world [6,39]. It is an important multi-valued logic function. The QMIN operation is shown in the equation no (7), the operator  $\land$  is QMIN operation. Truth table is shown in Table 1.

Table 1. Truth Table of Quaternary MIN(x,y).

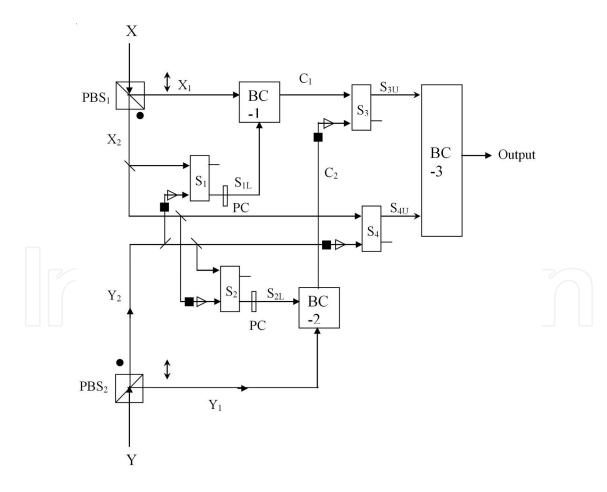

Polarization encoded all- optical QMIN Gate is shown in the Fig. 9. Here light from inputs X and Y fall into two PBS (PBS<sub>1</sub>& PBS<sub>2</sub>), where it split into two polarized light, one is vertically polarized ( $\uparrow$ ) and other is horizontally polarized (•).Hence, X<sub>1</sub>& Y<sub>1</sub> are vertically polarized (1) and  $X_2$   $X_2$  are horizontally polarized (•). Light from  $X_2$  and  $Y_2$  are fed to two Interferometric switches (here TOAD)  $S_1$  and  $S_2$  as incoming signal and also their control signals are taken from  $Y_2$  and  $X_2$  respectively. The lower outputs of  $S_1$  and  $S_2$  are passed through a PC (polarization converter, which is preferably half wave plate; converts vertically polarized light to horizontal one and vice versa). It is indicated as  $S_{1L}$  and  $S_{2L}$  respectively in the Fig. 9.  $X_1$  and  $S_{1L}$  is combined by a BC-1, the combined ray ( $C_1$ ) is connected to another switch  $S_3$  as incoming signal. Also  $Y_1$  and  $S_{2L}$  are combined by BC-2 and the combined ray ( $C_2$ ) is connected to  $S_3$  as control signal. The upper output channel of  $S_3 (S_{3U})$  is feed to BC-3. Again  $X_2$ and Y<sub>2</sub> are feed to another switch S<sub>4</sub> as incoming and the control signal respectively. All the control signals are amplified by EDFA (Erbium Doped Fiber Amplifier). When incoming light signal is incident on wavelength converter (WC) then the wavelength converter (WC) converts the wavelength of incoming signal to wavelength of control signal. The upper output channel of this switch  $S_4$  ( $S_{4U}$ ) is connected to BC-3. The combined ray is the final output. Let us describe the operational principles in detail [66].

- **1.** When X=0,  $X_1=X_2=0$ .  $X_2$  which act as a incoming signal of  $S_1$  and  $S_4$  is zero. So  $S_{1L}$  and  $S_{4U}$  receive no light. So the BC-1 receives no light and hence the output of BC-1 is zero therefore  $S_{3U}$  receives no light. Hence the final Output after BC-3 is 0. This result cannot be changed by any value of Y.

- 2. Similarly when Y=0,  $Y_1=Y_2=0$  so all the incoming signals of  $S_2$  and control signal of  $S_4$  and  $S_3$  is zero hence  $S_{4U}=S_{2L}=C_2=S_{3U}=0$  i.e. receive no light. So the final Output after BC-3 is 0. This result cannot change by any value of X.

- **3.** When X=1( $\ddagger$ ), X<sub>1</sub>=1 and X<sub>2</sub>=0. So S<sub>1L</sub>& S<sub>4U</sub> receives no light (as incoming signal of S<sub>1</sub> and S<sub>4</sub> is absent). And C<sub>1</sub>=1 ( $\ddagger$ ) i.e. vertically polarized light.

- Now as Y=1(1) then Y<sub>1</sub>=1, Y<sub>2</sub>=0. So S<sub>2L</sub>=0 (as incoming signal of S<sub>2</sub> is absent), C<sub>2</sub>=1. So S<sub>3U</sub>=1 (as C<sub>2</sub> is the incoming signal of S<sub>3</sub>). So the final Output after BC-3 is 1 (1).

- When Y=2 (•) i.e. horizontally polarized light, then Y<sub>1</sub>=0 (no light) and Y<sub>2</sub>=2. So S<sub>2L</sub> and hence C<sub>2</sub> receives vertically polarized light (1 i.e. 1). Hence S<sub>3U</sub>=1. So the final Output after BC-3 is 1 (1).

- Now when Y=3 (↔), then Y<sub>1</sub>=1,Y<sub>2</sub>=2. So S<sub>2L</sub>=1 (as incoming signal is present but control signal is absent at S<sub>2</sub>), C<sub>2</sub>=1. Hence S<sub>3U</sub>=1. So the final Output after BC-3 is 1 (\$).

- 4. When X is 2 (•) and Y is 1 (‡), then  $X_1 \& Y_2$  receives no light. That means here,  $X_1 = 0 \& Y_2 = 0$  and  $Y_1=1$ ,  $X_2=2$ . Hence  $S_{4U}=S_{2L}=0$  (as the control signal of  $S_4$  and incoming signal of  $S_2$  is absent) and  $S_{1L}=C_1=C_2=1$  i.e. vertically polarized light. So  $S_{3U}=1$  as both the incoming and control signal of  $S_3$  are present. So the final Output after BC-3 is 1 (‡).

- 5. When X=Y=2 (●) i.e. both of them are horizontally polarized light, then X<sub>1</sub>& Y<sub>1</sub> receives no light (0) and X<sub>2</sub>& Y<sub>2</sub> receives horizontally polarized light (2). Hence S<sub>4U</sub>=2 and S<sub>2L</sub>=0

(as both the incoming and control is present of  $S_4$  and  $S_2$ ) As  $Y_1=S_{2L}=0$ . So  $S_{3U}=0$ . So the final Output after BC-3 is 2 (•).

- 6. When X takes horizontally polarized light i.e. 2 (•) and Y is partially polarized light i.e.3 (↔) then X<sub>1</sub> receives no light (0) and Y1=1, X2=Y2=2. Hence S<sub>4U</sub>=2 and S<sub>2L</sub>=0, C<sub>2</sub>=1. Again as X<sub>2</sub>=Y<sub>2</sub>=2, then S<sub>1L</sub>=C<sub>1</sub>=0 (as both the incoming and control signal are present at S<sub>1</sub>). As C<sub>1</sub> is the incoming signal of S<sub>3</sub>, hence S<sub>3U</sub>=0. And the final Output 2 (•).

- 7. When X=3 (↔), then X<sub>1</sub>=1 and X<sub>2</sub>=2. When Y=1, then Y<sub>1</sub>=1 and Y<sub>2</sub>=0. So S<sub>4U</sub>=S<sub>2L</sub>=0 (as the control signal is absent in S<sub>4</sub> and the incoming signal is absent in S<sub>2</sub>) and S<sub>1L</sub>=1 (as incoming is present but control signal is absent in S<sub>1</sub>). So C<sub>1</sub>=C<sub>2</sub>=1, hence S<sub>3U</sub>=1. So final Output is 1 (\$).

- 8. When X=3 ( $\leftrightarrow$ ), then X<sub>1</sub>=1 and X<sub>2</sub>=2. When Y=2 (•), Y<sub>1</sub>=0 and Y<sub>2</sub>=2. So S<sub>4U</sub>=2 and S<sub>2L</sub>=S<sub>1L</sub>=0. So C<sub>1</sub>=1 and C<sub>2</sub>=0, hence S<sub>3U</sub>=0. So the final output is 2 (•).

- **9.** When X & Y both are partially polarized light i.e.  $3 \leftrightarrow$ , Then X<sub>1</sub>=Y<sub>1</sub>=1 and X<sub>2</sub>=Y<sub>2</sub>=2. So S<sub>4U</sub> receives horizontally polarized light (2 i.e. •) and S<sub>2L</sub>=S<sub>1L</sub>=0. Hence C<sub>1</sub>=C<sub>2</sub>=1, hence S<sub>3U</sub>=1. So final Output is  $3 \leftrightarrow$ ).

**Figure 9.** All-optical Quaternary QMIN(X,Y) Circuit. S (Switch): PBS : Polarizing Beam Splitter BC : Beam Combiner PC : Polarization Converter, ► EDFA : Erbium Doped Fiber Amplifier, ■ : WC Wavelength Converter.

#### 2.3. All-optical Quaternary delta LITERALS

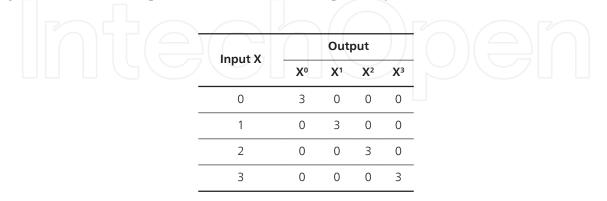

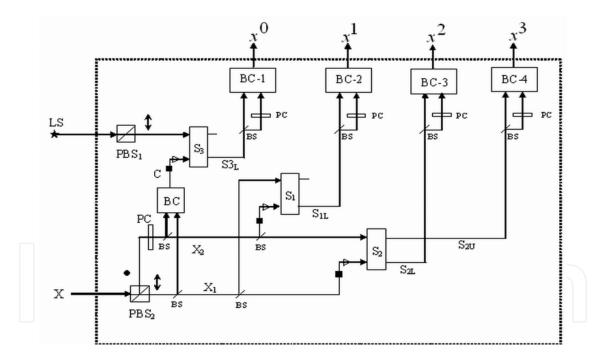

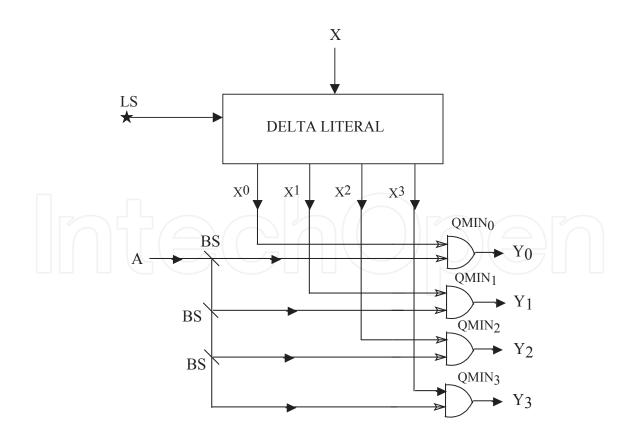

Literals are very important function in multi-valued logic based information processing [67]. The truth table of Delta literal circuit [66] is in the Table 2 and the circuit diagram is shown in the Fig. 10. Here, X is the quaternary input, which can take any one of the four quaternary logic states and the output is  $x^0$ ,  $x^1$ ,  $x^2$  and  $x^3$  respectively.

Table 2. Truth table of quaternary delta Literals.

Figure 10. All-optical Quaternary Delta Literal Circuit.

1. When X=0 (absent of light), X<sub>1</sub>& X<sub>2</sub> receives no light and the other outputs of the switch S<sub>1</sub>, S<sub>2</sub> are 0 as they receives no light. Here only vertically polarized light (<sup>↑</sup>), which comes from LS through PBS<sub>1</sub>, falls on S<sub>3</sub>. This act as incoming signal. Here as control signal is absent (because of C=0) the light comes out through lower channel of S<sub>3</sub> i.e. through S<sub>3L</sub>. A part of this directly enters in the beam combiner (BC) and another part is passed through PC, which converts vertically polarized (<sup>↑</sup>) to horizontally polarized

light (•). And hence the output of BC-1 is  $x^0$  receives partially polarized light i.e. 3 ( $\leftrightarrow$ ). Hence the final outputs are  $x^0=3(\leftrightarrow)$  i.e. partially polarized light and others receives no light i.e.  $x^1=0$ ,  $x^2=0$  and  $x^3=0$ .

- 2. When X=1 (1), then X<sub>1</sub>=1, X<sub>2</sub>=0 and C=1. So S<sub>3L</sub>=0 as control signal of S<sub>3</sub> is present and S<sub>1L</sub>=1 (1) as control signal of S<sub>1</sub> is absent. Other outputs (S<sub>2U</sub>& S<sub>2L</sub>) of the switch S<sub>2</sub> are absent, as the incoming signal of S<sub>2</sub> is absent. So the final outputs are  $x^0=0$ ,  $x^1=3(\leftrightarrow)$ ,  $x^2=0$  and  $x^3=0$ .

- 3. When X=2 (•), then X<sub>1</sub>=0, X<sub>2</sub>=1 and C=1. So  $S_{3L}=0$ ,  $S_{1L}=0$  as the incoming signal of  $S_1$  is absent.  $S_{2U}=0$  and  $S_{2L}=1$  (\$), because control signal of  $S_2$  is absent. Hence the final outputs are  $x^0=0$ ,  $x^1=0$ ,  $x^2=3(\leftrightarrow)$  and  $x^3=0$ .

- **4.** When X is partially polarized light i.e.3 ( $\leftrightarrow$ ), then all the X<sub>1</sub>, X<sub>2</sub>& C receives vertically polarized light i.e.1. So S<sub>3L</sub>= S<sub>1L</sub>= S<sub>2L</sub>=0 and S<sub>2U</sub>=1 ( $\ddagger$ ) as both the incoming and control signal of S<sub>3</sub>, S<sub>1</sub> and S<sub>2</sub> are present. So the final outputs are  $x^0=0$ ,  $x^1=0$ ,  $x^2=0$  and  $x^3=3$  ( $\leftrightarrow$ ).

#### 2.4. Design of All-optical Quaternary Multiplexer (4:1) :

From the truth Table 3 (truth table of QMIN gate) we can say that,

$$\begin{cases} 3 \land A = A \\ 0 \land A = 0 \end{cases} \quad \text{where } A \in \{0, 1, 2, 3\}$$

$$(8)$$

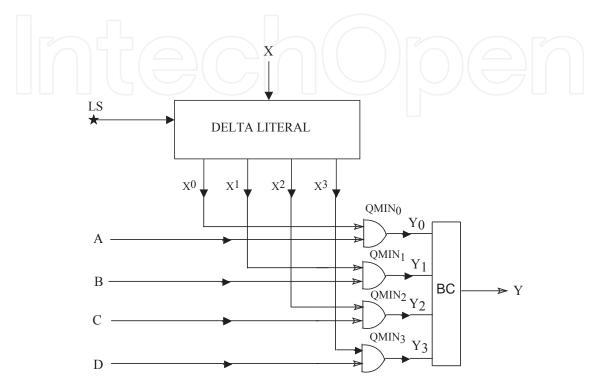

Now we design quaternary multiplexer (QMUX) and demultiplexer (QDEMUX) using the basic gates QMIN and Delta Literal, made by switching character of the non-liner material based switch [66].

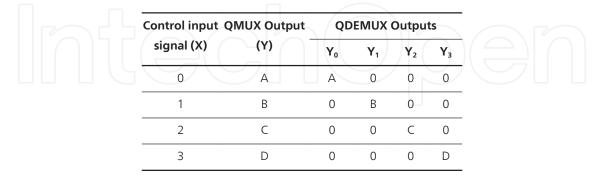

**Table 3.** Truth Table of Quaternary Multiplexer (QMUX) and Demultiplexer (QDEMUX).

Multiplexing means many into one. A multiplexer is system dealing with many inputs and only with single output. A quaternary multiplexer with n-control inputs can be used to route one of  $4^n$  data inputs (it may be any one of the four logical states) to the output. Fig. 11

is the design of 4:1 all-optical quaternary multiplexer. Here four inputs A, B, C and D [which can be any one of the 4-logical state i.e. 0(no light),  $1(\ddagger)$ ,  $2(\bullet)$ ,  $3(\leftrightarrow)$ ] are connected to four 2-input QMIN gates (QMIN<sub>0</sub>, QMIN<sub>1</sub>, QMIN<sub>2</sub>, and QMIN<sub>3</sub>). Other input of the QMIN is fed from one of the Delta Literal outputs (i.e. $x^0$ ,  $x^1$ ,  $x^2$  and  $x^3$ ) respectively as shown in Fig. 11. These inputs of QMIN are act as a select line.

Figure 11. All optical Quaternary 4:1 Multiplexer (QMUX).

- 1. When X (delta literal input) is zero i.e. with no signal (0), then  $x^{0}$  receives the logical state 3 (↔) i.e. partially polarized light and others outputs of the delta literal ( $x^{1}$ ,  $x^{2}$  and  $x^{3}$ ) receive no light (0) as discussed in earlier section. As  $x^{0}$  is connected with QMIN<sub>0</sub>, then according to the equation no 7, only QMIN<sub>0</sub> is active and others QMIN gates (QMIN<sub>1</sub>, QMIN<sub>2</sub> and QMIN<sub>3</sub>) are inactive. Hence the corresponding input A is at the output i.e.  $Y_{0} = A$ . and  $Y_{1} = Y_{2} = Y_{3} = 0$ . Hence after combining in BC we receives Y = A at the outputs.

- **2.** When X is vertically polarized light i.e. 1 (1), then only  $x^{-1}$  receives the logical state 3 ( $\leftrightarrow$ ). &  $x^0 = x^2 = x^3 = 0$  (no light). As  $x^1$  is connected with QMIN<sub>1</sub>, then according to the equation no (2) only QMIN<sub>1</sub> is active and QMIN<sub>0</sub>, QMIN<sub>2</sub> and QMIN<sub>3</sub> are inactive. Hence Y<sub>1</sub> = B & Y<sub>0</sub> = Y<sub>2</sub> = Y<sub>3</sub> = 0 and at the final output we receives Y = B.

- **3.** When X is horizontally polarized i.e. 2 (•), then only  $x^2$  receives the logical state 3 ( $\leftrightarrow$ ). And  $x^0 = x^1 = x^3 = 0$  (No light). Hence only QMIN<sub>2</sub> is active and QMIN<sub>0</sub>, QMIN<sub>1</sub> and QMIN<sub>3</sub> are inactive. Hence  $Y_2 = C \& Y_0 = Y_1 = Y_3 = 0$  and at the final output, we receives Y = C.

When X is partially polarized light i.e. 3 (↔), then only x<sup>3</sup>receives the logical state 3 (↔). And x<sup>0</sup>=x<sup>1</sup>=x<sup>2</sup>=0 (no light). Hence only QMIN<sub>3</sub> is active and others QMIN<sub>0</sub>, QMIN<sub>1</sub> and QMIN<sub>2</sub> are inactive. Hence Y<sub>3</sub> = D & Y<sub>0</sub> = Y<sub>1</sub> = Y<sub>2</sub> =0 and combining, at the final output we receives Y = D. The truth table of this circuit is shown in the Table 3 (second column).

#### 2.5. Design of All-optical Quaternary Demultiplexer (1:4):

A quaternary demultiplexer has the opposite function of QMUX. Here one input data is passed to one of the outputs according to the selection of the control. Fig. 12 is the design of 1:4 all-optical quaternary demultiplexers. Here one Input A is fed to every four 2-input QMIN gate as one input light (light from A is split by three beam splitters (BS) and fed to four 2-input QMIN gates) and other input of the QMIN is fed from one of the Delta Literal outputs (i.e. $x^0$ ,  $x^1$ ,  $x^2$  and  $x^3$ ) respectively. These inputs of QMIN gates act as select line. This circuit act like same way as multiplexer circuit i.e. one QMIN is active (depends on the selection of the control line) and others QMIN gates are inactive. The active QMIN gate passes the input data from A which may be one of the four logical sate. The final outputs are taken from the combination of four QMIN output line ( $Y_0$ ,  $Y_1$ ,  $Y_2$  and  $Y_3$ ) as shown in Fig. 12. The truth table is shown in the Table 3 (third column).

Figure 12. All optical Quaternary 1:4 Demultiplexer (QDEMUX).

## 3. Quaternary T-gate:

In section 2.4 we have reported all-optical 4:1 all-optical quaternary multiplexer. It is also known as 'T-Gate' [82]. The schematic diagram for quaternary T-gate is shown in Fig. 13. some logic operations are given in table 4.

| Name of the<br>functions    | Symbol & mathematical expression                                                                          | Inputs<br>(logical states) |   |   | ates) | Outputs                                |

|-----------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------|---|---|-------|----------------------------------------|

|                             |                                                                                                           | Α                          | В | С | D     |                                        |

| Compliment /<br>Inverter    | $\bar{x} = (R-1) - x$                                                                                     | 3                          | 2 | 1 | 0     | (3210)                                 |

| Successor                   | $Suc(x) = (x + 1) \mod 4$                                                                                 | 1                          | 2 | 3 | 0     | (1230)                                 |

|                             |                                                                                                           | 1                          | 2 | 3 | 0     | X₁=⟨1230⟩                              |

| Clockwise<br>Cycle          | $\hat{X}_b = (x+b) \mod 4$                                                                                | 2                          | 3 | 0 | 1     | X₂=⟨2301⟩                              |

|                             |                                                                                                           | 3                          | 0 | 1 | 2     |                                        |

|                             |                                                                                                           | 3                          | 0 | 1 | 2     | X_1c=⟨3012⟩                            |

| Counter<br>Cycle<br>Literal | $\hat{X}_{b^c} = (x - b) \mod 4$                                                                          | 2                          | 3 | 0 | 1     | $\hat{X}_{2^c} = \langle 2301 \rangle$ |

|                             |                                                                                                           | 1                          | 2 | 3 | 0     | $\hat{X}_{3^c} = \langle 1230 \rangle$ |

|                             |                                                                                                           | 0                          | 3 | 3 | 0     | $^{1}x^{2} = \langle 0330 \rangle$     |

|                             | ${}^{a}x^{b} = \begin{cases} (R-1) \text{ if } a \le x \le b \\ 0 \text{ otherwise} \end{cases}$          | 0                          | 3 | 3 | 3     | <sup>1</sup> x <sup>3</sup> =(0333)    |

|                             |                                                                                                           | 0                          | 0 | 3 | 3     | <sup>2</sup> x <sup>3</sup> =(0033)    |

| Truncated<br>Sum            | $X \boxplus a = \begin{cases} (X + a) \text{ if, } X < (R - 1) \\ (R - 1) & \text{otherwise} \end{cases}$ | 1                          | 2 | 3 | 3     | X ⊞ 1=⟨1233⟩                           |

| Truncated<br>difference     | $X \boxminus a = \begin{cases} (X - a) \text{ if, } X \ge a \\ 0 & \text{otherwise} \end{cases}$          | 0                          | 0 | 1 | 2     | X ⊟1=⟨0012⟩                            |

| Threshold<br>literals (up)  | $U_{a(x)} = \begin{cases} 1 & \text{if } x \ge a \\ 0 & \text{else} \end{cases}$                          | 0                          | 1 | 1 | 1     | <sup>U</sup> 1 <sup>(x)</sup> =(0111)  |

|                             |                                                                                                           | 0                          | 0 | 1 | 1     | <sup>U</sup> 2 <sup>(x)</sup> =(0011)  |

| Step literals               | $D_{a(x)} = \begin{cases} 1 & \text{if } x \le a \\ 0 & \text{else} \end{cases}$                          | 1                          | 1 | 0 | 0     | $^{D}1^{(x)} = \langle 1100 \rangle$   |

| (down)                      | a(x) = 0 else                                                                                             | 1                          | 1 | 1 | 0     | $^{D}2^{(x)} = \langle 1110 \rangle$   |

**Table 4.** Some well-known one input quaternary logical functions (radix *R*=4) and design process with quaternary T-gate.

The mathematical expression for all-optical quaternary T-gate using MIN & delta literals can be written as:

Figure 13. All optical Quaternary T-gate.

Where, ' $\wedge$ ' is MIN operator ( $x \wedge y$ = minimum of (x, y)) and  $\delta$ - literals function is  $x^a = (R-1)$  if x=a, else 0] The four incoming data transmission lines are 'A', 'B', 'C' and 'D' [which can be any one of the 4-logical state i.e. 0 (no light), 1( $\uparrow$ ), 2 (•), 3 ( $\leftrightarrow$ )] and 'X' is the selection input. By using proper section we can get any data (A, B, C or D) at the output. If X=0, the output is A, when X=1 then the output is B, for X=2 the output is C and when X=3 then the output is D respectively i.e. [82]:

$$T(A,B,C,D;x) = \begin{cases} A & \text{if } x = 0 \\ B & \text{if } x = 1 \\ C & \text{if } x = 2 \\ D & \text{if } x = 3 \end{cases}$$

(10)

This T-gate can successfully used for designing any quaternary circuits. So it is called 'universal' element of quaternary logic. Some quaternary logical operations with T-gate is shown in Table 4. Here inputs of T-gate A, B, C, and D are shown in colomn-3 of that table 4. X is the select input = $\langle 0123 \rangle$ . Here the quaternary multiplexer or T-gate is all-optical in nature. Hence all the quaternary circuits are all-optical.

## 4. Challenges in designing the polarization encoded all-optical system:

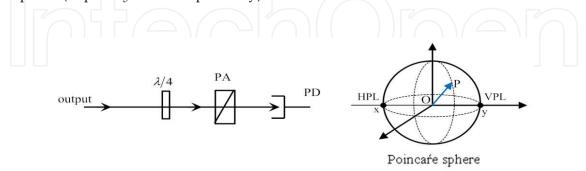

Here, in this proposed scheme, we have proposed and described an all-optical circuit for designing quaternary (four-valued) multiplexer & de-multiplexer with the help of some polarization encoded basic quaternary logic gates (quaternary min and quaternary delta literal). It is important to note that the above discussions are based on simple model. In order to experimentally achieve result from the proposed scheme, some design issues have to be considered. For example, polarization properties of fiber, predetermined values of the intensities, wavelength of laser light for control and incoming signals, introduction of filter, intensity losses due to beam splitters/fiber couplers etc. The output logical states of every ternary circuit can be determined by, stokes vector [S] measurement. Stokes vector can be calculated from the measurement of six intensities ( $I_{ij}$ ) in the photo detector (PD) by use of a linear analyzer (LA) followed by a quarter wave plate ( $\lambda$  /4plate), which is shown in the Fig. 14. The formula for calculating stokes vector is [83]:

$$\begin{bmatrix} \mathbf{S} \end{bmatrix} = \begin{bmatrix} \mathbf{S}_{0} \\ \mathbf{S}_{1} \\ \mathbf{S}_{2} \\ \mathbf{S}_{3} \end{bmatrix} = \sqrt{\frac{\mu_{0}}{\varepsilon_{0}}} \begin{bmatrix} \mathbf{I}_{(0,0^{\circ})} + \mathbf{I}_{(0,90^{\circ})} \\ \mathbf{I}_{(0,0^{\circ})} - \mathbf{I}_{(0,90^{\circ})} \\ \mathbf{I}_{(0,45^{\circ})} - \mathbf{I}_{(0,135^{\circ})} \\ \mathbf{I}_{(\frac{\lambda}{4},45^{\circ})} - \mathbf{I}_{(\frac{\lambda}{4},135^{\circ})} \end{bmatrix}$$

(11)

Where first subscript ('*i*') index lack or presence of  $\lambda/4$  plate and the second ('*j*') gives the azimuth of the analyzer.  $\mu_0$  and  $\varepsilon_0$  is free space permeability and permittivity. Degree of polarization (DOP) is also calculated by the equation:

DOP =

$$\frac{\sqrt{S_1^2 + S_2^2 + S_3^2}}{S_0}$$

(12)

The value of DOP can be plotted in Poincaré sphere in point 'P' and we found that, for vertically ( $\ddagger$ ) and horizontally ( $\bullet$ ) polarized light OP=DOP=1 and lies on the equator of the Poincaré sphere (at point *y* and *x* respectively).

Figure 14. Measurement technique of output logical states.

In high speed data communication (50 GB/s or TB/s) random change of polarization in a short time can produce power fluctuation at the output. So polarization dependent loss

(PDL) degrades the optical signal to noise ratio (OSNR) and also degrades the extinction ratio. PDL of 3 dB could cause 1 dB power penalty [84]. Optical depolarizers can be used to reduce the polarization-induced noise in optical sensing and measurement systems [85]. Again random birefringence in optical fibers induces an unpredictable rotation of the sate of polarization (SOP); this can be adjusted by using polarization controller and PM fiber. Intrinsic cross talk between two polarization states, imperfection of polarized tracking after transmission link etc may cause polarization mode dispersion (PMD). This may cause the delay among the different states of polarization. The effects of PMD are expected to be similar to those of other approaches that have been studied in the literature [86]. Optical amplifiers degrade the signal-to-noise ratio (SNR) of the amplified signal because of spontaneous emission added to the signal during its amplification (ASE). The OSNR-errors arise in this process. For polarized signal PHB will cause ASE polarization orthogonal to the signal polarization. Bruyere et al [87] have shown that the DOP of ASE could exceed 70% in transoceanic links with low PMD. Of course, the most of ASE light does not traverse the entire light path, and then OSNR-errors become less as < 0.6 dB. Polarization related problem discussed above would occur inside the considered circuit. The said problem will not occur in optical communications system once the signal comes out the output. State of polarization may be changed if it is passed through bi-refringent crystals or optically active substances. The significant advantage of this proposed scheme is that the schemes are all-optical in nature and can be easily and successfully be extended for higher order multiplexer and demultiplexer. As an example, for 16:1 multiplexer, 16-select lines can be constructed by two Delta literals outputs and 16-QMIN gates. Now select lines are to be fed to again 16-QMIN gate as first input and the second input is to be taken from the input signals. By selecting proper select line we can transfer any one of 16-input signals to the output. This scheme is easily practicable as the components of our design are technically highly developed and widely used in optical communication. The proposed scheme will work with other 2x2 Interferometric switches (like Mach-Zehnder interferometer) also.

#### 5. Conclusions and Future Scopes:

In present day digital signal processing is based on conventional binary number system (radix = 2). It has two logical states 'LOW' and 'HIGH'. Binary logic (or logic for that matter) is NOT a law of nature. The reason why binary logic seems more natural is because we have been more exposed to it. The perspective MVL is more like an extension of binary logic and very conventional, though broader in possibilities. In a wide sense, a signal may be anything that can be observed to have states that change in time and space. In narrow sense, a signal is a physical quantity that can be measured, usually by an electronic device. Signals, as conveyers of information about the state of a system, should be processed to extract and understand the information content encoded. Nowadays, digital systems, and sometimes mixed-signal systems, are prevalent in information transmission, storage, and processing. However, enormous, and ever increasing, amounts of information that can be handled, even in everyday life, focus attention to multiple-valued (MV) logic, which permit more compact

encoding of information within the same amount of digits. Although, having certain considerable demerits, multiple-valued logic is viewed as promising alternatives in many practical solutions. Many contemporary logic design technologies are oriented towards supporting an efficient implementing of various signal processing algorithms. In order to entirely exploit all the available resources, sophisticated methods are required. Humans count by tens, machines count by twos, these sums up the way we do arithmetic today. However, there are countless other ways to count. Challenges and opportunities are wide.

## Author details

Jitendra Nath Roy<sup>1\*</sup> and Tanay Chattopadhyay<sup>2</sup>

\*Address all correspondence to: jnroys@yahoo.co.in

1 Department of Physics, National Institute of Technology, Agartala, Jirania, Tripura, India

2 Mechanical operation (stage-II), Kolaghat Thermal Power station, WBPDCL, West Bengal, India

### References

- [1] Woods, D., & Naughton, T. J. (2012). Photonic neural networks. *Nature Physics*, 8, doi: 10.1038/nphys2283, 257-259.

- [2] Caulfield, H. J., & Dolev, S. (2010). Why future supercomputing requires optics. *Nature Photonics*, 4, doi:10.1038/nphoton.2010.94, 262-263.

- [3] Caulfield, H. J., Dolev, S., & Green, W. M. J. (2009). Appl. Opt. A, 48(Optical High-Performance Computing feature issue), http://dx.doi.org/10.1364/AO.48.0OHPC1.

- [4] Roy, S., Prasad, M., Topolancik, J., & Vollmer, F. (2010). All optical switching with bacterirhodopsin protein coated microcavities and its application to low power computing circuits. *Journal of Applied Physics*, 107, 053115, http://dx.doi.org/ 10.1063/1.3310385.

- [5] Reed, T., Mashanovich, G., Gardes, F. Y., & Thomson, D. J. (2010). Silicon optical modulators. *Nature Photonics*, 4, doi:10.1038/nphoton.2010.179, 518-526.

- [6] Hurst, S. L. (1984). Multiple-Valued Logic-Its Status and its Future. *IEEE Transactions* on computers, C-33(12), 1160-1179, Doi:10.1109/TC.1984.1676392.

- [7] Lohmann, A. W. (1988). Polarization and optical logic. Applied Optics, 25, 1594-1597.

- [8] Fagotto, E. A. M., & Abbade, M. L. F. (2009). All-optical demultiplexing of 4-ASK optical signals with four-wave mixing optical gates. *Optics Communications*, 283, 1102-1109, Doi: 10.1016/j.optcom.2009.10.094.

- [9] Khan, M. H. A., & Perkowski, M. A. (2007). GF(4) based synthesis of quaternary reversible / quantum logic gate. *Proc. of the 37th international symposium on multiple-val*ued logic, ISMVL'07 IEEE, Doi:10.1109/ISMVL.2007.26.

- [10] Obiniyi, A. A., Absalom, E. E., & Adako, K. (2011). Arithmetic Logic Design with Color-Coded Ternary for Ternary Computing. *International Journal of Computer Applications*, 26(11), 0975-8887, Doi: 10.5120/3162-2929, 31-37.

- [11] Garai, S. K., Pal, A., & Mukhopadhyay, S. (2010). All-optical frequency-encoded inversion operation with tristate logic using reflecting semiconductor optical amplifiers. *Optik*, 121, DOI:10.1016/j.ijleo.2009.02.011, 1462-1465.

- [12] Stakhov, A. (2002). Brousentsov's ternary principle Bergman's number system and ternary mirror-symmetrical arithmetic. *The Computer Journal*, 45(2), 221-236, doi: comjnl/45.2.221.

- [13] Walklin, S., & Conradi, J. (1997). A 10 Gb/s 4-ary ASK lightwave system. ECOC 97, IEE, Conference publication, 448(448), 255-258, DOI: cp:19971538.

- [14] Liu, S., Li, C., Wu, J., & Lin, Y. (1989). Optoelectronic multiple-valued logic implementation. *Optics letters*, 14(14), 713-715, http://dx.doi.org/10.1364/OL.14.000713.

- [15] Awwal, A. A. S., Karim, M. A., & Cherri, A. K. (1987). Polarization-encoded optical shadow-casting scheme: design of multi-output trinary combinational logic units. *Applied optics*, 26(22), 4814-4818, http://dx.doi.org/10.1364/AO.26.004814.

- [16] Imai, Y., & Ohtsuka, Y. (1987). Optical multiple-output and multiple-valued logic operation based on fringe shifting techniques using a spatial light modulator. *Applied optics*, 26(2), 274-277, doi: AO.26.000274.

- [17] Li, C., & Yan, J. (2011). Design Method and Implementation of Ternary Logic Optical Calculator. Advances in Information and Communication Technology, 347, Doi: 10.1007/978-3-642-18369-0\_17, 147-166.

- [18] Chattopadhyay, T. (2010). All-optical symmetric ternary logic gate. *Optics and Laser Technology*, 42, DOI: 10.1016/j.optlastec.2010.01.023, 1014-1021.

- [19] Song, Kai, & Yan, Liping. (2012). Design and implementation of the one step MSD adder of optical computer. *Applied Optics*, 51(7), 917, doi: AO.51.000917.

- [20] Chattopadhyay, T., Maity, G. K., & Roy, Jitendra Nath. (2008). Designing of all-optical tri-state logic system with the help of optical nonlinear material. *Journal of Nonlinear Optical Physics & Materials*, 17(3), 315-328, Doi: S0218863508004159.

- [21] Chattopadhyay, T., & Roy, J. N. (2011). Semiconductor optical amplifier (SOA)-assisted Sagnac switch for designing of all-optical tri-state logic gates. *Optik International*

*Journal for Light and Electron Optics*, 122(12), DOI: 10.1016/j.ijleo.2010.06.045, 1073-1078.

- [22] Chattopadhyay, T., & Roy, J. N. (2011, March 26-27). All-optical multi-valued computing: the future challenges and opportunities. Kolkata. *International conference on convergence of Optics and Electronics (COE 11)*, 94-101, 978-8-19064-011-4.

- [23] Vasundara Patel, K. S., & Gurumurthy, K. S. (2010). Quaternary Sequential Circuits. IJCSNS International Journal of Computer Science and Network Security, 10(7), 110, DOI: 10.1109/ICCIT.2009.5407139.

- [24] Yi, J., Huacan, H., & Yangtian, L. (2005). Ternary computer architecture. *Physica Scripta*, T 118(98), 101, doi:10.1238/Physica.Topical.118a00098.

- [25] Roy, J. N. (2009). Mach-Zehnder interferometer-based tree architecture for all-optical logic and arithmetic operations. *Optik-International Journal for Light and Electron Optics*, 120(7), 218-324, http://dx.doi.org/10.1016/j.ijleo.2007.09.004.

- [26] Khan, M. H. A., Siddika, N. K., & Perkowski, M. A. (2008). Minimization of quaternary galois field sum of products expression for multi-output quaternary logic function using quaternary Galois field decision diagram. *Proceedings of the 38<sup>th</sup> international symposium on Multiple-valued logic (DOI 10.1109/ISMVL.2008.31) IEEE*, 125-130, Doi: 10.1109/ISMVL.2008.31.

- [27] Li, G., Qian, F., Ruan, H., & Liu, L. (1999). Compact Parallel Optical Modified-Signed-Digit Arithmetic-Logic Array Processor with Electron-Trapping Device. *Applied Optics*, 38(23), 5039-5045, http://dx. doi.org/10.1364/AO.38.005039.

- [28] Chattopadhyay, T., & Sarkar, T. (2012). All-optical switching by Kerr nonlinear prism and its application to of binary-to-gray-to-binary code conversion. *Optics & Laser Technology*, 44(6), 1722-1728, http://dx.doi.org/10.1016/j.optlastec.2012.02.007.

- [29] Jung, Y. J., Lee, S., & Park, N. (2008). All-optical 4-bit gray code to binary coded decimal converter. *Proc. of SPIE*, 6890, 68900S, doi:10.1117/12.762429.

- [30] Nakamura, T., Kani, J. I., Teshima, M., & Iwatsuki, K. (2004). A quaternary amplitude shift keying modulator for suppressing initial amplitude distortion. *IEEE Journal of Lightwave Technology*, 22(3), 733-738, DOI: 10.1109/JLT.2004.824465.

- [31] Awwal, A. A. S., & Ahmed, J. U. (1993). Fast Carry free Adder Design Using QSD Number System. *IEEE*, Doi:10.1109/NAECON.1993.290791, 1085-1088, CH3306-8/93/0000-1085.

- [32] Awwal, A. A. S., & Ahmed, J. U. (1994). Two-bit restricted signed-digit quaternary full adder. *Proc. Of IEEE*, DOI:10.1109/NAECON.1994.332917, 1119-1125.

- [33] Cherri, A. K., & Al-Zayed, A. S. (2009). Circuit designs of ultra-fast all-optical modified signed-digit adders using semiconductor optical amplifier and Mach-Zehnder interferometer. *Optik*, doi:10.1016/j.ijleo.2009.02.029, in press.

- [34] Ghosh, A. K., Bhattacharya, A., Raul, M., & Basuray, A. (2012). Trinary arithmetic and logic unit (TALU) using savart plate and spatial light modulator (SLM) suitable for optical computation in multivalued logic. *Optics & Laser Technology*, 44(5), DOI: 10.1016/j.optlastec.2011.11.044, 1583-1592.

- [35] Jahangir, I., Hasan, D. M. N., & Reza, M. S. (2009, 23-26 Jan.) Design of Some Quaternary Combinational Logic Blocks Using a New Logic System. Singapore. *TENCON* '09, *IEEE Region 10 Conference*, Doi: 10.1109/TENCON.2009.5396095, 1-6.

- [36] Smith, K. C. (1988). Multiple-valued logic: a tutorial and appreciation. *IEEE computers*, 21(4), 1160-1179, doi:10.1109/2.48.

- [37] Cunha, R., Boudinov, H., & Carro, L. (2007). Quaternary look-up tables using voltage mode CMOS logic design. *Proceedings of the 37th International Symposium of multiple* valued logic (ISMVL'07) IEEE, 0-7695-2831-7, Doi:10.1109/ISMVL.2007.47.

- [38] Shanbhag, N. R., Nagchoudhuri, D., Ferd, R. E. S., & Visweswaran, G. S. (1990). Quaternary logic circuits with 2-jum CMOS technology. *IEEE Journal of solid-state circuits*, 25(3), 790-798, doi: 10.1109/4.102677.

- [39] Park, S. J., Yoon, B. H., Sub Yoon, K., & Kim, H. S. (2004). Design of Quaternary Logic Gate Using Double Pass-transistor Logic with neuron MOS Down Literal Circuit. *Proceedings of the 34 th International Symposium on Multiple-valued logic (ISMVL2004)*, 198-203, doi: 10.1109/ISMVL.2004.1319941.

- [40] Kerkho, H. G., & Tervoert, M. L. (1981). Multiple-valued logic charge-coupled devices. *IEEE Transactions computers*, C-30(9), 644-652, http://doi.ieeecomputersociety.org/ 10.1109/TC.1981.1675862.

- [41] Yasuda, Y., Tokuda, Y., Zaima, S., Pak, K., Nakamura, T., & Yoshida, A. (1986). Realization of Quaternary Logic Circuits by n-Channel MOS Devices. *IEEE Journal of solidstate circuits*, sc-21(1), 162-168, DOI: 10.1109/JSSC.1986.1052493.

- [42] Kerkhoff, H. G., & Tervoert, M. L. (1981). Multiple-Valued logic Charge-Coupled Devices. *IEEE Transactions computers*, C-30(9), 644-652, http://doi.ieeecomputersociety.org/10.1109/TC.1981.1675862.

- [43] Brilman, M., Etiemble, D., Oursel, J. L., & Tatareau, P. (1982). A 4-valued ECL encoder and decoder circuit. *IEEE Journal of solid-state circuits*, sc-17(3), 547-552, Doi: 10.1109/TC.1986.1676733.

- [44] Mangin, J. L., & Current, K. W. (1986). Characteristics of prototype CMOS quaternary logic Encoder-Decoder circuits. *IEEE Transactions on Computers*, C-35(2), 157-161, Doi: 10.1109/TC.1986.1676733.

- [45] Etiemble, D., & Israël, M. (2002). A current-mode folding / interpolating CMOS analog to quaternary encoding block. *Proc. Of 32nd IEEE International Symposium on Multiple-valued logic (ISMVL2002)*, 0-7695-2831-7, http://doi.ieeecomputersociety.org/ 10.1109/ISMVL.2002.1011099.

- [46] Chan, H. L., Mohan, S., & George, I. Haddad. (1996). Compact Multiple-Valued Multiplexerers Using negative Differential Resistance Devices. *IEEE Journal of Solid-State circuits*, 31(8), 1151-1155, doi=10.1.1.136.8146.

- [47] Chattopadhyay, T., Bhowmik, P., & Roy, J. N. (2012). Polarization encoded optical N-valued inverter. *JOSA B*, Accepted.

- [48] Keshavarzian, P., & Mirzaee, M. M. (2012). A novel, efficient CNTFET Galois design as a basic ternary-valued logic field. *Nanotechnology, Science and Applications*, 5, 1-11, http://dx.doi.org/10.2147/NSA.S27550.

- [49] Khorasaninejad, M., & Saini, S. S. (2011). All-optical logic gate in silicon nanowire optical waveguides. *IET Circuits, Devices and system*, 5(2), 115-122, 10.1049/iet-cds. 2010.0142.

- [50] Glesk, I., Runser, R. J., & Prucnal, P. R. (2001). New generation of devices for all-optical communication. *Acta physica slovaca*, 51(2), 151-162, http://dx.doi.org/ 10.1117/12.498224.

- [51] Wang, B. C., Baby, V., Tong, W., Xu, L., Friedman, M., Glesk, I., Runser, R. J., & Prucnal, P. R. (2002). A novel fast optical switch based on two cascaded terahertz optical asymmetric demultiplexers (TOAD). *Optics Express*, 10(1), 15-23, http://www.opticsinfobase.org/oe/abstract.cfm?URI=oe-10-1-15.

- [52] Houbavlis, T., & Zoiros, K. E. (2004). Numerical simulation of semiconductor optical amplifier assisted Sagnac gate and investigation of its switching characteristics. *Optical Engineering*, 43(7), 1622-1627, http://dx.doi.org/10.1117/1.1751132.

- [53] Zoiros, K. E., Chasioti, R., Koukourlis, C. S., & Houbavlis, T. (2007). On the output characteristics of a semiconductor optical amplifier driven by an ultrafast optical time division multiplexing pulse train. *Optik*, 118(3), 134-146, DOI: 10.1016/j.ijleo. 2006.01.012.

- [54] Shen, Z. Y., & Wu, L. L. (2008). Reconfigerable optical logic unit with a teraheartz optical asymmetric demultiplexer and electro-optic switches. *Applied Optics*, 47(21), 3737-3742, DOI: 10.1364/AO.47.003737.

- [55] Roy, J. N., Maity, A. K., & Mukhopadhyay, S. (2006). Designing of an all-optical time division multiplexing scheme with the help of non linear material based tree-net architecture. *Chinese Optics letters*, 4(8), 483-486.

- [56] Karim, M. A., & Awwal, A. A. S. (2003). *Optical Computing: an introduction*, Wiley, New York, Chap-6.

- [57] Chattopadhyay, T., & Roy, J. N. (2009). An all-optical technique for a binary-to-quaternary encoder and a quaternary-to-binary decoder. *J.Opt.A: Pure Appl. Opt.*, 11, doi: 10.1088/1464-4258/11/7/075501.

- [58] Shen, Z. Y., Wu, L., & Yan, J. (2012). The reconfigurable module of ternary optical computer. Optik International Journal for Light and Electron Optics, http://dx.doi.org/ 10.1016/j.ijleo.2012.03.081.

- [59] Chattopadhyay, T., & Roy, J. N. (2009). All-optical conversion scheme: binary to quaternary and quaternary to binary number. *Optics & Laser Technology*, 41(3), 289-294, http://dx.doi.org/10.1016/j.optlastec.2008.06.003.

- [60] Taraphdar, C., Chattopadhyay, T., & Roy, J. N. (2009). Polarization Encoded All-optical Ternary Max Gate. Kolkata. *International conference on computers and devices for communication CODEC-09*, Paper ID OLT-3512. Print, 978-1-42445-073-2, INSPEC Accession Number 11136770.

- [61] Taraphdar, C., Chattopadhyay, T., & Roy, J. N. (2011). All-optical integrated ternary MIN and MAX gate. Kolkata, India. *Proceedings of international conference on Trends in* optics and photonics (IconTOP 2011), 476-481, 978-81-908188-1-0.

- [62] Bhowmik, P., Roy, J. N., & Chattopadhyay, T. (2011). Designing of all-optical two input ternary MAX logical operation. *National conference of photonics and nano sciences*, *Dept of physics, Garhbeta college*, 51-58.

- [63] Roy, J. N., Chattopadhyay, T., Manna, S., & Maity, G. K. (2008). Polarization encoded all-optical quaternary max gate. IIT Delhi, India. *PHOTONICS '08, International Conference on Fiber Optics and Photonics*, 1-4.

- [64] Chattopadhyay, T., & Roy, J. N. *Quaternary MAX gate and its applications in all-optical domain,* unpublished.

- [65] Bhowmik, P., Chattopadhyay, T., Taraphdar, C., & Roy, J. N. (2011, March 26-27). Designing of All Optical Circuit for Two Input Ternary MIN Logical Operation. Kolkata. *International conference on convergence of Optics and Electronics, (COE 11),* 94-101, 978-8-19064-011-4.

- [66] Chattopadhyay, T., & Roy, J. N. (2009). Polarization encoded all-optical quaternary multiplexer and demultiplexer-a proposal. *Optik International Journal for Light and Electron Optics*, 120, 941-946, http://dx.doi.org/10.1016/j.ijleo.2008.03.030.

- [67] Chattopadhyay, T., & Roy, J. N. (2010). Polarization encoded TOAD based all-optical quaternary Literals. *Optik International Journal for Light and Electron Optics*, 121, 617-622, http://dx.doi.org/10.1016/j.ijleo.2008.09.014.

- [68] Taraphdar, C., Chattopadhyay, T., & Roy, J. N. (2011). Designing of an all-optical scheme for single input Ternary logical operations. *Optik International Journal for Light* and Electron Optics, 122(1), 33-36, http://dx.doi.org/10.1016/j.ijleo.2009.09.016.

- [69] Chattopadhyay, T., & Roy, J. N. Polarization encoded four valued ordinary inverter. XXXVI OSI Symposium on Frontiers in Optics and Photonics, (FOP 11) IIT, P 99, 978-81-309-1964-5.

- [70] Chattopadhyay, T., & Roy, J.N. (2012). All-optical ordinary quaternary inverter (QNOT) using binary NOT gate. *Optik International Journal for Light and Electron Optics*, in press, doi: 10.1016/j.ijleo.2012.01.035.

- [71] Chattopadhyay, T., & Roy, J.N. (2010). Polarization Encoded All-optical Quaternary Universal Inverter and Designing of Multi-valued Flip-flop. *Optical Engineering*, 49(3), 035201, DOI: 10.1117/1.3362897.

- [72] Chattopadhyay, T., & Roy, J.N. (2011). Polarization encoded all-optical quaternary successor with the help of SOA assisted Sagnac switch. *Optics communication*, 284(12), 2755-2762, DOI:10.1016/j.optcom.2011.02.005.

- [73] Chattopadhyay, T., & Roy, J.N. (2011). All-optical quaternary Galois field sum of product (GFSOP) circuits. *Optik International Journal for Light and Electron Optics*, 122(9), 758-763, http://dx.doi.org/10.1016/j.ijleo.2010.06.002.

- [74] Chattopadhyay, T., & Roy, J. N. (2010, 27-28 March). All-optical quaternary half-adder circuit with the help of Terahertz optical asymmetric demultiplexer (TOAD). Burdwan. National conference on materials, devices and circuits in communication Tech. (MDCCT'2010), TS. 4.12, 50.

- [75] Chattopadhyay, T., Das, M.K., Roy, J.N., Chakraborty, A.K., & Gayen, D.K. (2011). Interferometric switch based all optical scheme for Conversion of Binary number to its Quaternary Signed Digit form. *IET Circuits, Devices and system, (special issue on 'Optical Computing Circuits, Devices and Systems'*), 5(2), 132-142, doi: 10.1049/iet-cds. 2010.0056.

- [76] Chattopadhyay, T., & Roy, J.N. (2011). Easy conversion technique of Binary to Quaternary Signed Digit and vice versa. *Physics Express*, 1(3), 165-174.

- [77] Chattopadhyay, T., & Roy, J.N. (2009, March 1-4). All-optical conversion of binary number to quaternary signed digit (QSD) number. Kolkata, India. *Proceedings of international conference on Trends in optics and photonics (IconTOP 2009)*, 130-137.

- [78] Chattopadhyay, T., & Roy, J.N. (2011, 28<sup>th</sup> February- 1<sup>st</sup> March). All-optical carry free addition using quaternary signed digit (QSD). 18<sup>th</sup> West Bengal state science & Technology congress, 1(2), 3-4.

- [79] Chattopadhyay, T., Taraphdar, C., & Roy, J.N. (2009). Quaternary Galois field adder based all-optical multivalued logic circuits. *Applied Optics*, (*feature issue on 'optical high-performance computing'*), 48(22), E35-E44, http://dx.doi.org/10.1364/AO.48.000E35.

- [80] Chattopadhyay, T., Roy, J.N., & Chakraborty, A.K. (2009). Polarization encoded alloptical quaternary R-S flip-flop using binary latch. *Optics Communications*, 282, 1287-1293, DOI:10.1016/j.optcom.2008.12.022.

- [81] Taraphdar, C., Chattopadhyay, T., & Roy, J.N. (2011). Designing of Polarization encoded all-optical ternary multiplexer and Demultiplexer. *Recent Patents on Signal Processing*, 1(2), 143-155, doi:10.2174/1877612411101020143.

- [82] Chattopadhyay, T. (2010). All-optical quaternary circuits using quaternary T-gate. *Optik International Journal for Light and Electron Optics*, 121, 1784-1788, DOI:10.1016/ j.ijleo.2009.04.014.

- [83] Domanski, A.W. (2005). Polarization degree fading during propagation of partially coherent light through retarders. *Opto-Electronics Review*, 7<sup>th</sup> International Workshop on Nonlinear Optics applications, 13(2), 171-176.

- [84] Mecozzi, A., & Shtaif, M. (2002). The statistics of polarization dependent loss in optical communication systems. *IEEE photonics tech. letter*, 14(3), 313-315, DOI: 10.1109/68.986797.

- [85] Nelson, L.E, Nielson, T.N., & Kogelnik, H. (2001). Observation of PMD-induced coherent crosstalk in polarization-multiplexed transmission. *IEEE photonics tech. letter*, 13(7), 738-740, DOI:10.1109/68.930432.

- [86] Tang, J.M., & Shore, K.A. (1998). Strong picosecond optical pulse propagating in semiconductor optical amplifiers at transparency. *IEEE Journal of Quantum Electronics*, 34(7), 1263-1269, doi: 10.1109/3.687871.

- [87] Bruyere, F., & Andouin, O. (1994). Penalties in long-haul optical amplifiers systems due to polarization dependent loss and gain. *IEEE Photonics Tech. Letters*, 6(5), 654-656, doi: 10.1109/68.285570.

IntechOpen