## we are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

122,000

135M

Our authors are among the

TOP 1%

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

### Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

## Electronic Controllers in

### Analysis of Power Electronic Controllers in Electric Power Systems Using Simulink

Juan Segundo-Ramirez<sup>1</sup> and A. Medina<sup>2</sup> <sup>1</sup>Universidad Autónoma de San Luis Potosí <sup>2</sup>Universidad Michoacana de San Nicolás de Hidalgo México

#### 1. Introduction

Flexible ac Transmission Systems (FACTS) devices have emerged in power system because of the development of power electronics components for high voltage and power. The FACTS devices provide higher controllability in power systems by means of power electronic devices. Several FACTS equipments have been already introduced for various applications worldwide, and new types of FACTS are in the stage of being introduced in practice. FACTS technology provides a better ability to varying operational conditions and improves the usage of existing installations.

#### 2. Power electronic application in transmission systems

It can be seen that with growing line length and with higher power demand the opportunity for FACTS devices gets more important. The devices work electrically as fast current, voltage or impedance controllers. The power electronic allows very short reaction times down to far below one second (~ms). Detailed introductions in FACTS devices can also be found in the literature (Hingorani & Gyudyi, 2000) (Acha, et al. 2004) (Mathur & Varma, 2002)(Padiyar, 2007) (Zhang, Rehtanz, & Pal, 2006) with the main focus on new topologies, modeling and control.

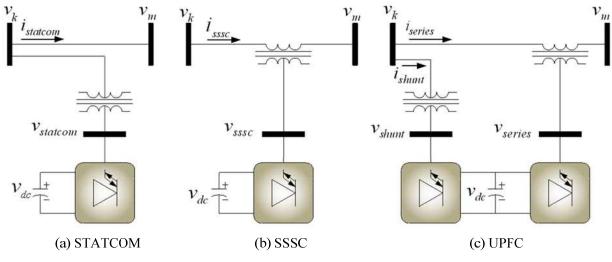

Basically, there are two groups of FACTS, one is based on thyristor valve operation (Hingorani & Gyudyi, 2000), and the other is based on Voltage Source Converters (VSCs) (Segundo-Ramírez & Medina, 2008) (Segundo-Ramírez & Medina, 2009). A list of some FACTS devices are shown in Table 1. The FACTS devices based on VSCs provide a controllable voltage magnitude and phase angle due to a Pulse Width Modulation (PWM) technique (Mohan, Underland, & Robins, 1995). The Static Compensator (STATCOM) (Hingorani & Gyudyi, 2000) is a shunt connected device that is able to provide reactive power support at a network location far away from the generators. Through this reactive power injection, the STATCOM can regulate the voltage at the connection node. The Static Synchronous Series compensator (SSSC) (Hingorani & Gyudyi, 2000) is a series device which injects a voltage in series with the transmission line. The Unified Power Flow Controller (UPFC) (Hingorani & Gyudyi, 2000) is the most versatile device of the family of FACTS devices, since it is able to control the active and the reactive power, respectively, as

well as the voltage at the connection node. In Figure 1 a schematic representation of the STATCOM, the SSSC, and the UPFC are presented. The compensating FACTS devices under analysis in this chapter are briefly described below.

| Connection Type        | FACTS Devices                                     |                                                 |

|------------------------|---------------------------------------------------|-------------------------------------------------|

|                        | Thyristor-Based FACTS                             | VSC-Based FACTS                                 |

| Shunt Connected        | Static Var Compensator (SVC)                      | Static Compensator (STATCOM)                    |

| Series Connected       | Thyristor Controlled Series<br>Compensator (TCSC) | Static Series Synchronous<br>Compensator (SSSC) |

| Back-to-Back Connected | HVDC                                              | Unified Power Flow Controller<br>(UPFC)         |

|                        |                                                   | HVDC VSC                                        |

Table 1. Overview of the principal FACTS-Devices.

Fig. 1. FACTS devices based on VSCs. (a) STATCOM, (b) SSSC, and (c) UPFC.

#### 2.1 Static compensator (STATCOM)

It is a shunt device that does not require passive elements for reactive compensation. The STATCOM operation is based on a VSC, which is supplied by a dc storage capacitor. The VSC terminals are connected to the dc system through a coupling transformer. The VSC produces a quasi-sine wave voltage at the fundamental frequency (50 or 60 Hz). The STATCOM can generate or absorb reactive power. A schematic representation of the STATCOM is shown in Figure 1(a).

Assuming that the losses in the VSC and the coupling transformer are negligible,  $v_{statcom}$  is in phase with the voltage at the terminal bus  $v_k$ . In this situation, the current  $i_{statcom}$  is completely reactive. If the magnitude of the voltage  $v_k$  is higher than the magnitude of  $v_{statcom}$ , the reactive current flows from the bus to the VSC, which means that the STATCOM absorbs reactive power. On the other hand, if the magnitude of  $v_{statcom}$  is higher than the magnitude of  $v_k$ , the reactive current flows from the VSC to the ac system. Then, the STATCOM injects reactive power to the system. In practice, the power losses of the STATCOM are not negligible and must be drawn from the ac system to maintain constant the dc capacitor voltage.

#### 2.2 Static synchronous series compensator (SSSC)

The SSSC is a series device in which a synchronous voltage source injects a fundamental frequency voltage in series with the transmission line through a coupling transformer. The synchronous voltage source is supplied by a VSC. A schematic representation of the SSSC is shown in Figure 1(b).

Ideally, the injected voltage is in quadrature with the line current. In this mode the VSC does not absorb or inject any real power. However, in practice, the VSC losses must be replenished by the ac system, in consequence a small phase lag is introduced for this purpose. The operating characteristics make this device very attractive for power transmission application. The main limitation of application is due to the losses and cost of the converter. The SSSC is a device which has so far not been built at transmission level because Series Compensator (fixed capacitor) and thyristor controlled series capacitor (TCSC) (Hingorani & Gyudyi, 2000) are fulfilling all the today's operational requirements at a low cost.

#### 2.3 Unified power flow controller (UPFC)

This device contains two VSCs connected together through a dc link storage capacitor. One of the VSCs is connected in series with the transmission line, while the other VSC is connected in shunt with the transmission line. The UPFC can control the active and reactive power flow in the transmission line, and at the same time can regulate the voltage magnitude at the connection node. To control the real and reactive power flow in the series side, the UPFC allows interchange of real power between the shunt and the series converters. The main disadvantage of this device is the high cost level due to the complex systems setup (Zhang, Rehtanz, & Pal, 2006). A schematic representation of the UPFC is shown in Figure 1(c).

#### 3. PSB/SIMULINK

Power System Blockset (PSB) for use with Matlab/Simulink employs state-variable analysis. In PSB complex control algorithms can be implemented into the models in an easy and fast way. Besides, PSB can use several Matlab toolboxes. In particular, it has the PWM generator and the VSC blocks. The main advantage of the PSB is that it is developed in Matlab/Simulink environment, this fact makes possible to use it together with several other control design tools. It is possible to use the Simulink Accelerator and the Real-Time Workshop to improve the PSB performance; a C code is generated. Additionally, the PSB can use several integration methods, which make it a powerful simulation tool.

#### 3.1 Modeling and analysis of FACTS by PSB/SIMULINK

This section is divided into three parts. Simulations relating to the STATCOM are presented first. This is followed by simulations carried out for the SSSC and then for the UPFC. The study case related to the STATCOM is described in detail using PSB/Simulink. For the cases of the SSSC and the UPFC, only the general implementation is described.

#### 3.2 Static compensator (STATCOM)

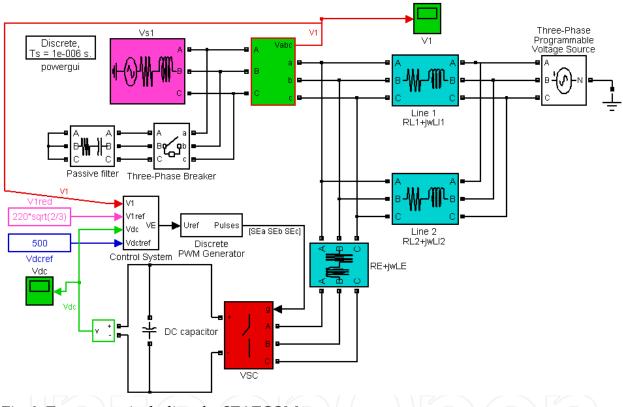

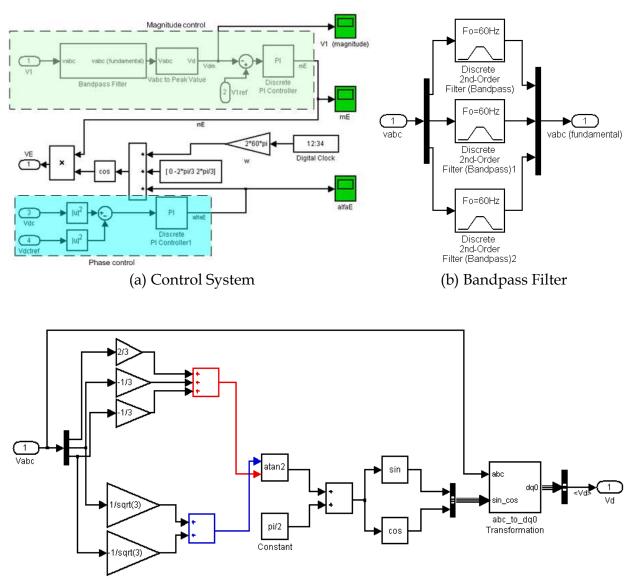

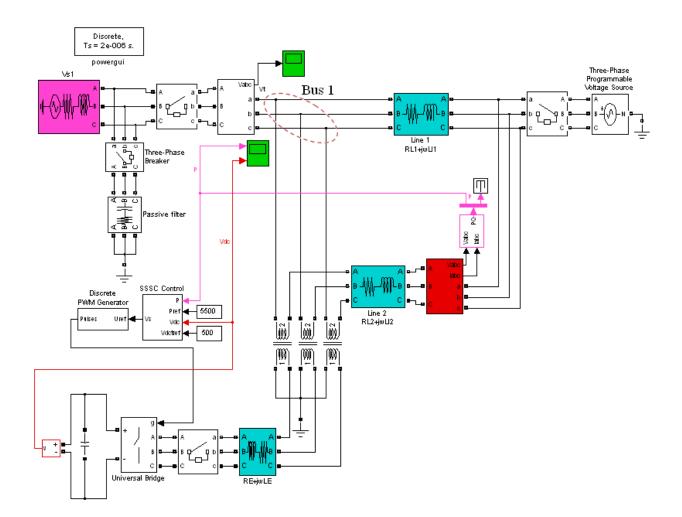

The test case is shown in Figure 2, where the STATCOM includes the control system described in (Mahyavanshi & Radman, 2006). The initial conditions are zero, the reference line to line voltage is 179.6292 volts at node 1, the reference voltage for the dc capacitor is 500 volts, and the modulation index is  $m_f$ =15 (900 Hz). The shunt transformer, the line 1 and the line 2 are represented by *RL* branches, whose impedances are 0.05 +  $j\omega \times 0.005 \Omega$ , 0.2 +  $j\omega \times 0.015 \Omega$ , and 0.15 +  $j\omega \times 0.01 \Omega$ , respectively. The Figure 3 shows the PI control used in this analysis. On the other hand, Figure 4 shows some important blocks parameters of the system. Figure 4 shows some important block of parameters for some components shown in Figure 2 and Figure 3. Please notice that a passive filter has been connected at bus 1, in order to drain the harmonic currents.

Fig. 2. Test system including the STATCOM.

The test case is initially in periodic steady state, at t = 0.05 s, the voltage magnitude of the three-phase programmable voltage source is increased 15%, and finally at t = 0.35 s, the initial operating point is reestablished. The study for the STATCOM is divided in two parts, firstly the three-phase breaker is open, and consequently the passive filter is disconnected. In the second part, the three-phase breaker is closed allowing the filtering function. The passive filter is represented as a RC branch with  $C = 80 \mu F$  and  $R = 0.5 \Omega$ .

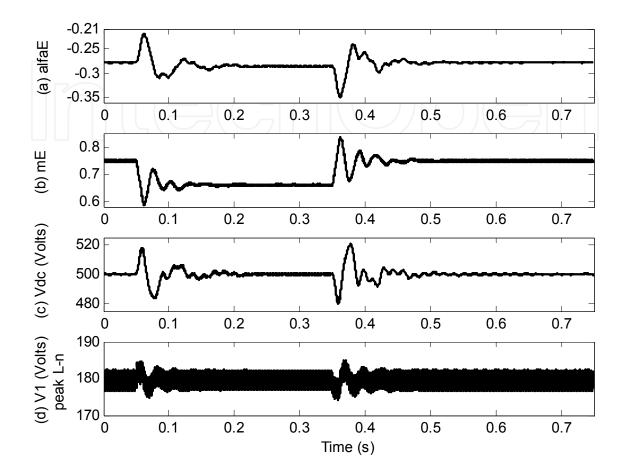

In the Figure 5, some selected transient waveforms of the STATCOM without the passive filter are shown: Figure 5(a) presents the output of the phase controller, alfaE, which is actually the phase angle of the voltage at the ac terminals of the VSC; Figure 5(b) presents the output of the magnitude control, which is the half part of the voltage magnitude at the ac terminal of the VSC; Figure 5(c) shows the voltage across the dc capacitor, and finally, the

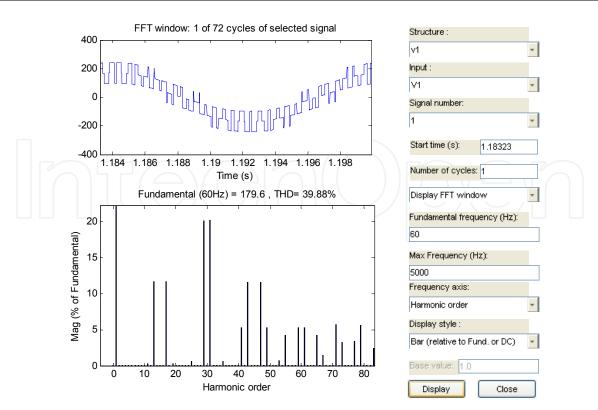

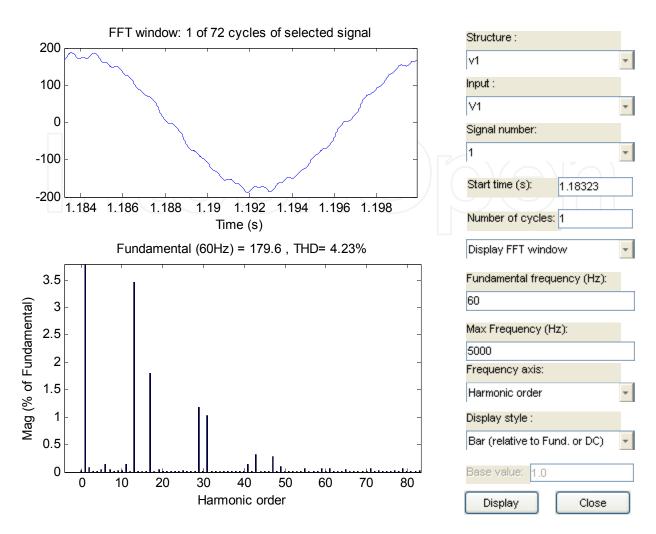

peak line-to-neutral voltage at the bus 1 is shown in Figure 5(d). Figure 6 shows the steady state waveform of the voltage at the bus 1 at the top of the figure, and its harmonic spectrum at the bottom of the figure. The Figure 6 was obtained using the FFT Analysis button in the powergui block.

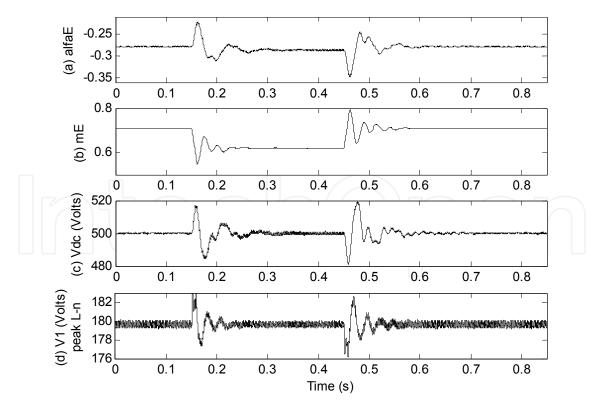

In the Figure 7, some selected transient waveforms of the STATCOM with the passive filter are shown: Figure 7(a) presents the output of the phase controller; Figure 7(b) presents the output of the magnitude control; Figure 7(c) shows the voltage across the dc capacitor, and finally, the peak line-to-neutral voltage at the bus 1 is shown in Figure 7(d). Figure 8 shows the steady state waveform of the voltage at the bus 1 at the top of the figure, and its harmonic spectrum at the bottom of the figure.

(c) Vabc to Peak Value

Fig. 3. STATCOM PI control system. (a) Main control system. (b) Bandpass filter. (c) Extraction of the peak value of a three-phase voltage in abc-reference.

| Function Block Parameters: Discrete PI Controller                                                                                                                                                                                                         | 🛛 📓 Function Block Parameters: Discrete PI Controller1 🛛 🚦                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Discrete PI Controller (mask) (link)                                                                                                                                                                                                                      | Discrete PI Controller (mask) (link)                                                                                                                                  |

| This block implements a discrete PI controller.                                                                                                                                                                                                           | This block implements a discrete PI controller.                                                                                                                       |

| Parameters                                                                                                                                                                                                                                                | Parameters                                                                                                                                                            |

| Proportional gain (Kp):                                                                                                                                                                                                                                   | Proportional gain (Kp):                                                                                                                                               |

| 0.001                                                                                                                                                                                                                                                     | 0.0000015                                                                                                                                                             |

| Integral gain (Ki):                                                                                                                                                                                                                                       | Integral gain (Ki):                                                                                                                                                   |

| 7                                                                                                                                                                                                                                                         | 30.000000000000e-005                                                                                                                                                  |

| Output limits: [Upper Lower]                                                                                                                                                                                                                              | Output limits: [Upper_Lower]<br>[10-10]*1000                                                                                                                          |

| [1 0]<br>Output initial value:                                                                                                                                                                                                                            | Output initial value:                                                                                                                                                 |

|                                                                                                                                                                                                                                                           |                                                                                                                                                                       |

| Sample time:                                                                                                                                                                                                                                              | Sample time:                                                                                                                                                          |

| Ts                                                                                                                                                                                                                                                        | Ts                                                                                                                                                                    |

|                                                                                                                                                                                                                                                           |                                                                                                                                                                       |

| <u>DK</u> <u>Cancel</u> Help <u>Apply</u>                                                                                                                                                                                                                 | OK Cancel Help Apply                                                                                                                                                  |

|                                                                                                                                                                                                                                                           | Function Block Parameters: Discrete PWM Generator                                                                                                                     |

| Block Parameters: VSC                                                                                                                                                                                                                                     | Discrete PWM Generator (mask) (link)                                                                                                                                  |

| Jniversal Bridge (mask) (link)                                                                                                                                                                                                                            | This discrete block generates pulses for carrier-based PW/M (Pulse Width Modulation),<br>self-commutated IGBTs,GTOs or FETs bridges.                                  |

| This block implement a bridge of selected power electronics devices. Series RC<br>snubber circuits are connected in parallel with each switch device. Press Help for<br>suggested snubber values when the model is discretized. For most applications the | Depending on the number of bridge arms selected in the "Generator Mode" parameter,<br>the block can be used either for single-phase or three-phase PWM control.       |

| internal inductance Lon of diodes and thyristors should be set to zero                                                                                                                                                                                    | Press Help for details on input(s) and outputs.                                                                                                                       |

| arameters                                                                                                                                                                                                                                                 | See power_1phPWM and power_3phPWM demos respectively for application                                                                                                  |

| Number of bridge arms: 3                                                                                                                                                                                                                                  | examples of single-phase and three-phase inverters using this block.                                                                                                  |

| Snubber resistance Rs (Ohms)                                                                                                                                                                                                                              |                                                                                                                                                                       |

| 1e5                                                                                                                                                                                                                                                       | Parameters                                                                                                                                                            |

| Snubber capacitance Cs (F)                                                                                                                                                                                                                                | Generator Model 3-arm bridge (6 pulses)                                                                                                                               |

| Power Electronic device Ideal Switches                                                                                                                                                                                                                    | Carrier frequency (Hz):                                                                                                                                               |

| Ron (Ohms)                                                                                                                                                                                                                                                | 15°60                                                                                                                                                                 |

| 1e-3                                                                                                                                                                                                                                                      | Sample time:                                                                                                                                                          |

| Measurements None                                                                                                                                                                                                                                         | Ts                                                                                                                                                                    |

|                                                                                                                                                                                                                                                           | Internal generation of modulating signal(s)                                                                                                                           |

| QK Cancel Help Apply                                                                                                                                                                                                                                      |                                                                                                                                                                       |

|                                                                                                                                                                                                                                                           | OK Cancel Help Apply                                                                                                                                                  |

|                                                                                                                                                                                                                                                           |                                                                                                                                                                       |

| lock Parameters: Vs1                                                                                                                                                                                                                                      | Block Parameters: Three-Phase Programmable Voltage Source                                                                                                             |

| ee-Phase Source (mask) (link)                                                                                                                                                                                                                             | Three-Phase Programmable Voltage Source (mask) (link)                                                                                                                 |

| ree-phase voltage source in series with RL branch.                                                                                                                                                                                                        | This block implements a three phase zero-impedance voltage source. The common<br>node (neutral) of the three sources is accessible via input 1 (N) of the block. Time |

| ameters                                                                                                                                                                                                                                                   | variation for the amplitude, phase and frequency of the fundamental can be<br>pre-programmed. In addition, two harmonics can be surimposed on the fundamental.        |

| nase-to-phase rms voltage (V):                                                                                                                                                                                                                            | the second se                                                       |

| 20                                                                                                                                                                                                                                                        | Note: For "Phasor smulation", frequency variation and harmonic injection are not<br>allowed. Specify Order =1 and Seq=1,2 or 0 to inject additional fundamendal       |

| ase angle of phase A (degrees):                                                                                                                                                                                                                           | components A and B in any sequence.                                                                                                                                   |

| l                                                                                                                                                                                                                                                         | Parameters                                                                                                                                                            |

| aquency (Hz):                                                                                                                                                                                                                                             | Positive-sequence: [Amplitude(Vrms Ph-Ph) Phase(deg.) Freq. (Hz) ]                                                                                                    |

| ernal connection: Yg                                                                                                                                                                                                                                      | [220 65 60]                                                                                                                                                           |

| Specify impedance using short-circuit level                                                                                                                                                                                                               | Time variation of. Amplitude                                                                                                                                          |

| urce resistance (Ohms):                                                                                                                                                                                                                                   | Type of variation: Step                                                                                                                                               |

| 5                                                                                                                                                                                                                                                         | Step magnitude (pu, deg. or Hz):                                                                                                                                      |

| urce inductance (H):                                                                                                                                                                                                                                      | 0.15                                                                                                                                                                  |

|                                                                                                                                                                                                                                                           | Variation timing (s): [Start End]                                                                                                                                     |

| De-3                                                                                                                                                                                                                                                      |                                                                                                                                                                       |

| Je-3                                                                                                                                                                                                                                                      | [0.05 0.35]                                                                                                                                                           |

| De-3                                                                                                                                                                                                                                                      | [U.U5 U.35]                                                                                                                                                           |

| De-3                                                                                                                                                                                                                                                      |                                                                                                                                                                       |

Fig. 4. Blocks parameters of important components.

6

Fig. 5. Selected transient waveforms of the STATCOM without passive filter. (a) Phase angle of the voltage at the ac terminals of the VSC. (b) Amplitude modulation ratio. (c) Voltage across the dc capacitor. (d) Peak line-to-neutral voltage at the bus 1.

From Figure 5 and Figure 7 it is easy to notice that the passive filter has a positive impact on the reduction of the harmonic distortion in the power network without affecting the performance of the controller. In Figure 6, the waveform of the voltage at bus 1 is severely distorted with a total harmonic distortion (THD) of 39.88%. In this case, some harmonic components have a magnitude of almost 20% of the fundamental component, which is an undesirable operating condition in practical applications. On the other hand, the obtained voltage at bus 1 when the passive filter is on has a THD of 4.23% and the highest magnitude of the harmonic components is around 3.5% of the fundamental component, as shown in Figure 8.

In this simulation analysis, a discrete representation of the system given in Figure 2 was used in order to carry-out the simulations, an integration step of  $1 \mu s$  was selected.

Fig. 6. Steady state waveform of the voltage at the bus 1 without passive filter (top), and its harmonic spectrum (bottom).

Fig. 7. Selected transient waveforms of the STATCOM with passive filter. (a) Phase angle of the voltage at the ac terminals of the VSC. (b) Amplitude modulation ratio. (c) Voltage across the dc capacitor. (d) Peak line-to-neutral voltage at the bus 1.

Fig. 8. Steady state waveform of the voltage at the bus 1 with passive filter (top), and its harmonic spectrum (bottom).

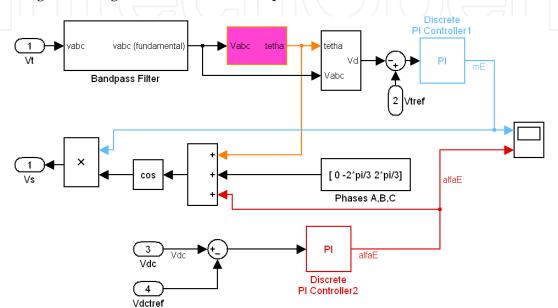

#### 3.2.1 Static synchronous series compensator (SSSC)

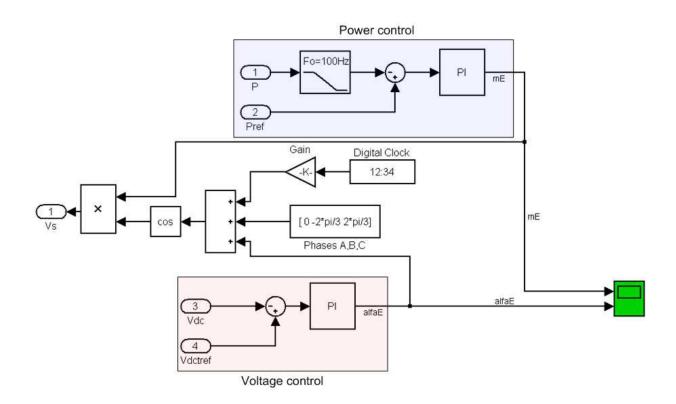

The test system for the analysis of the SSSC is shown in Figure 9. The network parameters are the same of those of Figure 2. The series transformers are represented b an ideal model. The series active power reference Pref in the line 2 is equal to 5500 W; the dc voltage capacitor reference is equal to 500 V; the gains of the power control are Kp=0.000015 and Ki=0.004, and its limits are 0 and 1; the gains of the dc voltage control are Kp=0.03 and Ki=1, and its limits are –  $\pi$  and  $\pi$

The SSSC includes the control system shown in Figure 10. This control has two control objectives: to control the active power (P) that flows in the transmission line connected in series with the SSSC, and to maintain the dc voltage capacitor at its reference value. Remember that the SSSC does not interchange active power in steady-state, only the power loss; otherwise the dc capacitor is discharged. In transient state the SSSC has transient interchanges of active power with the network, which is reflected in variation of the dc voltage. Under this situation, the control regulates the interchange of active power in order to maintain the dc voltage capacitor at its steady-state. The initial

conditions are zero; the active power reference Pref is 5500 W, and the index modulation is 41 (2.46 kHz). Pref is the active power reference in the transmission line in series with the SSSC.

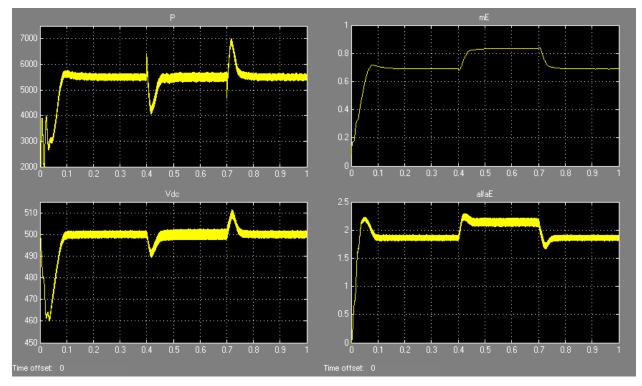

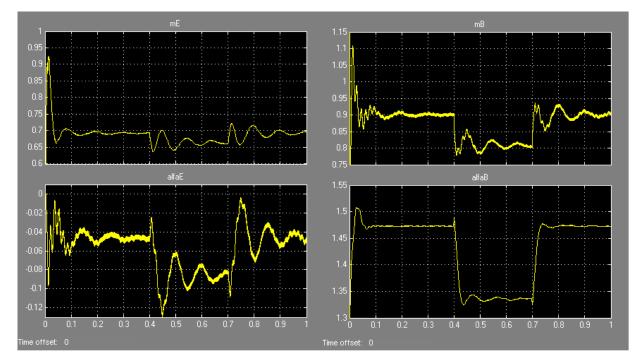

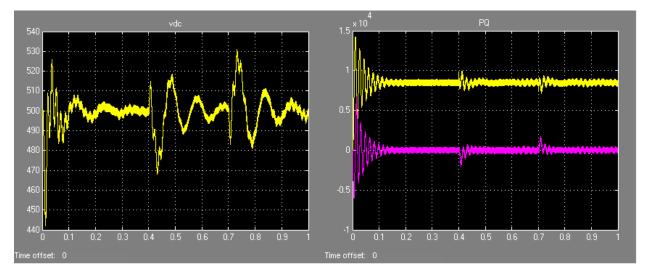

The test case has zero initial conditions for all the state variables, except for the voltage across the dc capacitor; its initial condition is 500 V. At t = 0.4 s the voltage magnitude of the three-phase programmable voltage source is increased 15%, and finally at t = 0.7 s, the initial operating point is reestablished. In this simulation analysis, a discrete representation of the system given in Figure 2 was used in order to carry-out the simulations, and an integration step of 2  $\mu s$  was selected. This analysis is also carried-out with and without the passive filter.

Figure 11 shows some selected transient waveforms of the SSSC without passive filter. In this figure it is possible to notice that the series active power decreases about 25% when the voltage magnitude of the three-phase programmable voltage source increases 15%, and the series active power increases about 25% when the same voltage goes back to the original value. The control objectives of the SSSC controller are achieved in six full cycles, as shown in this figure.

Fig. 9. Test system including the SSSC.

Fig. 10. SSSC control.

Fig. 11. Selected transient waveforms of the SSSC without passive filter. (Top left) Series active power. (Top right) Amplitude modulation ratio. (Bottom left) Voltage across the dc capacitor. (Bottom right) Phase angle of the voltage at the ac terminals.

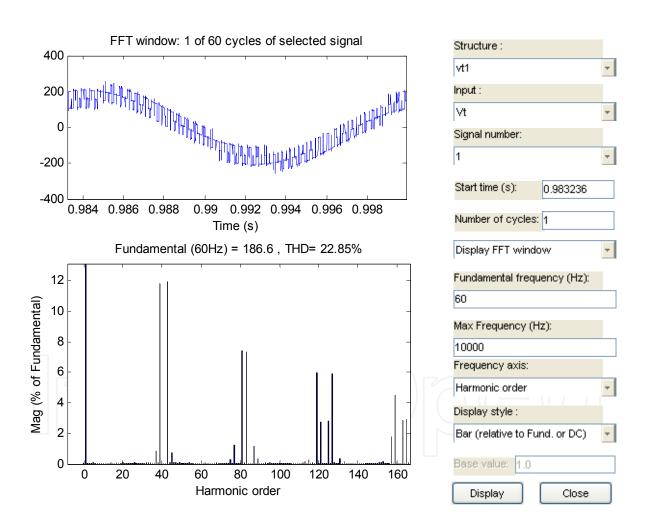

Figure 12 shows the steady state waveform of the voltage at bus 1 without passive filter. In this operating scenario, the voltage is highly distorted; the THD is around 22.85% and the harmonics 39 and 43 have a magnitude of around 12% of the fundamental component. Notice that THD is high even when the switching frequency is 2.46 kHz. On the other hand, of some selected variables, the transient and steady state solutions of the SSSC test system including the passive filter are shown in Figure 13 and Figure 14. Comparing Figure 11 and Figure 13, it is easy to notice that difference between these figures is negligible. The most remarkable difference is the reduction of the harmonic distortion in all the system, especially in the voltage at bus 1.

Fig. 12. Steady state waveform of the voltage at the bus 1 without passive filter (top), and its harmonic spectrum (bottom).

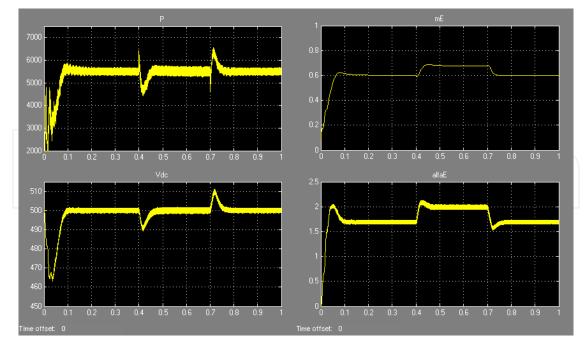

Fig. 13. Selected transient waveforms of the SSSC with passive filter. (Top left) Series active power. (Top right) Amplitude modulation ratio. (Bottom left) Voltage across the dc capacitor. (Bottom right) Phase angle of the voltage at the ac terminals.

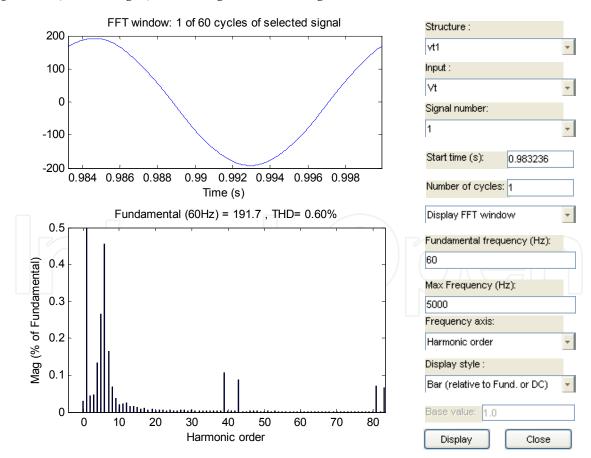

Fig. 14. Steady state waveform of the voltage at the bus 1 with passive filter (top), and its harmonic spectrum (bottom).

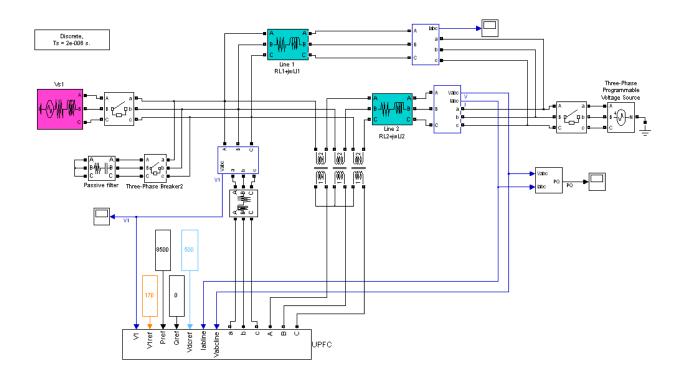

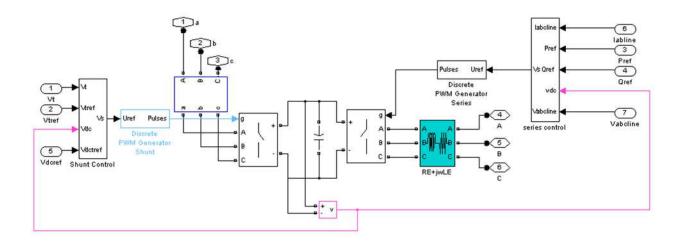

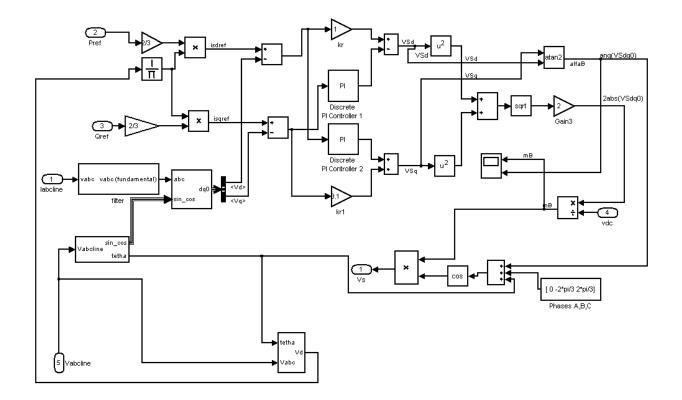

#### 3.2.2 Unified power flow controller (UPFC)

The UPFC test system of Figure 15 and Figure 16 shows the Simulink implementation of the UPFC. The network parameters are the same of those of Figure 2. The UPFC including the shunt control described in (Mahyavanshi & Radman, 2006) is schematically shown in Figure 18, and the series control proposed in (Fujita, Watanabe, & Akagi, 2001) is shown in Figure 17. The initial condition is zero, except for the dc capacitor voltage, which is 500 volts.

The series controller regulates the real (*Pref*=8500 watts) and reactive (*Qref*=0 vars) power flows by adjusting the injected series voltage. The shunt converter regulates the voltage across the dc capacitor and the sending end voltage V1 at bus 1. The modulation index is  $m_f$ =27, which represents a commutation frequency of 1.61 kHz. The RC passive filter has a capacitance of 80  $\mu$ F and a resistance of 0.2  $\Omega$ . The gains for the series controller are the following: Kp=1 and Ki=500 for the Discrete PI Controller 1, with no limits; Kp=2 and Ki=1000 for the Discrete PI Controller 2, with no limits. On the other hand, the gains for the shunt controller are: Kp=0.002 and Ki=1 for the Discrete PI Controller 1, with no limits; finally, Kp=0.0012 and Ki=0.09 for the Discrete PI Controller 2, with no limits. The UPFC analysis presented in this section only includes the case when the passive filter is connected, as shown in Figure 15.

Fig. 15. Test system including the UPFC.

Fig. 16. UPFC and its controllers.

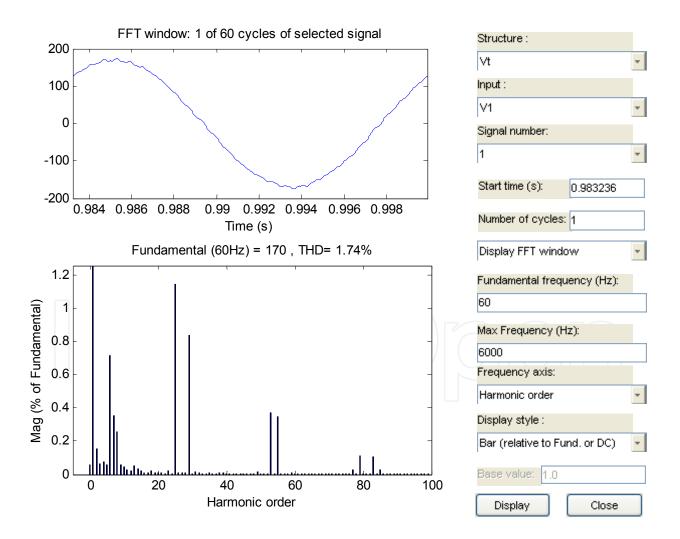

Fig. 17. Series controller.

The dynamic response of UPFC controllers are presented in Figure 19. From this figure, it is possible to observe that the variation of the three-phase programmable voltage source significantly affects the response of the series controller. This is because the magnitude of the voltages at the ends of the line controlled by the UPFC affects the power flow across the line. On the other hand, Figure 20 shows the transient waveform of the voltage across the dc capacitor and the active and reactive power flow in the controlled line. Notice that the reactive and active power remains close to the reference during the step changes in the three-phase programmable voltage source. Finally, Figure 21 presents the periodic steady-state solution of the sending end voltage V1 and its harmonic spectrum, which has a low THD of 1.74%.

Fig. 18. Shunt controller.

Fig. 19. Transient response of the series and shunt controllers of UPFC.

Fig. 20. Transient waveforms of selected variables: (Left) Voltage across the dc capacitor. (Right) Reactive (purple) and active (yellow) power.

Fig. 21. Steady state waveform of the voltage at the bus 1 (top) and its harmonic spectrum (bottom).

#### 4. Conclusions

In this chapter, implementation in Simulink of three FACTS devices based on VSC has been presented. These implementations include the STATCOM, SSSC, and the UPFC. All the implementations have been carried-out taking into account the control systems. The presented models can be used in order to analyze the dynamic and the periodic steady-state behavior of these FACTS components.

#### 5. Acknowledgements

The authors thank the Universidad Autónoma de San Luis Potosí (UASLP) and the Universidad Michoacana de San Nicolás de Hidalgo (UMSNH) for the facilities that were granted to carry out this chapter.

#### 6. References

- Acha, E., Fuerte-Esquivel, C., Ambriz-Pérez, H., & Angeles-Camacho, C. (2004). FACTS Modelling and Simulation in Power Networks, John Wiley & Sons, 9780470852712, England

- Fujita, H., Watanabe, Y., & Akagi, H. (2001). Transient Analisis of a Unified Power Flow Controller and its Application to Design of the DC-Link Capacitor. *IEEE Transaction* on Power Electronics, Vol. 16, No. 5, (september 2001), pp. 735-740, 0885-8993

- Hingorani, N. G., & Gyudyi, L. (2000). Undestanding FACTS, IEEE Press, 078033455, New York

- Mahyavanshi, B., & Radman, G. (2006). A Study of Interaction Between Dynamic Load and STATCOM. *Proceedings of the 38th southeastern symposium on system theory*, 0-7803-9457-7, Cookeville, TN, march 2006

- Mathur, R., & Varma, R. (2002). *Thyristor Based FACTS Controllers for Electrical Transmission Systems*, IEEE Computer Society Press, ISSN, Piscataway, New Jersey

- Mohan, N., Underland, T. M., & Robins, W. P. (1995). *Power Electronics: Converters, Applications, and Design,* Wiley, 0471226939, New York

- Padiyar, K. R. (2007). FACTS Controller in Power Transmission and Distribution, New Age, 978-81-224-2142-2, New Delhi

- Segundo-Ramírez, J., & Medina, A. (2009). Modeling of FACTS Devices Based on SPWM VSCs. IEEE Transaction on Power Delivery, Vol. 24, No. 4, (November 2009), pp. 1815-1823, 0885-8977

- Segundo-Ramírez, J., & Medina, A. (2008). Periodic Steady-State Solution of Electric Systems Including UPFCs by Extrapolation to the Limit Cycle. *IEEE Transaction on Power Delivery*, Vol. 23, No. 3, pp. 1506-1512

- Zhang, X.-P., Rehtanz, C., & Pal, B. (2006). *Flexible AC Transmission Systems: Modelling and Control,* Springer-Verlag. 978-3-540-30606-1, Germany

**Technology and Engineering Applications of Simulink** Edited by Prof. Subhas Chakravarty

ISBN 978-953-51-0635-7 Hard cover, 256 pages Publisher InTech Published online 23, May, 2012 Published in print edition May, 2012

Building on MATLAB (the language of technical computing), Simulink provides a platform for engineers to plan, model, design, simulate, test and implement complex electromechanical, dynamic control, signal processing and communication systems. Simulink-Matlab combination is very useful for developing algorithms, GUI assisted creation of block diagrams and realisation of interactive simulation based designs. The eleven chapters of the book demonstrate the power and capabilities of Simulink to solve engineering problems with varied degree of complexity in the virtual environment.

#### How to reference

In order to correctly reference this scholarly work, feel free to copy and paste the following:

Juan Segundo-Ramirez and A. Medina (2012). Analysis of Power Electronic Controllers in Electric Power Systems Using Simulink, Technology and Engineering Applications of Simulink, Prof. Subhas Chakravarty (Ed.), ISBN: 978-953-51-0635-7, InTech, Available from: http://www.intechopen.com/books/technology-andengineering-applications-of-simulink/analysis-of-power-electronic-controllers-in-electric-power-systems-usingsimulink

## INTECH

open science | open minds

#### InTech Europe

University Campus STeP Ri Slavka Krautzeka 83/A 51000 Rijeka, Croatia Phone: +385 (51) 770 447 Fax: +385 (51) 686 166 www.intechopen.com

#### InTech China

Unit 405, Office Block, Hotel Equatorial Shanghai No.65, Yan An Road (West), Shanghai, 200040, China 中国上海市延安西路65号上海国际贵都大饭店办公楼405单元 Phone: +86-21-62489820 Fax: +86-21-62489821 © 2012 The Author(s). Licensee IntechOpen. This is an open access article distributed under the terms of the <u>Creative Commons Attribution 3.0</u> <u>License</u>, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

# IntechOpen

# IntechOpen