# the world's leading publisher of Open Access books Built by scientists, for scientists

4,800

Open access books available

122,000

International authors and editors

135M

Downloads

154

TOD 10/

Our authors are among the

most cited scientists

12.2%

Contributors from top 500 universities

WEB OF SCIENCE™

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected.

For more information visit www.intechopen.com

### Implantable Cardioverter Defibrillators

Behzad Ghanavati

Department of Electrical Engineering, Mahshahr Branch, Islamic Azad University, Iran

#### 1. Introduction

In recently years, Artificial Neural Networks have been studied extensively and applied in medical field, and have been demonstrated to have much better pattern recognition ability. In this chapter we present a VLSI chip to be implemented using  $0.35~\mu m$  CMOS technology which is the implantable cardioverter defibrillator (ICDs).

Implantable cardioverter defibrillator is a device which monitors the heart and delivers electrical shock therapy in the event of a life-threatening arrhythmia.

At present most ICDs are often using time information from leads to classify rhythms. (Leong, P. H.W &Jabri, M.A November 1995) This means they cannot distinguish some dangerous rhythms from the safe one, as in the case of ventricular-tachycardia arrhythmia. (R. Coggins et al., 1995)

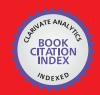

Our chip is used to distinguish between two types of arrhythmia; The Sinus Tachycardia (ST) arrhythmia and the Ventricular Tachycardia (VT) arrhythmia. The ST is a safe arrhythmia occurs during vigorous exercises and is characterized with rate of 120beat/minute. The VT is a fatal arrhythmia with the same rate. They can be separated only by detecting the morphology changes in each one. (Acherya,U,R.,2004)

Most morphology changes are appeared in the QRS-complex. The QRS-complex for both the ST and VT arrhythmia's are shown in fig.1. (Dale Dublin, 2000)

Since most morphology changes are appeared in the QRS-complex, for classifying the arrhythmias we must separate QRS complexes from ECG, consequently a new circuit for detecting QRS is designed. In this circuit the R-R distance between two QRS complexes and also the pulse width of QRS complex are used to improve the detection algorithm.

By using fuzzy logic and some parameters of ECG (pulse width, R-R interval and peak) we can separate QRS complex from ECG and after that apply this part to a Neural Network for classification.

The proposed analog VLSI chip can detect such morphology changes. It has the following advantages:

- It is easily interfaced to the analog signals in an ICD (in contrast to the digital systems which require analog to digital conversion).

- Analog circuits are generally small in area.

- Low voltage circuits are used to decrease battery weight and size and to extend battery life time which required for portable and modern wireless equipment.

- Hamming network did not need to have a training system and the reference vectors determine the weights.

• Although temperature variation is a major source of drift problems, no need for temperature compensation as the human body is considered a stable environment.

Fig. 1. Morphology change of QRS complex for both ST & VT.

This chapter deals with the design of Analog VLSI chip for implantable cardioverter defibrillator (ICDs). We first present the structure of system. Next, we describe each part separately and characteristic of each parts are described. Then, We show the circuits that are used for implementing of each part. Finally, we present the total block diagram of system with some simulations that verifies the functionality of system.

#### 2. Architecture

The proposed chip consists of 3 main parts:

- QRS detector circuit

- Extracting QRS from an ECG circuit

- Classifying QRS complex circuit

First these parts will be explained separately and then the block diagram of the chip will be presented.

#### 2.1 QRS detector circuit

The dominant component of the ECG is the QRS complex, which indicates the electrical depolarization of the muscles in the ventricle of the heart. Several clinical applications including implantable defibrillator require accurate QRS detection algorithms whiles The QRS is easily recognized by a human observer.

Various types of automated algorithms were proposed in the literature for detecting QRS. (K.Akazawa and K.Motoda 2001; Pan.J & Tompkins W.J 1985; Y. Suzuki, 1995) These algorithms use multiple features of the EGG including RR internal, pulse duration and amplitude, to detect QRS complexes. By processing several features, it is less likely that large amplitude but short duration noise would be mistaken for a QRS. Similarly, it is more likely that a true QRS with low amplitude, but normal width and RR internal would be correctly detected.

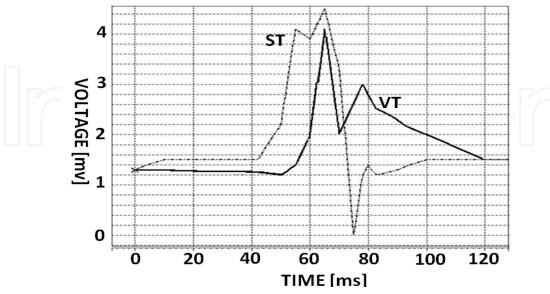

Fuzzy inference systems are well-suited for this application (fig.2), since detection in this system based on a few amounts of uncertainly which is very similar to the medical reasoning process.(O.Wieben, W.J Tompkins & V.X. Afonso 1999) Moreover the decision process is extremely easy to understand by human; consequently such easy interpretability allows external changes by experts on the decision process.

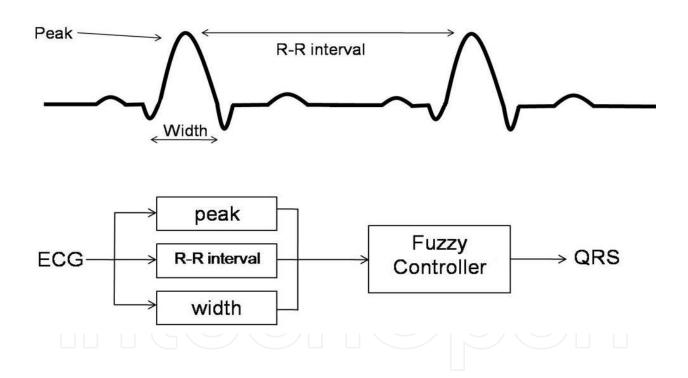

In this work, we are using a fuzzy inference system to identify QRS complexes. In this system QRS complex will be detected provided that a square wave synchronizes with them, consequently we use a fuzzy controller to adjust this square wave with QRS complexes.R-R internal, pulse duration and amplitude are features that enter to a controller as inputs parameter. Fuzzy controller evaluates these features and adjusts the output pulse of VCO to be synchronized with QRS complexes.

Fig. 2. QRS detection algorithm.

A feedback is used to correct the synchronization process. This feedback is produced by error between the output pulse of VCO and the pulse that show the width of QRS complex. This feedback is also enter to controller and processed by fuzzy controller. Finally, the output of fuzzy controller goes to VCO circuit and makes the output pulse of VCO to be synchronized with QRS complex (fig.3).

Fig. 3. QRS detection algorithms that is used in this project.

#### 3. Extracting QRS from an ECG circuit

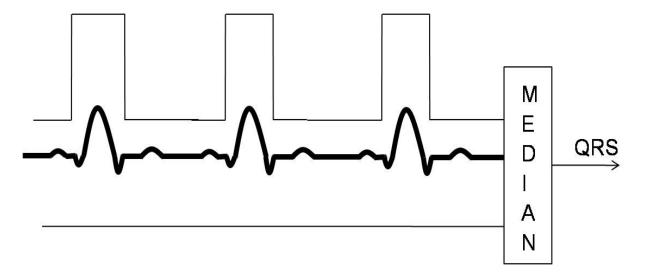

To separate QRS complexes, we passed ECG signals and synchronize VCO trough an analog median filter. (fig.4). Median Filter passes the median part of the input signals which, in this case, is QRS complexes.

Fig. 4. Median Filter.

#### 4. Classifying QRS complexes

The QRS complexes which were detected and separated from the rest of ECG signals are applied to an arrhythmia classifier. This classifier is used to distinguish between two types of arrhythmia: The Sinus Tachycardia (ST) arrhythmia and the Ventricular Tachycardia (VT) arrhythmia. The ST is a safe arrhythmia occurs during vigorous exercises and is characterized with rate of 120beat/minute. The VT is a fatal arrhythmia with the same rate. They can be separated only by detecting the morphology changes in each one.

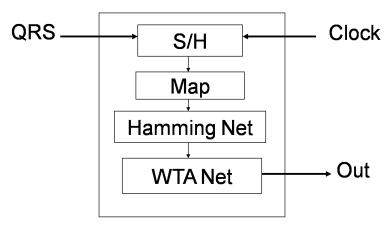

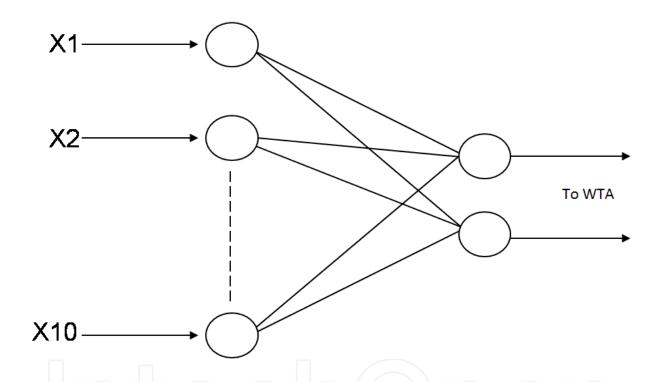

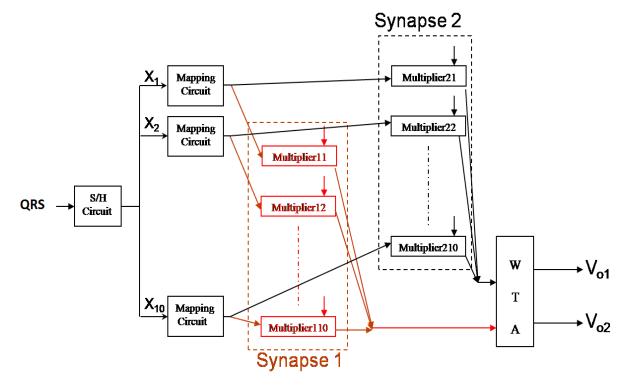

Since the most morphology changes are appeared in the QRS complex, we apply QRS complex to an arrhythmia classifier to classify it. This arrhythmia classifier consists of three building blocks: a sample and hold (S/H) circuit, a mapping circuit and a Hamming neural network classifier. Fig.5 represents a block diagram of the chip. First, the rhythm is inputted to a sample and hold circuit to obtain 10 samples of the input signal. These 10 samples are inputted to mapping circuits in parallel to map into unit length [-1 1]. The outputs of mapping circuits are input to Hamming Neural Network, which has two neurons in its output layer. Each neuron responds to a specified type of the input arrhythmia.

Fig. 5. Block diagram of QRS classifier.

#### 4.1 Hamming Neural Network

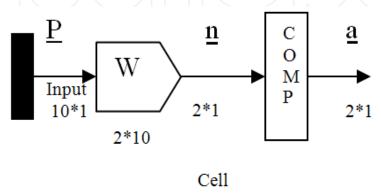

A Neural Network classifier is made of a Hamming network, which is a maximum likelihood classifier network that can be used to determine which of several exemplar vectors are the most similar to an input vector (Laurene Fausett,1994 & M. B. Menhaj,2000). Fig.6 shows the simplest structure of a competitive layer.

Fig. 6. A competitive cell.

$$\underline{a} = comp(W\underline{P}) \tag{1}$$

$$a_i = \begin{cases} 1, & i = i * \\ 0, & i \neq i * \end{cases}$$

(2)

$i^*$  is number of the cell that has the highest  $n_i$  for our application i=1, 2.

In the Hamming Network, reference vector determines the weights (w) of the network. The hamming distance between input vector (P) and reference vector is calculated by <u>n</u> vector (equation 3). (Laurene Fausett, 1994 & M. B. Menhaj, 2000)

Winner cell is determined with multiplying input vector to weights. The largest value corresponds to the smallest angle between input and weights vector if they are both of unit length [-1 1] (Laurene Fausett,1994 & M. B. Menhaj, 2000).

$$\underline{n} = W \underline{P} = \begin{bmatrix} W_{11} & W_{12} & \dots & W_{110} \\ W_{21} & W_{22} & \dots & W_{210} \end{bmatrix} \underline{P} = \begin{bmatrix} \cos \theta_1 \\ \cos \theta_2 \end{bmatrix}$$

(3)

#### 5. Circuit design

The designing method of blocks show in fig.5 is given below:

#### 5.1 Sample and hold (S&H) circuit

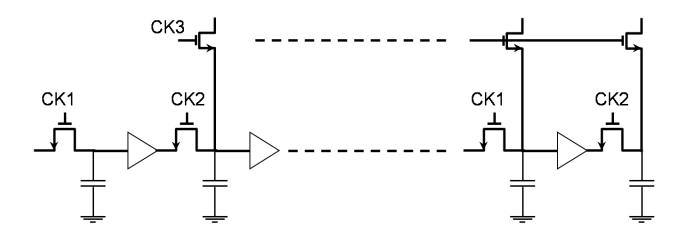

The Sample and hold delay circuit is made of 10 cascaded stages to obtain 10 samples of the input pulse. Fig. 7 shows S/H circuit.

Fig. 7. Three stages of S/H circuit.

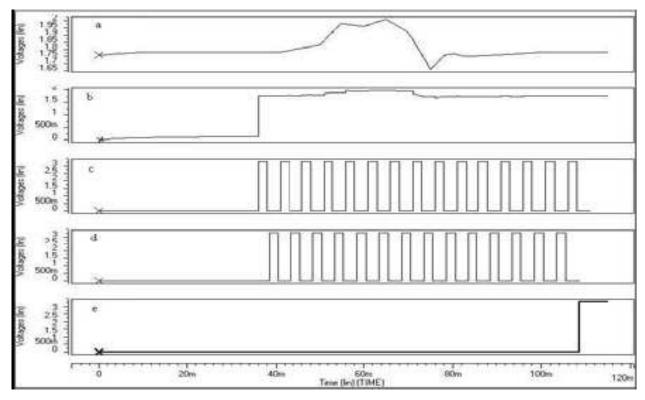

Two-phase non-overlapping clock ( $CK_1$ , $CK_2$ ) is used to control S/H. The sampled signal  $x_i$  then are inputted mapping circuit through another analog switch  $m_i$  controlled by  $CK_3$ . The timing diagram of  $CK_1$ ,  $CK_2$ ,  $CK_3$  and the simulation result of the 1<sup>st</sup> stage of sample and hold circuit are shown in fig. 8.

Fig. 8. (a) Input to S/H circuit. (b) Sampling signal of the 1st stage. (c) CK1. (d) CK2. (e) CK3. In Fig. 8, the input rhythm of ST is applied to the S/H circuit and output of 1st stage is shown.

#### 5.2 Mapping circuit

Before applying sampled data to Neural Network We have to map them into unit length [-1 1]. Figure 9 shows schematic of mapping circuit.

Fig. 9. Mapping circuit.

We use a simple differential pair in order to map input signal (sampled data) to unit length space [-1, 1]. By changing  $V_{ref}$  and W/L ratio of input stage of differential pair, we can map any space to unit length space. (Wilamowski, B 1999)

#### 5.3 Hamming Neural Network classifier

The Hamming Network consists of two groups of synapses and two layers of neurons. The first group with weight vector  $W_1$ = ( $W_{11}$ ,  $W_{12}$ ,  $W_{13}$ , ...,  $W_{115}$ ) is connected to first neuron layer. The second layer with weight vector  $W_2$ = ( $W_{21}$ ,  $W_{22}$ ,  $W_{23}$ , ...,  $W_{215}$ ) is connected to second neuron layer, each neuron in the output layer responds to a specified class of input arrhythmia. Figure 10 shows the structure of Network

Fig. 10. Hamming Neural Network.

#### 5.3.1 Synapse

The computation of inner product between input signal and the local interconnection weight is called synapse and is mostly done by using an analog multiplier.(S. T.Lee; H. Shawkey 1999)

We use a new low voltage low power four quadrant analog multiplier as a synapse. Since output of a synapse is current, output of 10 synapses can be summed at a single node of circuit.

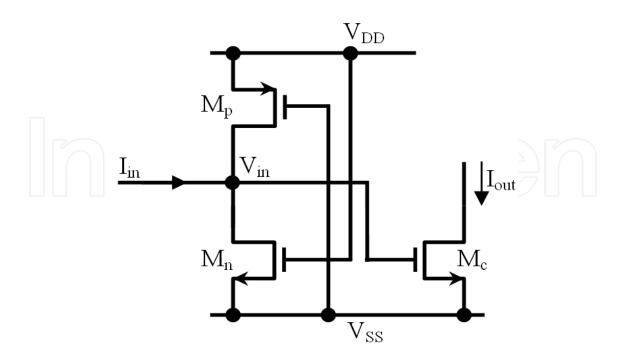

The circuit consists of four quadratic cells is shown in figure 11 where the relationship between the input current,  $I_{in}$ , and the output current,  $I_{out}$ , are quadratic. The quadratic cell is made of two transistors  $M_n$  and  $M_p$  which are biased to operate in triode region and  $M_c$  which operates at saturation region.

Fig. 11. Quadratic cell.

If  $M_n$  and  $M_p$  have the same transconductance,  $\left(k_p = \mu_p C_{ox} \frac{W}{L} = k_n = \mu_n C_{ox} \frac{W}{L} = k\right)$  Then, it can be easily shown that the voltage ( $V_{in}$ ) and the current ( $I_{out}$ ) are given by

$$V_{in} = aI_{in} + b \tag{4}$$

$$I_{out} = k(c + I_{in})^2 \tag{5}$$

$$\text{Where a, b and c are } \frac{1}{k(2V_{DD} - \left|V_{tp}\right| - V_{tn})}, \frac{V_{DD}(V_{tn} - \left|V_{tp}\right|)}{2V_{DD} - \left|V_{tp}\right| - V_{tn}} \ \text{ and } \frac{2V_{DD}(V_{DD} - \left|V_{tp}\right|)}{2V_{DD} - \left|V_{tp}\right| - V_{tn}} - V_{tn}$$

respectively.

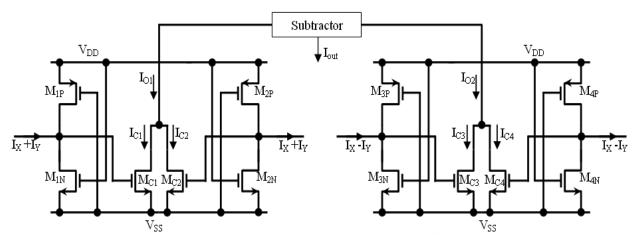

Figure 12 shows the proposed four quadrant current multiplier circuit. The input currents of a multiplier are the sum of currents  $I_X$  and  $I_Y$  and the subtraction of the input currents  $I_X$  and  $I_Y$ . By using quadratic relationship between input and output currents which are derived from Equation (5) drain currents of M  $_{C1}$ , M  $_{C2}$ , M  $_{C3}$  and M  $_{C4}$  would be

$$I_{C1} = k[c + a(I_X + I_Y)]^2$$

(6)

$$I_{C2} = k[c - a(I_X + I_Y)]^2$$

(7)

$$I_{C3} = k[c + a(I_X - I_Y)]^2$$

(8)

$$I_{C4} = k[c - a(I_X - I_Y)]^2 (9)$$

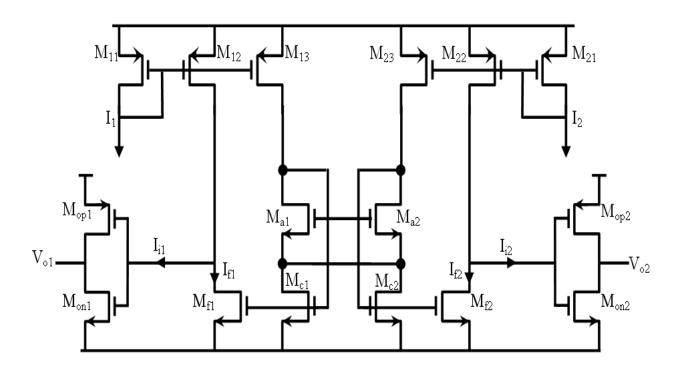

Fig. 12. Multiplier as a synapse.

According to Fig. 12,  $I_{O1}$  is the combination of  $I_{C1}$  and  $I_{C2}$  while  $I_{O2}$  is the combination of  $I_{C3}$  and  $I_{C4}$ .  $I_{O1}$  and  $I_{O2}$  can be shown as

$$I_{O1} = k[2c^2 + 2a^2(I_X + I_Y)^2]$$

(10)

$$I_{O2} = k[2c^2 + 2a^2(I_X - I_Y)^2]$$

(11)

The output current of the four quadrant current multiplier I  $_{out}$  is the difference between  $I_{O1}$  and  $I_{O2}$  and is given by

$$I_{OUT} = I_{O1} - I_{O2} = 8ka^2 I_X I_Y (12)$$

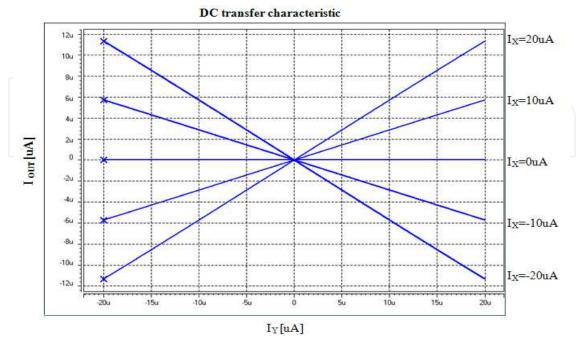

Fig. 13 Shows DC characteristic of current multiplier circuit under input current ranging from -20  $\mu A$  to 20  $\mu A.$

Fig. 13. DC transfer characteristic of four quadrant current multiplier.

#### 5.3.2 Winner take all

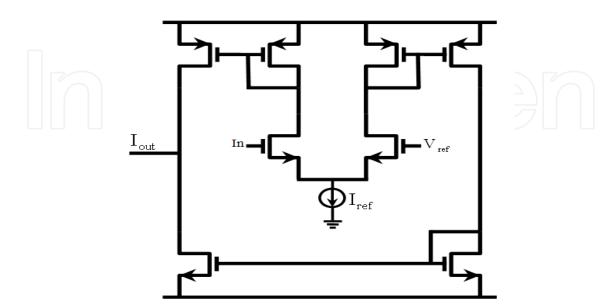

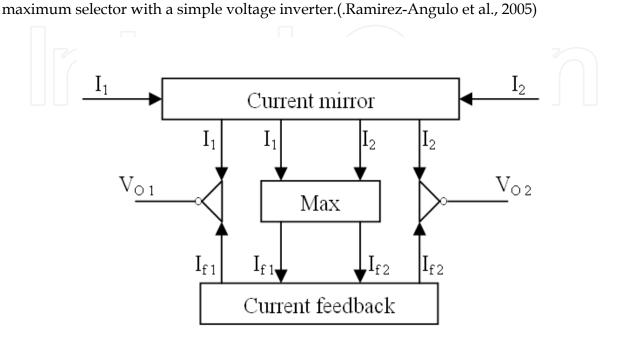

The function of the WTA is to accept input signals, compare their values and produce a high digital output value (logic 'one') corresponding to the largest input, while all other digital outputs are set to low output value (logic 'zero').(J.Ramirez-Angulo et al., 2005) Fig. 14 shows the block diagram of the WTA circuit. The circuit includes a 2-input current

Fig. 14. Winner take all circuit.

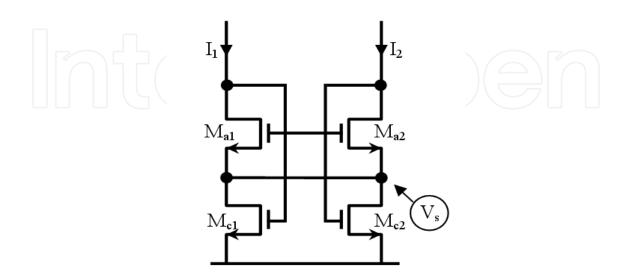

#### 5.3.3 The current max selector

The 2-input current maximum selector is shown in Fig. 15. The proposed current max selector has 2 input branches and each branch consists of an FVF (R.G. Carvajal et al., 2005), which is formed by voltage follower  $M_{\rm ai}$ , and current sensing transistor  $M_{\rm ci}$ .

Fig. 15. 2-input max circuit.

Transistor  $M_{ai}$  in an FVF performs as an improved voltage follower and the Gate-Source voltage drop of this transistor is constant (neglecting second-order effect) and independent of the load.

Transistor  $M_{ci}$  operates as a current sensing device. It can sink large current by keeping its Drain voltage approximately constant. Moreover, the existing impedance at the Source of transistor  $M_{ai}$  is very low due to the feedback loop.

The principle of operation of the circuit is as follow. The voltage at node " $V_S$ " follows the maximum of input currents  $I_1$ ,  $I_2$ , with a DC level shift  $V_{GSn}$  where n denotes the maximum current.

In this condition the transistor ( $M_{a1}$  or  $M_{a2}$ ) which carrying the minimum current, has the greater Gate-Source voltage than the value that should have to operate in saturation mode, at this condition this transistor operates in triode mode with Drain-Source voltage value close to zero, thus the current sensing transistor is turning off in this branch and minimum and maximum currents passed through current sensing transistor of winning branch due to properties of FVF cell.

#### 5.3.4 The overall structure of WTA circuit

The circuit of the 2-input WTA is shown in Fig.16. The currents (I<sub>1</sub>, I2) are the inputs of the circuit.

Each current is mirrored into current max Selector, as well as, into the feedback circuit due to PMOS current mirror  $M_{12}$ ,  $M_{22}$ .

Thus the input current of each voltage inverter is:

Fig. 16. 2-input WTA circuit.

$$I_{i1} = I_1 - I_{f1} \tag{13}$$

$$I_{i2} = I_2 - I_{f2} \tag{14}$$

We assume at the steady state, the current  $I_1$  is the largest input current  $I_1$ =max ( $I_1$ ,  $I_2$ ) So

$$I_{f1} = I_1 + I_2 \tag{15}$$

$$I_{f2} = 0 \tag{16}$$

From the Equation (13) - Equation (16) the input current of each voltage inverter is:

$$I_{i1} = I_1 - (I_1 + I_2) = -I_2 \tag{17}$$

$$I_{i2} = I_2 - 0 = I_2 \tag{18}$$

This means that only one input current of the voltage inverter, which is correspond to minimum current, is positive and all the other currents are negative. Thus the digital voltage outputs of the circuit will be at logic

$$\begin{cases} V_{o1} = 'one' \\ V_{o2} = 'zero' \end{cases}$$

(19)

Fig.17 shows the block diagram of the proposed QRS classifier

Fig. 17. Block diagram of the proposed QRS classifier.

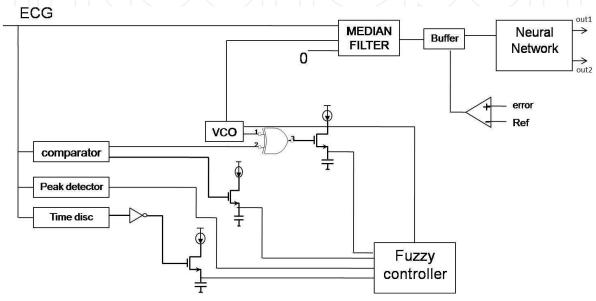

#### 6. The proposed arrhythmia classifier chip

The block diagram of proposed system is presented in fig.18.

In this system, multiple features of ECG are measured by analog circuit. These features are applied to a fuzzy controller to be processed. The output of fuzzy controller goes to a VCO which is used to synchronize the output pulse of VCO with the specific part of ECG. Finally, the QRS complexes which are filtered by median filter are applied to arrhythmia classifier provided that the error of detection algorithm is below a normal value. Moreover, the arrhythmia classifier has 2 outputs that each one responds to a specific type of the input arrhythmia.

Fig. 18. Block diagram of proposed system.

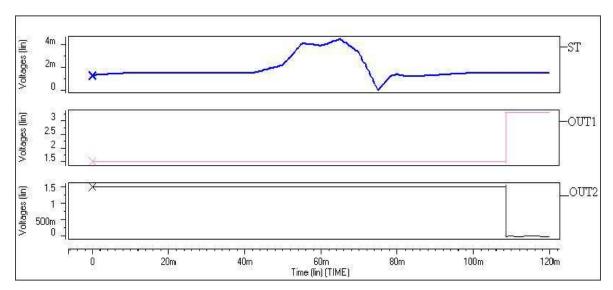

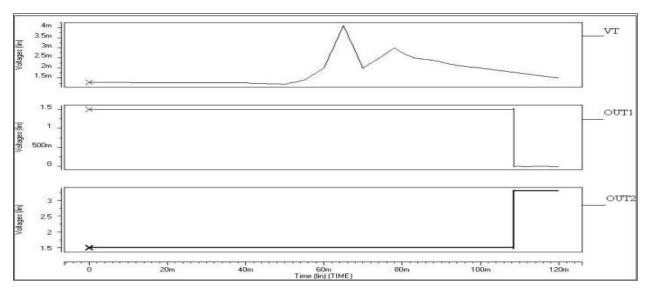

Simulation result of the system in both cases is shown in figure 19 and 20. In fig.19 the inputting rhythm of ST is applied to system caused to digital outputs of OUT1 goes to "One" and OUT2 goes to" Zero".

Fig. 19. Output of system for ST input.

In fig.20 the inputting rhythm of VT is applied to system caused to digital outputs of OUT1 goes to "Zero" and OUT2 goes to "One".

Fig. 20. Output of system for VT input.

#### 7. Conclusion

In this chapter a VLSI Analog chip for arrhythmia classification is presented.

The proposed Network has the following features:

- No need for A/D converter between the ECG and the classification system.

- The system operates in the low frequency range, so that the parasitic of the layout likely have no effect on the operation of the chip.

- This system can be extended to distinguish m types of arrhythmias by using m number of neurons in the output layer of the Hamming Neural Network circuit.

#### 8. References

Leong, P. H.W and Jabri, M.A (November 1995) *A low power VLSI Arrhythmia classifier* IEEE Transaction on Neural Networks volume 6, Page(s):1435-1445

R. Coggins, M. Jabri, B. Flower and S. Pickard (June 1995.) *A low- Power Network for On-Line Diagnosis of Heart Patients* Trans. IEEE Micro, pp. 18-25

Acherya, U,R. (2004) Classification of cardiac abnormalities using heart rate signal Med and Bio Eng, vol 42, P.288-293

Dale Dublin (2000) Rapid Interpretation of EKG McGraw-Hill

O.Wieben, W.J Tompkins and V.X. Afonso (1999) *classification of PVCS with a fuzzy logic system* IEEE Trans. Biomed. Eng,vol 38, pp.561-570,

Y. Suzuki (November 1995) *Self organizing QRS-wave recognition in ECG using neural networks* IEEETrans. Neural network, Vo1.6, No.6, pp. 1469-1477,

Pan.J and Tompkins W.J (1985) *a real-time QRS detection algorithm* IEEE Trans. Biomed. Eng,vol BME 32, n3, pp.230-236

K.Akazawa and K.motoda (September 2001) Adaptive threshold QRS detection algorithm for ambulatory ECG IEEE computer in cardiology, pp.445-448,

- H. Shawkey, H. Elsimary, H. Haddara, H.F. Ragaie, (1999) *Design of a VLSI Neural Network Arrhythmia Classifier* Proceeding of the sixteenth National Radio Science conference, NRSC'99. Egypt, page(s): C 27/1-C 2710

- Laurene Fausett (1994) fundamental of Neural Network. Prentice Hall

- M. B. Menhaj (2000) *Computational intelligence (vol1): Fundamental of Neural Networks,* Amirkabir center of Publishing,

- Behzad Razavi (2000) Design of Analog CMOS integrated circuits, McGraw-Hill,

- Du Chen, John G. Harris, Jose C.Principe (2004) *A Bio-amplifier with pulse output* Proceeding 26<sup>th</sup> Annual international conference of the Engineering in Medicine and Biology Society. EMBC volume2, page(s):4071-4074 vol.6

- Wilamowski, B. M and Jaeger, R.C and Kaynak, M. O(December 1999) *Neuro-Fuzzy Architecture for CMOS Implementation* IEEE Trans Industrial Electronics. Volume 46. Issue 6.page(s):1132-1136

- F. A. Salam and M. R. Choi(1991), Analog MOS Vector multipliers for the implementation of synapses in artificial neural networks Journal of Circuits, Systems, and Computers, vol. 1, no, 2, pp. 205-228.

- S. T.Lee and K. T. Lau (1999) A reconfigurable Low-voltage low-power building block for Artificial Neural Network Proc. Int. Conf. on Neural Networks. Volume 3, page(s): 1478-1481, vol.3.

- S. vlassis and S. siskos (1999) *High speed and high resolution WTA circuit* Proceedings of the 1999 IEEE international symposium on circuits and systems.ICAS'99.volume 2 page(s):224-227

- J.Ramirez-Angulo, G.Ducodray-Acevedo, R. G. Carjaval, A. Lopez-Martin (June 2005) Low-voltage high-performance voltage-mode and current-mode WTA circuit based on flipped voltage followers IEEE Trans. Circuits Syst. II, Express Briefs, vol. 52,no. 7.

- R.G. Carvajal, J. Ramírez-Angulo, A. López-Martin, A.Torralba, J. Galán, A. Carlosena and F. Muñoz1 (July 2005) *The Flipped Voltage Follower: A Useful Cell for Vow-Voltage Low-Power Circuit design* IEEE Transactions on Circuits and Systems I,Vol. 52, No.7

## Cardiac Defibrillation - Prediction, Prevention and Management of Cardiovascular Arrhythmic Events

Edited by Dr. Joyelle Harris

ISBN 978-953-307-692-8

Hard cover, 176 pages

Publisher InTech

Published online 14, November, 2011

Published in print edition November, 2011

Millions of people throughout the world currently depend on appropriate, timely shocks from implantable cardioverter defibrillators (ICDs) to avoid sudden death due to cardiovascular malfunctions. Therefore, information regarding the use, applications, and clinical relevance of ICDs is imperative for expanding the body of knowledge used to prevent and manage fatal cardiovascular behavior. As such, the apt and timely research contained in this book will prove both relevant to current ICD usage and valuable in helping advance ICD technology. This book is divided into three comprehensive sections in order to cover several areas of ICD research. The first section introduces defibrillator technology, discusses determinants for successful defibrillation, and explores assessments of patients who receive defibrillation. The next section talks about predicting, preventing, and managing near catastrophic cardiovascular events, and research presented in the final section examine special cases in ICD patients and explore information that can be learned through clinical trial examinations of patients with defibrillators. Each chapter of this book will help answer critical questions about ICDs.

#### How to reference

In order to correctly reference this scholarly work, feel free to copy and paste the following:

Behzad Ghanavati (2011). Implantable Cardioverter Defibrillators, Cardiac Defibrillation - Prediction, Prevention and Management of Cardiovascular Arrhythmic Events, Dr. Joyelle Harris (Ed.), ISBN: 978-953-307-692-8, InTech, Available from: http://www.intechopen.com/books/cardiac-defibrillation-prediction-prevention-and-management-of-cardiovascular-arrhythmic-events/implantable-cardioverter-defibrillators

# INTECH open science | open minds

#### InTech Europe

University Campus STeP Ri Slavka Krautzeka 83/A 51000 Rijeka, Croatia Phone: +385 (51) 770 447

Fax: +385 (51) 686 166 www.intechopen.com

#### InTech China

Unit 405, Office Block, Hotel Equatorial Shanghai No.65, Yan An Road (West), Shanghai, 200040, China 中国上海市延安西路65号上海国际贵都大饭店办公楼405单元

Phone: +86-21-62489820 Fax: +86-21-62489821 © 2011 The Author(s). Licensee IntechOpen. This is an open access article distributed under the terms of the <u>Creative Commons Attribution 3.0</u> <u>License</u>, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.