## we are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

122,000

135M

Our authors are among the

TOP 1%

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

## Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

### Ultra-Wideband RF Transceiver Design in CMOS Technology

Lingli Xia<sup>1,2</sup>, Changhui Hu<sup>1</sup>, Yumei Huang<sup>2</sup>, Zhiliang Hong<sup>2</sup> and Patrick. Y. Chiang<sup>1</sup> <sup>1</sup>Oregon State University, Corvallis, Oregon <sup>2</sup>Fudan University, Shanghai <sup>1</sup>USA <sup>2</sup>China

#### 1. Introduction

UWB (Ultra-Wideband) is one of the WPAN (Wireless Personal Area Network) Technologies; its main applications include imaging systems, vehicular radar systems and communications and measurement systems. Ever since the FCC released unlicensed spectrum of 3.1-10.6 GHz for UWB application in 2002, UWB has received significant interest from both industry and academia.

Comparing with traditional narrowband WPANs, (e.g. Bluetooth, Zigbee, etc.), the most significant characteristics of UWB are ultra-wide bandwidth (7.5 GHz) and low emitted spectrum density (-41.3 dBm/MHz). According to Shannon-Hartley theorem (Wikipedia, 2010), through an AWGN (Additive White Gaussian Noise) channel, the maximum rate of clean (or arbitrarily low bit error rate) data is limited to

$$C = BW \cdot \log_2\left(1 + \frac{P_S}{N_0 \cdot BW}\right) = BW \cdot \log_2\left(1 + SNR\right)$$

(1)

where, C is the channel capacity, BW is the channel bandwidth,  $P_s$  is the average power of the received signal,  $N_0$  is the noise spectral density. As can be seen from (1), Channel capacity increases linearly with bandwidth but only logarithmically with SNR. With a wide bandwidth, high data rate can be achieved with a low transmitted power.

Mutli-Band OFDM (MB-OFDM) and Direct-Sequence UWB (DS-UWB) are two main proposals for UWB systems; each gained multiple supports from industry. Due to incompatible of these two proposals, UWB technology faces huge difficulties in commercialization. On the other hand, Impulse Radio UWB (IR-UWB) has been a hot research area in academia because of its low complexity and low power.

In the following, we first introduce previous works on different kinds of UWB RF transceiver architectures, including MB-OFDM UWB, DS-UWB and IR-UWB transceivers. Both advantages and disadvantages of these architectures are thoroughly discussed in section 2. Section 3 presents a monolithic 3-5 GHz carrier-less IR-UWB transceiver system. The transmitter integrates both amplitude and spectrum tunability, thereby providing adaptable spectral characteristics for different data rate transmission. The noncoherent

receiver employs a simplified, low power merged-correlator, eliminating the need for a conventional sample-and-hold circuit. After self-correlation, the demodulated data is digitally synchronized with the baseband clock. Section 4 shows the measurement results and section 5 draws a conclusion.

#### 2. Previous works on UWB RF transceivers

Both MB-OFDM (Ranjan & Larson, 2006; Zheng, H. et al., 2007; Bergervoet et al., 2007; Beek et al., 2008) and DS-UWB (Zheng, Y. et al., 2007, 2008) are carrier-modulated systems, where a mixer is used to up/down convert the baseband (BB)/radio frequency (RF) signal, therefore requiring local oscillator (LO) synthesis. The main difference between these two systems is that MB-OFDM systems are dealing with continuous ultra-wideband modulated signals while DS-UWB systems are transmitting discrete short pulses which also occupy ultra-wide bandwidth. On the other hand, IR-UWB is a carrier-less pulse-based system, therefore, the fast hopping LO synthesis can be eliminated, thus reducing the complexity and power consumption of the entire radio. Furthermore, since the signal of a pulse-based UWB system is duty-cycled, the circuits can be shut down between pulses intervals which would lead to an even lower power design.

#### 2.1 MB-OFDM UWB

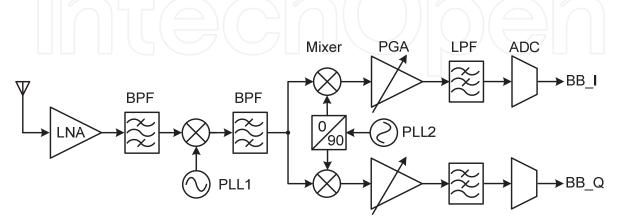

The main architectures of MB-OFDM UWB transceivers can be categorized into superheterodyne transceivers (Ranjan & Larson, 2006; Zheng, H. et al., 2007) and direct-conversion transceivers (Bergervoet et al., 2007; Beek et al., 2008), which are quite similar as those traditional narrow-band RF transceivers.

#### 2.1.1 Superheterodyne transceivers

In a superheterodyne transceiver, the frequency translation from BB to RF in the transmitter or from RF to BB in the receiver is performed twice. A superheterodyne receiver for MB-OFDM UWB is shown in Fig. 1, after being received by the antenna and filtered by an offchip SAW (Surface Acoustic Wave) filter (which is not shown in this figure), the UWB RF signal is down-converted to intermediate frequency (IF) signal first, and then further downconverted to BB signal by a quadrature mixer. Superheterodyne transceiver is a very popular architecture used in communication systems because of its good performance.

Fig. 1. Superheterodyne Receiver

Because of the two-step frequency translation, LO leakage does not have a significant impact on the receiver. Furthermore, multiple filters are employed to get rid of unwanted image and interference signals, which increase the dynamic range, sensitivity and selectivity of the receiver. However, superheterodyne receivers also exhibit significant disadvantages. Firstly, those bandpass filters need high Q to effectively filter out unwanted image and interference signals, which makes these filters difficult to be integrated in CMOS technology and thus off-chip components are employed which increase the cost. Secondly, two-step frequency translation architecture makes superheterodyne receivers less attractive in power consumption and chip area.

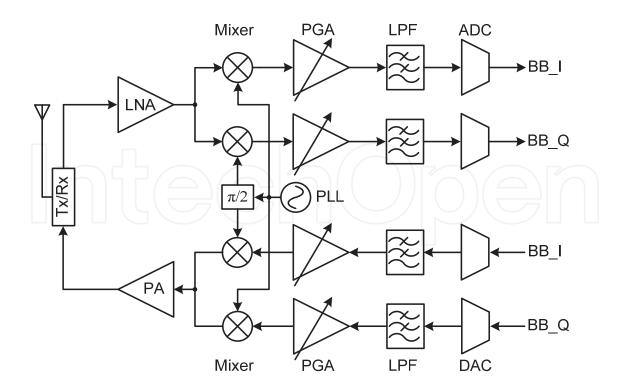

#### 2.1.2 Direct-conversion transceivers

Another more commonly used architecture for MB-OFDM UWB is direct-conversion, as shown in Fig. 2. The RF signal is directly down-converted to a BB signal or vice versa without any intermediate frequency (Gu, 2005), thus expensive IF passive filter can be eliminated, and then the cost and size of the overall transceiver are reduced. And because only one-step frequency translation is needed, the power consumption of a direct-conversion transceiver is much lower than a superheterodyn transceiver. The main problems that limit the application of a direct-conversion transceiver are flicker noise and DC offset. Flicker noise depends on the technology. A PMOS transistor exhibits less flicker noise than a NMOS transistor. DC offset is caused by LO or interference self-mixing, and mismatch in layout. DC offset can be solved by AC coupling or high-pass filtering with a SNR (Signal-to-Noise Ratio) loss. Fortunately, this SNR loss will not be a big issue in a MB-OFDM UWB system since the BB signal bandwidth is as high as 264 MHz.

Fig. 2. Direct-conversion Transceiver

#### 2.2 Pulse-based UWB

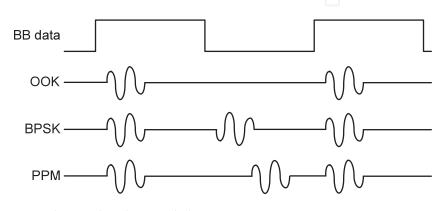

Unlike MB-OFDM UWB systems, pulse-based UWB systems are dealing with discrete pulses. There are many types of pulse modulation, such as OOK (On Off Keying), BPSK (Binary Phase Shift Keying) and PPM (Pulse Position Modulation), etc. As shown in Fig. 3, OOK modulation is performed by generating transmitted pulses only while transmitting '1' symbols. BPSK modulation generates 180° phase-shifted pulses while transmitting baseband symbols '1' and '0'. PPM modulation is performed by generating pulses at different phase delays. Therefore, BPSK has an advantage over other modulation types due to an inherent 3 dB increase in separation between constellation points (Wentzloff & Chandrakasan, 2006); however, BPSK modulation is not suitable for some receiver architectures, e.g., noncoherent receivers.

Fig. 3. Three commonly used pulse modulation

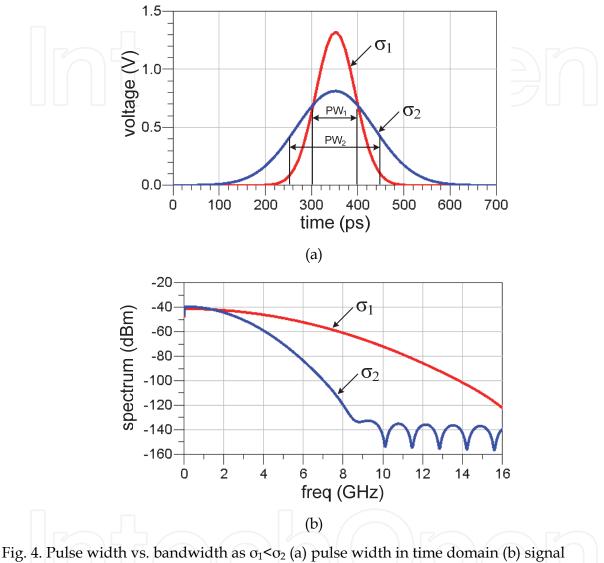

Pulse width is the duty cycle of a pulse in time domain, which is inversely proportional to the pulse bandwidth in frequency domain. The pulse width of a Gaussian pulse is defined as the pulse's temporal width at half of the maximum amplitude. As shown in Fig. 4, Gaussian pulse width is proportional to variance  $\sigma$ , the larger the  $\sigma$  is, the larger the pulse width and the smaller the signal bandwidth. For higher order Gaussian pulses, the pulse width is defined as the temporal width from the first to the last zero-crossing point.

Pulse repetition rate (PRR) is another important characteristic of the transmitted pulse,

$$f_p = n \cdot f_d \tag{2}$$

Where  $f_p$  is the pulse repetition rate,  $f_d$  is the baseband data rate, and n represents how many pulses are generated for each bit of information. If the PRR is doubled by increasing n or  $f_d$ , the transmitted power is elevated by 3 dB. Therefore, the IR-UWB transmitter needs gain control ability in order to satisfy the FCC spectral mask while transmitting at different pulse repetition rate. On the other hand, system throughput is limited by a high n. Therefore, high n is usually employed for low data rate systems where the goal is increased communication distance and improved BER.

Pulse UWB can be categorized into carrier-based DS-UWB (Zheng, Y. et al., 2007, 2008) and carrier-less IR-UWB (Lee, H. et al., 2005; Zheng, Y. et al., 2006; Xie et al., 2006; Phan et al., 2007; Stoica et al., 2005; Mercier et al., 2008). In a carrier-based pulse UWB system, the baseband pulse is up-converted to RF pulse by a mixer at the transmitter side, and vice verse at the receiver side, therefore a power consuming local oscillator is needed. In a carrier-less UWB system, no local oscillator is needed, the transmitted signal is up-converted

to RF band by performing differentiation on a Gaussian pulse; at the receiver side, the received pulse can be demodulated by down-sampling (Lee, H. et al., 2005), coherent (Zheng, Y. et al., 2006; Xie et al., 2006) or noncoherent (Phan et al., 2007; Stoica et al., 2005; Mercier et al., 2008) architectures.

Fig. 4. Pulse width vs. bandwidth as  $\sigma_1 < \sigma_2$  (a) pulse width in time domain (b) signal bandwidth in frequency domain

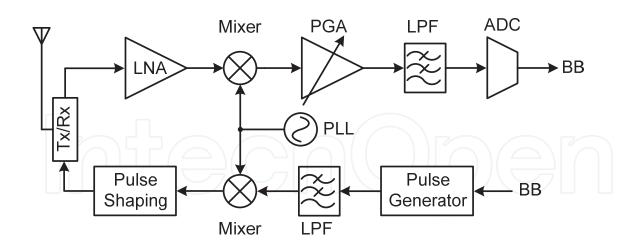

#### 2.2.1 Carrier-based pulse UWB transceivers

Both carrier-based pulse UWB and MB-OFDM UWB need local oscillators to perform frequency translation. As seen in Fig. 5, although these two systems are dealing with different kinds of signals, the receiver side consists of the same blocks as those in Fig. 2. The difference lies in the transmitter side, a pulse UWB transmitter needs no DAC, the digital baseband directly drives a pulse generator to generate a Gaussian pulse, and then the BB pulse is up-converted to RF band and transmitted through a UWB antenna after pulse shaping. Since the transmitted power spectral density is extremely low, power amplifier is optional in UWB systems. Although carrier-based pulse UWB still consumes significant power in LO signal generation, it has advantage in controlling the exact output spectrum.

Fig. 5. Carrier-based pulse UWB

#### 2.2.2 Carrier-less pulse UWB transceivers

Gaussian pulse is the most commonly used pulse shape in IR-UWB systems because of its good performance in frequency domain. The expressions for Gaussian pulse and its first order and second order differentiation are:

$$x(t) = \frac{A}{\sqrt{2\pi\sigma}} \exp(-\frac{t^2}{2\sigma^2})$$

(3)

$$x'(t) = -\frac{At}{\sqrt{2\pi\sigma^3}} \exp(-\frac{t^2}{2\sigma^2})$$

(4)

$$x''(t) = (\frac{At^{2}}{\sqrt{2\pi\sigma^{5}}} - \frac{A}{\sqrt{2\pi\sigma^{3}}})\exp(-\frac{t^{2}}{2\sigma^{2}})$$

(5)

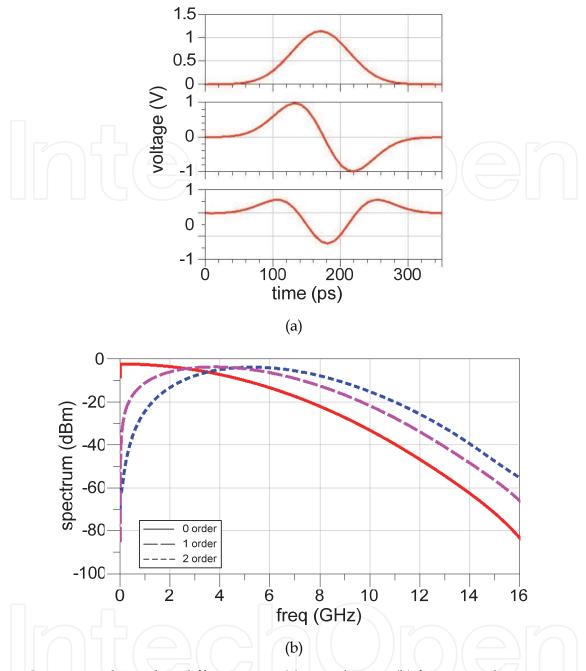

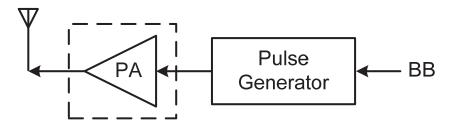

In time domain, the zero-crossing number increases as the differentiation order increases; while in frequency domain, the higher the differentiation order, the higher the center frequency with no significant change on the signal bandwidth, as shown in Fig. 6. Therefore, in an IR-UWB transmitter, frequency conversion is performed by differentiation of a Gaussian pulse, as show in Fig. 7, the transmitter consists of only a high order pulse generator and an optional power amplifier. An IR-UWB transmitter has the advantage of low complexity and low power; however, it also exhibits a big disadvantage of difficulty in controlling the exact output spectrum. Therefore, how to design a transmitter with tunable output spectrum is the main concern in IR-UWB systems.

IR-UWB receivers can be categorized into coherent receivers, noncoherent receivers, and down-sampling receivers. A down-sampling receiver resembles a soft-defined radio receiver. After being amplified by a low noise amplifier, the received signal is directly sampled by an ADC. In a coherent receiver, the received pulse correlates with a local pulse first to down-convert the RF pulse to BB, and then sampled by an ADC while in a noncoherent receiver the received pulse correlates with itself. These three architectures have different field of applications, and they will be discussed in detail in the following.

Fig. 6. Gaussian pulse and its differentiation (a) time domain (b) frequency domain

Fig. 7. IR-UWB transmitter

#### 1. Down-sampling receivers

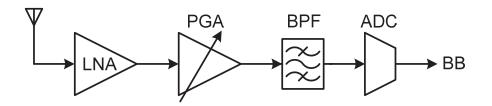

Fig. 8 is a down-sampling receiver (Lee, H. et al., 2005), although at first glance this architecture seems simple, it is seldom used in the 3-10.6 GHz frequency band for several reasons:

- It is very difficult to implement a high gain, ultra-wide bandwidth RF amplifier (at least 60 dB for 10 m transmission range), as it may easily oscillate and also consumes significant power;

- A high Q RF bandpass filter is not trivial. As mentioned earlier in 2.1.1, the requirement of a high Q off-chip BPF increases the cost. This problem also exists in a down-sampling IR-UWB receiver. As can be seen in Fig. 8, the ADC needs a high Q BPF to filter out the out of band interferences and noise to improve the dynamic range and linearity of the receiver and also to relax the stringent requirement on the ADC performance. Furthermore, the ultra-wideband impedance matching of the PGA output and the ADC input is also a big issue if an off-chip BPF is employed.

- A multi-gigahertz sampling rate ADC is very power consuming. According to Shannon theorem, for a signal bandwidth of 2 GHz (3-5 GHz frequency band), at least 4 GHz sampling rate is needed for down-sampling. Although 1 bit resolution may be sufficient (Yang et al., 2005), this ADC consumes significant power in the clock distribution of the high data rate communications.

Fig. 8. Down-sampling IR-UWB receiver

#### 2. Coherent and noncoherent receivers

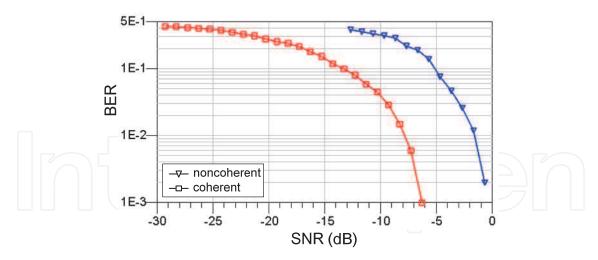

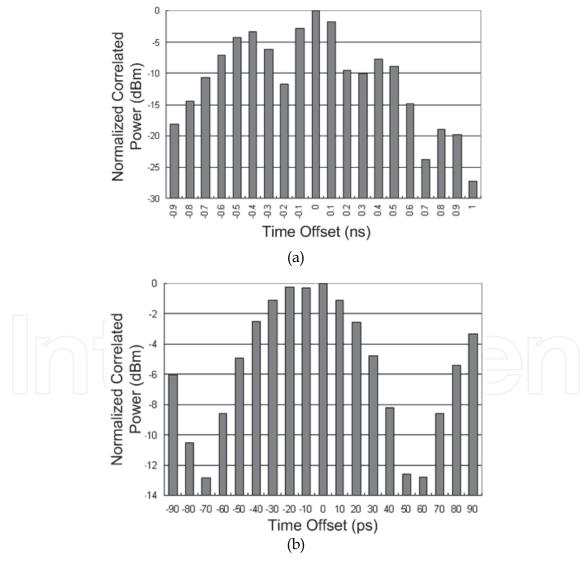

Both coherent and noncoherent receivers correlate the received pulse first, such that the center frequency is down-converted to baseband. The difference is that in a coherent receiver, the received pulse correlates with a local template pulse; in a noncoherent receiver, the received pulse correlates with itself. Therefore, a noncoherent technique exhibits the disadvantage that the noise, as well as signal, is both amplified at the receiver (Stoica et al., 2005). Fig. 9 shows an ADS simulation comparison of the BER performance between a BPSK modulated coherent receiver and an OOK modulated noncoherent receiver within a nonmultipath environment. As observed, a noncoherent receiver requires higher SNR than a coherent receiver for a fixed BER. However, the advantage of a noncoherent receiver is that it avoids the generation of a local pulse as well as the synchronization between the local and received pulses. As shown in Fig. 10, in order to obtain large enough down-converted signals for quantization, the local and received pulses must be synchronized within at least 100 ps in 3-5 GHz frequency band, which would be even tougher in 6-10 GHz frequency band. This precise timing synchronization can be achieved with a DLL or PLL which is very power consuming (Zheng, Y. et al., 2006; Sasaki et al., 2009). However, in a noncoherent receiver, only symbol level synchronization between the baseband clock and received data is needed with a resolution of ns.

Fig. 9. Performance of a coherent receiver and a noncoherent receiver

Fig. 10. Correlated power vs. time offset (between the received and local pulses) in a 3-5 GHz coherent receiver (a) every 100 ps (b) every 10 ps

#### 3. Proposed RF transceiver for IR-UWB systems

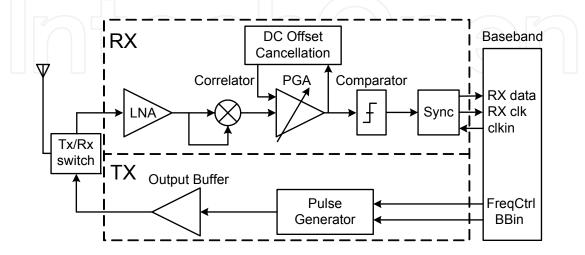

Considering those advantages and disadvantages discussed above, a 3-5 GHz fully integrated IR-UWB transceiver is presented as shown in Fig. 11 (Xia et al., 2011). The transmitter integrates both amplitude and spectrum tunability, thereby providing adaptable spectral characteristics for different data rate transmission. The receiver employs noncoherent architecture because of its low complexity and low power.

Fig. 11. The proposed IR-UWB transceiver system architecture with OOK modulation

#### 3.1 Transmitter

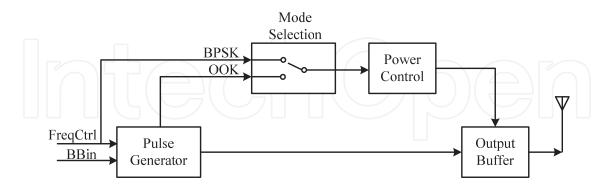

Since a noncoherent receiver detects only the energy of the received pulses rather than the phase of the pulses, BPSK modulation is not suitable for the noncoherent receiver. Hence, the types of possible modulation are limited to OOK and PPM. In this design, OOK modulation is chosen, with BPSK modulation implemented for future coherent receiver design. The detailed transmitter implementation includes a pulse generator, output buffer, mode selection and power control blocks, as shown in Fig. 12.

Fig. 12. The proposed IR-UWB transmitter

#### 3.1.1 Pulse generator

Basically, there are two categories of pulse generators, the analog pulse generator and the digital pulse generator. In (Zheng, Y. et al., 2006), an analog pulse generator is designed employing the square and exponential functions of transistors biased in saturation and weak

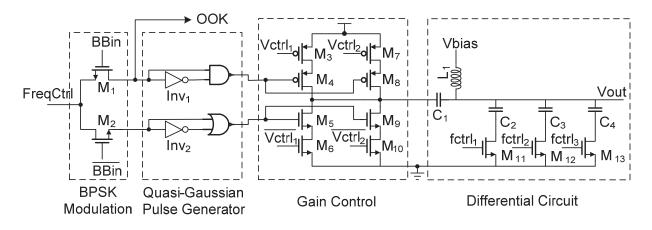

inversion region, respectively. The main disadvantage of this method is that the amplitude of the output pulse is very small; an ultra-wideband amplifier is thus needed. The basic concept of a digital pulse generator is to combine the edges of a digital signal and its inverted signal to form a very short duration pulse, and then a differential circuit is used to up-convert the signal. Except using a differential circuit, (Kim & Joo, 2005) presents another way to up-convert the signal. Four pulses are combined successively to form a fifth derivative Gaussian pulse. This method eliminates the inductor used in the differential circuit which consumes the majority portion of chip area. Unfortunately, this method severely suffers from the process variations. All these previous pulse generators have difficulty in controlling the exact pulse shape and its spectrum. In this design, an amplitude and spectrum tunable pulse generator is introduced to solve this problem (Xia et al., 2008).

Fig. 13. The proposed pulse generator

As can be seen in Fig. 13, BBin is the baseband input signal and FreqCtrl is a square-wave signal that determines the PRR of the transmitted pulses.  $M_1$  and  $M_2$  realize the BPSK modulation as selecting the upper path when BBin is high and selecting the lower path when BBin is low. When OOK modulation is chosen, only those pulses generate by the upper path is sent to the antenna by the power-controlled output buffer.  $M_3$ - $M_{10}$  are employed to implement 3-step amplitude control of the pulses, thereby enabling adaptable output spectral density in order to meet the FCC spectral mask at different data rate. 4-step spectrum control is also realized by control signals fctrl<sub>1-3</sub> showing a measured frequency tuning range of 3.2-4.1 GHz.

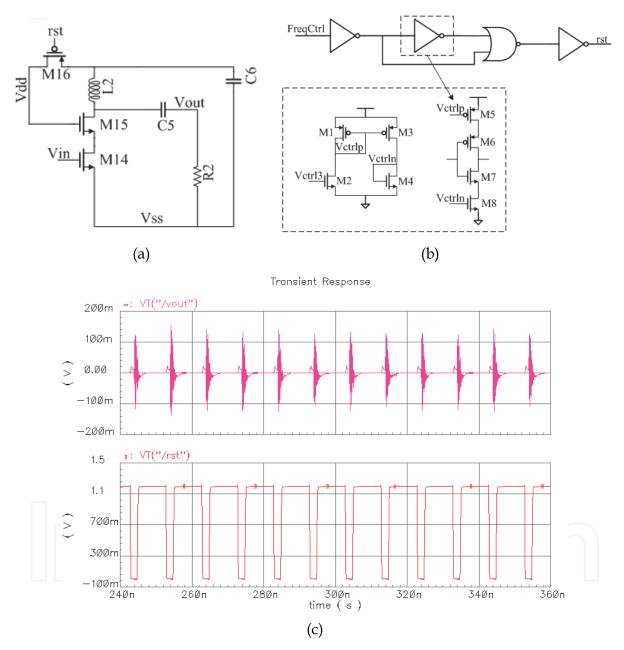

#### 3.1.2 Power-controlled output buffer

Since the transmitted power spectral density of UWB is extremely low, the power amplifier is optional in the transmitter. In this design, an output buffer is implemented to drive the antenna. As shown in Fig. 14(a), the cascode structure is employed to improve the input-output isolation. R2 is the 50 ohms impedance of a UWB antenna. Since the signal of pulse UWB is inherently duty-cycled, the output buffer can be disabled during the pulses intervals to save power. M16 is a large scale PMOS switch with a gate control signal rst generated by the power control block. C6 is a large capacitor to suppress the unwanted pulse generated by switching on/off. The power control block is shown in Fig. 14(b). M5 and M8 are used to control the charging and discharging current, thus controlling the delay time of the inverter. The biasing circuit is also shown in the figure. When BPSK is slected, the power control

block turns the output buffer on before the rising edge of the signal FreqCtrl and lasts for about 2 ns, regardless of whether BBin is high or low, as observed in Fig. 14(c); otherwise, when OOK is selected, the output buffer is enabled only when BBin is high. Therefore, the introduction of the power control block means that the transmitter power consumption is proportional to the data rate.

Fig. 14. Power-controlled output buffer (a) output buffer (b) power control block (c) transient simulation results

#### 3.2 Receiver

The proposed IR-UWB receiver employs the noncoherent receiver architecture as shown in Fig. 11. After first being amplified by the low noise amplifier (LNA), the received pulse is then self-correlated by a correlator, amplified by a programmable gain amplifier (PGA), and

then sent to a comparator for digital quantization. Finally the received data is synchronized with the baseband clock.

#### 3.2.1 Low noise amplifier

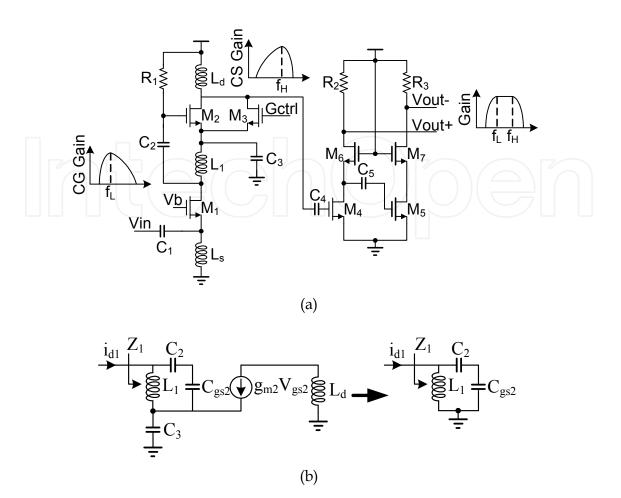

A UWB low noise amplifier needs to provide reasonable noise figure (NF) and impedance matching as well as a very large bandwidth. Hence, the design of a UWB LNA is more challenging than a traditional narrow-band LNA. Furthermore, wideband receivers typically incorporate single-ended inputs (Mastantuono & Manstretta, 2009) that remove the loss of the passive balun but also deteriorate the second-order distortion. In order to compromise these limitations, a single-ended LNA with a following active balun is implemented. As shown in Fig. 15(a), the single-ended LNA employs both current-reuse and staggered tuning techniques - using a common-source stage stacked on top of a common-gate input stage with different resonance frequencies (Weng & Lin, 2007). Inductor L<sub>1</sub> resonates out the parasitic capacitances at the drain of transistor M<sub>1</sub> at 3 GHz while also isolating the source of M<sub>2</sub> from the drain of M<sub>1</sub>. Inductor load L<sub>d</sub> of the common-source stage resonates at 5 GHz such that the output of the LNA covers the frequency range of 3-5 GHz. As shown in Fig. 15(b), the output load of  $M_1$  can be approximated to

$$Z_1 = sL_1 \mid |\frac{1}{sC_c} \tag{6}$$

where,  $C_c = C_2 C_{gs2} / (C_2 + C_{gs2})$ , and the resonance frequency of the common-gate and common-source stages are

$$f_L = \frac{1}{2\pi} \sqrt{\frac{1}{L_1 C_c}} \tag{7}$$

$$f_H = \frac{1}{2\pi} \sqrt{\frac{1}{L_d C_x}} \tag{8}$$

where,  $C_x = C_{gd2} + C_{gd3} + C_{gs4}$ . Transistor M<sub>3</sub>, which is parallel with M<sub>2</sub>, provides gain control tunability. If M<sub>3</sub> is switched on, the bias current for M<sub>1</sub> increases, thereby increasing g<sub>m1</sub>. The measured gain variation of the high gain and low gain mode is 7.5 dB.

A two-cascode stage active balun is used to convert the single-ended output of the LNA to differential signals. The output of M<sub>4</sub> connects to M<sub>6</sub> and the input of the second cascode. Since  $v_{gs5}$ =- $v_{gs6}$ , two balanced differential outputs can be achieved if  $g_{m5}$ = $g_{m6}$ . The maximum gain and phase mismatch of the balanced outputs in 3-5 GHz are 0.3 dB and 2.8°, respectively, as observed from post-extracted layout simulation.

#### 3.2.2 Correlator

The output of the LNA must be correlated - multiplied and then integrated in order to detect the energy of the received signal. Previous correlators used in both coherent receivers (Zheng, Y.et al., 2006, Liu et al., 2009) and noncoherent receivers (Lee, F.S. et al., 2007) needs

Fig. 15. Low noise amplifier and active balun (a) circuit implementation (b) small signal model of  $Z_1$

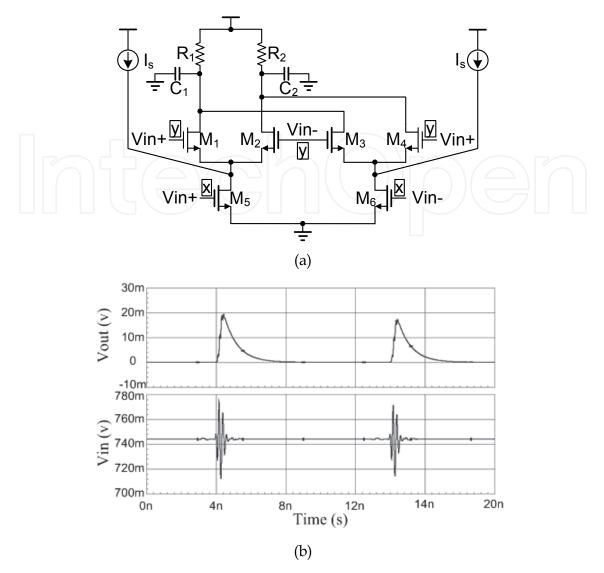

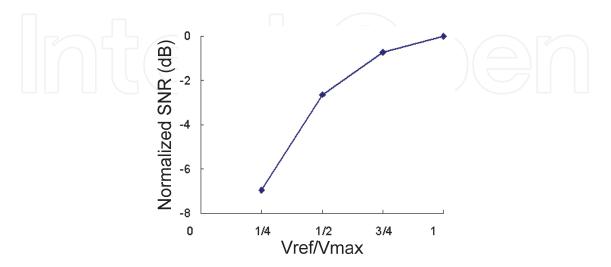

to synchronize the received pulse with local controlling signals first. This synchronization process is analogous to the RF front-end synchronization in a coherent receiver requiring a strict timing resolution. In this design, the duty-cycled characteristic of the IR-UWB system is used to remove the timing synchronization. Fig. 16(a) presents the proposed multiplier and integrator-merged correlator. The multiplier employs a Gilbert topology, while the integrator is realized by capacitors  $C_1$  and  $C_2$ . As shown in Fig. 16(b), after the pulse is multiplied with itself, the integrator begins to integrate, and between the pulses intervals, the integrator starts to discharge and ready for the next integration. C<sub>1</sub> and C<sub>2</sub> should be large enough to hold the integrated voltage for the comparator and yet small enough to discharge between pulses intervals in order to be ready for the next integration. The main limitation of the proposed correlator is that in order to get quantized signal with enough duty cycle, the reference voltage level of the comparator must be set to a lower level than that for a conventional correlator, inevitably sacrificing SNR of the receiver. As shown in Fig. 17, Vref and Vmax represent the reference voltage of the comparator and the maximum output voltage of the correlator, respectively. The SNR reduces by 2.64 dB as Vref is set to half of the Vmax. However, implementation complexity and power consumption are greatly reduced with the proposed technique and the noise introduced by sampling can be eliminated. Furthermore, this SNR reduction can be relaxed by introducing a proceeding programmable gain amplifier.

Fig. 16. Correlator (a) circuit implementation (b) simulation result

Fig. 17. SNR reduction due to the proposed correlator

#### 3.2.3 Programmable gain amplifier

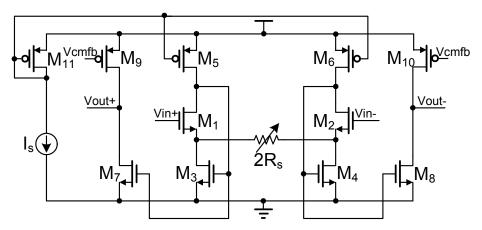

The PGA is critical in the receiver in order to increase the dynamic range of the system and also complement the SNR reduction in the proposed correlator. The proposed PGA consists of a fixed gain stage, an 8-step gain stage and a DC-offset cancellation circuit. Fig. 18 shows the 8-step wideband source degeneration programmable gain stage. The transconductance of the first stage is  $1/(Rs_1+Rs)$ , in which  $Rs_1$  is the resistance looking into the source of  $M_1$ . By varying the value of Rs, a variable gain is realized. The linearity of this amplifier is determined by  $Rs_1$ , where a smaller  $Rs_1$  results in better linearity performance. In Fig. 18, a negative feedback through  $M_3$  is employed (Helleputte et al. 2009), allowing  $Rs_1$  to be reduced to  $g_{o1}/(g_{m1}g_{m3})$ , greatly improving the linearity. The degeneration resistance Rs is controlled by 3-bit digital words to realize the 8-step gain control, with a minimum step size of 3 dB.

Fig. 18. 8-step programmable gain amplifier

#### 3.2.4 Comparison and synchronization

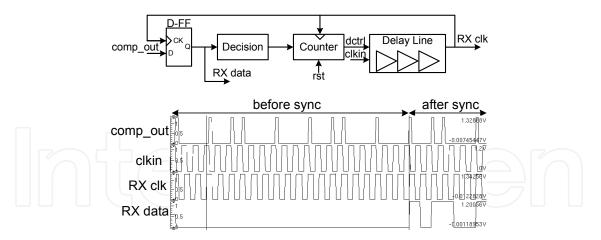

After the received signal is squared and integrated by the correlator, a comparator compares it with a reference voltage and performs digital quantization. However the comparator output is a return-to-zero (RZ) signal which needs to be converted to a non-return-to-zero (NRZ) signal that can synchronize with the baseband clock. In a coherent receiver, a DLL/PLL is usually introduced to perform synchronization between the received pulse and the local pulse, needing precision on the order of several tens of picoseconds. However, in a noncoherent receiver, the RZ signal quantized by the comparator exhibits a duty cycle on the order of ns. Therefore, a low jitter DLL/PLL is no longer necessary and a sliding correlator is employed. The digital synchronization circuit is shown in Fig. 19, where clkin, comp\_out, RX clk and RX data are the baseband clock, the comparator output, the recovered baseband clock and the recovered data, respectively. With a reset signal, the delay line control signal dctrl is set to 0, such that there is no delay between the RX clk and clkin. Then the Sync block starts operation, and RX clk samples comp\_out. If the RX clk is not synchronized with comp\_out, the decision block enables the counter that increases the value of dctrl -- thus elongating the latency of the delay line until RX clk and comp\_out are synchronized. The inevitable frequency offset between the baseband clock of the transmitter and receiver can be compensated by the digital baseband circuit, which is out of the discussion of this paper. During the measurement, the same clock source is used to get rid of the frequency offset.

Fig. 19. Clock and data synchronization

#### 4. Measurement results

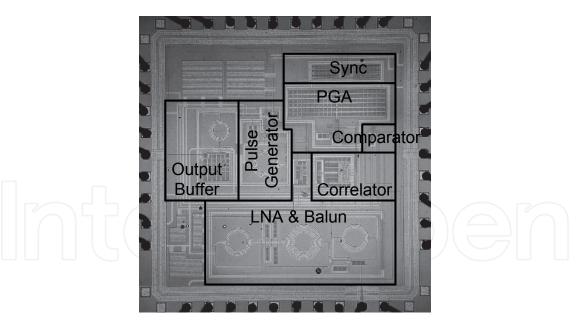

The proposed IR-UWB transceiver is implemented in a 0.13  $\mu$ m 1P8M CMOS technology. The transceiver die microphotograph is shown in Fig. 20. The die area is 2 mm×2 mm. The chip is bonded to the 4-layer FR-4 PCB with chip-on-board (COB) assembly. With a supply voltage of 1.2 V, the power consumption of the transmitter is only 1.2 mW and 2.2 mW when transmitting 50 Mb/s and 100 Mb/s baseband signals, respectively; the power consumption of the receiver is 13.2 mW.

Fig. 20. Microphotograph of IR-UWB transceiver

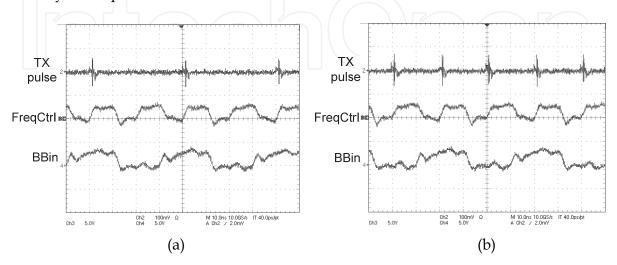

Fig. 21 shows OOK and BPSK modulated pulses. Baseband data (BBin) and clock (FreqCtrl) are generated by FPGA, and the output of the transmitter is measured with high sampling rate oscilloscope. As can be seen, with OOK modulation, pulses are generated only when transmitting symbols '1'; and with BPSK modulation, pulses are generated every clock cycle with polarity shift depending on the transmitting symbols. The amplitude and spectrum tunable transmitter has output pulses with peak-to-peak voltage of 240 mV, 170 mV and 115

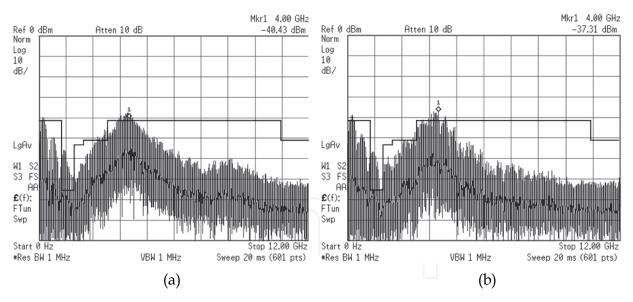

mV and the frequency center of the spectrum has a tuning range of 3.2-4.1 GHz. Fig. 22 shows the transmitted spectrum with pulse amplitude of 240 mV at data rate of 50 Mb/s and 100 Mb/s, respectively. As can be seen, the transmitted power increases by approximately 3 dB while the data rate is doubled. Hence, the amplitude of the transmitted pulses should be optimized in order to meet the FCC spectral density. The transmitted power at low frequency range is introduced by the switch in output buffer, and it can be filtered by off-chip filter and UWB antenna.

Fig. 21. OOK/BPSK transmitter (a) OOK modulation (b) BPSK modulation

Fig. 22. Transmitted Spectrum with maximum pulse amplitude at data rate of (a) 50 Mb/s (b) 100 Mb/s

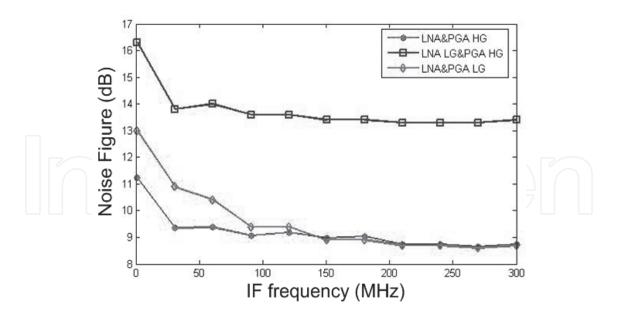

The receiver provides a total gain ranging 43-70 dB, in which the LNA exhibits a gain variation of 7.5 dB in high/low gain mode; the PGA incorporates an 8-step, 3-dB gain control with an rms error of 0.7 dB. The receiver shows a minimum noise figure of 8.6/13.3 dB while operating in high/low gain mode, with a noise figure variation less than 2 dB in the 3-5GHz frequency band, as shown in Fig. 23. The 1-dB compression point of the receiver is -28/-22 dBm in high/low gain mode.

109

Fig. 23. Noise figure of the receiver

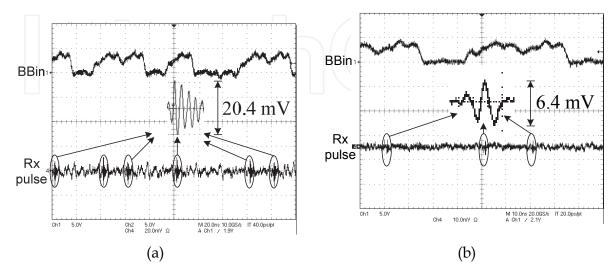

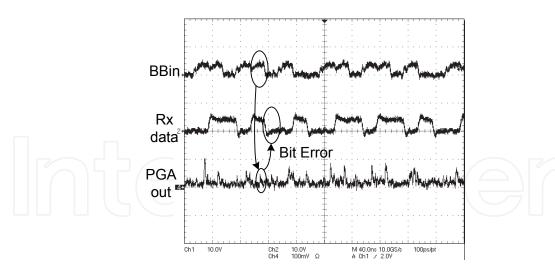

BER performance of the receiver with n of 1 is measured by transmitting 50 Mb/s random data from FPGA. The employed antennas are 3-5 GHz monopole omnidirectional antennas, manufactured by Fractus Corporation. As can be seen in Fig. 24, with transmitted amplitude of 115 mV, the received pulses are attenuated to only 20.4 mV (-50 dBm) and 6.4 mV (-61 dBm) when the distance between the antennas is 1 cm and 10 cm, respectively. The receiver achieves a BER of 10<sup>-3</sup> when the distance between the antennas is set to 1 cm (-50 dBm). While the distance extends to 10 cm (-61 dBm), the BER performance is greatly deteriorated to over 10<sup>-2</sup>. As shown in Fig. 25, the TX pulse is OOK modulated, every pulse represents bit 1 at baseband. The received pulses are correlated and then amplified by the PGA, where PGA out is the buffered output of the PGA. A bit error occurred in the synchronized RX data as the received pulses are distorted by the antennas and the transmission channel.

Fig. 24. Received pulses (a) 1 cm (b) 10 cm

Fig. 25. BER performance of the receiver when the distance between the antennas is 10 cm A summary of the measured results and a comparison with previously published papers is shown in Table 1.

| Paper              | Zheng, Y. et al. | Mercier et al. 2009   | Crepaldi, M. et al.      | This work        |

|--------------------|------------------|-----------------------|--------------------------|------------------|

| ruper              | 2006             | Lee, F.S. et al. 2007 | 2010                     |                  |

| <b>D</b> 1         |                  |                       |                          |                  |

| Band               | 3-5 GHz          | 3-5 GHz               | 3.6-4.3 GHz              | 3-5 GHz          |

| Data rate          | 400 Mb/s         | 16.7 Mb/s             | 1 Mb/s                   | 100 Mb/s         |

| Modulation         | PPM              | PPM                   | S-OOK                    | OOK              |

| TX pulse           | 195 mVpp         | 370 mVpp              | 610 mVpp                 | 240 mVpp         |

| amp.               |                  |                       |                          |                  |

| TX                 | 1.5 ns           | /                     | 2.0 ns                   | 1.0 ns           |

| pulsewidth         |                  |                       |                          |                  |

| RX Arch.           | coherent         | noncoherent           | noncoherent              | noncoherent      |

| RX NF              | 7.7-8.1 dB       | 8.5-9.5 dB            | /                        | 8.6 dB           |

| RX Gain            | 83.5 dB          | 40 dB                 | /                        | 70 dB            |

| IP <sub>1-dB</sub> | -22 dBm          | -45 dBm               | /                        | -28 dBm          |

| Sensitivity        | -80~-72 dBm      | -99 dBm @10-3         | -60∼-66 dBm@10-3         | -50 dBm @10-3    |

|                    |                  |                       |                          | -61 dBm @10-2    |

| Power              | 0.19nJ/pulse(TX) | 43pJ/pulse(TX)        | 65pJ/pulse+184           | 22pJ/pulse(TX)   |

| Consumption        | 0.2nJ/pulse(RX)  | 2.5nJ/pulse(RX)       | μŴ(TX)                   | 0.13nJ/pulse(RX) |

|                    |                  |                       | 134.5pJ/pulse(RX)        |                  |

| Chip Area          | 2.6 mmx1.7 mm    | 0.2mmx0.4mm(TX)       | 0.6 mm <sup>2</sup> (TX) | 2 mmx2 mm        |

|                    |                  | 1 mmx2.2 mm(RX)       | 1 mm <sup>2</sup> (RX)   |                  |

| Process            | 0.18 µm CMOS     | 90 nm CMOS            | 90 nm CMOS               | 0.13 µm CMOS     |

Table 1. Summary of the transceiver performance and comparison

#### 5. Conclusion

A low power 3-5 GHz IR-UWB transceiver system with maximum data rate of 100 Mb/s is presented in this paper. The power consumption of the transmitter and receiver is 22 pJ/pulse and 0.13 nJ/pulse, respectively. The transmitter implementation is based on a

former design and can realize OOK/BPSK modulation, where both the amplitude and spectrum of the output pulses are tunable. The introducing of a power control block in transmitter improves the power efficiency of the output buffer. In the receiver, a noncoherent technique is adopted for its low power and low complexity. A single to differential LNA with active balun is designed to eliminate off-chip balun. The correlator eliminates the sample-and-hold circuit to greatly simplify the circuit implementation. At baseband front-end, a synchronization circuit is implemented to have the data and clock synchronized at the output of the receiver. However, the duty-cycled characteristic of IR-UWB system is not utilized in the receiver to further reduce the power consumption. And lacking of low pass filter in the receiver could also deteriorate the performance. These should be improved in the future research.

#### 6. Acknowledgment

This work was supported by 863 project of China under Grant SQ2008AA01Z4473469.

#### 7. References

- Beek, R.; Bergervoet J.; Kundur, H. et al. (2008). A 0.6-to-10GHz receiver front-end in 45nm CMOS, *IEEE International Solid-State Circuits Conference*, 2008, pp. 128-129

- Bergervoet, J.R.; Harish, K.S.; Lee, S. et al. (2007). A WiMedia-compliant UWB transceiver in 65nm CMOS, *IEEE International Solid-State Circuits Conference*, 2007, pp. 112-113

- Crepaldi, M. et al. (2010). An Ultra-low-power interference-robust IR-UWB transceiver chipset using self-synchronizing OOK modulation", *IEEE International Solid-State Circuits Conference*, 2010, pp. 226-227

- Gu Q. (2005). *RF system design on transceivers for wireless communications*, Springer, ISBN 0-387-24161-2, United States of America

- Helleputte, N.V. & Gielen G. (2009). A 70 pJ/pulse analog front-end in 130 nm CMOS for UWB Impulse Radio Receivers, IEEE Journal of Solid-State Circuits, Vol. 44, No. 7, July 2009, pp. 1862-1871

- Kim, H.; Joo, Y. (2005). Fifth-derivative Gaussian pulse generator for UWB system, *IEEE Radio Frequency Integrated Circuits Symposium*, 2005, pp.671-674

- Lee, F.S. & Chandrakasan, A.P. (2007). A 2.5 nJ/b 0.65V 3-to-5GHz subbanded UWB receiver in 90nm CMOS, *IEEE Journal of Solid-State Circuits*, 2007, pp. 116-117

- Lee, H.; Lin, C.; Wu, C. et al. (2005). A 15mW 69dB 2Gsample/s CMOS analog front-end for low-band UWB applications, *IEEE International Symposium on Circuits and Systems*, 2005, pp. 368-371

- Liu, L.; Sakurai, T. & Takamiya M. (2009), A 1.28mW 100Mb/s impulse UWB receiver with charge-domain correlator and emedded sliding scheme for data synchronization, *Symposium on VLSI Circuits*, 2009, pp. 146-147

- Mastantuono, D. & Manstretta D. (2009). A Low-noise active balun with IM2 cancellation for multiband portable DVB-H receivers, *International Solid-State Circuits Conference*, 2009, pp. 216-217

- Mercier P.P.; Daly, D.C.; Bhardwaj, M. et al. (2008). Ultra-low-power UWB for sensor network applications, *IEEE International Symposium on Circuits and Systems*, 2008, pp. 2562-2565

- Phan, T.; Krizhanovskii, V. & Lee, S.G. (2007). Low-power CMOS energy detection transceiver for UWB impulse radio system, *IEEE Custom Integrated Circuits Conference*, 2007, pp. 675-678

- Ranjan, M. & Larson, L. (2006). A sub-1mm2 dynamically tuned CMOS MB-OFDM 3-to-8GHz UWB receiver front-end, IEEE International Solid-State Circuits Conference, 2006, pp. 128-129

- Sasaki, N.; Kimoto, K.; Moriyama, W. et al. (2009). A single-chip ultra-wideband receiver with silicon integrated antennas for inter-chip wireless interconnection, *IEEE Journal of Solid-State Circuits*, Vol. 44, No. 2, February 2009, pp. 382-392

- Stoica, L.; Rabbachin, A.; Repo, H.O. et al. (2005). An ultrawideband system architecture for tag based wireless sensor networks, *IEEE Transactions on Vehicular Technology*, Vol. 54, No. 5, September 2005, pp. 1632-1645

- Weng, R. & Lin P. (2007). A 1.5-V low-power common-gate low noise amplifier for ultrawideband receivers, *International Symposium on Circuits and Systems*, 2007, pp. 2618-2621

- Wentzloff, D.D. & Chandrakasan, A.P. (2006). Gaussian pulse generators for subbanded ultra-wideband transmitters, *IEEE Transactions on Microwave Theory and Techniques*, Vol. 54, No. 4, April 2006, pp. 1647-1655

- Wikipedia. (2010). Shannon-Hartley theorem, http://en.wikipedia.org/wiki/Ultrawideband

- Xia, L; Huang, Y. & Hong, Z. (2008). Low power amplitude and spectrum tunable IR-UWB transmitter, *Electronics Letter*, Vol. 44, No. 20, September 2008, pp. 1200-1201

- Xia, L.; Shao, K.; Chen, H. et al. (2010). 0.15-nJ/b 3-5-GHz IR-UWB system with spectrum tunable transmitter and merged-correlator noncoherent receiver, *IEEE Transactions* on Microwave Theory and Techniques, Vol. 59, No. 4, April 2011, pp. 1147-1156

- Xie, H.L.; Fan, S.Q.; Wang, X. et al. (2006). An ultra-low power pulse-based UWB transceiver SoC with on-chip ADC, *IEEE International Midwest Symposium on Circuits and Systems*, 2006, pp. 669-673

- Yang, C.; Chen, K. & Chiueh, T. (2005). A 1.2V 6.7mW impulse-radio UWB baseband transceiver, *International Solid-State Circuits Conference*, 2005, pp. 442-443

- Zheng, H.; Lou, S.; Lu, D. et al. (2007). A 3.1-8.0GHz MB-OFDM UWB transceiver in 0.18μm CMOS, *IEEE Custom Integrated Circuits Conference*, 2007, pp. 651-654

- Zheng, Y.; Tong, Y.; Ang, C.W. et al. (2006). A CMOS carrier-less UWB transceiver for WPAN applications, *IEEE International Solid-State Circuits Conference*, 2006, pp. 116-117

- Zheng, Y.; Wong, K.W.; Asaru, M.A. et al. (2007). A 0.18µm CMOS dual-band UWB transceiver, *IEEE International Solid-State Circuits Conference*, 2007, pp. 114-115

- Zheng, Y.; Arasu, M.A; Wong, K.W. et al. (2008). A 0.18µm CMOS 802.15.4a UWB transceiver for communication and localization, *IEEE International Solid-State Circuits Conference*, 2008, pp. 118-119

112

Ultra Wideband Communications: Novel Trends - System, Architecture and Implementation Edited by Dr. Mohammad Matin

ISBN 978-953-307-461-0 Hard cover, 348 pages Publisher InTech Published online 27, July, 2011 Published in print edition July, 2011

This book has addressed few challenges to ensure the success of UWB technologies and covers several research areas including UWB low cost transceiver, low noise amplifier (LNA), ADC architectures, UWB filter, and high power UWB amplifiers. It is believed that this book serves as a comprehensive reference for graduate students in UWB technologies.

#### How to reference

In order to correctly reference this scholarly work, feel free to copy and paste the following:

Lingli Xia, Changhui Hu and Patrick Chiang (2011). Ultra Wideband RF Transceiver Design in CMOS Technology, Ultra Wideband Communications: Novel Trends - System, Architecture and Implementation, Dr. Mohammad Matin (Ed.), ISBN: 978-953-307-461-0, InTech, Available from: http://www.intechopen.com/books/ultra-wideband-communications-novel-trends-system-architecture-andimplementation/ultra-wideband-rf-transceiver-design-in-cmos-technology

# Open science | open minds

#### InTech Europe

University Campus STeP Ri Slavka Krautzeka 83/A 51000 Rijeka, Croatia Phone: +385 (51) 770 447 Fax: +385 (51) 686 166 www.intechopen.com

#### InTech China

Unit 405, Office Block, Hotel Equatorial Shanghai No.65, Yan An Road (West), Shanghai, 200040, China 中国上海市延安西路65号上海国际贵都大饭店办公楼405单元 Phone: +86-21-62489820 Fax: +86-21-62489821 © 2011 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the <u>Creative Commons Attribution-NonCommercial-ShareAlike-3.0 License</u>, which permits use, distribution and reproduction for non-commercial purposes, provided the original is properly cited and derivative works building on this content are distributed under the same license.