We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

122,000

Our authors are among the

TOP 1%

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

### Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

### High Performance Organic Thin-Film Transistors and Nonvolatile Memory Devices Using High-κ Dielectric Layers

Albert Chin National Chiao-Tung University Taiwan, ROC

#### 1. Introduction

Pentacene-based organic thin-film transistors (OTFT<sub>S</sub>) are attractive because of their inherit merits of low cost, small weight and visible-light transparency, for potential use in applications such as organic displays, flexible displays and low-cost integrated circuit (IC) (Klauk et al, 1999; Zhou et al, 2005). The low thermal budget and rapid processing have strong advantages of energy saving and environment friendly (Chang et al, 2008), which are in sharp contrast to the prolonged 600°C annealing in conventional solid-phase crystallized (SPC) poly-crystalline silicon (poly-Si) TFTs (Hung et al, 2005). Although low thermal budget poly-Si TFTs can also be formed on plastic substrate using excimer laser annealing (Lemmi et al, 2004), the uniformity of threshold voltage ( $V_t$ ) and mobility are the major concerns for TFTs on different poly-Si grains. Alternatively, although even single crystal sub-µm MOSFETs can be realized on plastic substrate (Kao et al, 2005) by fabrication first, thinning down the substrate, transferring and bonding, this method still requires high thermal budget for device fabrication.

However, conventional OTFTs require a high operating voltage and show a poor subthreshold swing, which are opposite to the low power technology trend and detract from their suitability in IC operation. Besides, the relative low transistor current is difficult to drive the need high operation current of organic light-emitting diode (OLED). To address these issues, high dielectric constant ( $\kappa$ ) material is required for OTFTs to improve the device performance. Using high- $\kappa$  HfLaO as the gate dielectric, the pentacene OTFTs fabricated on SiO<sub>2</sub> showed even comparable device performance with SPC poly-Si TFTs, with extra merit of much better sub-threshold swing for low voltage and low power application (Chang et al, 2008). Similar good device performance was also achieved using high- $\kappa$  HfLaO on pentacene OTFTs, fabricated on low-cost flexible polyimide substrates and useful for portable low power electronics (Chang et al, 2009).

Besides the logic TFTs, non-volatile memory function is also necessary for system-on-panel (SOP) application (Yin et al, 2008). Previously, OTFT memory devices have been reported using polymer insulators as the charge trapping layer (Baeg et al, 2006). Nevertheless, the OTFT memory devices require low program/erase (P/E) voltages, low reading voltages and

long data retention. Using the high- $\kappa$  dielectrics for pentacene non-volatile memory fabricated on flexible polyimide substrate, low P/E voltage and reasonable long data retention were reached (Chang et al, 2008). The low P/E voltage results from the high gate capacitance using high- $\kappa$  layers, while the small band-gap high- $\kappa$  HfON trapping layer with deep trapping energy yields acceptable data retention. Further performance improvement of OTFT-based non-volatile memory is expected using advanced device design such as charge-trapping-engineered flash (CTEF) (Lin et al, 2008). The good device performance of logic OTFT and OTFT-based non-volatile memory should be useful to realize the flexible displays and low-cost IC in the near future.

#### 2. High-κ Dielectric OTFT

#### 2.1 Device Requirements

The technology goals for OTFT ICs are to achieve high speeds, large drive current and low power consumption. The high speed is necessary for SOP without using external Si logic ICs, while the low power is required for portable electronics. The high circuit speed arises from the high drive current of the OTFT, since the circuit delay ( $\tau$ ) is determined by

$$\tau = C_{\text{load}} V_{\text{max}} / I_{\text{drive}} \tag{1}$$

Here the  $C_{load}$ ,  $V_{max}$  and  $I_{drive}$  are the load capacitance, maximum voltage and drive current respectively. The current of OTFT is expressed as the following equation of a Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET)

$$I_{d} = \mu C_{ox}(W/L)[(V_{g}-V_{t})V_{d}-V_{d}^{2}/2]$$

(2)

The  $\mu$  and  $C_{ox}$  are the mobility and gate capacitance density, respectively. The *L*, W,  $V_g$  and  $V_d$  are the transistor's gate length, gate width, gate voltage and drain voltage, respectively. The source voltage is connected to ground (0 V). The maximum transistor drive current for the OTFT operated at saturation region ( $V_g$ - $V_t$ < $V_d$ ) is simplified as

$$I_d = \mu C_{ox} (W/L) (V_g - V_t)^2 / 2$$

(3)

A low  $V_t$  is beneficial for high drive current and low voltage operation, which is limited to a minimum 0.11 V of 4kT/q based on the thermal noise considerations. The increasing  $V_g$  can give the required high drive current but unfortunately increases the power consumption. Although the desired high drive current is reachable by decreasing L, the minimum L is limited to  $\mu$ m range from the practical consideration of low cost lithography. The increasing W can also increase the drive current, but this is opposite to the needed high resolution of display pixel. This is a fundamental challenge to use OTFT to drive high current OLED (Nomura et al, 2004), because of the low drive current from relatively low mobility. One useful method to improve the drive current is to increase  $C_{ox}$ :

The method to improve the unive current is to increase  $C_{0x}$ .

$$C_{\rm ox} = \varepsilon_0 \kappa / t_{\rm ox} \tag{4}$$

E

Although higher  $C_{ox}$  can be reached by decreasing the dielectric thickness ( $t_{ox}$ ), this is restricted by the exponentially increasing leakage current. Therefore, the most effective method is to use high- $\kappa$  material as the gate dielectric.

Currently, the high- $\kappa$  gate dielectric has been used for Intel's 45 nm node MOSFET, with a small equivalent oxide thickness (EOT) of 1 nm. Here the EOT is defined as

$$OT = t_{ox}(\kappa_{sio2}/\kappa) = t_{ox}(3.9/\kappa)$$

(5)

199

The  $\kappa_{sio2}$  is the dielectric constant for SiO<sub>2</sub>, which has a value of 3.9. It is important to notice that the combination of inorganic high  $C_{ox}$  and good mobility organic channel is the few practical method to realize the integrated OTFT with OLED, because of the needed high operation current for OLED. The high- $\kappa$  dielectric OTFT can be implemented to the existing process line of Si TFT for low cost and light weight displays shown in following sections.

#### 2.2 OTFT Device Design

One important advantage of OTFT is the significantly lower thermal budget and fast device process than SPC poly-Si TFT. However, the low hole mobility and poor sub-threshold swing are the drawbacks that give unwanted low drive current and slow turn on when operated at low voltage.

To overcome these problems, we used high- $\kappa$  HfLaO as the gate dielectric for OTFTs. To mimic poly-Si TFTs fabricated on glass panel, we first fabricated the metal-gate and high- $\kappa$  OTFTs on a thick SiO<sub>2</sub> layer grown on Si wafers. This is because of the different substrate size and processing equipments used for commercial glass panel and high- $\kappa$  dielectric process for Si MOSFET. Figure 1 shows the schematic device diagram of the high- $\kappa$  dielectric and organic channel OTFT, where a bottom gate electrode is used.

#### Si or polyimide substrate

Fig. 1. Schematic device diagram of the OTFT using high-κ gate dielectric and metal gate.

Currently, the pentacene is the commonly used organic material for OTFT. The first question is what kind of gate electrode should be used. The metal gate offers a simple and low temperature process compared with doped poly-Si gate used in sub- $\mu$ m MOSFET. However, the choice of proper metal-gate with adequate work-function is important to reach low leakage current of pentacene/high- $\kappa$ /metal-gate OTFT.

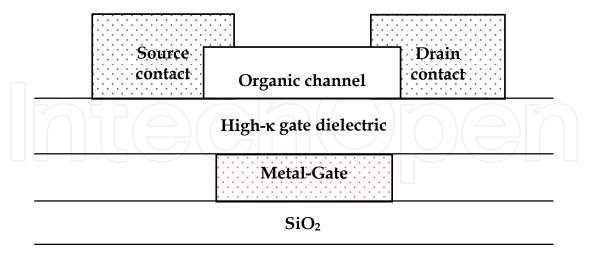

Figure 2 shows the schematic diagram of energy-levels of molecular pentacene. For comparison, those of the single crystalline Si are also plotted. The energy levels for small-molecular materials like pentacene are defined as the lowest unoccupied molecular orbital (LUMO) and the highest occupied molecular orbital (HOMO), which are different from the electronic bands in crystalline lattice such as Si. The appreciable energy bands in polymer material may be obtained for highly crystalline defect-free material but this is difficult to reach. The important current conduction for OTFT is mainly along the direction of the polymer chain. For pentacene, the majority carriers for conduction are the holes that are occupied at HOMO energy level with work-function very close to the valence band of Si crystal with only 0.1 eV difference.

Fig. 2. Schematic energy-level diagrams of molecular pentacene and single crystal Si. An ntype doping in Si body is needed to form the p-MOSFET, but pentacene is difficult to dope into n-type.

For low  $V_t$  pentacene OTFT, the gate electrode should have work-function close to HOMO energy similar to a hole conductive p-type Si MOSFET (p-MOSFET). The  $V_t$  of the Si p-MOSFET is expressed as

$$V_t = \phi_{MS} - Q_{ox} / C_{ox} - 2\phi_F - Q_{dpl} / C_{ox}$$

(6)

Here  $\phi_{MS}$  ( $\phi_M$ - $\phi_S$ ),  $Q_{ox}$ ,  $Q_{dpl}$  and  $2\phi_F$  are the work-function difference of metal-gate and pentacene, oxide charge, depletion region charge and surface bending voltage to turn on

OTFT, respectively. The  $\phi_F$  is energy difference of Fermi level (E<sub>F</sub>) to intrinsic level (E<sub>i</sub>), which is related to doping concentration (N<sub>D</sub>) and intrinsic carrier density (n<sub>i</sub>) in Si by

$$\phi_{\rm F} = (kT/q) \ln(N_{\rm D}/n_{\rm i}) \tag{7}$$

Note that the Si body of p-MOSFET is doped with opposite n-type doping. This lowers the leakage current in a p-MOSFET at off-state, when transistor is biased at  $V_g=0$  V and  $V_{ds}<0$  V. The n-type doping moves  $E_F$  toward  $E_C$  and forms energy barriers of p<sup>+</sup>-n junctions in source and drain that lowers the off-state leakage current.

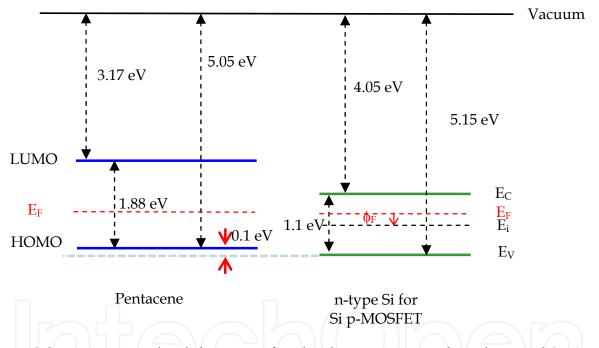

The  $V_t$  equation can also give important guideline to design the pentacene OTFT, although some of the important parameters are unknown in pentacene. Nevertheless, the pentacene is generally p-type and difficult to dope into n-type. Therefore, no leakage current blocking p<sup>+</sup>n junctions can be easily formed. One alternative method to lower the off-state leakage current is to form the partially depleted OTFT structure shown in Fig. 3(a), which has an opposite surface bend bending to accumulation mode shown in Fig. 3(b). This can be reached using relative low work-function metal-gate compared with the high work-function one used for low  $V_t$ Si p-MOSFET. However, the needed low leakage current is traded off the slightly high  $V_t$ , since higher  $V_g$  is required to form the strong hole accumulation mode and turn on the OTFT shown in Fig. 3(c). Such partially or even fully depleted channel has previously led to the invention of low leakage current form small energy bandgap Ge (0.66 eV) is the major concern of the Ge MOSFET (Chin et al, 2005).

Fig. 3. Schematic energy-level diagrams of pentacene/oxide/metal-gate OTFT with (a) low and (b) high work-function metal-gate under equilibrium and  $V_g=0$ ; (c) under a negative  $V_g$  bias to reach strong hole accumulation.

Although many elements in the periodic table have low work-function to meet the requirement of low off-state leakage, we choose the TaN as the gate electrode. This TaN electrode has been developed previously for metal-insulator-metal (MIM) capacitors used for Analog/RF and Dynamic Random Access Memory (DRAM) applications (Chiang et al, 2006), where similar bottom electrode device structure and process sequence were used. The

reason to choose TaN is because it has larger bond enthalpy than pure metals, which also has one of the strongest bond enthalpies among various metal-nitrides in the periodic table (Yu et al, 2005). Such robust metal-gate is required to lower the oxidation rate of gate electrode during subsequent high- $\kappa$  gate dielectric deposition and post-deposition anneal (PDA), under an O<sub>2</sub> ambient. The oxidized metal-surface will degrade the EOT and leakage current by trap-assisted tunneling.

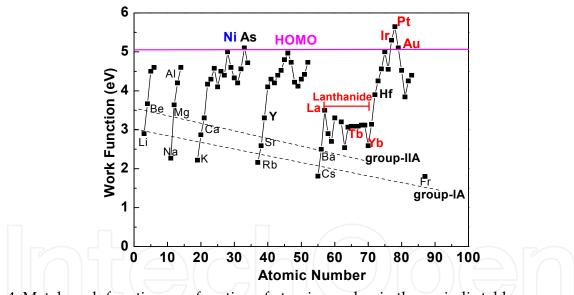

The second question is the choice of source-drain contact metals. Figure 4 shows the work-function of atoms in the periodic table. There are only 3 stable elements of Ir, Pt and Au that have work-function larger than the HOMO energy. The higher work-function than HOMO allows direct hole conduction via Schottky contact, without using p<sup>+</sup> doping in pentacene. Such direct source-drain metal contact provides unique advantages for low temperature and fast process compared with the high thermal budget of n<sup>+</sup>-doped SPC poly-Si TFT (Hung et al, 2005), which is the enable technology on low temperature flexible substrate. Note that the Ni metal may be a low cost choice since it has reported 5.0~5.1 eV work-function (Chiang et al, 2007) close to that of HOMO. However, the vital OTFT drive current may decrease exponentially with increasing energy barrier of metal-pentacene energy difference, if the metal work function is slighter lower than HOMO level. Here the Au is the most widely used source-drain contact metal for pentacene, due to the significantly lower melting temperature than Pt and Ir for easy deposition using a simple thermal evaporation.

Fig. 4. Metal work-function as a function of atomic number in the periodic table.

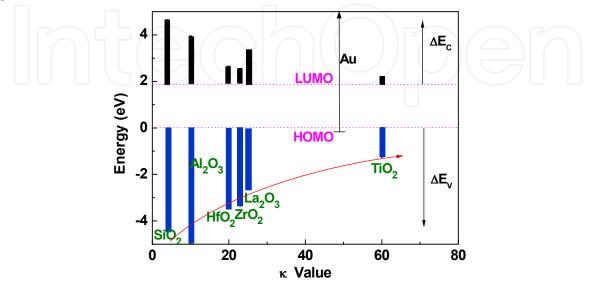

The next question is the choice of proper high- $\kappa$  gate dielectric for OTFT. Figure 5 shows the potential binary gate oxides for pentacene OTFT. Generally, the energy bandgap of high- $\kappa$  dielectric and valence or conduction band offset ( $\Delta E_V$  or  $\Delta E_C$ ) to pentacene decrease monotonically with increasing  $\kappa$  value. The higher  $\kappa$  value provides the wanted higher drive for OTFT. Nevertheless, a large enough  $\Delta E_V$  or  $\Delta E_C$  energy barrier of ~1 eV is required to reach the low gate leakage current for practical application. Fortunately, the  $\Delta E_V$  is larger than  $\Delta E_C$  for most high- $\kappa$  dielectrics that is useful to reach low gate leakage current in p-type OTFT. Therefore, the HfO<sub>2</sub>, ZrO<sub>2</sub>, La<sub>2</sub>O<sub>3</sub> (Chin et al, 2000) and TiO<sub>2</sub> (Cheng et al, 2008) are the few good candidates for pentacene OTFT. However, the  $\kappa$  value of TiO<sub>2</sub> or SrTiO<sub>3</sub>

depends strongly on the growth temperature and the degree of dielectric crystallization. The high process temperature of  $450 \sim 550^{\circ}$ C for higher  $\kappa$  SrTiO<sub>3</sub> (Chiang et al, 2006) is not suitable to integrate the OTFT onto organic substrate. Here the HfO<sub>2</sub> is the most used high- $\kappa$  gate dielectric for Intel's 45 nm node MOSFET using gate-last technology. The La<sub>2</sub>O<sub>3</sub> capping (Wu et al, 2000) on HfSiON has been widely used for low  $V_t$  32 nm node gate-first high- $\kappa$  n-MOSFET, such as IBM, Toshiba, IMEC, SEMATECH etc.

Fig. 5. Energy bandgap of oxides and band alignment to pentacene. Generally, both the bandgap and band offset become smaller with increasing  $\kappa$  value.

#### 2.3 High Performance OTFT on SiO<sub>2</sub>

The OTFT on SiO<sub>2</sub> has potential to replace the amorphous Si TFT on glass panel. The process of pentacene/high- $\kappa$ /metal-gate OTFT starts with a 50 nm thick TaN gate electrode that was formed by sputtering deposition on the SiO<sub>2</sub>/Si substrate through a shadow metal mask. An NH<sub>3</sub> plasma was further applied to the TaN surface (Chiang et al, 2005). Such NH<sub>3</sub> plasma treatment is the key factor to achieve low leakage current and small EOT in previous DRAM capacitors (Chiang et al, 2005; Cheng et al, 2008; Lin et al, 2009). Then the HfLaO gate dielectric with 20 nm thickness was deposited by electron beam evaporation at room temperature and followed by a 350°C O<sub>2</sub> PDA for 10 min. The adding La<sub>2</sub>O<sub>3</sub> into HfO<sub>2</sub> is especially important to decrease the leakage current at low process temperature (Chang et al, 2008). After that the pentacene active layer with 70 nm thickness was deposited by electron beam evaporation through a shadow mask. The OTFT was finished by depositing 50 nm thick Au onto the pentacene and forming the source/drain contact electrodes.

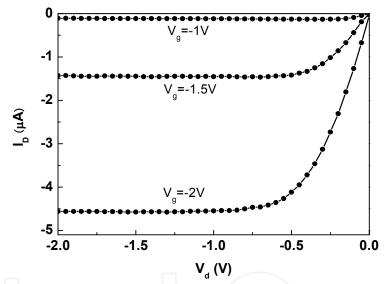

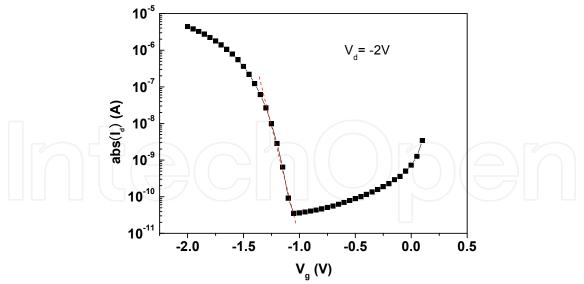

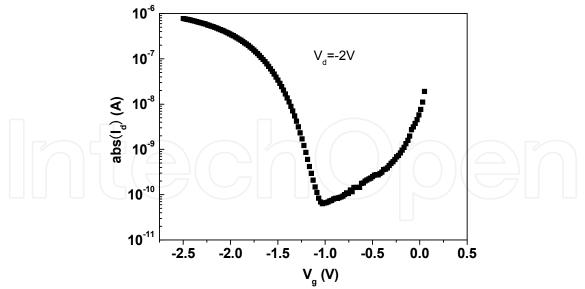

Figure 6 shows the output characteristics of the fabricated pentacene/high- $\kappa$ /metal-gate OTFT. Well-behaved  $I_d$ - $V_d$  characteristics were measured under dark and air ambient, even at a low operation voltage of 2 V. This is the lowest reported operation voltage of OTFT for low power ( $I_d \times V_d$ ) circuit application. Figure 7 shows the transfer characteristics of the pentacene/HfLaO/TaN OTFT. Here the  $V_t$  and mobility can be extracted from the linear  $I_d^{1/2}$ - $V_g$  plot using eq. (3). This pentacene/high- $\kappa$ /metal-gate OTFT shows excellent device integrity of a low  $V_t$  of -1.3 V, a record small sub-threshold swing of 78 mV/decade, good  $\mu_{FE}$  of 0.7 cm<sup>2</sup>/Vs and a large on- and off-state current ratio ( $I_{ont}/I_{off}$ ) of 1.0×10<sup>5</sup> (Chang et al,

2008). The low  $V_t$  and small sub-threshold swing ensure the OTFT to operate at low voltage. Such small sub-threshold swing is the best reported data among Si TFT (Hung et al, 2005) and OTFT (Klauk et al, 1999; Zhou et al, 2005; Kawasaki et al, 2006) to date, to the best knowledge. This small sub-threshold swing is close to the theoretical ideal value of 60 mV/decade for MOSFET at room temperature and even comparable with that of a 0.18-µm single crystalline Si MOSFET fabricated from an IC foundry (Kao et al, 2006).

To further understand the record low sub-threshold swing  $[d(log_{10}I_d)/dV_g]^{-1}$  of OTFT, we have examined the relation

Sub-threshold swing =

$$(kT/q)ln10[1+(C_{dpl}+C_{it})/C_{ox}]$$

(8)

Here  $C_{dpl}$  is the gate depletion capacitance density of pentacene. The  $C_{it}$  is the capacitance density from the pentacene/high- $\kappa$  interface trapped charges that equals to interface trap density  $D_{it}$  by  $C_{it}/q$ . To measure the gate capacitance density  $C_{ox}$ , an Au/HfLaO/TaN capacitor was fabricated side-by-side along with the pentacene/HfLaO/TaN OTFT. A  $C_{ox}$  of 950 nF/cm<sup>2</sup> and a high- $\kappa$  value of 24 were measured that gave a small EOT of 3.6 nm.

Fig. 6. Output characteristics of the pentacene/HfLaO/TaN OTFT. The device channel length and width are 80  $\mu$ m and 2000  $\mu$ m, respectively.

The  $C_{dpl}$  is smaller than high- $\kappa$   $C_{ox}$  and negligible, which leads to a  $D_{it}$  of 2×10<sup>12</sup> eV<sup>-1</sup>/cm<sup>2</sup> even processed at low temperature. This value is typical for high- $\kappa$  gate dielectric MOSFET on single crystalline Si (Cheng et al, 2007). This good electrical interface property is the merit of using HfLaO as the gate dielectric for OTFT.

204

Fig. 7. Transfer characteristics of the pentacene/HfLaO/TaN OTFT with channel length and width of 80  $\mu$ m and 2000  $\mu$ m respectively. The sub-threshold swing is defined as the slope of  $I_d$ - $V_g$  curve in voltage per current increase for 10X (a decade).

Table 1 summarizes the important device data of this p-channel OTFT and conventional nchannel poly-Si TFTs (Choi et al, 1999; Lin et al, 1999; Chang et al, 2003). The pentacene/high- $\kappa$ /metal-gate OTFT has better device performance in terms of lower  $V_t$  and much smaller sub-threshold swing. This OTFT device also has comparable normalized drive current ( $\mu C_{ox}$ ) with the poly-Si TFTs. Here the  $\mu C_{ox}$  is normalized to the channel length *L*, width *W* and over-drive  $V_{G}-V_T$ :

$$\mu C_{\rm ox} = 2I_{\rm d} \left( L/W \right) / (V_{\rm G} - V_{\rm T})^2 \tag{9}$$

Thus, the high  $C_{ox}$  is as important as the high mobility for high drive current. Besides, higher mobility above 5 cm<sup>2</sup>/Vs is reachable by optimizing the chemistry (Lee et al, 2006). The excellent device characteristics ensues the good potential for OTFT used for display.

| Active channel                 | Gate<br>dielectric             | V <sub>t</sub> ,<br>V | Sub-threshold<br>swing,<br>V/decade | μ,<br>cm²/Vs | $\mu C_{ox}$ ,<br>nF/cm <sup>2</sup> | Ion/Ioff            |

|--------------------------------|--------------------------------|-----------------------|-------------------------------------|--------------|--------------------------------------|---------------------|

| Pentacene<br>(This work)       | HfLaO                          | -1.3                  | 0.078                               | 0.7          | 674                                  | $1.0 \times 10^{5}$ |

| poly-Si<br>(Choi et al, 1999)  | LPCVD<br>SiO <sub>2</sub>      | 5.6                   | 1.4                                 | 20           | 863                                  | 3.5×10 <sup>5</sup> |

| poly-Si<br>(Lin et al, 1999)   | PECVD<br>TEOS SiO <sub>2</sub> | 8.1                   | 1.97                                | 12           | 716                                  | 3.0×10 <sup>5</sup> |

| poly-Si<br>(Chang et al, 2003) | PECVD<br>TEOS SiO <sub>2</sub> | -                     | 2.67                                | 3            | 259                                  | -                   |

Table 1. Device data of p-channel pentacene/HfLaO/TaN OTFTs and compared with n-channel poly-Si TFTs.

#### 2.4 OTFT on Flexible Substrate

The important advantages of OTFT are its flexibility and low process temperature that can be used for flexible displays and low-cost flexible electronics. Based on the excellent device performance of pentacene/high- $\kappa$ /metal-gate OTFTs on SiO<sub>2</sub> shown in previous section, the process temperature was further decreased to 200°C to fabricate the OTFTs on low-cost flexible polyimide substrates (Kapton HPP-ST, Dupont). This substrate is much more economical than other polyimide (Kapton E-type, DuPont) and polyethylene naphthalate (PEN) (Teonex Q65 PEN, Dupont) substrates, although the cost is traded off the degraded performance of poor surface roughness and impurity out-diffusion.

To improve the impurity diffusion, the polyimide substrates (Kapton HPP-ST, DuPont) with 125  $\mu$ m thickness were annealed at 200°C in a vacuum environment. To lower the internal stress, a thin 100 nm SiO<sub>2</sub> was deposited on the polyimide substrate at room temperature by electron beam evaporation. Then the pentacene/HfLaO/TaN OTFTs were fabricated on SiO<sub>2</sub>/polyimide by following the similar process steps in previous section on SiO<sub>2</sub>/Si, with lower 200°C PDA temperature and thicker 30 nm HfLaO gate dielectric (Chang et al, 2009). The thicker HfLaO is to compensate the degraded gate leakage current when processed at lower temperature. The schematic diagram of fabricated devices is shown in Fig. 1, where the OTFTs were measured in the dark and air ambient.

Figure 8 shows the output characteristics of the fabricated OTFT on SiO<sub>2</sub>/polyimide. Wellbehaved  $I_d$ - $V_d$  characteristics were obtained, under a low voltage operation of 2.5 V for low power electronics application. Figure 9 shows the  $I_d$ - $V_g$  characteristics of the pentacene/high- $\kappa$ /metal-gate OTFT on SiO<sub>2</sub>/polyimide. The  $V_t$  and mobility were extracted from the linear  $I_d^{1/2}$ - $V_g$  plot.

Fig. 8. Output characteristics of the pentacene/HfLaO/TaN OTFT on  $SiO_2$ /polyimide. The device channel length and width are 100 µm and 2000 µm, respectively.

Fig. 9. Transfer characteristics of the pentacene/HfLaO/TaN OTFT on SiO<sub>2</sub>/polyimide, with device channel length and width of 100  $\mu$ m and 2000  $\mu$ m respectively. The increasing current at V<sub>g</sub>>-1 V suggests the electron conduction, but the small current is due to the high barrier source-drain electrodes.

The pentacene/HfLaO/TaN OTFT on SiO<sub>2</sub>/polyimide shows good device performance of a low  $V_t$  of -1.25 V, a small sub-threshold swing of 130 mV/decade, a  $\mu_{FE}$  of 0.13 cm<sup>2</sup>/Vs and a  $I_{on}/I_{off}$  of 1.2×10<sup>4</sup> (Chang et al, 2009). The low operation voltage of -2.4 V is due to the low  $V_t$ and small sub-threshold swing. Such small sub-threshold swing is better than other reported values for flexible OTFTs (Choi et al, 2005, Kang et al, 2005; Klauk et al, 2005; Mizukami et al, 2006; Na et al, 2007), which is due to the using high- $\kappa$  HfLaO dielectric with a high capacitance density of 450 nF/cm<sup>2</sup> and a small EOT of 7.7 nm. The smaller mobility and  $I_{on}/I_{off}$  than similar OTFT fabricated on SiO<sub>2</sub>/Si were due to the rougher HfLaO surface of 4.2 nm measured by Atomic Force Microscopy (AFM), which was originated from the poor 9.0 nm surface roughness of low cost polyimide substrate (Kapton HPP-ST, Dupont). The drain current at  $V_g$ >-1 V may be attributed to the ambipolar behavior of electron conduction (Schön & Kloc 2001), although the current is limited by inadequate high workfunction source-drain electrodes. However, this ambipolar conduction may be useful for pentacene-based non-volatile memory discussed in next session.

Table 2 compares the important device data of our work with other flexible pentacene OTFTs using various gate dielectrics and fabricated on high quality polyimide (Kapton E-type) and PEN (Teonex Q65 PEN, DuPont) substrates. The pentacene/HfLaO/TaN flexible OTFT shows comparable device performance of normalized drive current and  $I_{on}/I_{off}$  with other OTFTs fabricated on high cost substrates, with the added merit of the best sub-threshold swing for fast turn on and low voltage operation. The good device performance of low voltage operated OTFT, on low cost polyimide substrate, should lead to future more economic low-power flexible electronics.

| Flexible substrate                  | Gate<br>dielectric   | V <sub>t</sub> ,<br>V | Sub-<br>threshold<br>swing,<br>V/decade | μ,<br>cm²/Vs | $\mu C_{ox}$ ,<br>nF/cm <sup>2</sup> | I <sub>on</sub> /I <sub>off</sub> |

|-------------------------------------|----------------------|-----------------------|-----------------------------------------|--------------|--------------------------------------|-----------------------------------|

| Polyimide                           |                      |                       |                                         |              |                                      |                                   |

| Kapton HPP-ST                       | HfLaO                | -1.25                 | 0.13                                    | 0.13         | 58                                   | $1.2 \times 10^{4}$               |

| (This work)                         |                      |                       |                                         |              |                                      |                                   |

| Polyimide                           |                      |                       | ( )                                     |              |                                      |                                   |

| Kapton E-type                       | BZN                  | 0.1                   | 0.3                                     | 0.5          | 110                                  | 3.5×10 <sup>5</sup>               |

| (Choi et al, 2005)                  |                      | $\neg$                |                                         |              |                                      |                                   |

| Polyimide<br>Kantan E tuna          | Mn-doped             |                       |                                         | 0.32         | 25                                   | <1×10 <sup>3</sup>                |

| Kapton E-type<br>(Kang et al, 2005) | BaSrTiO <sub>3</sub> | -1                    | -                                       | -0.32        | 35                                   | <b>\1^10</b> <sup>3</sup>         |

| PEN                                 | PVP                  | -                     | 0.6                                     | 0.1          | 6                                    | 1×10 <sup>4</sup>                 |

| (Klauk et al, 2005)                 |                      |                       |                                         |              |                                      |                                   |

| PEN                                 |                      |                       |                                         |              |                                      |                                   |

| (Mizukami et al,                    | $Ta_2O_5$            | 0.8                   | -                                       | 0.25         | 35                                   | -                                 |

| 2006)                               |                      |                       |                                         |              |                                      |                                   |

| PEN<br>(Na et al, 2007)             | TiSiO <sub>2</sub>   | -0.88                 | 0.315                                   | 0.67         | 95                                   | 1×10 <sup>4</sup>                 |

Table 2. Device data of pentacene active channel OTFTs using various gate dielectrics and fabricated on different flexible substrates.

#### **3. Organic Non-volatile Memory Devices Using High-κ Dielectric**

#### 3.1 Device requirements

Based on the good device performance of flexible OTFT, we can further apply to the non-volatile memory. Such non-volatile memory function is indispensible for SOP (Baeg et al, 2006). The first task for OTFT-based non-volatile memory is to choice the proper device structure that can meet the device requirement of low write power, long retention, good endurance and fast write speed.

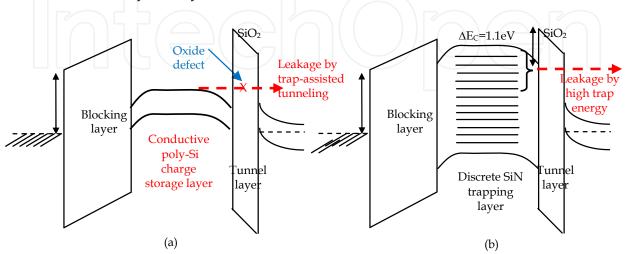

Among various new types non-volatile memory devices such as Phase Change Random Access Memory (PRAM) and resistive RAM (RRAM), the SiO<sub>2</sub>/poly-Si/SiO<sub>2</sub> floating gate flash memory device still has irreplaceable advantage of the lowest write current and being one-transistor (1T) in size compared with other one-transistor-one-resistor (1T1R) designs. Such low current is mandatory for page writing NAND logic and low power portable electronics. This floating gate flash memory shown in Fig. 10 (a) employs the well-known device physics and manufacturing experience of the Si industry. Digital data can be programmed into the device by injecting charges over tunnel oxide, or erased by removing the stored charges or injecting different polarity charges into the trapping layer. The program or erase function can be obtained by applying a large gate electric field across the tunnel oxide. This charge transfer is readable by measuring the  $V_t$  of the transistor.

The fundamental challenge of a conventional floating-gate flash device is that all the storage charges can leak out via a single oxide defect by trap-assisted tunneling shown in Fig. 10(a). This is due to the drawback of electrically conductive poly-Si charge storage layer. Unfortunately, such oxide defect is inevitable that can be generated by continuous device

operation and measurable from the stress-induced leakge current (SILC). One method to address this issue is to use the [metal-gate]-oxide-nitride-oxide-semiconductor (MONOS) device structure. As shown in Fig. 10(b), the programmed charges are stored in discrete and electrically-isolated zero-dimensional quantum traps within the Si<sub>3</sub>N<sub>4</sub>, while only the trapped charges, close to oxide defects generated by write cycles, can leak out. Besides, the physically separated traps allow the storage of 2 bits/cell in both source and drain sides to increase the memory density.

Fig. 10. Schematic energy band diagram of the electron trapping (a) poly-Si floating gate and (b) MONOS non-volatile memory devices.

In addition to the low write current and good endurance of multiple write cycles, the nonvolatile memory devices also need good data retention and fast write speed. However, the charge-storage energy in  $Si_3N_4$  traps is much higher than conventional poly-Si floating gate flash as shown in Fig. 10 that causes the stored charges to leak out. One method to maintain the good data retention, without scarifying the write speed, is to engineer the trap energy level. Here the deeper trapping energy level, the better data retention.

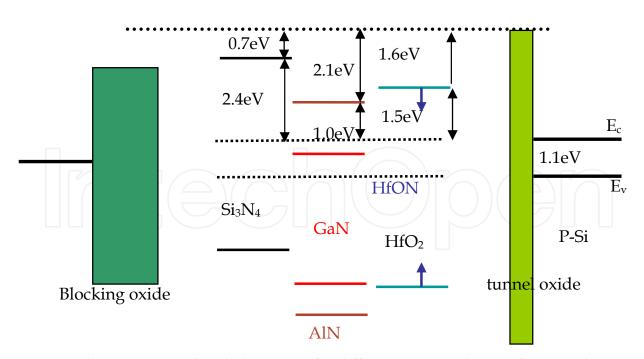

This can be reached by replacing the conventional Si<sub>3</sub>N<sub>4</sub> with a high- $\kappa$  metal-nitride dielectric shown in Fig. 11, where the later should have deeper  $\Delta E_C$  or  $\Delta E_V$  to barrier oxide layers for better charge retention. However, there are few metal-nitrides in the periodic table that can meet this requirement. Most metal-nitrides are metallic and similar to conductive poly-Si floating gate, which failed for discrete trapping MONOS application. The few candidates left are BN, AlN, GaN, InN etc, but the BN is difficult to process because of the strong bonding energy. Note that the AlGaN and GaInN have been widely used for blue-light LED. The using deep trapping energy AlN and AlGaN were initiated by Chin's group (Lai et al, 2005; Chin et al, 2005). Further lowering the P/E voltage with good retention can be reached by using higher  $\kappa$  synthesized HfON trapping layer (Lai et al, 2006). The significantly better retention using deep  $\Delta E_C$  AlGaN trapping layer was also affirmed by Samsung's work (Joo et al, 2006). The alternative high- $\kappa$  metal-nitride trapping layer was also listed in the *International Technology Roadmap for Semiconductors (ITRS,* 2007) for future generation charge-trapping flash (CTF) non-volatile memory.

Fig. 11. Schematic energy band alignments for different trapping layers of  $Si_3N_4$ , AlN, GaN and HfON within the MONOS structure.

#### 3.2 OTFT MONOS Non-volatile Memory on Flexible Polyimide

Similar to the OTFT on flexible polyimide, the bottom gate TaN-HfLaO-HfON-HfO<sub>2</sub>-Pentacene (MONOP) memory was fabricated on a low-cost flexible polyimide substrate (Kapton HPP-ST). The device fabrication starts the substrates annealing at 200°C. Then 100 nm SiO<sub>2</sub> was deposited and 50 nm TaN gate electrode was formed. After applying the NH<sub>3</sub><sup>+</sup> plasma to TaN surface, the 20 nm HfLaO blocking oxide, 20 nm HfON trapping layer and 6 nm HfO<sub>2</sub> tunnel layer were deposited. Then a 200°C O<sub>2</sub> PDA was applied to improve the dielectric quality. After that 70 nm pentacene active layer was deposited at 70°C. The device was finished by making Au source-drain electrodes and forming ohmic-like contact for the hole injection. Here a thicker HfLaO blocking layer is important to reduce gate leakage current during erase.

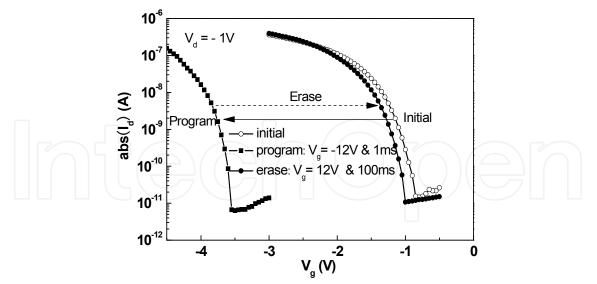

The transfer hysteresis curves of OTFT MONOP memory device under P/E are shown in Fig. 12. From the initial transfer characteristics at a saturation  $V_d$  of -3 V, the  $V_t$ , sub-threshold swing, mobility, and  $I_{or}/I_{off}$  were -1.4 V, 160 mV/decade, 0.1 cm<sup>2</sup>/Vs and 1×10<sup>4</sup>, respectively. These data are very close to the pentracene/HfLaO/TaN OTFT on the same flexible polyimide substrate shown in previous section. When a program  $V_g$  of -12 V and 1 ms was applied, the holes accumulated at HfO<sub>2</sub>/pentacene interface can tunnel through the HfO<sub>2</sub> by the large gate electric field and trapped in the HfON layer. This increases the  $|V_t|$  and shifts the  $I_d$ - $V_g$  curve in negative direction. When an erase  $V_g$  of 12 V for 100 ms was applied, the trapped holes in the HfON may tunnel out over the HfO<sub>2</sub> by the electric field and lowered the  $|V_t|$ . Alternatively, the minority carriers of electrons may also be generated in the depletion region of pentacene, tunnel into the HfON and annihilate the trapped holes (Chin et al, 2006). Therefore, the  $V_t$  value can be shifted, reversibly, by applying an appropriate program or erase  $V_g$ . Nevertheless, the erase is much more difficult than program since the density of minority carriers is less in large bandgap pentacene.

Fig. 12. Transfer hysteresis curves for a pentacene OTFT memory device under  $V_g$  = -12 V, 1 ms program and  $V_g$  = 12 V, 100 ms erase at  $V_d$  = -1 V. The channel length and width were 150 and 1500 µm, respectively.

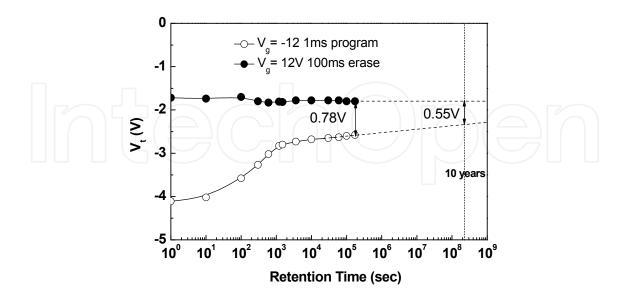

Good retention characteristics are necessary for non-volatile memory. Figure 13 shows the retention data under a program and erase condition of -12 V for 1 ms and 12 V for 100 ms. Here the  $V_t$  was extracted from the linear  $I_d$ - $V_g$  characteristics. The initial memory window of 2.4 V was obtained that decreased to 0.78 V after 48 hrs retention. The fast charge loss for the first 10<sup>3</sup> s is possibly due to the defects in the low temperature formed HfO<sub>2</sub> and the rough tunnel oxide surface by low cost polyimide substrate. The charge loss becomes stable at time longer than 10<sup>3</sup> s. If no other charge loss mechanism, an extrapolated 10-year retention window of 0.55 V may be reachable that is large enough for sense amplifier.

Fig. 13. Retention characteristics for pentacene MONOP OTFT device.

#### 4. Conclusions and Future Directions

The high transistor current of OTFT is the key factor to drive the high operation current OLED and high resolution display. This can be achieved by increasing the mobility of pentacene and gate dielectric Cox using high-k dielectric. Although the highest reported mobility for pentacene is better than amorphous Si, it is still inferior to poly-Si or high mobility InGaZnO (Nomura, et al, 2004). This limit makes the using high-k gate dielectric more important and inevitable. The using metal-gate is also necessary to decrease the OTFT leakage current and improve the *I*<sub>on</sub>/*I*<sub>off</sub> by forming the partially depleted OTFT. Good device integrity of pentacene/HfLaO/TaN OTFT on SiO<sub>2</sub> is reached with a low  $V_t$  of -1.3 V, the record best sub-threshold swing of 78 mV/decade, a good  $\mu_{FE}$  of 0.7 cm<sup>2</sup>/Vs and a large Ion/Ioff of 1.0×10<sup>5</sup>. The pentacene/HfLaO/TaN OTFT on low-cost flexible polyimide shows still reasonable good device performance of a low  $V_t$  of -1.25 V, a small sub-threshold swing of 130 mV/decade, a  $\mu_{FE}$  of 0.13 cm<sup>2</sup>/Vs and a  $I_{on}/I_{off}$  of 1.2×10<sup>4</sup>. Based on the good OTFT device performance, the MONOP non-volatile memory shows an initial memory window of 2.4 V and a 48 hrs retention window of 0.78 V, under a low P/E condition of -12 V for 1 ms and 12 V for 100 ms. Further improving the retention may be achievable using advanced CTEF non-volatile memory structure and using smoother flexible substrate.

One of the reasons to give pentacene the higher mobility than amorphous Si is due to the short range ordering. Further improving mobility might be achievable by forming other ordering in organic martial such as Si Cage Clusters (Hiura, Miyazaki, & Kanayama, 2001).

The author would like to thank Mr. M. F. Chang's device fabrication and the support from National Nano Program, National Science Council of Taiwan, R.O.C.

#### 5. References

- Baeg, K. J.; Noh, Y. Y.; Ghim, J.; Kang, S. J.; Lee, H. and Kim, D. Y. (2006). Organic nonvolatile memory based on pentacene field-effect transistors using a polymeric gate electret. *Adv. Mater.*, Vol. 18, No. 10, pp. 3179-3183.

- Chiang, K. C.; Chin, Albert; Lai, C. H.; Chen, W. J.; Cheng, C. F.; Hung, B. F.; & Liao, C. C. (2005). Very high κ and high density TiTaO MIM capacitors for analog and RF applications, *Proceedings of Symp. on VLSI Technology*, pp. 62-63, Kyoto, Japan.

- Chiang, K. C.; Huang, C. C.; Chen, G. L.; Chen, W. J.; Kao, H. L.; Wu, Y. H.; Chin, Albert & McAlister, S. P. (2006). High performance SrTiO<sub>3</sub> metal-insulator-metal capacitors for analog applications. *IEEE Trans. Electron Device*, Vol. 53, No. 9, pp. 2312-2319.

- Chiang, K. C.; Cheng, C. H.; Jhou, K. Y.; Pan, H. C.; Hsiao, C. N.; Chou, C. P.; McAlister, S. P.; Chin, Albert & Hwang, H. L. (2007). Use of a high work-function Ni electrode to improved the stress reliability of analog SrTiO<sub>3</sub> metal-insulator-metal capacitors. *IEEE Electron Device Lett.*, Vol. 28, No. 8, pp. 694-696.

- Chang, K. M.; Yang, W. C. & Tsai, C. P. (2003). Electrical characteristics of low temperature polysilicon TFT with a novel TEOS/oxynitride stack gate dielectric. *IEEE Electron Device Lett.*, Vol. 24, No. 8, pp. 512-514.

- Chang, M. F.; Lee, P. T.; McAlister, S. P. & Chin, Albert (2008). Low subthreshold swing HfLaO/pentacene organic thin-film transistors. *IEEE Electron Device Lett.*, Vol. 29, No. 3, pp. 215-217.

- Chang, M. F.; Lee, P. T.; McAlister, S. P. & Chin, Albert (2008). A flexible organic pentacene non-volatile memory incorporating high-к dielectric layer. *Appl. Phys. Lett.*, Vol. 93, No. 23, p. 23302.

- Chang, M. F.; Lee, P. T.; McAlister, S. P. & Chin, Albert (2009). Small-subthreshold-swing and low-voltage flexible organic thin-film transistors which use HfLaO as the gate dielectric. *IEEE Electron Device Lett.*, Vol. 30, No. 2, pp. 133-135.

- Cheng, C. F;. Wu, C. H.; Su, N. C; Wang, S. J.; McAlister S. P. & Chin, Albert. (2007). Very low Vt [Ir-Hf]/HfLaO CMOS using novel self-aligned low temperature shallow junctions. *Proceedings of International Electron Devices Meeting (IEDM)*, pp. 333-336, Washington DC, USA.

- Cheng, C. H.; Lin, S. H.; Jhou, K. Y.; Chen, W. J.; Chou, C. P.; Yeh, F. S.; Hu, J.; Hwang, M.; Arikado, T.; McAlister, S. P. & Chin, Albert (2008). The 300°C-processed high density TiO<sub>2</sub> MIM capacitors with low leakage current," *IEEE Electron Device Lett.*, Vol. 29, No. 8, pp. 845-847.

- Chin, Albert; Wu, Y. H., Chen, S. B., Liao, C. C. & Chen, W. J. (2000). High quality La<sub>2</sub>O<sub>3</sub> and Al<sub>2</sub>O<sub>3</sub> gate dielectrics with equivalent oxide thickness 5-10Å, *Proceedings of Symp. on VLSI Technology*, pp. 16-17, Hawaii, US.

- Chin, Albert; Laio, C. C.; Chiang, K. C.; Yu, D. S.; Yoo, W. J.; Samudra, G. S.; McAlister, S. P. & Chi, C. C. (2005). Low voltage high speed SiO<sub>2</sub>/AlGaN/AlLaO<sub>3</sub>/TaN memory with good retention. *Proceedings of International Electron Devices Meeting (IEDM)*, pp. 165-168, Washington DC, USA.

- Chin, Albert; Kao, H. L.; Tseng, Y. Y.; Yu, D. S.; Chen, C. C.; McAlister, S. P. & Chi, C. C. (2005). Physics and Modeling of Ge-on-Insulator MOSFETs, *Proceedings of European Solid State Device Research Conf. (ESSDERC)*, pp. 285-288, Grenoble, France.

- Choi, Y. W.; Lee, J. N.; Jang, T. W. & Ahn, B. T. (1999). Thin-film transistors fabricated with poly-Si films crystallized at low temperature by microwave annealing. *IEEE Electron Device Lett.*, Vol. 20, No. 1, pp. 2-4.

- Choi, Y. W.; Kim, I. D.; Tuller, H. L.; & Akinwande, A. I. (2005). Low-voltage organic transistors and depletion-load Inverters with high-K pyrochlore BZN gate dielectric on polymer substrate. *IEEE Trans. Electron Devices*, Vol. 52, No. 12, pp. 2819–2824.

- Hiura, H.; Miyazaki, T.; Kanayama, T. (2001). Phys. Rev. Lett., Vol. 86, No. 9, pp. 1733-1736.

- Huang, C. H.; Yang, M. Y.; Chin, Albert; Chen, W. J.; Zhu, C. X.; Cho, B. J.; Li, M.-F. & Kwong, D. L. (2003). Very Low Defects and High Performance Ge-On-Insulator p-MOSFETs with Al<sub>2</sub>O<sub>3</sub> Gate Dielectrics, *Proceedings of Symp. on VLSI Technology*, pp. 119-120, Kyoto, Japan.

- Hung, B. F.; Chiang, K. C.; Huang, C. C.; Chin, Albert & McAlister, S. P. (2005). Highperformance poly-silicon TFTs incorporating LaAlO<sub>3</sub> as the gate dielectric. *IEEE Electron Device Lett.*, Vol. 26, No. 6, pp. 384-386.

- International Technology Roadmap for Semiconductors (ITRS), 2007, Process Integration, Devices, & Structure Chapter, pp. 40-44. <u>www.itrs.net</u>

- Joo, K. H.; Moon, C. R.; Lee, S. N.; Wang, X.; Yang, J. K.; Yeo, I. S.; Lee, D.; Nam, O.; Chung, U. I.; Moon, J. T. & Ryu, B. I. (2006). Novel charge trap devices with NCBO trap layers for NVM or image sensor. *Proceedings of International Electron Devices Meeting* (*IEDM*), pp. 979–982, San Francisco, CA, USA.

- Kang, K. T.; Lim, M. H.; Kim, H. G.; Choi, Y. W.; Tuller, H. L.; Kima, I. D. & Hong, J. M. (2005). Mn-doped Ba<sub>0.6</sub>Sr<sub>0.4</sub>TiO<sub>3</sub> high-к gate dielectrics for low voltage organic transistor on polymer substrate. *Appl. Phys. Lett.*, Vol. 87, No. 24, p. 242908.

- Kao, H. L.; Chin, Albert; Hung, B. F.; Lee, C. F.; Lai, J. M.; McAlister, S. P.; Samudra, G. S.; Yoo, W. J. & Chi, C. C. (2005). Low noise RF MOSFETs on flexible plastic substrates. *IEEE Electron Device Lett.*, Vol. 26, No. 7, pp. 489-491.

- Kao, H. L.; Chin, Albert; Liao, C. C.; Chen, C. C.; McAlister, & Chi, C. C. Electrical stress effects and device modeling of 0.18µm RF MOSFETs. (2006). *IEEE Trans. Electron Device*, Vol. 53, No. 4, pp. 636-642.

- Klauk, H.; Gundlach, D. J.; Nichols, J. A. & Jackson, T. N. (1999). Pentacene organic thin-film transistors for circuit and display applications. *IEEE Trans. Electron Devices*, Vol. 46, No. 6, pp. 1258-1263.

- Klauk, H.; Halik, M.; Zschieschang, U.; Eder, F.; Rohde, D.; Schmid, G. & Dehm, C. (2005). Flexible organic complementary circuits. *IEEE Trans. Electron Devices*, Vol. 52, No. 4, pp. 618–622.

- Kawasaki, M.; Imazeki, S.; Ando, M.; Sekiguchi, Y.; Hirota, S.; Uemura, S. & Kamata, T. (2006). High-resolution full-color LCD driven by OTFTs using novel passivation film. *IEEE Trans. Electron Devices*, Vol. 53, No. 3, pp. 435–441.

- Lai, C. H.; Chin, Albert; Chiang, K. C.; Yoo, W. J.; Cheng, C. F.; McAlister, S. P.; Chi, C. C. & Wu, P. (2005). Novel SiO<sub>2</sub>/AlN/HfAlO/IrO<sub>2</sub> memory with fast erase, large ΔV<sub>th</sub> and good retention. *Proceedings of Symp. on VLSI Technology*, pp. 210-211, Kyoto, Japan.

- Lai, C. H.; Chin, Albert; Kao, H. L.; Chen, K. M.; Hong, M.; Kwo, J.; & Chi, C. C. (2006). Very low voltage SiO<sub>2</sub>/HfON/HfAlO/TaN memory with fast speed and good retention," *Proceedings of Symp. on VLSI Technology*, pp. 54-55, Hawaii, USA.

- Lemmi, F.; Chung, W.; Lin, S.; Smith, P.M.; Sasagawa, T.; Drews, B.C.; Hua, A.; Stern, J.R. & Chen, J.Y. (2004). High-performance TFTs fabricated on plastic substrates. *IEEE Electron Device Lett.*, Vol. 25, No. 7, pp. 486-488.

- Lee, S.; Koo, B.; Shin, J.; Lee, E.; Park, H. & Kim, H. (2006). Effects of hydroxyl groups in polymeric dielectrics on organic transistor performance. *Appl. Phys. Lett.*, Vol. 88, No. 16, p. 162109.

- Lin, C. W.; Yang, M. Z.; Yeh, C. C.; Cheng, L. J.; Huang, T. Y.; Cheng, H. C.; Lin, H. C.; Chao, T. S. & Chang, C. Y. (1999). Effects of plasma treatments, substrate types, and crystallization methods on performance and reliability of low temperature polysilicon TFTs, *Proceedings of International Electron Devices Meeting (IEDM)*, pp. 305-308, Washington DC, USA.

- Lin, S. H.; Chin, Albert; Yeh, F. S. & McAlister S. P. (2008). Good 150°C Retention and Fast Erase Charge-Trapping-Engineered Memory with Scaled Si<sub>3</sub>N<sub>4</sub>, *Proceedings of International Electron Devices Meeting (IEDM)*, pp. 843-846, San Francisco, CA, USA.

- Lin, S. H.; Chiang, K. C.; Chin, Albert; & Yeh, F. S. (2009). High density and low leakage current MIM capacitor using stacked TiO<sub>2</sub>/ZrO<sub>2</sub> insulators. *IEEE Electron Device Lett.*, Vol. 30, No. 7, pp. 715-717.

- Mizukami, M.; Hirohata, N.; Iseki, T.; Ohtawara, K.; Tada, T.; Yagyu, S.; Abe, T.; Suzuki, T.; Fujisaki, Y.; Inoue, Y.; Tokito, S. & Kurita, T. (2006). Flexible AM OLED panel driven by bottom-contact OTFTs, *IEEE Electron Device Lett.*, Vol. 27, No. 4, pp. 249-251.

- Na, J. H.; Kitamura, M.; Lee, D. & Arakawa, Y. (2007). High performance flexible pentacene thin-film transistors fabricated on titanium silicon oxide gate dielectrics. *Appl. Phys. Lett.*, Vol. 90, No. 16, p. 163514.

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya. T.; Hirano M. & Hosono H. (2004). Roomtemperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. *Nature*, Vol. 432, pp. 488-392.

- Schön, J. H. & Kloc, H. (2001). Fast organic electronic circuits based on ambipolar pentacene field-effect transistors. *Appl. Phys. Lett.*, Vol. 79, No. 24, p. 4043.

- Wu, Y. H.; Yang, M. Y.; Chin, Albert & Chen, W. J. Electrical characteristics of high quality La<sub>2</sub>O<sub>3</sub> dielectric with equivalent oxide thickness of 5Å. (2000) *IEEE Electron Device Lett.*, Vol. 21, No. 7, pp. 341-343.

- Yin, H; Kim, S.; Lim, H.; Min, Y.; Kim, C. J.; Song, I.; Park, J.; Kim, S. J.; Tikhonovsky, A.; Hyun, J. & Park Y. (2008). Program/erase characteristics of amorphous gallium indium zinc oxide nonvolatile memory. *IEEE Trans. Electron Devices*, Vol. 55, No. 8, pp. 2071-2077.

- Yu, D. S.; Chin, Albert; Wu, C. H.; Li, M.-F.; Zhu, C.; Wang, S. J.; Yoo, W. J.; Hung B. F. & McAlister, S. P. (2005). Lanthanide and Ir-based dual metal-gate/HfAlON CMOS with large work-function difference, *Proceedings of International Electron Devices Meeting (IEDM)*, pp. 649-652, Washington DC, USA.

- Zhou L.; Park, S.; Bai, B.; Sun, J.; Wu, S. C.; Jackson, T. N.; Nelson, S.; Freeman, D. & Hong, Y. (2005). Pentacene TFT driven AM OLED displays. *IEEE Electron Device Lett.*, Vol. 26, No. 9, pp. 640-642.

# IntechOpen

# IntechOpen

## IntechOpen

Polymer Thin Films Edited by Abbass A Hashim

ISBN 978-953-307-059-9 Hard cover, 324 pages **Publisher** InTech **Published online** 01, April, 2010 **Published in print edition** April, 2010

This book provides a timely overview of a current state of knowledge of the use of polymer thin film for important technological applications. Polymer thin film book covers the scientific principles and technologies that are necessary to implement the use of polymer electronic device. A wide-ranging and definitive coverage of this emerging field is provided for both academic and practicing scientists. The book is intended to enable readers with a specific background, e.g. polymer nanotechnology, to become acquainted with other specialist aspects of this multidisciplinary field. Part A of the book covers the fundamental of the key aspect related to the development and improvement of polymer thin film technology and part B covers more advanced aspects of the technology are dealt with nano-polymer layer which provide an up-to-date survey of current research directions in the area of polymer thin film and its application skills.

#### How to reference

In order to correctly reference this scholarly work, feel free to copy and paste the following:

Albert Chin (2010). High Performance Organic Thin-Film Transistors and Nonvolatile Memory Devices Using High-Dielectric Layers, Polymer Thin Films, Abbass A Hashim (Ed.), ISBN: 978-953-307-059-9, InTech, Available from: http://www.intechopen.com/books/polymer-thin-films/high-performance-organic-thin-film-transistors-and-nonvolatile-memory-devices-using-high-dielectric-

#### InTech Europe

University Campus STeP Ri Slavka Krautzeka 83/A 51000 Rijeka, Croatia Phone: +385 (51) 770 447 Fax: +385 (51) 686 166 www.intechopen.com

#### InTech China

Unit 405, Office Block, Hotel Equatorial Shanghai No.65, Yan An Road (West), Shanghai, 200040, China 中国上海市延安西路65号上海国际贵都大饭店办公楼405单元 Phone: +86-21-62489820 Fax: +86-21-62489821 © 2010 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the <u>Creative Commons Attribution-NonCommercial-ShareAlike-3.0 License</u>, which permits use, distribution and reproduction for non-commercial purposes, provided the original is properly cited and derivative works building on this content are distributed under the same license.

## IntechOpen