### we are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

122,000

135M

Our authors are among the

TOP 1%

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

### Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

(1)

### Ultralow-power LSI Technology with Silicon on Thin Buried Oxide (SOTB) CMOSFET

Takashi Ishigaki, Ryuta Tsuchiya, Yusuke Morita, Nobuyuki Sugii and Shin'ichiro Kimura Central Research Laboratory, Hitachi, Ltd. Japan

#### 1. Introduction

For a variety of applications from mobile to high-performance computing, the power consumption of very-large-scale-integrated (VLSI) circuits is a serious issue. The scaling rule has been a paradigm for miniaturizing complementary metal-oxide-semiconductor (CMOS) field-effect-transistors (FETs) in VLSI circuits for a long period. In the ideal scaling rule, the supply voltage  $V_{dd}$  should decrease in proportion to the miniaturization of the transistor. This  $V_{dd}$  reduction has roughly been successful so far. In extremely scaled transistors such as those in the 45-nm logic node and beyond, however, it is very difficult to further decrease  $V_{dd}$ . Unless  $V_{dd}$  is reduced with the scaling rule, the power consumption of the LSI will increase significantly due to an increase in both operational and standby-leakage power (Sakurai, 2004; Chen, 2006). The primary cause of this difficulty is widely recognized as the increase in threshold voltage ( $V_{th}$ ) variation of CMOSFETs, because  $V_{dd}$  should be set higher considering the margin to the increase  $V_{th}$  variation (Takeuchi et al., 1997).

Variation of transistor characteristics, primarily  $V_{\text{th}}$  variation, is increasing substantially in sub-100-nm technologies. This makes the  $V_{\text{dd}}$  reduction, required by the scaling rule, difficult, and significantly increases the power consumption of an LSI chip. Here, power consumption *P* of an inverter, which is the representative LSI unit circuit, is defined as

#### $P = CV_{\rm dd}^2 f + I_{\rm leak} V_{\rm dd}$

where *C*, *f*, and  $I_{\text{leak}}$  are load capacitance, operation frequency, and leakage current, respectively. The first and second terms on the right-hand side represent operational and standby power, respectively. As the scaling proceeds, *C* and  $I_{\text{leak}}$  decrease due to the size reduction of transistors, and *f* increases. Since the miniaturization enables the number of circuits crammed onto a single chip to increase exponentially, it is extremely important to lower  $V_{\text{dd}}$  to maintain power consumption of an LSI chip (Moore, 1979). In the ITRS 2008 roadmap, the rate of  $V_{\text{dd}}$  reduction below 1 V is forecasted to be extremely small.

The origin of  $V_{\text{th}}$  variation is not only due to lithographic variations and layer thicknesses, but also due to line edge roughness (LER) and random dopant fluctuation (RDF) (Asenov et al., 2003; Mizuno et al., 1994). In particular, it has been pointed out that the  $V_{\text{th}}$  variation caused by the number and special distribution of impurities in the channel of transistors (RDF) becomes serious with the scaling. The magnitude of the  $V_{\text{th}}$  variation is described by

Source: Solid State Circuits Technologies, Book edited by: Jacobus W. Swart, ISBN 978-953-307-045-2, pp. 462, January 2010, INTECH, Croatia, downloaded from SCIYO.COM

(3)

standard deviation  $\sigma V_{\text{th}}$ , since the distribution of  $V_{\text{th}}$  usually shows a normal distribution. The  $V_{\text{th}}$  variation becomes small with the wider area of the gate because the impurity distribution should be random. This relationship is well known (Pelgrom et al., 1989) and is defined as

$$\sigma V_{\rm th} = A_{\rm Vt} / (L_{\rm g} W_{\rm g})^{1/2} \tag{2}$$

where  $L_g$  and  $W_g$  are the length and width of a gate, and the gradient  $A_{Vt}$  is called the Pelgrom coefficient. Moreover, in conventional bulk CMOSFETs, the following relationship exists

$$A_{\rm Vt} \propto t_{\rm ox} (N_{channel})^{1/4}$$

where  $t_{ox}$  and  $N_{channel}$  are the thickness of a gate oxide and a channel impurity density. Because  $N_{channel}$  has increased to suppress the short channel effect (SCE),  $A_{Vt}$  has increased with scaling. Thus, it is understood that the present  $V_{th}$  variation problem is inevitably caused by the conventional bulk CMOSFETs' miniaturization.

To solve these problems, it is necessary to first decrease the  $V_{th}$  variation due to size variations by suppressing SCE, and secondly to decrease RDF by lowering the impurity densities of the channel. FinFETs, which have strong immunity from SCE without increasing the impurity density of the channel, are reported to have low  $V_{th}$  variation (Thean et al., 2006). On the other hand, to continue to both improve the speed and reduce the power from the system-LSI designer's viewpoint, it is necessary to set  $V_{th}$  and  $V_{dd}$  to the best value in every circuit block or set of transistors in LSI circuits. The multiple  $V_{th}$  design, such as that with two or three kinds of  $V_{th}$  setting, is already indispensable. Additionally, a technique that controls  $V_{dd}$  adaptively according to the state of operation has also been applied (Nakai et al., 2005). A technique to apply substrate bias  $V_{bb}$  to control  $V_{th}$  flexibly is used in some applications, also (Miyazaki et al., 2000). This  $V_{bb}$  control technique is a strong tool that can minimize the performance deviation due to temperature fluctuation as well as the variation of each chip. However, in present scaled bulk CMOSFETs, it is difficult to apply  $V_{bb}$  because of the increase in the junction leakage current between the source/drain and the substrate.

To solve the power consumption and  $V_{\text{th}}$  variation issues, we have proposed a fully depleted silicon-on-insulator (FD-SOI) CMOSFET with an ultrathin buried oxide (BOX), named "silicon on thin BOX (SOTB)". In this chapter, we will describe the features, process and characteristics of the SOTB CMOSFET. Its wide-range back-gate controllability, which enables the optimization of both performance and power after fabrication, will also be described. In addition, to solve some intrinsic problems with SOI technology such as poor electrostatic discharge (ESD) susceptibility and low breakdown voltage, an SOTB/bulk hybrid technology for system-on-chip (SoC) applications will be presented. In the later part of this chapter, we will show the variability reduction and back-gate bias control in the SOTB scheme and demonstrate its impact on the power reduction of VLSI circuits.

#### 2. SOTB CMOSFET

#### 2.1 Features of SOTB CMOSFET

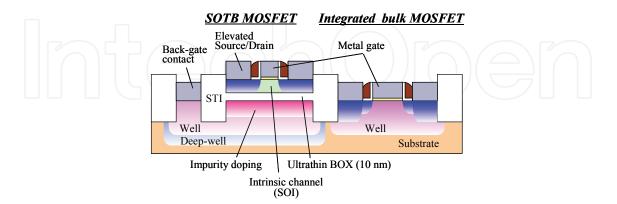

To solve the  $V_{\text{th}}$  variation problem due to RDF and satisfy the demand from circuit designers, we have proposed the SOTB CMOSFET (Tsuchiya et al., 2004; Ishigaki et al., 2008; Morita et al., 2008). Figure 1 shows a schematic cross-section of the SOTB structure.

Ultrathin SOI and BOX layers make the transistor highly immune from SCE, and its intrinsic channel without halo implant suppresses the  $V_{\text{th}}$  variation due to RDF. The thin BOX and impurity doping in the substrate just beneath the thin BOX enables a multiple  $V_{\text{th}}$  design. This thin BOX and the doped region also enable the wide-range back-gate controllability which realizes optimization of both performance and power after fabrication.

Fig. 1. Schematic cross-sectional view of hybrid SOTB/bulk CMOSFETs.

Some intrinsic problems with (FD-) SOI technology such as poor electrostatic discharge (ESD) susceptibility and low breakdown voltage are well known (Yoshimi et al., 1990). Such adverse effects can be easily avoided by combining bulk technology on the same wafer. The previous approach to integrating SOI and bulk technologies required the use of selective epitaxial growth to compensate for the height difference (Yang et al., 2003), which significantly increases process complexity. In this SOTB structure, bulk CMOSFETs for high-voltage I/O operation, ESD protection, and analog circuits can be easily integrated by removing the thin SOI/BOX layers. This simplified SOTB/bulk hybrid technology is preferable for SoC applications because no design change for the conventional peripheral circuits is required.

Regarding the isolation between transistors and back-gate contacts, this SOTB technology uses a conventional shallow-trench isolation (STI) process similar to the bulk technology. The slight change is that the trench is formed by dry etching three layers: the SOI, BOX, and substrate, as shown in Fig. 1. Consequently, the isolation between devices on the SOI and back-gate contacts is ensured by STI. The well region, acting as a back gate and ground plane, was formed beneath the BOX layer and connected to the region of the back-gate contact through the area underneath the STI. The back-gates for NMOS and PMOS are also isolated by STI. This back-gate contact structure in SOTB technology can be fabricated with the same mask layout as the conventional bulk CMOSFET. A triple-well structure is also adopted to prevent leakage for back-gate biasing.

#### 2.2 Device design and fabrication

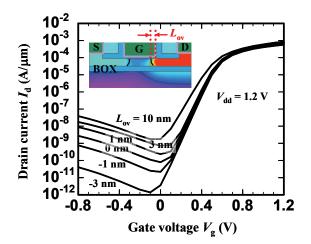

For low-standby power (LSTP) applications, a single mid-gap metal gate with an intrinsic channel is easily introduced in the fabrication process and is suitable for the desired  $V_{\text{th}}$  (Fenouillet-Beranger et al., 2008). However, unless the gate-induced drain leakage (GIDL) current is suppressed to less than the subthreshold leakage, off-current  $I_{\text{off}}$  cannot be reduced at the desired  $V_{\text{th}}$ . GIDL increases when gate bias  $V_{\text{g}}$  becomes negative (for NMOS, vice versa for PMOS). This is because of band-to-band tunneling in and around the drain junction below the gate edges. This leakage current is a source-to-drain current in SOI

structures because of the BOX layer, unlike the bulk transistor in which the GIDL current flows to the substrate. In the SOTB structures, the intrinsic channel is also effective to suppress GIDL because of low electric fields around the drain junction below the gate edges. Note that in an SOTB device, it is unnecessary to consider either the junction depth (because it is controlled only by SOI thickness) or the channel-impurity profile (because the SOTB device has an intrinsic channel with no halo implant). Therefore, the control of GIDL in an SOTB is simple. Only the gate overlap length  $L_{ov}$ , which is defined as the length of the overlapped region between gate and source/drain extensions, needs to be controlled. Figure 2 plots the calculated GIDL with various  $L_{ov}$  values by using the ATLAS simulation (http://www.silvaco.com). The parameters used in this calculation are as follows:  $L_g$ , SOI

(http://www.silvaco.com). The parameters used in this calculation are as follows:  $L_g$ , SOI thickness, BOX thickness, and gate oxide thickness are 65, 15, 10, and 2 nm at  $V_{dd}$  = 1.2 V, respectively. The inset shows the potential distribution with  $L_{ov}$  of 10 nm when  $V_g$  is -0.5 V and  $V_{dd}$  is 1.2 V. It is shown that the potential on the drain edge is steep due to the bias difference between the gate and drain. When  $L_{ov}$  is 10 nm,  $I_{off}$  (at  $V_g$  = 0 V) increases because of the subthreshold leakage and the GIDL since the large overlap enhances both the SCE and the GIDL. By decreasing  $L_{ov}$  to less than a few nm, GIDL can be reduced sufficiently. At the same time, however, on-state current  $I_{on}$  also decreases. Therefore, this indicates that  $L_{ov}$  should be carefully optimized for a target specification.

Fig. 2. Simulated NMOS  $I_d$  –  $V_g$  characteristics as a function of gate overlap length  $L_{ov}$  at  $V_{dd}$  = 1.2 V. The inset shows the potential distribution in SOTB structure at  $V_g$  = -0.5 V.

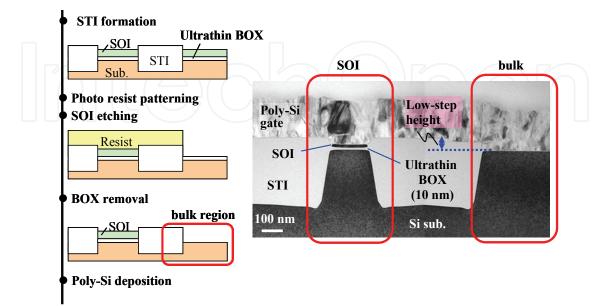

Figure 3 shows a process flow and a cross-sectional transmission electron microscope (TEM) image of an SOI/bulk hybrid structure. After the STI formation, the SOI layers ( $t_{SOI} \sim 12 \text{ nm}$ ) on both the well contact and bulk active regions were removed by dry etching using a BOX layer ( $t_{BOX} \sim 10 \text{ nm}$ ) as a stopper, followed by the removal of the BOX layer. Due to the small step height of 22 nm ( $t_{SOI} + t_{BOX}$ ), gate patterning can easily be performed on both the SOI and bulk regions simultaneously. This process enables the SOTB/bulk hybrid structure to be fabricated without requiring epitaxial growth to compensate for the height difference. The SOI region is on the left side of the TEM image, and the integrated bulk regions was confirmed. These integrated hybrid bulk CMOSFETs with a 7.5-nm-thick gate dielectric were fabricated on the exposed surface of the silicon support wafer by removing SOI/BOX layers. The quality of the surface after the BOX removal is a concern in this process. Carrier mobilities as high as a universal curve and gate oxide interface trap density ( $D_{it}$ ) as low as

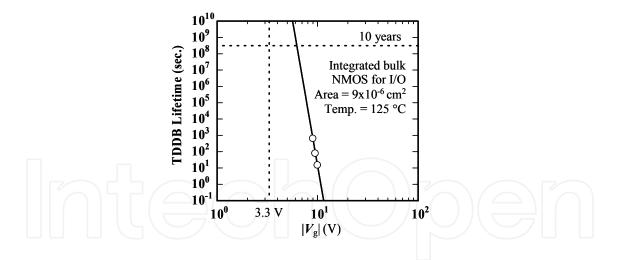

$10^{11}$  eV<sup>-1</sup>cm<sup>-2</sup> were confirmed with no sacrificial oxidation of the surface, indicating that little damage was caused by dry etching during the SOI-layer removal (Ishigaki et al., 2008). A sufficiently long time-dependent dielectric breakdown (TDDB) lifetime is ensured at  $V_g$  = 3.3 V, as shown in Fig. 4.

Fig. 3. Process flow of hybrid SOI/bulk fabrication and a cross-sectional TEM image of poly-Si gate on hybrid SOI/bulk regions.

Fig. 4. TDDB lifetime of integrated bulk NMOS for I/O operation.

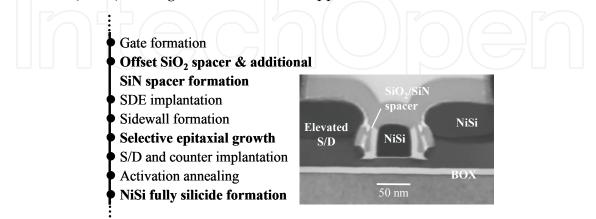

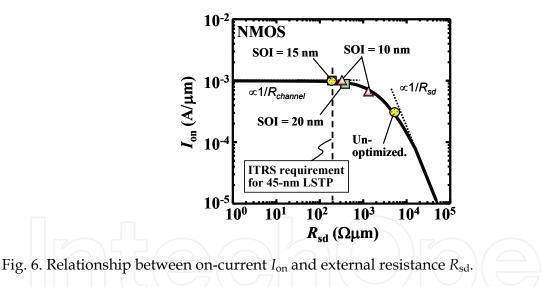

Figure 5 shows the following process steps as well as a cross-sectional TEM image of a fabricated 50-nm-gate-length SOTB MOSFET. In the dual oxidation process, SiON gate dielectrics were formed at an equivalent oxide thickness (EOT) of 1.9 nm for SOTB core CMOSFETs, and 7.5 nm for bulk I/O CMOSFETs. To precisely control  $L_{ov}$ , an additional SiN offset spacer was formed after the first SiO<sub>2</sub> spacer formation and before the source/drain extension implantation. After forming a sidewall, an elevated source/drain structure was formed by selective epitaxial growth to obtain low external resistance. To prevent recesses in the SOI, the conditions for gate- and sidewall- etching and precleaning before epitaxy were

carefully optimized, resulting in a low external resistance, as shown in Fig. 6. In low-power FD-SOIs with intrinsic channels, no dual metal technology between NMOS and PMOS gates, such as nickel silicide phase control (Veloso et al., 2006), is required when using nickel silicide as a gate electrode material. The gate poly-Si and the source/drain epitaxial Si were set to their optimal heights before gate-cap removal and fully silicided simultaneously in a single step without using chemical mechanical polishing (CMP). The metal inserted polysilicon stack (MIPS) metal-gate structure is also applicable for SOTB CMOSFETs.

#### 3. Characteristics of SOTB CMOSFET

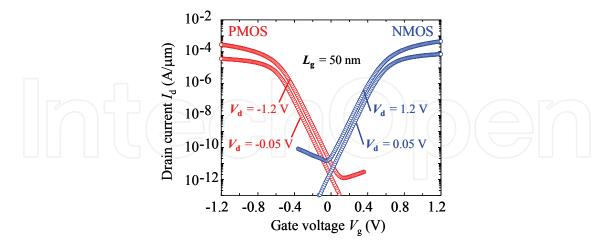

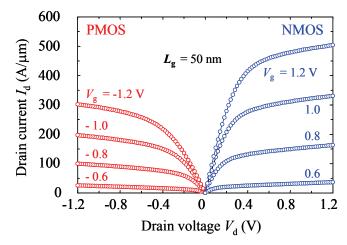

The typical subthreshold characteristics of the 50-nm-gate-length SOTB CMOSFETs at  $V_{dd}$  = 1.2 V are plotted in Fig. 7. The desired symmetrical characteristics were successfully obtained with a single Ni FUSI gate. The off-state drain currents were less than 20 pA/µm due to the reduction of GIDL with properly controlled  $L_{ov}$ . At the same time, comparable on-currents were obtained with the conventional bulk CMOSFETs. The  $I_{off}$  could be further reduced to 1 pA/µm by reducing  $L_{ov}$  (Ishigaki et al., 2009). These  $I_{on}/I_{off}$  values are in good agreement with the data based on bulk or FD-SOI technology for LSTP applications (Kimizuka et al., 2005). These SOTB CMOSFETs also suppressed the SCE even with the intrinsic channel because of the thin SOI and BOX layers. Figure 8 demonstrates that the

SOTB CMOSFET is free from the self-heating effect thanks to the thin BOX. That is, negative drain conductance (decreasing  $I_d$  with increasing  $V_d$ ) was not observed.

Fig. 7. Typical  $I_d$ - $V_g$  characteristics of 50-nm-gate-length SOTB CMOSFET.

Fig. 8.  $I_d$ - $V_d$  characteristics of 50-nm-gate-length SOTB CMOSFET. No self-heating is evident due to the thin BOX.

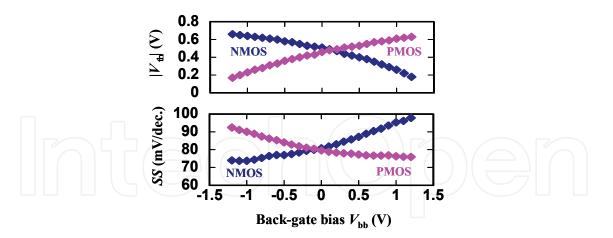

In the SOTB scheme, time-to-time or area-to-area (including die-to-die or wafer-to-wafer) device characteristics can be widely controlled using the back-gate bias  $V_{bb}$ . In particular, forward back-gate bias can be effectively used because there is no substrate leakage. Note that a forward bias higher than 0.6 V can never be applied in conventional bulk CMOSFETs owing to the significant increase in p-n junction leakage current from source to substrate. The dependences of  $V_{th}$  and the subthreshold slope (*SS*) of a 50-nm-gate-length SOTB CMOSFET on  $V_{bb}$  at  $V_{dd}$  = 1.2 V are shown in Fig. 9. By applying a reverse  $V_{bb}$ ,  $V_{th}$  increased to above 0.6 V, and the *SS* decreased to less than 80 mV/decade. In contrast, by applying a forward back-gate bias of 1.2 V,  $V_{th}$  can be lowered by more than 0.3 V while keeping the *SS* small. In such a high forward bias, there is no increase in the substrate leakage currents.

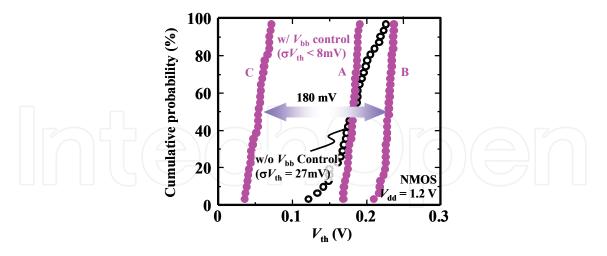

As for conventional bulk structures, reverse biasing can be used to reduce the standby leakage after fabrication. However, this is less effective because both  $V_{\text{th}}$  variation and GIDL increases (Yasuda et al., 2007). In the SOTB scheme, GIDL is sufficiently suppressed by the intrinsic channel and the controlled  $L_{\text{ov}}$ , and forward  $V_{\text{bb}}$  is also effective in adjusting the  $V_{\text{th}}$  variation. The die-to-die compensation for the  $V_{\text{th}}$  of each chip is demonstrated in Fig. 10.

Fig. 9. Dependences of  $V_{\text{th}}$  and *SS* for a 50-nm-gate-length SOTB CMOSFET as a function of back-gate bias  $V_{\text{bb}}$  at  $V_{\text{dd}}$  = 1.2 V.

Each circle represents a 50-nm-gate-length NMOS of a chip. The open circles indicate the  $V_{\text{th}}$  distribution without  $V_{bb}$  control, and the closed circles indicate the distribution with  $V_{bb}$  control, that is, when the  $V_{bb}$  was adjusted for each transistor to approach the target  $V_{th}$ . The  $V_{bb}$  values range from -1.2 to 1.2 V, in 0.2-V increments. Without  $V_{bb}$  control, the range of  $V_{th}$  distributions is about 0.1 V due to size (gate length or layer thicknesses such as SOI) variations or channel dose fluctuations. The standard deviation  $\sigma V_{th}$  with  $V_{bb}$  control was suppressed to 1/4 (case A) even with such a wide  $V_{bb}$  step. In addition, the typical  $V_{th}$  can be set arbitrarily within a range of 0.18 V (cases B and C), which is larger than the 0.1 V of the original  $V_{th}$  distribution, while keeping the variation suppressed. It is assumed, for instance, that setting the optimum  $V_{bb}$  according to the speed and the power of the chip will improve the yield.

Fig. 10.  $V_{\text{th}}$  shift and variation reduction of Poly-Si gate SOTB NMOS using back-gate bias  $V_{\text{bb}}$  ( $V_{\text{bb}}$ : -1.2 <  $V_{\text{bb}}$  < 1.2 V, increments = 0.2 V).

#### 4. Reduction of power consumption

The nominal  $V_{\text{th}}$  cumulative probability plot (not shown) of SOTB CMOSFETs indicates that the distribution is random and SCE is suppressed even down to 50 nm (Morita et al., 2008).

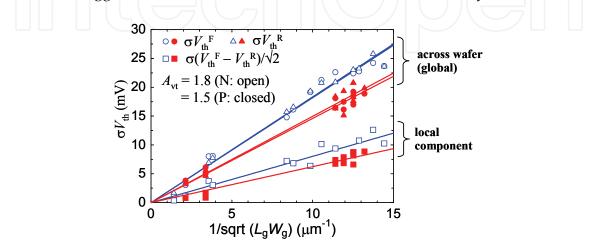

The Pelgrom plot is shown in Fig. 11. The slope of the plot, the Pelgrom coefficient  $A_{vt}$ , is 1.8 and 1.5 mVµm for NMOS and PMOS, respectively. These values are about half those of conventional bulk CMOSFETs of the same technology generation due to the intrinsic channel without halo implant. Impurities below the BOX layer have a small impact on the variability. The local component of variation is also plotted. To extract the local variation of  $V_{th}$ , the difference between the forward and the reverse measurement by exchanging the source and drain was used (Tanaka et al., 2000). It has already been confirmed that this method simply represents the local variation of adjusting pair transistors (Sugii et al., 2008). These results suggest the SOTB CMOSFET is robust in terms of variability.

Fig. 11. Pelgrom plot of SOTB CMOSFETs for both global and local components.

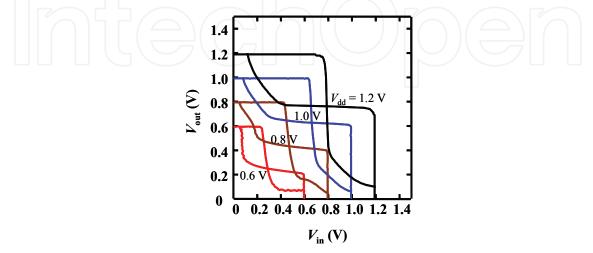

Because static random access memory (SRAM) has been integrated in recent VLSI circuits with large capacities occupying large areas, reducing the power consumption of SRAMs is becoming increasingly important. Moreover, since the SRAM circuit is most sensitive to the local  $V_{\text{th}}$  variation, it is assumed that achieving low  $V_{\text{dd}}$  is most difficult with SRAM. Figure 12 plots the characteristics of 6T-SOTB SRAM cells 0.99 µm<sup>2</sup> in size. The static noise margins (SNM) of 0.357 V at  $V_{\text{dd}} = 1.2$  V and 0.142 V at  $V_{\text{dd}} = 0.6$  V indicate a much more stable operation in comparison with conventional bulk ones. The fail bit count (FBC) analysis indicated that the SOTB-SRAM can operate as low as 0.6 V, whereas the bulk SRAM with the same cell size operates at 1.1 V (Tsuchiya et al., 2009).

Fig. 12. Measured butterfly curves of 50-nm-gate-length SOTB SRAM cell.

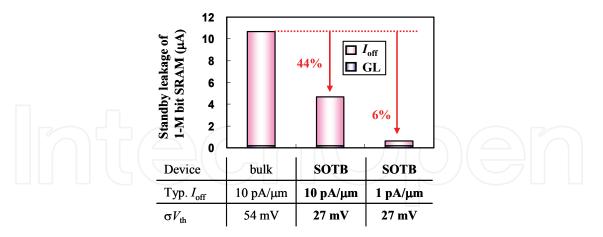

The variability of SOTB CMOSFETs has a significant impact on standby power consumption. The total standby leakage of a conventional 6T-SRAM cell is roughly expressed as

$$I_{\text{standby}} = 3I_{\text{off}} + 2I_{\text{gate}} \tag{4}$$

where  $I_{gate}$  is the gate leakage when the gate node of a transistor is high. We calculated the standby leakage of an SRAM between SOTB and bulk devices, taking variability into account. When  $V_{th}$  decreases from a typical value (ideally at the minimum  $I_d$  point determined both by subthreshold and GIDL currents),  $I_{off}$  increases on the subthreshold slope of 80 mV/decade. On the other hand,  $I_{off}$  also increases with larger  $V_{th}$  because of the GIDL with a slope of 400 mV/decade. The summation of off-currents taking  $V_{th}$  distribution into account is expressed as

$$\Sigma I_{\text{off}} = \int P\left(\Delta V_{\text{th}}\right) \times I_{\text{off}}\left(\Delta V_{\text{th}}\right)$$

(5)

where *P* is a probability of  $V_{\text{th}}$  in the distribution, and  $\Delta V_{\text{th}}$  is the deviation from the typical  $V_{\text{th}}$ . The  $\sigma V_{\text{th}}$  of SOTB and bulk devices is 27 and 54 mV, respectively.  $I_{\text{gate}}$  is calculated as a constant without taking variability into account because its value is much smaller for LSTP applications, where  $J_{\text{g}}$  is 2 x 10<sup>-3</sup> A/cm2. The integrated standby leakage of 1-Mbit SRAM is shown in Fig. 13. One typical  $I_{\text{off}}$  of SOTB devices is calculated as 10 pA/µm compared with bulk devices. The other typical  $I_{\text{off}}$  value of SOTB devices is 1 pA/µm. When the typical  $I_{\text{off}} = 10 \text{ pA}/\mu\text{m}$ , the standby leakage of the SOTB device is 44% that of the bulk ones. This result indicates that reducing  $\sigma V_{\text{th}}$  by half also reduces the standby leakage by half. Moreover, when the typical  $I_{\text{off}}$  of an SOTB device = 1 pA/µm, the standby leakage can be further reduced to 6%. In the case of  $I_{\text{off}} = 1 \text{ pA}/\mu\text{m}$ , which indicates a lower on-state current, the driving performance can be boosted by using back-gate biasing in the SOTB technology.

Fig. 13. Estimated standby leakage of 1-Mbit SRAM taking  $V_{\rm th}$  variability into account.

#### 5. Conclusion

Recently, the scalability of CMOSFETs has become a topic of utmost importance. In SOTB technology, scalability can be pursued by reducing the SOI and BOX thicknesses. The minimum SOI thickness is considered to be 6 nm, after which the influence of the quantum effect or mobility degradation appears (Uchida et al., 2001). Given this value and

considering the thickness variation, the minimum gate length of the SOTB CMOSFET is expected to be about 20 nm while maintaining a small  $V_{\text{th}}$  variation (Sugii et al., 2009). In addition, the applicability of back-gate biasing is important. Even if the uniformity of transistors is not maintained, the characteristic variation can be eased by correcting  $V_{bb}$ . In this chapter, it was shown that both operating voltage and standby power can be substantially reduced due to the low variability of the SOTB CMOSFET. This indicates that

the power consumption of VLSI circuits can be drastically reduced. Moreover, when combined with  $V_{bb}$  control, it is possible to obtain the optimum power efficiency by flexibly changing  $V_{dd}$  and  $V_{th}$  to the operation situation. It is hoped that these flexible voltage controls will be applied to VLSI circuits in the future to meet the increasingly complex application demands.

#### 6. Acknowledgements

The authors would like to thank the staff of Renesas Technology and the Hitachi Central Research Laboratory (HCRL) for fabricating the devices. We would also like to thank K. Torii of HCRL and T. Onai, M. Odaka and K. Kasai of the Hitachi R&D group for their encouragement. This work was partly supported by the Ministry of Education, Culture, Sports, Science and Technology of Japan.

#### 7. References

- Asenov, A. et al. (2003). Intrinsic parameter fluctuations in decananometer MOSFETs introduced by gate line edge roughness. *IEEE Trans Electron Devices*, 50, pp. 1254-1260, 0018-9383

- Chen, T. C. (2006). Where CMOS is going : trendy hype vs. real technology, *Plenary of ISSCC*, pp. 1-18, 1-4244-0079-1, San Francisco

- Fenouillet-Beranger, C. et al. (2008). FDSOI devices with thin BOX and ground plane integration for 32 nm node and below. *ESSDERC.*, pp. 206-209, 978-1-4244-2363-7

- Ishigaki, T. et al. (2008). Wide-range threshold voltage controllable silicon on thin buried oxide integrated with bulk complementary metal oxide semiconductor featuring fully silicided NiSi gate electrode. *Jpn J Appl Phys.*, 47(4), pp. 2585-2588

- Ishigaki, T. et al. (2009). Silicon on thin BOX (SOTB) CMOS for ultralow standby power with forward-biasing performance booster. *J. Solid-State Electronics*, 53, pp. 717-722, 0038-1101

- Kimizuka, K. et al. (2005). Ultra-Low Standby Power (U-LSTP) 65-nm node CMOS Technology Utilizing HfSiON Dielectric and Body-biasing Scheme. Proceedings of VLSI technology symp., pp. 218-219, 4-900784-00-1, Kyoto

- Miyazaki, M. et al. (2000). A 1000-MIPS/W microprocessor using speed adaptive thresholdvoltage CMOS with forward bias, *Dig. Tech. Papers IEEE Int. Solid-State Circuits Conf.*, pp. 420-421, 0-7803-5856-2

- Mizuno, T. et al. (1994). Experimental study of threshold voltage fluctuation due to statistical variation of channel dopant number in MOSFET's. *IEEE Trans Electron Devices*, 41, pp. 2216-2221, 0018-9383

- Moore, G. E. (1979). Are We Really Ready for VLSI?. Keynote Address of ISSCC, pp. 54-55

- Morita, Y. et al. (2008). Smallest *V*<sub>th</sub> variability achieved by intrinsic silicon on thin BOX (SOTB) CMOS with single metal gate, *Proceedings of VLSI technology symp.*, pp. 166-167, 978-1-4244-1802-2, Honolulu

- Nakai, M. et al. (2005). Dynamic voltage and frequency management for a low-power embedded microprocessor. *IEEE J. Solid-State Circuits*, 40, pp. 28-35, 0018-9200

- Pelgrom, M. J. M. et al. (1989). Matching properties of MOS transistors. *IEEE J. Solid-State Circuits*, 24, pp. 1433-1439, 0018-9200

- Sakurai, T. (2004). Perspectives of low-power VLSI's. *IEICE Trans. Electron.,* E87-C, pp. 429-436

- Sugii, N. et al. (2008). Comprehensive Study on Vth Variability in Silicon on Thin BOX (SOTB) CMOS with Small Random-Dopant Fluctuation: Finding a Way to Further Reduce Variation. *IEEE Trans Electron Devices*, pp. 249-252, 1-4244-2377-4, San Francisco

- Sugii, N. et al. (2009). Local Vth Variability and Scalability in Silicon on Thin BOX (SOTB) CMOS with Small Random-Dopant Fluctuation. *IEEE Trans Electron Devices*, to be published

- Takeuchi, K. et al. (1997). Channel Engineering for the Reduction of Random-Dopant-Placement-Induced Threshold Voltage Fluctuation, *Tech. Dig. Int. Electron Devices Meet.*, pp. 841-844, 0-7803-4100-7, Washington, D. C.

- Tanaka, T. et al. (2000). Direct Measurement of V<sub>th</sub> Fluctuation Caused by Impurity Positioning. *Proceedings of VLSI technology symp.*, pp. 136-137, 0-7803-6308-6, Honolulu

- Thean, A. et al. (2006). Performance and Variability Comparisons between Multi-Gate FETs and Planar SOI Transistors, *Tech. Dig. Int. Electron Devices Meet.*, pp. 881-884, 1-4244-0439-8

- Tsuchiya, R. et al. (2004). Silicon on thin BOX : a new paradigm of the CMOSFET for lowpower and high-performance application featuring wide-range back-bias control, *Tech. Dig. Int. Electron Devices Meet.*, pp. 631-634, 0-7803-8684-1, San Francisco

- Tsuchiya, R. et al. (2009). Low Voltage (*V*<sub>dd</sub>~0.6 V) SRAM Operation Achieved by Reduced Threshold Voltage Variability in SOTB (Silicon on Thin BOX). *Proceedings of VLSI technology symp.*, pp. 150-151, 978-4-86348-009-4, Kyoto

- Uchida, K. et al. (2001). Experimental evidences of quantum-mechanical effects on low-field mobility, gate-channel capacitance, and threshold voltage of ultrathin body SOI MOSFETs, *Tech. Dig. Int. Electron Devices Meet.*, pp. 633-636, 0-7803-7050-3, Washington D. C.

- Veloso, A. et al. (2006). Dual work function phase controlled Ni-FUSI CMOS (NiSi NMOS, Ni<sub>2</sub>Si or Ni<sub>32</sub>Si<sub>12</sub> PMOS): Manufacturability, Reliability & Process Window Improvement by Sacrificial SiGe cap. *Proceedings of VLSI technology symp.*, pp. 116-117, 1-4244-0005-8, Honolulu

- Yang, M. et al. (2003). High Performance CMOS Fabricated on Hybrid Substrate With Different Crystal Orientations, *Tech. Dig. Int. Electron Devices Meet.*, pp. 453-456, 0-7803-7872-5, Washington D. C.

- Yasuda, Y. et al. (2007). Design methodology of body-biasing scheme for low power system LSI with Multi-*V*<sub>th</sub> transistors. *IEEE Trans Electron Devices*, 54(11), pp. 2946-2952, 0018-9383

- Yoshimi, M. et al. (1990). Analysis of the drain breakdown mechanism in ultra-thin-film SOI MOSFETs. *IEEE Trans Electron Devices*, 37, pp. 2015-2021, 0018-9383

Solid State Circuits Technologies Edited by Jacobus W. Swart

ISBN 978-953-307-045-2 Hard cover, 462 pages **Publisher** InTech **Published online** 01, January, 2010 **Published in print edition** January, 2010

The evolution of solid-state circuit technology has a long history within a relatively short period of time. This technology has lead to the modern information society that connects us and tools, a large market, and many types of products and applications. The solid-state circuit technology continuously evolves via breakthroughs and improvements every year. This book is devoted to review and present novel approaches for some of the main issues involved in this exciting and vigorous technology. The book is composed of 22 chapters, written by authors coming from 30 different institutions located in 12 different countries throughout the Americas, Asia and Europe. Thus, reflecting the wide international contribution to the book. The broad range of subjects presented in the book offers a general overview of the main issues in modern solid-state circuit technology. Furthermore, the book offers an in depth analysis on specific subjects for specialists. We believe the book is of great scientific and educational value for many readers. I am profoundly indebted to the support provided by all of those involved in the work. First and foremost I would like to acknowledge and thank the authors who worked hard and generously agreed to share their results and knowledge. Second I would like to express my gratitude to the Intech team that invited me to edit the book and give me their full support and a fruitful experience while working together to combine this book.

#### How to reference

In order to correctly reference this scholarly work, feel free to copy and paste the following:

Takashi Ishigaki, Ryuta Tsuchiya, Yusuke Morita, Nobuyuki Sugii and Shin'ichiro Kimura (2010). Ultralowpower LSI Technology with Silicon on Thin Buried Oxide (SOTB) CMOSFET, Solid State Circuits Technologies, Jacobus W. Swart (Ed.), ISBN: 978-953-307-045-2, InTech, Available from: http://www.intechopen.com/books/solid-state-circuits-technologies/ultralow-power-lsi-technology-with-silicon-

on-thin-buried-oxide-sotb-cmosfet

#### InTech Europe

University Campus STeP Ri Slavka Krautzeka 83/A 51000 Rijeka, Croatia Phone: +385 (51) 770 447 Fax: +385 (51) 686 166 InTech China

Unit 405, Office Block, Hotel Equatorial Shanghai No.65, Yan An Road (West), Shanghai, 200040, China 中国上海市延安西路65号上海国际贵都大饭店办公楼405单元 Phone: +86-21-62489820 Fax: +86-21-62489821

www.intechopen.com

# IntechOpen

## IntechOpen

© 2010 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the <u>Creative Commons Attribution-NonCommercial-ShareAlike-3.0 License</u>, which permits use, distribution and reproduction for non-commercial purposes, provided the original is properly cited and derivative works building on this content are distributed under the same license.

# IntechOpen