We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

122,000

Our authors are among the

TOP 1%

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

### Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

### The Evolution of Theory on Drain Current Saturation Mechanism of MOSFETs from the Early Days to the Present Day

Peizhen Yang<sup>1</sup>, W.S. Lau<sup>1</sup>, Seow Wei Lai<sup>2</sup>, V.L. Lo<sup>2</sup>, S.Y. Siah<sup>2</sup> and L. Chan<sup>2</sup> <sup>1</sup>Nanyang Technological University, <sup>2</sup>Chartered Semiconductor Manufacturing Singapore

#### 1. Introduction

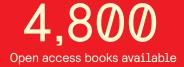

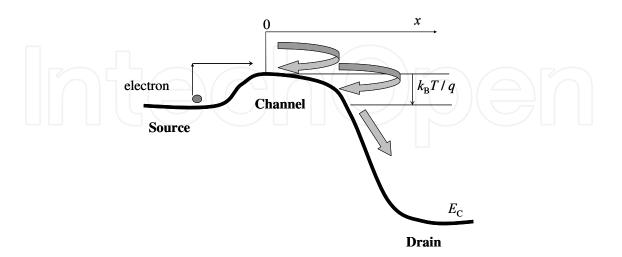

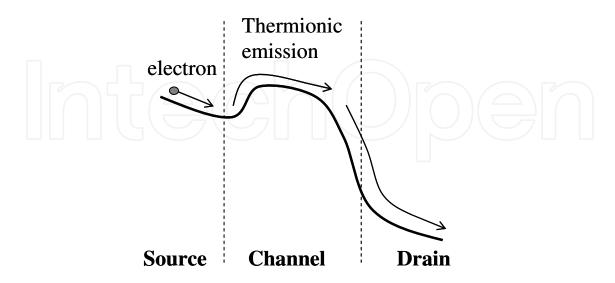

Metal-oxide-semiconductor (MOS) digital logic is based on the enhancement-mode MOS transistors. During the past 40 years, the gate length of Si-based MOS transistors has been scaled down from about 10 µm to below 0.1 µm (100 nm). Currently, MOS transistors fabricated by 45 nm CMOS technology are readily available from various silicon foundries. Moreover, Taiwan Semiconductor Manufacturing Company (TSMC) has successfully developed 28 nm CMOS technology using the conventional silicon oxynitride as the gate insulator with polysilicon gate (Wu et al., 2009). IBM has demonstrated the use of high-K dielectric as the gate insulator with metal gate for their sub-22 nm CMOS technology (Choi et al., 2009). SEMATECH has developed their 16 nm CMOS technology using high-K/metal gate (Huang et al., 2009). Furthermore, several research groups have already reported on the development of 10 nm planar bulk MOS transistors (Wakabayashi et al., 2004; Wakabayashi et al., 2006; Kawaura et al., 2000). It has been reported using a hypothetical double-gate MOS transistor that a direct source-drain (S/D) tunneling sets an ultimate scaling limit for transistor with gate length below 10 nm (Jing & Lundstrom, 2002). Aggressive scaling brings about significant improvement in the integration level of Si-based MOS logic circuits. In addition, it also improves the switching speed because the drain current is increased when a smaller gate length and a smaller effective gate dielectric thickness are used. According to the conventional MOS transistor theory based on the constant electron mobility, the linear drain current (i.e. drain current at low drain voltage) will increase with the reduction of the gate length. Based on the classical concept of velocity saturation, the saturation drain current (i.e. drain current at high drain voltage) will not increase when the gate length is decreased. This theory is obviously contradictory to the experimental observation. Experimentally, we observe that the linear drain current and the saturation drain current are increased when the gate length is reduced. Hence, there is a need to investigate the drain current saturation mechanism in the nanoscale MOS transistors. First and foremost, we need to know the type of electrical conduction between the source and drain (S/D) regions for the state-of-the-art MOS transistors ( $L \ge 32$  nm). Fig. 1 shows the various types of electrical conduction between the source and the drain of a n-channel MOS (NMOS) transistor (i) thermionic emission, (ii) thermally assisted S/D tunneling and (iii) direct S/D tunneling

Source: Solid State Circuits Technologies, Book edited by: Jacobus W. Swart, ISBN 978-953-307-045-2, pp. 462, January 2010, INTECH, Croatia, downloaded from SCIYO.COM

(Kawaura & Baba, 2003). In the thermionic emission, carriers are thermally excited in the source, and then they go over the potential barrier beneath the gate. In the thermallyassisted S/D tunneling, carriers are thermally excited in the source, and then they tunnel slightly beneath the top of the potential barrier. Both thermionic emission and thermallyassisted S/D tunneling have strong temperature dependence. In contrast, the direct S/D tunneling does not need any thermal excitation and thus it has a weak dependence on temperature. Since the tunneling probability increases exponentially with decreasing potential barrier width, a decrease in the gate length will significantly increase the direct S/D tunneling and thus increase the subthreshold current (Kawaura & Baba, 2003). Fortunately, the tunneling current will only exceed the thermal current and degrade the subthreshold slope when the gate length is less than 5 nm (experimentally 4 nm and theoretically 6 nm) (Kawaura et al., 2000). Therefore, we only need to be concerned with thermionic emission between the source and the drain for the state-of-the-art MOS transistors ( $L \ge 32$  nm). This chapter will discuss the evolution of theory on drain current saturation mechanism of MOS transistors from the early days to the present day. Section 2 will give an overview of the classical drain current equations that involve the concepts of velocity saturation and pinchoff. Section 3 will address the ambiguity involving the occurrence of velocity saturation and the presence of velocity overshoot in the nanoscale transistors. Section 4 will discuss the newer drain current transport concepts such as ballistic transport and quasi-ballistic transport. Section 5 will discuss the physics behind the apparent velocity saturation observed during transistor scaling and how it differs from the classical concept of velocity saturation within a transistor. Finally, Section 6 will discuss the actual mechanism behind the drain current saturation in nanoscale transistors.

Fig. 1. Various types of electrical conduction between the source and the drain of a NMOS transistor (i) thermionic emission, (ii) thermally assisted S/D tunneling and (iii) direct S/D tunneling. Note that  $E_F$  refers to the Fermi level.  $E_c$  refers to the conduction band edge.

#### 2. Classical drain current equations for MOS transistors

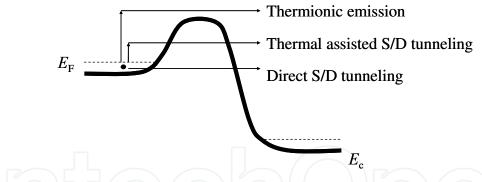

For long-channel MOS transistors ( $L = 10 \ \mu$ m), the drain current saturation is related to pinchoff (Hofstein & Heiman, 1963). A qualitative discussion of MOS transistor operation is useful, with the help of Fig.2. For NMOS transistor, a positive gate voltage ( $V_{GS}$ ) will cause inversion at the Si/SiO<sub>2</sub> interface. When the drain voltage ( $V_{DS}$ ) is small, the channel acts as a resistor and the drain current ( $I_{ds}$ ) is proportional to  $V_{DS}$  (see Fig.3). This is known as the linear operation of the MOS transistor. The equation of the linear drain current is given by (Sah, 1991, b),

The Evolution of Theory on Drain Current Saturation Mechanism of MOSFETs from the Early Days to the Present Day

$$I_{\rm ds} = \frac{\mu_{\rm eff} W C_{\rm ox}}{L_{\rm eff}} \Big[ (V_{\rm GS} - V_{\rm th}) V_{\rm DS} - 0.5 V_{\rm DS}^2 \Big]$$

(1)

where  $\mu_{\text{eff}}$  is the low-field mobility. *W* is gate width.  $L_{\text{eff}}$  is the effective channel length.  $C_{\text{ox}}$  is the gate oxide capacitance per unit area.  $V_{\text{th}}$  is the threshold voltage.

By taking the partial derivative of equation (1) with respect to  $V_{DS}$ , the expression for the drain conductance ( $g_d$ ) is as follows,

$$g_{\rm d} = \frac{\partial I_{\rm DS}}{\partial V_{\rm DS}} \bigg|_{V_{\rm GS}} = \frac{\mu_{\rm eff} W C_{\rm ox}}{L_{\rm eff}} (V_{\rm GS} - V_{\rm th} - V_{\rm DS})$$

(2)

Note that  $g_d$  decreases linearly with increasing  $V_{DS}$ . At  $V_{DS} = V_{GS} - V_{th}$ ,  $g_d$  becomes zero and thus  $V_{DS}$  loses its influence on the number of electrons that can be injected by the source. This is because the depletion layer at the drain prevents the drain electric field from pulling out more electrons from source into the channel. Since  $V_{GS}$  can decrease the potential barrier of the source-to-channel pn junction,  $I_{ds}$  can be increased by using a bigger  $V_{GS}$ . Pinchoff point occurs when the electron density in the channel dropped to around zero. The current-saturation drain voltage ( $V_{Dsat}$ ) is given by,

$$V_{\rm Dsat} = V_{\rm GS} - V_{\rm th,sat} \tag{3}$$

where  $V_{\text{th,sat}}$  is the saturation threshold voltage. The saturation drain current ( $I_{\text{ds}}$ ) is then given by (Sah,1991,b),

$$I_{\rm ds} = \frac{\mu_{\rm eff} W C_{\rm ox}}{2L_{\rm eff}} \left( V_{\rm GS} - V_{\rm th} \right)^2 \tag{4}$$

However, the constancy of  $I_{ds}$  at high  $V_{DS}$  is not maintained in the short-channel MOS transistors because the additional  $V_{DS}$  beyond  $(V_{GS} - V_{th})$  will cause the pinchoff point to move slightly towards the source in order to deplete more electrons. This slight reduction in  $L_{eff}$  can be considered negligible for the long channel transistors but it becomes significant for the short channel transistors and thus results in a small  $g_d$  when  $V_{DS} \ge V_{GS} - V_{th}$ .

Fig. 2. NMOS transistor operating in (a) the linear mode, (b) the onset of saturation, and (c) beyond saturation where the effective channel length ( $L_{eff}$ ) is reduced.  $V_{th,lin}$  and  $V_{th,sat}$  are the linear threshold voltage and the saturation threshold voltage , respectively.  $Q_{inv}$  is the inversion charge.

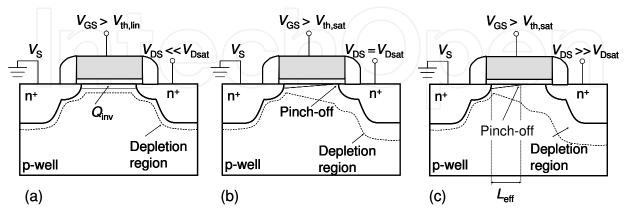

Fig. 3. Experimental  $I_{ds}$  versus  $V_{DS}$  characteristics of the NMOS transistor with physical gate oxide thickness of 300 Å (a)  $L = 10 \mu m$ ,  $W = 10 \mu m$ , (b)  $L = 3 \mu m$ ,  $W = 10 \mu m$ .

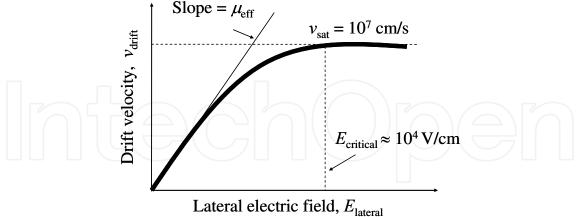

For short-channel MOS transistors ( $L < 1 \mu m$ ), (Taur et al., 1993) proposed that the drain current saturation, which occurs at  $V_{DS}$  smaller than the long-channel current-saturation drain voltage ( $V_{\text{Dsat}} = V_{\text{GS}} - V_{\text{th,sat}}$ ), is caused by velocity saturation. From Fig.4, when the lateral electric field ( $E_{lateral}$ ) is small (i.e.  $V_{DS}$  is low), the drift velocity ( $v_{drift}$ ) is proportional to  $E_{\text{lateral}}$  with  $\mu_{\text{eff}}$  as the proportionality constant. When  $E_{\text{lateral}}$  is further increased to the critical electric field ( $E_{critical}$ ) that is around 10<sup>4</sup> V/cm,  $v_{drift}$  approaches a constant known as the saturation velocity  $(v_{sat})$  (Thornber, 1980). Based on the time-of-flight measurement, at temperature of 300 K,  $v_{sat}$  for electrons in silicon is 10<sup>7</sup> cm/s while  $v_{sat}$  for holes in silicon is 6×10<sup>6</sup> cm/s (Norris & Gibbons, 1967).

Fig. 4. Schematic diagram of the drift velocity ( $v_{eff}$ ) as a function of the lateral electric field ( $E_{\text{lateral}}$ ). Note that  $E_{\text{lateral}} \approx V_{\text{DS}} / L_{\text{eff}}$ .

According to the velocity saturation model, the equation of the saturation  $I_{ds}$  for the nanoscale MOS transistor is given by (Taur & Ning, 1998, c),

$$I_{\rm ds} = v_{\rm sat} W C_{\rm ox} \left( V_{\rm GS} - V_{\rm th, sat} \right) \tag{5}$$

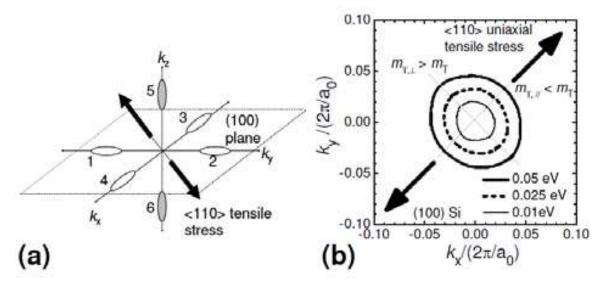

In contrast with the theoretical predictions that  $v_{sat}$  is independent of  $\mu_{eff}$  (Thornber, 1980), the experimental data show that the carrier velocity in the nanoscale transistor and the lowfield mobility are actually related (Khakifirooz & Antoniadis, 2006). This can be better understood as follows. The effects of strain on  $\mu_{\rm eff}$  can be investigated qualitatively in a simple way through Drude model,  $\mu_{\text{eff}} = q\tau / m^*$  where  $\tau$  is the momentum relaxation time, *m*<sup>\*</sup> is the effective conductivity mass, and *q* is the electron charge (Sun et al., 2007). For <110> NMOS transistors that are fabricated on (100) Si substrate, there are four in-plane conduction band valleys (1, 2, 3, 4) and two out-of-plane conduction band valleys (5, 6), as shown in Fig. 5(a). The application of <110> uniaxial tensile stress will remove the degeneracy of the conduction band valleys such that the out-of-plane valleys (5, 6) will have a lower electron energy state that the in-plane valleys (1, 2, 3, 4). Since electrons will preferentially occupy the lower electron energy state, there will be more electrons in valleys (5, 6) compared to valleys (1, 2, 3, 4) and thus the effective in-plane mass becomes smaller. Besides the strain-induced splitting of the conduction band valleys, the strain-induced warping of the out-of-plane valleys (5, 6) in (100) silicon plane also plays a part in the electron mobility enhancement. In the absence of mechanical stress, the energy surface of the out-of-plane valleys (5, 6) is " circle" shaped and the effective mass of valleys (5, 6) is  $m_{\rm T}$ . When <110> tensile stress is applied, the effective mass of valleys (5, 6) along the stress direction  $(m_{T_{1/2}})$  is decreased but the effective mass of valleys (5, 6) that is perpendicular to the stress direction  $(m_{T,\perp})$  is increased (Uchida et al., 2005). By taking into account the change in the effective mass of the out-of-plane valleys (5, 6) and the strain-induced conduction subband splitting, the low-field mobility enhancement of the bulk <110> NMOS transistors under uniaxial <110> tensile stress can be modeled (Uchida et al., 2005).

Fig. 5. Effects of <110> uniaxial tensile stress on the conduction band valleys of (100) silicon plane (a) Four in-plane valleys (1, 2, 3, 4) and two out-of-plane valleys (5,6), (b) Energy contours of the out-of-plane valleys (5, 6), which is modified from (Uchida et al., 2005). Note that  $a_0$  is the unstrained silicon lattice constant.  $k_x$ ,  $k_y$  and  $k_z$  are the wave vectors along x direction, y direction and z direction, respectively.  $m_{T,//}$  is the effective mass of valleys (5,6) along the stress direction,  $and m_{T,\perp}$  is the effective mass of valleys (5,6) in the direction that is perpendicular to the stress direction.  $m_T$  is the effective mass of valleys (5,6) in the absence of mechanical stress.

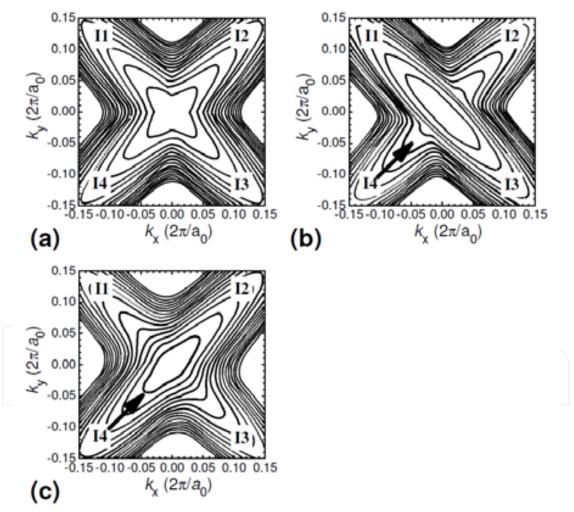

For <110> p-channel MOS (PMOS) transistors that are fabricated on (100) Si substrate, the lowest energy valence band edge has four in-plane wings (I1, I2, I3, I4) and eight out-ofplane wings (O1, O2, O3, O4). Fig.6, which is modified from (Wang et al., 2006), shows the effects of mechanical stress on the iso-energy contours of the valence band edge. In the absence of mechanical stress, the innermost contours are "star" shaped. When uniaxial compressive stress is applied along <110> channel direction, the innermost contours become oval shaped. In addition, the spacing between the contours increases for I1 and I3 wings while decreases for I2 and I4 wings. This indicates the hole energy lowering of I1 and I3 wings, and the hole energy rise of I2 and I4 wings. Since holes will preferentially occupy the lower hole energy state, there will be a carrier repopulation from I2 and I4 wings to I1 and I3 wings. As the channel length is along the direction of I2 and I4 wings, the hole mobility of <110> PMOS transistor will be improved. On the other hand, the application of uniaxial tensile stress along <110> channel direction leads to the opposite conclusion. The carriers are redistributed from I1 and I3 wings to I2 and I4 wings, leading to a hole mobility degradation in <110> PMOS transistor.

Fig. 6. Iso-energy contours separated by 25 meV in (100) silicon substrate for valence band edge, modified from (Wang et al., 2006). (a) No mechanical stress, (b) Uniaxial compressive stress along <110> direction, (c) Uniaxial tensile stress along <110> direction. Note that  $a_0$  is the unstrained silicon lattice constant.  $k_x$  and  $k_y$  are the wavevectors along x direction and y direction, respectively. The arrow indicates the direction of the mechanical stress.

In addition to the simulation results of the strain-induced variation to the conduction band edge and the valence band edge, the change in the effective carrier mass by mechanical stress can also be studied by piezoresistance measurements. Device-level piezoresistance measurements in the channel plane can be readily done. From Table I, which is modified from (Chiang et al., 2007), the piezoresistance coefficient along the channel direction ( $\pi_L$ ) is negative for NMOS transistor and is positive for PMOS transistor. This indicates that uniaxial tensile stress will decrease the effective carrier mass along the channel direction ( $m_x$ ) for NMOS transistor but will increase  $m_x$  for PMOS transistor. In the other words, <110> tensile stress will increase the electron mobility of <110> NMOS transistor while <110> compressive stress will increase the hole mobility of <110> PMOS transistor. Since the on-state current ( $I_{on}$ ) enhancement is observed in the nanoscale transistors with the implementation of various strain engineering techniques (Yang et al., 2004; C-H. Chen et al., 2004; Yang et al., 2008; Wang et al. , 2007), the carrier velocity in the nanoscale transistor must be related to the low-field mobility, and thus equation (5) needs to be modified so as to account for the strain-induced  $I_{on}$  enhancement.

Table I Device-level piezoresistance coefficients in the longitudinal direction ( $\pi_L$ ), the tranverse direction ( $\pi_T$ ), and the out-of-plane ( $\pi_{out}$ ) direction for <110> channel MOS transistors that are fabricated on (100) Si substrate (Chiang et al., 2007). The units are in 10<sup>-11</sup> m<sup>2</sup>/N. Note that "longitudinal" means parallel to the direction of channel length in the channel plane, "transverse" means perpendicular to the direction of channel length in the channel plane, and "out-of-plane" means in the direction of the normal to the channel plane.

|                 | NMOS transistor | PMOS transistor |

|-----------------|-----------------|-----------------|

| $\pi_{ m L}$    | -49             | +90             |

| $\pi_{\Gamma}$  | -16             | -46             |

| $\pi_{\rm out}$ | +87             | -44             |

However, for short channel transistors, the experimental  $V_{\text{Dsat}}$  is smaller than that predicted by equation (3) (Taur et al., 1993). Using the concept of velocity saturation, (Suzuki & Usuki, 2004) proposed an equation for  $V_{\text{Dsat}}$  that can account for the disparity between the experimental  $V_{\text{Ds}}$  and the  $V_{\text{Dsat}}$  that is predicted by equation (3).

$$V_{\text{Dsat}} = \frac{V_{\text{GS}} - V_{\text{th,sat}}}{0.5 + \sqrt{0.25 + \frac{\mu_{\text{eff}} \left( V_{\text{GS}} - V_{\text{th,sat}} \right)}{v_{\text{sat}} L_{eff}}}}$$

(6)

Since velocity overshoot occurs in the nanoscale transistor (Kim et al., 2008; Ruch, 1972), equation (6) needs to be modified. In the physics-based model for MOS transistors developed by (Hauser, 2005),  $v_{sat}$  is treated as a fitting parameter that can be increased to  $2.06 \times 10^7$  cm/s so as to fit the experimental  $I_{ds}$  versus  $V_{DS}$  characteristics of the nanoscale NMOS transistor (L = 90 nm). Although this approach is conceptually wrong, it serves as an easy way to avoid detailed discussion in velocity overshoot and quasi-ballistic transport. Hence, the resulting equation is as follows,

$$V_{\text{Dsat}} = \frac{V_{\text{GS}} - V_{\text{th,sat}}}{0.5 + \sqrt{0.25 + \frac{\mu_{\text{eff}}(L_{\text{eff}})}{v_{\text{sat}}(L_{\text{eff}})} \frac{V_{\text{GS}} - V_{\text{th,sat}}}{L_{\text{eff}}}}}$$

(7)

where  $\mu_{\text{eff}}$  and  $v_{\text{sat}}$  are functions of  $L_{\text{eff}}$ . To avoid confusion, we introduce another parameter called the effective saturation velocity ( $v_{\text{sat}\_\text{eff}}$ ). According to (Lau et al., 2008, b),  $v_{\text{sat}\_\text{eff}}$  is taken to be the average value of the carrier velocity ( $v_{\text{eff}}$ ) when  $V_{\text{GS}}$  is close to the power supply voltage ( $V_{\text{DD}}$ ). When uniaxial tensile stress is applied, both  $\mu_{\text{eff}}$  and  $v_{\text{sat}\_\text{eff}}$  of NMOS transistor will be increased. By replacing  $v_{\text{sat}}(L_{\text{eff}})$  in equation (7) by  $v_{\text{sat}\_\text{eff}}(\mu_{\text{eff}}, L_{\text{eff}})$ ,

$$V_{\text{Dsat}} = \frac{V_{\text{GS}} - V_{\text{th,sat}}}{0.5 + \sqrt{0.25 + \frac{\mu_{\text{eff}}(L_{\text{eff}})}{v_{\text{sat}\_\text{eff}}(\mu_{\text{eff}}, L_{\text{eff}})} \frac{V_{\text{GS}} - V_{\text{th,sat}}}{L_{\text{eff}}}}$$

(8)

For long channel MOS transistors, the large  $L_{\text{eff}}$  will make the third term in the denominator of equation (8) negligible and thus  $V_{\text{Dsat}} \approx (V_{\text{GS}} - V_{\text{th,sat}})$ . For the short channel MOS transistors, the third term in the denominator of equation (8) must be considered and thus  $V_{\text{Dsat}}$  is expected to be smaller than  $(V_{\text{GS}} - V_{\text{th,sat}})$ . According to conventional MOS transistor theory (Taur & Ning, 1998, a),  $V_{\text{Dsat}}$  is given by  $(V_{\text{GS}} - V_{\text{th,sat}})/m$  where the body effect coefficient (*m*) is typically between 1.1 and 1.4.

#### 3. Does velocity saturation occur in the nanoscale MOS transistor?

For NMOS transistor, the electrons are accelerated by the lateral electric field ( $E_{lateral}$ ) and thus the drift velocity ( $v_{drift}$ ) increases. For (100) Si substrate, the optical phonon energy is bigger than 60 meV (Sah, 1991, a). When the kinetic energy of the electron exceeds 60 meV, the optical phonons are generated. However, the generation rate of optical phonon is very large and thus only a few electrons can have energy higher than 60 meV. An equilibrium is reached when the rate of energy gain from  $E_{\text{lateral}}$  is equal to the rate of energy loss to phonon scattering. This corresponds to the maximum  $v_{\text{drift}}$  that occurs at  $E_{\text{lateral}}$  around 10<sup>4</sup> V/cm. The maximum  $v_{\text{drift}}$  is known as the velocity saturation ( $v_{\text{sat}}$ ). Based on the Monte Carlo simulation by (Ruch, 1972), the distance over which  $v_{\text{drift}}$  will overshoot the electron  $v_{\rm sat}$  is less than 100 nm but this transient in velocity will only last for 0.8 ps before reaching its equilibrium value of 107 cm/s. According to (Mizuno, 2000), the amount of channel doping concentration  $(N_{ch})$  will determine if velocity overshoot can be observed in bulk MOS transistors. For NMOS transistor with L = 80 nm, velocity overshoot can occur if  $N_{ch} <$ 10<sup>17</sup> cm<sup>-3</sup>. For NMOS transistor with L = 30 nm, velocity overshoot can occur even if  $N_{\rm ch} \approx$  $10^{18}$  cm<sup>-3</sup>. This can be attributed to the effective channel length ( $L_{eff}$ ), which is a function of both the mask gate length (L) and  $N_{ch}$ . In fact, (Kim et al., 2008) has reported that the experimental findings of electron velocity overshoot in 36 nm bulk Si-based NMOS transistor at room temperature. Furthermore, the Monte Carlo simulation performed by (Miyata et al., 1993) show that electron velocity overshoot actually increases when the tensile stress is increased. This can account for the strain-induced Ion enhancement in the nanoscale NMOS transistors (Yang et al., 2004; C-H. Chen et al., 2004; Yang et al., 2008). Hence, it is more likely that velocity overshoot occur in the nanoscale transistor rather than velocity saturation.

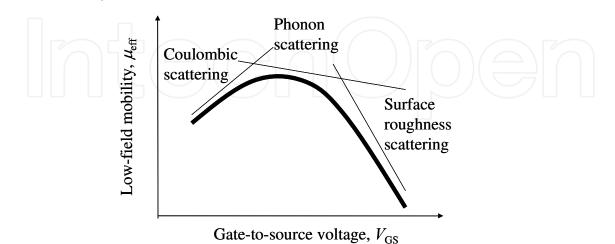

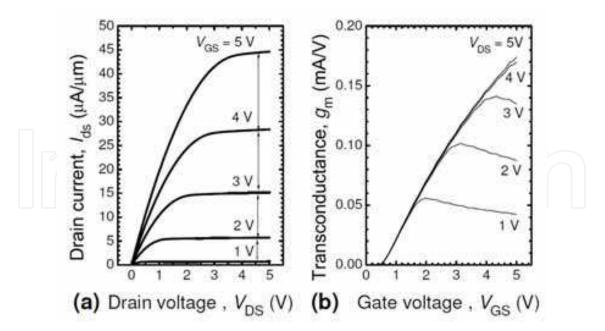

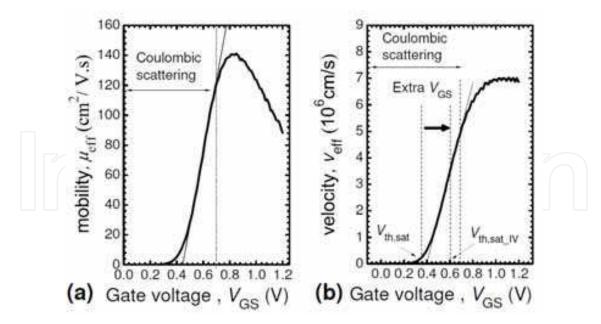

Here, we will like to point out another misconception about the occurrence of velocity saturation in the nanoscale MOS transistors. Based on the classical concept of velocity saturation, the saturation Ids of the short channel MOS transistor has a linear relationship with  $V_{GS}$  (see equation 5), and thus the saturation  $I_{ds}$  versus  $V_{DS}$  characteristics is expected to have constant spacing for equal V<sub>GS</sub> step (Sze & Ng, 2007). On the other hand, the saturation  $I_{ds}$  of the long channel MOS transistor is controlled by pinchoff (Hofstein & Heiman, 1963). Based on the constant mobility assumption, equation 4 predicts that the saturation Ids of long channel MOS transistor has a quadratic relationship with  $V_{GS}$  and thus the saturation  $I_{ds}$ versus V<sub>DS</sub> characteristics is expected to have increasing spacing for equal V<sub>GS</sub> step (Sze & Ng, 2007). However, constant spacing for equal  $V_{GS}$  step is often observed in the experimental  $I_{ds}$  versus  $V_{DS}$  characteristics of the long channel MOS transistor, as shown in Fig.3. This can be understood from the validity of the constant mobility assumption. Experimental data have shown that mobility is actually a function of  $V_{GS}$  (Takagi et al., 1994). From Fig.7,  $\mu_{\text{eff}}$  first increases with increasing  $V_{\text{GS}}$  owing to Coulombic scattering and then decreases owing to phonon scattering and surface roughness scattering. To further investigate, we measured the  $I_{ds}$  versus  $V_{DS}$  characteristics and the  $I_{ds}$  versus  $V_{GS}$ characteristics of a long-channel NMOS transistor. Considering equal V<sub>GS</sub> step, we observed an increasing spacing for  $1 \text{ V} \le V_{\text{GS}} \le 3 \text{ V}$  but constant spacing for  $3 \text{ V} \le V_{\text{GS}} \le 5 \text{ V}$  in the saturation  $I_{ds}$  versus  $V_{DS}$  characteristics of the NMOS transistor (see Fig.8). Since the transconductance  $(g_m)$  is a measure of the low-field mobility ( $\mu_{eff}$ ) (Schroder, 1998), the  $g_m$ versus  $V_{GS}$  characteristics is expected to have the same features as the mobility versus  $V_{GS}$ characteristics. From Fig. 8(a), the drain current saturation of the NMOS transistor occurs at  $V_{\rm DS}$  around 3 V. With reference to Fig. 8(b), when  $V_{\rm DS}$  = 3 V and 0 V  $\leq V_{\rm GS} \leq$  3 V,  $g_{\rm m}$  increases monotonically with increasing V<sub>GS</sub> owing to Coulombic scattering. When V<sub>GS</sub> is further increased to beyond 3 V, surface roughness scattering will start to dominate and then g<sub>m</sub> will decrease with increasing  $V_{GS}$ . Hence, for  $1 \text{ V} \le V_{GS} \le 3 \text{ V}$ , the saturation  $I_{ds}$  versus  $V_{DS}$ characteristics has increasing spacing for equal  $V_{GS}$  step. For  $3 \text{ V} \le V_{GS} \le 5 \text{ V}$ , the saturation  $I_{ds}$  versus  $V_{DS}$  characteristics has constant spacing for equal  $V_{GS}$  step. Since velocity saturation does not occur in long channel transistor, the constant spacing observed in the saturation  $I_{ds}$  versus  $V_{DS}$  characteristics at high  $V_{GS}$  cannot be used as an indicator of the onset of velocity saturation.

Fig. 7. Effects of the scattering mechanisms on the  $\mu_{\text{eff}}$  versus  $V_{\text{GS}}$  characteristics of MOS transistor.

Fig. 8. Constant spacing is observed in the saturation  $I_{ds}$  versus  $V_{DS}$  characteristics of a NMOS transistor ( $L = 10 \mu m$ ,  $W = 10 \mu m$ , physical gate oxide thickness of 300 Å) for equal  $V_{GS}$  step.

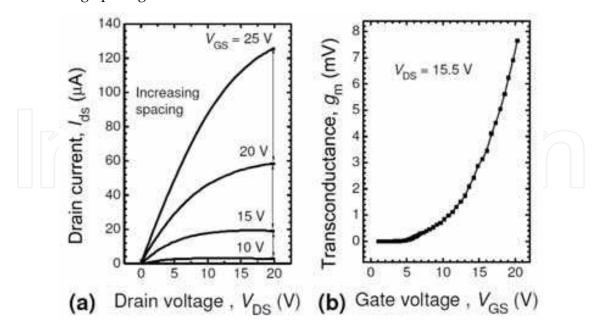

Here, it is interesting to note that it is common for the saturation  $I_{ds}$  versus  $V_{DS}$  characteristics of the zinc oxide thin-film transistors to have increasing spacing for equal  $V_{GS}$  step (Cheong et al., 2009; Yaglioglu et al., 2005). The mobility of these materials (~ 10 to 20 cm<sup>2</sup>/V.s) is only one tenth of the mobility of silicon (~ 100 to 300 cm<sup>2</sup>/Vs). In Fig.9, which is modified from (Cheong et al., 2009), the drain current saturation occurs at  $V_{DS}$  around 15 V. The increasing spacing observed in the saturation  $I_{ds}$  versus  $V_{DS}$  characteristics of the thin-

Fig. 9. Zinc oxide thin-film transistors with  $L = 20 \ \mu\text{m}$  and  $W = 40 \ \mu\text{m}$  (a) Increasing spacing observed in the experimental  $I_{ds}$  versus  $V_{DS}$  characteristics of, (b) Monotonically increasing  $g_{\text{m}}$ . Modified from (Cheong et al., 2009).

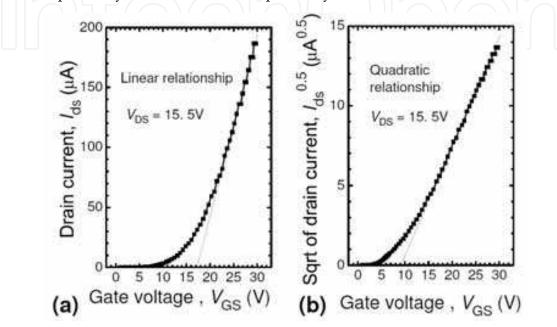

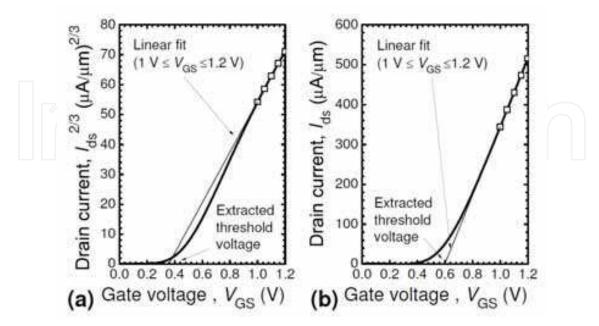

film transistor is related to the monotonically increasing  $g_m$  with increasing  $V_{GS}$ . Next, we will study the dependency of the saturation  $I_{ds}$  of the thin film transistor on  $V_{GS}$ . From Fig. 10, if  $I_{ds}$  and  $V_{GS}$  have linear dependency,  $V_{th,sat}$  extracted by linear interpolation is around 17.5 V. If  $I_{ds}$  and  $V_{GS}$  have quadratic dependency,  $V_{th,sat}$  extracted by extrapolating the linear portion of the  $I_{ds}^{0.5}$  versus  $V_{GS}$  plot is around 10 V. As seen in the  $I_{ds}$  versus  $V_{DS}$  characteristics of the thin-film transistor (see Fig.9), the transistor is in cutoff mode when  $V_{GS} \le 10$  V. Hence, it is more appropriate to say that  $I_{ds}$  of thin-film transistor and  $V_{GS}$  have quadratic dependency.

Fig. 10. Relationship between  $I_{ds}$  and  $V_{GS}$  of the zinc oxide thin-film transistors ( $L = 20 \ \mu m$  and  $W = 40 \ \mu m$ ) (a) Linear dependency (b) Quadratic dependency. Modified from (Cheong et al., 2009).

### 4. Newer theories on the saturation drain current equations of the nanoscale MOS transistor

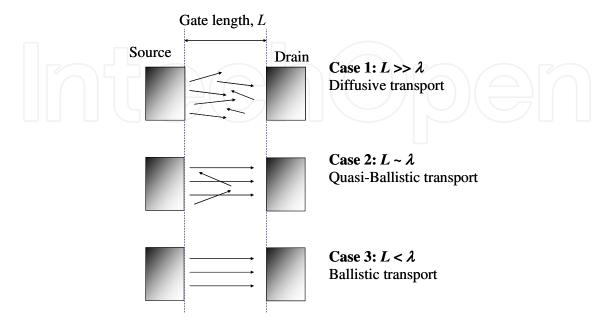

According to (Natori, 2008), the type of carrier transport in the MOS transistor depends on the relative dimension between the gate length (*L*) and the mean free path ( $\lambda$ ), as illustrated in Fig. 11. Qualitatively,  $\lambda$  is the average distance covered by the channel carrier between the successive collisions. When *L* is much bigger than  $\lambda$ , the channel carriers will experience diffusive transport. When *L* is comparable to  $\lambda$ , the carriers undergo only a small number of scattering events from the source to the drain and thus the carriers will experience quasiballistic transport. Ballistic transport will only occur when  $L < \lambda$ . The experimentally extracted  $\lambda$  is in the range of 10 nm for the nanoscale transistor (M-J. Chen et al., 2004; Barral et al., 2009). Hence, the state-of-the-art MOS transistor ( $L \ge 32$  nm) is more likely to experience quasi-ballistic transport rather than ballistic transport. This section will discuss the main concepts of ballistic transport and then proceed to discuss about the existing quasiballistic theories. The emphasis of this section is to introduce a simplified equation for the saturation drain current of the nanoscale MOS transistor that is able to address quasiballistic transport while having electrical parameters that are obtainable from the standard

device measurements. Here, we will introduce two equations that can satisfy the above criteria (i) Based on the concept of the effective saturation velocity ( $v_{sat_{eff}}$ ), which is a function of  $\mu_{eff}$  and temperature (Lau et al., 2008, b) and (ii) Based on the virtual source model (Khakifirooz et al., 2009).

Fig. 11. Types of carrier transport in MOS transistors, which is modified from Fig. 1 in (Natori, 2008). Note that  $\lambda$  is the mean free path of the carrier.

#### 4.1 Ballistic transport

In vacuum, electrons will move under the influence of electric field according to Newton's second law of motion,

$$F = m_e a = -qE \tag{9}$$

where F,  $m_e$ , a, q and E are the resultant force acting on the electron, the electron mass, the acceleration of the electron, the electronic charge, and the electric field, respectively. Under such a situation, if the applied electric field is constant in both magnitude and direction, the electrons will accelerate in the direction opposite to that of the electric field. This type of transport is known as the ballistic transport. In the other words, if there is no obstacle to scatter the electrons, the electrons will experience ballistic transport (Heiblum & Eastman, 1987). Furthermore, (Bloch, 1928) postulated that the wave-particle duality of electron allows it to move without scattering in the densely packed atoms of a crystalline solid if (i) the crystal lattice is perfect and (ii) there is no lattice vibration. However, doping impurities such as boron, arsenic and phosphorus are added to the silicon crystal so as to tune the electrical parameters such as the threshold voltage and the off-state current ( $I_{off}$ ). These dopants will disrupt the periodic arrangement of the crystal lattice and thus results in collisions with the impurity ions and the crystalline defects. Moreover, the atoms in crystals are always in constant motion according to the Particle Theory of Matter. These thermal vibrations cause waves of compression and expansion to move through the crystal and thus scatter the electrons (Heiblum & Eastman, 1987). Therefore, achieving ballistic transport in Si-based MOS transistors is only an ideal situation (Natori, 2008).

#### 4.2 Quasi-ballistic transport

Having established that thermionic emission from the source to the channel is still relevant in the state-of-the-art MOS transistor ( $L \ge 32$  nm) in Section 1, we will proceed to discuss the main concepts behind quasi-ballistic transport. (Lundstrom, 1997) derived an equation that relates the saturation  $I_{ds}$  of the nanoscale transistor to  $\mu_{eff}$  as follows,

$$I_{\rm ds} = \left[\frac{C_{\rm ox} W}{\frac{1}{v_{\rm T}} + \frac{1}{\mu_{\rm eff} \ \varepsilon(0^+)}}\right] (V_{\rm GS} - V_{\rm th,sat}) \tag{10}$$

where the random thermal velocity of the carriers ( $v_T$ ) does not depend  $V_{GS}$ . The only variable in the  $v_T$  equation is the temperature (T).

$$v_{\rm T} = v_{\rm T}(T) = \sqrt{(2k_B T) / (\pi m_t)}$$

(11)

where the transverse electron mass of silicon ( $m_t$ ) is equal to 0.19  $m_0$  where the free electron mass ( $m_0$ ) is equal to 9.11 × 10<sup>-31</sup> kg (Singh, 1993). Using equation (11),  $v_T$  is approximately equal to 1.2 × 10<sup>7</sup> cm/s at temperature of 25 °C.  $k_B$  is the Boltzmann constant. *T* is the absolute temperature.  $\varepsilon(0^+)$  is defined as the average electric field within the length  $\ell$  where a  $k_B T/q$  potential drop occurs, as shown in Fig.12 in (Lundstrom & Ren, 2002). Despite the lack of equation for  $\varepsilon(0^+)$  (Lundstrom, 1997; Lundstrom & Ren, 2002), Lundstrom has made an important contribution to relate the low-field mobility ( $\mu_{eff}$ ) to  $I_{on}$  of the deep submicron MOS transistors, and thus his theory is able to account for the strain-induced enhancement in  $I_{on}$  (Yang et al., 2004; C-H. Chen et al., 2004; Yang et al. 2008; Wang et al., 2007).

According to (Lundstrom, 1997), if a carrier backscatters beyond  $\ell$ , it is likely to exit from the drain and is unlikely to return back to the source (see Fig. 12). For NMOS transistor,  $\ell$  is the distance between the top of the conduction band edge and the point along the channel where channel potential drops by  $k_{\rm B}T/q$ .

Fig. 12. Definition of the critical length ( $\ell$ ) for NMOS transistor.  $\ell$  is defined to be the distance between the top of the conduction band edge and the point along the channel where channel potential drops by  $k_{\rm B}T/q$ . Beyond  $\ell$ , the carriers are unlikely to return to the source.

By inspection of equations (10) and (11), a loop-hole can be found in Lundstrom's 1997 theory. If equations (10) and (11) are correct, MOS transistors will function very poorly when the temperature is lowered from room temperature to very low temperature such as liquid helium temperature. However, there are numerous reports that MOS transistors and CMOS integrated circuits can function quite well at the liquid helium temperature (Chou et al., 1985; Ghibaudo & Balestra, 1997; Yoshikawa et al., 2005). Hence, there is a need to modify Lundstrom's 1997 theory. Indeed, (Lundstrom & Ren, 2002) made an attempt to incorporate Natori's 1994 theory into their theory. However, the resulting theory is very much not similar to equation (10) and has not been compared with real device performance. Based on equation (24) in (Natori, 1994), the saturation drain current of the nanoscale MOS transistor is as follows,

$$I_{\rm ds} = \frac{8\hbar W \left[ C_{\rm ox} \left( V_{\rm GS} - V_{\rm th,sat} \right) \right]^{3/2}}{3m_{\rm t} \sqrt{q\pi M_{\rm v}}}$$

(12a)

where  $\hbar$  is the reduced Planck's constant.  $M_v$  is the product of the lowest valley degeneracy and the reciprocal of the fraction of the carrier population in the lowest energy level. For a NMOS transistor that is fabricated on (100) Si substrate, the fraction of the carrier population at the strong inversion is around 0.8 at 77 K but it decreases to around 0.4 at 300 K (Stern, 1972). In the other words,  $M_v$  is a function of temperature (*T*).

Rearranging equation (12a) results in,

$$I_{\rm ds} = \left[\frac{C_{\rm ox} W}{\frac{1}{v_{\rm inj}(V_{\rm GS}, T)}}\right] \left(V_{\rm GS} - V_{\rm th, sat}\right)$$

(12b)

where the injection velocity  $(v_{inj})$  is given by (Natori, 1994),

$$v_{\rm inj}(V_{\rm GS},T) = \frac{8\hbar\sqrt{C_{\rm ox}(V_{\rm GS}-V_{\rm th,sat})}}{3m_{\rm t}\sqrt{q\pi M_{\rm v}(T)}}$$

(12c)

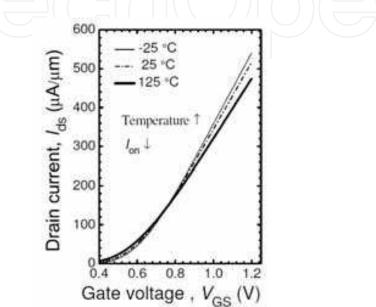

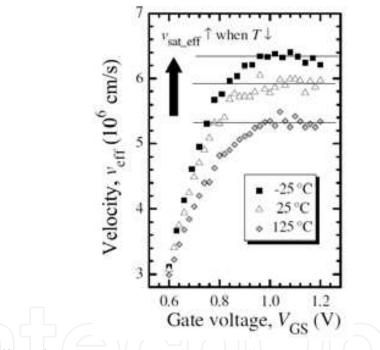

With reference to Fig.8 in (Natori, 1994),  $v_{inj}$  increases with increasing temperature (T) and increasing  $V_{GS}$ . If Natori's theory is true,  $v_{ini}$  can be very high even though the temperature is very low. We propose that this feature of Natori's 1994 theory can be used to cover the shortcomings of Lundstrom's 1997 theory. However, there are some aspects of Natori's 1994 theory that contradict the experimental data. From Fig. 8 in (Natori, 1994), his theory, which disregards the channel scattering, predicted that the saturation  $I_{ds}$  of the nanoscale NMOS transistor will increase when temperature increases. However, this is contradictory to the experimental data. Fig. 13 shows that the experimental  $I_{ds}$  of a NMOS transistor (L= 60 nm) actually decreases when temperature increases. This can be explained by the increase in channel scattering when temperature increases (Takagi et al., 1994; Kondo & Tanimoto, 2001; Mazzoni et al., 1999). Moreover, equation (12b) cannot account for the strain-induced enhancement in Ion (Yang et al, 2004; C-H. Chen et al, 2004; Yang et al., 2008; Wang et al., 2007). Hence, without the help of Lundstrom's 1997 theory, Natori's 1994 theory is contradictory to the experimental data.

In addition, Natori's 1994 theory predicts that the saturation  $I_{ds}$  of the nanoscale MOS transistors will follow a  $(V_{GS} - V_{th,sat})^{3/2}$  relationship. Fig. 14a shows the saturation  $I_{ds}^{2/3}$  versus  $V_{GS}$  characteristics of a NMOS transistor (L = 60 nm). The threshold voltage extracted by the linear extrapolation is smaller than the threshold voltage of conduction. This shows that the saturation  $I_{ds}$  of the nanoscale MOS transistors does not follow a  $(V_{GS} - V_{th,sat})^{3/2}$  relationship. Fig. 14b shows the saturation  $I_{ds}$  versus  $V_{GS}$  characteristics of the same NMOS transistor. In this case, the extracted threshold voltage is close to the threshold voltage of conduction. Hence, the saturation  $I_{ds}$  of nanoscale transistors is more likely to follow a  $(V_{GS} - V_{th,sat})$  relationship.

Fig. 13. Effects of temperature on the saturation  $I_{ds}$  versus  $V_{GS}$  characteristics of a NMOS transistor (L = 60 nm,  $W = 5 \mu \text{m}$ ).

Fig. 14. As opposed to Natori's 1994 theory, the saturation  $I_{ds}$  of the short channel NMOS transistor does not follow a  $(V_{GS} - V_{th,sat})^{3/2}$  relationship.

#### 4.3 New equation that unifies Natori's 1994 theory and Lundstrom's 1997 theory

We propose a simplified equation that can unify both Natori's 1994 theory and Lundstrom's 1997 theory, as follows (Lau et al., 2008, b),

where

$$I_{ds} = \left[ \frac{C_{ox}W}{\frac{1}{v_1(V_{GS},T)} + \frac{1}{v_1(V_{GS},T)}} \right] (V_{GS} - V_{th,sat})$$

(13)

$$v_1(V_{GS},T) = v_{inj}(V_{GS},T)$$

(14)

$$v_2(V_{\rm GS}, T) = \mu_{\rm eff}(V_{\rm GS}, T) \varepsilon(0^+)$$

(15)

(Lundstrom, 1997) proposed that  $v_1$  is equal to  $v_T$  that is only dependent on *T*, as shown in equation (11). On the other hand, our theory proposed that  $v_1$  is a function of both  $V_{GS}$  and *T*, and  $v_1$  can be higher than  $v_T$  given by equation (11). (Natori, 1994) proposed that  $v_1$  is equal to  $v_{inj}$ , which is a function of both  $V_{GS}$  and *T*. Recently, (Natori et al., 2003; Natori et al., 2005) simulated the  $v_{inj}$  characteristics using the multi-subband model (MSM). In weak inversion,  $v_{inj}$  is almost independent of  $V_{GS}$  and is approximately equal to 1.2 x 10<sup>7</sup> cm/s, which is equal to  $v_T$ . In strong inversion,  $v_{inj}$  will increase due to carrier degeneration but is confined within a narrow range from 1.2 x 10<sup>7</sup> cm/s to 1.6 x 10<sup>7</sup> cm/s.

Here, we would like to highlight that both Lundstrom's 1997 theory and Natori's 1994 theory did not consider the series resistance ( $R_{sd}$ ). Although the conduction band edge ( $E_c$ ) profile in the n-channel will be the same with or without  $R_{sd}$  (Martinie et al., 2008), the  $E_c$ within S/D regions will be different when the effects of  $R_{sd}$  is considered. If the effects of  $R_{sd}$ are disregarded, *E*<sub>c</sub> within S/D regions will appear as a horizontal line, as illustrated in Fig. 12. However, the presence of  $R_{sd}$  will cause a potential drop in the S/D regions, resulting in a built-in electric field within the S/D regions (see Fig. 15). This electric field in the source region will accelerate the electrons. Since scattering decreases when temperature decreases (Takagi et al., 1994; Kondo & Tanimoto, 2001; Mazzoni et al., 1999), one would expect that there will be minimal scattering in the source when the temperature is very low. Hence, the presence of  $R_{sd}$  will allow the electrons to attain higher energy prior to thermionic emission into the channel. According to (M-J. Chen et al., 2004), the source series resistance ( $R_s$ ) is about 75  $\Omega$ -µm. If the drain current ( $I_{ds}$ ) is about 800 µA/µm, the voltage drop due to  $R_s$  is about 800  $\mu$ A/ $\mu$ m x 75  $\Omega$ - $\mu$ m = 60 mV. (Note that the thermal voltage,  $k_{\rm B}T/q$  is approximately 26 meV at room temperature.) We proposed that the electrons are "heated" up by the 60 meV energy due to  $R_{sd}$  and thus their velocities can be significantly larger than 1.2 x 10<sup>7</sup> cm/s (as predicted by equation 12c). Moreover, this extra energy is expected to increase with increasing  $V_{GS}$  because higher  $V_{GS}$  implies a bigger  $I_{ds}$ . With this extra energy from electron heating in the  $R_{sd}$  region, the carriers can overcome the potential barrier at the liquid nitrogen temperature despite not being able to gain energy from the surrounding. The significance of  $v_2$  term is that it establishes a link between  $I_{on}$  and  $\mu_{eff}$ . This provides a better compatibility between theory and Ion enhancement in the nanoscale transistors by various stress engineering techniques (Yang et al., 2004; C-H. Chen et al., 2004; Yang et al.,

2008; Wang et al., 2007). However, there is no  $v_2$  term in Natori's 1994 theory, as shown in equation (12b). Nevertheless,  $v_2$  is covered by Lundstrom's 1997 theory, as shown in equation (10). Hence, we incorporate  $v_2$  in Lundstrom's 1997 theory into equation (13).

Fig. 15. The effects of S/D series resistance on the conduction band edge of a NMOS transistor in the saturation operation.

Another loop-hole in Lundstrom's 1997 theory is that there is no equation for  $\varepsilon(0^+)$ . From Fig.9 in (M-J. Chen et al., 2004), the slope of the near-source channel conduction band increases when  $V_{\text{GS}}$  increases. In the other words, the electric field near the top of potential barrier,  $\varepsilon(0^+)$  increases with increasing  $V_{\text{GS}}$ . Hence, we deduce that  $\varepsilon(0^+)$  is a function of both  $V_{\text{GS}}$  and  $V_{\text{DS}}$  such that  $\varepsilon(0^+, V_{\text{GS}}, V_{\text{DS}} = V_{\text{DD}})$  is approximately equal to  $\varepsilon(0^+, V_{\text{GS}}, V_{\text{DS}} = V_{\text{Dsat}})$ . Note that  $V_{\text{DD}}$  is the power supply voltage. This is consistent with Fig. 5 in (Fuchs et al., 2005). Therefore, we propose that  $\varepsilon(0^+)$  can be expressed as follows,

$$\varepsilon(0^+) = \frac{\alpha_1 V_{\text{Dsat}}}{L_{\text{eff}}} \tag{16a}$$

where the correction factor ( $\alpha_1$ ) is smaller than 1. Based on the conventional MOS transistor theory (Taur & Ning, 1998, a),  $V_{\text{Dsat}}$  is given by  $(V_{\text{GS}} - V_{\text{th,sat}})/m$  where  $1.1 \le m \le 1.4$ . Furthermore, (Suzuki & Usuki, 2004) proposed a drain current model that shows that  $V_{\text{Dsat}}$  is smaller than ( $V_{\text{GS}} - V_{\text{th,sat}}$ ) for the short-channel MOS transistors. This shows that the relationship of  $V_{\text{Dsat}} = (V_{\text{GS}} - V_{\text{th,sat}})/m$  is still reasonably correct for very short MOS transistors. Therefore,  $\varepsilon(0^+)$  can also be expressed by,.

$$\varepsilon(0^{+}) = \frac{\alpha_2 \left( V_{\rm GS} - V_{\rm th,sat} \right)}{L_{\rm eff}}$$

(16b)

where the correction factor ( $\alpha_2$ ) is smaller than 1. The value of  $\alpha_2$  can be estimated from the effective carrier velocity ( $v_{eff}$ ) versus  $V_{GS}$  characteristics and the  $\mu_{eff}$  versus  $V_{GS}$  characteristics. Using the saturated transconductance method suggested by (Lochtefeld et al., 2002),  $v_{eff}$  was extracted as a function of  $V_{GS}$  as shown in Fig.16 (a). For the contact etch stop layer (CESL) with a tensile stress of 1.2 GPa,  $\nu_{sat_eff}$  of the NMOS transistor (L = 60 nm) was 7.3 × 10<sup>6</sup> cm/s. Using the constant current method with reference current,  $I_{ref}$

=0.1µA(W/L), the extracted  $V_{\text{th,sat}}$  was about 0.3 V. Next,  $L_{\text{eff}}$ , which is extracted using the method proposed by (Guo et al., 1994), was about 0.030 µm. Substituting  $L_{\text{eff}}$  = 3 x 10<sup>-6</sup> cm,  $V_{\text{GS}}$  = 1.2 V,  $V_{\text{th,sat}}$  = 0.3 V into equation (16b),

$$\varepsilon(0^+) = 3 \times 10^5 \alpha_2$$

(in units of V/cm) (16c)

Re-arranging  $\nu_{\text{sat}\_\text{eff}} = \mu_{\text{eff}} \epsilon(0^+)$ ,

$$\varepsilon(0^{+}) = \frac{v_{\text{sat\_eff}}}{\mu_{\text{eff}}}$$

(16d)

Next,  $\mu_{\text{eff}}$  is extracted as a function of  $V_{\text{GS}}$  using a method described by (Schroder, 1998). From Fig. 16(b), when  $V_{\text{GS}}$  is 1.2 V,  $\mu_{\text{eff}}$  was about 85 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at. Substituting  $\nu_{\text{sat\_eff}}$  = 7.3 ×10<sup>6</sup> cm/s and  $\mu_{\text{eff}}$  = 85 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> into equation (16d),

$$\varepsilon(0^{+}) = \frac{v_{\text{sat\_eff}}}{\mu_{\text{eff}}} = \frac{7.3 \times 10^{6}}{85} = 8.588 \times 10^{4} \text{ V/cm}$$

(16e)

According to (Lee et al., 2009),  $\varepsilon(0^+)$  of a PMOS transistor (L = 50 nm) is between 8 ×10<sup>4</sup> V/cm and 3 ×10<sup>5</sup> V/cm for various gate overdrives. By solving equations (16c) and (16e),  $\alpha_2$  is around 0.29. Note that  $\alpha_2$  is 0.5 for the conventional MOS transistor theory (Taur & Ning, 1998, a).

160 velocity, v<sub>aff</sub> (10°cm/ s) mobility. µ<sub>cif</sub> (cm<sup>-/</sup> V.s) at eff 6 120 100  $\mu_{eff}$ 80 NMOS NMOS transistor transistor 60 = 1.2 V = 0.05 V DS. ns 2 40 0.7 GPa 0.7 GPa 20 1.2 GPa 1.2 GPa 8.0 0.0 0.5 1.0 1.5 0.5 1.0 1.5 (a) Gate voltage , V<sub>GS</sub> (V) (b) Gate voltage , V<sub>GS</sub> (V)

Fig. 16. Effects of uniaxial tensile stress on (a) the  $v_{\text{eff}}$  versus  $V_{\text{GS}}$  characteristics, (b) the  $\mu_{\text{eff}}$  versus  $V_{\text{GS}}$  characteristics of a NMOS transistor (L = 60 nm, W = 0.12 µm). Note  $v_{\text{sat_eff}}$  is the average value of  $v_{\text{eff}}$  when  $V_{\text{GS}}$  is close to  $V_{\text{DD}}$ . The uniaxial tensile stress is induced by the contact etch stop layer (CESL). The film stress of the two CESL split are 0.7 GPa tensile stress and 1.2 GPa tensile stress.

Equation (13) is then modified by defining a new parameter called the effective carrier velocity ( $\nu_{eff}$ ). The resulting equation is as follows (Yang et al., 2007; Lau et al., 2008, a; Lau et al., 2008, b),

$$I_{\rm ds} = v_{\rm eff}(\mu_{\rm eff}, V_{\rm GS}, T) W C_{\rm ox} (V_{\rm GS} - V_{\rm th, sat})$$

(17)

where  $v_{\text{eff}}$  is a function of  $\mu_{\text{eff}}$ ,  $V_{\text{GS}}$  and T at a constant  $V_{\text{DS}}$  (see Fig.16a and Fig.17). Furthermore,  $v_{\text{eff}}$  is also related to  $v_1$  and  $v_2$ , as follows,

$$v_{\rm eff}(\mu_{\rm eff}, V_{\rm GS}, T) = \left(\frac{1}{v_1(V_{\rm GS}, T)} + \frac{1}{v_2(\mu_{\rm eff}, V_{\rm GS}, T)}\right)^{-1}$$

(18)

When temperature decreases,  $v_{inj}$  decreases (Natori, 1994). Since  $v_1$  is related to  $v_{inj}$  (see equation 14),  $v_1$  is expected to decrease with decreasing temperature. On the other hand, mobilities due to Coulombic scattering, phonon scattering and surface roughness scattering will increase with decreasing temperature (Takagi et al., 1994; Kondo & Tanimoto, 2001; Mazzoni et al., 1999). As  $v_2$  is related to  $\mu_{eff}$  (see equation 15), we expect  $v_2$  to increase when temperature decreases. Fig. 17 shows that the experimental  $v_{eff}$  increases when temperature decreases, and hence  $v_2$  dominates over  $v_1$ .

Fig. 17. The effect of temperature on  $v_{\text{sat}\_eff}$ . Note that  $v_{\text{sat}\_eff}$  corresponds to the average value of  $v_{\text{eff}}$  when  $V_{\text{GS}}$  is close to  $V_{\text{DD}}$  (L = 60 nm,  $W = 5 \mu \text{m}$ ,  $V_{\text{DS}} = V_{\text{DD}} = 1.2$  V).

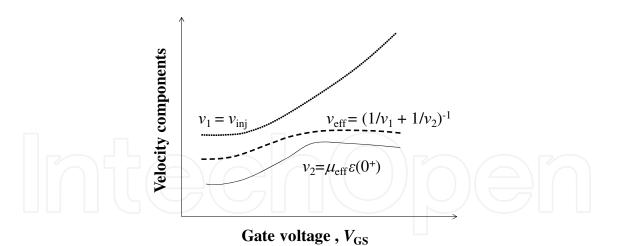

Another evidence to illustrate the importance of  $v_2$  over  $v_1$  is through their behavior with  $V_{\text{GS}}$ . Fig.18 shows the behavior of  $v_1$ ,  $v_2$ ,  $v_{\text{eff}}$  with  $V_{\text{GS}}$ . Since  $v_1$  is related to  $v_{\text{inj}}$ ,  $v_1$  is expected to increase when  $V_{\text{GS}}$  increases (Natori, 1994). On the other hand,  $v_2$  is related to  $\mu_{\text{eff}}$ , as shown in equation (15). Hence, the  $v_2$  versus  $V_{\text{GS}}$  characteristics will tend to follow that of the  $\mu_{\text{eff}}$  versus  $V_{\text{GS}}$  characteristics (see Fig. 7). When  $V_{\text{GS}}$  is low,  $v_2$  is expected to increase with increasing  $V_{\text{GS}}$  owing to the screening of the Coulombic scattering centres. When  $V_{\text{GS}}$  is high, an increase in  $V_{\text{GS}}$  will decrease  $\mu_{\text{eff}}$  and  $\varepsilon(0^+)$ . From equation (16b),  $\varepsilon(0^+)$  is expected to increase with increasing  $V_{\text{GS}}$ . Hence,  $v_2$  is expected to approach a constant at high  $V_{\text{GS}}$  owing to the opposing effects of  $\mu_{\text{eff}}$  and  $\varepsilon(0^+)$ .

Fig. 18. A schematic diagram showing the relationship of  $v_1$ ,  $v_2$  and  $v_{\text{eff}}$  with  $V_{\text{GS}}$ .

Since  $v_{\text{eff}}$  approaches a constant when  $V_{\text{GS}}$  close to  $V_{\text{DD}}$  (see Fig. 16a and Fig. 17), it is more appropriate to replace  $v_{\text{eff}}$  in equation (17) can be replaced by  $v_{\text{sat_eff}}$ , resulting in (Yang et al., 2007; Lau et al., 2008,a; Lau et al., 2008,b),

$$I_{\rm ds} = v_{\rm sat\_eff}(\mu_{\rm eff}, T) W C_{\rm ox,inv} \left( V_{\rm GS} - V_{\rm th,sat\_IV} \right)$$

(19)

where  $v_{\text{sat}_{eff}}$  is the average value of  $v_{eff}$  when  $V_{\text{GS}}$  is close to  $V_{\text{DD}}$ . In Fig. 16(a),  $v_{\text{sat}_{eff}}$  increases when tensile stress increases, and thus leads to  $I_{\text{on}}$  enhancement in the short channel NMOS transistor. This shows that equation (19) is able to account for the strain-induced  $I_{\text{on}}$  enhancement by various strain engineering techniques (Yang et al., 2004; C-H. Chen et al., 2004; Yang et al. 2008; Wang et al., 2007). As shown in Fig.17,  $v_{\text{sat}_{eff}}$  increases when temperature decreases, resulting in a better  $I_{\text{on}}$  performance at very low temperature. This shows that equation (19) is able to explain the  $I_{\text{on}}$  enhancement at liquid helium temperature (Chou et al., 1985; Ghibaudo & Balestra, 1997; Yoshikawa et al., 2005).

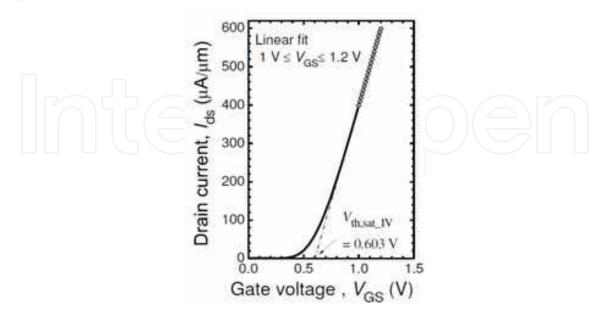

Fig. 19. Extraction of  $V_{\text{th,sat_IV}}$  from the saturation  $I_{\text{ds}}$  versus  $V_{\text{GS}}$  characteristics of a NMOS transistor (L = 60 nm,  $W = 2 \mu \text{m}$ ,  $V_{\text{DS}} = 1.2 \text{ V}$ ).

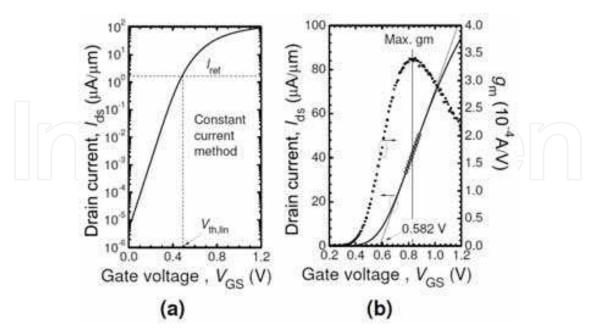

Moreover,  $V_{\text{th,sat}}$  in equation (17) needs to be replaced by  $V_{\text{th,sat_IV}}$ . As illustrated in Fig. 19,  $V_{\text{th,sat_IV}}$  can be extracted from the saturation  $I_{\text{ds}}$  versus  $V_{\text{GS}}$  characteristics. First, a best-fit line is performed on the saturation  $I_{ds}$  versus  $V_{GS}$  characteristics when  $V_{GS}$  is close to  $V_{DD}$ . For our transistors,  $v_{\text{eff}}$  approaches a constant when  $1 \text{ V} \le V_{\text{GS}} \le 1.2 \text{ V}$ .  $V_{\text{th,sat_IV}}$  can be found by the interception between the best-fit line and the  $V_{GS}$  axis. In this example,  $V_{th,sat_{IV}}$  was 0.603 V. For comparison, we extracted  $V_{\text{th,sat}}$  using the Constant Current (CC) method with the reference drain current ( $I_{ref}$ ) defined as  $0.1\mu A(W/L)$ . The extracted  $V_{th,sat}$  was 0.351 V, which is much smaller than  $V_{\text{th,sat_IV}}$ . Moreover, we also observed that  $V_{\text{th,sat_IV}}$  is also bigger than the linear threshold voltage ( $V_{\text{th,lin}}$ ). In Fig. 20(a),  $V_{\text{th,lin}}$  extracted using CC method was 0.484 V. In Fig. 20(b),  $V_{\text{th,lin}}$  extracted using maximum  $g_{\text{m}}$  method was 0.557 V. We believe that  $V_{\text{th,sat_IV}}$  is bigger than  $V_{\text{th,lin}}$  and  $V_{\text{th,sat}}$  because it accounts for the additional  $V_{\text{GS}}$  that is required to produce electrons to screen the Coulombic scattering centres, as shown in Fig. 21. On the other hand,  $V_{\text{th,lin}}$  and  $V_{\text{th,sat}}$  indicate the onset of inversion. Furthermore, polysilicon depletion and quantum mechanical effects will make the gate oxide appears thicker, and thus  $C_{ox}$  in equation (17) has to be replaced by  $C_{ox,inv}$ , which is the gate oxide capacitance per unit area at inversion.

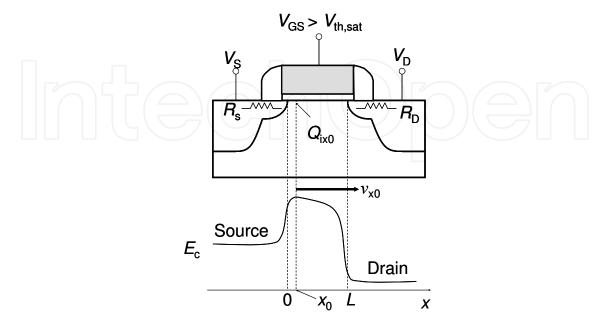

#### 4.4 Virtual source model for nanoscale transistors in saturation mode

(Khakifirooz et al., 2009) proposed a semi-empirical model for the saturation drain current of the nanoscale transistor. This model is based on the location of the "virtual source", which is the top of the conduction band profile for NMOS transistor, as shown in Fig. 22. Based on the "charge-sheet approximation", the saturation  $I_{ds}$  of the nanoscale transistor can be described by the product of the local charge density and the carrier velocity, as follows (Khakifirooz & Antoniadis, 2008).

$$I_{\rm ds} = WQ_{\rm ixo}v_{\rm xo} \tag{20}$$

Fig. 20. Extraction of  $V_{\text{th,lin}}$  of a NMOS transistor in the linear operation (L = 60 nm,  $W = 2 \mu \text{m}$ ,  $V_{\text{DS}} = 0.05 \text{ V}$ ) (a) Using constant current method with  $I_{\text{ref}} = 0.1 \mu \text{A } W/L$ ,  $V_{\text{th,lin}} = 0.484 \text{ V}$ , (b) Using maximum  $g_{\text{m}}$  method ( $V_{\text{th,lin}} = 0.582 \text{ - } V_{\text{DS}}/2 = 0.557 \text{ V}$ ).

Fig. 21.  $V_{\text{th,sat_IV}}$  includes a component to overcome the Coulombic scattering by "screening". The virtual source charge density ( $Q_{xio}$ ) is given by (Khakifirooz et al., 2009),

$$Q_{\rm xio} = C_{\rm ox} \frac{k_{\rm B}T}{q} ln \left[ 1 + \exp\left(\frac{V_{\rm GS} - I_{\rm ds}R_{\rm s} - V_{\rm th,sat}}{mk_{\rm B}T/q}\right) \right]$$

(21)

where  $R_s$  is the source series resistance. The body-effect coefficient (*m*) can be expressed as (Taur & Ning, 1998,b),

$$m = 1 + \frac{\sqrt{\varepsilon_0 \varepsilon_{Si} q N_{ch} / (4\psi_B)}}{C_{ox}}$$

(22)

where  $\varepsilon_0$  is the permittivity of free space.  $\varepsilon_{Si}$  is the dielectric constant of silicon.  $N_{ch}$  is the channel doping concentration.  $\psi_B$  is the difference between the Fermi level in the channel region and the intrinsic Fermi level.

The virtual source velocity ( $v_{xo}$ ) is the average velocity of the channel carriers at the potential barrier near the source.

$$v_{\mathrm{x0}} = \frac{v}{1 - C_{\mathrm{ox}} R_{\mathrm{s}} W (1 + 2\delta) v}$$

(23)

where  $\delta$  is the drain-induced-barrier lowering (DIBL) with units of V/V. The carrier velocity can be extracted as follows,

$$v = \frac{I_{\rm ds} / W}{C_{\rm ox} (V_{\rm GS} - V_{\rm th,sat})}$$

(24)

According to (Khakifirooz et al., 2009), the above model has a reasonably good fit to the experimental  $I_{ds}$  versus  $V_{GS}$  characteristics and the experimental  $I_{ds}$  versus  $V_{DS}$  characteristics of nanoscale Si-based MOS transistors fabricated using poly-SiON gate stack as well as high-

K metal gate stack. The extracted  $v_{xo}$  for NMOS transistor (L = 35 nm) is around  $1.4 \times 10^7$  cm/s. Since  $v_{sat}$  for electrons in silicon is  $10^7$  cm/s (Norris & Gibbons, 1967), this shows that velocity saturation does not occur in the nanoscale Si-based MOS transistor.

Fig. 22. Illustration of the virtual source point ( $x_0$ ) in a NMOS transistor. The carrier charge density ( $Q_{ixo}$ ) and the virtual velocity ( $v_{xo}$ ) are defined at the top of the conduction band profile along the channel direction.  $R_s$  is the source series resistance.  $R_D$  is the drain series resistance.

#### 5. Apparent velocity saturation in the nanoscale MOS transistor

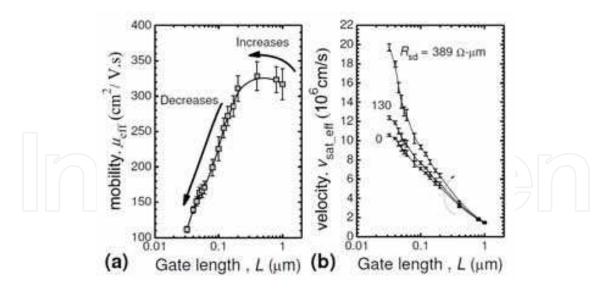

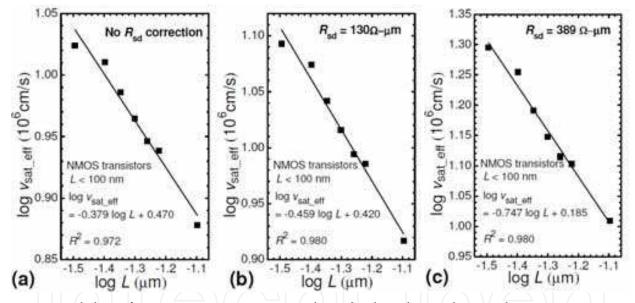

Fig. 23 shows the maximum  $\mu_{\text{eff}}$  versus *L* characteristics and the  $v_{\text{sat}_{eff}}$  versus *L* characteristics of a bulk NMOS transistor.  $\mu_{\text{eff}}$  is extracted from the linear  $I_{\text{ds}}$  versus  $V_{\text{GS}}$  characteristics (Schroder, 1998).  $v_{\text{eff}}$  is extracted using the saturation transconductance method (Lochtefeld et al., 2002).  $R_{\text{sd}}$  correction to  $v_{\text{eff}}$  has to be done as described by (Chou & Antoniadis, 1987) .  $R_{\text{sd}}$  is extracted using a modified version of the method according to (Chern et al., 1980). Note that  $v_{\text{sat}_{eff}}$  is the average value of  $v_{\text{eff}}$  when  $V_{\text{GS}}$  is close to  $V_{\text{DD}}$ . By taking the maximum  $\mu_{\text{eff}}$  to be independent of the gate length,  $v_{\text{sat}_{eff}}$  = constant x  $L_{\text{eff}}$  -1, based on equation (16b) and equation (16d). However, the experimental  $v_{\text{sat}_{eff}}$  = constant x  $L_{\text{eff}}$  - $\beta$  where  $\beta$  is less than 1 despite the uncertainty in  $R_{\text{sd}}$  measurements (see Fig. 24). This indicates that the carrier velocity tends to saturate when *L* decreases (see Fig. 23b).

Since the relationship between the carrier velocity and the low-field mobility is wellestablished (Khakifirooz & Antoniadis, 2006), we can have a better understanding of the apparent velocity saturation in the nanoscale MOS transistors by looking at the mobility. A strong reduction of mobility is typically observed in the silicon-based MOS transistors when the gate length is scaled (Romanjek et al., 2004; Cros et al., 2006; Cassé et al., 2009; Huet et al., 2008; Fischetti & Laux, 2001). The reason of this degradation is still not clearly understood. It is first attributed to the halo implants as its contribution to the channel doping concentration increases with decreasing gate length (Romanjek et al., 2004). However, this mobility degradation is also observed in the undoped double gate MOS

Fig. 23. Effects of scaling on bulk NMOS transistors ( $W = 1 \mu m$ ) (a) the  $\mu_{eff}$  versus *L* characteristics, (b) the  $v_{sat\_eff}$  versus *L* characteristics. Note that  $v_{sat\_eff}$  increases with increasing  $\mu_{eff}$ .  $R_{sd} = 0 \Omega$ - $\mu m$  refers to the case where  $R_{sd}$  correction is not performed.

Fig. 24. Validity of  $v_{\text{sat}\_eff}$  = constant x  $L_{\text{eff}}$  - $\beta$  where  $\beta$  is less than 1 despite the uncertainty in  $R_{\text{sd}}$  measurements. Note that log  $v_{\text{sat}\_eff}$  = - $\beta$ log  $L_{\text{eff}}$  + log constant.

transistors (Cros et al., 2006) and the undoped fully-depleted silicon-on-insulator (FD-SOI) MOS transistors (Cassé et al., 2009). This indicates that the halo implant is not the dominant factor involved in the degradation. Another limiting transport mechanism expected to be non-negligible in the short-channel MOS transistor is the presence of crystalline defects induced by S/D extension implants (Cros et al., 2006). Furthermore, Monte Carlo studies shows that ballistic transport has significant impact on the mobility degradation (Huet et al., 2008). Another explanation is that the increase in the long-range Coulombic scattering interactions between the high-density electron gases in the S/D regions and the channel electrons for very short channel MOS transistors (Fischetti & Laux, 2001). In an attempt to clarify the mobility degradation mechanism, (Cassé et al., 2009) used the differential

magnetoresistance technique for mobility extraction to eliminate the effects of series resistance  $(R_{sd})$  and the ballisticity introduced by L-independent resistance. However, strong mobility degradation is still observed in the undoped FD-SOI MOS transistors (L < 100 nm) at 20 K and thus the mobility degradation is likely to be caused by (i) the long-range Coulombic scattering interactions between the electron gases in the S/D regions and the channel electrons, (ii) the charged defects at the S/D regions, and (iii) the neutral defects at the S/D regions (Cassé et al., 2009). The apparent saturation of carrier velocity when L decreases can be understood as follows. As discussed in section 4.3, the effects of  $v_2$ dominates over the effects of  $v_1$  such as  $v_{\text{eff}} \approx v_2$ . From equation (15),  $v_2$  is the product of  $\mu_{\text{eff}}$ and  $\varepsilon(0^+)$ . From equation (16b),  $\varepsilon(0^+)$  increases when  $L_{\text{eff}}$  decreases. In short, when L decreases,  $\mu_{\text{eff}}$  decreases but  $\epsilon(0^+)$  increases. Hence,  $v_{\text{eff}}$  is expected to approach a constant when *L* decreases. Since  $v_{\text{sat}_{eff}}$  is the average value of  $v_{\text{eff}}$  when  $V_{\text{GS}}$  is close to  $V_{\text{DD}}$ ,  $v_{\text{sat}_{eff}}$  is expected to approach a constant when L decreases. This is probably why (Hauser, 2005) is able to use the velocity saturation model (see equation 5) to fit the experimental  $I_{ds}$  versus  $V_{\rm DS}$  characteristics of the nanoscale NMOS transistor (L = 90 nm). Note that Hauser used  $v_{\rm sat}$ as a fitting parameter. In his physics-based model,  $v_{sat}$  is taken to be 2.06×10<sup>7</sup> cm/s rather than  $1 \times 10^7$  cm/s (saturation velocity of electrons in silicon at room temperature). Therefore, the physics behind the apparent saturation of the carrier velocity is different from that of velocity saturation (the rate of energy gain from the lateral electric field is equal to the rate of energy loss to the surroundings by phonon scattering).

#### 6. Drain current saturation mechanism of the nanoscale MOS transistors

As mentioned in section 2, the two well-known mechanisms for drain current saturation in MOS transistors are pinch off and velocity saturation. However, we have shown that velocity saturation is unlikely to occur in the nanoscale MOS transistors. In addition, (Kim et al., 2008) reported that the experimental observation of velocity overshoot in the nanoscale bulk NMOS transistor (L = 36 nm) at room temperature. In section 5, we have unveiled that the apparent velocity saturation that occurs during scaling is caused by (i) the long-range Coulombic scattering interactions between the electron gases in the S/D regions and the channel electrons, (ii) the charged defects at the S/D regions and (iii) the neutral defects at the S/D regions (Cassé et al. 2009). Since velocity saturation involves the tradeoff between the rate of energy gain from lateral electric field and the rate of energy loss to the surroundings by phonon scattering, we believe that velocity saturation does not occur in the nanoscale transistors. Hence, it is possible that the drain current saturation mechanism in nanoscale MOS transistor is caused by pinch off rather than velocity saturation. In fact, several groups of researchers have developed compact models for the pinch-off region of the nanoscale MOS transistors (Navarro et al., 2005; Weidemann et al., 2007). For  $V_{DD} = 1 \text{ V}$ , the pinch-off point is less than 10 nm from the drain side (Navarro et al., 2005). This shows that the pinch-off point will always remain within the channel even though this point tends to shift towards the source side with increasing  $V_{\text{DS}}$ .

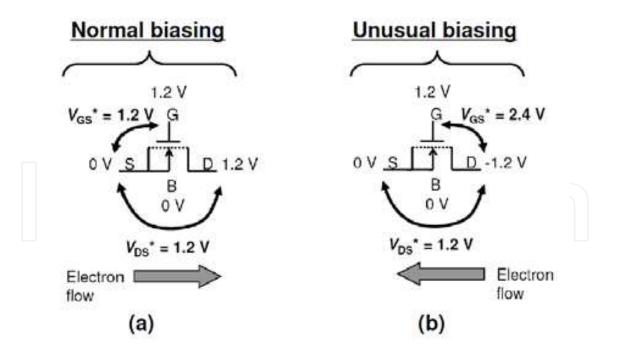

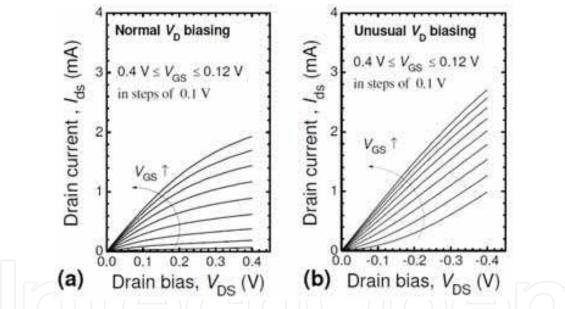

Our previous work gives the experimental evidence that the drain current saturation in the nanoscale NMOS transistor is caused by pinchoff (Lau et al., 2009). By simply changing the polarity of the drain bias ( $V_D$ ), it is possible to create a situation whereby pinchoff is unlikely to occur. As shown in Fig. 25, the normal biasing involves the application of a positive  $V_D$  to the drain terminal of a NMOS transistor. On the other hand, the unusual biasing involves

the application of a negative  $V_{\rm D}$  to the drain terminal of a NMOS transistor. The most obvious implication of such biasing is the direction of the electron flow. For the normal biasing condition, the electrons are injected from source terminal to drain terminal. For the unusual biasing condition, the electrons are injected from drain terminal to source terminal. In the other words, the effective source terminal for the unusual biasing is actually the drain terminal. To avoid confusion, we define  $V_{\rm GS}^*$  as the potential difference between the gate terminal and the terminal that injects electrons into the channel.  $V_{\rm DS}^*$  is the potential difference between the source terminal and drain terminal. From equation (8), the condition for pinchoff to occur is as follows,

$$V_{\rm DS}^{*} \ge \frac{V_{\rm GS}^{*} - V_{\rm th,sat}}{m}$$

(25)

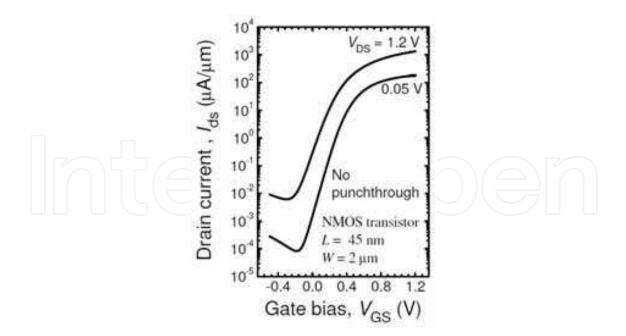

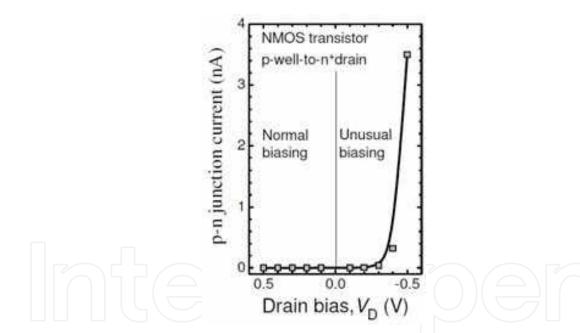

where *m* is between 1.1 and 1.4 (Taur & Ning, 1998,a). For our NMOS transistors,  $V_{DD}$  is 1.2 V. Under the normal biasing,  $V_{GS}^*$  is 1.2 V and  $V_{DS}^*$  is 1.2 V (see Fig. 25a). Under the unusual biasing,  $V_{GS}^*$  is 2.4 V and  $V_{DS}^*$  is 1.2 V (see Fig. 25b). Hence, normal biasing will be able to satisfy the condition for pinchoff and thus pinchoff can occur. However, the condition for pinchoff and thus pinchoff can occur. However, the condition for pinchoff cannot be satisfied under the unusual biasing because  $V_{GS}^*$  is much bigger than  $V_{DS}^*$ . From Fig.26, the nanoscale NMOS transistor (L = 45 nm) used in our study does not suffer from punchthrough. Note that negative  $V_D$  will forward bias the p-well-to-n<sup>+</sup>drain junction. To minimize the amount of forward biased p-n junction current in NMOS transistor under the unusual biasing, we limited the  $V_D$  to be -0.4 V (see Fig. 27). As shown

Fig. 25. Biasing conditions of the NMOS transistor (a) Under the normal biasing, a positive  $V_D$  of 1.2 V is applied to the drain terminal. The p-well-to-n<sup>+</sup> drain junction is reversed biased. (b) Under the unusual biasing condition, a negative  $V_D$  of -1.2 V is applied to the drain terminal. The p-well-to-n<sup>+</sup> drain junction is forward biased.

The Evolution of Theory on Drain Current Saturation Mechanism of MOSFETs from the Early Days to the Present Day

Fig. 26. The  $I_{ds}$  versus  $V_{GS}$  characteristics of the nanoscale NMOS transistor (L = 45 nm,  $W = 2 \mu m$ ).

Fig. 27. Selection of the unusual  $V_D$  biasing condition for NMOS transistor.

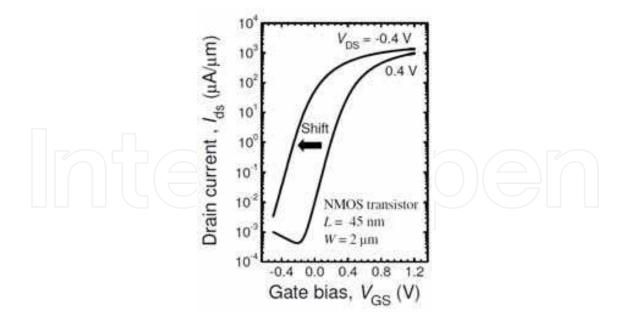

in Fig. 28, the application of  $V_D$ = -0.4 V to the NMOS transistor will shift the  $I_{ds}$  versus  $V_{GS}$  characteristics towards the left. If drain current saturation mechanism is caused by velocity saturation, we will expect drain current saturation to occur in both normal  $V_D$  biasing and unusual  $V_D$  biasing. If drain current saturation mechanism is caused by pinchoff, we will expect drain current saturation to occur in the normal  $V_D$  biasing but not in the unusual  $V_D$  biasing. Fig. 29 shows that there is no obvious current saturation in the experimental  $I_{ds}$  versus  $V_{DS}$  characteristics of the NMOS transistor under the unusual biasing (negative  $V_D$ ).

Fig. 28. Effects of the negative  $V_D$  on  $I_{ds}$  versus  $V_{GS}$  characteristics of NMOS transistor.

Fig. 29. The  $I_{ds}$  versus  $V_{DS}$  characteristics of a bulk NMOS transistor (L = 45 nm,  $W = 2 \mu m$ ) (a) Normal  $V_D$  biasing (positive  $V_D$ ), (b) Unusual  $V_D$  biasing (negative  $V_D$ ).

#### 7. References

- Barral, V.; Poiroux, T.; Munteanu, D.; Autran, J-L. & Deleonibus, S. (2009). Experimental Investigation on the Quasi-Ballistic Tranport: Part II – Backscattering Coefficient Extraction and Link With the Mobility. *IEEE Trans. Electron Dev.*, Vol. 56, No. 3., (Mar 2009) pp.420-430, ISSN: 0018-9383.

- Bloch, F. (1928). Uber die Quantenmechanik der Elektronen in Kristalgittern. Zeitschrift fur Physik, Vol. 52, No. 7-8, pp. 555-600. (Note: This paper was in German. The title after translation into English is "Quantum mechanics of electrons in crystal lattices".)

- Cassé, M. ; Rochette, F.; Thevenod, L.; Bhouri, N.; Andrieu, F.; Reimbold, G.; Boulanger, F.; Mouis, M.; Ghibaudo, G. & Maude, D.K. (2009). A comprehensive study of magnetoresistance mobility in short channel transistors: Application to strained and unstrained silicon-on-insulator field-effect transistors. J. Appl. Phys., Vol. 105, No. 8, (April 2009) pp. 084503-1 to 084503-9, ISSN: 0021-8979.

- Chen, C-H.; Lee, T.L.; Hou, T.H.; Chen, C.L.; Chen, C.C.; Hsu, J.W.; Cheng, K.L.; Chiu, Y.H.; Tao, H.J.; Jin, Y.; Diaz, C.H.; Chen, S.C. & Liang, M.-S. (2004). Stress Memorization Technique (SMT) by Selectively Strained-Nitride Capping for sub-65 nm High-Performance Strained-Si Device Application. Symposium on VLSI Technology Digest of Technical Papers, pp. 56-57, ISBN-10: 0 7803 8289 7, Honolulu, USA, Jun 2004, Widerkehr and Associates, Gaithersburg.

- Chen, M-.J.; Huang, H.-T.; Chou, Y.-C.; Chen, R.-T.; Tseng, Y.-T.; Chen, P.-N. & Diaz, C.H. (2004). Separation of channel backscattering coefficients in nanoscale MOSFETs. *IEEE Trans. Electron Dev.*, Vol. 51, No. 9, (Sept 2004) pp. 1409-1415, ISSN: 00189383.

- Cheong, W-S.; Yoon, S-M.; Yang, S. & Hwang, C-S. (2009). Optimization of an Amorphous In-Ga-Zn-Oxide Semiconductor for Top-Gate Transparent Thin-Film Transistor. *Journal of the Korean Physical Society*, Vol. 54, No. 5, (May 2009) pp. 1879-1884, ISSN: 0374-4884.

- Chern, J. G. J.; Chang, P.; Motta, R. F. & Godinho, N. (1980). A new method to determine MOSFET channel length. *IEEE Electron Device Lett.*, Vol. 1, No. 9, (Sept 1980) pp. 170-173, ISSN: 0741-3106.

- Chiang, W.T.; Pan, J.W.; Liu, P.W.; Tsai, C.H. & Ma, G.H. (2007). Strain Effects of Si and SiGe Channel on (100) and (110) Si Surfaces for Advanced CMOS Applications. Symposium on VLSI Technology, Systems and Application (VLSI-TSA), pp. 84-85, ISBN-10: 1424405858, Hsinchu, Taiwan, April 2007, Institute of Electrical and Electronics Engineers Inc., United States.

- Choi, K.; Jagannathan, H.; Choi, C.; Edge, L.; Ando, T.; Frank, M.; Jamison, P.; Wang, M.; Cartier, E.; Zafar, S.; Bruley, J.; Kerber, A.; Linder, B.; Callegari, A.; Yang, Q.; Brown, S.; Stathis, J.; Iacoponi, J.; Paruchuri, V. & Narayanan, V. (2009). Extremely Scaled Gate-First High-k/Metal Gate Stack with EOT of 0.55 nm Using Novel Interfacial Layer Scavenging Techniques for 22nm Technology Node and Beyond. Symposium on VLSI Technology Digest of Technical Papers, pp. 138-139, ISBN: 978-1-4244-3308-7, in Kyoto, Japan, Jun 2009.

- Chou, S.Y.; Antoniadis, D.A. & Smith, H.I. (1985). Observation of electron velocity overshoot in sub-100-nm-channel MOSFET's in Silicon. *IEEE Electron Dev. Lett.*, Vol. 6, No. 12, (Dec 1985) pp. 665-667, ISSN: 0741-3106.

- Chou S.Y. & Antoniadis, D.A. (1987). Relationship between measured and intrinsic transconductances of FET's. *IEEE Trans. Electron Dev.*, Vol. 34, No. 2, (Feb 1987) pp. 448 450, ISSN: 0018-9383.

- Cros, A.; Romanjek, K.; Fleury, D.; Harrison, S.; Cerutti, R.; Coronel, P.; Dumont, B.; Pouydebasque, A.; Wacquez, R.; Duriez, B.; Gwoziecki, R.; Boeuf, F.; Brut, H.; Ghibaudo, G. & Skotnicki, T. (2006). Unexpected mobility degradation for very short devices: A new challenge for CMOS scaling. *IEEE Electron Devices Meeting* (IEDM), pp. 1-4, ISBN-10: 1424404398, San Francisco, CA, United States, Dec 2006, Institute of Electrical and Electronics Engineers Inc., Piscataway, NJ, United States.

- Fischetti, M.V. & Laux, S.E. (2001). Long-range Coulomb interactions in small Si devices. Part I: Performance and reliability. J. Appl. Phys, Vol. 89, No. 2, (Jan 2001) pp. 1205-1231, ISSN: 00218979.

- Fuchs, E.; Dolfus, P.; Carval, G.L.; Barraud, S.; Villanueva, D.; Salvetti, F.; Jaouen, H. & Skotnicki, T.(2005). A new backscattering model giving a description of the quasiballistic transport in nano-MOSFET. *IEEE Trans. Electron Dev.*, Vol. 52, No. 10, (Oct 2005) pp. 2280-2289, ISSN: 0018-9383.

- Ghibaudo, G. & Balestra, F. (1997). Low temperature characterization of silicon CMOS devices. *Microelectron. Reliab.*, Vol. 37, No. 9, (Sept 1997) pp. 1353-1366, ISSN: 0026-2714.

- Guo, J.-C.; Chung, S.S.-S. & Hsu, C.C.-H. (1994). A new approach to determine the effective channel length and the drain-and-source series resistance of miniaturized MOSFET's . *IEEE Trans. Electron Dev.*, Vol. 41, No. 10, (Oct 1994) pp. 1811-1818, ISSN: 0018-9383.

- Hauser, J.R. (2005). A New and Improved Physics-Based Model for MOS Transistors. *IEEE Trans. Electron Dev.*, Vol. 52, No. 12, (Dec 2005) pp. 2640- 2647, ISSN: 00189383.

- Heiblum, M. & Eastman, L. F. (1987). Ballistic Electrons in Semiconductors. *Scientific American*, Vol. 256, No. 2, (Feb 1987) pp. 64-73, ISSN: 00368733.

- Hofstein, S.R. & Heiman, F.P. (1963). Silicon insulated-gate field-effect transistor. *IEEE Proceedings*, Vol. 51, No. 9, (Sept 1963) pp. 1190- 1202.

- Huang, J.; Heh, D.; Sivasubramani, P.; Kirsch, P. D.; Bersuker, G.; Gilmer, D. C.; Quevedo-Lopez, M.A.; Hussain, M. M.; Majhi, P.; Lysaght, P.; Park, H.; Goel, N.; Young, C.; Park, C.S.; Park, C.; Cruz, M.; Diaz, V.; Hung, P. Y.; Price, J.; Tseng, H.-H. & Jammy, R. (2009) Gate First High-k/ Metal Gate Stacks with Zero SiO<sub>x</sub> Interface Achieving EOT = 0.59 nm for 16 nm Application. Symposium on VLSI Technology Digest of Technical Papers, pp. 34-35, ISBN: 978-1-4244-3308-7, in Kyoto, Japan.

- Huet, K.; Querlioz, D.; Chaisantikulwat, W.; Saint-Martin, J.; Bournel, A.; Moulis, M. & Dollfus, P. (2008). Monte Carlo study of apparent magnetoresistance mobility in nanometer scale metal oxide semiconductor field effect transistors. J. Appl. Phys., Vol. 104, No. 4, (Aug 2008) pp. 044504-1 to 044504-7, ISSN: 00218979.

- Jing, W. & Lundstrom, M. (2002). Does source-to-drain tunneling limits the ultimate scaling of MOSFETs ? IEEE Electron Devices Meeting (IEDM), pp. 707-710, ISBN-10: 0 7803 7462 2, San Francisco, CA, USA, Dec 2002, Institute of Electrical and Electronics Engineers, Piscataway, NJ, USA.

- Kawaura, H.; Sakamoto, T. & Baba, T. (2000). Observation of source-to-drain direct tunneling in 8 nm gate electrically variable shallow junction metal-oxidesemiconductor field-effect transistors. *Appl. Phys. Lett.*, Vol. 76, No. 25, (Jun 2000) pp. 3810-3812, ISSN: 00036951.

- Kawaura, H. & Baba, T. (2003). Direct Tunneling from Source to Drain in Nanometer-Scale Silicon Transistors. *Jpn. J. Appl. Phys.*, Vol. 42, No. 2A, (Feb 2003) pp. 351-357, ISSN: 00214922.

- Khakifirooz, A. & Antoniadis, D.A. (2006). Transistor Performance Scaling: The Role of Virtual Source Velocity and Its Mobility Dependence. *IEEE Electron Devices Meeting* (IEDM), pp. 1-4, ISBN-10: 1424404398, San Francisco, CA, United states, Dec 2006, Institute of Electrical and Electronics Engineers, Piscataway, NJ, United States.

- Khakifirooz, A. & Antoniadis, D.A. (2008). MOSFET Performance Scaling Part I: Historical Trends. IEEE Trans. Electron Dev., Vol. 55, No. 6 (Jun 2008) pp. 1391-1400, ISSN 0018-9383.

- Khakifirooz, A.; Nayfeh, O.M. & Antoniadis, D.A. (2009). A simple semiempirical shortchannel MOSFET current: voltage model continuous across all regions of operation and employing only physical parameters. IEEE Trans. Electron Dev., Vol. 56, No. 8 (Aug 2009) pp. 1674-1680, ISSN 0018-9383.

- Kim, J.; Lee, J.; Yun, Y.; Park, B-G.; Lee, J.D. & Shin, H. (2008). Extraction of Effective Carrier Velocity and Observation of Velocity Overshoot in Sub-40 nm MOSFETs. *Journal of Semiconductor Technology and Science*, Vol. 8, No. 2, (Jun 2008) pp. 115-120, ISSN: 1598-1657. Note that this is a Korean journal.

- Kondo, M. & Tanimoto, H. (2001). Accurate Coulomb mobility model for MOS inversion layer and its application to NO-oxynitride devices. *IEEE Trans. Electron Dev.*, Vol. 48, No. 2, (Feb 2001) pp. 265-270, ISSN: 00189383.

- (a) Lau, W.S.; Yang, Peizhen; Eng, C.W.; Ho, V.; Loh, C.H.; Siah, S.Y.; Vigar, D. & Chan, L. (2008). A study of the linearity between *I*<sub>on</sub> and log*I*<sub>off</sub> of modern MOS transistors and its application to stress engineering. *Microelectronics Reliab.*, Vol. 48, No. 4, (April 2008) pp. 497-503, ISSN: 0026-2714.

- (b) Lau, W.S.; Yang, Peizhen; Ho, V.; Toh, L.F.; Liu, Y.; Siah, S.Y. & Chan, L. (2008). An explanation of the dependence of the effective saturation velocity on gate voltage in sub-0.1 μm metal-oxide-semiconductor transistors by quasi-ballistic transport theory. *Microelectronics Reliab.*, Vol. 48, No. 10, (Oct 2008) pp. 1641-1648, ISSN: 0026-2714.

- Lau, W.S.; Yang, Peizhen; Chian, Jason Zhiwei; Ho, V.; Loh, C.H.; Siah, S.Y. & Chan, L. (2009). Drain current saturation at high drain voltage due to pinch off instead of velocity saturation in sub-100 nm metal-oxide-semiconductor transistors. *Microelectronics Reliab.*, Vol. 49, No. 1, (Jan 2009) pp. 1-7, ISSN: 00262714.

- Lee, W.; Kuo, J. J.-Y; Chen, W. P.-N; Su, P. & Jeng, M-C. (2009). Impact of Uniaxial Strain on Channel Backscattering Characteristics and Drain Current Variation for Nanoscale PMOSFETs. Symposium on VLSI Technology Digest of Technical Papers, pp. 112-113, ISBN: 978-1-4244-3308-7, Kyoto, Japan, Jun 2009.

- Lochtefeld, A.; Djomehri, I.J.; Samudra, G. & Antoniadis, D.A. (2002). New insights into carrier transport in n-MOSFETs. *IBM J. Res. & Dev.*, Vol. 46, No. 2-3, (March-May 2002) pp. 347-357, ISSN: 00188646.

- Lundstrom, M. (1997). Elementary Scattering Theory of the Si MOSFET. *IEEE Electron Device Lett.*, Vol. 18, No. 7, (July 1997) pp. 361-363, ISSN: 0741-3106.

- Lundstrom, M. & Ren, Z. (2002). Essential physics of carrier transport in nanoscale MOSFETs. *IEEE Trans. Electron Dev.*, Vol. 49, No. 1, (Jan 2002) pp. 133 -141, ISSN: 00189383.