# **DISCLAIMER:**

This document does not meet the current format guidelines of the Graduate School at The University of Texas at Austin.

It has been published for informational use only.

The Dissertation Committee for Michael Brendan Sullivan certifies that this is the approved version of the following dissertation:

# LOW-COST DUPLICATION FOR SEPARABLE ERROR DETECTION IN COMPUTER ARITHMETIC

Committee:

Mattan Erez, Supervisor

Earl E. Swartzlander, Jr., Co-Supervisor

Nur A. Touba

Aloysius K. Mok

Michael J. Schulte

# LOW-COST DUPLICATION FOR SEPARABLE ERROR DETECTION IN COMPUTER ARITHMETIC

by

Michael Brendan Sullivan, BA; BS; MS; MSE

# DISSERTATION

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

# **DOCTOR OF PHILOSOPHY**

THE UNIVERSITY OF TEXAS AT AUSTIN August 2015

# LOW-COST DUPLICATION FOR SEPARABLE ERROR DETECTION IN COMPUTER ARITHMETIC

Michael Brendan Sullivan, PhD The University of Texas at Austin, 2015

Supervisors: Mattan Erez Earl E. Swartzlander, Jr.

Low-cost arithmetic error detection will be necessary in the future to ensure correct and safe system operation. However, current error detection mechanisms for arithmetic either have high area and energy overheads or are complex and offer incomplete protection against errors. Full duplication is simple, strong, and separable, but often is prohibitively costly. Alternative techniques such as arithmetic error coding require lower hardware and energy overheads than full duplication, but they do so at the expense of high design effort and error coverage holes. The goal of this research is to mitigate the deficiencies of duplication and arithmetic error coding to form an error detection scheme that may be readily employed in future systems. The techniques described by this work use a general duplication technique that employs an alternate number system in the duplicate arithmetic unit. These novel dual modular redundancy organizations are referred to as *low-cost duplication*, and they provide compelling efficiency and coverage advantages over prior arithmetic error detection mechanisms.

# CONTENTS

| Ab  | ostrac  | t             |             |                                                  | v    |

|-----|---------|---------------|-------------|--------------------------------------------------|------|

| Co  | onten   | ts            |             |                                                  | vi   |

| Lis | st of 7 | <b>[ables</b> |             |                                                  | vii  |

| Lis | st of I | Figures       |             |                                                  | viii |

| 1   | Intr    | oductio       | n           |                                                  | 1    |

|     | 1.1     | Arithr        | netic Erroi | Detection Design Goals                           | 1    |

|     |         | 1.1.1         | Strong, F   | ault-Agnostic Error Detection                    | 2    |

|     |         | 1.1.2         | Separable   | e Checking                                       | 2    |

|     |         | 1.1.3         | Low-Late    | ency, Concurrent Detection                       | 2    |

|     |         | 1.1.4         | Low Are     | a and Energy Overheads                           | 3    |

|     | 1.2     | Curren        | nt Separab  | le Arithmetic Error Detection Approaches         | 3    |

|     |         | 1.2.1         | Duplicat    | ion, Partial Duplication, and Lazy Duplication . | 3    |

|     |         | 1.2.2         | Residue     | Checking                                         | 4    |

|     | 1.3     | A New         | v Approach  | h: Low-Cost Duplication                          | 5    |

|     | 1.4     | The St        | ructure of  | this Dissertation                                | 6    |

| 2   | Bacl    | kground       | d Concept   | S                                                | 8    |

|     | 2.1     | •             | -           | s in Computer Arithmetic                         | 8    |

|     |         | 2.1.1         |             | chanisms                                         | 8    |

|     |         |               | 2.1.1.1     | Transient Faults                                 | 9    |

|     |         |               | 2.1.1.2     | Permanent Faults                                 | 9    |

|     |         |               | 2.1.1.3     | Design Faults                                    | 10   |

|     |         |               | 2.1.1.4     | Environmental Timing Faults                      | 10   |

|     |         |               | 2.1.1.5     | Fabrication Faults                               | 11   |

|     |         | 2.1.2         | Error Mo    | odels                                            | 11   |

|     |         |               | 2.1.2.1     | Bits and Bursts                                  | 11   |

|     |         |               | 2.1.2.2     | Arithmetic Weight                                | 12   |

|     |         |               | 2.1.2.3     | Single Device Errors                             | 12   |

|     |         |               | 2.1.2.4     | Single Component Errors                          | 12   |

|   | 2.2 | Backg   | round for Goal #1: Strong and Fault-Agnostic                                    |                |

|---|-----|---------|---------------------------------------------------------------------------------|----------------|

|   |     | Error   | Detection                                                                       | 13             |

|   |     | 2.2.1   | Ensuring that the Duplicate Checker is Fault-Agnostic .                         | 14             |

|   | 2.3 | Backg   | round for Goal #2: Separable Checking                                           | 14             |

|   |     | 2.3.1   | A Taxonomy of Separable Error Detectors                                         | 15             |

|   |     |         | 2.3.1.1 Non-Systematic Checkers                                                 | 16             |

|   |     |         | 2.3.1.2 Inseparable Checkers                                                    | 16             |

|   |     |         | 2.3.1.3 Design Co-Dependent Checkers                                            | 17             |

|   |     |         | 2.3.1.4 Design-Reactive Checkers                                                | 17             |

|   |     |         | 2.3.1.5 Timing-Reactive Checkers                                                | 17             |

|   |     |         | 2.3.1.6 Fully Separable Checkers                                                | 17             |

|   | 2.4 | Backg   | round for Goal #3: Low-Latency, Concurrent                                      |                |

|   |     | Error   | Detection                                                                       | 18             |

|   | 2.5 | Backg   | round for Goal #4: Low Area and Energy Overheads                                | 18             |

|   | 2.6 | The M   | Iethodology of this Research                                                    | 19             |

|   |     | 2.6.1   | Hardware Synthesis and Analysis                                                 | 19             |

|   |     | 2.6.2   | Encoding of Input Operands and End-to-End Protection                            | 19             |

|   |     | 2.6.3   | Arithmetic Error Correction                                                     | 20             |

| 3 | Low | -Cost F | Duplication for Fixed-Point Addition                                            | 21             |

| 3 | 3.1 |         | arry-Save Number System and a Modified Checker                                  | 21             |

|   | 3.1 | 3.1.1   | Carry-Save Addition                                                             | 21             |

|   |     | 3.1.2   | The Carry-Save Equality Checker                                                 | 22             |

|   |     | 3.1.3   |                                                                                 | 22             |

|   |     | 3.1.3   | Numbers                                                                         | 23             |

|   | 2 2 | Carry-  | -Save Duplication                                                               | 23<br>24       |

|   | 3.2 | 3.2.1   | Relationship to Existing Work                                                   | 24<br>25       |

|   |     | 5.2.1   | 3.2.1.1 Lazy Error Detection                                                    | 2 y<br>2 5     |

|   |     |         | 3.2.1.1         Eazy Enfor Detection           3.2.1.2         Residue Checking | 2)<br>26       |

|   |     | 3.2.2   | Carry-Save Duplication Evaluation                                               | 20             |

|   | 3.3 | c .     | -Free/Carry-Propagate Duplication:                                              | 27             |

|   | 3.3 | •       | ing-Reactive Variant of Carry-Save Duplication                                  | 31             |

|   |     |         |                                                                                 | 31             |

|   |     |         |                                                                                 | 22             |

|   | 3 / | 3.3.1   | Carry-Free/Carry-Propagate Evaluation                                           | 33<br>38       |

|   | 3.4 | 3.3.1   |                                                                                 | 33<br>38<br>38 |

|   |      | 3.4.2   | CP/CF Duplication Discussion and Future Work         | 38 |

|---|------|---------|------------------------------------------------------|----|

| 4 | Low  | -Cost D | Puplication for Fixed-Point Multiplication           | 40 |

|   | 4.1  | Low-C   | Cost Duplicate Multiplication Methodology            | 40 |

|   |      | 4.1.1   | The Baseline Multipliers                             | 40 |

|   |      | 4.1.2   | Strict and Lazy Duplication                          | 41 |

|   |      | 4.1.3   | Residue Checking                                     | 42 |

|   | 4.2  | Carry-  | Save Low-Cost Duplication                            | 43 |

|   |      | 4.2.1   | Carry-Save Karatsuba Duplication                     | 44 |

|   | 4.3  | Residu  | e Number System Duplication                          | 47 |

|   | 4.4  | Discus  | sion and Future Work                                 | 50 |

|   |      | 4.4.1   | Further RNS Duplication Evaluation                   | 50 |

|   |      | 4.4.2   | Alternate Number Systems and Organizations           | 50 |

|   |      | 4.4.3   | Signed Arithmetic and Multiply-Accumulate            | 50 |

| 5 | Floa | ting-Po | int Multiplication                                   | 52 |

|   | 5.1  | A Brie  | f Introduction to Floating-Point Multiplication      | 53 |

|   | 5.2  | Prior V | Nork in Floating-Point Error Detection               | 56 |

|   | 5.3  | Approx  | ximate Duplication Based on Truncated Multiplication | 57 |

|   |      | 5.3.1   | An Imprecision Threshold Checker for Truncated       |    |

|   |      |         | Significand Multiplication                           | 58 |

|   |      | 5.3.2   | Using Truncated Significand Multiplication for       |    |

|   |      |         | Approximate Duplication                              | 59 |

|   |      | 5.3.3   | Separable Detection of Different Floating-Point      |    |

|   |      |         | Rounding Modes                                       | 63 |

|   |      | 5.3.4   | Use of Other Approximation Schemes and Number        |    |

|   |      |         | Systems                                              | 63 |

|   | 5.4  | Applic  | ation-Level Error Injection and Sensitivity Study    | 64 |

|   |      | 5.4.1   | Binary Instrumentation-Based Error Injector          | 65 |

|   |      |         | 5.4.1.1 Comparison to Prior Error Injectors          | 65 |

|   |      | 5.4.2   | Error Injection Results                              | 66 |

|   | 5.5  | Discus  | sion and Future Work                                 | 69 |

|   |      | 5.5.1   | The Use of Carry-Save Duplication for Exponent       |    |

|   |      |         | Checking                                             | 69 |

|    | 5.5.2     | The Use of Lazy Carry-Save Duplication for          |    |

|----|-----------|-----------------------------------------------------|----|

|    |           | Significand Checking                                | 69 |

|    | 5.5.3     | The Use of RNS Duplication for Significand Checking | 69 |

|    | 5.5.4     | Correctly Diagnosing Permanent Failures             | 70 |

|    | 5.5.5     | Dynamically Tunable Coverage                        | 70 |

| 6  | Summary & | Broader Applicability                               | 72 |

|    | 6.0.6     | Security Applications                               | 72 |

|    | 6.0.7     | Stochastic or Timing-Speculative Computing          | 73 |

| Re | eferences |                                                     | 74 |

# LIST OF TABLES

| 1.1 | An overview of the low-cost duplication schemes in this dissertation. | 7  |

|-----|-----------------------------------------------------------------------|----|

| 3.1 | Baseline adder properties.                                            | 29 |

| 3.2 | The overheads of carry-save duplication and lazy error detection      | 30 |

| 3.3 | A summary of the separable adder error detectors with complete        |    |

|     | single-component error coverage                                       | 33 |

| 3.4 | Baseline adders with varying delay budgets                            | 34 |

| 3.5 | The area and energy allocation of the baseline adders.                | 34 |

| 3.6 | The absolute cost of separable error detection for adders of          |    |

|     | varying speeds. Strict, carry-save, and CP/CF duplication are shown.  | 35 |

| 3.7 | The overheads of separable error detection relative to adders of      |    |

|     | varying speeds. Strict, carry-save, and CP/CF duplication are shown.  | 36 |

| 3.8 | The CP/CF parameters used in Table 3.6 and Table 3.7.                 | 37 |

| 4.1 | The baseline multipliers selected for this work                       | 41 |

| 4.2 | The overheads of lazy and lazy carry-save duplication. Lazy           |    |

|     | carry-save duplication avoids the need for carry-propagate            |    |

|     | addition in the duplicate unit, increasing efficiency.                | 45 |

| 4.3 | The overheads of lazy and carry-save Karatsuba duplication            |    |

|     | (relative to a baseline Karatsuba multiplier).                        | 47 |

| 4.4 | The overheads of residue number system duplication                    |    |

|     | (relative to the compressor-based fully parallel multiplier)          | 49 |

| 5.1 | An example of truncated multiplication. Two 3-bit significands        |    |

|     | are multiplied. DecE and BinE denote the exact result (before         |    |

|     | normalization or rounding), and DecA and BinA give the                |    |

|     | approximate result from a truncated multiplier using the first        |    |

|     | three bits of the partial product matrix                              | 58 |

# LIST OF FIGURES

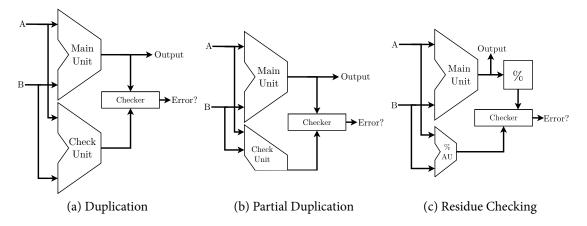

| 1.1 | Arithmetic error detection through duplication and residue             |    |

|-----|------------------------------------------------------------------------|----|

|     | checking. The % component represents residue generation, and           |    |

|     | the % arithmetic unit (AU) performs residue generation and             |    |

|     | modular arithmetic                                                     | 4  |

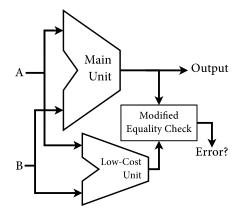

| 1.2 | A block diagram of low-cost duplication. An operation is               |    |

|     | performed both with the main arithmetic unit and with a                |    |

|     | low-cost duplicate unit. This low-cost unit converts the inputs        |    |

|     | into an alternate number system, using redundant arithmetic            |    |

|     | and application-specific number representations to increase the        |    |

|     | speed and efficiency of the duplicate operation. Following the         |    |

|     | completion of the operation, a modified checker tests the              |    |

|     | equality of the main arithmetic result with the duplicate result in    |    |

|     | its alternative format                                                 | 6  |

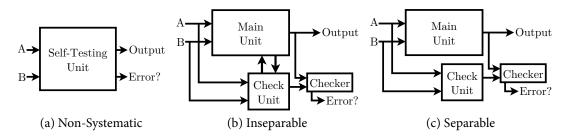

| 2.1 | The separability classification of arithmetic error detecting codes    |    |

|     | and the design of different error checkers                             | 15 |

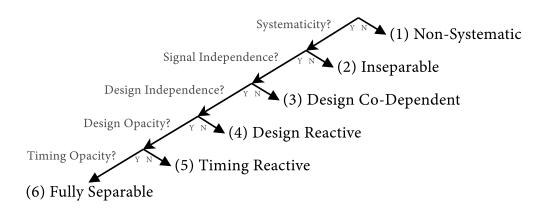

| 2.2 | A taxonomy of separability. Designs are arranged in order of           |    |

|     | increasing separability going from the upper right to the bottom left. | 16 |

| 3.1 | An example depicting decimal and binary three-operand                  |    |

|     | addition. Carry-save arithmetic uses the intermediary sum and          |    |

|     | carry results directly and can perform binary arithmetic within a      |    |

|     | constant full-adder delay                                              | 23 |

| 3.2 | A depiction of the carry-save equality checker. Cancellation is        |    |

|     | detected between the carry-save and positional inputs through a        |    |

|     | bit-sliced, constant-delay structure. Any non-complementary            |    |

|     | bits are detected through an OR reduction tree                         | 23 |

| 3.3 | The Dadda dot diagram [105] of the bits and carry dependencies      |    |

|-----|---------------------------------------------------------------------|----|

|     | in the one's and two's complement checkers. Dots represent bits     |    |

|     | of data, and directional arrows indicate a carry-dependence         |    |

|     | between bits. Therefore, the top and bottom row of dots             |    |

|     | respectively represent the sum and carry bits output from the full  |    |

|     | adders in the carry-save equality checker. An 8-bit checker is      |    |

|     | shown; no carry-dependence exists between digits due to the         |    |

|     | carry-save representation. The carry-out of the final bit-slice     |    |

|     | differs between the one's complement and two's complement           |    |

|     | equality checker; it is accordingly highlighted in grey             | 24 |

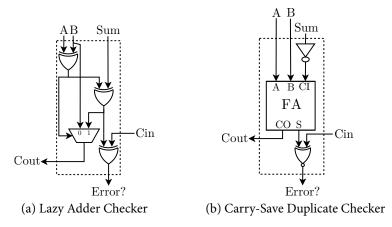

| 3.4 | A 1-bit slice of the lazy adder checker [106] and of the carry-save |    |

|     | duplicate checker.                                                  | 25 |

| 3.5 | A block diagram of the carry-save residue checker. All carry        |    |

|     | propagation during residue generation and modular addition is       |    |

|     | avoided by using carry-save modular multi-operand adders            |    |

|     | (CS-MOMAs); a carry-save equality checker is used at the output     |    |

|     | to verify the congruence of the output with the result of modular   |    |

|     | arithmetic. The % component represents carry-save residue           |    |

|     | generation without a final carry-propagate modular adder            | 28 |

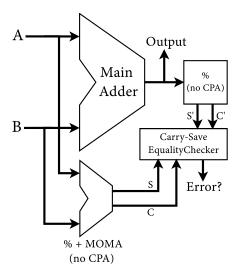

| 3.6 | Pareto-efficient 16-bit adder designs. The highlighted adder        |    |

|     | minimizes the $ED^2$ metric and is used as a baseline. A similar    |    |

|     | selection procedure is used to choose the 32, 64, and 128-bit       |    |

|     | baseline adders                                                     | 28 |

| 3.7 | The area and power of traditional and modified residue checking,    |    |

|     | normalized with respect to carry-save duplication (denoted          |    |

|     | "long residue checking"). The carry-save duplicate checker is       |    |

|     | marked by a rhombus                                                 | 29 |

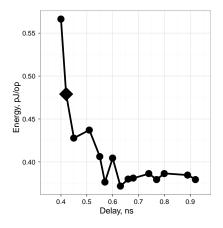

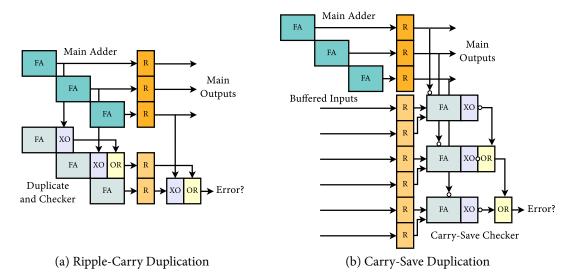

| 3.8 | Ripple-carry duplication and carry-save duplication for a 3-bit     |    |

|     | ripple-carry adder. Cells labeled FA denote full adders, R denote   |    |

|     | registers, XO denote XOR gates, and OR denote OR gates. While       |    |

|     | both ripple-carry duplication and carry-save duplication use the    |    |

|     | same number of logic cells, ripple-carry duplication uses fewer     |    |

|     | pipeline registers due to some overlapped execution. For            |    |

|     | simplicity, two-rail checking logic is not shown                    | 32 |

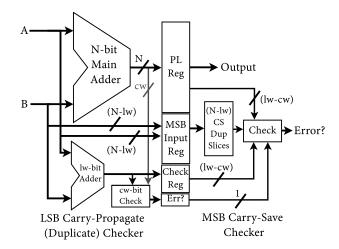

| 3.9  | A block diagram of carry-propagate/carry-free duplication. A               |    |

|------|----------------------------------------------------------------------------|----|

|      | partial adder duplicates the <i>lw</i> least-significant bits of addition, |    |

|      | <i>cw</i> of which are checked in the first pipeline stage (in parallel    |    |

|      | with the main addition). In the following pipeline stage, the              |    |

|      | ( <i>lw-cw</i> ) duplicated-but-unchecked bits are equality checked, and   |    |

|      | the $(N-cw)$ unduplicated bits are checked via carry-save                  |    |

|      | duplication. The carry-out of the strict duplicate adder (which is         |    |

|      | passed through a register to the carry-in of the carry-save                |    |

|      | duplicate checker) is not shown.                                           | 33 |

| 3.10 | An alternate error detection scheme that employs a split two-rail          |    |

|      | checker along with duplication.                                            | 39 |

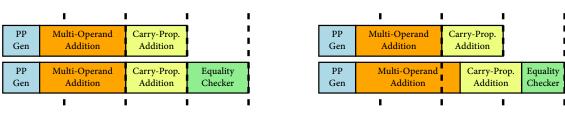

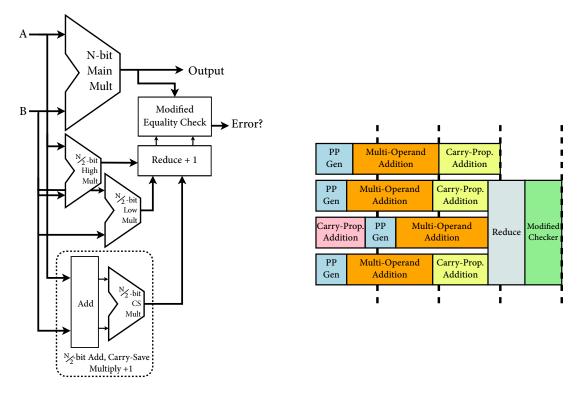

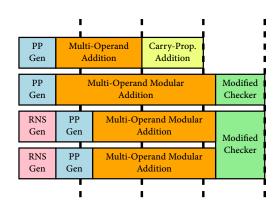

| 4.1  | The stages of strict and lazy duplication. "PP gen" denotes partial        |    |

|      | product generation. Strict duplication uses a mirrored multiplier          |    |

|      | for checking, whereas lazy duplication utilizes any extra                  |    |

|      | detection latency to reduce the complexity of the duplicate                |    |

|      | multiplier. Simple timing diagrams are shown for a multiplier;             |    |

|      | the relative time spent in each step of computation is not                 |    |

|      | accurate and is for visualization purposes                                 | 41 |

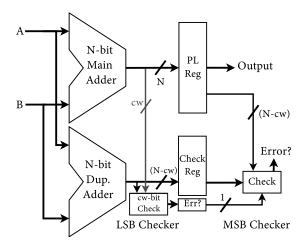

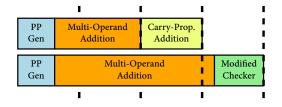

| 4.2  | Carry-propagate addition can be eliminated in the duplicate                |    |

|      | multiplier by employing a carry-save equality checker.                     | 44 |

| 4.3  | Karatsuba multiplication can perform an N-bit fixed-point                  |    |

|      | multiplication using three <sup>N</sup> /2-bit multipliers. Carry-free     |    |

|      | duplication uses a modified checker to eliminate the                       |    |

|      | carry-propagate addition of the sub-components.                            | 46 |

| 4.4  | A block diagram and visualization of RNS duplication. "RNS                 |    |

|      | Gen" represents residue generation. Partial product generation             |    |

|      | and multi-operand addition are modified specific to each                   |    |

|      | modulus. Multiplication of an RNS-encoded number can                       |    |

|      | proceed more quickly than its fixed-point counterpart; this extra          |    |

|      | slack can lead to overall cost savings                                     | 48 |

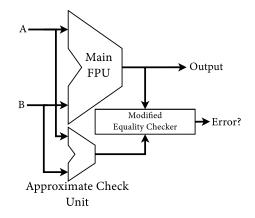

| 5.1  | Block diagram of approximate duplication. A reduced-precision              |    |

|      | unit checks the results of computation (to within a known tolerance).      | 53 |

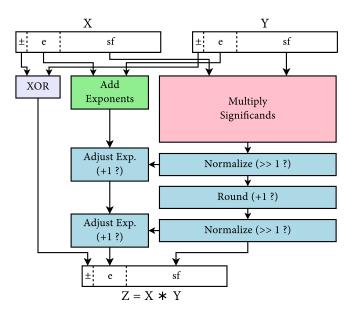

| 5.2 | A block diagram of floating-point multiplication. The exponents    |    |

|-----|--------------------------------------------------------------------|----|

|     | of the inputs are summed, the significands multiplied, and the     |    |

|     | significand of the result normalized and rounded to fit within the |    |

|     | footprint of the output number. Sign logic is shown in purple,     |    |

|     | exponent addition logic is shown in green, significand             |    |

|     | multiplication is shown in pink, and normalization and             |    |

|     | rounding logic is shown in blue                                    | 55 |

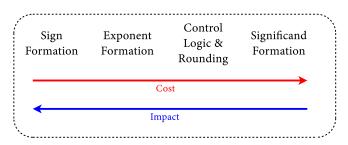

| 5.3 | A depiction of the relative hardware cost of the components in a   |    |

|     | floating-point multiplier and their impact on the final magnitude  |    |

|     | of the result.                                                     | 55 |

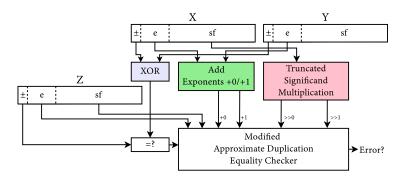

| 5.4 | A block diagram of approximate duplication using a truncated       |    |

|     | significand multiplier. The scheme is general enough to use any    |    |

|     | form of approximation, so long as it always underestimates the     |    |

|     | exact result and has a well-characterized maximum relative         |    |

|     | imprecision.                                                       | 60 |

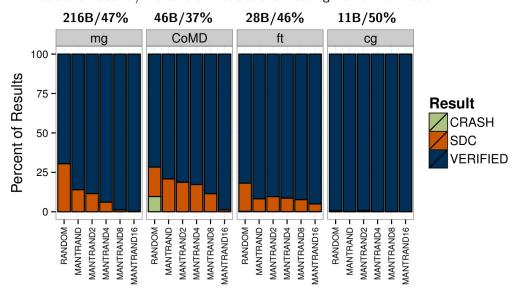

| 5.5 | The results of an application-level error injection campaign for   |    |

|     | floating-point multiplication. Ten thousand undetected errors      |    |

|     | are injected into each of six error detection schemes per program; |    |

|     | each error detection scheme is chosen to be representative of a    |    |

|     | partial duplication or approximate duplication organization. The   |    |

|     | results of every injected error are classified and tabulated based |    |

|     | on their effect on the program output                              | 67 |

| 5.6 | A block diagram of flexible approximate duplication. The           |    |

|     | maximum relative checking error is tunable and can be              |    |

|     | determined at runtime.                                             | 70 |

# 1 INTRODUCTION<sup>\*</sup>

Rising levels of integration and decreasing component reliabilities make error protection increasingly important in computer systems. At the same time, the crucial need for energy efficiency necessitates low-cost reliability techniques. The error protection of arithmetic circuitry is typically more expensive than that of memory or data movement; protection of arithmetic has correspondingly been reserved for critical or high-availability applications. Current trends, however, indicate that error protection of the arithmetic pipeline will be necessary in the future for more diverse application areas.

This dissertation investigates a novel class of arithmetic error detection schemes based on a general technique called *low-cost duplication*. These low-cost duplicate units are able to provide substantive strength and efficiency advantages over existing arithmetic error detection schemes. Section 1.1 describes the four design goals that motivate low-cost duplication. Section 1.2 describes the general error detection techniques that are currently in use; these techniques are unable to satisfy all of the aforementioned design goals. Section 1.3 introduces low-cost duplication; a set of error detection schemes based on low-cost duplication are able to simultaneously satisfy all four design goals, providing complete and efficient reliability for the arithmetic pipeline.

### 1.1 ARITHMETIC ERROR DETECTION DESIGN GOALS

A comprehensive and implementable arithmetic error detection scheme should improve the reliability of the arithmetic pipeline without impacting the design or efficiency of the arithmetic units themselves. Also, the arithmetic error detection circuitry should have low hardware overheads and should readily interface with higher level error recovery systems. More formally, these requirements lead to four design goals for effective arithmetic error detection. This research describes a set of error detection mechanisms that simultaneously satisfy all of these goals.

<sup>\*</sup> Parts of this chapter appear in [1], with Earl E. Swartzlander, Jr. serving as supervisor.

### 1.1.1 Strong, Fault-Agnostic Error Detection

Error detection mechanisms often limit their coverage to restricted classes of faults or errors, such as permanent gate oxide faults [2, 3, 4, 5] or those errors that originate from one gate or cell [6, 7, 8, 9, 10]. There are numerous faults that can affect the datapath of a system, some of which produce error patterns that are not well captured by synthetic models. Due to the uncertainty of fault rates and error manifestation in the arithmetic pipeline it is best for an error detection mechanism to have high error coverage across faults and to not rely on a restrictive error model. A beneficial side effect of this strong error detection is that it simplifies system-level reliability analysis. Without complete error coverage, proper analysis of the system-level effect of undetected errors is complicated and requires intimate knowledge of the expected workloads and arithmetic circuitry.

### 1.1.2 Separable Checking

An error detection mechanism is separable if the checking procedure can operate without any communication from the protected unit. Separability is critical for efficient design development, as it allows error detection to proceed independent of arithmetic. This independence enables the reuse of tested and optimized arithmetic units and also facilitates the modification of arithmetic circuitry without concern for its impact on reliability. Separability also enables the fine-grained gating of error detection, allowing the use of alternate error detection mechanisms where appropriate and avoiding the checking overheads for naturally resilient applications [11, 12, 13].

#### 1.1.3 Low-Latency, Concurrent Detection

Arithmetic error detection mechanisms rely on higher-level recovery mechanisms to halt error propagation and restore proper machine function. Low, fixed latency error detection simplifies the design of this error reporting and handling system. It also allows designers to keep all datapath error reporting synchronous, which is important for efficient common-case error recovery at higher system levels [13, 14, 15].

### 1.1.4 Low Area and Energy Overheads

Faults, by their nature, are typically infrequent and unpredictable. While the expected fault rate for the arithmetic pipeline may be high enough to warrant error detection circuitry, this circuitry should not needlessly waste chip area or energy during error-free operation. The importance of efficient error detection is exacerbated by the current trend towards energy-constrained operation.

#### 1.2 CURRENT SEPARABLE ARITHMETIC ERROR DETECTION APPROACHES

There are two broad techniques that find wide applicability to separable error detection across different arithmetic operations: duplication and residue checking. Duplication and residue checking each have advantages, but neither approach is able to satisfy all of the aforementioned design goals.

### 1.2.1 Duplication, Partial Duplication, and Lazy Duplication

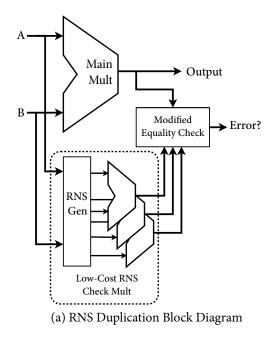

Coarse-grained spatial duplication, also known as dual modular redundancy (DMR), is simple, intuitive, strong, separable, and general, and it may be applied to any arithmetic operation (as shown in Figure 1.1a). The area and power costs of duplication, however, are often prohibitive. Duplication has only been employed in specialized processors where reliability is of paramount importance, surpassing the need for efficiency [16, 17, 18, 19, 20]; even IBM uses alternative arithmetic error detection mechanisms in some of its notoriously reliable mainframe computers for increased efficiency [21, 22, 23]. Also, full duplication can also have incomplete coverage against certain faults. Timing violations, design faults, and fabrication faults can possibly affect both the main arithmetic unit and duplicate check unit, escaping error detection and possibly resulting in silent data corruption or a system failure.

Partial duplication (Figure 1.1b) is an ad-hoc method that only replicates *some* sub-components to reduce the overheads of full duplication. Two prevailing partial duplication strategies seem to exist: (1) focusing on those components (such as control circuitry) where an error tends to have a massive effect on the output [24], or (2) duplicating just enough circuitry to cover a narrow range of errors, such as those that affect a single bit of the output [25]. Because partial

Figure 1.1: Arithmetic error detection through duplication and residue checking. The % component represents residue generation, and the % arithmetic unit (AU) performs residue generation and modular arithmetic.

duplication is applied in an ad-hoc manner, it can potentially have large and unbounded coverage holes.

Lazy duplication decreases the cost of strict duplication by employing a simplified duplicate checker with a long checking latency [26, 27]. While lazy duplication retains the strength and separability of the DMR organization, it suffers from a long detection latency and can potentially introduce hidden data movement and synchronization costs in higher-level error reporting and recovery mechanisms.

### 1.2.2 Residue Checking

Addition and multiplication can be checked by testing the equality of Equation 1.1, where  $|N|_A = N \mod A$  and  $\oplus$  denotes a modular operation [28]. If both sides of Equation 1.1 are equal, it is likely that no error has occurred. If they are not equal, then some error *has* occurred.

$$|a \oplus b|_A \stackrel{!}{=} ||a|_A \oplus |b|_A|_A \tag{1.1}$$

This scheme is called *residue checking*, and it is depicted by Figure 1.1c. In order to simplify operations, residue checking often relies on a restricted class of residues in the form  $A = [2^a - 1; a \in \mathbb{N}]$  [29]. The error coverage of a residue code depends on the width, *a*, of its checking modulus. In general, large checking

moduli are prohibitively expensive. As a result, residue checking has lower error coverage than duplication [12, 30].

# 1.3 A NEW APPROACH: LOW-COST DUPLICATION

Full duplication satisfies most of the design goals from Section 1.1, offering strong, separable, low-latency error detection. However, its high area and energy overheads preclude full duplication from being a realistic error detection scheme for most processors. Also, some faults (such as design bugs or environmental timing faults) may lead to correlated errors in both the main and duplicate arithmetic unit, lessening the fault-agnosticism of traditional DMR organizations [31, 32]. Residue checking offers the ability to lower the hardware and energy overheads of arithmetic error protection, but it does so at the expense of high design-effort or holes in error coverage. Partial duplication maintains the simplicity of duplication at lower costs but it has correspondingly low error coverage, meaning that undetected errors can significantly corrupt program state.

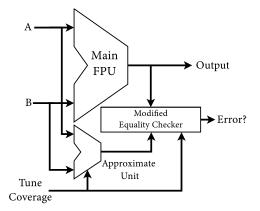

This dissertation investigates novel organizations of dual modular redundancy that provide compelling strength and efficiency advantages over simple duplication. Specifically, this work is based off of the intuition that a *low-cost duplicate checker* may employ a non-standard number system with superior speed and efficiency. Also, because the output of the duplicate unit is discarded after error detection, many of the costs traditionally associated with these non-standard number systems (such as the data movement and storage costs of redundant arithmetic or the imprecision accumulation of approximate arithmetic) have little to no impact. Figure 1.2 shows a block diagram of the low-cost duplication process.

Low-cost duplication differs from lazy duplication (as described above in Section 1.2.1) in two respects. First, lazy duplicate checkers perform arithmetic in the same number representation as the main arithmetic unit, and do not fit the definition of a specialized low-cost duplicate unit considered in this dissertation. Also, unlike lazy duplicate checking, low-cost duplication maintains the low-latency error detection of strict duplication in order to simplify implementation, cheapen higher-level recovery, and avoid a dependence on aggressive latency-tolerant microarchitectural features to lessen performance loss.

Figure 1.2: A block diagram of low-cost duplication. An operation is performed both with the main arithmetic unit and with a low-cost duplicate unit. This low-cost unit converts the inputs into an alternate number system, using redundant arithmetic and application-specific number representations to increase the speed and efficiency of the duplicate operation. Following the completion of the operation, a modified checker tests the equality of the main arithmetic result with the duplicate result in its alternative format.

Low-cost duplicate units can be thought of in two ways. First, low-cost duplication can be considered as a more efficient replacement for DMR in systems demanding high reliability and availability—in fact, its substantive cost savings may even make low-cost duplication a viable approach in systems where DMR is prohibitively costly. Alternatively, low-cost duplication can be thought of as a more optimized baseline for the evaluation of specialized or best-effort error detection mechanisms. Currently, the assumption is often made that concurrent, strong, low-latency duplication requires >100% implementation overheads. This dissertation suggests, however, that with careful design this may not always be the case.

Table 1.1 gives an overview of the low-cost duplication organizations considered in this research. The schemes use operation-appropriate low-cost number systems to check the results of fixed-point addition, fixed-point multiplication, and floating-point multiplication.

# 1.4 THE STRUCTURE OF THIS DISSERTATION

The dissertation proceeds as follows. Chapter 2 reviews the basic concepts related to arithmetic error detection and defines the scope of this research. Chap-

| Arithmetic Operation          | Chapter | Number System                                        |

|-------------------------------|---------|------------------------------------------------------|

| Fixed-Point Addition          | 3       | Carry-Save Arithmetic                                |

| Fixed-Point Multiplication    | 4       | Carry-Save or Residue<br>Number System<br>Arithmetic |

| Floating-Point Multiplication | 5       | Truncated Fractional<br>Arithmetic                   |

Table 1.1: An overview of the low-cost duplication schemes in this dissertation.

ter 3 develops a parameterized family of low-cost duplicate checkers for addition. Chapter 4 investigates an alternative form of low-cost duplication to protect multiplication. Finally, Chapter 5 examines approximate duplication for the low-cost, precision-proportional protection of floating-point multiplication and Chapter 6 describes how low-cost duplication may have broader applicability to other problem domains.

# 2 BACKGROUND CONCEPTS<sup>†</sup>

Before describing the main contribution of this dissertation, some error detection concepts and terminology are reviewed. Section 2.1 introduces some relevant terminology and describes the faults and errors that can affect arithmetic. Sections 2.2–2.5 give further motivation and conceptual background for the design goals (from Section 1.1) of strong, separable, low-latency, and low-cost error detection. Section 2.6 describes the methodology and assumptions used by this research.

# 2.1 FAULTS AND ERRORS IN COMPUTER ARITHMETIC

This research adopts the established terminology that a *fault* is a physical phenomenon or defect that may cause an error or failure, an *error* is a discrepancy between the intended and actual data in a system, and a *failure* is an instance in time when a system displays a behavior that is contrary to its specification [31, 33]. The aim of this dissertation is to use strong and efficient error detection to prevent arithmetic pipeline errors from developing into a system failure. Correspondingly, an error indicates the corruption of data in an arithmetic unit or its pipeline registers and a failure indicates that erroneous results are propagated to subsequent instructions or to memory.

### 2.1.1 Fault Mechanisms

A plethora of faults can cause arithmetic errors; a brief description follows of five of the most frequently studied fault mechanisms. These five faults differ in the way that they tend to manifest and whether they persist—some faults tend to be transient, others are active intermittently (only in certain conditions or for some inputs), and others tend to permanently affect a system until the affected component is removed. The rate of these faults is largely unknown in current technologies and this uncertainty is exacerbated by the unpredictability of future technology challenges and limitations [34, 35, 36, 37, 38].

<sup>†</sup> Parts of this chapter appear in [1], with Earl E. Swartzlander, Jr. serving as supervisor.

#### 2.1.1.1 TRANSIENT FAULTS

**Mechanism:** Transient (or soft) faults are those that corrupt a single computation. Such faults are typically caused by a chain of events following the strike of an energetic particle from the environment. The fundamental mechanism behind a transient fault is as follows: (1) an energetic ion<sup>1</sup> strikes the active region of a transistor, freeing electron-hole pairs as it passes through the device; (2) freed charge collects at the source and drain of the device, generating current; (3) this generated current propagates through the transistor, regardless of its state; (4) a fault occurs if the current passing through an off-state transistor is sufficient to overcome its load capacitance and erroneously switch devices connected to its output [41].

**Properties and Error Activation:** Transient faults are rare and unpredictable and can occur any time during system operation. The manifestation of a transient fault is an erroneous current or voltage spike at the output of one or more neighboring transistors [42, 43, 44]. A particle-induced spike may or may not cause an error, and there are different effects that can prevent a transient fault in a pipeline register or logic from becoming microarchitecturally visible [34, 41, 45, 46]. The rate and duration of transient faults is highly variable and it depends on situational factors (altitude, latitude), environmental factors (temperature, position in the solar cycle), supply voltage, and the specifics of fabrication technology [47, 48, 49, 50, 51, 52, 53].

#### 2.1.1.2 PERMANENT FAULTS

**Mechanism:** There are a variety of mechanisms that can cause a device to become permanently faulty. Extrinsic gate oxide breakdown can occur during the infancy of a weak chip [54, 55], and end-of-life faults may develop over time due to electromigration [56], hot carrier degradation [57], or other time-dependent breakdown mechanisms [36, 58].

<sup>&</sup>lt;sup>1</sup> Such an energetic ion can be produced by multiple events. Two likely candidates are alpha particles that are produced directly by the decay of solder material and package impurities [39] or secondary ionized particles that follow the nuclear spallation of an environmental neutron passing through the processor substrate [40].

**Properties and Error Activation:** The manifestation of a permanent fault is generally the same as an erroneous open or short-circuited wire. Once permanent faults manifest, their effects tend to persist. Permanent faults generally occur either during the infancy of a chip or after years of continuous operation, leading to the so-called *bathtub curve* for fault rates over time [54].

### 2.1.1.3 DESIGN FAULTS

**Mechanism:** Despite aggressive pre-silicon testing, design faults can make their way into a computer system. The most famous arithmetic design fault is probably the Intel Pentium FDIV bug [59], where a lookup table flaw in floating-point division caused an incorrect result for certain inputs. Because of the design flaw, Intel was responsible for replacing faulty processors to astute customers at a reported cost of \$475 million USD (approximately \$693.5 million USD in today's currency) [60, 61].

**Properties and Error Activation:** It is likely that any straightforward design fault will be caught during testing. Therefore, uncaught design faults are likely to manifest as errors intermittently for specific inputs. So long as these problematic inputs persist, the design error will manifest. Unlike permanent or fabrication faults, design bugs are completely intrinsic and affect every fabricated chip—in a large system, every node is affected. Also, the manifistation of a design fault is not confined to a single device or wire, and its effect on the output of a component is not well characterized.

#### 2.1.1.4 ENVIRONMENTAL TIMING FAULTS

**Mechanism:** Environmental timing faults can result when insufficient timing and voltage margins are provided for the operating conditions of a chip. This can occur due to voltage droop [62, 63] age and temperature-related slowdown [37, 64, 65], and on-chip variability [32, 65]. As an example, floating-point design errors have caused a recall of AMD Opteron chips due to a heat density issue where demanding workloads cause timing faults [66].

**Properties and Error Activation:** Similar to design faults, environmental timing faults are typically intermittent and will persist so long as the operating conditions or supply voltages are outside of the safe range. The manifestation of a timing fault depends on the detailed timing information of a circuit; variability in devices, the environment, and voltage add uncertanty to the characterization of such faults [32, 63, 65].

#### 2.1.1.5 FABRICATION FAULTS

**Mechanism:** Deep sub-micron technologies suffer from some fabricationrelated fault mechanisms that can lead to manufacturing defects. For instance, step coverage problems during the metalization process can lead to faulty open circuits in a fabricated design [38]. Complete testing of fabrication faults is expensive, and corresponding post-synthesis testing coverage targets of less than 100% fail to catch all faults [67].

**Properties and Error Activation:** Fabrication faults will typically manifest as short-circuited or open-circuited bridging defects. Their effects will persist throughout the lifetime of an affected chip.

### 2.1.2 Error Models

An arithmetic error occurs when a fault propagates through logic and pipeline state to produce an incorrect result. The direct observation or simulation of faults is difficult and time-consuming and it is highly design and technology-dependent. As such, many error detection mechanisms employ synthetic error models for analysis. Some of the most common and important error models are described below.

#### 2.1.2.1 BITS AND BURSTS

A common error model for memory is to consider a single erroneous bit or a contiguous burst of bits in error. While some studies of application error propagation attempt to use single-bit-flip errors for arithmetic [68, 69, 70], none of the faults from Section 2.1.1 are constrained to produce single-bit errors. Such studies may therefore underestimate the severity of arithmetic errors and correspondingly overestimate the potential for weak error protection techniques to mitigate system failures.

#### 2.1.2.2 ARITHMETIC WEIGHT

The severity of an arithmetic error is sometimes expressed in terms its *arithmetic weight*. This can be thought of as the Hamming weight of the non-adjacent normal form of the distance between the intended and corrupted output value [71, 72]. While the concept of arithmetic weight is important to the theory of arithmetic error detecting (and correcting) codes, it is not especially suited for use as a synthetic error model as faults do not typically manifest in a way that constrained to certain arithmetic weights.<sup>2</sup>

#### 2.1.2.3 SINGLE DEVICE ERRORS

A common error model is to assume a single faulty gate, cell, or node in the arithmetic unit or checker. This model is referred to as a single device (SD) error,<sup>3</sup> and the erroneous output can propagate from the faulty node to affect one or more connected devices in the component. The SD error model captures the effects of most transient, permanent, or fabrication faults, as it is unlikely that such faults affect many simultaneous devices.

#### 2.1.2.4 SINGLE COMPONENT ERRORS

A more general approach than the SD error model is to assume an arbitrary error in any single component. This model, the single component (SC) error model, can capture multiple faults within the arithmetic unit or checker. An example of such a severe fault is a powerful transient error that affects a burst of pipeline latches [43, 73, 74] or neighboring logic cells [44, 75]. Design faults and environmental timing violations can produce arbitrary errors in an arithmetic unit, and as such they may be encompassed by the SC error model so long as it is known that the fault will only affect a single system component. Section 2.2.1

<sup>2</sup> Careful arithmetic unit design can constrain the arithmetic weight of errors [10]. Certain co-dependant checkers (as defined later in Section 2.3.1.3) can therefore use arithmetic weight as an effective error model, but this is not true for more separable error detection schemes.

<sup>3</sup> In the case of transient faults, this model is often referred to as a single event upset [41]. Confusingly, due to its ability to affect an entire connected component, this error model is also called a *multiple error* [22] or a *single distributed fault* [29].

that a duplicate checker can provide complete coverage against the SC error model.

# 2.2 BACKGROUND FOR GOAL #1: STRONG AND FAULT-AGNOSTIC ERROR DETECTION

The typical approach to arithmetic error detection is either to attempt a best-effort mechanism with incomplete error coverage, such as residue checking [12, 28, 29, 30, 76, 77], or to try and select the most prevalent faults or errors and to deal with them with specialized mechanisms. Examples of such specialized mechanisms include detectors for transient faults [78, 79], gate oxide faults [2, 3, 4, 5], timing violations [80, 81], fabrication-related faults [82], and design faults [26]. Alternatively, an error detector can focus on a narrow error model, such as the single-device errors [6, 7, 8, 9, 10]; depending on the protected circuit, such an error model may capture the effects of some faults (such as single-event-transient faults, gate oxide faults, and some fabrication-related faults) but may miss others (single-event-multiple-transient faults, timing, violations, and design faults).

While specialized error detection mechanisms boast low area and energy overheads, their use in a comprehensive arithmetic error detection scheme is fraught with difficulty. Choosing the most prevalent fault mode can be costly and difficult, especially given the uncertainty of future technologies, use-cases, environmental conditions and design constraints. Also, whether and how a fault manifests as an error is strongly design dependent. This design dependence introduces additional development complexity—error detection mechanisms that protect against a narrow error model must often dictate or react to the arithmetic unit design to have high coverage, and there can be a tradeoff between arithmetic unit optimization and error coverage [6, 10, 83, 84].

In lieu of using such detection mechanisms, this work proposes the use of low-cost duplication for holistic, fault-agnostic arithmetic error detection. The high error coverage of low-cost duplication avoids the need to tailor error detection towards the most severe and prevalent errors, lessening the onus of fault rate analysis, error modeling, and system-level error propagation and failure modeling on the chip designer.

### 2.2.1 Ensuring that the Duplicate Checker is Fault-Agnostic

Strict duplication achieves complete single component error coverage, which can be considered a relatively strong level of protection. The SC error model, however, is generally not applicable to correlated faults that can simultaneously affect both the arithmetic unit and checker. In the case of strict duplication, such potentially-correlated faults include design faults and environmental timing violations, both of which can affect both the main and duplicate arithmetic unit.

There are well-known and well-established methods of ensuring that correlated design and environmental timing faults do not simultaneously affect the arithmetic unit and checker. Design faults can be correctly diagnosed by ensuring design diversity between the main arithmetic unit and checker; this approach has been recognized since the beginnings of mechanical computation [26, 31, 85, 86]. Timing violations can be correctly diagnosed by manipulating designs or supply voltages to keep all checking circuitry well off of the circuit's critical path [2].

Ensuring design diversity and keeping the duplicate checker off of the critical path has an added cost for duplication. Since the most efficient main arithmetic unit is normally employed, diversified duplication implies some inefficiency [86]. Also, keeping the duplicate checker off of the critical path requires some additional checking latency. In contrast, low-cost duplication makes use of redundancy and alternate number representations in the checker and is naturally diversified by construction. Thorough these alternate number systems, low-cost duplication can be more efficient than the main arithmetic unit despite this diversification. Also, by avoiding lengthy carry-propagation, low-cost duplication is able to operate faster than the main arithmetic unit and can be non-critical without additional checking latency.

### 2.3 BACKGROUND FOR GOAL #2: SEPARABLE CHECKING

Systematicity and separability are important classifying properties of error detecting mechanisms. A mechanism is *systematic* if its data bits and check bits are distinct and the data can be extracted from the codeword without first passing through a decoder. A code is *separable* if checking can proceed without any communication from the checked unit. By construction, all separable codes must be

Figure 2.1: The separability classification of arithmetic error detecting codes and the design of different error checkers.

systematic. A simple high-level illustration of non-systematic, systematic (but inseparable) and separable checkers is shown in Figure 2.1.

It is highly desirable for an error detection scheme to be separable for several reasons. First and foremost, separable checkers make for modular designs, as shown by Figure 2.1c, and allow chip designers to implement arithmetic units and checkers independently. This modularity lessens the design burden of reliable execution. Also, separable designs can operate completely off of the critical path (during error-free execution) and allow pre-existing and highly optimized arithmetic units to be used without introducing new design constraints and unwanted timing effects. For these reasons, this research focuses exclusively on separable error detection mechanisms.

The full meaning of the term *separability* is not always clear from prior research, and there exists a gradient in the degree of separability provided by error detection mechanisms. To be clear and precise, this research uses a complete taxonomy of separable error detection checkers that is presented below.

# 2.3.1 A Taxonomy of Separable Error Detectors

The definition of separability is normally limited to the physical communication required by a checker, as described above. This leaves potential for separable designs to require intimate knowledge of the main arithmetic unit, or even to constrain the main unit design in order to satisfy an error model. Such design interaction greatly reduces the modularity advantages of separability, complicating the design of a reliable arithmetic pipeline. To eliminate this grey area in classification and to be more explicit about the modularity of competing designs, this research uses a more complete separability classification that is

Figure 2.2: A taxonomy of separability. Designs are arranged in order of increasing separability going from the upper right to the bottom left.

shown in Figure 2.2. This classification separates physically separable designs into four classes that vary in their design modularity and independence. When combined with non-systematic and inseparable checkers, the full classification ends up with six classes; each of these classes is briefly described below.

### 2.3.1.1 NON-SYSTEMATIC CHECKERS

A non-systematic checker uses a single encoding for both the data and redundant check information such that the data bits are not preserved. Such checkers either demand the system-wide adoption of this specialized encoding or require that the data be encoded and decoded before entering the protected arithmetic pipeline. The most studied example of non-systematic checkers are the AN codes, a non-systematic representation of residue coding [71, 72].

#### 2.3.1.2 INSEPARABLE CHECKERS

A systematic-but-inseparable checker separates the information and check bits, but uses both as inputs to a single unit to generate an arithmetic result and error indicator. An example of such a checker is optimized parity prediction, where the parity prediction circuitry and main arithmetic unit are carefully co-designed to allow sharing of circuitry between the two without compromising the single device error coverage of the error detection scheme [7, 8, 9].

#### 2.3.1.3 DESIGN CO-DEPENDENT CHECKERS

If a separable checker relies on the main arithmetic unit to be designed or synthesized in a certain fashion in order to provide coverage guarantees, it is referred to as a design co-dependent separable checker. An example of a design co-dependent separable checker is parity prediction where the main arithmetic unit is synthesized in such a way that any SD error will result in a unidirectional (and therefore detectable) error [6].

#### 2.3.1.4 DESIGN-REACTIVE CHECKERS

Design-reactive separable checkers are designed in response to a specific arithmetic unit. While such checkers do not dictate the arithmetic unit design itself, they require intimate knowledge of the arithmetic unit in order to provide coverage guarantees. Also, appropriate design-reactive separable checkers may be unknown for some main arithmetic unit designs. An example of a designreactive separable checker is the auto-creation of residue checking circuitry to provide complete SD error coverage for simple multipliers [10].

#### 2.3.1.5 TIMING-REACTIVE CHECKERS

Timing-reactive separable checkers treat the main arithmetic unit is a black box, and do not require intimate knowledge of the arithmetic unit design. Such checkers, however, reactively utilize detailed timing information from the main unit to overlap some computation with error detection and increase efficiency. This research develops some timing-reactive error detection organizations, and garners modest efficiency gains using detailed timing information from the main unit [87].

#### 2.3.1.6 FULLY SEPARABLE CHECKERS

Finally, fully separable checkers require no knowledge of the main arithmetic unit apart from its output interface and the arithmetic operation it supports. No checking is overlapped with computation. In addition to timing-reactive designs, this research develops fully separable checkers. There is a tradeoff between the timing-reactive and fully separable checkers, with full separability providing superior design modularity at some associated cost.

# 2.4 BACKGROUND FOR GOAL #3: LOW-LATENCY, CONCURRENT ERROR DETECTION

Low-latency, concurrent error detection simplifies the higher level replay and state restoration mechanisms that are necessary for arithmetic error correction. Long-latency error reporting can require higher level mechanisms to stall in order to guarantee that errors do not propagate outside of a correctable region [15]. Alternatively, higher level mechanisms may need to handle long-latency detected errors with more expensive recovery mechanisms, such as transactional rewind for data rematerialization or the use of a distant global checkpoint, impacting system efficiency [13, 88].

### 2.5 BACKGROUND FOR GOAL #4: LOW AREA AND ENERGY OVERHEADS

Arithmetic errors tend to be rare, unpredictable events, and due to the complexity of logic they can be difficult and costly to detect. Therefore, the high and fixed overheads of conventional strong error detection are generally wasted during fault-free operation. Meanwhile, general-purpose computers continue to be applied to a more diverse range of applications, including those with high reliability demands [89]. This motivates the development of low-cost error detection techniques such as those considered in this dissertation.

Lower error detection overhead often comes at the expense of separability, strength, or detection latency. Many existing mechanisms attempt to lower the overheads of error detection by violating separability, by restricting error coverage to a narrow set of fault or error models, or by asynchronously reporting detected errors with a long and unpredictable latency. In contrast, the goal of this research is to lower the area and energy costs of duplication without sacrificing greatly in these areas—this dissertation shows that careful design can reduce the overheads of duplication without losing its strength and implementation benefits.

# 2.6 THE METHODOLOGY OF THIS RESEARCH

This research focuses on timing-reactive and fully separable checkers that can provide complete detection of single-component errors. Such error detection mechanisms are able to satisfy all of the design goals listed in Section 1.1.

#### 2.6.1 Hardware Synthesis and Analysis

Unless otherwise noted, gate-level design space exploration is used to examine the area and energy required for hardware components. The Synopsys toolchain is used for synthesis, targeting the 40nm TSMC standard cell library [90, 91]. All circuits are compiled using the Synopsys Design Compiler with high mapping effort and optimization options consistent with an area-optimized implementation. Structural Verilog descriptions of each circuit are used throughout, with compressor-based multipliers and minimum-depth parallel prefix adders. The Synopsys Design Compiler provides area (in  $\mu$ m<sup>2</sup>) and power (in  $\mu$ W) estimates for each design. Dynamic power is estimated at the gate level using random test vectors.A TSMC wire model is used for timing estimates, and it is assumed that each circuit is driven by, and drives, a pipeline register. Wherever energy estimates are given, it is assumed that the protected arithmetic unit determines the clock frequency of its parent chip; energy consumption is derived accordingly using the timing and power estimates. Dual-rail encoded equality checkers are used at the output of error detection to create totally self-checking designs.

### 2.6.2 Encoding of Input Operands and End-to-End Protection

This research focuses on arithmetic error detection in a generative context, where operands arrive to the arithmetic unit in an unencoded format (or using a non-arithmetic, systematic ECC code). An alternative organization is to protect an operation in an end-to-end fashion, where local memory and data movement are protected by the same error code as the operation [76, 92, 93, 94]. An example of a cohesive end-to-end protection scheme is the STAR computer, an experimental processor that uses residue checking to protect memory, data movement, and arithmetic [76].

An end-to-end strategy is not considered in this study, as it pushes complexity to the memory and data movement subsystems (the costs of which often surpass that of arithmetic in control-intensive architectures). Also, operations that do not preserve the error code suffer an increase in complexity under end-to-end arithmetic error detection. This diffusion of implementation costs makes the evaluation of end-to-end schemes difficult without fixed knowledge of the microarchitecture in which a protected arithmetic unit operates. It is assumed that the low-cost duplicate checkers from this research will be incorporated with other protection mechanisms for data storage and movement to form an end-to-end protection scheme (similar to most existing solutions [16, 17, 18, 19, 20, 21, 22, 23, 77]).

# 2.6.3 Arithmetic Error Correction

There has been a wealth of work that focuses on the correction of arithmetic errors [71, 95, 96, 97, 98, 99]. Such efforts either violate separability [98, 99], add costly hardware and correction latency [71, 96], or their correction capabilities are limited to simple, synthetic errors [95].

Furthermore, unlike memory errors (where an uncorrected error can result in data loss) arithmetic errors can typically be corrected by replaying the erroneous instruction.<sup>4</sup> Such replay is especially effective for low-latency error detectors, since microarchitectural replay mechanisms can handle an error before it is allowed to overwrite any of the input data [15]. For these reasons, this research focuses solely on arithmetic error detection, leaving the role of error correction to higher system levels.

<sup>4</sup> In the case of a permanently faulty arithmetic unit, correction-through-replay may have to occur on a different, fault-free arithmetic unit or using a different set of instructions. Higher-level recovery mechanisms exist to deal with such situations [22].

# 3 LOW-COST DUPLICATION FOR FIXED-POINT ADDITION <sup>‡</sup>

Adders are fundamentally important to computer systems and their protection against errors is correspondingly imperative in high availability and missioncritical systems. Addition is utilized for different purposes including data manipulation, memory addressing, and control flow—this means that an error in addition can manifest in many ways, ranging from silent data corruption to catastrophic system failure. The wide range of maladies that can result from an adder error potentially makes the strong protection of addition desirable across many problem domains, including scientific computing and system software.

This chapter describes a low-cost duplicate organization for adders based on the redundant carry-save number representation. Section 3.1 describes carrysave addition and presents a modified equality checker with a carry-save input. Section 3.2 describes and evaluates a fully-separable carry-save duplication scheme for fast adders and Section 3.3 extends it to form a timing-reactive separable checker for any speed of adder.<sup>5</sup>

# 3.1 THE CARRY-SAVE NUMBER SYSTEM AND A MODIFIED CHECKER

Addition using a non-redundant positional number system (such as two's complement) requires a lengthy carry propagation for addition; even the fastest possible adders require a logarithmic number of stages to perform this carry propagation [101, 102]. There are redundant number representations, however, where addition can be performed with superior efficiency in constant time. The following subsections describe constant-time addition using the *carry-save* number system<sup>6</sup> [101, 102] and present a modified equality checker that evaluates the equality of a positional number with a carry-save input.

Parts of this chapter appear in [87, 100], with Earl E. Swartzlander, Jr. serving as supervisor.

<sup>5</sup> Refer back to Section 2.3.1 for the distinction between a fully separable and a timing-reactive checker.

<sup>6</sup> Carry-save numbers are sometimes also referred to as *stored-carry* numbers [101].

#### 3.1.1 Carry-Save Addition

Binary carry save addition performs arithmetic with the redundant digit set  $d \in \{0, 1, 2, 3\}$  [102]. Intuitively, carry-save addition saves the intermediary carry signals during addition instead of adding them to more significant bit positions. This results in the need for 2*N* bits to represent an *N*-bit dynamic range, but it allows addition to proceed quickly and efficiently in a carry-free fashion.<sup>7</sup>

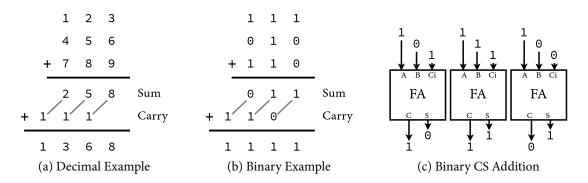

Figure 3.1 illustrates carry-save addition through an example. Figure 3.1a demonstrates the multi-operand addition of three decimal numbers. Each positional column of digits is independently added, with the result being a sum digit and one carry digit to be added to the next most significant position. Full non-redundant multi-operand addition performs this carry propagation and addition, adding the labeled intermediary result called the sum to the carry. Carry-save addition keeps the number in this intermediary representation as both a sum and a carry, meaning that conversion back to a non-redundant form entails the addition of the two terms and 2*N* bits are required to represent an *N*-bit result. It can be seen, however, that the carry-save addition of each positional digit proceeds independently, leading to constant-time addition that does not depend on the input operand width.

Figure 3.1b shows another illustrative example of carry-save arithmetic using a binary representation, and Figure 3.1c gives its hardware implementation. It can be seen that *N*-bit three-operand binary addition can be performed using *N* full adders following a (constant) single full-adder delay.

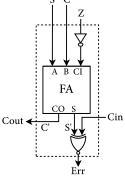

# 3.1.2 The Carry-Save Equality Checker

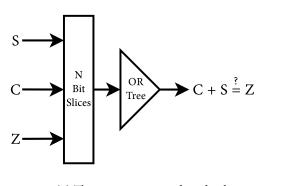

Given a carry-save input represented by a sum and carry term, {*S*, *C*} and a weighted positional fixed-point input, *Z*, the equality of  $S+C \stackrel{?}{=} Z$  can be evaluated by detecting whether  $S+C-Z \stackrel{?}{=} 0$  through cancellation. This cancellation can be detected without carry-propagation by reducing the three-input addition S+C+(-Z) down to a carry-save intermediary term {*S'*, *C'*} and detecting whether *S'* and *C'* complement each other. Such a modified equality checker with one carry-save and one weighted input is shown in Figure 3.2. While this work (published

<sup>7</sup> Carry-save addition is carry-free *between* digits. A limited amount of carry propagation is needed to form each digit.

Figure 3.1: An example depicting decimal and binary three-operand addition. Carry-save arithmetic uses the intermediary sum and carry results directly and can perform binary arithmetic within a constant full-adder delay.

(a) The carry-save equality checker

(b) A checker bit slice

Figure 3.2: A depiction of the carry-save equality checker. Cancellation is detected between the carry-save and positional inputs through a bit-sliced, constant-delay structure. Any non-complementary bits are detected through an OR reduction tree.

in [100]) is the first to use this modified equality checker for arithmetic error detection, a similar equality comparison has been employed elsewhere [102, 103, 104] for carry-save arithmetic.

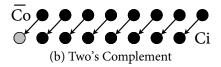

# 3.1.3 Carry-Save Equality for One's/Two's Complement Numbers

The carry-save equality checker is easily adapted to work for either one's or two's complement numbers. One's complement arithmetic involves an endaround-carry signal in the main adder. Correspondingly, the one's complement equality checker carries around the carry of the final bit-slice, as shown by the

Figure 3.3: The Dadda dot diagram [105] of the bits and carry dependencies in the one's and two's complement checkers. Dots represent bits of data, and directional arrows indicate a carry-dependence between bits. Therefore, the top and bottom row of dots respectively represent the sum and carry bits output from the full adders in the carry-save equality checker. An 8-bit checker is shown; no carry-dependence exists between digits due to the carry-save representation. The carry-out of the final bit-slice differs between the one's complement and two's complement equality checker; it is accordingly highlighted in grey.

Dadda dot diagram [105] in Figure 3.3a. For two's complement arithmetic, the final check slice carry-out is checked against the complemented carry-out of the main adder and the main adder carry-in is propagated into the first checking stage, as depicted in Figure 3.3b. While two's complement checking requires an additional stage, the first and last check-slice can be significantly simplified such that the complexity and power efficiency of the checker are only marginally affected.

# 3.2 CARRY-SAVE DUPLICATION

Carry-save duplication makes use of the carry-save equality checker<sup>8</sup> to verify addition in constant time with low hardware overheads.<sup>9</sup> Whereas full duplication checks for the equality of Z = Z' (assuming Z is the result following the addition of input operands A and B and Z' is the result of the duplicate adder), carry-save duplication tests for A + B = Z using the carry-save equality checker. The input operands A and B assume the role of the sum and carry terms of the carry-save input to the checker, and no redundant representation is propagated outside of the modified equality check.

<sup>8</sup> Carry-save duplication uses a two-rail encoded equality output (unlike the depiction from Figure 3.2a) in order to be a self-checking design.

<sup>9</sup> Constituent work also calls the carry-save duplicate checker the *long residue checker* [100] for reasons later explained in Section 3.2.1.2.

Figure 3.4: A 1-bit slice of the lazy adder checker [106] and of the carry-save duplicate checker.

## 3.2.1 Relationship to Existing Work

Apart from its obvious relation to full duplication, carry-save duplication has close ties to alternate adder error detection schemes including lazy error detection and residue checking. The nature of the relationship between carry-save duplication and this existing work is investigated below.

## 3.2.1.1 LAZY ERROR DETECTION

Figure 3.4a shows one bit-slice of the lazy error checker<sup>10</sup> proposed by Yilmaz et al. [106]. Each slice checks one output bit using a modified full adder and an XOR gate; the error signal from each bit is ORed together to determine if an error has occurred. The checker has no carry dependence, such that the checker delay (apart from the OR tree) does not directly depend on the word width. Careful inspection shows that the functionality of the carry-save and lazy checkers are essentially equivalent;<sup>11</sup> each is a bit-sliced design, and the two have similar error coverage. Figure 3.4(b) replicates a slice of the carry-save duplicate checker for a side-to-side comparison.

<sup>10</sup> Despite the name similarity, the lazy error checker is unrelated to lazy duplication (described previously in Section 1.2.1).

<sup>11</sup> The carry-save and lazy checker bit-slices have a different carry interface and therefore cannot be mixed.

While the carry-save duplicate checker is functionally similar to the lazy checker, the carry-save scheme has the potential to significantly reduce error detection overheads using standard cell synthesis. An important advantage of carry-save duplication is that it uses a full adder as a fundamental unit. There exist efficient full-adder cells [107] in many standard cell libraries, increasing the efficiency of carry-save duplication without resorting to custom cell design.

To demonstrate the efficiency advantages of the carry-save duplicate organization, this research makes use of the mirror adder cell found in the Nangate 45nm standard cell library [108].<sup>12</sup> Isolated analysis<sup>13</sup> of the checkers in Figure 3.4 shows that a carry-save duplicate bit-slice consumes 10.73% less area and 19.66% less power than its lazy-checker counterpart. The following section evaluates all separable adder protection approaches, and finds that the full carry-save duplicate scheme has efficiency advantages equal to or greater than these initial estimates.

#### 3.2.1.2 RESIDUE CHECKING

Residue checking (described briefly in Section 1.2.2) can be applied to addition. In general, the strength of a residue check is proportional to its checking modulus and its latency is inversely proportional to the modulus, such that the strongest and lowest-latency organization is the residue check whose modulus is as large as the input operand width. Such a strong and fast residue checker is equivalent to full duplication.

The above observation relating residue checking to full duplication provides an insight into the relationship between carry-save duplication and residue checking. Carry-save duplication is equivalent to a limited-carry variant of residue checking, described below, in the case of a maximal checking modulus. **Carry-Save Residue Checking:**

An improved residue checker is presented that uses residue generation circuitry with carry-save outputs along with a carry-save equality checker. The

13 This isolated analysis characterizes and analyzes a single checker bit-slice in the context of its application as an error detection for addition.

<sup>12</sup> Unlike the overall experimental methodology described in Section 2.6, area and power estimates in this section (Section 3.2) utilize the 45nm Nangate Open Cell Library [108]. This is done to be consistent with published work [100]. Section 3.3 and the rest of this dissertation uses the TSMC 40nm library and is consistent with the previously described methodology from Section 2.6.