Copyright

$\mathbf{b}\mathbf{y}$

Milad Olia Hashemi

2016

The Dissertation Committee for Milad Olia Hashemi certifies that this is the approved version of the following dissertation:

# ${\bf On\mbox{-}Chip\ Mechanisms}$ to Reduce Effective Memory Access Latency

| Committee:                 |

|----------------------------|

|                            |

|                            |

|                            |

| Yale N. Patt, Supervisor   |

| Tate IV. I and, Supervisor |

|                            |

|                            |

| Douglas M. Carmean         |

|                            |

|                            |

| Derek Chiou                |

| Derek Ciliou               |

|                            |

|                            |

| Mattan Erez                |

|                            |

|                            |

| D11 C. D11                 |

| Donald S. Fussell          |

# On-Chip Mechanisms to Reduce Effective Memory Access Latency

by

Milad Olia Hashemi, B.S.E.E.; M.S.E.

#### DISSERTATION

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN

August 2016

## Acknowledgements

Only a fraction of the work that has allowed me to write this dissertation is my own. I can't imagine the strength that it must've taken my parents to immigrate to a new and unfamiliar country with no resources and then raise two kids. They always prioritized our education over any of their own needs. I was only able to write this dissertation because of their sacrifice. I thank my parents: Homa and Mohammad, and my sister Misha for their unwavering love.

I would never have pursued a Ph.D. or arrived at UT without my wife, Kelley. Well before I had any idea, she knew that I wouldn't be happy leaving graduate school without a doctorate. I thank her for her advice, clairvoyance, and patience throughout these last seven years.

My time in graduate school has allowed me to meet and work with amazing people who have taught me far more than I could list here. This starts with my advisor, Professor Yale N. Patt. Despite his accomplishments, Professor Patt maintains a contagious passion for both teaching and research. He's taught me how to learn, how to ask questions, how to attack problems, and tried to teach me how to share knowledge with others. I'm still not sure why he agreed to let me join HPS, but it's one of the pivotal moments of my life. It's an honor to be counted as a member of his research group, I thank him for his faith in me.

I've had the incredible opportunity of learning from Doug Carmean for the past five years. Technically, Doug has taught me how to pay attention to details and more importantly, how to listen to everybody and not allow preconceptions to color your opinion of what they're saying. Beyond work, Doug is one of the kindest people that I know and he has impacted my life in more ways than I can count. I thank him for putting up with my constant pestering and being so open with me when he had no reason to be.

I'd like to thank Professor Derek Chiou, Professor Mattan Erez, and Professor Don Fussell for serving on my committee. Professor Erez and Professor Chiou are instrumental to my success at UT. The wealth of knowledge that they've shared with me has given me the foundation to work in computer architecture and motivated me to want to work in this field. The university is lucky to have such amiable and brilliant individuals.

Many of the research directions that I've worked on have come as a result of discussions with Professor Onur Mutlu. Professor Mutlu is an incredibly motivational, hardworking, and intelligent person. I'd like to thank him for teaching me how to never be satisfied with the work that I've done, how to continuously strive for more, and for pushing me to not give up when things didn't go my way. I'd like to thank him and Professor Moinuddin Qureshi for their advice, research discussions, and for always treating me like one of their own family.

I wouldn't have joined HPS without Eiman Ebrahimi. Eiman was the first person to teach me how to do research and how to strive towards writing high-quality papers. I'd like to thank him for his advice and support throughout my time at UT. I'd like to thank Carlos Villavieja for putting up with an obstinate young graduate student and showing him how to grow both as a person and a researcher. I'd also like to thank him for proof-reading this entire dissertation. I'd like to thank the entire HPS research group while I've been at UT, and in particular Khubaib for always being eager to talk about research, José Joao for his guidance and maintaining our computing systems, Rustam Miftakhutdinov for the insane amount of work that he put into our simulation infrastructure, and Faruk Guvenilir for maintaining our computing systems after José and for completing countless miscellaneous tasks without complaint.

Finally, I'd like to thank my friends: Will Diel, Curtis Hickmott, Zack Smith, Trevor Kilgannon, and David Cate for keeping me sane for over a decade now.

Milad Hashemi August 2016, Austin, TX

# On-Chip Mechanisms to Reduce Effective Memory Access Latency

by

Milad Olia Hashemi, Ph.D.

The University of Texas at Austin, 2016

Supervisor: Yale N. Patt

This dissertation develops hardware that automatically reduces the effective latency of accessing memory in both single-core and multi-core systems. To accomplish this, the dissertation shows that all last level cache misses can be separated into two categories: dependent cache misses and independent cache misses. Independent cache misses have all of the source data that is required to generate the address of the memory access available on-chip, while dependent cache misses depend on data that is located off-chip. This dissertation proposes that dependent cache misses are accelerated by migrating the dependence chain that generates the address of the memory access to the memory controller for execution. Independent cache misses are accelerated using a new mode for runahead execution that only executes filtered dependence chains. With these mechanisms, this dissertation demonstrates a 62% increase in performance and a 19% decrease in effective memory access latency for a quad-core processor on a set of high memory intensity workloads.

## Table of Contents

| Ackno   | wledgements                                                                                   | iv  |

|---------|-----------------------------------------------------------------------------------------------|-----|

| Abstra  | act                                                                                           | vi  |

| List of | Tables                                                                                        | x   |

| List of | Figures                                                                                       | xii |

| Chapt   | er 1. Introduction                                                                            | 1   |

| 1.1     | The Problem                                                                                   | 1   |

| 1.2     | Independent vs. Dependent Cache Misses                                                        | 2   |

| 1.3     | Reducing Effective Memory Access Latency                                                      | 4   |

| 1.4     | Thesis Statement                                                                              | 6   |

| 1.5     | Contributions                                                                                 | 6   |

| 1.6     | Dissertation Organization                                                                     | 8   |

| Chapt   | er 2. Related Work                                                                            | 9   |

| 2.1     | Research in Reducing Data Access Latency via Predicting Memory Access Addresses (Prefetching) | 9   |

| 2.2     | Research in Reducing Data Access Latency via Pre-Execution                                    | 10  |

| 2.3     | Research in Reducing Data Access Latency via Computation Near Memory                          | 13  |

| 2.4     | Research in Reducing Data Access Latency via Memory Scheduling $$ .                           | 14  |

| Chapt   | er 3. The Runahead Buffer                                                                     | 15  |

| 3.1     | Introduction                                                                                  | 15  |

| 3.2     | Background                                                                                    | 16  |

| 3.3     | Runahead Observations                                                                         | 17  |

| 3.4     | Mechanism                                                                                     | 20  |

|         | 3.4.1 Hardware Modifications                                                                  | 20  |

|         | 3.4.2 Dependence Chain Generation                                                             | 22  |

|         | 3.4.3 Runahead Buffer Execution                                                               | 25  |

|         | 3.4.4 Dependence Chain Cache                                                                  | 25  |

|        | 3.4.5  | Runahead Buffer Hybrid Policies                 | 26  |

|--------|--------|-------------------------------------------------|-----|

|        | 3.4.6  | Runahead Enhancements                           | 26  |

| 3.5    | Metho  | odology                                         | 28  |

| 3.6    | Resul  | ts                                              | 31  |

|        | 3.6.1  | Performance Results                             | 32  |

|        | 3.6.2  | Sensitivity to Runahead Buffer Parameters       | 38  |

|        | 3.6.3  | Performance with Prefetching                    | 38  |

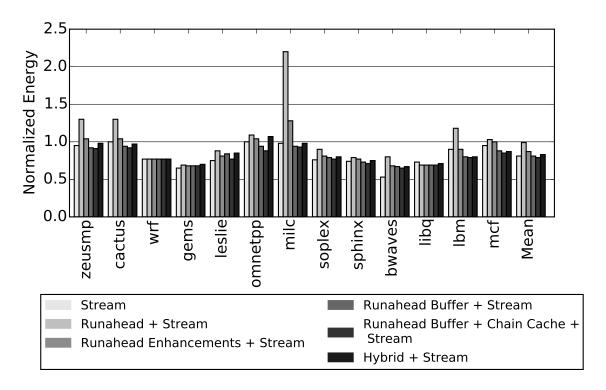

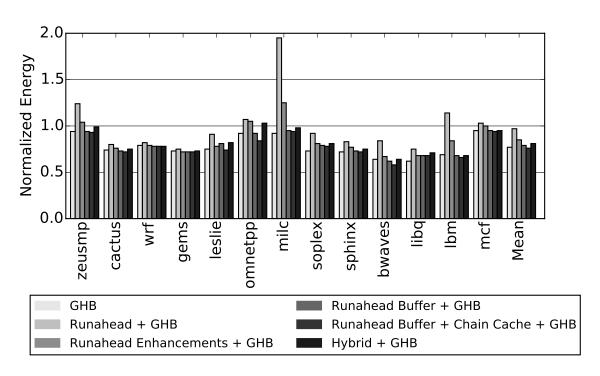

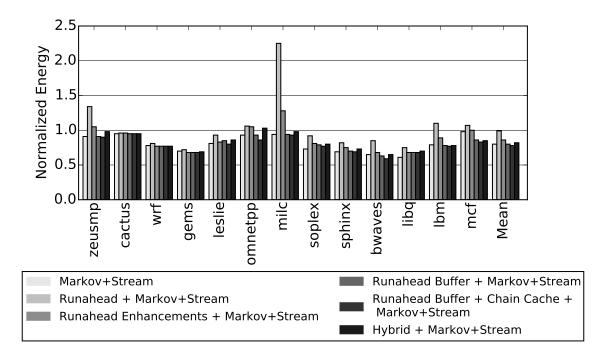

|        | 3.6.4  | Energy Evaluation                               | 41  |

|        | 3.6.5  | Sensitivity to System Parameters                | 45  |

| 3.7    | Concl  | usion                                           | 45  |

| Chapte | er 4.  | The Enhanced Memory Controller                  | 47  |

| 4.1    | Introd | duction                                         | 47  |

| 4.2    | Backg  | ground                                          | 47  |

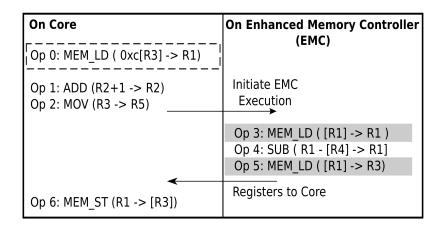

| 4.3    | Mecha  | anism                                           | 50  |

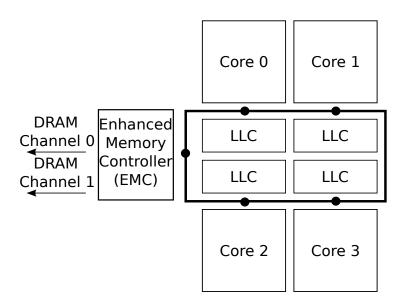

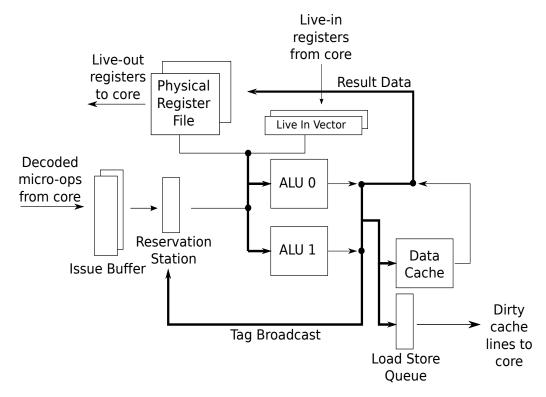

|        | 4.3.1  | EMC Compute Microarchitecture                   | 53  |

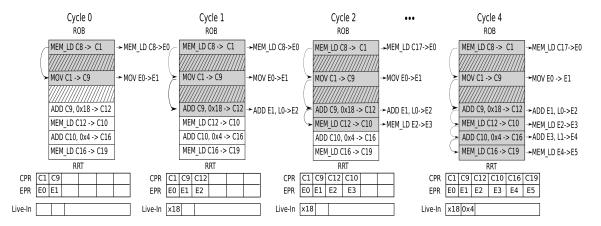

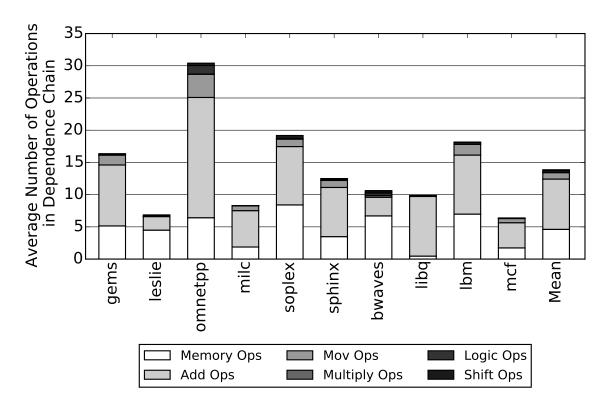

|        | 4.3.2  | Generating Chains of Dependent Micro-Operations | 57  |

|        | 4.3.3  | EMC Execution                                   | 60  |

| 4.4    | Metho  | odology                                         | 62  |

| 4.5    | Resul  | ts                                              | 66  |

|        | 4.5.1  | Performance Analysis                            | 68  |

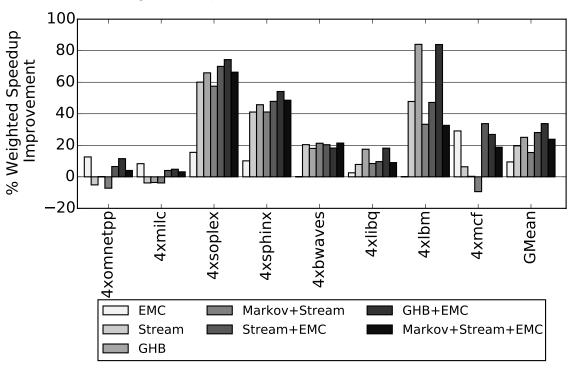

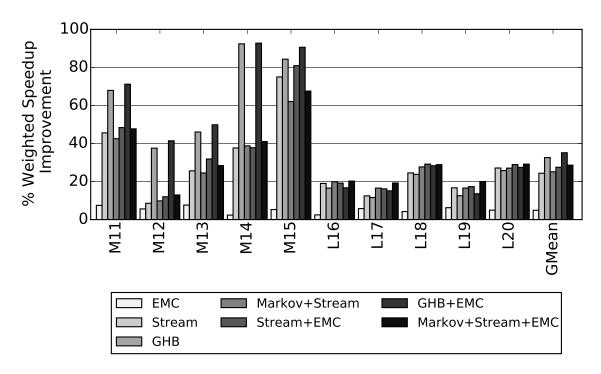

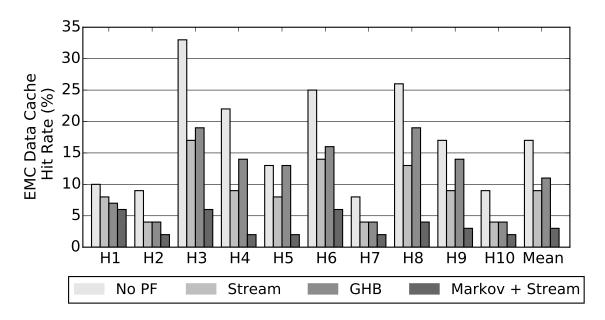

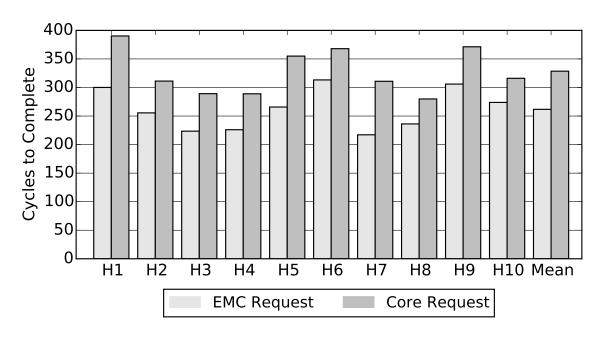

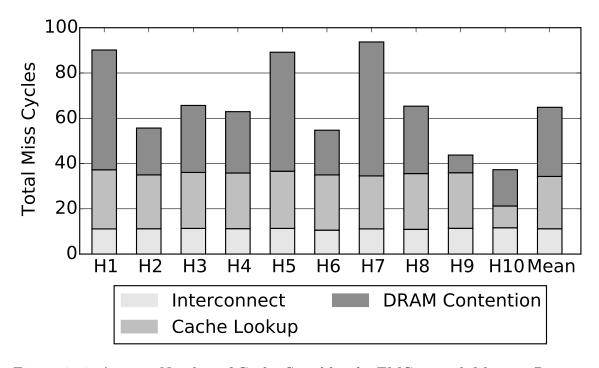

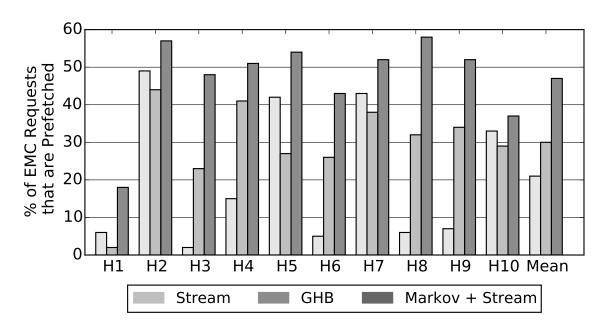

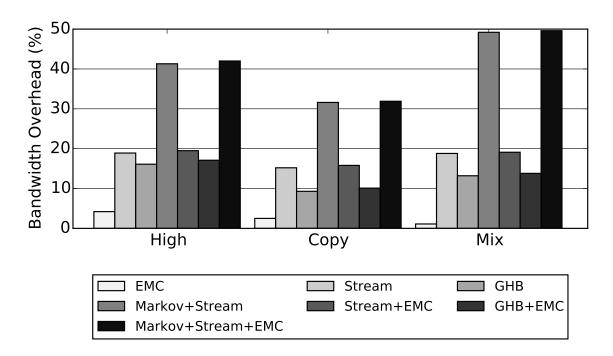

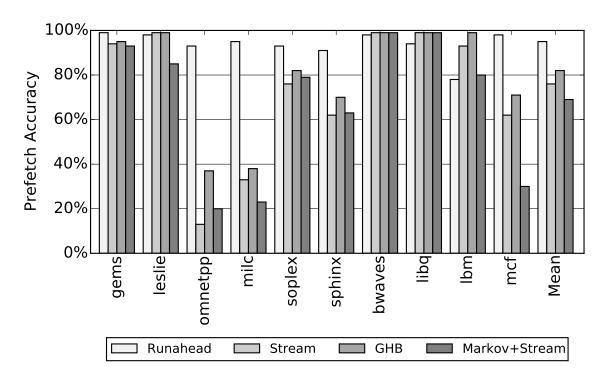

|        | 4.5.2  | Prefetching and the EMC                         | 73  |

|        | 4.5.3  | Sensitivity to EMC Parameters                   | 73  |

|        | 4.5.4  | Single-Core Results                             | 76  |

|        | 4.5.5  | Multiple Memory Controllers                     | 76  |

|        | 4.5.6  | EMC Overhead                                    | 78  |

|        | 4.5.7  | Energy and Area                                 | 79  |

|        | 4.5.8  | Sensitivity to System Parameters                | 82  |

| 4.6    | Concl  | usion                                           | 84  |

| Chapte | er 5.  | Runahead at the Enhanced Memory Controller      | 85  |

| 5.1    | Introd | duction                                         | 85  |

| 5.2    | Mecha  | anism                                           | 89  |

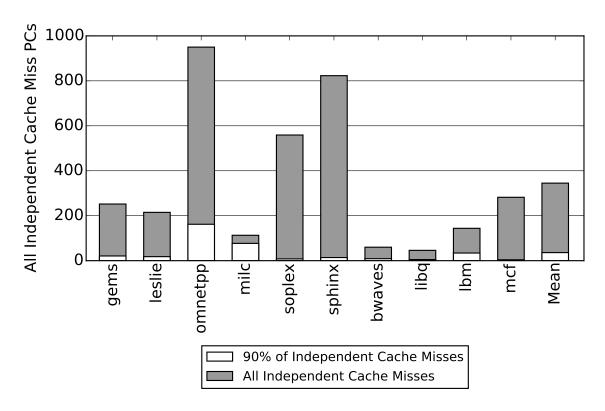

|        | 5.2.1  | Runahead Oracle Policies                        | 89  |

|        | 5.2.2  | Hardware Stall Policy                           | 95  |

|        | 5.2.3  | EMC Runahead Control                            | 101 |

| 5.3    | Metha  | odology                                         | 104 |

| 5.4                                                | Resul  | ts                                                                                  | 104 |

|----------------------------------------------------|--------|-------------------------------------------------------------------------------------|-----|

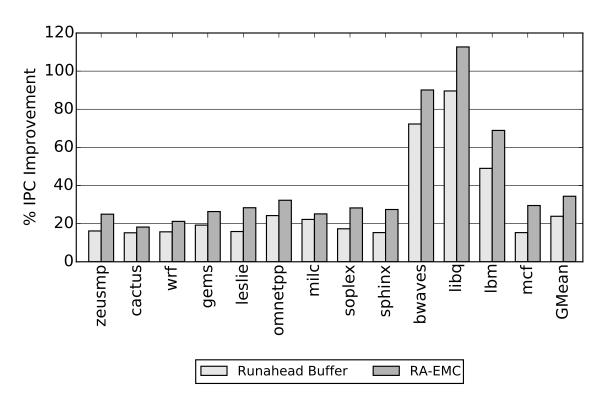

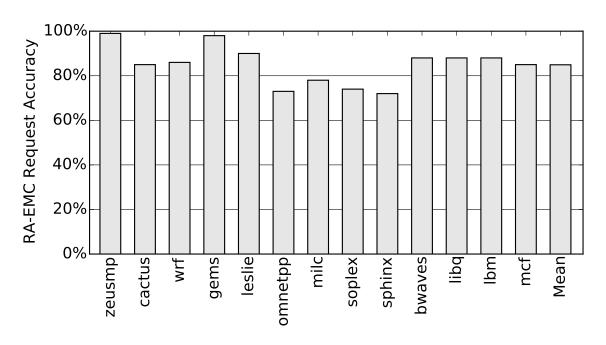

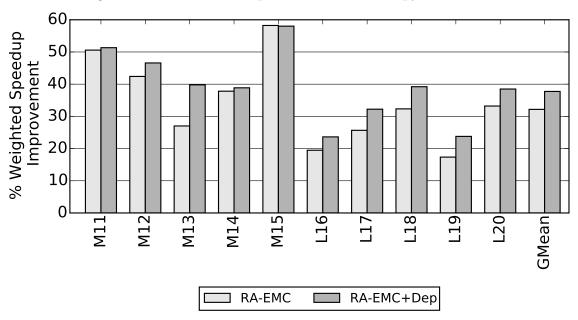

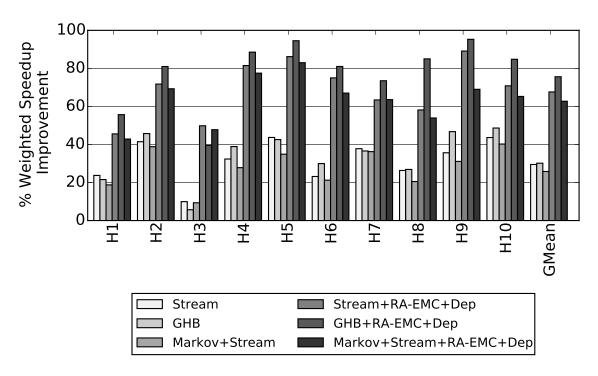

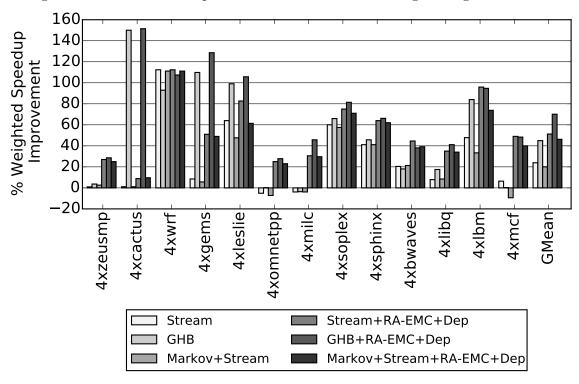

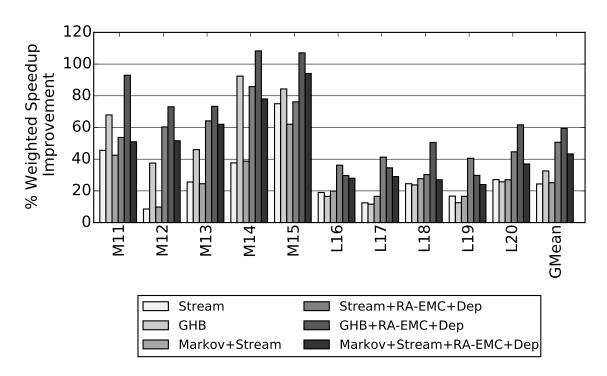

|                                                    | 5.4.1  | Performance Results                                                                 | 104 |

|                                                    | 5.4.2  | RA-EMC Overhead                                                                     | 105 |

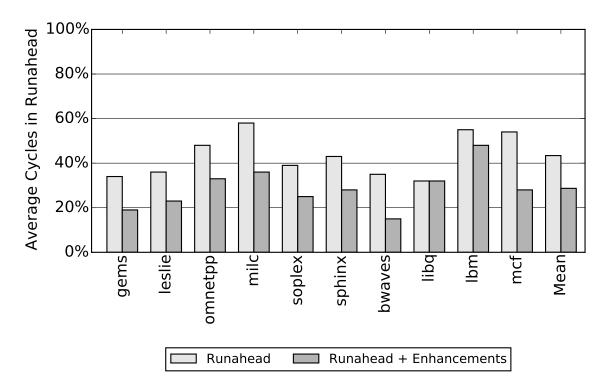

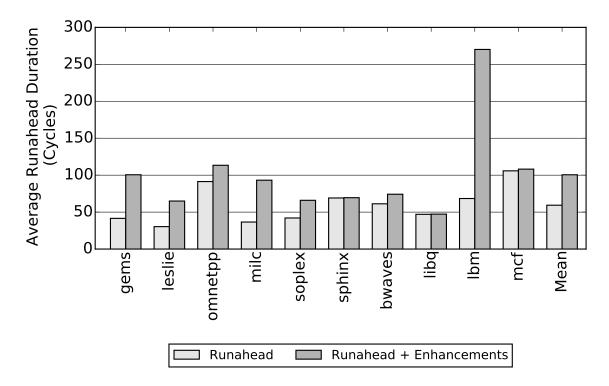

|                                                    | 5.4.3  | $RA\text{-}EMC + Prefetching \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | 107 |

|                                                    | 5.4.4  | Energy Results                                                                      | 109 |

|                                                    | 5.4.5  | Sensitivity To System Parameters                                                    | 112 |

|                                                    | 5.4.6  | Dependent Miss Acceleration                                                         | 113 |

| 5.5                                                | Concl  | usion                                                                               | 114 |

| Chapter 6. Multi-core Enhanced Memory Controller I |        | Multi-core Enhanced Memory Controller Policies                                      | 115 |

| 6.1                                                | Intro  | luction                                                                             | 115 |

| 6.2                                                | Meth   | $\operatorname{odology}$                                                            | 115 |

| 6.3                                                | Multi  | -core RA-EMC Policies                                                               | 117 |

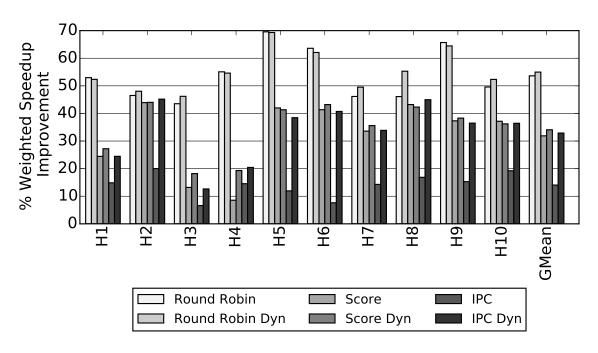

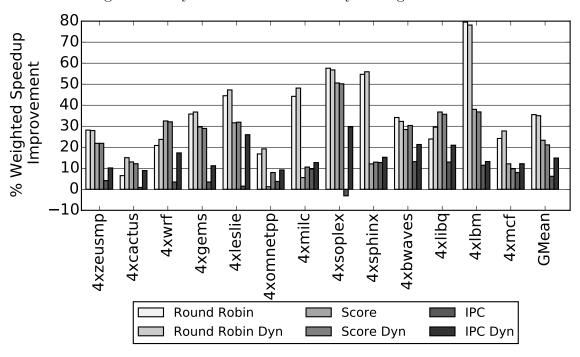

|                                                    | 6.3.1  | Policy Evaluation                                                                   | 117 |

|                                                    | 6.3.2  | Dynamically Adjusting Runahead Distance                                             | 121 |

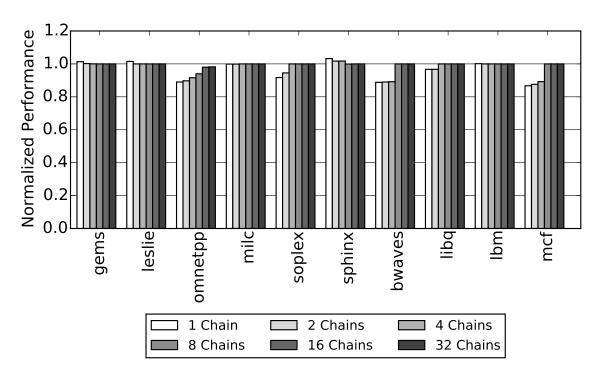

|                                                    | 6.3.3  | Effect of Increasing RA-EMC Contexts                                                | 123 |

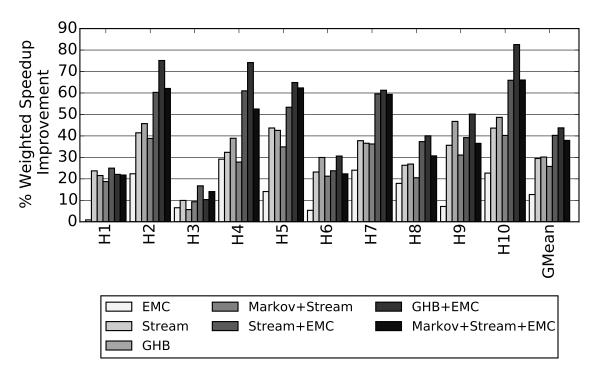

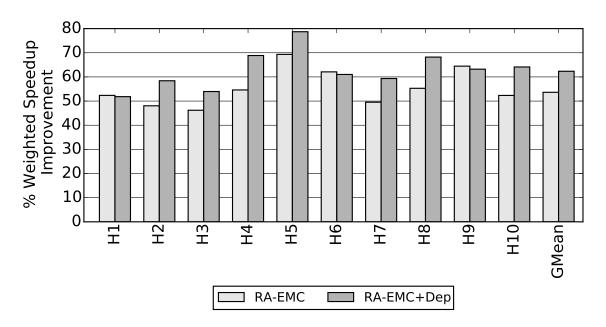

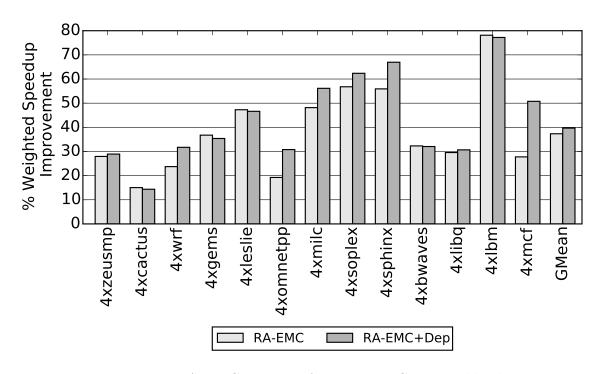

| 6.4                                                | Multi  | -core RA-EMC Evaluation                                                             | 123 |

|                                                    | 6.4.1  | Energy Evaluation                                                                   | 131 |

| 6.5                                                | Sensit | civity to System Parameters                                                         | 133 |

| 6.6                                                | Concl  | usion                                                                               | 135 |

| Chapte                                             | er 7.  | Conclusions and Future Work                                                         | 136 |

| Bibliog                                            | graphy | V                                                                                   | 140 |

## List of Tables

| 3.1  | SPEC06 Classification by Memory Intensity                   | 28  |

|------|-------------------------------------------------------------|-----|

| 3.2  | Simulation Comparison                                       | 30  |

| 3.3  | Runtime Power Consumption (W)                               | 31  |

| 3.4  | DRAM Power Comparison                                       | 31  |

| 3.5  | Average DRAM Bandwidth Consumption (GB/S)                   | 32  |

| 3.6  | Additional Runahead Buffer Hardware Overhead                | 32  |

| 3.7  | System Configuration                                        | 33  |

| 3.8  | Chain Cache Statistics                                      | 36  |

| 3.9  | Performance Sensitivity to Runahead Buffer Parameters       | 38  |

| 3.10 | Runahead Buffer Performance and Energy Sensitivity          | 45  |

| 4.1  | Multi-core System Configuration                             | 63  |

| 4.2  | Multi-Core Workloads                                        | 64  |

| 4.3  | Multi-Core Workload IPC                                     | 65  |

| 4.4  | Multi-Core Workload Memory Bandwidth (GB/S) and Power (W) . | 65  |

| 4.5  | Performance Sensitivity to EMC Parameters                   | 75  |

| 4.6  | EMC Single Core Performance                                 | 76  |

| 4.7  | EMC and Multiple Memory Controllers                         | 77  |

| 4.8  | EMC Dependence Chain Length                                 | 78  |

| 4.9  | EMC Interconnect Overhead                                   | 79  |

| 4.10 | Additional EMC Storage Overhead                             | 83  |

| 4.11 | Additional EMC Area Overhead                                | 84  |

| 4.12 | EMC Performance and Energy Sensitivity                      | 84  |

| 5.1  | Additional RA-EMC Hardware Overhead                         | 101 |

| 5.2  | Runahead Load to Use Distance (Instructions)                | 104 |

| 5.3  | System Configuration                                        | 105 |

| 5.4  | RA-EMC Communication Overhead                               | 107 |

| 5.5  | Effective Memory Access Latency (Cycles)                    | 111 |

| 5.6  | Normalized RA-EMC Static and Dynamic Energy                 | 112 |

| 5.7  | RA-EMC Performance and Energy Sensitivity                   | 113 |

| 6.1  | Multi-Core System Configuration                             | 116 |

| 6.2  | Multi-Core Workloads                                       | 117 |

|------|------------------------------------------------------------|-----|

| 6.3  | SPEC06 Classification by Memory Intensity                  | 117 |

| 6.4  | RA-EMC Accuracy and Runahead Distance (Instructions)       | 120 |

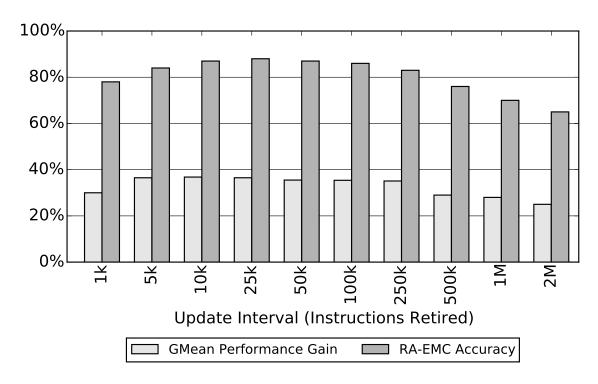

| 6.5  | RA-EMC Accuracy and Interval Length (Retired Instructions) | 121 |

| 6.6  | Dynamic Runahead Accuracy and Distance                     | 123 |

| 6.7  | RA-EMC Context Performance Sensitivity                     | 123 |

| 6.8  | RA-EMC+Dep Statistics                                      | 126 |

| 6.9  | RA-EMC+Dep Effective Memory Access Latency Reduction       | 127 |

| 6.10 | RA-EMC+Dep+GHB Performance with Throttling                 | 131 |

| 6.11 | System On-Chip Overhead                                    | 134 |

| 6.12 | Multi-Core RA-EMC Performance and Energy Sensitivity       | 135 |

## List of Figures

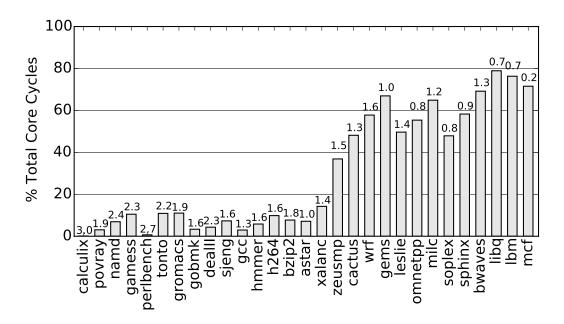

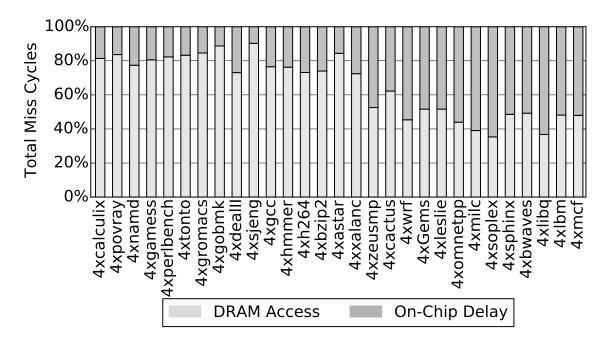

| 1.1  | SPEC CPU2006 Stall Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

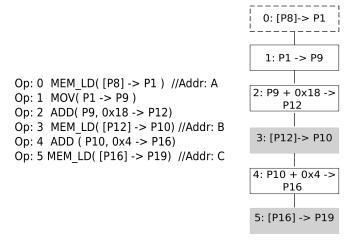

| 1.2  | Dependence Chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3  |

| 1.3  | Fraction of all Cache Misses that are Dependent Cache Misses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5  |

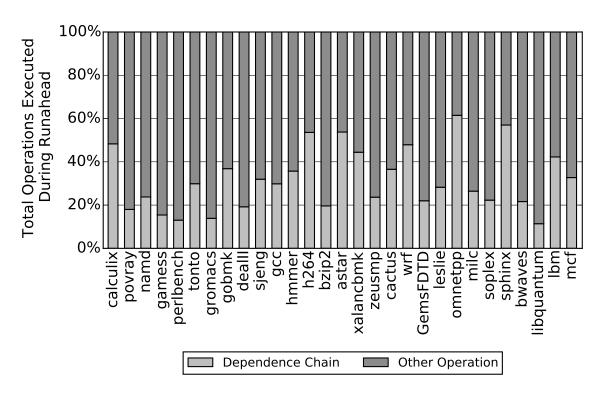

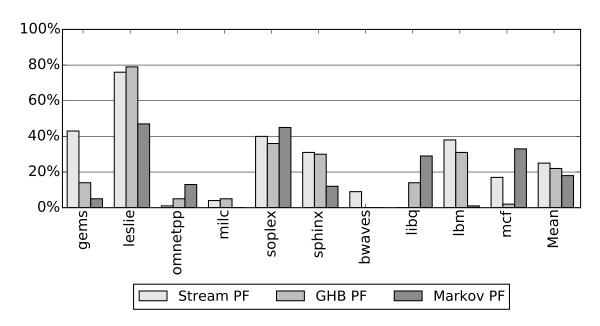

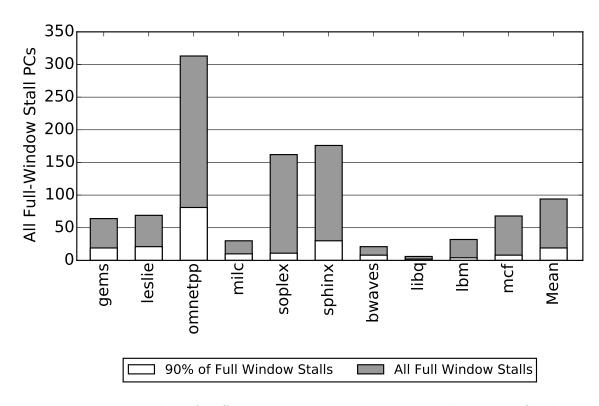

| 3.1  | Breakdown of Operations Executed during Traditional Runahead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18 |

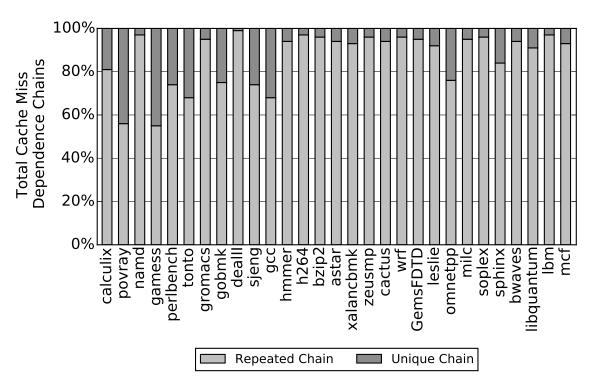

| 3.2  | Unique vs. Repeated Dependence Chains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18 |

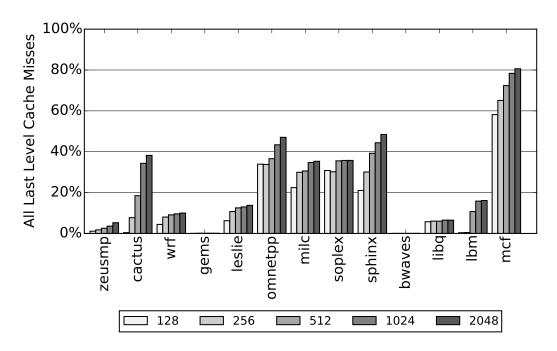

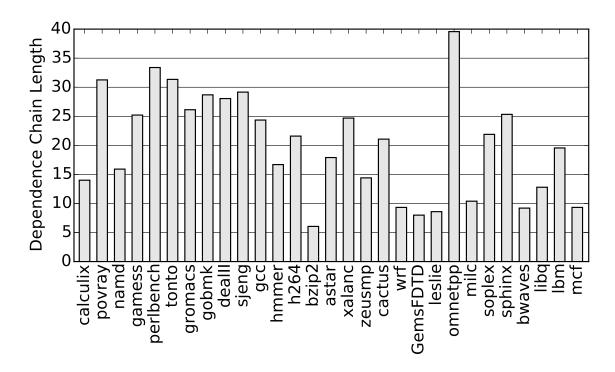

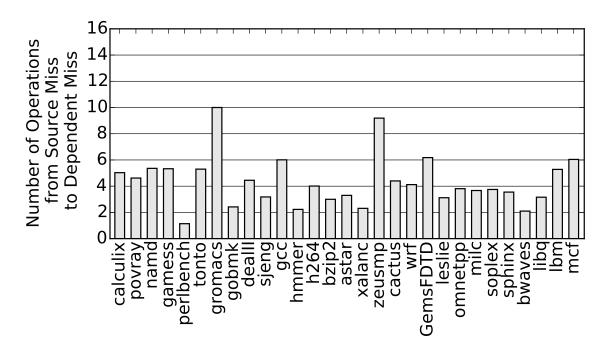

| 3.3  | Average Length of a Runahead Miss Dependence Chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19 |

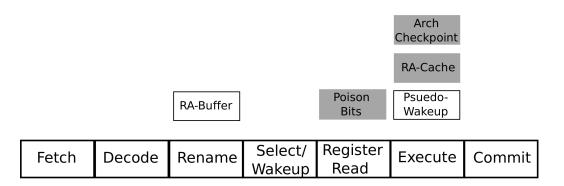

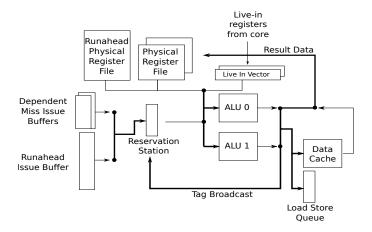

| 3.4  | The Runahead Buffer Pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21 |

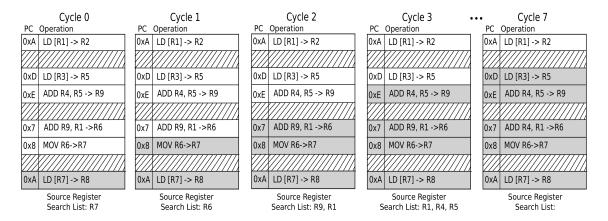

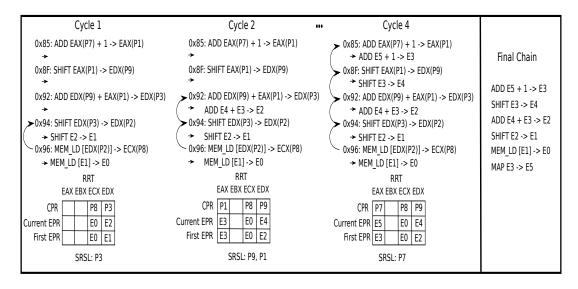

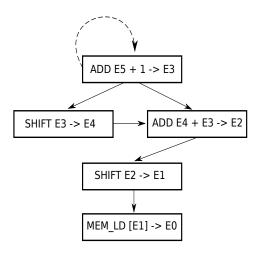

| 3.5  | Dependence Chain Generation Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22 |

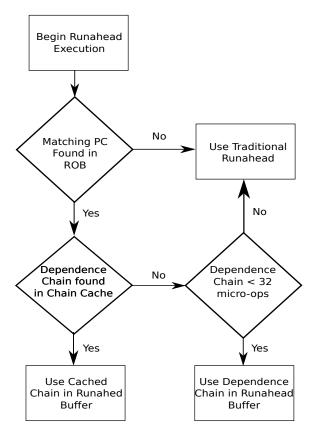

| 3.6  | Flow Chart of the Hybrid Policy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 27 |

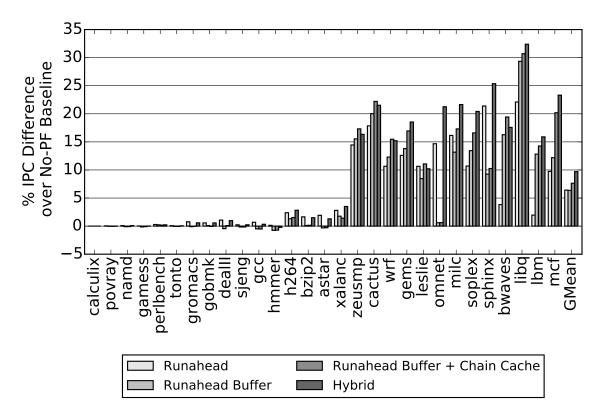

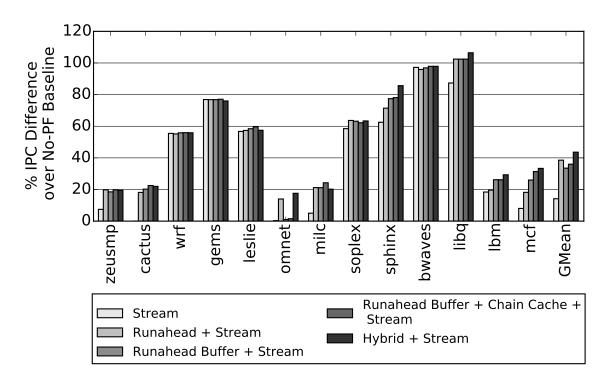

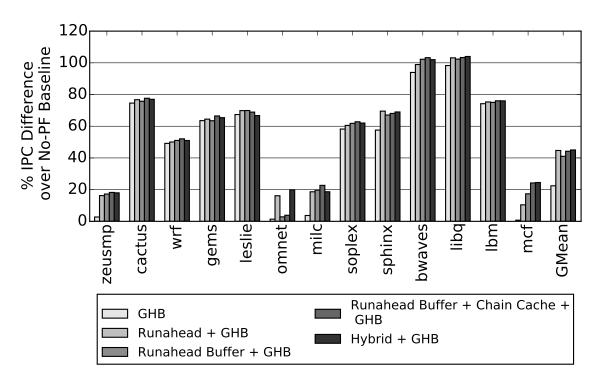

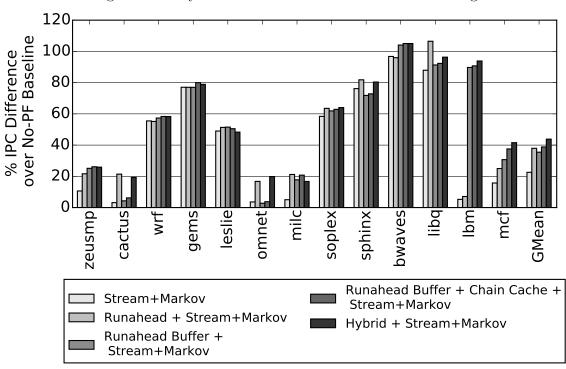

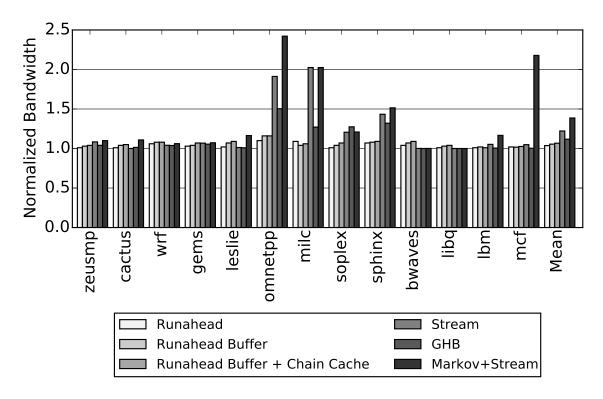

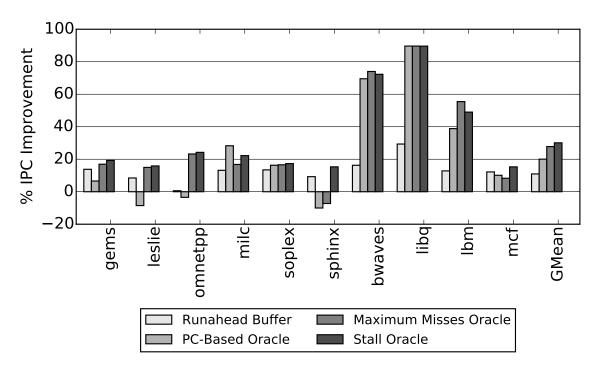

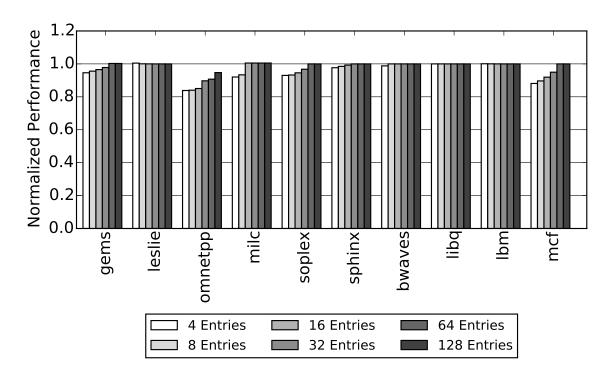

| 3.7  | Runahead Performance Normalized to a No-Prefetching System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34 |

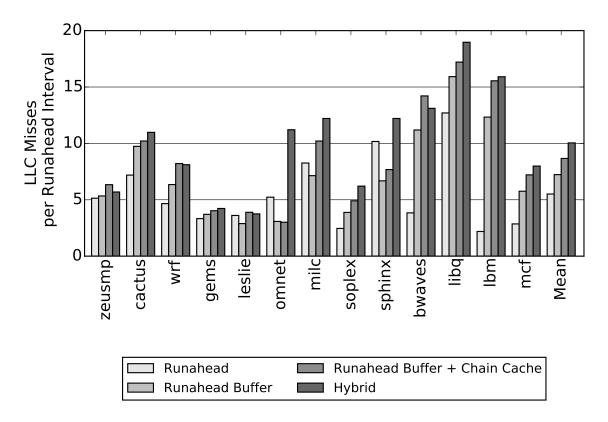

| 3.8  | Average Number of Memory Accesses per Runahead Interval                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35 |

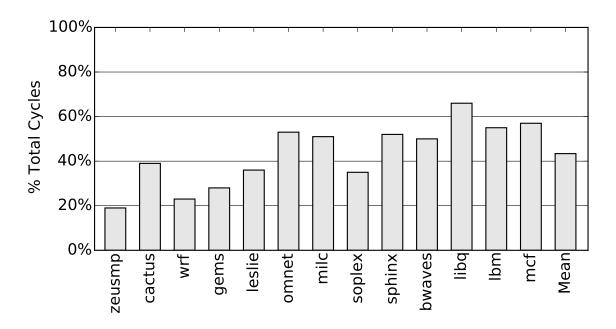

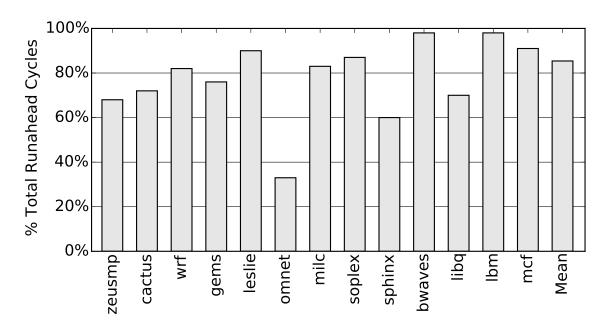

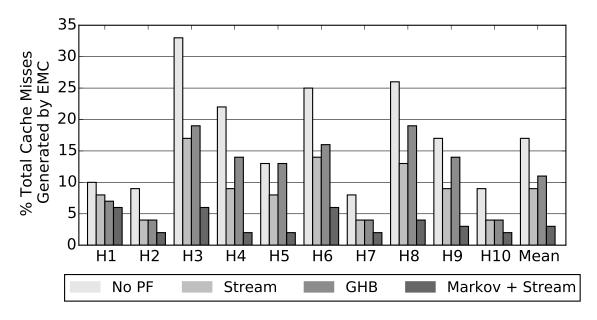

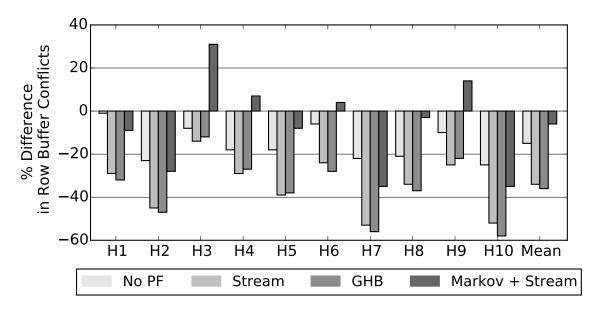

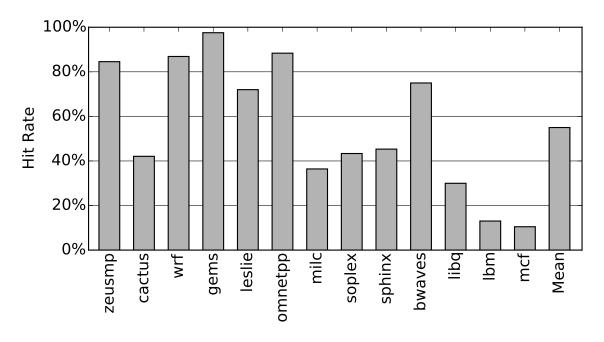

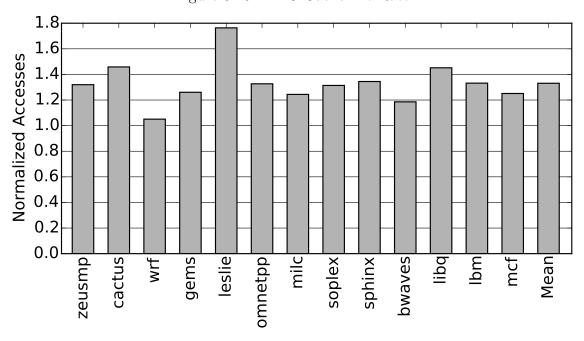

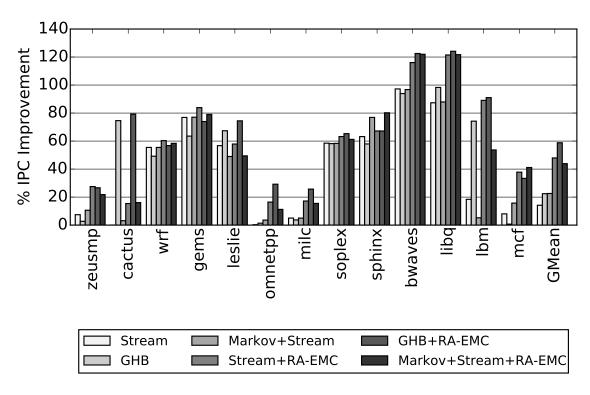

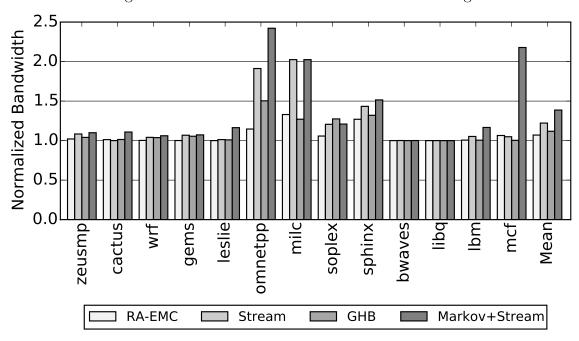

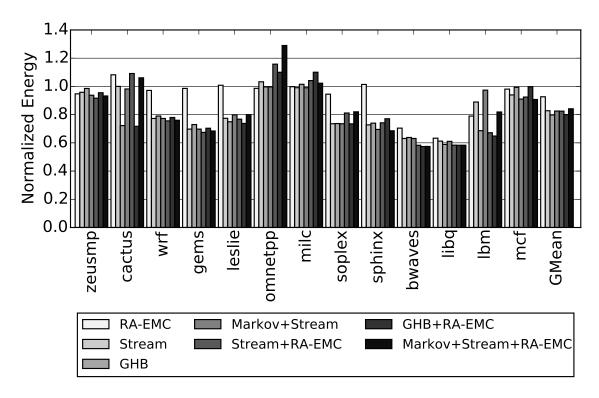

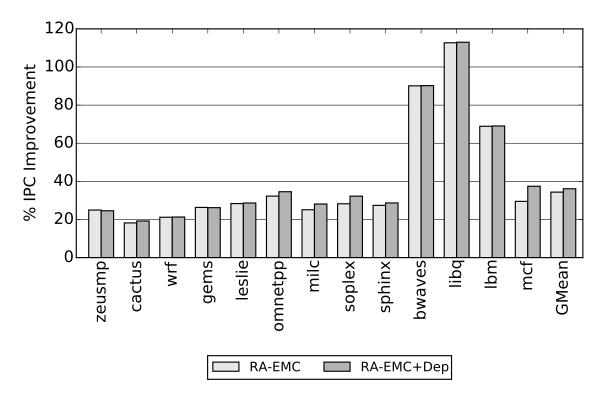

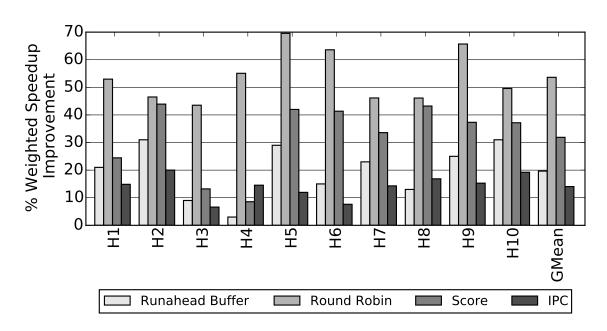

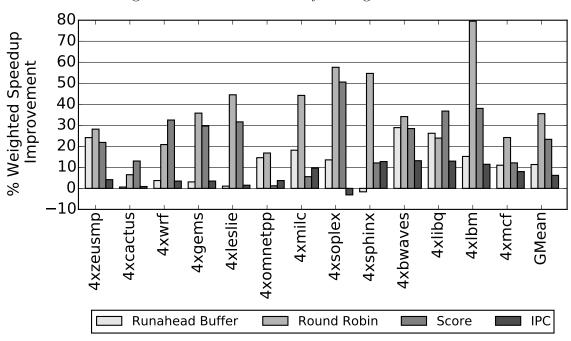

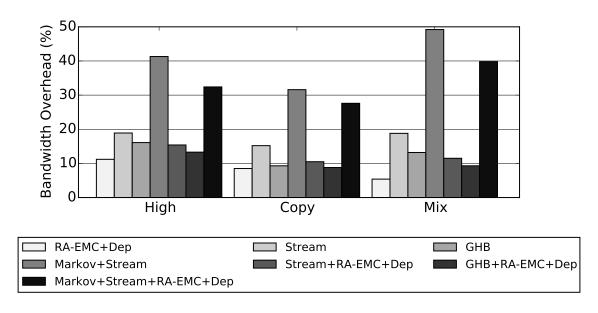

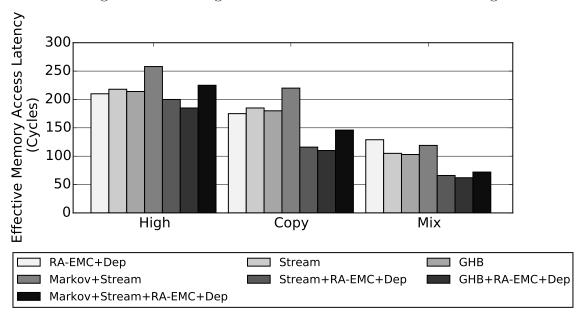

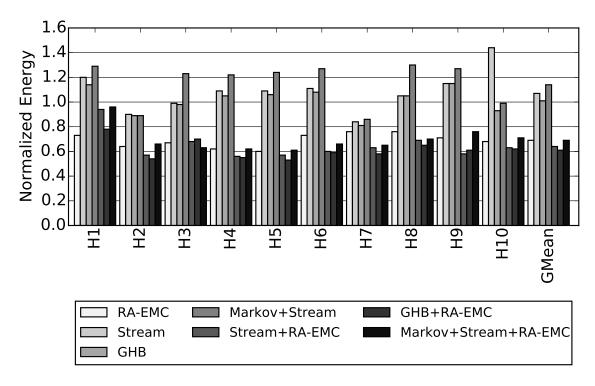

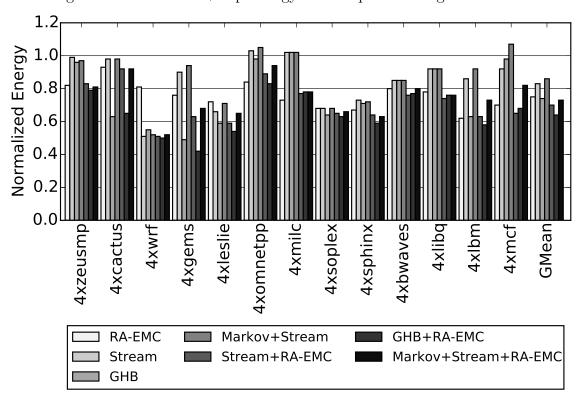

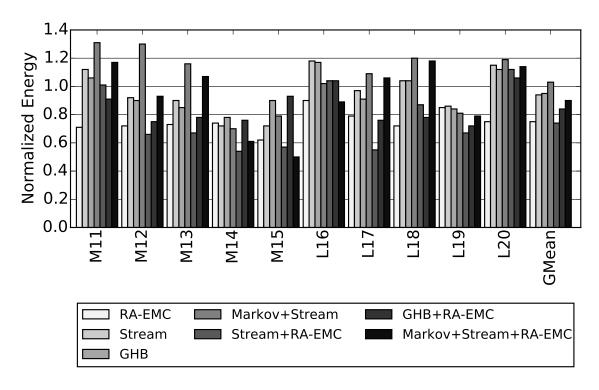

| 3.9  | Percent of Time the Core is in Runahead Buffer Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 36 |