Copyright

by

Sundaravaradan Navalpakkam Ananthan

2016

## The Thesis Committee for Sundaravaradan Navalpakkam Ananthan Certifies that this is the approved version of the following thesis:

# Automated Model-Based Transmission Line Fault Location Method Using Reduced Equivalent Circuit

# APPROVED BY SUPERVISING COMMITTEE:

Supervisor:

Surya Santoso

**Ross Baldick**

# Automated Model-Based Transmission Line Fault Location Method Using Reduced Equivalent Circuit

by

## Sundaravaradan Navalpakkam Ananthan, B.Tech

## Thesis

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

## Master of Science in Engineering

The University of Texas at Austin December 2016

### Acknowledgements

I would like to express my sincerest gratitude to my advisor, Dr. Surya Santoso, for his continuing support, expert guidance, incredible patience, understanding and encouragement throughout my study and research. I also thank Dr. Ross Baldick for reading this thesis.

I thank Naveen Ganta, Harsha Vardhana Padullaparti, Min Lwin and Quan Huy Nguyen for the help and assistance they provided me during my graduate study.

Finally, I would like to express my gratitude to my parents for their love, support and encouragement in every stage of my life.

### Abstract

## Automated Model-Based Transmission Line Fault Location Method Using Reduced Equivalent Circuit

Sundaravaradan Navalpakkam Ananthan, MSE

The University of Texas at Austin, 2016

Supervisor: Surya Santoso

Transmission lines are a vital part of power systems and are prone to a variety of short-circuit faults. Transmission line faults must be accurately identified and cleared so as to restore the faulted line back to normal operation in the shortest amount of time possible. Common fault locating practices used by utilities involve multiple manual data analysis stages which could cause time delays. This thesis presents an automated model-based transmission line fault location approach to improving the existing manual process.

A fault location process comprises of data preprocessing of the fault record and estimating the fault location using impedance-based techniques. This thesis first elucidates the data preprocessing steps, proposes and validates an algorithm for determining the fault current and voltage. It then proposes an automated fault location method by simulating relevant fault scenarios on a reduced equivalent circuit to determine the fault location. The proposed fault location method is implemented using MATLAB and OpenDSS. The need and process of forming reduced equivalent circuits for automating the fault location process are presented. A test circuit was used to illustrate the method and to evaluate the technical capabilities of the algorithm.

The technical performance of the proposed fault location method was analyzed on a variety of aspects such as line and generator outage, the presence of mutual coupling, the presence of fault resistance, and multiple combinations of the above. The algorithm is robust and capable of handling the above mentioned issues which affect the fault location estimate.

|  | Table | of | Content | S |

|--|-------|----|---------|---|

|--|-------|----|---------|---|

| List | of Tablesx                                                                                                                   |

|------|------------------------------------------------------------------------------------------------------------------------------|

| List | of Figures xi                                                                                                                |

| 1.   | INTRODUCTION 1                                                                                                               |

|      | 1.1 Motivation1                                                                                                              |

|      | 1.2 Prior Art                                                                                                                |

|      | 1.3 Objective                                                                                                                |

|      | 1.4 Thesis Organization4                                                                                                     |

| 2.   | OUTLINE OF MODEL-BASED FAULT LOCATION APPROACH 6                                                                             |

|      | 2.1 Potential of Reduced Equivalent Circuit for Model-Based Fault Location<br>Method                                         |

|      | 2.2 Working Scheme Summary of Model-Based Fault Location Approach.8                                                          |

|      | 2.2.1 Reduced Equivalent Circuit in CAPE9                                                                                    |

|      | 2.2.2 Reduced Equivalent Circuit in OpenDSS12                                                                                |

|      | 2.2.3 Role of MATLAB in Model-Based Fault Location12                                                                         |

| 3.   | FAULT RECORD PREPROCESSING 15                                                                                                |

|      | 3.1 Fault Recording Devices and Fault Record15                                                                               |

|      | 3.1.1 Common Format for Transient Data Exchange - COMTRADE File<br>Format                                                    |

|      | 3.2 Proposed Algorithm for Determining Fault Instant and Prefault Instant20                                                  |

|      | 3.3 MATLAB Implementation of Data Preprocessing Procedure22                                                                  |

|      | 3.4 Transmission Line Fault Data for Evaluating the Proposed Algorithm for<br>Determining Fault Instant and Prefault Instant |

|      | 3.4.1 Case 1: A Single-Line-to-Ground Fault24                                                                                |

|      | 3.4.2 Case 2: A Line-to-Line Fault                                                                                           |

|      | 3.5 Evaluation of the Proposed Algorithm for Determining the Fault Instant and Prefault Instant                              |

| 4. | AUTOMATED FAULT LOCATION USING REDUCED EQUIVALENT C<br>Model-Based Fault Location Approach | IRCUIT FOR<br>32 |

|----|--------------------------------------------------------------------------------------------|------------------|

|    | 4.1 Software Tools Used                                                                    | 32               |

|    | 4.1.1: CAPE - Computer-Aided Protection Engineering                                        | 32               |

|    | 4.1.2: OpenDSS - Open Distribution System Simulator                                        | 34               |

|    | 4.1.3: MATLAB                                                                              | 34               |

|    | 4.2 System Model Used                                                                      | 35               |

|    | 4.3 Formation of Reduced Equivalent Circuits in CAPE                                       | 36               |

|    | 4.4 Modeling in OpenDSS                                                                    |                  |

|    | 4.4.1 Generator                                                                            |                  |

|    | 4.4.2 Transmission Line                                                                    |                  |

|    | 4.4.3 Bus Tie                                                                              | 40               |

|    | 4.4.4 Mutual Coupling                                                                      | 40               |

|    | 4.5 Implementation of Proposed Approach in MATLAB                                          | 42               |

| 5. | Analysis of Reduced Equivalent Circuit Based Fault Log<br>Method                           | CATION<br>44     |

|    | 5.1 Reduced Equivalent Circuit Validation                                                  | 44               |

|    | 5.2 Size of Circuit                                                                        | 50               |

|    | 5.3 Fault Resistance                                                                       | 55               |

|    | 5.4 Line Configuration Change and Generator Outage                                         | 58               |

|    | 5.5 Fault Location Reach                                                                   | 65               |

|    | 5.5.1 Fault Location Reach - Case 1                                                        | 66               |

|    | 5.5.2 Fault Location Reach - Case 2                                                        | 69               |

|    | 5.6 Test Case Including all the Above Scenarios                                            | 71               |

| 6. | SUMMARY AND FUTURE WORK                                                                    | 76               |

|    | 6.1 Summary                                                                                | 76               |

|    | 6.2 Advantages                                                                             | 77               |

|    | 6.3 Future Work                                                                            | 78               |

### BIBLIOGRAPHY

# List of Tables

| Table 3-1 : Event analysis for Case 1                                   | 24 |

|-------------------------------------------------------------------------|----|

| Table 3-2 : Event analysis for Case 2                                   | 27 |

| Table 3-3 : Comparison of fault location results for Case 1             | 30 |

| Table 3-4 : Comparison of fault location results for Case 2             | 31 |

| Table 5-1 : Equivalent circuit validation                               | 47 |

| Table 5-2 : Equivalent circuit validation for small circuit             | 52 |

| Table 5-3 : Equivalent circuit validation for large circuit             | 54 |

| Table 5-4 : Analysis of line configuration change                       | 60 |

| Table 5-5 : Analysis of generator outage                                | 63 |

| Table 5-6 : Analysis of test case including all the scenarios discussed | 74 |

# List of Figures

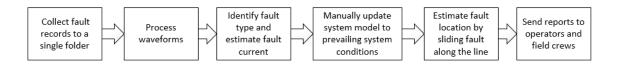

| Figure 1-1: Outline of fault location process used by utilities                        | . 3 |

|----------------------------------------------------------------------------------------|-----|

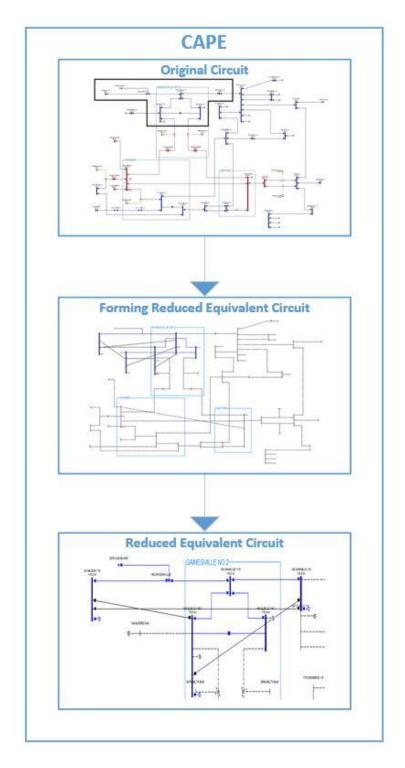

| Figure 2-1 : Reduction of large complex circuit into smaller equivalent circuits based |     |

| on DFR location                                                                        | 11  |

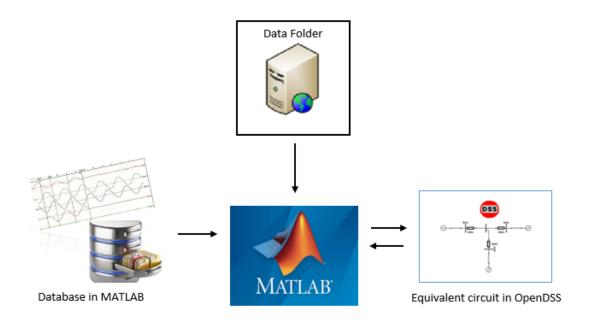

| Figure 2-2 : Role of MATLAB in the model-based fault location                          | 13  |

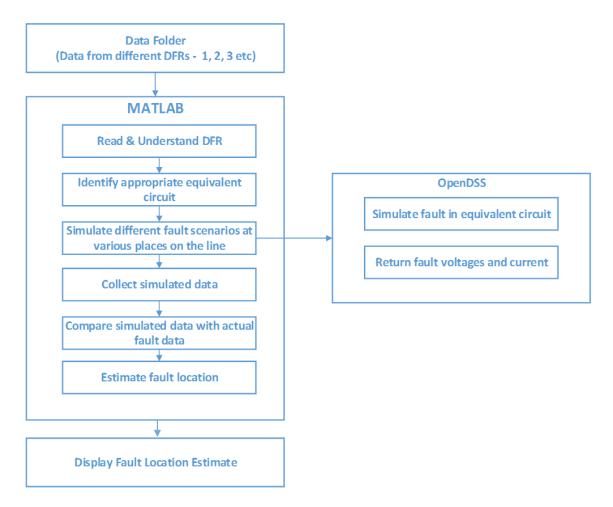

| Figure 2-3 : Flowchart depicting the sequential workflow of MATLAB and OpenDSS.        | 14  |

| Figure 3-1 : Sample configuration file                                                 | 17  |

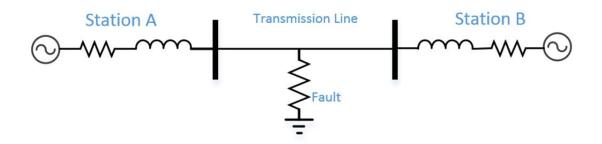

| Figure 3-2 : Transmission line fault                                                   | 24  |

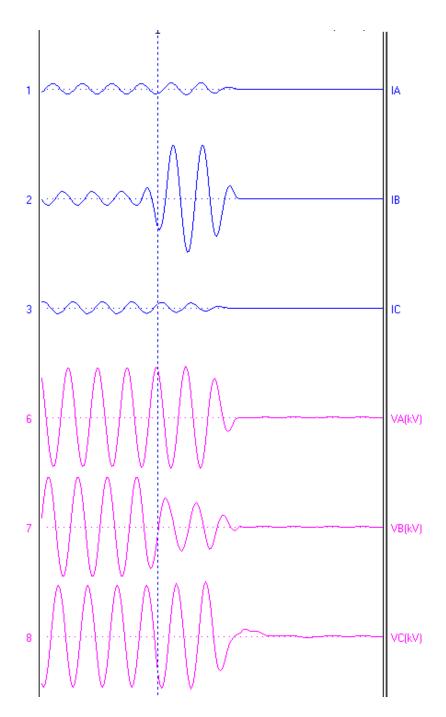

| Figure 3-3 : Phase voltage and current waveform of phase A, B and C for Case 1         | 26  |

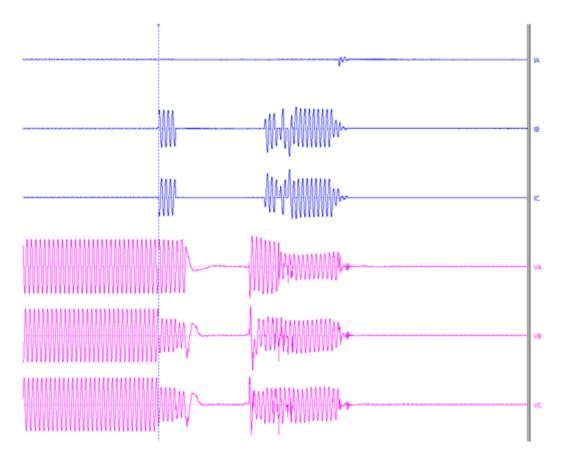

| Figure 3-4 : Phase voltage and current waveform of phase A, B and C for Case 2         | 28  |

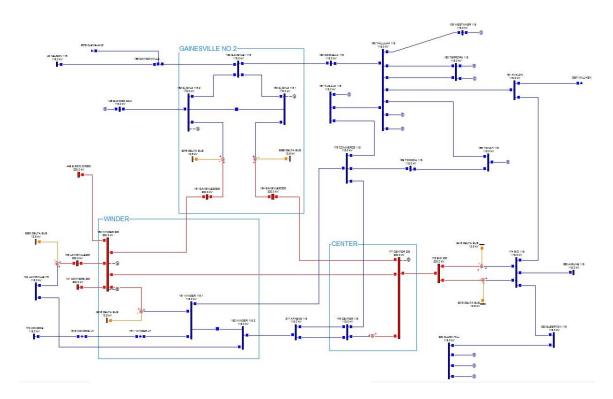

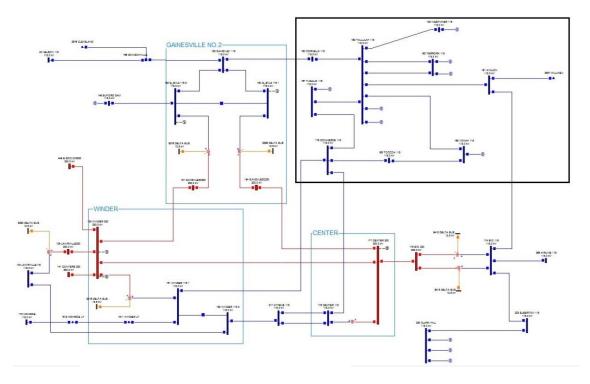

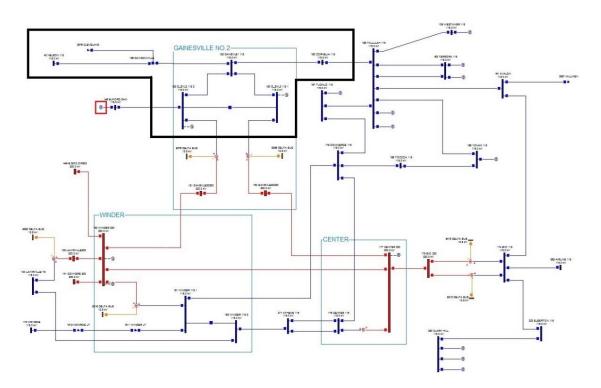

| Figure 4-1 : One line diagram of cape.gdb                                              | 35  |

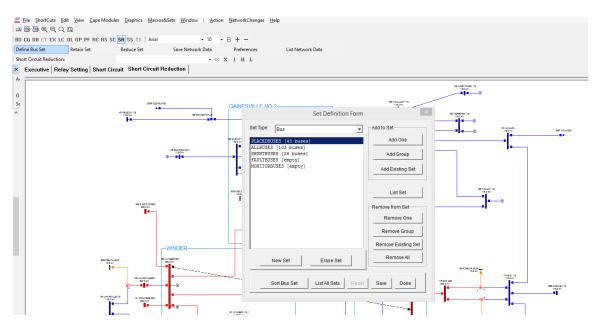

| Figure 4-2 : Network reduction using CAPE – 1                                          | 37  |

| Figure 4-3 : Network reduction using CAPE – 2                                          | 37  |

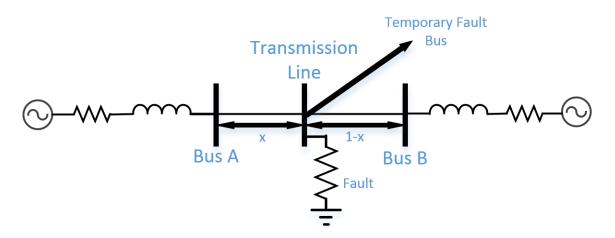

| Figure 4-4 : Transmission Line Fault in OpenDSS                                        | 39  |

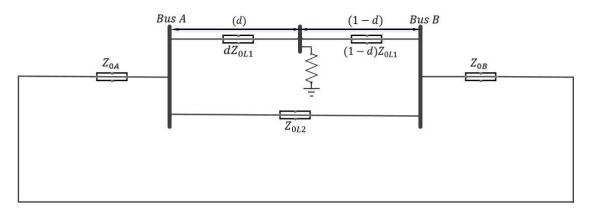

| Figure 4-5 : Zero-sequence circuit without mutual coupling                             | 41  |

| Figure 4-6 : Effect of mutual coupling on zero-sequence circuit                        | 41  |

| Figure 5-1 : Reduced Equivalent Circuit -1                                             | 45  |

| Figure 5-2 : Reduced Equivalent Circuit -2                                             | 46  |

| Figure 5-3 : Small reduced equivalent circuit – 1                                      | 50  |

| Figure 5-4 : Small reduced equivalent circuit – 2                                      | 51  |

| Figure 5-5 : Large reduced equivalent circuit – 1                                      | 53  |

| Figure 5-6 : Large reduced equivalent circuit – 2                                      | 53  |

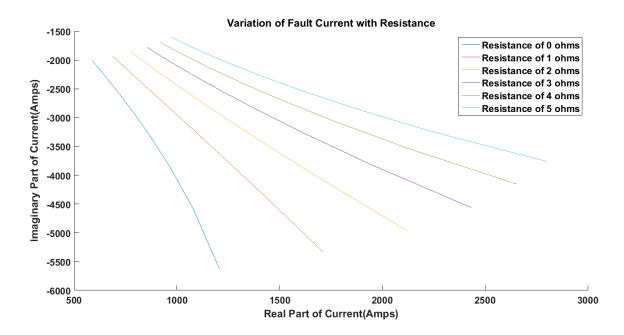

| Figure 5-7 : Single line to ground fault analysis                                      | 56  |

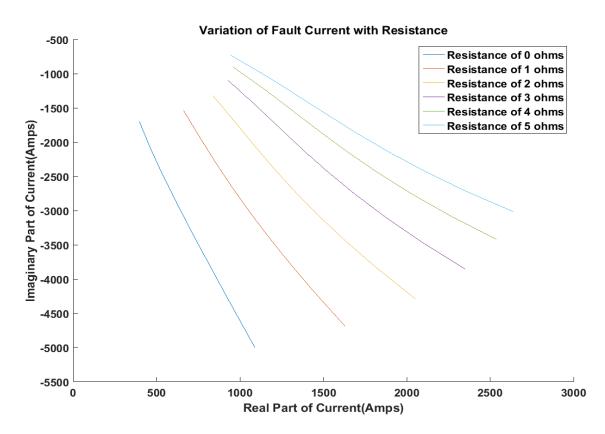

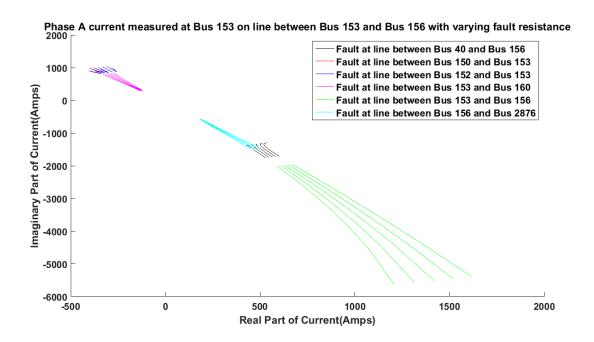

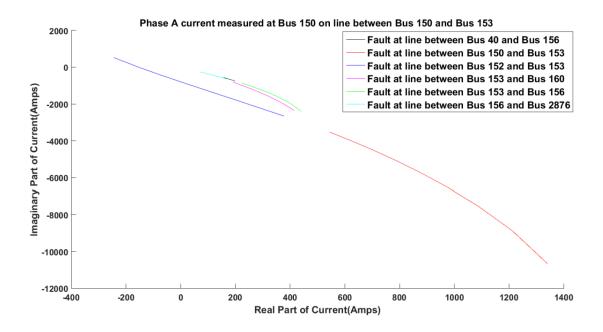

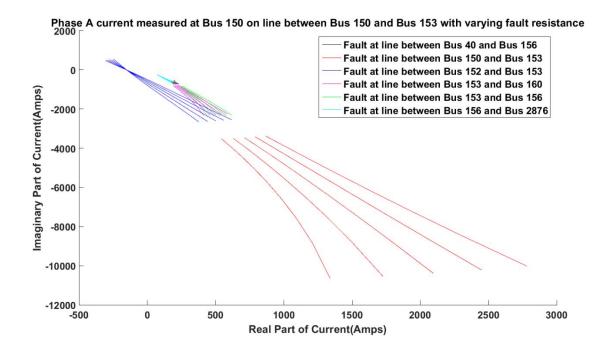

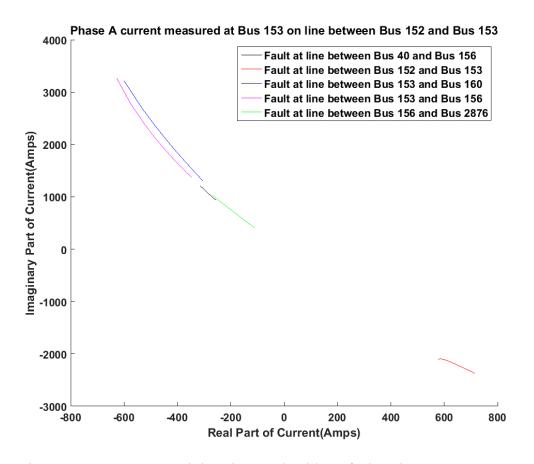

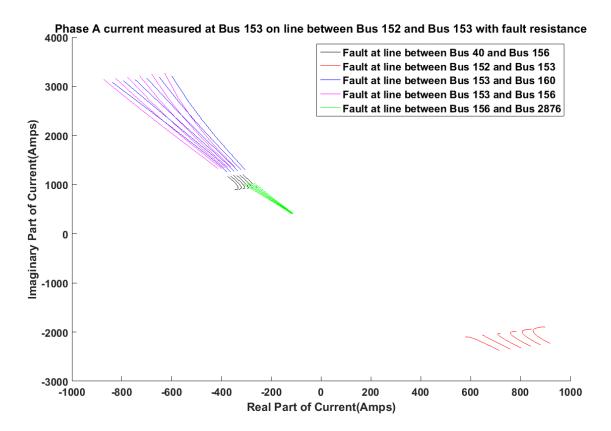

| Figure 5-8 : Variation of fault current with resistance - 1                            | 57  |

| Figure 5-9 : Variation of fault current with resistance - 2          | 58 |

|----------------------------------------------------------------------|----|

| Figure 5-10 : Circuit diagram with generator outage                  | 62 |

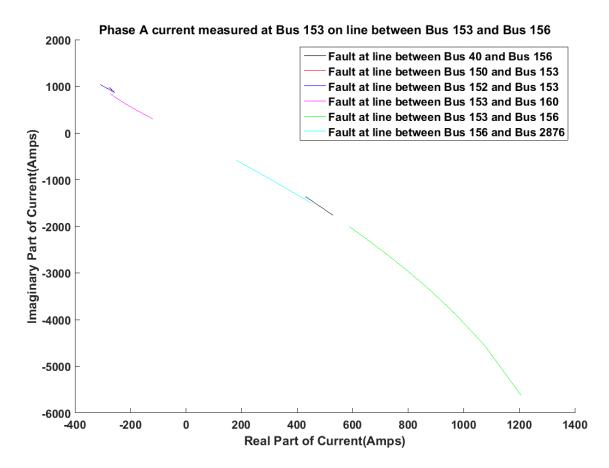

| Figure 5-11 : Reduced Equivalent Circuit                             | 66 |

| Figure 5-12 : Case 1 - Fault location reach without fault resistance | 67 |

| Figure 5-13 : Case 1 - Fault location reach with fault resistance    | 68 |

| Figure 5-14 : Case 2 - Fault location reach without fault resistance | 70 |

| Figure 5-15 : Case 2 - Fault location reach with fault resistance    | 70 |

| Figure 5-16 : Case 3 - Fault location reach without fault resistance | 72 |

| Figure 5-17 : Case 3 - Fault location reach with fault resistance    | 73 |

#### **1. INTRODUCTION**

#### **1.1 MOTIVATION**

Transmission lines are a vital part of a power system as they transfer electrical power over long distances from the source to the load. They are subjected to a variety of electrical faults as they are exposed to environmental effects such as lightning strikes or conductors coming in contact with each other during stormy weather conditions, animal or tree contact with a transmission line and insulation failure [1]. When a transmission line fault occurs, the fault has to be cleared as soon as possible so as to prevent permanent damage to equipment and devices, reduce the duration of power quality problems faced by customers and to restore the line to normal operating conditions.

Transmission line fault analysis has been a major topic for research for decades. Over the years, there has been development in communication technology, computational capability and system modeling which has led to the availability of more data and development of several algorithms for fault analysis. When there is a transmission line fault, protection equipment operates to de-energize the faulted line. Different recording devices located in substations will be triggered by the fault event and will record the required current, voltage and status signals. These records are used by different groups for fault investigation.

Fault records obtained from devices like digital relays and digital fault recorders need to be pre-processed to obtain the required useful fault data. This data is then analyzed and used in a fault location algorithm to obtain the fault location. As the fault analysis progress through each stage, it requires quick operation of personnel with different capabilities present at different locations to gather the required data and perform the tests, which may result in delays. For example, for a fault occurring at night, the maintenance crew even if available have to wait until the next day for the protection engineer (who may only work normal day shifts) to calculate and estimate the fault location. Hence, this necessitates the need for an effective, reliable and automated fault location approach.

The major contribution of this thesis is to propose an approach for automated fault location and analyze the proposed method. The proposed approach aims at producing rapid and accurate fault location estimates as and when a fault record is received by the protection engineer.

#### **1.2 PRIOR ART**

Modern day digital relays use impedance-based fault location algorithms to produce fault location estimates. Over the years, several impedance-based fault location methods have been developed as they are simple to use and provide reasonable fault location estimates. Impedance-based fault location algorithms have specific requirements and the fault location estimates are affected by several factors which have been studied by several researchers. Some of the components which are sources of error in the fault location estimates calculated by impedance-based fault location methods are loads, mutual coupling between two lines, DC offset, CT saturation, inaccuracy in the line model, inaccuracy in extracting the fault current and voltage, presence of 3 terminal lines, tapped radial lines and many others. [2] [3] [4] [5] [6]. Hence, the fault location estimate obtained directly from the relays need not be always accurate.

A common procedure utilized by most utilities for identifying fault location is presented below. This method is not completely automated and requires manual manipulation to obtain the fault location.

Figure 1-1: Outline of fault location process used by utilities

Figure 1-1 gives the outline of the fault location process followed by utilities to determine or estimate fault location. First, the disturbance records from digital fault recorders (DFRs) and digital relays are automatically brought to a single folder. The appropriate waveforms are analyzed to extract the magnitude and phasor relationships of fault voltages and current as well as to determine the fault type. The entire system modeled in a short-circuit program such as CAPE (Computer-Aided Protection Engineering) [7] or ASPEN (Advanced Systems for Power Engineering) [8] is available to the utility. This model is manually manipulated by the utility to represent the prevailing system conditions. The fault location is then identified by 'sliding' fault down the line till calculated current values match the measured current values. Finally, after identifying the fault location, reports with the estimated fault location is sent to operators and field crews.

#### **1.3 OBJECTIVE**

The above mentioned process for fault location commonly used by utilities is not completely automated and requires manual manipulation to obtain the fault location estimate. The aim of the proposed solution is to preserve the existing fault location technique (sliding fault along the length of the line and comparing it with actual values from fault record) but implement it in a different way so that the fault location process can be automated as well as make it convenient to use. The data preprocessing steps such as finding the appropriate fault current and voltage levels as well as the type of fault is to be automated. For this purpose, a novel method to calculate appropriate fault current and fault voltage to be used in fault location algorithms from the fault record is presented. A modern technique using reduced equivalent circuits for model-based fault location is developed to reduce the complexity of the fault location process. The performance and capability of the developed algorithm are evaluated. This is done by analyzing the accuracy of the fault location estimates as well as by studying other factors which may influence the fault location estimates such as effects due to the presence of mutual coupling between lines, fault resistance, generator outage, line configuration change, and fault location reach of a circuit (distance up to which accurate fault location can be identified).

#### **1.4 THESIS ORGANIZATION**

The work presented in the following chapters are organized as follows. Chapter 1 presents the introduction to the thesis and explains the motivation for developing the proposed model-based fault location using reduced equivalent circuit approach.

Chapter 2 provides an outline of the proposed approach. It explains the potential of the proposed method and working scheme of the method.

Chapter 3 discusses fault records and explains how to interpret fault records present in COMTRADE file format which is one of the most commonly used industry standard file format for transient waveform and event data. This chapter further discusses the fault record preprocessing steps required before being able to apply any fault location algorithm. This chapter also proposes a method to identify the appropriate fault current and fault voltage to be used in the fault location algorithms.

Chapter 4 describes the proposed fault location method in detail. This chapter discusses different software packages used for analysis and the sample system model used for analysis. This chapter illustrates the process of formation of reduced equivalent circuits,

modeling of different circuit components in OpenDSS and implementing the proposed approach in MATLAB.

Chapter 5 presents the technical analysis of the proposed method. It begins with validating the reduced equivalent circuit short-circuit characteristics followed by demonstrating ways to tackle the common issues faced by utilities such as line and generator outages, the presence of mutual coupling and fault resistance. This chapter illustrates the robustness and advantages of the proposed method.

Chapter 6 presents a concise summary of the contents of the thesis. It also recapitulates the advantages of the proposed method and discusses the scope of future work.

## 2. OUTLINE OF MODEL-BASED FAULT LOCATION APPROACH

This chapter provides an outline of the proposed methodology. This chapter starts by discussing the potential of using a reduced equivalent circuit for model-based fault location. The working scheme of reduced equivalent circuits for model-based fault location is introduced. The chapter briefly presents the role of different components involved in the proposed method.

# **2.1 POTENTIAL OF REDUCED EQUIVALENT CIRCUIT FOR MODEL-BASED FAULT LOCATION METHOD**

Existing fault location approaches commonly used by utilities are not completely automated and requires manual manipulation to obtain the fault location. Based on initial preprocessing of the fault record, the faulted line and fault characteristics are obtained. Several fault scenarios are then simulated with faults along the entire length of the transmission line. Fault location is identified when the simulated fault characteristics of a fault scenario match the measured fault characteristics obtained from the recorded fault waveform. These approaches make use of the full circuit model available to the utility in some power system simulation software such as CAPE or ASPEN.

The tasks of simulating sliding faults and comparing simulated fault currents to the actual measured fault current are laborious. This process can be automated provided the short-circuit analysis software can be commanded or driven to perform the desired actions. Unfortunately, there is no third-party software to drive CAPE externally. Other short-circuit programs may be driven by a third-party program, however, switching from one software program to another may introduce disruption and incur operational changes. For

these reasons, automating fault location search using a full-circuit model where the shortcircuit program cannot be driven using an external software is difficult and cumbersome.

The above discussion describes the necessity of developing an alternative approach to overcome the difficulties of automating fault location search using a full-circuit model. The solution proposed below is to emulate the full-circuit model-based fault location approach, however, with reduced-circuit models. In the proposed approach, a series, i.e., a library, of equivalent circuits are developed to replicate short-circuit characteristics of circuits and buses where digital fault recording devices (DFR) are located. Each equivalent circuit is converted into a short-circuit analysis program that can be driven by an external software. OpenDSS is chosen for this purpose because it is a freeware and developed by EPRI (Electric Power Research Institute). MATLAB developed by Mathworks is chosen as the driver because it has been widely used to drive OpenDSS as well as its scripts are easier to edit to improve an existing algorithm if required. Furthermore, MATLAB can be used to preprocess fault record data and post-process results from OpenDSS as well.

The proposed solution intends to preserve the existing successful fault location technique (sliding fault along the length of the line and comparing it with actual values from fault record) used by utilities but implements it differently so that the fault location process can be automated as well as make it convenient to use. By implementing this approach, fault location can be estimated for a variety of scenarios such as tapped lines, three terminal lines as well as a fault at lines farther away from the recording device. The fault location process is automated and can produce the fault location estimate as and when data from a DFR is put in the data folder. This eliminates the tedious and cumbersome process of obtaining fault current and voltages from the fault records as well as manually performing the sliding fault process to obtain fault location. Furthermore, the approach is universal. Most utilities have the entire transmission system modeled in CAPE or ASPEN or any other software. Even if a third party software can drive one of these short-circuit analysis softwares, the coding and development for automating the fault location process has to be done for each short-circuit analysis software separately and is not universal. Hence, equivalent circuits are implemented using OpenDSS and are independent of the software used by utility (CAPE, ASPEN or any other software) in which the whole system model is available. The library of equivalent circuits in OpenDSS, driven by MATLAB is used for estimating fault location and no other software is required. The hardware requirements to implement this approach is also minimal. It does not require any large investments or any new equipment to be installed. Hence, the proposed approach can be implemented by any utility with their existing infrastructure and system.

#### 2.2 WORKING SCHEME SUMMARY OF MODEL-BASED FAULT LOCATION APPROACH

This approach aims at identifying the exact location of a fault occurring in the transmission or distribution system by using data from intelligent electronic devices (IEDs) or fault recorders which monitor different lines at different locations throughout the system. The information from these fault recording devices, which are placed at the end of certain lines, are sent to a data folder through supervisory control and data acquisition (SCADA) and other communication systems. The centralized data folder where data from all the DFRs arrive is monitored continuously. As and when a DFR record arrives in that folder, it is processed automatically and the location of the fault will be identified. This process is done using MATLAB, a user friendly software which provides the opportunity to control and drive OpenDSS. The process can be done either in real-time or off-line.

Several different commercially available fault analysis platforms are used by utilities to model electrical transmission network and its protection systems. For the development and illustration of the proposed approach, CAPE software has been used. The entire electrical transmission network is assumed to be available in CAPE.

Network reduction is a common feature found in most power system analysis and protection engineering software. CAPE has a similar feature where a large complex system can be reduced to a small equivalent circuit that depicts the short-circuit characteristics of the actual large system for the elements under consideration. This is done by using the Short Circuit Reduction module in CAPE. The developed equivalent circuit in CAPE can be modeled in OpenDSS using network data obtained from CAPE after reducing the network. This conversion from CAPE to OpenDSS is done using MATLAB which highlights the versatility of MATLAB and OpenDSS. Using the above steps, a library of equivalent circuits would be created in OpenDSS. These equivalent circuits can be easily manipulated using MATLAB to perform fault analysis. OpenDSS software is used here because CAPE doesn't allow external software to drive it.

MATLAB reads and processes data from DFR present in the data folder and appropriately selects the equivalent circuit from equivalent circuit library based on DFR location. The selected equivalent circuit in OpenDSS will be driven by MATLAB to perform fault analysis by sliding a fault along the suspected faulted lines. By comparing the data obtained from fault analysis and that which was obtained from DFRs, fault location would be estimated.

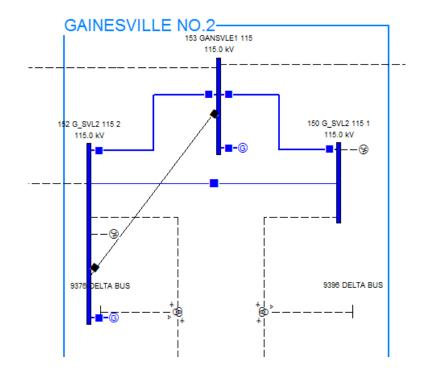

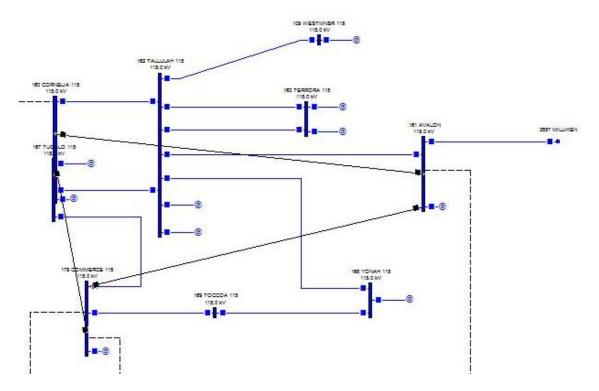

#### 2.2.1 Reduced Equivalent Circuit in CAPE

In CAPE software, the equivalent circuit can be obtained using Short Circuit Reduction module. The user can choose the size of the equivalent circuit by choosing the buses to retain from the large original circuit in the equivalent circuit. The equivalent circuit represents the portion of original circuit present surrounding the DFR device. The circuit would be reduced such that the short-circuit characteristics of the equivalent circuit are same as that of the original circuit. Each DFR or a group of DFRs will have its own equivalent circuit model stored in the library of circuits. This library of equivalent circuits is modeled in OpenDSS from the network data obtained from reduced equivalent circuits in CAPE.

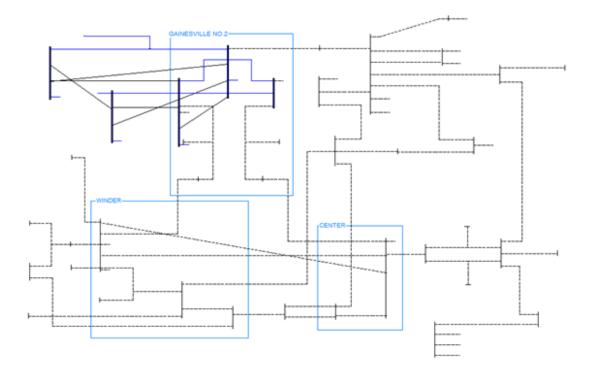

Figure 2-1 : Reduction of large complex circuit into smaller equivalent circuits based on DFR location

#### 2.2.2 Reduced Equivalent Circuit in OpenDSS

Using the network data of the reduced equivalent circuit obtained from Short Circuit Reduction module in CAPE, the reduced equivalent circuit is modeled in OpenDSS to run different fault scenarios. The data in CAPE is translated to OpenDSS as CAPE does not have the facility to be driven or controlled by other software platforms like MATLAB. OpenDSS provides that feature where it can be driven by MATLAB for modeling, editing and simulating the equivalent circuit. The equivalent circuit would be driven by MATLAB to simulate faults at several fault locations along the line and with various fault impedances. The results of each iteration of faulted scenarios are collected by MATLAB. Modeling of the equivalent circuit in OpenDSS from the network data of the equivalent circuit obtained in CAPE is done manually, but this process can be automated too.

#### 2.2.3 Role of MATLAB in Model-Based Fault Location

MATLAB is used to read the fault records from DFRs as and when it receives them in the data folder. MATLAB calculates the fault current, fault voltages, instant of fault occurrence and the location of the DFR from the fault record. MATLAB would then identify the correct equivalent circuit from the library of circuits. Once the equivalent circuit is identified, MATLAB would then run several iterations of the chosen equivalent circuit in OpenDSS to simulate faults at various locations along the length of the line and obtain the fault currents and voltages. It then compares the simulated data with the actual fault voltages and currents obtained from the fault record from data folder to estimate the fault location. MATLAB provides the fault location estimate based on the best possible match that it sees from the comparison. In order to calculate the fault current and voltages, the channel mapping information associated with each DFR must be preloaded into MATLAB. Figure 2-2 shows the role of MATLAB in the proposed model-based fault location.

Figure 2-2 : Role of MATLAB in the model-based fault location

The following is a flow chart explaining the role of MATLAB and OpenDSS and their sequential tasks in determining the fault location.

Figure 2-3 : Flowchart depicting the sequential workflow of MATLAB and OpenDSS

#### **3. FAULT RECORD PREPROCESSING**

The need for an automated fault location approach and the potential of the proposed method have been discussed in the previous chapters. Chapter 2 provided an outline of the proposed approach. The following chapters discuss the proposed technique in detail.

This chapter discusses the data preprocessing steps when a fault record is received by the operator. The chapter starts with introducing fault recording devices and the common industry standard file format in which fault records are present in (Common Format for Transient Data Exchange - COMTRADE file format). The raw data present in fault records need to be processed, appropriate prefault/fault voltage and current have to be obtained to estimate the fault location accurately. This chapter compares the fault location estimates obtained using data from different time intervals in the fault record and uses one-ended impedance-based algorithms to prove the efficacy of the proposed method. The entire process of fault location has been implemented using MATLAB. Hence, no additional software is required for data preprocessing.

#### **3.1 FAULT RECORDING DEVICES AND FAULT RECORD**

Recording devices are primarily used to monitor the status of various devices in the power system and to record voltages and currents at a particular location during certain events. Recording devices may differ in sampling rate, length of record and type of record they can capture based on their purpose of usage [9]. Some examples of recording devices are Digital Fault Recorders (DFRs) and microprocessor-based relays.

Recording devices produce fault records when they detect any disturbance in the instrument they monitor. The recording device can be triggered by a variety of conditions based on their setting such as over-current, change in observed voltage or impedance. Recording devices monitoring transmission lines are configured to produce fault records

such that they contain pre-fault information, event or fault data and post-fault information. Recording devices monitoring transmission line for faults require fast recording systems as transmission line faults are usually short lived.

Prefault section of fault record contains information regarding the normal system conditions before the disturbance or fault event has occurred. Event data contains fault voltages and currents and status of protective devices (if monitored by the DFR). Post-fault information shows how the system has responded and operated under the fault condition.

#### 3.1.1 Common Format for Transient Data Exchange - COMTRADE File Format

The rise in measurement and digital technology has led to increasing usage of recording devices for a variety of purposes. Fault records can be in a variety of data formats depending on the manufacturer of the recording device and have to be read in specific software platforms. Hence, IEEE had defined a common data file format for exchanging various fault, test and simulation data of electrical power system components, namely, IEEE Standard Common Format for Transient Data Exchange (COMTRADE) for Power Systems (IEEE Standard C37.111-1999) [10]. This format of representing data contains up to 4 types of files. They are header file, configuration file, data file and information file. This section provides an outline to the different types of files present in COMTRADE file format.

The header file is an optional ASCII text file which provides supplementary information other than the fault data and configuration data. It can contain a variety of information such as additional details regarding the fault, system parameters and status of the system components. Header file has ".hdr" extension to distinguish it from other file types. A single fault record can contain several measurements of a variety of quantities in different scales stored in the data file. The configuration file contains the information required to interpret the contents of the data file. The configuration file has ".cfg" extension to distinguish it from other file types. It contains the following information in the given order. The first line consists of station name along with identification of the recording device followed by COMTRADE Standard revision year. The next line contains the total number of channels and type of channels. A number followed by 'A' represents the number of analog channels and number followed by 'D' represents the number of digital channels present. The analog channel information is next followed by status (digital) channel information. Each line represents a channel recorded in the DFR. This is followed by line frequency, sampling rate information, date/time stamp, data file type and time stamp multiplication factor. Figure 3-1 shows a sample configuration file.

StationA, Device1,2013 40.16A.24D 1,IA,,, Amps,0.00100000000,0.0,0.0,-842000,846000,400,1,P 2,IB,,, Amps,0.00100000000,0.0,0.0,-6186000,6090000,400,1,P (represents multiple line of analog channel information) 1,ENT,,,0 2,TP,,,0 3,50 51,,,0 (represents multiple line of status channel information) . . . . . . 60.000000 1 960.0000,240 17/03/2016,17:47:40.027375 17/03/2016,17:47:40.093000 ASCII 1

Figure 3-1 : Sample configuration file

Each line of analog channel information contains the following: analog channel index number, channel identifier, phase identification, circuit component monitored,

channel units, channel multiplier, channel offset, channel time skew from start of sample period, range of data value (minimum followed by maximum) for that channel, voltage or current transformer ratio (primary followed by secondary) and primary or secondary data scaling identifier.

From the above example, the third line has information about the first channel. From Figure 3-1, we can infer that the analog channel contains measurements of current in 'A' phase in amperes. If the data value were 100, the actual current value would be 100 multiplied by channel multiplier (0.001 in this case) and then the offset factor (0 in this case) is added. The minimum data value that could be present is -842000 in the data file for that channel (not the actual measured value in amperes) and the maximum value is 846000. The current transformer ratio used for measurement of this channel quantity is 400:1. Finally, 'P' represents that the measured quantity is the primary value and hence the actual current value in phase A. In the example, there are no channel identifier or phase identification element present and are hence left empty.

Each line of digital channel information contains the following: status channel index number, channel name, channel phase identification, circuit component monitored and normal state of the status channel (0 or 1). From Figure 3-1, consider the first digital channel. It has the status channel index number which is '1' and channel name which is 'ENT'. Information about channel phase identification and circuit component monitored are not specified and are hence empty in the configuration file. The normal state of the channel is '0'.

Line frequency and sampling data information come next after digital channel information. Line frequency is specified in hertz (Hz). The sampling data information is as follows: number of sampling rates in the data file, sampling frequency in Hertz and last sample number at the given sampling rate. In the above example, there is one sampling rate of 960 Hz and the last sample number is 240. Date/time stamp is specified as day, month, year, hour, minute and seconds. The data file according to this example will be in ASCII format and hence is denoted by 'ASCII' in the second last line. Finally, the time stamp multiplication factor is the last line and is 1 in our example.

The order of contents must be maintained throughout according to IEEE Standard C37.111-1999 [10] so that the records are interpreted correctly by any human or computer.

The data file contains scaled values of the channel measured. Configuration files contain the conversion factors which need to be implemented to get the actual measured values. Hence, the data files will be in the exact order and format as defined in the configuration file. The data file has ".dat" extension to distinguish it from other file types.

Information can be stored in binary or ASCII format in the data file. In this section, we shall discuss ASCII data file format. Each row contains the data of different channels for that sample number and hence the total number of rows depends on the length of the recording. The first column contains the sample number followed by the time stamp for the data of that sample number. The next set of columns contain data values for each analog channel followed by data for status channels. At the end of the file after the last row of measurement data, an ASCII end of file marker (EOF) is placed to denote the end of the data file.

Information file contains additional information required apart from the standard information provided in the above files to be able to analyze the fault record by different users. This file can contain public information which is accessible by all users and private information that is available only to certain users. The information file is an optional file and has ".inf" file extension.

A fault record in COMTRADE format have a configuration and data file and may or may not contain header file and information file as they are optional files. The file names can be the same for all the 4 types of files, and they are distinguished by their file type.

# **3.2 PROPOSED ALGORITHM FOR DETERMINING FAULT INSTANT AND PREFAULT INSTANT**

In this section, an algorithm is proposed for determining the appropriate instant for taking fault current and fault voltage measurement. This step is crucial in fault analysis as the values obtained in this step directly affects the fault location estimate. The efficacy of the proposed algorithm is demonstrated in this chapter by implementing the algorithm on sample fault records and using the identified fault current and voltage measurement for fault location.

Transmission line faults are accompanied by significant raise in current along with voltage drop in the faulted phase. Different algorithms have been proposed and implemented over the years for fault detection in relays. For our analysis, we sweep through the current values obtained from previous step and fault is said to be detected when the magnitude of current corresponding to that sample set is higher than three times the magnitude of current at that instant is three times the value of current 3 cycles before that instant. This sample number is considered as fault instant and the sample number which was 3 cycles before it is considered as prefault instant. Usually, when a fault occurs, the current flowing through the line raises to large values within a few cycles. In some fault records, data only for few cycles before the fault may not be available. Hence, the instant 3 cycles before the first detection of large current value is considered as prefault instant. On continuing examining the set of current values beyond the fault instant, we compare current

value obtained corresponding to each sample with three times the prefault current value. The fault exists until this condition fails. In other words, all the sample sets which have RMS currents larger than 3 times the prefault current value are considered as fault instants.

The instant where the fault current settles after rising and voltage settles after falling down is the appropriate moment for taking values to be used in fault location algorithms. This can be achieved by using the following two criteria to obtain the fault current and voltage. The percentage change in the calculated fundamental RMS current between successive sample data set is within 1 percent and the percentage change in the calculated fundamental RMS voltage between successive sample data set is within 3 percent. These threshold values were determined experimentally and were found appropriate for a variety of fault records which were studied. These criteria also depend on sampling frequency. The above values are for 960 Hz. At higher sampling rate, the percentage change in current and voltage between successive sample data would be much lesser because the signal is sampled more frequently. Hence, dividing it by the number of times the sampling frequency exceeds 960 Hz gives the required threshold value. For example, for 5760 Hz, the current criterion would be 0.16 percent and voltage criterion would be 0.5 percent. To further ensure that the waveforms have settled, we further check if the current and voltage condition is satisfied for the next half cycle (next 8 sample sets for 960 Hz).

The fault current and voltage of most permanent faults settles to a steady state value and can be estimated using the above method. In cases where the above criteria could not be satisfied, the highest RMS current value and the corresponding voltage can be considered as fault current and fault voltage. This may lead to inaccuracies in measurement due to transients or small spikes in current which may occur.

#### **3.3 MATLAB IMPLEMENTATION OF DATA PREPROCESSING PROCEDURE**

This section contains discussion and implementation of the data preprocessing steps of the fault record using MATLAB.

Fault records present in COMTRADE file format have at least 2 files as discussed in previous sections. When a new fault record is received by the utility, it is to be imported into MATLAB and processed. Furthermore, a single DFR record can have measurements from monitors measuring different lines. Hence, the appropriate channels measuring the fault current and voltage have to be identified. This can be done in several ways based on the setup implemented by the utility.

One approach is that separate folders can be used for disturbance or fault records corresponding to each transmission line monitored. Hence, when a fault record is received from a DFR, it is automatically put into its corresponding folder. MATLAB can be programmed to check for new files in each DFR folder, and when a file is received, it can then process the fault record and select the appropriate equivalent circuit based on the folder in which it is present. Another approach is to identify the faulted line using the header file which may contain information regarding the fault. Once the faulted line is known, the appropriate current and voltage channels can be processed. Another approach which can be used if the above two methods are not viable is by having to process all the channels present in the fault record and identifying the channels recorded in it as every channel may have to be processed till the channels corresponding to the faulted line is identified.

Once the faulted line is known, the voltage and current measurements of the faulted line can be processed. In the data file, each column refers to a channel and each row is a sample. The data in the configuration file is used to obtain the right conversion parameters to acquire the measurements in engineering units such as volts (V) and amperes (A). Care should be taken to avoid mismatch in units such as kilovolts (kV) and amperes (A) or volts (V) and kiloamperes (kA). The data obtained after conversion can be plotted in a graph to ensure that the right channels have picked up from the fault record. Other data such as sampling rate of the fault record and length of the fault records can be identified from the configuration file.

The measurements obtained from fault records are discrete samples and hence Discrete Fourier Transform (DFT) [11] [12] is applied to obtain the phasor quantities. The fundamental RMS quantity is required for using the fault location algorithm. This can be obtained from the result of DFT on the raw data.

DFT is applied on one cycle data. Hence, the number of samples present in one cycle depends on the sampling frequency of the recorder. DFT in this manner is applied to the entire sample set with moving rate of the window as one sample. Hence, a fundamental RMS quantity is present corresponding to each sample in the set. This is done because the fault instant and prefault instant is unknown and has to be identified later. Else, DFT can be applied to a sample set starting with prefault and fault instant to determine the prefault and fault current/voltage for using in the fault location algorithm. This quantity is referred to as fundamental RMS quantity or as just voltage/current accordingly.

The algorithm proposed in the previous section is implemented in MATLAB to calculate prefault as well as fault current and fault voltage. These values obtained are then used in fault location algorithms to estimate the location of the fault.

# **3.4 TRANSMISSION LINE FAULT DATA FOR EVALUATING THE PROPOSED ALGORITHM FOR DETERMINING FAULT INSTANT AND PREFAULT INSTANT**

In this section, two transmission line fault data are considered to illustrate the process.

#### 3.4.1 Case 1: A Single-Line-to-Ground Fault

The first case taken for analysis is a transmission line fault on a 345 kV line which is 69.94 miles long and connects station A and station B as shown in Figure 3-2. From the event analysis performed by utility using data at station A, the report revealed that there was a single line-to-ground fault on the line creating around 6 kA of fault current on the B phase of the line. The actual location of the fault was at 15.33 miles from station A caused by buzzard droppings on the insulator. Table 3-1 summarizes the characteristics of the fault event along with the line impedance data.

Figure 3-2 : Transmission line fault

| Table 3-1 : Event ana | lysis | for | Case | 1 |

|-----------------------|-------|-----|------|---|

|-----------------------|-------|-----|------|---|

| Line Data                           | Fault Data                                    |

|-------------------------------------|-----------------------------------------------|

| Line Voltage $(kV) = 345$           |                                               |

|                                     | Fault Type = $BG$                             |

| Total Line Length (miles) = $69.94$ |                                               |

|                                     | Distance to fault from Station A (line miles) |

| Total Line Impedance:               | from event analysis $= 15.33$                 |

| R1 (ohms) = 3.9159                  |                                               |

| X1  (ohms) = 43.2536                |                                               |

| R0 (ohms) = 41.6944                 |                                               |

| X0 (ohms) = 122.9647                |                                               |

The relevant waveforms of the faulted line present in the fault records are shown in Figure 3-3. The sampling frequency of the fault record was 960 Hz. The first three

waveforms from top show the currents in phase A, B and C of the line respectively and the bottom three waveforms show the phase voltages of phases A, B and C respectively. Phase B current waveform clearly shows an increase in magnitude while phase B voltage waveform shows a sag which is indicative of a single line-to-ground fault on phase B.

Figure 3-3 : Phase voltage and current waveform of phase A, B and C for Case 1

#### 3.4.2 Case 2: A Line-to-Line Fault

The second case taken for analysis is a line-line fault involving B and C phases. The breakers protecting the circuit tripped and locked out because a tree fell on the line about 2.6 miles from station C. The breakers at both ends of the circuit had tripped, reclosed, and tripped back out. The faulted line is a 138 kV, 12.88-mile long line between station C and station D. The fault current was more than 20 kA. Table 3-2 summarizes the characteristics of the fault event along with the line impedance data.

Table 3-2 : Event analysis for Case 2

| Line data                                                                                                      | Fault Data                                                                  |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Line Voltage (kV) = 138<br>Total Line Length (miles) = 12.88                                                   | Fault Type = BC                                                             |

| Total Line Impedance:<br>R1 (ohms) = 1.4702<br>X1 (ohms) = 6.6083<br>R0 (ohms) = 7.8176<br>X0 (ohms) = 23.1480 | Distance to fault from Station 1 (line miles)<br>from event analysis = 2.64 |

Figure 3-4 shows the waveforms related to the faulted line present in the fault records. The sampling frequency of the fault record was 3840 Hz. The first three waveforms show the currents in phase A, B and C of the line. The first waveform is the current in phase A followed by current in phases B and C respectively. The last 3 waveforms show the phase voltage waveforms where the first waveform corresponds to phase A followed by phase B and C respectively. The swell in the current waveforms in phase B and C clearly indicate the presence of a line-to-line fault. It also clearly shows the circuit has tripped, reclosed and tripped back out. The actual location of fault for this event is at 2.64 miles from station C.

Figure 3-4 : Phase voltage and current waveform of phase A, B and C for Case 2

# **3.5** Evaluation of the Proposed Algorithm for Determining the Fault Instant and Prefault Instant

This section illustrates the proposed method and describes the results obtained from using the method on the two test cases mentioned previously. Simple and commonly used impedance-based fault location techniques such as Reactance method, Takagi method and Novosel method [2] [3] [13] [14] [15] are used to demonstrate the efficacy of the proposed method. The fault location results obtained by using the proposed method to get fault current and voltage is compared with the results obtained by using voltage and current data at other time intervals.

Case 1 is a single line-to-ground fault in phase B of the line (BG fault). The fault record has a total of 240 samples which includes prefault, fault and post-fault information. The sampling frequency of the recorder was 960 Hz, hence, there are 16 samples per cycle (60 Hz fundamental frequency). On applying DFT on once cycle data, we get 224 RMS current and voltage values (one for each nth sample as the starting sample and the sample set contains 1 cycle of data samples). The last 16 samples (or 1 cycle data) is omitted as the DFT will not contain data of 1 complete cycle. Furthermore, the last cycle data is usually post-fault data and has no useful information for fault location.

On sweeping through the calculated current values, it was observed that the current value corresponding to the 55th sample was thrice that of the current value corresponding to the 7th sample value (3 cycles correspond to 48 samples). Hence, the fault is considered to have started at the 55th sample. The value of current and voltage corresponding to the 7th sample was taken as prefault values. The fault existed for 41 samples (until the 95th sample). On applying the proposed method for identifying fault current and voltage, it was observed that the voltage and current had stabilized starting from the 68th sample. The prefault and fault current and voltage values were used in 3 impedance-based algorithms. Comparison between results obtained by using the proposed method and results obtained by taking the faulted cycle at several other different time instants are shown in Table 3-3. The actual fault location was at 15.33 miles from station A. It can be observed to taking data from other faulted cycles for estimating fault location.

|                                                            | At instant of<br>identification<br>of fault<br>inception | Half cycle<br>after fault<br>inception | Proposed<br>Method | One and a half<br>cycle after<br>fault inception | Two cycles<br>after fault<br>inception |

|------------------------------------------------------------|----------------------------------------------------------|----------------------------------------|--------------------|--------------------------------------------------|----------------------------------------|

| Sample number<br>of data obtained<br>for fault<br>analysis | 55                                                       | 63                                     | 68                 | 79                                               | 87                                     |

| Reactance (miles)                                          | 57.88                                                    | 20.38                                  | 15.40              | 14.23                                            | 12.90                                  |

| Takagi (miles)                                             | 59.64                                                    | 20.35                                  | 15.33              | 14.23                                            | 13.26                                  |

| Novosel (miles)                                            | 58.50                                                    | 20.30                                  | 15.25              | 14.23                                            | 13.11                                  |

Table 3-3 : Comparison of fault location results for Case 1

There are several sources of error while using impedance-based fault location methods [2]. Hence, impedance-based fault location may not accurately pinpoint the exact fault location but location estimates closer to the actual fault location is always better. This can be seen in Case 2. The fault location obtained using the proposed method gives a result closer to the actual fault location than fault location obtained using data from other fault instants as shown in Table 3-4.

The sampling frequency of fault record in Case 2 is 3840 Hz and the total number of samples is 7757. The fault is a line-line fault involving phases B and C. Hence, the line to line current and voltages of phase B and C are calculated instead of phase currents and voltages corresponding to each sample. Also, line-to-line currents and voltages are used in the fault location algorithms as well. On following the above procedure, the fault was identified to start at the sample number 1908. The voltages and currents of the sample number 1716 (3 cycles correspond to 192 samples) were taken as prefault voltages and currents. As the sampling frequency of this record was 4 times compared to 960 Hz, the criteria used for checking if the voltage and current has reached steady state is also altered accordingly. The criteria were changed such that the percentage change in calculated fundamental RMS current between successive sample data set should be within 0.25 percent and the percentage change in the calculated fundamental RMS voltage between successive sample data set should be within 0.75 percent (1/4 times the value used for 960 Hz). The sample number of data used for fault analysis derived using the proposed method is 1972. The actual fault location was 2.64 miles from Station A. The proposed algorithm gives a closer result to the actual fault location than that calculated by using data from other faulted cycles for the same impedance-based fault location methods.

|                                                            | At instant of<br>identification<br>of fault<br>inception | Half cycle<br>after fault<br>inception | Proposed<br>Method | Two cycles<br>after fault<br>inception | Two and a half<br>cycles after<br>fault inception |

|------------------------------------------------------------|----------------------------------------------------------|----------------------------------------|--------------------|----------------------------------------|---------------------------------------------------|

| Sample number<br>of data obtained<br>for fault<br>analysis | 1908                                                     | 1940                                   | 1972               | 2036                                   | 2068                                              |

| Reactance<br>(miles)                                       | 22.04                                                    | 9.57                                   | 3.11               | 3.13                                   | 3.13                                              |

| Takagi (miles)                                             | 23.87                                                    | 9.56                                   | 3.11               | 3.13                                   | 3.13                                              |

| Novosel (miles)                                            | _                                                        | 9.63                                   | 3.12               | 3.16                                   | 3.15                                              |

Table 3-4 : Comparison of fault location results for Case 2

The above results show that the proposed method is a suitable technique for obtaining the appropriate fault current and voltages. Having processed the fault record and obtained the fault current and voltages, they can be used in to estimate the fault location. The following chapters discuss model-based fault location process using reduced equivalent circuit.

# 4. AUTOMATED FAULT LOCATION USING REDUCED EQUIVALENT CIRCUIT FOR MODEL-BASED FAULT LOCATION APPROACH

The previous chapters had highlighted the need for an automated fault location method and an outline of the proposed automated fault location method using reduced equivalent circuit method. The working scheme and some of the advantages of using the proposed approach have also been discussed in the previous chapters. This chapter discusses in detail the implementation of the proposed approach.

First, the system model used for demonstrating the proposed approach is described followed by the procedure for formation of reduced equivalent circuits in OpenDSS. The modeling of different power system components in openDSS is also explained. This is followed by implementation of the proposed fault location approach using MATLAB.

# 4.1 SOFTWARE TOOLS USED

The approach is universal as explained in Chapter 2. Most of the present day commercially available power system packages have the capability to form equivalent circuits. Here, reduced equivalent circuits modeled in OpenDSS which are driven by MATLAB is used to find fault location. Hence, it is independent of the software used by utility in which they have their system model.

CAPE is a prominent software for power system protection engineering and is used widely by utilities across the world. To illustrate the proposed method, an example system model present in CAPE is used throughout the thesis for implementation, analysis and validation of the proposed method.

# 4.1.1: CAPE - Computer-Aided Protection Engineering

CAPE is a powerful tool developed for protection engineers dealing with high voltage transmission and distribution systems. CAPE has several modules for this purpose

such as Database Editor, Short-Circuit, One Line Diagram, Coordination Graphics, Relay Setting, Relay Checking, System Simulator, Line Constants and Power Flow [7] The hardware requirements for CAPE are simple. It runs on Windows PC and supports any Windows compatible printer.

CAPE uses the Short-Circuit Module for fault studies. The process of fault study is simplified by using the One-Line Diagram interface it provides. Along with the conventional fault types such as balanced three-phase, phase-to-phase (line-to-line), balanced two-phase-to-ground and one-phase-to-ground (single-line-to-ground) faults, CAPE allows the users to define a fault condition consisting of any connection among different phases and ground with fault impedance at any place on the network. Hence, real life fault conditions such as fallen conductors or simultaneous faults involving several buses with arbitrary impedances or current injections can be studied. Furthermore, CAPE has Short-Circuit Reduction Module which can reduce large circuit into a small equivalent circuit. The components of the reduced equivalent circuit exhibit the same characteristics as that it exhibited when it was part of the large circuit model.

CAPE provides the user with a variety of tools and options to model the network accurately and in detail. The fault analysis study can be made more accurate by providing precise initial system conditions rather than using a flat prefault voltage profile. The Power Flow module in CAPE can be used to give these initial conditions to Short-Circuit module.

As CAPE has the ability to model a particular system in great detail, the data conversion ability is of great importance as it allows CAPE to import data from several other software such ASPEN as well as export network data into similar formats. Though CAPE cannot be driven by an external software, the capability to export data accurately is used to obtain reduced equivalent circuit data to be modeled in OpenDSS.

# 4.1.2: OpenDSS - Open Distribution System Simulator

The Open Distribution System Simulator (*OpenDSS*, or simply, *DSS*) [16] is a comprehensive electrical system simulation tool. OpenDSS can perform a variety of RMS steady-state analysis. In addition, it supports many new types of analyses that are designed to meet future needs. OpenDSS is capable of performing power flow calculations and study harmonics, dynamics and faults in a power system.

OpenDSS is implemented as both a stand-alone executable program and a COM DLL designed to be driven from a variety of existing software platforms. For example, it can be driven entirely from an MS Office tool through VBA, or from any other 3<sup>rd</sup> party analysis program that can handle COM. OpenDSS is commonly driven by the familiar Mathworks MATLAB program. The COM interface also provides direct access to the text-based command interface as well as numerous methods and properties for accessing many of the parameters and functions of the simulator's models. Many of the results can be retrieved through the COM interface as well as from various output files. Output files are typically written in Comma-separated Value (CSV) format that can be imported easily into other tools for post processing. This provides powerful external analytical capabilities as well as excellent graphics for displaying results, hence, making it is easier to understand and analyze the results.

#### **4.1.3: MATLAB**

MATLAB [17] is a very common software used by engineers and scientists worldwide to analyze and design systems. MATLAB offers a plethora of tools to choose from to perform a variety of operations. The MATLAB platform has been optimized for solving engineering and scientific problems. The matrix-based MATLAB language makes it is easy to express computational mathematics. Built-in graphics make it easy to visualize and gain insights from data. A vast library of prebuilt toolboxes helps users to implement algorithms effortlessly and efficiently.

# 4.2 SYSTEM MODEL USED

For the purpose of analysis and verification of the proposed algorithm, the example circuit available in CAPE called "cape.gdb" is used. The database file of the test system is a repository of all the network data of the test system. Several reduced equivalent circuits will be made from this circuit model and fault analysis will be performed to demonstrate the capabilities of model-based fault location using reduced equivalent circuit algorithm.

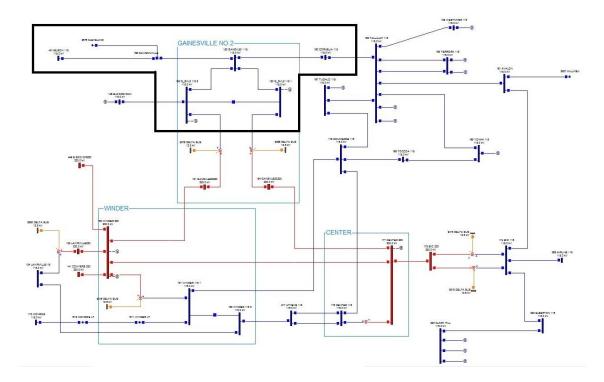

This sample circuit has 103 buses, 187 branches, 26 sets of lines with mutual coupling and 2 sets of bus ties present. Figure 4-1 shows the one line diagram representation of the circuit.

Figure 4-1 : One line diagram of cape.gdb

#### 4.3 FORMATION OF REDUCED EQUIVALENT CIRCUITS IN CAPE

The advantages of forming reduced equivalent circuit have been discussed in Chapter 2. Most commercial power system analysis software offer a network reduction module. This section shows how to form reduced equivalent network using CAPE.

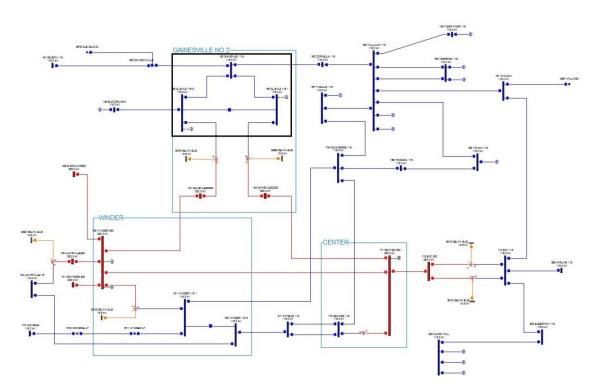

CAPE uses two methods of network reduction. In the first method, CAPE completely reduces the specified set of buses, leading to an equivalent network with a minimum number of buses but with possibly many additional equivalent sources and impedances. In the second method, CAPE retains some extra buses in an attempt to minimize the number of equivalent branches created. [18]. Throughout the thesis, the first method of circuit reduction is used.

The steps to reduce the network are as follows:

- 1. Load the database file into CAPE

- Select the Short Circuit Reduction module and create a new bus set as shown in Figure 4-2. This bus set may be the set of buses you want to reduce or the set of buses you want to retain. Add the set of buses you want to reduce/retain to that bus set.

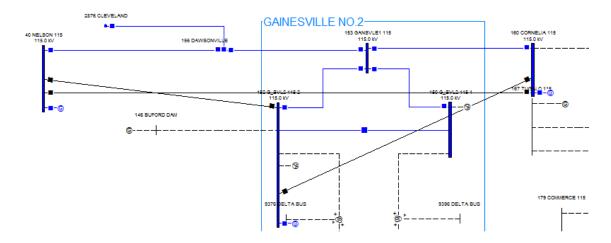

- 3. Once the bus set is defined, select reduce set if you want to remove the selected buses from the system or select retain to retain the selected set of buses and remove all the other buses. A sample circuit after network reduction is shown in Figure 4-3 where only certain buses near Gainesville station are retained and all the other buses are removed. It can also be observed that several new branches and generators have been added to the existing set of lines and generators to be able to replicate the retained system's behavior before network reduction.

Figure 4-2 : Network reduction using CAPE – 1

Figure 4-3 : Network reduction using CAPE – 2

4. After the system has been reduced, the network data can be saved as a new database file which can be used as and when required. The reduced network data is also exported to build reduced equivalent circuits in OpenDSS.

# 4.4 MODELING IN OPENDSS

This section presents the data exported by CAPE and the data required by OpenDSS to model the components of a power system. This section discusses four major components commonly encountered while forming reduced equivalent circuits for the purpose of fault location. These are generators, transmission lines, tie bus and mutual coupling.

OpenDSS does not require the list of buses to be defined at the beginning. If a bus name is not present at the time of creating any power system component, a new bus is created with that name.

# 4.4.1 Generator

CAPE exports the following details for a generator: bus voltage, bus name and bus number to which the generator is connected, MVA rating of the generator and positive-, negative- and zero-sequence impedance parameters of the generator.

A generator model can be created in OpenDSS either by defining its short-circuit capacity or by directly defining its impedance parameters. In this case, the generators are defined using the impedance parameters as all the required impedance data are available. The other requirements to create a generator in OpenDSS are the bus to which the generator is connected, the base kV of the generator, per unit value of the generated voltage, phase angle shift (if present), the frequency of the generator and the number of phases present (which is 3 by default).

#### 4.4.2 Transmission Line

CAPE exports the following details for branches or transmission lines: bus number and bus name of from bus and to bus, operating line voltage and impedance parameters of the line. Transmission lines are simple to define in OpenDSS. The above parameters are sufficient to define a line in OpenDSS. The line length is taken as unity while defining in OpenDSS as CAPE is made to export total impedance of the line and not impedance per unit length so that it is easy to implement sliding fault analysis. Fault location is represented in terms of percentage distance of the total line length from a bus at one end of the line.

To create a fault at distance 'x' per unit (pu) from Bus A on a transmission line of length '1 (one)' pu in OpenDSS, a temporary bus has to be created at the point of fault on the transmission line between the two buses. This temporary bus splits the transmission line into two lines, one with length 'x' and other with length '1-x' as shown in Figure 4-4.

Figure 4-4 : Transmission Line Fault in OpenDSS

The ability of OpenDSS to be driven by MATLAB gives the advantage of being able to vary 'x' and obtain results for each case without any manual intervention to get fault data for faults at various distances.

#### 4.4.3 Bus Tie

A tie breaker acts as a coupler between feeders for circuits with two feeders or more. During failure of any one feeder, the power is fed through the second feeder and tie breaker. Bus tie data in CAPE are from bus, to bus and status of breaker which is open or closed.

In OpenDSS, a bus tie which is closed is modeled as a line with almost zero impedance between the two buses which acts as a closed switch between two buses. When a bus tie is open, the line is not modeled at all. Hence, it is like an open switch.

# **4.4.4 Mutual Coupling**

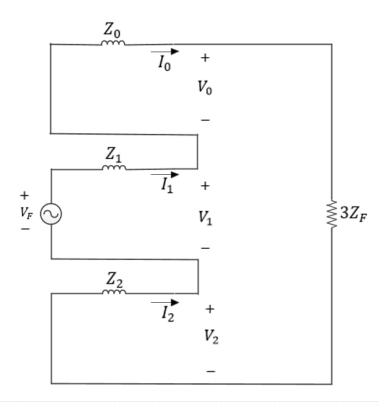

Mutual coupling between transmission lines is a common phenomenon that occurs when two lines travel close to each other, for example, in the same tower. As a result, it affects the transmission line impedance and the fault characteristics of the system. Hence, two parallel lines which are affected by mutual coupling cannot be modeled in the similar manner as normal transmission lines explained in Section 4.4.2.

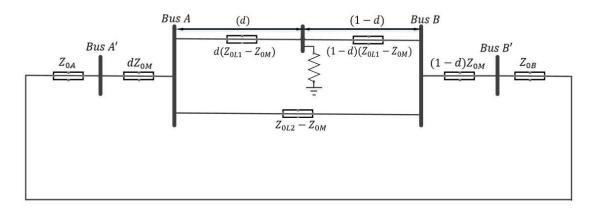

Mutual coupling mainly affects the zero-sequence parameters in a transmission line [19]. Hence, its effect can be observed majorly in unbalanced ground faults and not in three-phase faults. The positive- and negative-sequence circuits are unaffected and need not be modified. In CAPE, the mutual coupling data are given as follows: from and to bus data of the first line, from and to bus data of the second line and mutual impedance parameters between the two lines.

Figure 4-5 : Zero-sequence circuit without mutual coupling

Figure 4-6 : Effect of mutual coupling on zero-sequence circuit

In OpenDSS, as the positive- and negative-sequence line parameters are unaffected, the positive- and negative- sequence line impedances are not modified and modeled like two normal transmission lines discussed in Section 4.4.2. The modeling of zero-sequence circuit showing the effect of mutual coupling is presented in Figure 4-6 [20].

Once again, the ability of OpenDSS to be driven by MATLAB gives the advantage of being able to vary the modeling of transmission lines and its parameters according to our requirement without any manual intervention. When mutual coupling data is read by MATLAB, the zero-sequence parameters of the corresponding lines are changed as well as the way the lines are modeled are modified from the circuit diagram shown in Figure 4-5 to the circuit diagram shown in Figure 4-6. The zero-sequence parameter of line 1 is changed from  $Z_{0L1}$  to  $Z_{0L1}$ - $Z_{0M}$  and zero-sequence parameter of line 2 is changed from  $Z_{0L2}$  to  $Z_{0L2}$ - $Z_{0M}$ . Two new buses are introduced (Bus A' and Bus B') at each end of the transmission line between the ends of the transmission line and the rest of the reduced equivalent circuit as shown in Figure 4-6. A line of impedance  $dZ_{0M}$  is introduced between Bus A and Bus A' and another line of impedance  $(1-d)Z_{0M}$  is introduced between Bus B and Bus B' where 'd' is the distance of the fault from Bus A. When there is no fault, 'd' is zero.  $Z_{0A}$  and  $Z_{0B}$  are source impedances on the sides of Bus A and Bus B respectively. The rest of the reduced equivalent circuit around the mutually coupled line is represented in the circuit diagram shown in Figure 4-6 using  $Z_{0A}$  and  $Z_{0B}$ .

# 4.5 IMPLEMENTATION OF PROPOSED APPROACH IN MATLAB

In Chapter 2, the usefulness of MATLAB being able to drive OpenDSS has been discussed. This section discusses the how the proposed algorithm is implemented using MATLAB and OpenDSS.

Preprocessing of fault records is a key step as described in Chapter 3. The outcome of the above process gives the fault voltage and fault current of the fault event. Using the DFR data, the location of the fault recorder and the appropriate equivalent circuit is selected. The above steps have been accomplished using MATLAB. MATLAB polls the folder where fault record arrives at regular intervals to process new fault records as and when they reach the monitored folder. This is followed by the preprocessing steps described in Chapter 3.

The required equivalent circuit data exported by CAPE is available in ".csv" file format. This data is read by MATLAB and dynamically creates the circuit in OpenDSS. Additionally, MATLAB is programmed to place monitors at all the ends of all the lines to obtain the current and voltage measurement which can be used for analysis other than fault location. A sliding fault is placed on each line and the voltages and currents corresponding to each fault scenario at all the locations being monitored are available. The resolution of the sliding fault can be varied according to the requirement, for example, the sliding fault can be programmed to create a fault at every 10% of the total line distance or it can be programmed to create a fault at every 5% of the total line distance. Similarly, the above sliding fault analysis can be performed with various fault resistances as well. The voltages and current measurements obtained for different fault scenarios are made into a table for simplifying the analysis.