# Localization and Detection of Bond Wire Faults in Multi-chip IGBT Power Modules

Cuili Chen¹, Volker Pickert¹, Maher Al-Greer², Chunjiang Jia³, Chong Ng³

<a href="mailto:c.chen22@ncl.ac.uk">c.chen22@ncl.ac.uk</a>, <a href="mailto:volker.pickert@ncl.ac.uk">volker.pickert@ncl.ac.uk</a>, <a href="mailto:m.al-greer@tees.ac.uk">m.al-greer@tees.ac.uk</a>, <a href="mailto:chunjiang.jia@ore.catapult.org.uk">c.chunjiang.jia@ore.catapult.org.uk</a>, <a href="mailto:chunjiang.jia">c.chunjiang.jia@ore.catapult.org.uk</a>, <a href="mailto:chunjiang.jia">c.chunjiang.jia</a>, <a href="mailto:chunjiang.jia">c.chunjiang.

<sup>1</sup>School of Engineering, Newcastle University, Newcastle Upon Tyne, UK

<sup>2</sup>School of Science Engineering and Design, Teesside University, Tees Valley, Middleborough, UK

<sup>3</sup>Offshore Renewable Energy Catapult, Newcastle upon Tyne, UK

Abstract—Multi-chip Insulated Gate Bipolar Transistor (mIGBT) power modules (PMs) degrade over power cycling. Bond wire lift-off is one of the major failure modes. This paper presents a technique to diagnose bond wire lift-off by analyzing the on-state voltages across collector and emitter terminals and the voltages across collector and Kelvin emitter terminals. The proposed method can indicate the first lift-off out of 37 bond wires in a mIGBT. The main novelty of the proposed technique is that it can locate the chip that has bond wire lift-off(s). In addition, the temperature dependence of the proposed approach is negligible. The paper describes the proposed technique in detail and shows results and discussions based on practical tests which are carried out on two mIGBT PMs with different packages.

Index Terms— Multi-chip insulated gate bipolar transistor, bond wire lift-off, fault diagnosis.

## I. INTRODUCTION

The Insulated Gate Bipolar Transistor (IGBT) is one of the most commonly used semiconductors in power electronics. Today the power capability of a single IGBT power module (PM) has been boosted up to kiloampere [1, 2]. These IGBT PMs are realized through multi-chip paralleled package to achieve the required high current level. However, the increase in paralleling chips within one package will introduce severe thermal stress on the module and as such affects its lifetime. It is reported that about 21% of the power converter failures are attributed to semiconductors [3]. Solder fatigue and bond wire failures are reported as the most common failures that occur over lifetime [4-6]. This paper is going to focus on the bond wire failure.

A large number of research papers have been published, proposing different detection methods for bond wire lift-off [7-14]. Techniques proposed have been applied either intrusively on opened PMs with direct access to bond wires or non-intrusively on unopened package measuring voltages and currents at available terminals: the collector C, the emitter E, the gate G, the auxiliary emitter AE which provides the return path for the gate current, and the Kelvin emitter KE which acts as sensing point if provided.

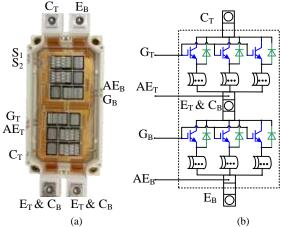

Fig. 1a shows the layout of the terminals in a half-bridge IGBT PM, Infineon FF600R17ME4, which has three IGBT chips and three anti-parallel diodes in parallel for the top switch and the same design for the bottom switch. In Fig. 1a, the terminals of the top switch are labeled by the index T and the terminals of the bottom switch are labelled by the index B. As in most standard PMs illustrated in Fig. 1a, the collector of the top IGBT chips is soldered onto the Direct Copper Bonded (DCB) layer that is connected with the C<sub>T</sub> terminal. The

collector of the bottom chips is also soldered to the DCB but connected to  $C_B$ . The emitter of the IGBT chips is attached to the DCB through bond wires. The emitter terminals for load current are  $E_T$  and  $E_B$  for the top and the bottom switch individually. In the half-bridge topology,  $E_T$  and  $C_B$  share the same terminal.  $G_T$  and  $G_B$  are the gate terminals for the top and the bottom switch respectively.  $AE_T$  and  $AE_B$  terminals are connected via wires with the corresponding emitter tracks for  $E_T$  and  $E_B$  on the DCB layer. Both terminals provide the current return paths for the gate drives. Fig. 1b shows the schematic of the PM along with the terminals.

Fig. 1. Infineon 1.7 kV 600A half-bridge IGBT PM (FF600R17ME4): (a) Interior view, (b) Terminal illustration.

There are seven signal terminals, as shown in Fig. 1a, along the edge of the PM frame ( $G_T$ ,  $AE_T$ ,  $C_T$ ,  $AE_B$ ,  $G_B$ ,  $S_1$ , and  $S_2$ ) in the form of pins, where  $S_1$  and  $S_2$  are two terminals of the DCB temperature sensor. The position of these terminals is subject to manufacturer preferences and DCB layout.

In literatures [7-14], all of the five terminals (C, E, G, AE, and KE) have been used for bond wire degradation detection either by directly monitoring an electrical signal (intrinsic signature) that will change with bond wire lift-off or by stimulating and monitoring a responding signal (induced signature) where the responding signal correlates with bond wire lift-off. Table I summaries recent contributions in detecting bond wire lift-off.

# A. Intrinsic signatures

Intrinsic signatures are obtained by direct measurement of either the voltage across two of the five terminals or the current through any terminal.

Table I Comparison of existing techniques for bond wire state estimation

| Detection<br>type  | Involved terminals | Signatures                                     | Number of IGBT chips each switch | Total number of bond wires in one switch | Number of first detected bond wires lift-off – sensitivity        |

|--------------------|--------------------|------------------------------------------------|----------------------------------|------------------------------------------|-------------------------------------------------------------------|

|                    | С-Е                | V <sub>CE(on)</sub> [7]                        | 1                                | 6                                        | First – 20mV increase                                             |

|                    |                    | $V_{\text{CE(on)}}$ at the inflexion point [8] | 1                                | 5                                        | Second – 9 mV increase                                            |

|                    |                    | $R_{\text{CE(on)}}[9]$                         | 2                                | 8                                        | Second – $0.1 \text{ m}\Omega$ increase                           |

| Intrinsic          |                    | $\Delta V_{\text{CE(turn-off)}}$ [10]          | 2                                | 24                                       | Fourth – 20 V increase                                            |

| signatures         | CAE                | $V_{	ext{G-AE}}$ [11]                          | 2                                | 12                                       | Sixth – detects only if all bond wires are detached from one chip |

|                    | G-AE               | $I_{\rm G}$ [12]                               | 2                                | 12                                       | Sixth – detects only if all bond wires are detached from one chip |

|                    | KE                 | Sense point [13]                               | 2                                | 4                                        | First – 700 mV increase                                           |

| Induced signatures | Open<br>module     | Temperature [14]                               | 1                                | 4                                        | First – 0.5 °C increase                                           |

#### 1) Signatures from Collector (C) and Emitter (E)

The on-state voltage  $V_{\rm CE(on)}$  measured across the terminals C and E has been widely exploited to monitor the bond wire state [15, 16]. However,  $V_{\rm CE(on)}$  has also been popularized as a Thermo-Sensitive Electrical Parameter (TSEP) because of its linear relationship with temperature variation. Therefore, the bond wire state diagnosis based on  $V_{\rm CE(on)}$  is influenced by the temperature of the chips. This dependency has been studied extensively.

For instance, authors in [7] proposed to measure  $V_{\text{CE(on)}}$  under sensing current (100 mA) as well as loading current (50 A) to decouple the influence of the virtual junction temperature  $T_{\text{vj}}$  and bond wire lift-off. This method has now been well established [5, 6, 17]. In [8, 18, 19], the influence of  $T_{\text{vj}}$  is eliminated by taking advantage of the inflexion point at which the temperature dependence of  $V_{\text{CE(on)}}$  is negligible.

On-state resistance  $R_{\text{CE(on)}}$  is the combination of  $V_{\text{CE(on)}}$  and  $I_{\text{C}}$  and has also been investigated as bond wire lift-off indicator [9, 20]. Advanced algorithms such as the recursive least square algorithm is used to exclude the impact from  $T_{\text{vi}}$ .

In on-line operation, the overshoot of  $V_{\text{CE}}$  during the turn-off transient, denoted as  $\Delta V_{\text{CE(turn-off)}}$  in Table I, has also been reported for bond wire lift-off prediction [10].

# 2) Signatures from Gate (G) and Auxiliary Emitter (AE)

In [11, 12, 21-23], voltage  $V_{G-AE}$  and gate peak current  $I_G$  during the turn-on transient were proposed. These methods can only detect a complete chip failure meaning all bond wires have been lifted from one IGBT chip.

#### 3) Signatures from Kelvin Emitter (KE)

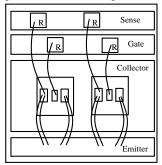

In [13], sensing bond wires were introduced which were bonded across the DCB. As such additional tracks were formed on the DCB to connect the sensing bond wires with corresponding KE terminals. The implementation of the approach is depicted in Fig. 2. The DCB layer of the power module is redesigned to introduce the sensing terminal via the additional copper track, the additional sensing resistor, and the additional bond wires. The bond wires are used to connect the emitter side of the IGBT chip to the sensing point via the sensing resistor. The equivalent circuit is shown in Fig. 2. In the

case a bond wire in one of the IGBT chip is lifted, the voltages measured via the sensing bond wire will shift. However, in order to include sensing bond wires, the DCB of the PM has to be redesigned. In addition, large resistive sense resistors are required to reduce the power loss caused by the measurement.

Fig. 2. Implementation of the sensing bond wires by redesign of the DCB layer (left) and its equivalent circuit diagram (right) [13].

## B. Induced signatures

In order to detect induced signatures, voltage or current signals must be injected first. The response from these signals can then be measured.

Authors in [14] proposed applying electromagnetic induction thermography to open PMs. In this method, the pulsed electromagnetic field produces eddy currents. The temperature distribution, as the response of the eddy current, changes when there is bond wire lift-off. This is used to detect bond wire states.

## C. Research gap

In principal, each technique described in Table I is able to detect bond wire lift-off. However, for most of them, the ratio of the earliest detection of failure to the total bond wire number is between two out of five to one out of six. Therefore, they are not suitable for detecting early bond wire lift-offs for mIGBT PMs with large number of bond wires. In addition, locating the bond wire lift-off has not been reported in any of these methods.

## D. Contribution and structure of this paper

This paper proposes a method to detect and locate the early lifted bond wires in mIGBT PMs. The method makes use of the well-known on-state voltage measurement across C and E. Meanwhile, voltages across terminals C and KE are measured. All measurement results are processed to identify the number of lifted bond wires and locate these lifted wires.

This paper is organized as follows. The proposed technique is described in Section II. The experimental set-up is presented in Section III including practical results on an Infineon IGBT module with three IGBT chips for each switch. The fault diagnosis regarding bond wire lift-off detection and location is presented in Section IV. A repeat of the test is carried out on a Dynex mIGBT PM and results are described in Section V to demonstrate that the method is applicable to PMs with different layouts. Section VI concludes the work.

## II. METHODOLOGY OF PROPOSED TECHNIQUE

The proposed technique is demonstrated on the Infineon power module FF600R17ME4 using its bottom switch.

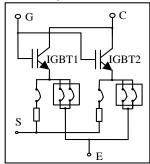

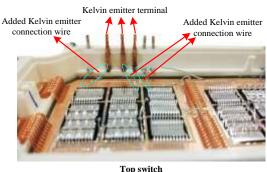

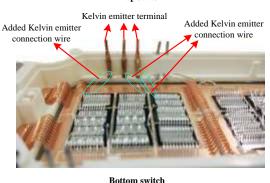

# A. Modification for Kelvin emitter connection

The Kelvin connection is realized by introducing additional terminals as shown in Fig. 3. Thin copper wires, 50  $\mu m$  in diameter, are used to connect the emitter side of the IGBT chip with the added Kelvin pins which are glued against the frame of the IGBT module. In this prototype, two wires are used for each IGBT chip. The Kelvin pins are copper. Compared with the technique in [13], the technique proposed in this paper does not need any modification to the DCB layer. The extra Kelvin connection can be constructed with only limited modification to the mIGBT module.

Fig. 3. Half bridge IGBT module with added pins for Kelvin emitter connection.

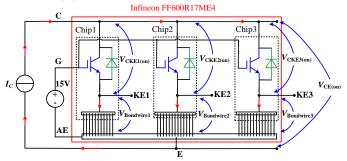

## B. Schematic for experiment setup

Fig. 4 illustrates the experimental setup for testing the bottom switch of FF600R17ME4 by showing the exact number of bond wires per chip. Three KE terminals (KE1, KE2, and KE3) are also introduced in addition to the existing four terminals C, AE, E, and G. Introduction of three additional terminals allows the measurement of seven voltages, three voltages across the three chips:  $V_{\text{CKE1(on)}}$ ,  $V_{\text{CKE2(on)}}$ ,  $V_{\text{CKE3(on)}}$ ; three voltages across the bond wires connected to each IGBT chip:  $V_{\text{Bondwire1}}$ ,  $V_{\text{Bondwire2}}$ ,  $V_{\text{Bondwire3}}$ ; and the voltage across C and E:  $V_{\text{CE(on)}}$ .

Fig. 4. Schematic of on-state voltage measurement for FF600R17ME4.

The KE terminals KE1, KE2, and KE3 are directly bonded with the corresponding emitters of the IGBT chips as shown in Fig. 3. The voltages  $V_{\rm CKE1(on)}$ ,  $V_{\rm CKE2(on)}$ , and  $V_{\rm CKE3(on)}$  are measured across C and KE1, KE2, and KE3 respectively representing the on-state voltages of the corresponding chips.

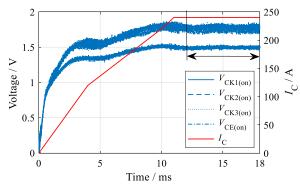

Fig. 5. Collector current and on-state voltage waveforms upon current injection at  $T_{vi}$ =46 °C.

Fig. 5 is an example of the measurement at  $T_{\rm vj}$ =46 °C. The collector current is controlled by the TopCon power source. The current rises to 240A in a step by step approach to compromise with the limitation of the TopCon device and to avoid overshot during the injection. Fig. 5 shows also the on-state voltages  $V_{\rm CKE1(on)}$ ,  $V_{\rm CKE2(on)}$ ,  $V_{\rm CKE3(on)}$ , and  $V_{\rm CE(on)}$ .

In these tests, each measurement is repeated twice. The RMS values of voltage measurement in the region highlighted with arrow are the on-state voltage for each measurement. The average value of the two measurements are used as the final voltage measurements. The final voltage measurements are used in the plot like Fig. 9.

# C. $V_{CKE(on)}$ and $V_{CE(on)}$

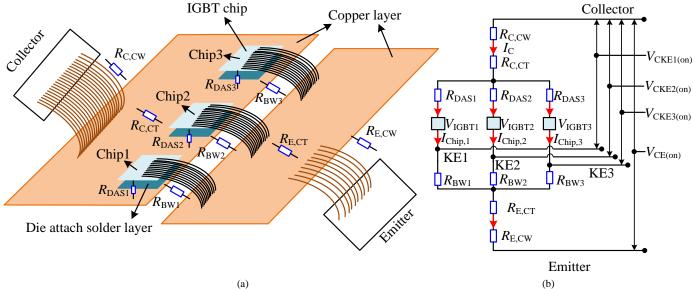

The C-E circuitry of the bottom switch in Fig. 3 is exhibited in Fig. 6a. All the influential parts are displayed. The collector terminal is linked to the copper layer via the copper wires. The collector copper wire are denoted as  $R_{\rm C,CW}$ . The collector

copper track is represented by  $R_{\text{C,CT}}$ . IGBT chips are soldered onto the copper layer. This solder layer is considered as pure resistance and the corresponding resistors are represented as  $R_{\text{DAS1}}$ ,  $R_{\text{DAS2}}$ , and  $R_{\text{DAS3}}$  for Chip1, Chip2, and Chip3 respectively. The voltages across the IGBT chip collector pad and emitter pad are denoted as  $V_{\text{IGBT1}}$ ,  $V_{\text{IGBT2}}$ , and  $V_{\text{IGBT3}}$  for the three IGBT chips. The emitter pad of the IGBT chip is connected to the emitter copper layer via bond wires. Then, copper wires are used to connect the emitter copper track with the emitter terminal. The resistors of the bond wires are presented by  $R_{\text{BW1}}$ ,  $R_{\text{BW2}}$ , and  $R_{\text{BW3}}$  for the three chips. The emitter copper track and emitter copper wires are pure resistance and denoted as  $R_{\text{E,CT}}$  and  $R_{\text{E,CW}}$  respectively.

Fig. 6b depicts the equivalent diagram of the C-E circuitry.  $V_{\text{CKE(on)}}$  and  $V_{\text{CE(on)}}$  can be derived as below. It can be noted that the difference between  $V_{\text{CKE(on)}}$  and  $V_{\text{CE(on)}}$  is the voltage across the bond wires, emitter copper track, and emitter copper wires.

$$V_{CKE,i(on)} = I_C R_{C,CW} + I_C R_{C,CT} + I_{Chip,i} R_{DAS,i} + V_{IGBT,i}$$

where  $i=1,2,3$ . (1)

$$V_{CE(on)} = I_C R_{C,CW} + I_C R_{C,CT} + I_{Chip,i} R_{DAS,i} + V_{IGBT,i} + I_{Chip,i} R_{BW} + I_C R_{E,CW} + I_C R_{E,CT}$$

(2)

Note, as  $R_{DAS,i}$ ,  $V_{IGBT,i}$ , and  $R_{BW,i}$  are in parallel in (2), i is either only 1 or only 2 or only 3.

Fig. 6. (a) Illustration about components in the C-E and C-KE path. (b) Equivalent circuitry between C-E.

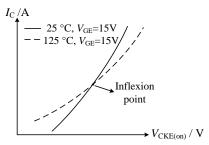

Fig. 7 shows the forward characteristic of an IGBT chip at constant gate emitter voltage  $V_{\rm GE}$ . The figure shows that  $V_{\rm CKE(on)}$  is non-linear and influenced by the collector current  $I_{\rm C}$  and  $T_{\rm vj}$ . Above the inflexion point,  $V_{\rm CKE(on)}$  at a particular current level rises at rising  $T_{\rm vj}$  and below the inflexion point  $V_{\rm CKE(on)}$  declines at rising  $T_{\rm vj}$ .

Fig. 7. Forward characteristic of an IGBT chip

Since the three IGBT chips are not exactly the same, each has its own on-state forward characteristic, therefore:  $V_{\text{CKE1(on)}} \neq V_{\text{CKE2(on)}} \neq V_{\text{CKE3(on)}}$ .

Parallel connected bond wires attached to an IGBT chip can be described with an equivalent resistance  $R_{0,i}$  at  $T_0$  and its temperature coefficient is  $\beta_i$ , where i is the chip number (i=1,2,3). Thus, the voltage across the bond wires of chip i is:

$$V_{BW,i} = R_{BW} I_{Chip,i} = (R_{0,i} + \beta_i (T_{vj} - T_0)) I_{Chip,i}$$

(3)

The on-state voltage  $V_{\text{CE(on)}}$  can be described as given in (4),

(5) and (6)

$$V_{CE(on)} = V_{CKE1(on)} + I_C R_{E,CW} + I_C R_{E,CT} + V_{BW1}$$

(4)

$$V_{CE(on)} = V_{CKE2(on)} + I_C R_{E,CW} + I_C R_{E,CT} + V_{BW2}$$

(5)

$$V_{CE(on)} = V_{CKE3(on)} + I_C R_{E,CW} + I_C R_{E,CT} + V_{BW3}$$

(6)

Since  $I_{\rm C}$ ,  $R_{\rm E,CT}$ , and  $R_{\rm E,CW}$  does not change upon bond wire lift-off, it is clear that if the bond wire voltage of chip i decreases the corresponding on-state voltage of chip i must increase and vice-versa. This relationship can be used to determine bond wire conditions.

# D. $V_{CKE(on)}$ and $V_{CE(on)}$ change in the case of bond wire lift-off

In order to illustrate the above on an example, it is assumed that one bond wire has lifted from Chip1 in Fig. 4. The IGBT switch is in on-state by applying +15V. The collector current is controlled by the DC current source. In this case one bond wire is lifted from Chip1, the equivalent resistance of the bond wires connecting to Chip1 will increase. Consequently, the collector current  $I_{\text{Chip1}}$  flowing through Chip1 will decrease. In order to maintain the same current level from the DC current source, collector currents  $I_{\text{Chip2}}$  and  $I_{\text{Chip3}}$  flowing through the other two chips will increase respectively. As a result,  $V_{\text{CKE1(on)}}$ ,  $V_{\text{CKE2(on)}}$ , and  $V_{\text{CKE3(on)}}$  will change in different ways as indicated in (7).

$$V_{CKE1(on)} \downarrow, V_{CKE2(on)} \uparrow, V_{CKE3(on)} \uparrow$$

(7)

Accordingly, the bond wire voltages vary as below:

$$V_{BW1} \uparrow, V_{BW2} \uparrow, V_{BW3} \uparrow$$

(8)

Despite individual voltage variations, the voltage  $V_{\text{CE(on)}}$ , summation of  $V_{\text{BW},i}$  and  $V_{\text{CKE},i(\text{on})}$ , always goes up when there is bond wire lift-off. The alterations of these voltages are summarized in Table II.

Table II Voltage variation in the case of one bond wire lift-off in Chip1

| Chip  | $V_{ m CKE(on)}$                  | $V_{\mathrm{CE(on)}}$ |

|-------|-----------------------------------|-----------------------|

| Chip1 | $V_{\mathrm{CKE1(on)}}\downarrow$ | 1                     |

| Chip2 | $V_{\mathrm{CKE2(on)}} \uparrow$  | 1                     |

| Chip3 | $V_{\mathrm{CKE3(on)}} \uparrow$  | <b>↑</b>              |

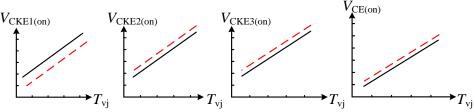

Fig. 8. On-state voltage variation in the case of bond wire lift-off in Chip1. Solid line: Healthy. Dashed line: Lift-off in Chip1.

$V_{\rm CKE1(on)}, V_{\rm CKE2(on)}, V_{\rm CKE3(on)},$  and  $V_{\rm CE(on)}$  are estimated and visualized in Fig. 8 where each voltage is shown as a function of  $T_{\rm vj}$ . It should be pointed out that the collector current following through the IGBT switch is constant. With the help of Fig. 8, the following general statements can be concluded:

- V<sub>CKE(on)</sub> decreases when the corresponding chip

has lost a bond wire and V<sub>CKE(on)</sub> increases for the

remaining chips.

- $V_{\text{CE(on)}}$  will always increase as bond wire lift-off.

These statements form the base of the new proposed bond wire detection and location technique.

# E. Fault detection and location without the knowledge of $T_{vj}$

So far the knowledge of  $T_{vj}$  is required for the proposed technique. The following section illustrates how bond wire states can be predicted without the knowledge of  $T_{vj}$ .

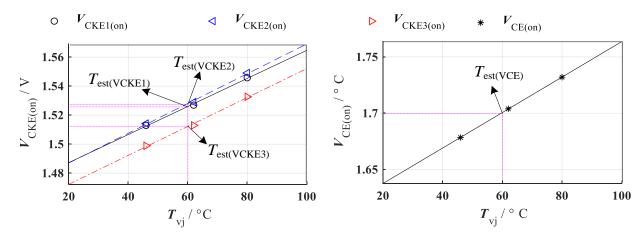

Fig. 9 shows the voltage-temperature characteristics ( $V_{\text{CKE}i(\text{on})}$  and  $V_{\text{CE(on)}}$ ) of FF600R17ME4 PM measured at  $I_{\text{C}}$ =240A and  $V_{\text{GE}}$ =15V. Fig. 9 is extracted from Fig. 12 and all four characteristics represent the baselines for a healthy PM.

Fig. 9.  $V_{\text{CKE1(on)}}$ ,  $V_{\text{CKE2(on)}}$ ,  $V_{\text{CKE3(on)}}$ , and  $V_{\text{CE(on)}}$  baselines at  $I_{\text{C}} = 240$  A and  $V_{\text{GE}} = 15$ V representing a healthy PM.

# Scenario 1: Healthy condition

At healthy condition, for example as shown in Fig. 9, each measured voltages  $V_{\text{CKE1(on)}}=1.525\text{V}$ ,  $V_{\text{CKE2(on)}}=1.527\text{V}$ ,  $V_{\text{CKE3(on)}}=1.511\text{V}$ , and  $V_{\text{CE(on)}}=1.701\text{V}$  will estimate the same temperature of 60°C.  $T_{\text{vj}}$  is commonly treated as the global temperature [24-26] and as such it can be described as (9).

$$T_{est(V_{CKE_1})} = T_{est(V_{CKE_2})} = T_{est(V_{CKE_3})} = T_{est(V_{CE})} = T_{vj}$$

(9)

where  $T_{\rm est(VCKE1)}$ ,  $T_{\rm est(VCKE2)}$ ,  $T_{\rm est(VCKE3)}$ , and  $T_{\rm est(VCE)}$  are the estimated temperatures from the measured voltages  $V_{\rm CKE1(on)}$ ,  $V_{\rm CKE2(on)}$ ,  $V_{\rm CKE3(on)}$ , and  $V_{\rm CE(on)}$  respectively.

# Scenario 2: Bond wire lift-off at Chip1

If a bond wire has lifted, the base line shifts away from the healthy baseline. This is shown in Fig. 10 where a new line is added for Chip1 but shifted under the healthy baseline. The new line results that  $T_{\text{est(VCKE1)}} \neq T_{\text{vj}}$ . In fact,  $T_{\text{vj}}$  becomes larger than  $T_{\text{est(VCKE1)}}$ .

$$T_{est(V_{CKE1})} < T_{vj} \tag{10}$$

From the previous findings, we know that the baselines for  $V_{\text{CKE2(on)}}$ ,  $V_{\text{CKE3(on)}}$ , and  $V_{\text{CE(on)}}$  shift upwards. As such it can be derived as (11). The shift for  $V_{\text{CE(on)}}$  is shown in Fig. 10. The on-state voltage of Chip2 and Chip3 follow the same tendency.

Fig. 10. Prediction change in the case of bond wire lift-off in Chip1 at  $I_C = 240$  A. Dotted line in the left diagram: variation of  $V_{\text{CKEI}(\text{on})}$  at bond wire lift-off. Dotted line in the right diagram: variation of  $V_{\text{CE}(\text{on})}$  at bond wire lift-off.

$$\begin{split} T_{est(V_{CKE2})} &> T_{vj} \\ T_{est(V_{CKE3})} &> T_{vj} \\ T_{est(V_{CE})} &> T_{vj} \end{split} \tag{11}$$

Equation (12) shows the difference between the estimated temperature of each chip and the estimated temperature based on  $V_{\rm CE(on)}$ . The estimated temperature differences are deployed to determine the number of bond wire lift-off and the location of the lift-off.

$$\Delta T_{est1} = |T_{est(V_{CKE1})} - T_{est(V_{CE})}|$$

$$\Delta T_{est2} = |T_{est(V_{CKE2})} - T_{est(V_{CE})}|$$

$$\Delta T_{est3} = |T_{est(V_{CKE3})} - T_{est(V_{CE})}|$$

(12)

# F. Influence of the solder layer, copper track and copper wire

This section discusses the influence of the solder layer, copper track and copper wire on the estimation of bond wire lift-off. To describe the linear relationship between  $V_{\rm CE(on)}$ ,  $V_{\rm CKE1(on)}$ ,  $V_{\rm CKE2(on)}$ ,  $V_{\rm CKE3(on)}$  and the temperature, the reference curves for  $V_{\rm CE(on)}$ ,  $V_{\rm CKE1(on)}$ ,  $V_{\rm CKE2(on)}$ , and  $V_{\rm CKE3(on)}$  are described by (13), (14), (15), and (16).

$$V_{CE(on)} = k_{CE}T + b_{CE} \tag{13}$$

$$V_{CKE1(on)} = k_{CKE1}T + b_{CKE1}$$

$$\tag{14}$$

$$V_{CKE2(on)} = k_{CKE2}T + b_{CKE2}$$

(15)

$$V_{CKE3(on)} = k_{CKE3}T + b_{CKE3}$$

(16)

Where,  $k_{\text{CE}}$ ,  $k_{\text{KE1}}$ ,  $k_{\text{KE2}}$ ,  $k_{\text{KE3}}$ ,  $b_{\text{CE}}$ ,  $b_{\text{KE1}}$ ,  $b_{\text{KE2}}$ ,  $b_{\text{KE3}}$  are the constants to describe the linear relationship between  $V_{\text{CE(on)}}$ ,  $V_{\text{CKE1(on)}}$ ,  $V_{\text{CKE2(on)}}$ , and  $V_{\text{CKE3(on)}}$  and temperature.

Therefore, the estimated temperature can be derived as (17), (18), (19), and (20) respectively.

$$T_{est(V_{CE})} = (V_{CE(on)} - b_{CE}) / k_{CE}$$

(17)

$$T_{est(V_{CKE1})} = (V_{CKE1(on)} - b_{CKE1}) / k_{CKE1}$$

(18)

$$T_{est(V_{CKE2})} = (V_{CKE2(on)} - b_{CKE2}) / k_{CKE2}$$

(19)

$$T_{est(V_{CKE3})} = (V_{CKE3(on)} - b_{CKE3}) / k_{CKE3}$$

(20)

For example, in the case, there is bond wire lift-off in Chip1. The estimation drift by  $V_{\text{CKE1(on)}}$  is derived as (21).

$$\Delta T_{est1} = \left| \frac{V_{CKE1(on)}(k_{CKE1} - k_{CE}) + a \times k_{CE} - b}{k_{CE}k_{CKE1}} \right|$$

(21)

It can be noted that  $|k_{\text{CKE1}}-k_{\text{CE}}| < |k_{\text{CE}}|$  and  $|k_{\text{CKE1}}-k_{\text{CE}}| < |k_{\text{CKE1}}|$ . Therefore, the temperature impact caused by the die attach solder is small. Also the emitter copper wire and copper track have the same coefficient of thermal expansion and are exposed to the same temperature swing. Thus, their resistance rarely changes which means that  $I_{\text{CR}}=1$ , the case of bond wire failure. In summary, the

Where,  $a = I_{\text{Chip1}}R_{\text{BW1}} + I_{\text{C}}R_{\text{E,CT}} + I_{\text{C}}R_{\text{E,CW}}$ ,  $b = -b_{\text{CE}}k_{\text{CKE1}} + b_{\text{CKE1}}k_{\text{CE}}$ .

to the same temperature swing. Thus, their resistance rarely changes which means that  $I_CR_{E,CT}+I_CR_{E,CW}$  can be assumed as constant in the case of bond wire failure. In summary, the impact of die attach solder is small. The emitter copper track and emitter copper wire do not influence the estimation.  $\Delta T_{\rm est1}$  mainly varies with the bond wire part  $|I_{\rm Chip1}R_{\rm BWI}/k_{\rm CKE1}|$ .

#### III. EXPERIMENTAL SET-UP

# A. Test bench

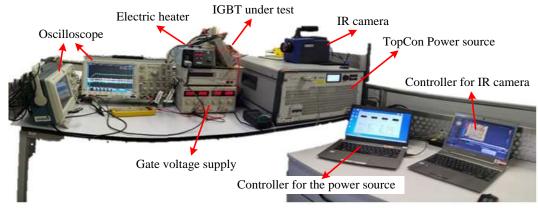

Experimental tests were conducted to verify the method described in Section II. The test rig is shown in Fig. 11. It is constructed according to the schematic in Fig. 4. The IGBT under test is mounted on a heat plate. The junction temperature is varied by the electric heater. Firstly, the IGBT is switched on by the voltage source. Then, a current pulse is injected into the IGBT by the TopCon power source, which is controlled by the computer shown on the bottom left. The thermal characteristics are recorded by the IR camera, which is controlled by the computer shown on the bottom right. Two oscilloscopes are used to capture electrical parameters. The IR camera starts to record temperature measurements when the IGBT module has been heated for about 20 minutes and the IGBT has reached thermal equilibrium. The IR camera is preferred since it can record the thermal information of each pixel in the picture quickly and accurately. In addition, the IR camera is only used to acquire  $T_{vi}$  of the module.

## B. Test conditions

In this study, ten on-state voltage tests were carried out in succession to measure  $V_{\rm CKE1(on)}, V_{\rm CKE2(on)}, V_{\rm CKE3(on)}$ , and  $V_{\rm CE(on)}$  at different bond wire states. Bond wires are cut to imitate the lift-off failure. Table III shows the lift-off conditions of all tests.

| Table II | I Nur | nber ( | of lifte | d bone | d wires | in IG | BT ch | ips in | each | test |

|----------|-------|--------|----------|--------|---------|-------|-------|--------|------|------|

| Test     | 1     | 2      | 3        | 4      | 5       | 6     | 7     | 8      | 9    | 10   |

| Chip1    | 0     | 1      | 2        | 3      | 4       | 4     | 4     | 4      | 4    | 4    |

| Chip2    | 0     | 0      | 0        | 0      | 0       | 2     | 4     | 4      | 4    | 5    |

| Chip3    | 0     | 0      | 0        | 0      | 0       | 0     | 0     | 2      | 4    | 6    |

Fig. 11. Test rig set up.

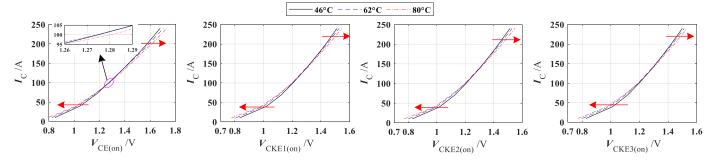

Fig. 12. Forward characteristics of the bottom IGBT switch of FF600R17ME4 at three temperatures.  $V_{\rm GE} = 15 \text{ V}$ .

# IV. BOND WIRE LIFT-OFF DIAGNOSIS

# A. Characterization for $V_{CE(on)}$ and $V_{CKE(on)}$

The proposed  $V_{\rm CE(on)}$  and  $V_{\rm CKE(on)}$  approach is tested on the FF600R17ME4 module. Fig. 12 is the forward characteristics  $V_{\rm CKE1(on)}$ ,  $V_{\rm CKE2(on)}$ ,  $V_{\rm CKE3(on)}$ , and  $V_{\rm CE(on)}$  at three different temperatures. It provides the reference of the IGBT at healthy condition.

The inflexion point of  $V_{\rm CE(on)}$  is around  $I_{\rm C}=100$  A. It is important to emphasize that  $I_{\rm C}$  -  $V_{\rm CE(on)}$  curves at different temperatures do not cross each other at the same point. This means inflexion point is not strictly temperature independent but the temperature dependency is small and thus negligible.

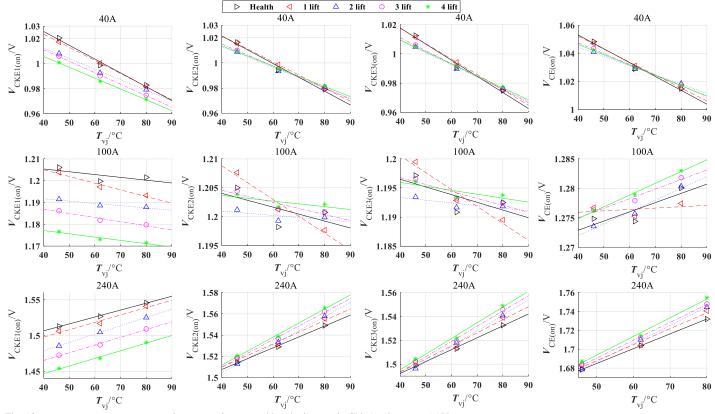

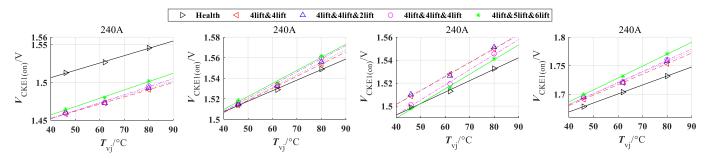

## B. Voltage shift upon bond wire lift-offs

Fig. 13 depicts the variation of  $V_{\rm CKE1(on)}$ ,  $V_{\rm CKE2(on)}$ ,  $V_{\rm CKE3(on)}$ , and  $V_{\rm CE(on)}$  upon bond wire lift-offs in Chip1 at 40 A, 100 A, and 240 A. These current values were chosen to represent the behavior of the voltage variations at the collector current levels of below, around, and above the inflexion point.

Table IV Linearity of the on-state voltage versus temperature

| $I_{\rm C}$ | $V_{ m CKE1}$ | $V_{ m CKE2}$ | $V_{ m CKE3}$ | $V_{\mathrm{CE}}$ |

|-------------|---------------|---------------|---------------|-------------------|

| 40A         | 0.9949        | 0.9940        | 0.9951        | 0.9939            |

| 100A        | 0.8358        | 0.6172        | 0.6969        | 0.7531            |

| 240A        | 0.9897        | 0.9914        | 0.9900        | 0.9957            |

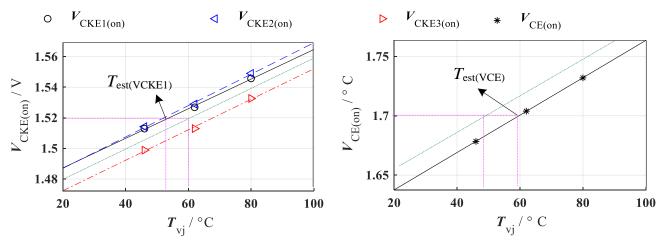

Table IV describes the linearity of the on-state voltage versus temperature. The linearity is derived from the measurement in Fig. 13. Each value is the average linearity of all the measurements at different bond wire failure condition. It can be noted that there is no clear linearity at  $I_{\rm C}=100{\rm A}$  (around inflexion point) where the temperature dependency is negligible. The variation upon the first bond wire failure is too small for  $I_{\rm C}=40{\rm A}$  (below inflexion point). As such this current level cannot be chosen for practical applications. When  $I_{\rm C}=240{\rm A}$  is applied, all voltages show good linearity with temperature.  $V_{\rm CKE1(on)}$  declines about 7 mV upon the first bond wire lift-off, whereas  $V_{\rm CKE2(on)}$ ,  $V_{\rm CKE3(on)}$ , and  $V_{\rm CE(on)}$  rises about 3 mV.

Fig. 13.  $V_{\text{CKE1(on)}}$ ,  $V_{\text{CKE2(on)}}$ ,  $V_{\text{CKE3(on)}}$ , and  $V_{\text{CE(on)}}$  against  $T_{\text{vj}}$  and bond wire cuts in Chip1 only.  $V_{\text{GE}} = 15 \text{ V}$ .

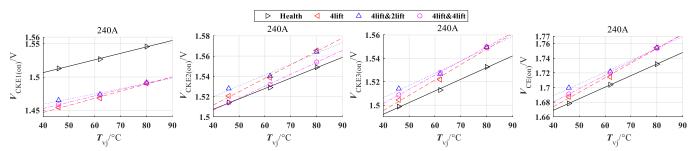

Bond wires were also cut for Chip2 and Chip3 as detailed in Table III. Fig. 14 and Fig.15 show results for these scenarios at  $I_{\rm C}$ =240A. Both figures show that  $V_{\rm CKE(on)}$  drops for those chips with lifted bond wires and  $V_{\rm CKE(on)}$  rises for the remaining chips. For example, Fig. 13 shows clearly the changes in  $V_{\rm CKE1(on)}$ ,  $V_{\rm CKE2(on)}$  and  $V_{\rm CKE3(on)}$  between a healthy module denoted as "Health" and a module where Chip1 lost four bond wires denoted as "4lift". Cutting two additional bond wires at Chip2 is represented by "4lift&2lift" as shown in Fig. 14, which shows that  $V_{\rm CKE2(on)}$  starts to decrease (as two bond wires were cut) and  $V_{\rm CKE1(on)}$  and  $V_{\rm CKE3(on)}$  rise slightly compared to results "4lift". The tendency of the results shown in Fig. 15 is similar

with that in Fig. 13. When there is bond wire failure in Chip3,  $V_{\text{CKE3(on)}}$  goes down, however,  $V_{\text{CKE1(on)}}$  and  $V_{\text{CKE2(on)}}$  goes up.

It is of interest to observe that every time a bond wire lifts-off  $V_{\rm CE(on)}$  increases. This has been reported in other literature [7, 8] too. The rise is due to the total equivalent resistance increases upon bond wire cut. However, from 4lift&2lift to 4lift&4lift, only two bond wires are cut which means there is only slight variance between the two measurements. Thus, the measurement of 4lift&2lift is higher than 4lift&4lift at lower temperature and overlaps with 4lift&4lift at high temperature.

Overall, test results confirm that the variations in  $V_{\text{CE(on)}}$  and  $V_{\text{CKE(on)}}$  can detect and locate the bond wire lift-off failures.

Fig. 14.  $V_{CKE1(on)}$ ,  $V_{CKE2(on)}$ ,  $V_{CKE2(on)}$ ,  $V_{CKE3(on)}$ , and  $V_{CE(on)}$  at various  $T_{vj}$  and bond wire cuts in Chip1 and Chip2. (4lift: four lift-off in Chip1; 4lift&2lift: four lift-off in Chip1 and four lift-off in Chip2.)

Fig. 15.  $V_{\text{CKE1(on)}}$ ,  $V_{\text{CKE2(on)}}$ ,  $V_{\text{CKE2(on)}}$ ,  $V_{\text{CKE2(on)}}$ , and  $V_{\text{CE(on)}}$  at various  $T_{\text{vj}}$  and bond wire cuts in Chip1, Chip2, and Chip 3. (4lift&4lift&2lift: four lift-off in both Chip1 and Chip2 and two lift-off in Chip3; 4lift&4lift&4lift&4lift&6lift: four lift-off in Chip2, and six lift-off in Chip3. (Chip3)

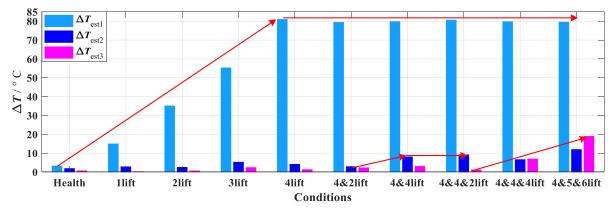

Fig. 16. Estimated temperature error for different bond wire lift-offs at  $I_C = 240$ A.

## C. Analysis for fault detection and location

Fig.16 describes the estimated temperature difference  $\Delta T_{\mathrm{est},i}$  (i=1,2,3) for different bond wire lift-off conditions at  $I_{\mathrm{C}}$  = 240 A. The arrows denote the trend of  $\Delta T_{\mathrm{est},i}$  for each IGBT chip. On the condition of lift-off in Chip1,  $\Delta T_{\mathrm{est}1}$  shoots up with every additional cut.  $\Delta T_{\mathrm{est}2}$  and  $\Delta T_{\mathrm{est}3}$  keep unchanged around almost zero. In the case of lift-off in Chip2,  $\Delta T_{\mathrm{est}2}$  goes up. When there is bond wire lift-off in Chip3,  $\Delta T_{\mathrm{est}3}$  starts to rise. This phenomenon locates the faulty chip and the level of  $\Delta T_{\mathrm{est}}$  can determine the number of bond wire lift-off.

It can be noticed that the temperature drift of Chip2 and Chip3 are smaller than that of Chip1. This is linked to the specified bond wire cut sequence and the current redistribution among these IGBT chips upon the bond wire lift-off. The bond wire lift-off is carried out on IGBT chips one by one to capture as more failure condition as possible. For example, if bond wires are lifted in Chip2 and Chip3 in the first test, the failure scenarios of lift-offs only in Chip1 are lost.

Due to the lift-off in Chip1, the increment of bond wire resistance in Chip1 circuit causes the decline of  $I_{\text{Chip1}}$ . As the total current  $I_{\text{C}}$  does not change, the extra current is shared between Chip2 and Chip3. This means the variation in  $I_{\text{Chip1}}$  is larger than that in  $I_{\text{Chip2}}$  and  $I_{\text{Chip3}}$ . As illustrate in previous section,  $\Delta T_{\text{est1}}$  varies with the bond wire part  $|I_{\text{Chip1}}R_{\text{BWI}}/k_{\text{CKE1}}|$ . The influence of the resistance is amplified by multiply  $I_{\text{Chip1}}$  causing the drift in Chip1 to be the largest.

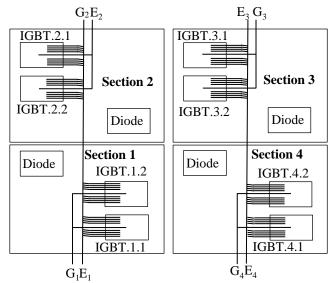

## V. TESTS ON POWER MODULE WITH DIFFERENT PACKAGE

In order to verify the feasibility of the proposed technique on power modules with a different package, repeated tests were carried out on the Dynex DIM400NSM33-F000 PM. The layout of DIM400NSM33-F000 is shown in Fig. 17. This is a 3.3 kV 400 A single switch IGBT module with eight IGBT chips and each IGBT chip has eight bond wires. Each IGBT chip is denoted by the numbers as shown in Fig. 17.

Fig. 17. Layout of the DIM400NSM33-F000 IGBT module.

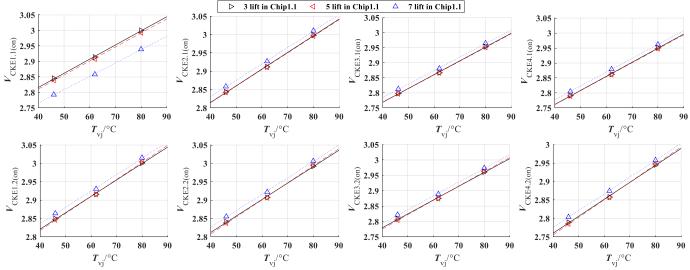

The test rig is constructed according to Fig. 4. Fig. 18 shows the experimental results for the bond wire lift-off in the IGBT chip 1.1, denoted as IGBT.1.1, where 3, 5, and 7 bond wires have been cut. All tests are carried out on the same opened IGBT module without gel. For each test, the gate drive voltage is kept at 15 V. The collector current  $I_{\rm C}$  is maintained at 360 A.

The first three lifted bond wires cause a 6 mV decrease in  $V_{\rm CKE1.1(on)}$  and about 1 mV increment in the on-state voltage of the other chips. More cuts lead to further decreases of  $V_{\rm CKE1.1(on)}$ , whereas all the other on-state voltages of the IGBT chips increase. The experimental results on the Dynex module are consistent with the results from the Infineon module. It confirms that the proposed method can be applied to PMs with different packages.

As it is known that the on-state voltage under load current is not only influenced by bond wire failure but also the virtual junction temperature  $T_{\rm vj}$ . The technique proposed in this paper can estimate the bond wire lift-off as well as locate the lift-off. Furthermore, since the temperature differece is dervied by feeding the voltage measurement to the references at health condition, the influence of temperature on the estimation is negligible. Compared to work presented in the past, like [13], the proposed method does not rely on the knowledge of  $T_{\rm vj}$  to determine bond wire lift-off. In addition, since the Kelvin Emitter terminal is only a measurement point in the proposed technique, there is no current flowing through, the power loss caused by the bond wire is eliminated.

Fig. 18. Experimental results: On-state voltage change upon bond wire lift-off in Chip1.1 at  $I_C = 360$  A.

# VI. CONCLUSION

The paper describes for the first time a technique that is able to detect and locate the bond wire lift-off in multi-chip IGBT (mIGBT) power modules (PMs). The proposed technique is based on the on-state voltage measurements of  $V_{\rm CKE}({\rm on})$  across the collector and the Kelvin emitter and the voltage  $V_{\rm CE(on)}$  across the collector and the emitter. Compared with the traditional  $V_{\rm CE(on)}$  approach, the proposed technique can detect early bond wire lift-offs in mIGBT PMs and the accuracy of the detection is independent of junction temperature.

It is shown that  $V_{\rm CKE(on)}$  decreases for the chip where the bond wire is lifted and increases for the remaining chips.  $V_{\rm CE(on)}$  always increases.

Tests conducted on the Infineon module show that the technique is able to detect the first lifted bond wire out of 37. The resolution is 7 mV for detecting the first bond wire lift-off. A second test was conducted on a 64-bond wire PM from Dynex of different package. The proposed system can detect the third bond wire lift-off. As such the proposed technique can be applied to various packaged PMs.

The proposed technique requires a small set of additional Kelvin terminals embedded in the frame of the power module where terminals are commonly placed. The additional Kelvin emitters are directly bonded with the emitter of the chips and no DCB layout change is required.

## VII. ACKNOWLEDGEMENT

The authors would like to thank Offshore Renewable Energy Catapult in the United Kingdom for their support in the project.

# References

- [1] Dynex. (2012). DIM800NSM33-F000 Single Switch IGBT Module.

- [2] Infineon. (2013). Technical Information FF1000R17IE4 IGB.

- [3] E. Wolfgang, "Examples for failures in power electronics systems," presented at the ECPE Tutorial on Reliability of Power Electronic Systems, Nuremberg, Germany, 2007.

- [4] Y. Shaoyong, X. Dawei, A. Bryant, P. Mawby, L. Ran, and P. Tavner, "Condition Monitoring for Device Reliability in Power Electronic Converters: A Review," *Power Electronics, IEEE Transactions on*, vol. 25, pp. 2734-2752, 2010.

- [5] P. Ghimire, S. Bęczkowski, S. Munk-Nielsen, B. Rannestad, and P. B. Thøgersen, "A review on real time physical measurement techniques and their attempt to predict wear-out status of IGBT," in 2013 15th European Conference on Power Electronics and Applications (EPE), 2013, pp. 1-10.

- [6] J. E. Nicolas Degrenne1, Erwan David, Roman Boldyrjew and Stefan Mollov,, "A Review of Prognostics and Health Management for Power Semiconductor Modules," presented at the Annual Conference of the Prognostics and Health Management Society 2015, 2015.

- [7] J. Bing, V. Pickert, C. Wenping, and B. Zahawi, "In Situ Diagnostics and Prognostics of Wire Bonding Faults in IGBT Modules for Electric Vehicle Drives," *Power Electronics, IEEE Transactions on*, vol. 28, pp. 5568-5577, 2013.

- [8] U.-M. B. Choi, Frede, "Real-time condition monitoring of IGBT modules in PV inverter systems," presented at the CIPS 2018 - 10th

- International Conference on Integrated Power Electronics Systems, 03/20/2018 03/22/2018 at Stuttgart, Deutschland, 2018.

- [9] M. A. Eleffendi and C. M. Johnson, "In-Service Diagnostics for Wire-Bond Lift-off and Solder Fatigue of Power Semiconductor Packages," *IEEE Transactions on Power Electronics*, vol. 32, pp. 7187-7198, 2017.

- [10] A. T. Bryant, K. Xiaosong, E. Santi, P. R. Palmer, and J. L. Hudgins, "Two-step parameter extraction procedure with formal optimization for physics-based circuit simulator IGBT and p-i-n diode models," *IEEE Transactions on Power Electronics*, vol. 21, pp. 295-309, 2006.

- [11] L. Zhou, S. Zhou, and M. Xu, "Investigation of gate voltage oscillations in an IGBT module after partial bond wires lift-off," *Microelectronics Reliability*, vol. 53, pp. 282-287, 2// 2013.

- [12] S. Zhou, L. Zhou, and P. Sun, "Monitoring Potential Defects in an IGBT Module Based on Dynamic Changes of the Gate Current," *IEEE Transactions on Power Electronics*, vol. 28, pp. 1479-1487, 2013.

- [13] J. Lehmann, M. Netzel, R. Herzer, and S. Pawel, "Method for electrical detection of bond wire lift-off for power semiconductors," in *Power Semiconductor Devices and ICs*, 2003. Proceedings. ISPSD '03. 2003 IEEE 15th International Symposium on, 2003, pp. 333-336.

- [14] K. Li, G. Y. Tian, L. Cheng, A. Yin, W. Cao, and S. Crichton, "State Detection of Bond Wires in IGBT Modules Using Eddy Current Pulsed Thermography," *IEEE Transactions on Power Electronics*, vol. 29, pp. 5000-5009, 2014.

- [15] M. Held, P. Jacob, G. Nicoletti, P. Scacco, and M. H. Poech, "Fast power cycling test of IGBT modules in traction application," in Power Electronics and Drive Systems, 1997. Proceedings., 1997 International Conference on, 1997, pp. 425-430 vol.1.

- [16] X. C. Y. Xiong, Z. J. Shen, C. Mi, H. Wu, V. K. Garg, "Prognostic and Warning System for Power-Electronic Modules in Electric, Hybrid Electric, and Fuel-Cell Vehicles," *IEEE Transactions on Industrial Electronics*, vol. 55, pp. 2268-2276, 2008.

- [17] V. Smet, F. Forest, J. J. Huselstein, A. Rashed, and F. Richardeau, "Evaluation of Vce Monitoring as a Real-Time Method to Estimate Aging of BondWire-IGBT Modules Stressed by Power Cycling Monitoring," *IEEE Transactions on Industrial Electronics*, vol. 60, pp. 2760-2770, 2013.

- [18] A. Singh, A. Anurag, and S. Anand, "Evaluation of Vce at Inflection Point for Monitoring Bond Wire Degradation in Discrete Packaged IGBTs," *IEEE Transactions on Power Electronics*, vol. 32, pp. 2481-2484, 2017.

- [19] Y. Peng, P. Sun, L. Zhou, X. Du, and J. Cai, "A temperature-independent method for monitoring the degradation of bond wires in IGBT modules based on transfer characteristics," in 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), 2017, pp. 751-755.

- [20] A. Babel, A. Muetze, R. Seebacher, K. Krischan, and E. G. Strangas, "Condition monitoring and failure prognosis of IGBT inverters based on on-line characterization," in 2014 IEEE Energy Conversion Congress and Exposition (ECCE), 2014, pp. 3059-3066

- [21] M. Du, K. Wei, J. Li, and L. Xie, "Condition monitoring IGBT module bond wire lift-off using measurable signals," in *Power Electronics and Motion Control Conference (IPEMC)*, 2012 7th International, 2012, pp. 1492-1496.

- [22] W. Kexin, D. Mingxing, X. Linlin, and L. Jian, "Study of Bonding Wire Failure Effects on External Measurable Signals of IGBT Module," *IEEE Transactions on Device and Materials Reliability*, vol. 14, pp. 83-89, 2014.

- [23] Y. Liu, D. Xiang, and Y. Fu, "Prognosis of chip-loss failure in high-power IGBT module by self-testing," in *IECON 2016 42nd Annual Conference of the IEEE Industrial Electronics Society*, 2016, pp. 6836-6840.

- [24] Infineon. (AN2008-01). Technical Information IGBT Modules Definition and use of junction temperature values.

- [25] H. P. S. D. Ltd., "Junction Temperature Definitions," 2015.05.29.

- [26] Y. Avenas, L. Dupont, and Z. Khatir, "Temperature Measurement of Power Semiconductor Devices by Thermo-Sensitive Electrical Parameters-A Review," *Power Electronics, IEEE Transactions on*, vol. 27, pp. 3081-3092, 2012.