## UiO **Department of Informatics** University of Oslo

# **PCIe Device Lending**

Using Non-Transparent Bridges to Share Devices

Lars Bjørlykke Kristiansen Master's Thesis Spring 2015

## PCIe Device Lending

Lars Bjørlykke Kristiansen

11th May 2015

#### Abstract

We have developed a proof of concept for allowing a PCI Express device attached to one computer to be used by another computer without any software intermediate on the data path. The device driver runs on a physically separate machine from the device, but our implementation allows the device driver and device to communicate as if the device and driver were in the same machine, without modifying either the driver or the device. The kernel and higher level software can utilize the device as if it were a local device.

A device will not be used by two separate machines at the same time, but a machine can transfer the control of a local device to a remote machine. We have named this concept "device lending". We envision that machines will have, in addition to local PCIe devices, access to a pool of remote PCIe devices. When a machine needs more device resources, additional devices can be dynamically borrowed from other machines with devices to spare. These devices can be located in a dedicated external cabinet, or be devices inserted into internal slots in a normal computer.

The device lending is implemented using a Non-Transparent Bridge (NTB), a native PCIe interconnect that should offer performance close to that of a locally connected device. Devices that are not currently being lent to another host will not be affected in any way. NTBs are available as add-ons for any PCIe based computer and are included in newer Intel Xeon CPUs.

The proof of concept we created was implemented for Linux, on top of the APIs provided by our NTB vendor, Dolphin. The host borrowing a device has a kernel module to provide the necessary software support and the other host has a user space daemon. No additional software modifications or hardware is required, nor special support from the devices. The current implementation works with some devices, but has some problems with others. We believe however, that we have identified the problems and how to improve the situation. In a later implementation, we believe that all devices we have tested can be made to work correctly and with very high performance.

## Contents

| 1 | Intro | oduction                                          | 3 |

|---|-------|---------------------------------------------------|---|

|   | 1.1   | Background                                        | 3 |

|   | 1.2   | Problem statement                                 | 6 |

|   | 1.3   | Main contributions                                | 6 |

|   | 1.4   | Limitations                                       | 7 |

|   | 1.5   | Research method                                   | 7 |

|   | 1.6   | Overview                                          | 7 |

| 2 | PCI   | Express                                           | 9 |

|   | 2.1   | PCI device                                        | 9 |

|   | 2.2   | Transparent bridges and PCIe switches 1           | 1 |

|   |       | 2.2.1 Hotplug capable PCIe slots                  | 2 |

|   |       | 2.2.2 Hotplug from a software perspective         | 4 |

|   | 2.3   | Thunderbolt                                       | 5 |

|   | 2.4   | Virtualization support in PCIe                    | 5 |

|   |       | 2.4.1 IOMMU 1                                     | 7 |

|   |       | 2.4.2 Single-Root IO Virtualization               | 8 |

|   |       | 2.4.3 Multi-Root IO Virtualization                | 0 |

|   | 2.5   | PCIe switches with support for partitioning       | 1 |

|   | 2.6   | Message Signalled Interrupts                      | 2 |

|   | 2.7   | Non-Transparent Bridges                           | 3 |

|   |       | 2.7.1 Dolphin NTB Software                        | 3 |

|   | 2.8   | Page Attribute Table                              | 4 |

|   | 2.9   | Application level distribution                    | 5 |

|   | 2.10  | Related work                                      | 5 |

|   |       | 2.10.1 Nvidia GRID                                | 6 |

|   |       | 2.10.2 Micron IO virtualization                   | 6 |

|   |       | 2.10.3 Sharing SR-IOV devices with multiple hosts | 7 |

|   |       | 2.10.4 Ladon                                      | 7 |

|   | 2.11  | Chapter summary                                   | 9 |

| 3 | Linu  | x Kernel 3                                        | 1 |

|   | 3.1   | Device and driver subsystem                       | 1 |

|   | 3.2   | PCI subsystem                                     | 1 |

|   |       | 3.2.1 PCI device structure                        | 1 |

|   |       | 3.2.2 Configuration space access                  | 2 |

|   |       | 3.2.3 Driver interface                            |   |

|   |       | 3.2.4 DMA API                                     | 5 |

|   | 3.3   | BIOS, firmware and ACPI                           | 7 |

|   |      | 3.3.1    | Hotplugging 38                                       |

|---|------|----------|------------------------------------------------------|

|   | 3.4  | IOMM     | U support                                            |

|   |      | 3.4.1    | VFIO                                                 |

|   |      | 3.4.2    | Sysfs interface                                      |

|   | 3.5  | Chapte   | r summary                                            |

|   | р.   | 1.       |                                                      |

| 4 |      | -        | Implementation 41                                    |

|   | 4.1  |          | menting with Thunderbolt                             |

|   | 4.2  |          | menting with Native PCIe hotplug 43                  |

|   |      | 4.2.1    | NTB EEPROM modification    43                        |

|   |      | 4.2.2    | Hotplug - ACPI                                       |

|   |      | 4.2.3    | Resource issues                                      |

|   | 4.3  | -        | menting with NTB 46                                  |

|   |      | 4.3.1    | Device lending                                       |

|   | 4.4  |          | ng remote device into Linux PCI subsystem            |

|   |      | 4.4.1    | Intercepting configuration space accesses 48         |

|   | 4.5  |          | to device BARs                                       |

|   | 4.6  |          | interrupts                                           |

|   | 4.7  |          | initiated DMA 52                                     |

|   |      | 4.7.1    | Allocation of coherent DMA buffers 55                |

|   |      | 4.7.2    | Streaming mappings 56                                |

|   |      | 4.7.3    | Utilizing an IOMMU for increased mapping granularity |

|   |      | 4.7.4    | Interrupt context considerations                     |

|   | 4.8  |          | memory based communication channel                   |

|   | 4.9  |          | owner daemon                                         |

|   | 4.10 |          | cations to the Dolphin driver                        |

|   |      |          | Lacking mapping resources                            |

|   |      |          | Reserved memory regions and ioremap attributes       |

|   |      | -        |                                                      |

|   | 4.12 | Chapte   | r summary                                            |

| 5 | Eval | uation a | and Discussion 67                                    |

| 0 | 5.1  |          | DA audio codec                                       |

|   | 5.1  | 5.1.1    | Device-driver interface                              |

|   |      | 5.1.2    | Audio playback   68                                  |

|   |      | 5.1.3    | Testing remote device access                         |

|   |      | 5.1.4    | Missing features                                     |

|   | 5.2  |          | blatile Memory Express SSD                           |

|   | 5.2  | 5.2.1    | Device-driver interface                              |

|   |      | 5.2.2    | Testing device         71                            |

|   |      | 5.2.3    | Missing features                                     |

|   | 5.3  |          | thernet NIC                                          |

|   | 5.5  | 5.3.1    | Device-driver interface                              |

|   |      | 5.3.2    | Testing remote device access                         |

|   |      | 5.3.3    | Performance and validation                           |

|   |      | 5.3.4    | Missing features                                     |

|   |      | 5.5.т    | 1                                                    |

| 6 | Con  | clusion   |                                    | 75 |

|---|------|-----------|------------------------------------|----|

|   | 6.1  | Summa     | ary                                | 75 |

|   | 6.2  | Main C    | Contributions                      | 75 |

|   | 6.3  | Future    | work                               | 76 |

|   |      | 6.3.1     | Multiple devices                   | 76 |

|   |      | 6.3.2     | SR-IOV device sharing              | 76 |

|   |      | 6.3.3     | Improvements to the Dolphin driver | 76 |

|   |      | 6.3.4     | Device control negotiation         | 76 |

|   |      | 6.3.5     | Use in virtual machines            | 77 |

|   |      | 6.3.6     | Isolating borrowed device          | 77 |

| A | Acce | essing th | ne source code                     | 79 |

#### CONTENTS

## **List of Figures**

| Steam download statistics                               | 3                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Various device pools                                    | 5                                                                                                                                                                                                                                                                                                                                                                                |

| The configuration space of a PCI device                 | 10                                                                                                                                                                                                                                                                                                                                                                               |

| PCIe switch                                             | 12                                                                                                                                                                                                                                                                                                                                                                               |

| Hotplug registers                                       | 13                                                                                                                                                                                                                                                                                                                                                                               |

|                                                         | 15                                                                                                                                                                                                                                                                                                                                                                               |

| Thunderbolt architecture                                | 16                                                                                                                                                                                                                                                                                                                                                                               |

| P2P transaction with IOMMU                              | 17                                                                                                                                                                                                                                                                                                                                                                               |

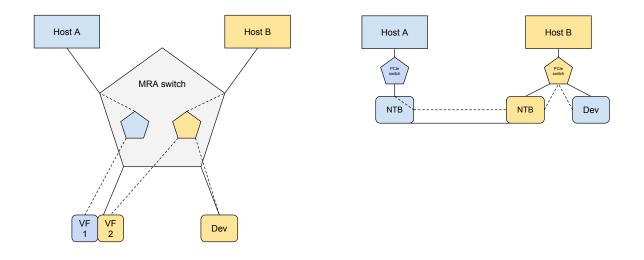

| PCIe switch vs MRA switch                               | 21                                                                                                                                                                                                                                                                                                                                                                               |

| The MSI capability structure                            | 22                                                                                                                                                                                                                                                                                                                                                                               |

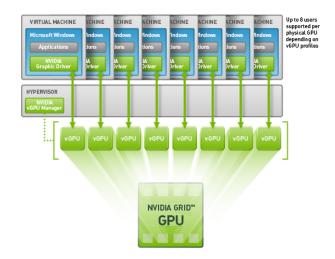

| Nvidia GRID promotion material showing virtual GPUs     | 26                                                                                                                                                                                                                                                                                                                                                                               |

| MR-IOV vs device lending                                | 47                                                                                                                                                                                                                                                                                                                                                                               |

| MSI through NTB                                         | 51                                                                                                                                                                                                                                                                                                                                                                               |

| Address spaces with NTB mapped memory                   | 53                                                                                                                                                                                                                                                                                                                                                                               |

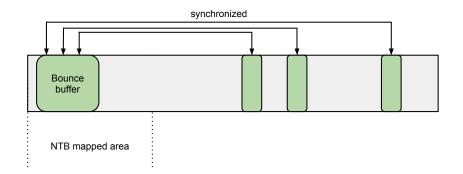

| Bounce buffer mapped with NTB                           | 57                                                                                                                                                                                                                                                                                                                                                                               |

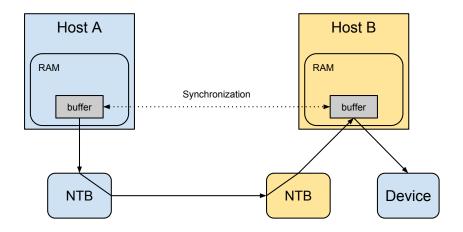

| Streaming DMA with a bounce-buffer on the other machine | 58                                                                                                                                                                                                                                                                                                                                                                               |

|                                                         | Various device poolsThe configuration space of a PCI devicePCIe switchHotplug registersHotplug memory windowsThunderbolt architectureP2P transaction with IOMMUPCIe switch vs MRA switchThe MSI capability structureNvidia GRID promotion material showing virtual GPUsMR-IOV vs device lendingMSI through NTBAddress spaces with NTB mapped memoryBounce buffer mapped with NTB |

## **List of Tables**

| 5.1 | The various devices we tested and our assessment of them |   |   | • |   | • |       |   |   |   | 67 |

|-----|----------------------------------------------------------|---|---|---|---|---|-------|---|---|---|----|

| 5.2 | The features used by the various devices                 |   | • | • | • | • | <br>• | • |   | • | 68 |

| 6.1 | Comparison of PCIe device pool schemes                   | • | • | • | • | • | <br>• |   | • | • | 76 |

## List of code snippets

| 3.1 | Cut down version of the device structure [1]                               | 32 |

|-----|----------------------------------------------------------------------------|----|

| 3.2 | Greatly cut down version of pci_dev structure in the Linux kernel [1]      | 33 |

| 3.3 | Functions in the DMA API to synchronize buffer between CPU and device      | 37 |

| 3.4 | Output from running ls on a PCI device in sysfs                            | 39 |

| 4.1 | pci_ops structure in the Linux kernel (include/linux/pci.h)                | 48 |

| 4.2 | Exporting the BARs of a device                                             | 51 |

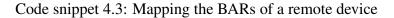

| 4.3 | Mapping the BARs of a remote device                                        | 51 |

| 4.4 | The dma_ops structure                                                      | 54 |

| 4.5 | Hooking the DMA API                                                        | 56 |

| 4.6 | Create mapping using IOMMU                                                 | 60 |

| 4.7 | Our simple shared memory based communcation channel algorithm              | 63 |

| 4.8 | The client of the shared memory based communcation channel                 | 63 |

| 5.1 | This method produced incorrect results for us with WC enabled. Most of the |    |

|     | function has been removed to reduce the noise. Notice that the SDL_CTL     |    |

|     | register is written twice.                                                 | 70 |

## Chapter 1

## Introduction

### 1.1 Background

The current trend in Internet services is "cloud computing", where the applications are running in "the cloud" and users have access to their data from their smartphone, tablet or a computer anywhere in the world. Most of the time, the cloud is not just used as a data storage for user applications, but instead, the applications themselves run in the cloud, and only a thin client application runs on the users device.

Cloud computing has gained popularity not only from being convenient for users, but also for its flexibility for the developers and service owners. The burden of maintaining the physical infrastructure is placed on the cloud provider instead of the application developer which allows the developer to focus on developing the application. This is also often cheaper for the developers compared to running their own servers. As the developer creates new applications or the use of their existing application changes, they can rent additional computers and change the specification of their computers to meet the new demands. The machines can also be located around the world to be geographically near their customers.

Cloud providers are able to rent out cheap machines thanks to one important technology: Virtualization. This technology allows multiple virtual machines (VM) to run on a single physical machine. Combined with the ever-increasing advances in computing power, storage and hardware in general, virtualization enables cloud providers to rent out virtual machines at a very low cost. The cloud providers saves physical space, power consumption, hardware cost and maintinance cost by having a smaller number of powerful machines with multiple VMs.

Since multiple virtual machines run on a single physical machine, they share the resources

Figure 1.1: Download rates over 48 hours from the game platform Steam [4] North America is coloured blue, Europe is green.

(a) A normal 48 hour snapshot of Steam (b) The sudden spike on the right is GTA V downloads. getting released for downloads (preload)

of the host. Some of the resources allocated to each VM are more static than others, for example, when a VM is created, the amount of RAM, number of CPU cores and network interfaces are given. The allocated resources can however in many cases be changed without powering down the VM. Some of the resources are however more naturally shared between the VMs including CPU time (time each virtual core executes on a physical core), disk access (bandwidth) and network bandwidth. These resources are time-shared between the VMs and each VMs timeslice can be dynamically changed and scale to meet the demands of the VM at any given time. If all of the virtual machines use all their resources all the time, this sharing will be close to static. In a lot of situations, however, the demands will change over time and can be "bursty". An example of this can be seen in the day-night cycle in the download rates on the Steam gaming platform in figure 1.1. Other services might have short term spikes in their resource usage such as content generation, simulations, nightly code compilations or a cute cat video gone viral. This can also be seen in the Steam download rates when GTA V is released for download. A VM provider can take advantage of the bursty nature of most computation and overprovision the combined resources of the VMs on a single host. If the cloud provider is able to quickly react to changes in resource usage, the cloud provider can rent out more computing power than they physically have. When the sum of resources used by the VMs on a host gets close to the limit, one or more of the VMs can be migrated, live, to another host without the users noticing it and when the combined VM usage is low, some hosts can be completely freed of VMs. These temporarily idle hosts can now be powered down to conserve power or for upgrades and maintenance.

In addition to the more traditional machine resources, newer VM software has support for allowing VMs to directly access some types of hardware devices. This is useful when the extra performance cost of emulating or otherwise intercepting the hardware affects the performance too much or emulation is infeasible. This direct device assignment is enabled by hardware virtualization support called IO Memory Management Units (IOMMU). In the same way that a normal Memory Management Unit (MMU) allows processes to have their own address space and isolate each process from each other and the kernel, an IOMMU isolates each VM and the VM's assigned devices from the host and other VMs.

With an IOMMU, a VM can be given direct control of a hardware device without the VM being able to break out of its isolation. For example, a dedicated network card can be given exclusively to a VM which gives the VM control of all packets to and from this network card. The host OS or other VMs will not be able to use a device that has been assigned to a VM. While directly assigning hardware devices to a VM improves performance by lowering overhead, it conflicts with the main benefit of virtualization, sharing powerful hardware dynamically.

Some network cards have multiple Ethernet connectors, each one seen as a separate device from the software perspective. In PCI terms this is called a multi-function device. Other devices can also be multi-function, for instance most Graphical Processing Units (GPU) with HDMI connectors have a dedicated audio function in addition to the GPU itself. Each function will have it's own driver instance in an OS and the driver does not need to be aware of the fact that the device is part of a multi-function device. Each of these functions can be separately assigned to a VM, for instance, assigning a single Ethernet port on a multi-port Ethernet card saves physical space in the host machine compared to each VM having it's own dedicated card.

The ideal would be to allow VMs direct control of the hardware to have low overhead, but still share the devices with multiple other VMs. The PCI standard Single Root IO Virtualization (SR-IOV) is a solution to this problem. A device that supports SR-IOV can appear as if it has multiple virtual functions (VF) and from the software perspective, this is similar to multi-function devices. Each VF is isolated from each other and can be safely assigned to a VM, but unlike with ordinary multi-function devices, VFs will share the same physical device resources.

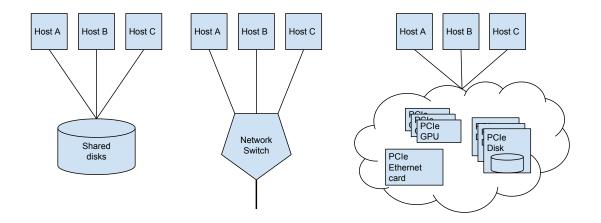

Figure 1.2: Various device pools

For instance, a network card with SR-IOV can allow multiple VMs to share a single Ethernet connector and the device itself will take care of sharing its resources with the VMs accessing it. This is done without affecting the performance benefits of direct hardware control.

Virtualization is beneficial when the application requirements are below the resource limits of the physical hardware, but just as easily, the resources required by an application can be greater than the resources in a single physical machine. To cope with this, the machine resources will need to be increased, but unlike with VMs, a physical machine cannot be dynamically upgraded with the touch of a button. If a host needs more storage space, a new hard drive must be added. The resources provided by hard drives, GPUs, network cards and other hardware devices typically come in chunks unlike like the fluid resources that can be assigned to VMs. If this is more than what is needed, the extra resources will either go unused, or create additional complexity in assigning VMs to physical machines. Additionally, adding more hardware to a host is a lot less dynamic than assigning hardware resources to VMs. There are also practical limits to how far a single host can be upgraded in terms of number of devices. Avoiding this problem can mean distributing the application to run on multiple servers. This is not only substantial work, but depending on the resources that are insufficient, can be impractical or difficult to do efficiently. If only one resource is lacking, for instance hard drive space or GPU power, distributing the work is not ideal.

If the hardware resources can be shared between multiple physical machines in the same way as resources can be shared between VMs, flexibility and resource utilization can be increased. This also no longer applies to only virtualization, but non-virtualized server settings can also benefit from sharing resources with other servers and dynamically assigning the resources to servers that need them. Allowing the resources used by a server to go beyond it's physical confines and be shared by multiple servers will make using optimal price-performance hardware instead of more expensive, powerful hardware possible. Such a setting can be seen as servers having access to a pool of resources as seen in figure 1.2.

A Network Attached Storage (NAS) can be seen as a pool of storage space that can be dynamically assigned and shared by multiple hosts and it is perhaps the most widely used form of inter-host resource sharing. A NAS can give a host access to greater storage space and potentially higher performance, often for a lower price than a locally attached disk in each machine with the same performance and capacity. For a VM provider, having a storage pool makes the assignment of VMs to hosts easier because the storage space required by the VM is no longer a factor in assigning VMs to physical hosts. Also, without the storage pool, if the assignment was not perfect, some of the hosts would have unused storage space, but with a

storage pool, the free space is not fragmented and is available for all hosts to consume. Taking bandwidth into consideration as well, some hosts might have VMs with high disk activity and others where the disk is used for cold storage, but in a NAS the total bandwidth can can also be combined using RAID and shared with all users. The result is that a host potentially has access to more disk space with higher bandwidth while the total number of disks is lower. The added flexibility of a storage pool applies to other resources as well, although not all of them are as easy to share efficiently while retaining the same level of performance.

In some ways, having a "top of the rack" network switch can be seen as a network pool. The servers in the rack are connected to a switch, which in turn is connected by a high speed link to the rest of the network. Compared to having a link from each server to the rest of the network, the cost and complexity should be greatly reduced and depending on the hardware, performance can be as good or better. Indeed, the switch can come at substantially lower cost than a dedicated fiber link in each server.

So far, each of the device pool types have been specific to a single type of device. A more flexible alternative would be a generic device pool that can share any device type and be used to share network, storage and GPUs. Allowing the hosts to share a single high speed network interface eliminates the "top of the rack" switch, the intra rack network cables, and the network cards in every server. This can reduce costs but also increase performance as all servers have the ability to achieve the peak bandwidth of the shared network card. In addition, increasing the network bandwidth of all the servers can be achieved by adding a single new card. This card can be used by all servers in combination with the other or the two card can be split among the servers. The same IO sharing pool can be used to share storage devices and GPUs.

#### **1.2 Problem statement**

The IO pool technologies available today are often vendor-dependent and part of a rack architecture. This can make the price too high for some use cases and locks a user to a specific hardware vendor. In this thesis, we investigate the generic IO device pool idea and we examine and evaluate existing solutions, standards and ideas before designing and implementing our own. We aim for our design to be relatively low cost, and require little user effort, so the devices need to be usable without modified drivers. We also want keep the needed additional hardware to a minimum and aim at designing a solution allowing an existing server cluster to be upgraded.

To acheive our goals, we develop a mechanism that allows PCIe devices to be dynamically reassigned from one machine to another. Specifically, the devices inside one server can be used by another machine either locally attached to a host or in an external cabinet. Our implementation is implemented for the Linux kernel and the PCIe based interconnect available from Dolphin Interconnect Solutions (Dolphin).

### **1.3** Main contributions

PCIe Multi-Root IO Virtualization (MR-IOV) is a standard for sharing multiple devices between multiple hosts. This vendor neutral PCIe standard can be used to create a pool of IO devices including disks, network cards and GPUs. Unfortunately, compliant hardware is virtually non-existent. Various vendors have created alternative PCIe device pool solutions, but most have significant limitations. Perhaps the most common way to get a device pool is as part of a complete rack solution, which creates a vendor lock-in. Possibly, the devices themselves are

part of a fixed package, and thus the flexibility is greatly reduced.

Our proof of concept design is unique because it lacks these limitations. First of all, the hardware required is easily available from multiple vendors and the rest of the solution is software based and can be converted to work with the different hardware available. Unlike most set-ups where all devices are placed in a pool outside the machines, often with a proprietary interconnect, our proposal is based on a standard PCIe interconnect. While the devices can be placed in an external enclosure, locally attached devices can also be used by remote machines. This is possible because our solution works at the software layer and the devices are, as in traditional PCIe, owned by only one computer. Instead of reassigning the device from one computer to another, the device can be controlled by the other computer with no change to the PCIe layer, instead, software arbitrates which computer controls a device. Since each device is controlled by a single computer at a time, we have named this "device lending". Because our implementation only deals with the remote access of a device connected to another computer, access to devices directly attached will not be affected in any way.

#### **1.4 Limitations**

In this thesis, we have discussed multiple other solutions for multi-host PCIe sharing, but because of the lack of availability for most of the solutions, we were unable to compare real world benchmarks of our solution to the others.

For our proof of concept, we describe multiple design alternatives, but to limit the scope of this thesis, not all were implemented. Also, some functionalities which we believe to be critical for optimal performance where not implemented since they were not necessary for a simple working prototype. We prioritized the implementation of the functionalities required for a few selected devices to work. In particular, functionalities considered legacy and not used in modern devices, such as port IO, was not implemented.

### **1.5 Research method**

In this thesis, we have followed the design paradigm as defined by Association for Computing Machinery [9]. Following this, our goal was to specify, design and implement a proof of concept. The implementation is tested in order to validate the design. Because of our incomplete understanding of the background material when starting this thesis, the design and requirements changed multiple times before we settled on a final design. The various designs that we discussed, tested and abandoned are documented in the thesis as well as what we learned under way.

### **1.6** Overview

This thesis will begin with chapter 2, on PCIe, in which we will detail the workings of PCIe, focusing on what we were required to know before creating our proof of concept and what we learned. In the next chapter, chapter 3, we will cover the background material needed for our implementation related to the Linux kernel, focusing on the interface between a device driver and a device. After this, all background information needed to explain the implementation is covered. Chapter 4 explains the implementation and our design choices. While chapter 4 details the final implementation, the next chapter, chapter 5 tells more of how we gradually developed

the solution by testing different devices and and debugging the interaction between device driver and device.

## **Chapter 2**

## **PCI Express**

Peripheral Component Interconnect (PCI) is a standardized bus used in different computer architectures. Any computer architecture that has a PCI bus can use the same type of devices. Introduced in 1992, its an old standard and has been superseded by PCI Express (PCIe). Currently the newest version of the PCIe specification [20] is 3.1. Both PCI and PCIe are standards developed by PCI-SIG.

Software-wise, PCIe is fully backwards-compatible with its predecessor. This allows operating systems and drivers written for PCI to work with PCIe. The identical software architecture made the transition easier for developers and software as drivers and operating systems designed for conventional PCI would support PCIe out of the box. This also means that the legacy PCI specification (PCI Local Bus Specification [19]) is still relevant for PCIe. From the hardware side on the other hand, PCIe and PCI are quite different. One of the more important differences are that in PCI, most devices are on the same bus and thus, they share bandwidth. This meant that two devices could not use the maximum bandwidth provided by PCI at the same time, PCIe, on the other hand, has no shared bus and is, in fact, packet based.

PCIe is layered in a similar way to TCP/IP. The top layer is the transaction layer containing Transaction Layer Packets (TLP) which are mostly memory read or write requests. In addition, there is also port IO requests, legacy interrupts and some internal events. Below is the Data Link Layer which guarantees the delivery of TLPs and is responsible for retransmissions and error corrections. At the bottom is the physical layer, dealing with circuitry and such and is specific to the physical medium.

### 2.1 PCI device

Each PCI device can be identified by its location in the PCI tree. Its location is given by the bus it's connected to and a unique device number on this bus and each device can have multiple functions. Each function is identified by the combination of <bus number, device number, function number>, the "bus-device-function" (BDF).

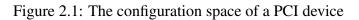

When the machine boots up, the platform firmware will scan for PCI devices on all buses, the device  $\langle X, 0, 0 \rangle$  is always present. The firmware discovers a device by reading its *configuration space*. The contents of the configuration space is standardized and is either a type 1 which is used for bridges, and type 0 which is used for all other devices, including endpoint devices and it can seen in figure 2.1. The contents of a device's configuration space allows the firmware to determine the type of device and other vital information about it.

If there is no device for a given BDF, all configuration reads will yield 0xff. This allows the system to discover the valid BDFs and the types of devices present. The devices' most basic

| Devi         | ce ID           | )        |        |          |            | Vende    | or ID           |                  |

|--------------|-----------------|----------|--------|----------|------------|----------|-----------------|------------------|

| Sta          | atus            |          |        |          |            | Com      |                 |                  |

|              | Clas            | SS       |        |          |            | Revision |                 |                  |

| BIST         |                 | Тур      | e      |          | Latency ti | mer      | Cache line size |                  |

|              |                 |          | E      | BAR 0    | )          |          |                 |                  |

|              |                 |          | E      | BAR 1    |            |          |                 |                  |

|              | Defines driver- |          |        |          |            |          |                 |                  |

|              |                 |          | E      | BAR 3    | ;          |          |                 | device interface |

|              |                 |          | E      | BAR 4    |            |          |                 |                  |

|              |                 |          | E      | BAR 5    | i          |          |                 |                  |

|              |                 |          | Car    | dbus (   | CIS        |          |                 |                  |

| Subsys       | stem I          | D        |        |          | Sub        | system   | Vendor ID       | -                |

|              |                 | Ex       | pansic | on RO    | M BAR      |          |                 | -                |

|              |                 | Reser    | ved    |          |            |          | Next capability | -                |

|              |                 |          | Re     | eserve   | ed         |          |                 | -                |

| Max latency  |                 | Min C    | Gnt.   |          | Interrupt  | pin      | Interrupt line  | -                |

| Memory BAR:  |                 |          |        |          |            |          |                 | J                |

| 7 6 5        | 4               | 3        | 2      | 1        | 0          |          |                 |                  |

| Base address |                 | Prefetch | Loca   | ation    | 0          |          |                 |                  |

| IO BAR       |                 |          |        |          |            |          |                 |                  |

| 7 6 5        | 4               | 3        | 2      | 1        | 0          |          |                 |                  |

| Base ac      | dress           | 5        |        | Reserved | 1          |          |                 |                  |

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

configurations will also be set by writing to the configuration space.

The "next capability" register in the configuration space of a device, is a pointer into another place in a device's configuration space, to a linked list of capability structures. Each capability structure has a next pointer and an ID defining its type. Capability structures are used to define additional properties of the device. New capability structures can be defined in the future. One example of a capability is the Message Signalled Interrupt capability seen in figure 2.6. In PCI-X 2.0 ("PCI extended", not PCIe), the configuration space was extended from 256 bytes to 4KB. The extended configuration space is also present in PCIe devices and it is used for an additional linked list of capabilities. A PCIe device will show the system that it is a PCIe device by implementing the PCIe capability structure [20].

The configuration space is not the main interface for a device, but rather, it allows the device to define its interface and its requirements. The BAR registers inform the system of the memory-mapped (MMIO) registers and IO port ranges of the device. Port mapped IO is however deprecated in the PCIe standard so we will not spend much time discussing it. The system uses the MMIO BAR registers to discover the size and number of device-defined memory-mapped areas containing device registers. These areas are used by a device driver to communicate with the device. Unlike the configuration space, the contents of the BAR areas are device-specific and not part of the PCI or PCIe standard. Once the BAR registers are programmed, the system can read and write to their memory addresses to interact with the device.

Each MMIO BAR can be either prefetchable or non-prefetchable. The prefetchable areas behave a lot like normal memory because they are guaranteed to have no side effects on read operations. This allows the system to do preemptive reads and merge operations to increase performance. The MMIO range defined by a non-prefetchable BAR cannot be prefetched by the system. Also non-prefetchable memory can only be placed in the lower 4GB of memory since the addresses are 32-bit only. Non-prefetchable memory is only intended to be used for control registers and such, and not for large storage spaces. Since non-prefetchable BARs are not used for large memory areas, the 32 bit limitation is not significant.

The BARs and the configuration space allow the CPU to interact with the device, but the device can also interact with the host machine. First of all, it can raise interrupts to tell the CPU that it has completed a task or some event has occurred. Also, devices can, like the CPU, access memory by using Direct Memory Access (DMA), to reach the RAM and MMIO registers. Without DMA, the CPU would have to write to MMIO registers of the device to transfer data, but this would occupy the CPU while the transfer was in progress. Devices with DMA engines can instead be instructed to read buffers directly from main memory.

### 2.2 Transparent bridges and PCIe switches

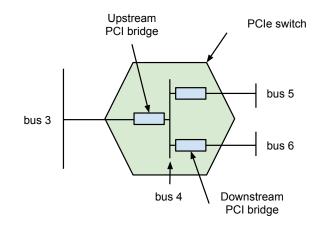

In traditional PCI, most devices shared a single bus. On this bus, only one device could communicate at a time which caused the total bandwidth on this bus to be shared. Some PCI systems however, had two or more buses that were connected to each other by a PCI-PCI bridge. Each bridge has two distinct ends: primary and secondary. The bus connected to the primary side is closer to the chipset of the system and the secondary is closer to the endpoint devices. The bridges forwards traffic according to a set of rules. The bridge will forward traffic it receives on the primary bus to the secondary bus, *downstream*, if the destination of the traffic is within the address ranges configured for the bus. In the same way, traffic on the secondary bus is forwarded upstream (secondary to primary) if the destination is not within the range of the bridge. The bridges forward all PCI traffic including interrupts, MMIO and configuration space accesses. In PCIe buses and bridges are reused to model the PCIe switches, see figure

Figure 2.2: A PCIe switch is composed of multiple PCI-PCI bridges and a bus.

2.2. All switches have an internal PCI bus. A single bridge, also referred to as the upstream port, connects the internal bus to another bus closer to the chipset / root complex. All the other bridges are downstream and are called downstream ports. At the top level of a PCIe fabric are the *root ports*. These ports are directly connected to the root complex of the machine. PCIe switches and PCI bridges route memory accesses directly to its destination. A transaction from a device to another device's MMIO registers does not go through the chipset or the CPU, but takes the shortest path through the PCIe fabric. This is sometimes referred to as Peer To Peer transactions (P2P) and can be very efficient, for instance data can be transferred from one GPU to another without involving the RAM or the CPU.

#### 2.2.1 Hotplug capable PCIe slots

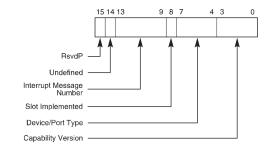

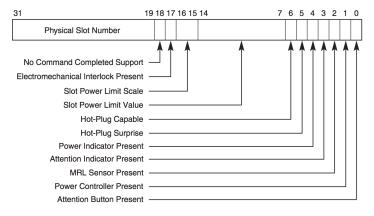

The PCIe capability structure declares various PCIe specific properties of a device or bridge including the PCIe capabilities register which can be seen in figure 2.3(a). For bridges, this includes whether the bridge is the upstream or downstream bridge in the switch and downstream bridges can have an additional bit set to indicate that it is a "slot". Slots are physical connectors that other devices can be connected to. Each slot has a dedicated slot capability register that can be seen in figure 2.3(b) and for the most part declares hotplug related capabilities. During the scan of the PCIe fabric, the OS will read these registers and learn the features and capabilities of the slot.

A slot indicates to the system software that is capable of hotplugging by setting the hotplug bit in the slot capability register. This signals that the tree beyond the bridge can be removed and replaced while the system is running. Section 6.4 of the PCIe specification specifies three parts of hotplug and specifies how both the software and the bridge should behave to implement hotplug.

- 1. The operating system needs to detect and react to the hotplug events.

- 2. The physical connector needs to allow a device to be removed or added without damaging any components.

- 3. The PCI-bridge associated with this port needs to communicate the status of the slot to the OS.

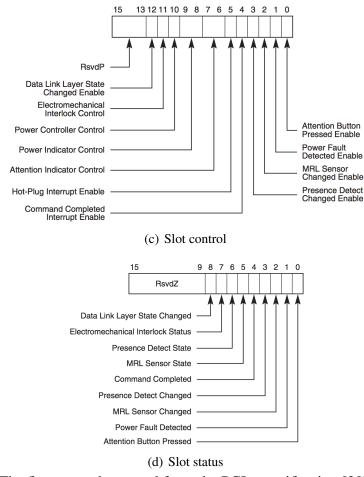

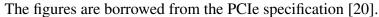

The various hotplug related features of a slot can be enabled and controlled by the system software with the control register seen in figure 2.3(c). Finally, the status register, in figure

#### (a) PCIe capabilities

(b) Slot capabilities

Figure 2.3: Registers related to hot-plug in the PCIe Capability Structure of a downstream port

2.3(d), is used by the OS for reading the state of a slot.

For the OS to detect when the slot is disconnected or connected on a hotplug-capable slot the OS first needs to set a bit in the control register: "hot plug interrupt enable". When this bit is set, the slot will generate an interrupt when a hotplug event occurs. When such an interrupt arrives, the OS can read the status register of the slot to detect if anything is plugged into or removed from the slot. When a hot-add event is detected, the OS will perform a scan of the devices behind the bridge, the same scan as when the system boots, by reading the new device's configuration space.

For a slot with the surprise hotplug bit set, a hotplug event can happen at any time. In both, slots that are capable of surprise hotplug and those that are not, there are multiple mechanisms for negotiating between the OS and user before the slot is disconnected. For instance, to assist in human interaction, two indicator lights may be present on the slot: the attention light and the power light which are controlled by the operating system. The OS can enable the power indicator to indicate that the device is powered and may not be removed and the attention light is used to allow the OS to indicate to the user the identity of a slot or call attention to it. For instance, when the OS has prepared a device for removal, the OS may blink the attention light to indicate that the device is ready for unplugging. On the other hand, the attention button may be pressed by a user, for instance to request removal of the device and the system can indicate a response with the attention light. Additionally, the specification says that a "software user interface" can be implemented. To help the user in knowing which physical slot corresponds to a slot in the OS user interface, the slots may be numbered and the slot manufacturer will have user-visible number on the slot and the same number will be programmed into the slot capability register. This makes it easier for the user to see, for example, the slot that contains a malfunctioning card, in much the same way as the indicators.

The manually-operated retention latch (MRL) is a mechanical mechanism that holds a device securely in place and a sensor may be implemented to alert the system of an imminent disconnect or of a new connection. If the power controller is also implemented, the MRL sensor will automatically cut power to the device when a disconnection is sensed. An electromechanical interlock can also be present and used by the OS to physically lock the device in place when the device is not ready to be disconnected.

#### 2.2.2 Hotplug from a software perspective

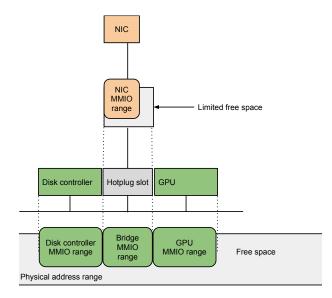

When a device is hot-added, its position in the PCIe fabric is always behind the bridge of the associated hotplug slot. Adding a new device introduces new bridges, buses and end point devices with associated MMIO areas and port IO ranges, depending on the kind of device that is added. Because of how bridges work in the tree-structured PCIe, all of the new device's resources must fit within the resources of the slot. Adding a new device becomes a problem when the bridge associated with the slot does not have sufficient space for the new device. The windows allocated to the slot must be within the windows of the bridge upstream of the slot. This applies to bus number, IO space, prefetchable and non-prefetchable memory which each have separate windows that all need to fit. Fixing this is hard, as the additional space must come from the upstream bridge and this applies recursively. Depending on the configuration of the tree upstream, the resource windows of the slot can be expanded by expanding the windows of all upstream bridges. Often however, this conflicts with the ranges of an entirely different part of the tree. Figure 2.4 shows a device behind a slot and the resource windows allocated to the slot as well as what is needed by the device behind the slot. In the figure, removing the NIC and replacing it with a device that consumes more memory resources poses a problem. For the connecting bridge to expand to accommodate this, there needs to be free space on either side of

#### 2.3. THUNDERBOLT

Figure 2.4: Devices behind a bridge must have their BARs within the resource windows of the upstream bridge

its range. In the figure however, both sides are occupied. One of the devices' resource windows must be moved for the system to be able to allocate the required resources to the new device. Moving the resource windows of a part of the PCIe fabric is however, not trivial as it would disrupt traffic for all downstream devices and associated drivers. If hotplugging is allowed, you can end up in situations where the total available capacity of the system allows the device to be added, but the resources available for the hotplug slot is insufficient and the new device cannot be used. To avoid the lack of resources in a hotplug slot, the system can allocate more space at boot time than what is required for any device connected at boot time.

### 2.3 Thunderbolt

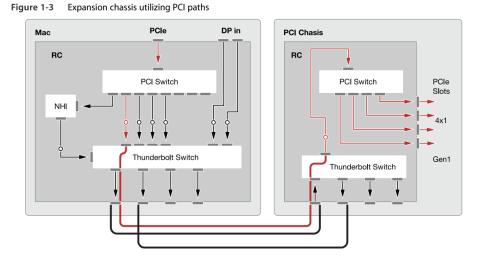

Thunderbolt is a consumer centric, high speed, external interconnect developed by Intel and Apple. The technology repurposes the Mini DisplayPort formfactor and are backwards compatible, falling back to normal Mini DisplayPort if a DisplayPort device is detected. Native Thunderbolt communication is a custom protocol that can tunnel both Mini DisplayPort traffic and PCIe traffic at the same time (it can also tunnel SATA, Ethernet and others). The traffic is routed by a Thunderbolt switch at each end of the connection as can be seen in figure 2.5. This switch multiplexes and demultiplexes the traffic into PCIe and Mini DisplayPort. It also enables the devices to be daisy-chained (Device A is connected to device B which is connected to device C and so on). A typical scenario would be a Thunderbolt display (not pure Mini DisplayPort) with multiple Thunderbolt ports which allows a computer with only a single port to attach multiple devices. Since Thunderbolt is an interconnect which can tunnel PCIe and allows hotplugging and complex structures (daisy chaining etc.) and is easily available, it is an interesting research topic for us.

### 2.4 Virtualization support in PCIe

Virtualization is a technology that allows multiple OSs to run on a single machine by separating them into virtual machines. This is achieved by tricking the OSs into believing that they are

Borrowed from Apple's Thunderbolt Device Driver Guide [5]

Figure 2.5: Thunderbolt architecture

running on bare metal and trapping privileged instructions and emulating them. A virtual machine will then be unable to access the other virtual machines or the host OS or any applications running outside its own virtualized environment. To increase the performance of virtualization, newer CPUs have hardware support for virtualization which greatly increases performance by handling more of the isolation in dedicated hardware on CPU instead of in software.

Still, there are some things whose behaviour the host must emulate in software. This carries significant overhead and decreases performance for the guests. This applies for instance to IO, where a VM cannot be allowed direct access to a device because software running on the VM may use this access to break out of isolation. This is because devices typically have direct access to the main memory of the host. Software running in a guest can order a device to read and write to physical addresses owned by the host or other VMs. Malware that has infected a guest OS can use this to break out of the VM and infect other VMs and the host. In addition, the memory layout of the host will be different from the hosts due to each VM having its own address space separate from the host's. Since the devices work with the host's physical address space and not the VMs this would make device access impossible without significant support in the guest OS.

To have both isolation and more direct hardware access, newer computers have an IO Memory Management Unit (IOMMU). IOMMUs are explained in detail in the next section (2.4.1). This hardware has the ability to give the virtual machine more direct access to IO devices such as PCIe devices. The IOMMU assists in doing this while still keeping the necessary isolation between the virtual machine and its connected devices and the rest of the system. To do this, the IOMMU needs to translate the memory accesses from a device to the guest's actual physical memory location. The guest OS might also configure the devices' address spaces that conflicts with the address space of the host. To solve this, the IOMMU translates all memory accesses between the guest OS and the device. In addition, the device may also perform DMA to other devices, which also requires address translation. Furthermore, interrupt from the devices must also be redirected to the VM. All of this must be implemented in such a way that isolation between the guests and the host is not compromised.

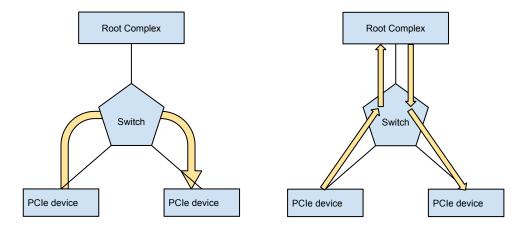

Figure 2.6: Left: normal peer to peer transaction through a PCIe switch. Right: transaction is routed through the root complex and to the IOMMU

#### **2.4.1 IOMMU**

In modern operating systems, processes have their own linear and isolated address spaces. This is enabled by the Memory Management Unit (MMU) of modern CPUs. It has the ability to create a virtual address space by translating the addresses used by the CPU before passing them on to the chipset and memory controller. The addresses are translated following the software defined *page table*. The translation works on a page size granularity (4KB by default on x86). Since the table would be very large if every single page must be present, the table is organized in multiple levels. Each entry in the top-level table points to another table. Also, each entry can be marked as invalid.

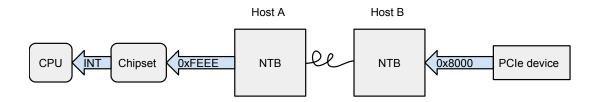

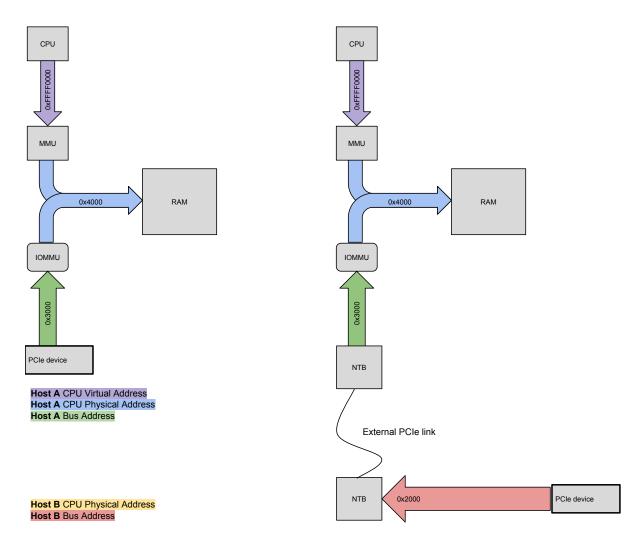

The I/O Memory Management Unit (IOMMU) is similar to the MMU, but is located between the chipset and the PCIe fabric (or other external buses). The most important feature of the IOMMU is the DMA remapper (DMAR). It translates the addresses of memory operations from the CPU to the PCIe fabric and from the PCIe fabric to RAM. Like with an MMU, access to unmapped addresses is denied. This provides isolation between the PCIe bus and the rest of the machine. An IOMMU can group PCIe devices into domains. Each domain has separate mappings and it's own address space similar to processes with MMUs. When an IOMMU is combined with normal CPU virtualization support, IOMMU domains can be overlapped with a virtual machines address space, which allows a VM to interact directly with a device and the device with the VM's virtual RAM. The access control features and domains of the IOMMU maintain isolation between the VMs and the host. When dealing with an IOMMU domain, there are multiple address spaces that need to be considered. The virtual memory address space, CPU physical address space, bus physical address space and the domain address space. An illustration of the address spaces can be seen in figure 4.3. In addition to isolating virtual machines, an IOMMU can be used to isolate device-driver pairs from the rest of the OS and other devices and drivers. This limits the potential damage an error (or malicious activity) that a device can do to the system. Not all CPUs have an IOMMU, but it is supported by more and more CPUs from Intel, AMD, ARM and IBM. Intel documents the features and workings of their IOMMU technology, VT-d, in their "Intel Virtualization Technology for Directed I/O" [6]. Since Intel CPUs are very common, we used the Intel IOMMU as a sample of what an IOMMU is capable of in the rest of the thesis.

As with most abstractions, DMA remapping brings a performance overhead. The memory translation tables are located in system memory in the same way as with an MMU. When a memory access passes the IOMMU, it must look up in the IOMMU's page table to translate the

access. This can be a performance issue since this can mean going through multiple levels of indirections in the page table. Although cache is present on the remapping engine to mitigate this. However, the cache depends on a good heuristic that predicts future accesses to lower the latency of checking the table in main memory. Peer to peer transactions are also heavily inhibited when remapped, since all transactions will be routed through the root complex instead of taking the shortest path. In external devices, this could involve a much lower bandwidth link which is unnecessary.

In an effort to increase performance of DMA remapping, PCI-SIG has developed the ATS specification [20]. It allows endpoint devices to translate the addresses themselves by having their own cache of their own most used remappings. This is implemented as an extension to the PCIe transaction level protocol. Each memory access will have a bit set if the address is already translated. This is done on a packet basis so the device may send one read that's pre translated and one that is not immediately after. This can be beneficial if the device knows what addresses will be accessed often. To learn the mapping of a page the ATC in the endpoint device can send a translation request to the translation agent in the root complex. The result of this request can be stored in the the devices own ATC and is valid until it receives an invalidate request from the root complex translation agent. The device is encouraged to locally cache addresses that will be accessed in the near future, especially if the access will be repeated. This allows for much more intelligent cache behaviour as the device itself often knows more about its own access pattern that the IOMMU in the root complex will. This could also greatly increase performance of peer to peer access since the traffic no longer needs to be routed through the root complex, see figure 2.6.

An IOMMU might be used to fulfil other purposes than to assist in virtualization. One example is to isolate a device and its driver from the rest of the system to prevent a malfunction or bug from affecting the rest of the system. Another example is to use an IOMMU to assist in scatter-gather operations to devices not capable of scatter-gather operations. This can be useful because a buffer in a virtual memory address space is seldom linear in the physical address space.

#### 2.4.2 Single-Root IO Virtualization

An IOMMU allows a virtual machine to directly control a physical IO device in a safe and isolated manner. This VM will have full control over the device. This leads to increased performance compared to emulated hardware typically used in virtual machines. For instance, a VM typically has an emulated network card. When the VM OS sends a packet using this emulated hardware, the hypervisor will pass this packet through to the network stack in the host OS. Here the packet will get routed as any other packet, typically to a NIC and out of the host. If the VM is instead given a physical NIC, all packets will be sent out to the cable attached to the NIC. This removes a lot of the software overhead, and lowers the amount of times the data is copied before it is sent out on the cable. IBM has shown that a 10Gb SR-IOV capable Ethernet NIC can be almost saturated by a VM [15].

In addition, the VM will have full access to the bandwidth of this device since no other VM or the host can use it at the same time. It will not have to share it with other users. This is also the weak point of direct hardware assignment.

Much of the advantage of running virtual machines is the increased efficiency of having a few powerful machines instead of a lot of weak or under-utilized ones. Giving each guest direct access to its own IO device conflicts with this since each the host hardware now needs multiple IO devices. In addition, these IO device might no longer be fully utilized all the time. The additional number of devices will also use more power, need more room and have a higher up-front cost.

To get both the performance of direct hardware control and the efficiency of device sharing, a new standard was created, Single Root IO Virtualization [18] (SR-IOV). SR-IOV solves this by allowing a single physical function (PF) to act as multiple virtual functions (VF). The device itself emulates the multiple VFs. The virtual devices are isolated from each other and the device itself shares its own physical resources across the VFs in a way that makes sense for the device type. For instance a network card can act as if an Ethernet switch connects the VFs and the outbound connection. A storage device can be partitioned or provide concurrent access to the same storage space, but with some synchronization features. The VFs can be directly assigned to a virtual machine in the same way as any other function. The virtual devices can have some features disabled to prevent them from being able to negatively affect the operations of other VFs or the physical device. Features of the device that can affect all VFs and the physical funtion are typically only available for the PF. For some devices, potentially unsafe functionalities are needed by the VFs for correct operation, or desired by users. For instance, a NIC might want to set its own MAC address, but it would be unfortunate if one VF, intentionally or unintentionally, set to the same MAC address as another VF or the PF. Potentially, the device could deny this, but this might not be practical for all purposes and it's not very flexible. In Intel's NICs with SR-IOV, there is a communication channel between the drivers for the VFs on the VMs and the driver for the PF on the host. This allows the PF driver to control the requests by the VF drivers in a safe manner that can be defined by software. Since the VMs are isolated from each other and the host, there is no guaranteed way for them to communicate. A hypervisor could implement support for a communication channel between the driver, but to avoid having to support various hypervisors, the drivers will communicate with the help of the device itself. A mailbox and doorbell mechanism on the NIC itself is used by the VF drivers and the PF drivers to communicate [13] and allow a VM to perform potentially unsafe operations under the control of the host.

A device that implements SR-IOV has the SR-IOV capability structure in it's configuration space. The host can control the SR-IOV related features of the device by setting the desired values in the SR-IOV capability. Before the enable bit is set in this structure, no virtual functions will be present. Before enabling this, the host can set the number of desired virtual functions. There is a limit to the number of VF a given device support which it reports through a register in its SR-IOV capability structure. Various other parameters dealing with the BARs for the VFs are also present.

Since the number of function numbers for a given device is fairly limited, Alternative Routing Interpretation (ARI) was created which allows for more functions for a single device. It raises the number of functions to 255, but if the number of VFs exceed this, an additional bus number can be used.

In the same way as hot add, increasing the number of VFs, or enabling it can require more resources than available in the upstream bridge. This will require the OS to expand these resources. This includes memory resources and bus numbers. IO space is not needed as VF cannot have IO BARs. To avoid the difficulties with this, the platform firmware should also be SR-IOV aware. If the firmware is SR-IOV aware, it can reserve space for the additional devices at boot time, for instance by using the maximum number of VFs for a given device. Such preallocation is much simpler as it can be performed before any use of other PCI devices starts.

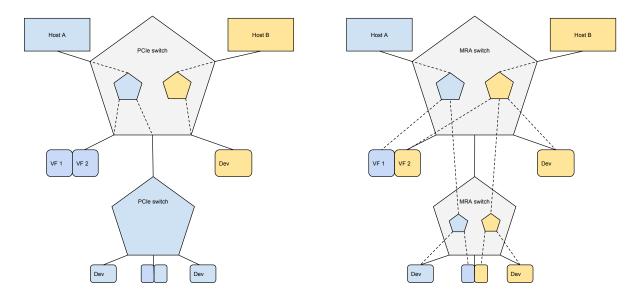

#### 2.4.3 Multi-Root IO Virtualization

PCI and PCIe are strictly for use by a single host machine. Multi-Root IO virtualization (MR-IOV) [17] is a PCI-SIG developed standard for allowing multiple hosts to be connected to the same PCIe fabric. MR-IOV allows the connected hosts to have devices dynamically assigned to them and to concurrently share devices like VMs can with SR-IOV. Each host connected to the MR-IOV fabric has their own own virtual hierarchy (VH). The VH is consistent with the traditional PCI model as there will be only one root complex in each VH. Each host only sees its own VH and it does not need to know that it's part of a MR-IOV fabric as the VH operates identically to standard PCIe. For MR-IOV to be utilized, new PCIe switches must be used which are called Multi Root Aware (MRA) switches. Normal PCIe switches can be present in a MR-IOV fabric, but a VH cannot span such switches, only MRA switches. A figure showing a MRA switch with two VHs can be seen on the right side of figure 2.7.

While the MRA switch can assign any single device to a VH, normal devices cannot be used concurrently by more than one host, even if it's SR-IOV capable. However, specially designed MRA capable endpoint devices can be concurrently used by multiple hosts in the same way as SR-IOV devices can be used concurrently by multiple VMs. The device will present individual configuration spaces to the different hosts similar to SR-IOV. A device can implement both SR-IOV and MR-IOV to allow it be used by VMs in different hosts at the same time. If it does, each host has control over the SR-IOV capability of its own virtual device.

In the MR-IOV hierarchy a host is assigned the Multi-Root PCI Manager (MR PCIM) role. It is responsible for setting up the MRA switch and the other hosts VH's. This host will be the only host aware / need to be aware of the fact that this is a MR-IOV switch. The MR PCIM will scan the switch and all connected devices. When its done it will assign the devices to a VH. The final step is connecting a host to its VH. The other host will then discover their own VH and scan it for devices, set the devices and operate as normal.

MRA switches have two distinct forms of hotplug: the normal physical hotplug and the virtual hotplug. The virtual hotplug is the one seen by the non-PCIM hosts. When such a host interacts with this capability, the MR PCIM is notified. The MR PCIM acts as a layer between the hotplugging controlled by the other hosts and the physical hotplug control. When a device is removed, the event is propagated by the MR PCIM to the virtual hotplug interface of all VHs with the affected devices. The same applies to other events and statuses such as button presses. The MR PCIM also has the ability to reassign devices from one VH to another. This is presented to the other hosts as a hotplug event in the virtual host.

MR-IOV is can be very useful in solving the problems we introduced in this thesis as it allows great flexibility by allowing for dynamic reassignment as well as concurrent use of devices. With the exception of the MR PCIM, no modification is required to the hosts hardware or software which is useful for easy adoption. Unfortunatly, the MRA switches require new chips to be designed. The same applies to the MRA devices which are the only devices than can be shared by multiple VH at the same time. At the moment however, we have not found any MR-IOV capable switch available for sale and the same also applies to MRA devices. As it stands MR-IOV cannot be used for this reason. Considering that the MR-IOV standard was finished in 2008, its lack availability is not a good sign for its future adoption either.

#### **NextIO**

NextIO was a start-up developing IO virtualization products. Their product was a competitor to the traditional top-of-the-rack network switch. Their main product was an external cabinet with room for PCIe devices. This cabinet was connected to multiple hosts with a 10Gb/s PCIe

Figure 2.7: Left: A PCIe switch with two partitions. Each host sees its own fabric and switch. Right: An MRA switch. More finely grained device assignments.

cables. The cabinet was fitted with a 10 or 40 Gb/s Ethernet card or a Fiber Channel card. Their product allowed all of the hosts to access the single NIC at the same time, sharing its bandwidth. In addition, the cabinet supported other PCIe devices, but as far as we know, they could not be shared, but only be assigned to a single host. Although the details are a little vague, we believe that the cabinet was an implementation of a PCIe MRA switch. This fits well with the Ethernet and Fiber Channel cards that could be shared by the hosts, but not other cards. We believe these cards, delivered by NextIO themselves, where MRA cards, capable of being controlled by multiple hosts. If so, NextIO was one of the few vendors that produced MR-IOV products, but in 2013, NextIO went bankrupt.

### **2.5** PCIe switches with support for partitioning

Some PCIe switches have support for so-called partitioning. Partitioning is not part of the PCIe specification and is vendor dependent. It is a feature that allows multiple hosts to be connected to a single physical switch somewhat like MRA switches. The switch will partition the traffic in such a way that the each host sees its own virtual switch and PCIe fabric. An illustration of a partitioned switch compared MRA switches can be seen in figure 2.7. Each partition have a single root complex and zero or more devices, and each port of the physical switch is assigned to a partition. Unlike a MRA (MR-IOV) switch, the different root complexes cannot share devices or overlap in any way. The different partitions can be connected to one another with NTBs, however, which can provide communication between the partitions, (see section 2.7). These switches are inferior to true MRA switches, but are readily available. Our findings so far indicate that the partitioning is limited to a single switch, and cannot span multiple switches like VHs in MRA switches. This limits the granularity of the assignments to the entire sub tree of downstream port of the switch. In the case of an external switch and an external expansion chassis, a single host would be in control of the entire chassis. If an expansion chassis has an internal switch that supports partitioning, it is possible to assign individual devices to the hosts, but each host must then be connected to the chassis by a separate link. It is perhaps possible for two switches to be connected and have the virtual switch span the physical switches or have something like the VH in a MRA switch. Combining multiple such switches, one "main" switch

| 31 30 29 26 27 20 23 24 23 22 21 20 19 16 17 10 13 14 13 12 11 10 9 6 7 6 3 4 5 2 1 0 |         |          |              |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------|---------|----------|--------------|--|--|--|--|--|--|--|--|

| Reserved                                                                              | Control | Next cap | Cap ID (MSI) |  |  |  |  |  |  |  |  |

| MSI address low                                                                       |         |          |              |  |  |  |  |  |  |  |  |

| MSI address high                                                                      |         |          |              |  |  |  |  |  |  |  |  |

| MSI Data                                                                              |         |          |              |  |  |  |  |  |  |  |  |

|                                                                                       |         |          |              |  |  |  |  |  |  |  |  |

### Control register:

| _ | 7             | 6     | 5          | 4     | 3     | 2           | 1     | 0          |

|---|---------------|-------|------------|-------|-------|-------------|-------|------------|

|   | 64-bit enable | Multi | -message e | nable | Multi | -message ca | pable | MSI enable |

#### Figure 2.8: The MSI capability structure

as well as one in each expansion chassis, could allow each host to be assigned individual devices for separate chassis.

Possibly, a switch port could be reassigned from one partition to another on the fly, without interfering with the traffic in unchanged ports. If so, it would be possible to use such a switch to allow PCIe devices to be dynamically assigned to different hosts in a cluster. In theory, this should look like and behave as a physical hotplug event. If the switch also reports these events as hotplug events, there would not necessarily be any need for modification to drivers or the OS to support it. A master's thesis from MIT titled "PCI Express Multi-Root Switch Reconfiguration During System Operation" [24] tested the repartitioning of a PLX switch while the hosts where live. In their test setup, two hosts and two NICs were connected to the switch. In one experiment, one of the NICs was moved from one partition to the other. They reported no ill effects from this migration. Unfortunately, measurements of the possible effects of this seem to be lacking. Possibly the operation of the non-moved device could be affected. It would also have been interesting to see a running bandwidth benchmark from one NIC while the switch was being repartitioned. This should show if the repartitioning had any negative negative effects on performance. There is also little discussion on the time it takes to migrate a device, but presumably it is fast.

### 2.6 Message Signalled Interrupts