University of Oslo Department of Informatics

Multiple-Input Common-Gate FGUVMOS Transistor and Its Application in Multiple-Valued Logic Circuits

Øyvind Hagen

Cand. Scient. Thesis

May 2006

### Acknowledgments

This thesis brings to an end my work for the Cand. Scient. degree at the Department of Informatics, University of Oslo.

I would like to thank my advisor Yngvar Berg for accepting me as his student and for his relentless guidance to the field of active floating-gate circuits.

I would also like to thank Dag T. Wisland for his help with circuit simulations, chip layout and measurement equipment. A thanks to Espen Torstensen for building the test circuit board is also in order. The experiences shared by my fellow graduate students, especially Rene Jensen and Johannes G. Lomsdalen, was invaluable for completing this thesis.

And at last, but not least, I would like to thank my family for their unwavering support.

Department of Informatics, University of Oslo, May 2006. Øyvind Hagen

### Abstract

The demand for reduced area and power consumption have usually been met with improvements in processing techniques, allowing for increased integration and a reduction in the power supply voltage. Some technology improvements have also occurred, such as strained silicon and silicon-on-insulator. But some design techniques also feature a significant reduction in area and power consumption, such the asynchronous design approach. Reducing the amount of interconnects is another approach, for which multiple-valued logic might be an ideal candidate.

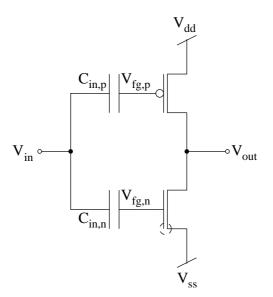

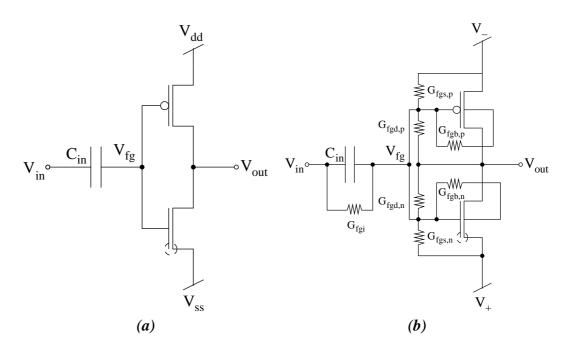

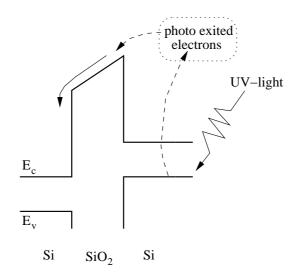

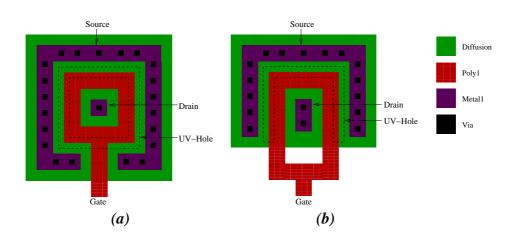

This thesis explores the multiple-input common-gate FGUVMOS transistor and the design of multiple-valued logic circuits using this transistor. We examine in detail a UV-programming technique for initializing the floating-gate. There is no need for any extra programming circuitry with this programming method, since it utilizes the supply rail of the nMOS transistor to place a charge on the floatinggate. An important benefit of the floating-gate initialization is a matching of the pMOS and nMOS transistor at a predetermined current level. We also look closer at some of the layout issues concerning FGUVMOS circuits.

We also explore a new area of application for the FGUVMOS transistor, namely multiple-valued logic. The main design parameter of the FGUVMOS transistor—the capacitive division ratios of the coupling capacitors to the floating-gate—is well suited for designing voltage-mode multiple-valued logic circuits. Several multiple-valued logic circuits are examined in detail and several design issues are addressed. Measurements on a fabricated chip are supplied, as well as simulations of the various circuits. And the voltage output functions for the presented circuits are also developed.

# Contents

| Acknowledgments     I |                         |                                |    |  |  |  |

|-----------------------|-------------------------|--------------------------------|----|--|--|--|

| Abstract              |                         |                                |    |  |  |  |

| 1                     | Intr                    | oduction                       | 1  |  |  |  |

|                       | 1.1                     | Multiple-Valued Logic          | 2  |  |  |  |

|                       | 1.2                     | Floating-Gate Circuits         | 4  |  |  |  |

|                       | 1.3                     | Overview of the Thesis         | 4  |  |  |  |

| 2                     | Multiple-Valued Logic 7 |                                |    |  |  |  |

|                       | 2.1                     | Introduction                   | 7  |  |  |  |

|                       | 2.2                     | Algebraic Notation             | 8  |  |  |  |

|                       | 2.3                     | Radix and Complexity           | 9  |  |  |  |

|                       | 2.4                     | Signal Representation          | 11 |  |  |  |

|                       | 2.5                     | Signal Integrity               | 12 |  |  |  |

|                       | 2.6                     | Summary                        | 13 |  |  |  |

| 3                     | Floa                    | ting-Gate UVMOS Devices        | 15 |  |  |  |

|                       | 3.1                     | Introduction                   | 15 |  |  |  |

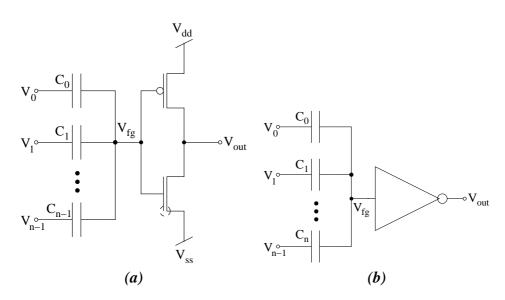

|                       | 3.2                     | Floating-Gate UVMOS Transistor | 16 |  |  |  |

|                       | 3.3                     | Capacitive Voltage Division    | 17 |  |  |  |

|                       | 3.4                     | FGUVMOS Transistor Equations   | 19 |  |  |  |

|                       | 3.5                     | Programming Technique          | 20 |  |  |  |

|                       | 3.6                     | Layout Considerations          | 25 |  |  |  |

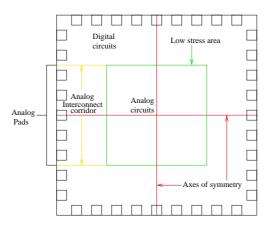

|                       |                         | 3.6.1 Transistors              | 25 |  |  |  |

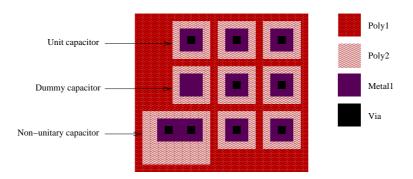

|                       |                         | 3.6.2 Capacitors               | 26 |  |  |  |

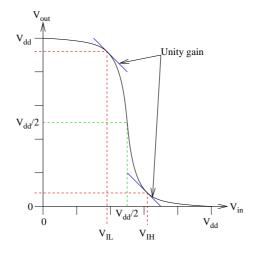

|                       | 3.7                     | Noise Margins                  | 28 |  |  |  |

|                       | 3.8                     | Summary                        | 30 |  |  |  |

| 4                     | FGU                     | JVMOS MVL Circuits             | 33 |  |  |  |

|                       | 4.1                     | Introduction                   | 33 |  |  |  |

|    | 4.2         | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34        |

|----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|    | 4.3         | Multiple-Valued Inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 38        |

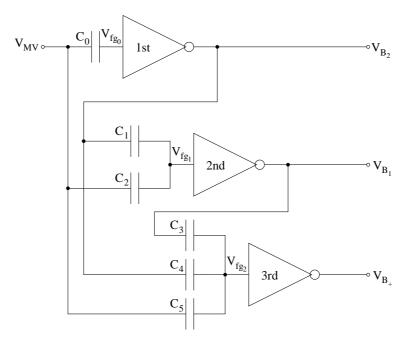

|    | 4.4         | Binary to Multiple-Valued Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 42        |

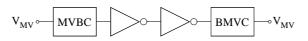

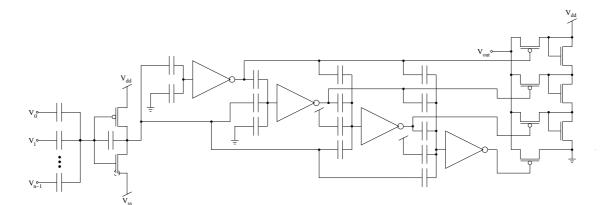

|    | 4.5         | Multiple-Valued to Binary Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50        |

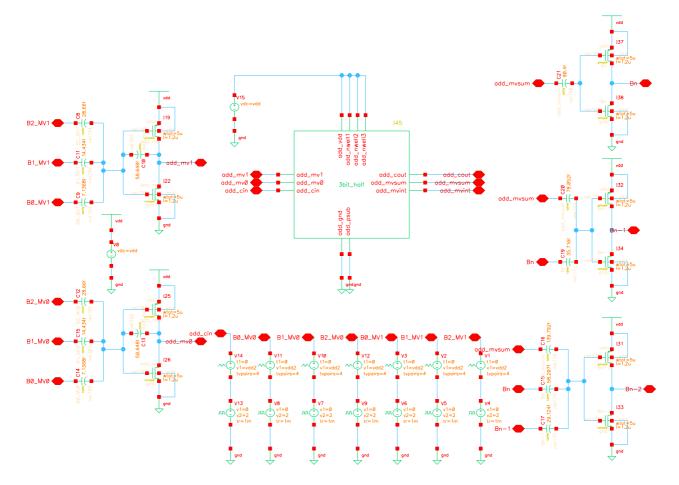

|    | 4.6         | Multiple-Valued Full-Adder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 59        |

|    | 4.7         | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 57        |

| 5  | Con         | clusion And Further Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>69</b> |

|    | 5.1         | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59        |

|    |             | 5.1.1 Common-Gate FGUVMOS Transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 59        |

|    |             | 5.1.2 Multiple-Valued Logic Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 70        |

|    |             | · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 70        |

|    | 5.2         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 71        |

| Bi | bliogr      | aphy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 73        |

| A  | Simu        | ilation Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 87        |

| B  |             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 93        |

| D  | B.1         | - · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>93</b> |

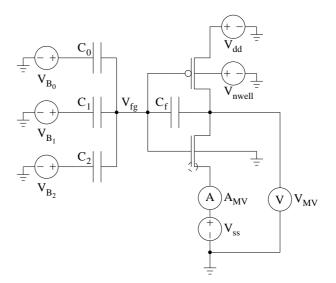

|    | Б.1<br>В.2  | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 93<br>94  |

|    | <b>D</b> .2 | Measurement Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14        |

| С  | -           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 95        |

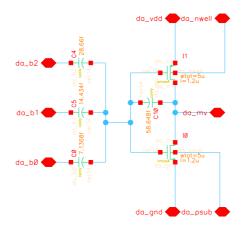

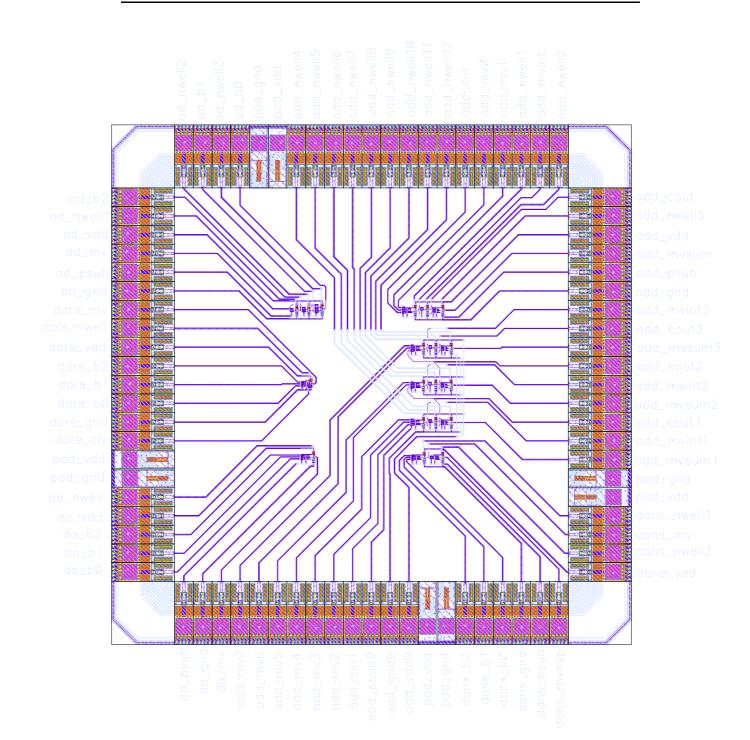

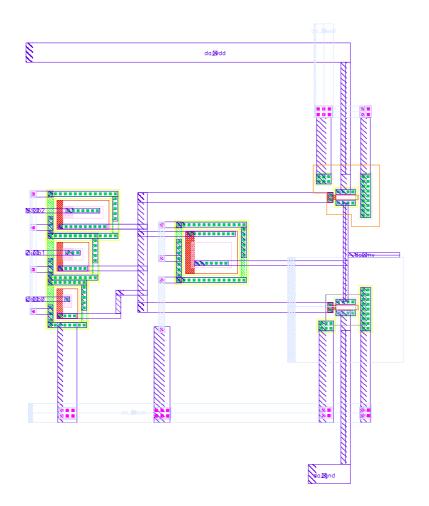

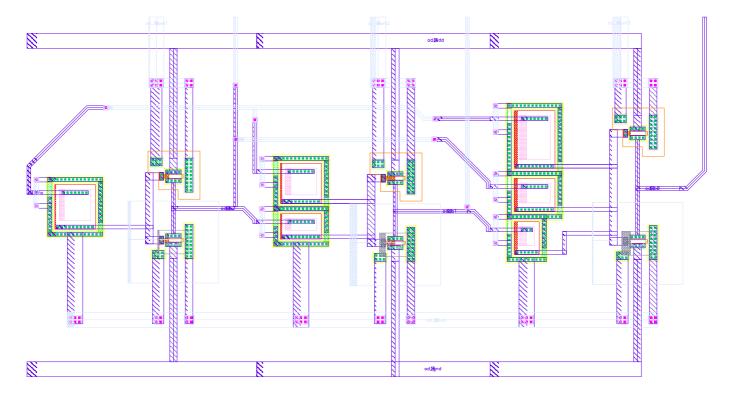

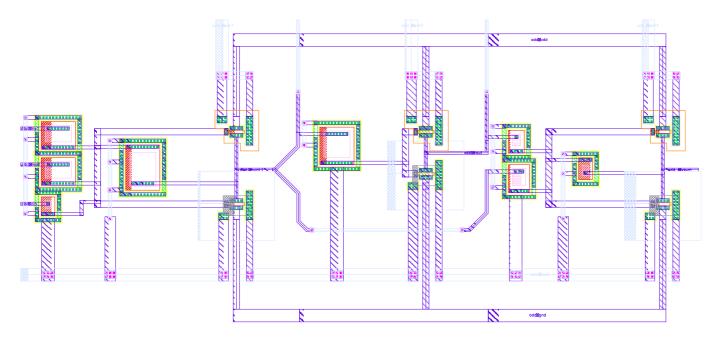

|    |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 95        |

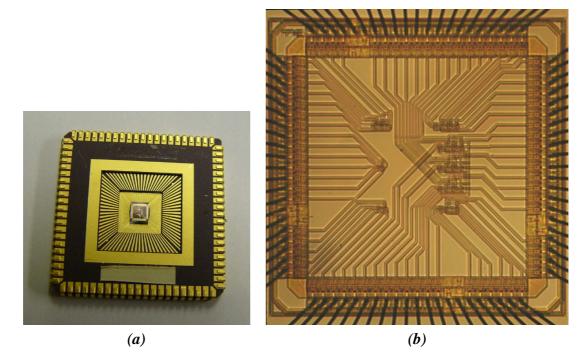

|    | C.2         | Fabricated Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | )0        |

| D  | Mat         | The second secon | 01        |

|    | D.1         | Simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | )1        |

|    |             | D.1.1 Binary Inverter Presentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |

|    |             | D.1.2 Multiple-Valued Inverter Presentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |

|    |             | D.1.3 Binary to Multiple-Valued Converter Presentation 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

|    |             | D.1.4 Multiple-Valued to Binary Converter Presentation 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | )5        |

|    |             | D.1.5 Multiple-Valued Adder Presentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |

|    | D.2         | Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

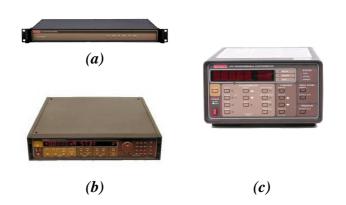

|    |             | D.2.1 UV-light Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12        |

|    |             | D.2.2 Programming Voltages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |

|    |             | D.2.3 UV-light Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |

|    |             | D.2.4 Initializing Measurement Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13        |

|    |             | D.2.5 BMVC Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |

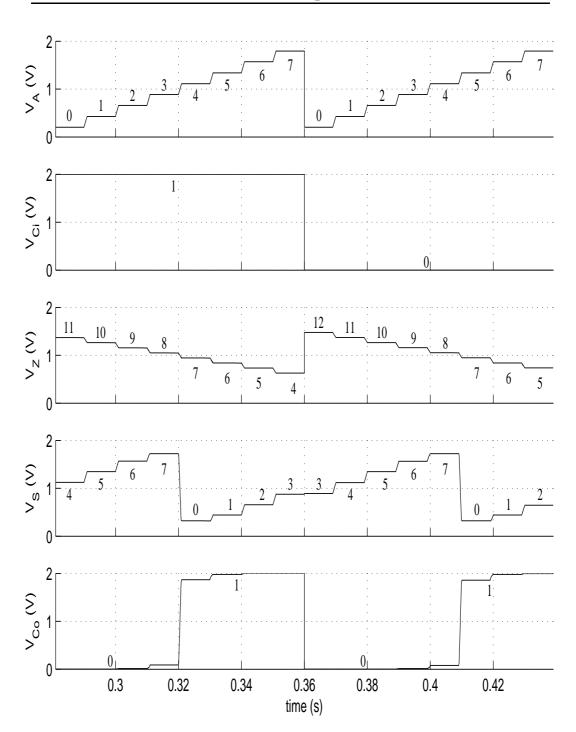

|    |             | D.2.6 BMVC Presentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 18        |