## UiO **Department of Informatics** University of Oslo

# Accelerating Numerical Simulations on Multiple GPUs with Multiple CUDA Streams

Applied on a Sediment-Transport Model for Dual Lithologies

Heidi-Christin Bernhoff-Jacobsen Master's Thesis Spring 2015

# Accelerating Numerical Simulations on Multiple GPUs with Multiple CUDA Streams

Heidi-Christin Bernhoff-Jacobsen

Spring 2015

# Contents

| Co | onten   | ts                                                      | ii   |

|----|---------|---------------------------------------------------------|------|

| Li | st of l | Figures                                                 | vi   |

| Li | st of [ | Tables                                                  | vii  |

| Li | st of A | Acronyms                                                | viii |

| 1  | Intr    | roduction                                               | 1    |

|    | 1.1     | Background                                              | 1    |

|    | 1.2     | Motivation                                              | 3    |

|    | 1.3     | Document Structure/Chapter Overview                     | 3    |

| 2  | The     | sis Domain                                              | 5    |

|    | 2.1     | Sediment Transport Model                                | 5    |

|    | 2.2     | Area of Interest Used for Testing                       | 6    |

|    | 2.3     | The Computer System                                     | 6    |

|    | 2.4     | Speedup                                                 | 7    |

|    | 2.5     | Thesis Questions and Problems to be Solved              | 8    |

|    | 2.6     | Contribution of This Work                               | 9    |

| 3  | Met     | hodology                                                | 11   |

|    | 3.1     | Paradigms for The Discipline of Computing               | 11   |

|    | 3.2     | The Numerical Method For Partial Differential Equations | 12   |

|    |         | 3.2.1 Stability                                         | 12   |

|    | 3.3     | The Variables                                           | 12   |

|    | 3.4     | The Data                                                | 13   |

|    | 3.5     | Domain Decomposition Method                             | 13   |

|    | 3.6     | Empirical Research Method                               | 14   |

|    |         | 3.6.1 Quantitative Analysis                             | 15   |

|    |         | 3.6.2 Qualitative Analysis                              | 15   |

|   | 3.7  | Enhan    | ncement Methods And Techniques                    |      | 15 |

|---|------|----------|---------------------------------------------------|------|----|

| 4 |      |          | ematical Model                                    |      | 17 |

|   | 4.1  |          | erical Analysis of a                              |      |    |

|   |      |          | Sediment Transport Model                          |      | 17 |

|   | 4.2  |          | erical Scheme                                     |      | 20 |

|   |      | 4.2.1    |                                                   |      | 20 |

|   |      | 4.2.2    | 1                                                 |      | 20 |

|   |      | 4.2.3    | 5 1                                               |      | 20 |

|   |      | 4.2.4    | Ī                                                 |      | 21 |

|   |      |          | 4.2.4.1 Spatial Discretization on Diffusion       |      | 22 |

|   |      |          | 4.2.4.2 Spatial Discretization on Convection      |      | 23 |

|   |      |          | 4.2.4.3 Boundary Condition (BC)                   |      | 23 |

|   |      | 4.2.5    |                                                   |      | 26 |

|   |      | 4.2.6    | Numerical Scheme for Convection                   |      | 28 |

| 5 | Higl | h Perfoi | rmance Computing (HPC)                            |      | 31 |

|   | 5.1  | Superc   | computing in a Historical Perspective             |      | 32 |

| 6 | Para | allel Co | omputer Architectures                             |      | 35 |

|   | 6.1  |          | el Computing                                      |      | 35 |

|   |      | 6.1.1    |                                                   |      |    |

|   |      |          | A Scheme for Parallel Architectures               |      | 35 |

|   |      | 6.1.2    |                                                   |      | 37 |

|   |      |          | 6.1.2.1 The Task/Channel Model for Parallel Archi | tec- |    |

|   |      | ( 1 0    | tures)                                            |      | 37 |

|   |      | 6.1.3    | 1 1                                               |      | 39 |

|   |      |          | 6.1.3.1 CUDA - Compute Unified Device Architec    |      | 39 |

|   |      |          | 6.1.3.2 CUDA C Programming Model                  |      | 41 |

| 7 |      |          | eous Computing with CUDA C                        |      | 47 |

|   | 7.1  | Hetero   | ogeneous Computing                                |      | 47 |

|   | 7.2  | Paralle  | el Programming Features in CUDA C                 |      | 48 |

|   |      | 7.2.1    | Parallel kernel                                   |      | 48 |

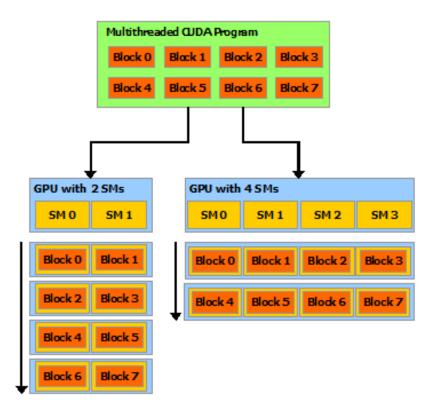

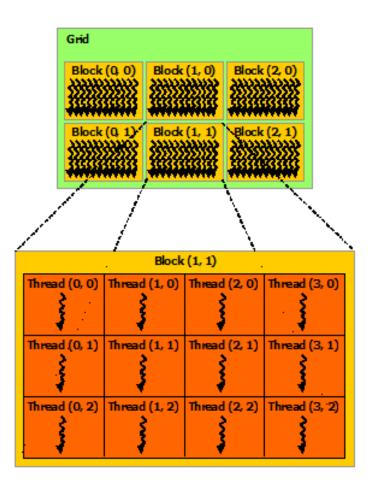

|   |      | 7.2.2    | Scalability                                       |      | 48 |

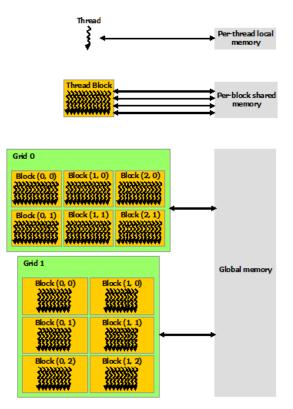

|   |      | 7.2.3    | CUDA Device Memory                                |      | 49 |

|   |      |          | 7.2.3.1 Linear memory                             |      | 50 |

|   |      |          | 7.2.3.2 Page-Locked Host Memory                   |      | 50 |

|   |      | 7.2.4    | Synchronous Execution                             |      | 51 |

|   |      | 7.2.5    | Asynchronous Concurrent Execution                 |      | 52 |

|   |      | 7.2.6    | CUDA Streams                                      |      | 52 |

|       |          | 7.2.6.1                                 | Streams and Events on a Multi-GPU application   | 52       |

|-------|----------|-----------------------------------------|-------------------------------------------------|----------|

|       |          | 7.2.6.2                                 | Synchronization                                 | 53       |

|       | 7.2.7    | CUDA Ev                                 | •                                               | 53       |

|       | 7.2.8    | CUDA Fe                                 | eatureas for a Multi-GPU System                 | 54       |

|       |          | 7.2.8.1                                 | Peer-to-Peer (P2P) Memory Access                | 54       |

|       |          | 7.2.8.2                                 | Peer-to-Peer (P2P) Memory Copy                  | 55       |

|       |          | 7.2.8.3                                 | Unified Virtual Address Space (UVA)             | 56       |

|       |          | 7.2.8.4                                 | Peripheral Component Interconnect Express (PCIe | ) 56     |

| Impl  | ementa   | tion of the                             |                                                 |          |

| Sedin | ment Tr  | ansport N                               | Iodel                                           | 57       |

| 8.1   | Analysi  | is of a Para                            | allel Architecture for the                      |          |

|       |          |                                         |                                                 | 58       |

|       | 8.1.1    | The Task/                               | Channel approach for a Parallel Architecture    | 58       |

|       |          | 8.1.1.1                                 | Partitioning                                    | 58       |

|       |          | 8.1.1.2                                 | Partitioning for a Multi-GPU system             | 59       |

|       |          | 8.1.1.3                                 | Communication                                   | 59       |

|       |          | 8.1.1.4                                 | Communication for a Multi-GPU system            | 59       |

|       |          | 8.1.1.5                                 | Agglomerating and Mapping                       | 60       |

|       |          | 8.1.1.6                                 | Agglomerating and Mapping for a Multi-GPU       |          |

|       |          |                                         | system                                          | 61       |

| 8.2   |          |                                         | Regarding Both                                  |          |

|       | Serial a |                                         | I Implementations                               | 61       |

|       | 8.2.1    |                                         | for Implementation                              | 62       |

|       |          | 8.2.1.1                                 | Spatial and Time Intervals - dx, dy and dt      | 65       |

|       |          | 8.2.1.2                                 | Ghost Points                                    | 66       |

|       |          | 8.2.1.3                                 | Influx                                          | 66       |

|       | 8.2.2    |                                         | Data Read Into The System With The              |          |

|       |          |                                         | Library                                         | 67       |

|       | 8.2.3    |                                         | les                                             | 68       |

|       | 8.2.4    | Coalesceo                               | d Memory                                        | 69       |

| 8.3   |          | -                                       | ation with ANSI C                               | 69       |

| 0.4   | 8.3.1    |                                         | n of Coalesced Memory for the Serial Code       | 69       |

| 8.4   |          | arallelization of Serial Code using the |                                                 |          |

|       |          |                                         | on                                              | 70       |

|       | 8.4.1    |                                         | n and Copying of Coalesced Memory               | 71       |

|       | 0 4 0    |                                         | rallel Code                                     | 71       |

|       | 8.4.2    |                                         | and Blocks in a Grid                            | 72<br>72 |

|       | 8.4.3    |                                         | on for a Single GPU                             | 73<br>74 |

|       | 8.4.4    |                                         | ons for Multiple GPUs                           | 74<br>75 |

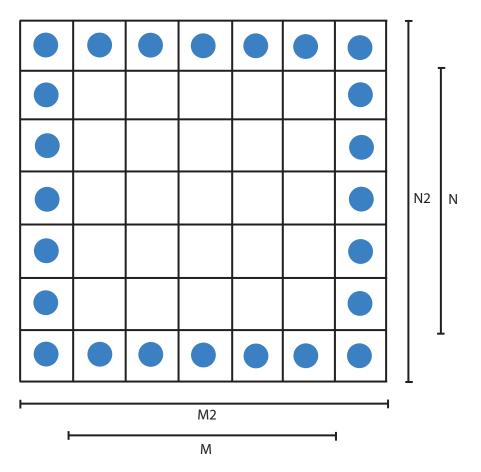

|       |          | 8.4.4.1                                 | Data Decomposition                              | 75       |

8

|     |        | 8.4.4.2           | Pinned Memory on Host | 78  |

|-----|--------|-------------------|-----------------------|-----|

|     |        | 8.4.4.3           | Implementation 2      | 79  |

|     |        | 8.4.4.4           | Implementation 3      | 82  |

|     |        | 8.4.4.5           | Implementationn 4     |     |

|     |        | 8.4.4.6           | Implementation 5      | 85  |

|     |        | 8.4.4.7           | Implementation 6      | 86  |

|     |        | 8.4.4.8           | CUDA Kernels          | 87  |

| 9   | Perf   | ormance Analysis  | S                     | 89  |

|     | 9.1    | •                 |                       | 89  |

|     | 9.2    |                   |                       |     |

|     | 9.3    |                   |                       |     |

|     | 9.4    |                   |                       |     |

|     | 9.5    | The Karp-Flatt M  | ſetric                | 90  |

|     | 9.6    | The Isoefficiency | Metric                | 90  |

| 10  | Con    | clusion           |                       | 91  |

|     | 10.1   | Summary           |                       | 91  |

|     |        |                   |                       |     |

|     |        |                   |                       |     |

|     | 10.3   |                   |                       |     |

| A   | List   | of Code Example   | 25                    | 103 |

| Bil | oliogr | aphy              |                       | 104 |

# **List of Figures**

| 4.1  | 5 Point Stencil                                                   | 22 |

|------|-------------------------------------------------------------------|----|

| 5.1  | Tianhe-2, Chinese Supercomputer                                   | 33 |

| 6.1  | GPU devoting more transistors to data processing than CPU [NVIDIA |    |

|      | CUDA Toolkit Documentation, v7.0]                                 | 40 |

| 6.2  | GPU Computing Applications [NVIDIA CUDA Toolkit Documen-          |    |

|      | <i>tation</i> , v7.0]                                             | 41 |

| 6.3  | The CUDA Architecture [NVIDIA CUDA Toolkit Documentation,         |    |

|      | <i>v</i> 7.0]                                                     | 42 |

| 6.4  | Automatic scalability in the CUDA architecture [NVIDIA CUDA       |    |

|      | <i>Toolkit Documentation</i> , v7.0]                              | 43 |

| 6.5  | Grid of thread block in the CUDA architecture [NVIDIA CUDA        |    |

|      | <i>Toolkit Documentation, v7.0</i> ]                              | 44 |

| 6.6  | Memory Hierarchy of the CUDA architecture [REF: NVIDIA] .         | 46 |

| 8.1  | One Row of Ghost Points Around the Boundary                       | 66 |

| 8.2  | Domain Decomposed on GPUs                                         | 76 |

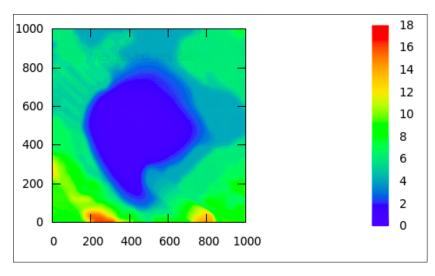

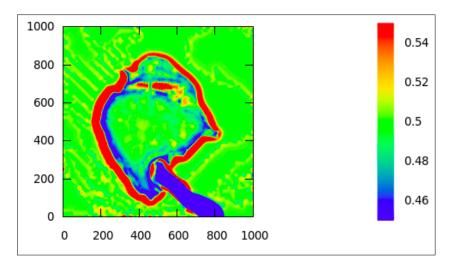

| 10.1 | Solution of <i>h</i> after 1000 years                             | 94 |

| 10.2 | Solution of <i>s</i> after 1000 years                             | 94 |

|      | -                                                                 |    |

# **List of Tables**

| 2.1  | Questions This Thesis Aims To Answer                               | 9   |

|------|--------------------------------------------------------------------|-----|

| 4.1  | Varibles for the Mathematical Model                                | 18  |

| 4.2  | Transport Coefficients for Sand and Mud                            | 19  |

| 4.3  | Derivation of the Formulas for Boundary Conditions at the Influx . | 25  |

| 6.1  | Flynn's Taxonomy for Parallel Computer Architecture                | 36  |

| 6.2  | CUDA Memory Hierarchy                                              | 40  |

| 7.1  | CUDA's Hierarchical Execution Model                                | 48  |

| 7.2  | Levels of Parallelism in CUDA                                      | 49  |

| 7.3  | Different "kinds" of Memory Copy in CUDA                           | 50  |

| 8.1  | Additional Variables for the Programmed Code                       | 64  |

| 8.2  | Implementations with Various Features for Parallel Architecture .  | 71  |

| 10.1 | Available GPUs for Testing                                         | 91  |

| 10.2 | Implementation Specifications                                      | 93  |

| 10.3 | Speedup on GeForce GTX 590 for the maximum of 4 GPUs               | 96  |

| 10.4 | Speedup on Tesla K20 for the maximum of 2 GPUs                     | 97  |

| 10.5 | Answers to the Thesis Questions                                    | 100 |

# List of Acronyms

| CPU    | Central Processing Unit                                 |

|--------|---------------------------------------------------------|

| GPU    | Graphics Processing Unit                                |

| GPGPU  | General-purpose computing on Graphics Processing Units  |

| HPC    | High Performance Computing                              |

| PDE    | Partial Differential Equation                           |

| PDE's  | Partial Differential Equation's                         |

| CFD    | Computational Fluid Dynamics                            |

| FDM    | Finite Difference Method                                |

| f FEM  | Finite Element Method                                   |

| FVM    | Finite Volume Method                                    |

| FTCS   | Forward Time Centered Space                             |

| DDT    | Domain Decomposition Methods                            |

| BVP    | Boundary Value Problem                                  |

| BC     | Boundary Condition                                      |

| CUDA   | Compute Unified Device Architecture                     |

| SM     | Stream Multiprocessor                                   |

| SM's   | Stream Multiprocessor's                                 |

| SP     | Stream Processor                                        |

| SP's   | Stream Processor's                                      |

| IPCs   | Interprocessor Communications                           |

| PCB    | Printed Circuit Board                                   |

| I/O    | Input/Output                                            |

| UVA    | Unified Virtual Addressing                              |

| PCIe   | Peripheral Component Interconnect Express (PCI Express) |

| OpenMP | Open Multi Processing                                   |

| MPI    | Message Passing Interface                               |

| SISD   | Single Instruction, Single Data stream                  |

| SIMD   | Single Instruction, Multiple Data stream                |

| MIMD   | Multiple Instruction, Multiple Data streams             |

| MISD   | Multiple Instruction, Single Data streams               |

| SIMT   | Single Instruction, Multiple Threads                    |

|        | -                                                       |

# Chapter 1

# Introduction

Improving the overall computational time is one of the challenges in scientific computing today. Performing simulations and visualizations of large data have been very slow or impossible to do on desktop computers or laptops. This is due to the limited processing capacity of these computers' Central Processing Unit (CPU). This thesis will investigate the field of High Performance Computing (HPC) and the possibility of running the simulations of a sediment transport model in parallel on the many cores of the Graphics Processing Unit (GPU), and observe if these computations will perform faster, and yield results with the same accuracy as a CPU. It will also look at the possibility of coupling multiple GPUs, and observe if that will give an additional speedup.

### 1.1 Background

In the field of scientific computing/computational science, mathematical models and quantitative analysis techniques are used to solve a big specter of scientific problems. Computers are used to perform simulations of the modeled equations and other forms of computations. With the computer simulation we get a solution that is a numerical approximations to the problem we are aiming to solve. Numerical simulations can be performed in many various fields and with different objectives, such as reconstructing and understanding events like earthquakes and tsunamis, or predicting the future like a weather forecast or predicting unobserved events such as where to find oil. Other fields where this is used include medical applications, various physical phenomenon and rocket science.

Computer programs have traditionally been written for serial computations. Problems have been broken down to a set of instructions that have been executed sequentially, one after another, on a single core on the Central Processing Unit (CPU). The CPUs have over the last years moved away from having one core to having multiple cores that can run in parallel. In 2006 Intel released a dual-core processor called Intel Core 2 Duo, and CPUs with 4, 8, 16 and more processors has been produced since then. The mainstream desktop computers and laptops sold today have multi-core processors, a single CPU with two or more processing units called cores, that can run multiple instructions simultaneously. To perform a simulation with billions of computations on a CPU with e.g. 8 cores running in parallel will still take a very long time, and we see that for such cases the multi-core CPUs still have their limitations. Coupling multiple CPUs into a cluster has been done to increase processing speed, but the purchase of all the units for such a cluster is often rather expensive. Reducing cost is one of the motifs why this thesis investigates the use of GPUs. Another motif is reducing computational time by running simulations on parallel computers.

For certain problems in the field of scientific computing, the graphics card, has been used to do the computations. The GPU is a circuit board originally designed to rapidly alternate and render graphics on the computer screen. The possibility to use the GPU to other tasks than graphics rendering has made scientists explore the GPU's architecture through General-Purpose computing on Graphics Processing Units (GPGPU).

Accelerators such as GPUs are used to speed up computationally-intensive tasks. These are also implemented in supercomputers around the world used by e.g. researchers.

Compute Unified Device Architecture (CUDA) [*NVIDIA CUDA Toolkit Documentation, v7.0*] is a parallel computing platform and programming model. It allows software developers to access the power of GPUs through the CUDAaccelerated libraries end extensions to standard programming languages such as C, C++, Fortran etc.

The CUDA architecture available on NVIDIA graphics cards will be tested in this thesis, allowing the simulations of ["Application of a dual-lithology, depthdependent diffusion equation in stratigraphic simulation"] sediment transport model to run in parallel on a single GPU. Coupling of multiple GPUs will also be tested. Both the single- and multi-GPU will be tried with synchronous and asynchronous simulations. The asynchronous version will perform the communication between the GPU and CPU, or between the multiple GPU's simultaneously with the computations, and by that aim to avoid the overhead due to communications (between the nodes). Here the communication between the GPUs will be tested using the Peripheral Component Interconnect Express (PCI Express, also abbreviated PCIe). Computer busses move information between the different parts of the hardware in a computer system including the CPU, RAM and peripheral devices. The PCIe is an expansion bus that in this case moves information between the nodes of an GPU. In addition to running parallel code on multiple GPUs, multiple OpenMP threads will will be spawn on the CPU to reduce kernel launch overhead

The geological phenomenon described in the equation set derived by [*Rivenæs* 1993] is one of many in the field of geology and geophysics. On the path to the numerical solution to the mathematical sediment transport model, the equation set is discretized using a Finite Difference method according the Forward-Time Central-Space (FTCS) scheme.

The software is then implemented for GPU's produced by Nvidia in CUDA C and additional OpenMP threads, but also in plain C for CPU(s). The CPU implementation is used for comparison of speedup.

### 1.2 Motivation

The major motivation behind this work is to reduce computational time. The results of large systems can take hours, days or moths to compute. For both research and the industry reducing the overall computing time means money saved. For business it may result in getting a product out on the market sooner, and in research it means moving forward towards new findings. Getting results faster is an important goal for everyone.

### **1.3 Document Structure/Chapter Overview**

**Chapter 1:** Introduction presents the problem and why the filed is interesting to investigate.

**Chapter 2:** Thesis Domain describes the problem to be investigated more thoroughly, and give a more precise description of the problem to be analized.

Chapter 3: Describes the different methodologies.

**Chapter 4:** Presents the mathematical model, discretizing schema and boundaryand initial conditions.

Chapter 5: Gives an overview of High Performance Computing.

Chapter 6: Presents Parallel Architectures, Flynn's taxonomy and Foster's methodology.

Chapter 7: Presents the features in CUDA C applied in this thesis.

**Chapter 8:** Presents details in the various implementations of the sediment transport.

Chapter 9: Presents a performance analysis.

Chapter 10: Results and Conclusion, contribution and future work

# Chapter 2

# **Thesis Domain**

### 2.1 Sediment Transport Model

The mathematical model investigated in this thesis is a sediment transport model evolved/described by ["Application of a dual-lithology, depth-dependent diffusion equation in stratigraphic simulation"]. The model describes an application of a two-dimensional (2D) basin simulation. It is based on topographical diffusion of a dual-lithology mass, as it runs down a dynamic slope and into a basin. The two materials are classified as sand and mud. Each lithology has its own transport-coefficient function, and the effect of compaction is included in the mass balance, as well as depth-dependent transport coefficients (diffusivities).

This physical phenomenon is described by a set of Partial Differential Equations (PDEs). The equation set is a coupled system consisting of a diffusion part and a convection part.

**Diffusion** describes/is the movement/motion of (mud/silt) molecules as it flows from one region of high concentration to a a region of low concentration along a concentration gradient. Diffusion can also relate to other matters as e.g. pressure along a pressure gradient or temperature along a temperature gradient. The word diffusion comes from the latin word "diffundere", and means "to spread out". We here use the word in the context of mass transportation.

**Convection** is another transport phenomenon in the field of physics and fluid mechanics. It describes the collective movement of groups/aggregates of molecules within fluids. It describes how the masses (of sand) moves in a circulatory motion as the variation in density (of the mud/silt) changes.

A broader elaboration of these equations will be handled in chapter 4 "The Mathematical Model". A thorough presentation is given on how to get from an equation set representing a physical model to the final computational model that is used for implementations of the system.

To be able to do the computations/simulations on a computer, the area of interest, also called domain, is separated into a grid consisting of discrete grid points. Calculations on our equations are performed for each grid-point. The equationsystem consists of various variables that may hold different values on the different grid-points.

**Forward-Time Central-Space (FTCS)** scheme is the **Finite Difference Method** used to discretize the equations. In the **numerical analysis** the path to an algorithm representing the numerical approximation of the analog equations is displayed.

Other extensive details regarding the analysis of **Computational Fluid Dynamics** (**CFD**) are presented in the same chapter.

#### 2.2 Area of Interest Used for Testing

The area of interest that will be focused on when testing the numerical algorithms is situated in Florida. More specificly **Lake Okeechobee** and the **Kissimmee River**. The lake is remarkably shallow with a maximum depth of only 4 m. and an average depth of 2.7 m. The Kissimmee River is the single contributor of sediments to the lake, counting for 30% of the (water-)volume added to the lake. High resolution data for the lake's bathymetry are derived from depth sounding, and they are publicly available. These data will be utilized in the simulated model.

#### 2.3 The Computer System

The application is based on the numerical model of a 2D system with time series. In the process of implementing a computer system for the sediment-transport model, there are several considerations to be taken. The simulations of this model are to be run for large data-sets and it will be computing-heavy. If the system is to be computed on a CPU of any desktop computer, even the more powerful ones, it will most probably take terribly long time. The widely used term **Big Data** can be be used when simulating a numerical model as the sediment-transport model and with data-sets as large as the ones for Lake Okeechobee, since this yields a system so large and complex that traditional data processing applications are inadequate. For that reason this thesis will investigate the field of **High Performance Computing (HPC)**, which is the practice of aggregating computing power that delivers a much higher performance than than what is possible on a single CPU.

This system consists of a set of numerical PDE's to be computed for a large set for grid points. At each grid point computations on the same equations will be performed, but the values of the equation's variables may differ from one grid point to the next. In a multiprogramming context, this system classifies under the **Singel Instruction, Multiple Data streams (SIMD)** paradigm. This means that the system may benefit from an implementation made for a parallel computer architecture. In a parallel context this thesis will investigate the use of hardware accelerators such as the GPUs produced by NVIDIA, a bleeding edge technology.

In the process of the thesis work there will be two main implementations. The first is a serial application made for computations on a CPU, the next is a parallel implementation made to run on a single GPU. The development of the parallel code normally demands extended programming skills that can take time to master and take in use. On the other hand, if the parallel system runs much faster than the serial system then there are tremendous benefits. A further extension is to evolve the parallel system to run on multiple GPU's of an arbitrary number. One focus will then be on GPU's sharing the same PCI Express bus for data transfer.

The programing languages that will be used are C for the serial system to run on a CPU, and C with the CUDA extensions/bindings called CUDA C, used for the parallel GPU-version. Multiple technologies such as CUDA C combined withe Open MP threads will be tested for the implementation of the multi-GPU application.

Further details on HPC will be surveyed in the Chapter 5. Details regarding CUDA C programming will be targeted in the Chapter 7.

### 2.4 Speedup

Measurements of performance will be made for the different systems, and they will be compared in various ways. The performance enhancement can be measured using speedup as a quantifying metric for relative performance improvement. More on this topic will be surveyed in the Chapter 9: Performance Analysis.

In this research the aim is to see if there are any improvements in computational time comparing a parallel application running on a single GPU to a serial application running on a CPU. An additional focus is to see if there is even more time to save if running the system on multiple GPU's.

Another research aspect to focus on is if the parallel computations yields results with the same accuracy as the serial computations.

If the parallel system achieves a good speedup, it will open up for the possibility to run larger simulations. One possibility could be to do data-simulations over a larger grid representing a larger interest domain or it could be a more refined grid with a higher number of grid points within the same domain size, but yielding a more detailed result. Other possibilities could be the choice of extending the time series to include more time steps, or even a combination of the different options that opens up if good speedup is achieved.

So, will the parallel code run faster and yield results in shorter time than the serial code, and will the parallel code yield results with the same accuracy as the CPU?

The next section will state the questions this thesis will aim to answer.

#### 2.5 Thesis Questions and Problems to be Solved

One of the areas this thesis will investigate is wether there are any benefits in implementing a parallel system. Then another question is; if there are time to save when running the application on one GPU, will there be more time to save when run on multiple GPUs?

Performing simulations and visualizations of large data and complex systems has been very slow or impossible to compute due to the lack of computing power of the CPU. The evolution in the GPU production has been amazing over the last years, towards a circuit board adapted for heavy computations and other tasks than graphics rendering. With the use of GPGPU, a new world has opened up to computer programmers.

Here is a structured presentation of the questions this thesis will aim to answer and the problems this thesis will aim to solve.

- Q 1: Is a parallel application running on a single GPU faster than a serial application running on a CPU? And if so:

- Q 2: Is a parallel application running on multiple GPUs faster than a parallel application running on a single GPU?

- Q 3: Is the application enhancing performance utterly if additional CUDA Streams are utilized?

If the the GPU-implementations yields the results faster, then the further questions will be:

- Q 3: Does the parallel application running on a single GPU yield results with the same accuracy as the serial application running on a CPU?

- Q 4: Does the parallel application running on multiple GPU's yield results with the same accuracy as the application running on a single GPU?

Table 2.1: Questions This Thesis Aims To Answer

### 2.6 Contribution of This Work

This thesis has reached the goal the of answering the Thesis Questions in table 2.1. The goal was to enhance speedup for sediment-transport simulations, with the use of GPUs. Another goal was to achieve solutions with the same accuracy as the solution from a CPU-simulation. Through this investigation, the enhanced speedup has been more than satisfactory for simulations on both a a single GPU as well as on multiple GPUs. The numerical results yield the same accuracy on GPUs as on CPU. This clearly show the benefits of using GPUs for sediment-transport simulations.

# Chapter 3

# Methodology

### **3.1** Paradigms for The Discipline of Computing

This thesis investigates a technology-oriented discipline with fundamentals in mathematics and engineering. The discipline of computing embraces all of computer science and computer engineering. The two fields do not differ in the core material. [*Comer* et al. 1989] suggests paradigms for the discipline of computer science, and emphasizes:

- 1. Theory based in the mathematical model.

- 2. Abstraction based in experimental scientific method.

- 3. Design based in engineering, involves designing and testing a system.

With their view on methodologies for the field, this chapter presents methods utilized on the path to a solution to the problem aimed to be solved in this thesis.

The main problem to be tested is if a computer-system can enhance performance if the simulation is executed on a parallel architecture like the SIMD architecture on a GPU, compared to execution on a serial CPU.

For this purpose the chosen mathematical model is the sediment-transport model by [*Rivenæs* 1993]. This model consists of a coupled system of Partial Differential Equations (PDE's). To be able to compute the set of analog PDE's, the equations has to be discretized and for that a numerical method is needed.

### **3.2 The Numerical Method For Partial Differential** Equations

The approach to find numerical solutions to PDE's has led researchers into the field of numerical analysis, and numerous well established numerical methods has been evolved to help in this matter. Some of these method are, the Finite Difference Method (FDM), Finite Element Method (FEM) and Finite Volume Method (FVM).

On the sediment transport model the **Finite Difference Method** is applied. With this method, functions are represented by their values at discrete points in a grid. Through the differences in these values, derivatives are approximated. From the mathematical model the numerical model is derived using an **Explicit Method**. This is a discretizing method applying a forward difference in time, and central difference in space, called **Forward-Time Central-Space (FTCS)**. It is a first-order method in time and a second-order method in space. For the sediment transport model there are 2 dimensions in space, so second-order derivatives are calculated in both *x*- and *y*-direction. The calculations made for time-step  $u^l$  uses the values at calculated at timestep  $u^{l-1}$ .

#### 3.2.1 Stability

To maintain numerical stability for 1D problems with the FTCS method, the following condition has to satisfied.

$$r = \frac{\alpha \delta t}{\delta x^2} \le \frac{1}{2}$$

This means that the size of the time step,  $\delta t$  is restricted by this stability condition. For problems with large diffusivity the  $\delta t$  has to be very small. A small  $\delta t$  can be a major disadvantage of this method, as it will have to perform many time-iterations to simulate a given time period.

For systems with many variables and multiple large data-sets as the sedimenttransport system, the simulations can take a long time. Therefore numerous optimization techniques and methods will be tested and investigated in this thesis.

### 3.3 The Variables

The variables used in this investigation are given by the mathematical model by [*Rivenæs* 1993] as seen in the chapter 4. It is a massive equation system with a myriads of variables that are operated on as the numerical model is simulated

through the vey many time steps. Some of these variables holds scalars or constants, while other variables are large data-sets extracted from survey of seismic activity. The data-sets used in the computational domain is gridded for the spatial discretization.

#### **3.4** The Data

The data that will be used in the sediment-transport simulations are extracted from Lake Okeechobee in Florida. The lake is positioned in a shallow geological trough and is of the size 1.900 square kilometers (730 sq. mi). It is exceptionally shallow with an average depth of 3 meters (9 feet). The Kissimmee River gives the influx of sand and mud to the lake.

The massive data-sets used in these computations are the results of seismic measurements of Lake Okeechobee. These data are publicly available [*Gtopo30* 1996].

### 3.5 Domain Decomposition Method

In the field of numerical analysis and numerical PDE's, simulations are mostly performed over massive data-domains. Computations performed on very large data-set(s) takes time. If they are executed sequentially it takes much longer time then if they are executed in parallel on a single GPU, and even more time can be saved if run on multiple GPU's compared to a single GPU. With the purpose of the enhancement to yield a faster result, a method to run the simulations on multiple GPU's is applied. Solving boundary value problems on multiple GPU's can be done by splitting the data-domain into smaller subdomains, where computations for each subdomain are computed on one of the dedicated GPU's in the multi-GPU system. The Domain Decomposition Method (DDM) is a method that splits a data-domain into independent, adjacent subdomains. The method is ideal for parallel computing on a **Boundary Value Problems (BVP)**.

A 1D problem can only be subdivided in a 1D decomposition. Let the intervals over the linear domain M be denoted  $[m_{start}, m_{end}]$ . For a 1D domain on the interval [0, 1], if split into two equally sized subdomains, one is on the interval  $[0, \frac{1}{2}]$  and the other is on the interval  $[\frac{1}{2}, 1]$ .

A 2D-problem is exposed to a variation of decomposition possibilities. The domain can be decomposed in 1D or 2D manners. A 2D decomposition of a 2D domain is decomposed both horizontally or verti-

cally.

Let the intervals over a MxN domain be denoted  $[m_{start}, m_{end}]x[n_{start}, n_{end}]$ . With a 2x2 decomposition on the interval [0, 1]x[0, 1], the different subdomains are, when equally sized, on the intervals:

$[0, \frac{1}{2}]x[0, \frac{1}{2}], \\ [\frac{1}{2}, 1]x[0, \frac{1}{2}], \\ [0, \frac{1}{2}]x[\frac{1}{2}, 1] \text{ and } \\ [\frac{1}{2}, 1]x[\frac{1}{2}, 1]$

A 1D decomposition on a 2D domain can be decomposed horizontally or vertically.

A 1D decomposition into 4 subdomains will with a 1x4 decomposition on the interval [0,1]x[0,1] give subdomains on these intervals:

$[0,1]x[0,\frac{1}{4}], \\ [0,1]x[\frac{1}{4},\frac{1}{2}], \\ [0,1]x[\frac{1}{2},\frac{3}{4}] \text{ and} \\ [0,1]x[\frac{3}{4},1].$

If decomposed in the other direction; 4x1 on the same interval, it yields subdomains on these intervals:

$[0, \frac{1}{4}]x[0, 1],$  $[\frac{1}{4}, \frac{1}{2}]x[0, 1],$  $[\frac{1}{2}, \frac{3}{4}]x[0, 1] \text{ and }$  $[\frac{3}{4}, 1]x[0, 1].$

A 2D decomposition yields a larger number of neighbors that boundary values has to be communicated to than a 1D decomposition. Due to communicationoverhead a 2D decomposition is not necessarily a better choice than a 1D decomposition.

### **3.6 Empirical Research Method**

To evaluate the results in this research, empirical research method is used. It is a way to acquire knowledge through experimenting and testing, and it may also be achieved through direct or indirect observations or experience. Empirical evidence is the record of a someone's direct observations or experience and can be analyzed **quantitatively** or/and **qualitatively**.

Implementing, testing and comparing the applications will make up for a large part of the empirical studies in this work. There will of course be iterations of application development with the intent of making improvements. Based on the problem domain and the questions this thesis aims to solve, both a qualitative and a quantitative analysis will be made.

#### 3.6.1 Quantitative Analysis

For the quantitative analysis of the results, the execution time of the various systems are measured. This time is given by a very direct observation of benchmarking the actual speed of the executed system. Execution time for all the different systems can be compared, and by the comparison it is possible answer some of this thesis' questions.

Through the quantitative analysis of these result it is possible to decide if a parallel implementation is faster than a serial implementation, and if a parallel implementation of multiple GPU's is faster than an implementation of one GPU. It is also possible to decide if an implementation with OpenMP threads yields a faster solution.

**Performance** and **Speedup** are two "methods" to analyze the measurements and enhancement between to different systems. Both methods are in this way quantitative as both methods derive results form quantitative measurements. More about the these two methods is reviewed in the chapter on Performance Analysis 9.

#### **3.6.2** Qualitative Analysis

For a **qualitative** analysis of the results, this thesis examines the numerical results of the simulations, and makes comparisons between the serial implementation and the various parallel versions. If the different systems parallel systems, through execution, render the same correct numerical result as the serial system, it can be said that the parallel implementations produce a result of equal quality as the serial.

Although speedup and performance are analyzed qualitatively, it would be possible to say that a system that gives a noticeable speedup and improved performance, in addition to a correct numerical result of course, adds to the total quality of the application.

#### **3.7** Enhancement Methods And Techniques

Computer programs have been implemented with the aim and ambition to solve the problems this thesis states. The code has been produced with a variety of features, exploiting the possibilities that lies within the chosen technologies. Extensive empirical testing has been conducted through running the different programs evolved with the different programming details made for optimization. Along with the use of the well-established methods presented here, the research is accomplished with a great specter of enhancing programming techniques and methods. A broader explanation on how these methods and the large variety of enhancement techniques are used, is presented in several of the chapters throughout this thesis.

## Chapter 4

# **The Mathematical Model**

## 4.1 Numerical Analysis of a Dual-Sediment Transport Model

There are several numerical strategies for solving this system, and Clark et al. [*Clark, Wei*, and *Cai* 2010] has studied two of the possibilities for solving a coupled system of distinct nonlinear equations governing sediment transport of Lake Okeechobee, Florida. They used high-resolution bathymetry data of the actual lake derived from depth-sounding [*Gtopo30* 1996]. The computations were performed on a multicore-based cluster.

This thesis will investigate the numerical strategy of a fully-explicit numerical scheme, and the computations will be tested on the CUDA architecture on NVIDIA GPUs.

Erosion and deposition of sediment is a process often modeled using a diffusion equation. The speed of diffusion represents the transport efficiency of the sediment. When multiple sediments are involved in the model, one can add another equation for each sediment. Various physical processes like sediment compaction, tectonic movements and carbonate production can be governed by a numerous empirical rules, but has been neglected by Clark et al. in order to investigate the parallel performance of their diffusion equation alone.

To model sediment transport in fluvial, on- and off-shore environments, diffusion has been used. Jordan and Flemings [*Jordan* and *Flemings* 1991] suggest a model for sediment transport, approximating a slope-controlled diffusion, and their work gives the basic equation:

$$\frac{\partial h}{\partial t} = \nabla. \left( \kappa \nabla h \right) \tag{4.1}$$

#### where

h = h(x, y, t) is the height of the basin in the *x*, *y*-plane at a given time(step), *t* is the time and

$\kappa = \kappa(x, y, t)$  is the transport coefficient or the efficiency of the diffusion. This equation (4.1) was later modified by Rivenæs [*Rivenæs* 1993], so two types of sediments could be handled in the model, with one transport coefficient for each sediment.

The variables used for mathematical system are:

| Variable Name | Explanation                                |

|---------------|--------------------------------------------|

| h             | Bathymetry (Height of the basin)           |

| S             | Fraction of sand                           |

| (1-s)         | Fraction of mud/silt                       |

| α             | Transport coefficient for sand             |

| β             | Transport coefficient for mud/silt         |

| A             | Layer thickness                            |

| $C_s$         | Compaction ratio for sand                  |

| $C_m$         | Compaction ratio for mud                   |

| $f_s$         | Influx sand                                |

| $f_m$         | influx mud                                 |

| dx            | Size of spatial step in x-direction        |

| dy            | Size of spatial step in y-direction        |

| dt            | Size of time step                          |

| l             | Temporal discretization step               |

| i             | Spatial discretization step in x-direction |

| j             | Spatial discretization step in y-direction |

Table 4.1: Varibles for the Mathematical Model

$$\frac{\partial h}{\partial t} = \nabla \cdot (\alpha s \nabla h) + \nabla \cdot (\beta (1 - s) \nabla h)$$

(4.2)

and

$$A\frac{\partial s}{\partial t} + s\frac{\partial h}{\partial t} = \nabla \cdot (\alpha s \nabla h). \tag{4.3}$$

Here,

$\alpha = \alpha(x,y)$  and  $\beta = \beta(x,y)$  are the two diffusion coefficients for sand and silt/mud, and

s = s(x, y, t) and (1 - s(x, y, t)) are the corresponding fractions of the two sediment

types at a particular location. For this case *s* represents the first material, sand, and (1-s) represents the second; material, silt. Further

A is the layer thickness, representing the height of unsettled sediments in the basin, and in this case it's set to 1 m. Also, A scales the partial derivatives of s with respect to distance and determines how effective changes in h will be affecting the sediment concentration.

When taking into consideration the compaction ratio for sand and silt, the equations 4.2 and 4.3 are represented by:

$$\frac{\partial h}{\partial t} = \frac{1}{C_s} \nabla \cdot (\alpha s \nabla h) + \frac{1}{C_m} \nabla \cdot (\beta (1-s) \nabla h)$$

(4.4)

and

$$A\frac{\partial s}{\partial t} + s\frac{\partial h}{\partial t} = \frac{1}{C_s}\nabla \cdot (\alpha s \nabla h).$$

(4.5)

where

$C_s$  is the compaction ratio for sand and  $C_m$  is the compaction ratio for mud.

Water discharge rates, water-flow induced shear-stress and drag-coefficient can be neglected due to the separation of the two material types rather than having one diffusion coefficient based on grain-size.

For simplicity the values are not depth dependent, since Clark et al. [*Clark*, *Wei*, and *Cai* 2010] assume that sediment diffusion is not as vigorous in the lake as for the seashore. Therefor they utilize lower values than those suggested by the lakes mean depth of 2.7 m. In this case, they use the coefficients for sand and silt, and the table below shows the different regions with the corresponding transport coefficients in square meters per year  $(m^2/yr)$ .

| Region          | Sand $(\alpha)$ | Silt $(\beta)$ |

|-----------------|-----------------|----------------|

| Kissimmee River | 70.000          | 100.000        |

| Lake Okeechobee | 2.100           | 3.000          |

| Surronds        | 70              | 100            |

Table 4.2: Transport Coefficients for Sand and Mud

### 4.2 Numerical Scheme

The problem to be solved is a typical initial value problem. Clark et al. [*Clark*, *Wei*, and *Cai* 2010] solve the initial value problem by time integration, and at time step *l* the latest numerical solutions of *h* and *s*, denoted  $h^{l+1}$  and  $s^{l+1}$ . To have the equations system solved by a computer, the continuous equations need to be transferred into discrete counterparts by using techniques for numerical discretization. Solving the analogue equations will yield a correct result, while solving the discretized scheme will give an approximation to the solution. Various numerical discretization strategies can be chosen, but this thesis will look exclusively at the **Fully-explicit scheme**.

#### **4.2.1** Initial Condition (IC)

At the start of our simulations, at time step 0, we set the initial condition to be:

$$h(x, y, 0) = h^0(x, y)$$

$$s(x, y, 0) = s^0(x, y)$$

These initial values for h and s that are used at the start of the simulations at time step 0, come from seismic measurements of Lake Okeechobee in Florida [*Gtopo30* 1996].

#### 4.2.2 Temporal Discretization

The time domain  $0 < t \le T$  is divided into a number of equal-distanced discrete time levels with  $\Delta t$  set as the step size. The time level index is noted with l and we use superscript l such that  $h^l$  denotes  $h(x, y, l\Delta t)$  and  $s^l$  denotes  $s(x, y, l\Delta t)$ . The temporal derivatives are then approximated as:

$$\frac{\partial h}{\partial t} \approx \frac{h^{l+1} - h^l}{\Delta t}, \quad \frac{\partial s}{\partial t} \approx \frac{s^{l+1} - s^l}{\Delta t}$$

#### 4.2.3 Fully-Explicit Numerical Scheme

Using a fully explicit discretization scheme, the equations 4.4 and 4.5 are transformed into:

$$\frac{h^{l+1} - h^l}{\Delta t} = \frac{1}{C_s} \nabla \cdot (\alpha s^l \nabla h^l) + \frac{1}{C_m} \nabla \cdot (\beta (1 - s^l) \nabla h^l)$$

(4.6)

$$A\frac{s^{l+1}-s^l}{\Delta t}+s^{l+1}\frac{h^{l+1}-h^l}{\Delta t}=\frac{1}{C_s}\nabla\cdot(\alpha s^l\nabla h^{l+1})$$

(4.7)

It is to be noted that *h* is must be updated before *s* during each time-step. This is why the newly computed  $h^{l+1}$  from the first equation is immediately used to compute  $s^{l+1}$  in the second equation. Another remark is that Wei et al. [*Wei* et al. 2013] suggests  $s^{l+1}$  instead of  $s^l$ , used in the  $s\frac{\partial h}{\partial t}$  term on the left side of equation 4.5. They have shown with numerical experiments that this trick improves the numerical stability of this fully-explicit scheme in which both  $h^{l+1}$  and  $s^{l+1}$  are computed straight forwardly. The values  $h^{l+1}$  and  $s^{l+1}$  can be computed using simple algebraic operations, and exploit the advantage that no linear systems need to be solved.

The values of  $\alpha$ ,  $\beta$  and mesh spacing limits the size of  $\Delta t$  in the fully-explicit scheme. The maximum allowed  $\Delta t$  is of order  $O\left(\Delta x^2/max(\alpha,\beta)\right)$

This scheme has 1. order accuracy in time.

#### 4.2.4 Spatial Discretization

The equations 4.4 and 4.5 for respectively diffusion and convection are partially differentiatiated with respect to both x and y as represented by:

$$\frac{\partial h}{\partial t} = \frac{1}{C_s} \left( \frac{\partial}{\partial x} \left( \alpha s \frac{\partial h}{\partial x} \right) \right) + \frac{1}{C_s} \left( \frac{\partial}{\partial y} \left( \alpha s \frac{\partial h}{\partial y} \right) \right) + \frac{1}{C_m} \left( \frac{\partial}{\partial x} \left( \beta \left( 1 - s \right) \frac{\partial h}{\partial x} \right) \right) + \frac{1}{C_m} \left( \frac{\partial}{\partial y} \left( \beta \left( 1 - s \right) \frac{\partial h}{\partial y} \right) \right)$$

(4.8)

and

$$A\frac{\partial s}{\partial t} + s\frac{\partial h}{\partial t} = \frac{1}{C_s} \left( \frac{\partial}{\partial x} \left( \alpha s \frac{\partial h}{\partial x} \right) \right) + \frac{1}{C_s} \left( \frac{\partial}{\partial y} \left( \alpha s \frac{\partial h}{\partial y} \right) \right)$$

$$= \frac{1}{C_s} \left[ \left( \frac{\partial}{\partial x} \left( \alpha s \frac{\partial h}{\partial x} \right) \right) + \left( \frac{\partial}{\partial y} \left( \alpha s \frac{\partial h}{\partial y} \right) \right) \right]$$

(4.9)

Motivated by numerical and programming simplicity, [*Wei* et al. 2013] use **Finite Differences** for the spatial discretization.

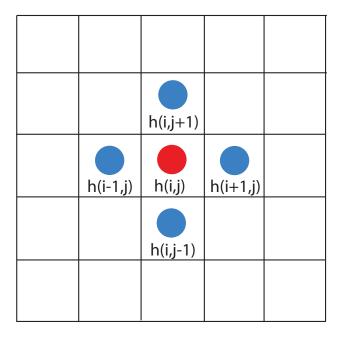

The 5-point stencil applied on this application is displayed in figure 4.1:

Figure 4.1: 5 Point Stencil

#### 4.2.4.1 Spatial Discretization on Diffusion

**Centered Difference** in space is a standard way that will be used for the two diffusion terms on the right hand side of 4.4, and this will give a second-order accuracy in space. Applying centered difference to the  $\nabla \cdot (\alpha s \nabla h)$  term yields the following discretized form:

$$\nabla \cdot (\alpha s \nabla h) = \frac{\alpha_{(i+1/2,j)} s_{(i+1/2,j)} (h_{(i+1,j)} - h_{(i,j)}) - \alpha_{(i-1/2,j)} s_{(i-1/2,j)} (h_{(i,j)} - h_{(i-1,j)})}{\Delta x^2} + \frac{\alpha_{(i,j+1/2)} s_{(i,j+1/2)} (h_{(i,j+1)} - h_{(i,j)}) - \alpha_{(i,j-1/2)} s_{(i,j-1/2)} (h_{(i,j)} - h_{(i,j-1)})}{\Delta y^2}$$

(4.10)

where the subscripts *i*, *j* are the indices at a grid point in a 2D uniform mesh with the mesh spacing  $\Delta x$  and  $\Delta y$ . The half-indexed terms in the formula 4.10 are

evaluated as:

$$\alpha_{(i+1/2,j)}s_{(i+1/2,j)} = (\alpha_{(i,j)} s_{(i,j)} + \alpha_{(i+1,j)} s_{(i+1,j)})/2$$

#### 4.2.4.2 Spatial Discretization on Convection

Equation 4.5 is a convection equation with respect to s, due to the term  $\nabla(\alpha s \nabla h)$ . To obtain numerical stability, one-sided upwind finite difference is preferred over centered difference, although it has a first order accuracy. Therefore, when checking the flow direction, the convection term  $\nabla(\alpha s \nabla h)$  is moved to the left side of the equation, as customary. By this  $-\nabla h$  gives the convection velocity. The approximation of the x-component,  $-\partial h/\partial x \approx (h_{i-1,j} - h_{i+1,j})/2\Delta x$ , and the sign determines how the x-component of the convection term is discretized by one-sided upwind difference. More specifically, if  $h_{i-1,j} > h_{i+1,j}$  approximation with this schema is used:

$$\frac{\partial}{\partial x} \left( \alpha s \frac{\partial h}{\partial x} \right) \approx \left( \frac{\alpha_{ij} s_{ij} - \alpha_{i-1j} s_{i-1j}}{\Delta x} \right) \times \left( \frac{h_{i+1j} - h_{i-1j}}{2\Delta x} \right)$$

(4.11)

otherwise this is used:

$$\frac{\partial}{\partial x} \left( \alpha s \frac{\partial h}{\partial x} \right) \approx \left( \frac{\alpha_{i+1j} s_{i+1j} - \alpha_{ij} s_{ij}}{\Delta x} \right) \times \left( \frac{h_{i+1j} - h_{i-1j}}{2\Delta x} \right)$$

(4.12)

In the y-direction the discretization is done similarly.

#### 4.2.4.3 Boundary Condition (BC)

In the numerical model most of the boundary has a no-flow condition. The entire boundary is using **Homogeneous Neumann Boundary Condition**, and it is described as follows:

$$\frac{\partial h}{\partial n} = \frac{\partial s}{\partial n} = 0 \tag{4.13}$$

One part of the boundary has a non-zero inflow along a 1.5 km wide channel representing the River Kissimmee. Where a river crosses the boundary of the

solution domain, the **Dirichlet Boundary Condition** is set for *s* and the non-zero **Inhomogeneous Neumann BC** is set for  $\frac{\partial h}{\partial n}$ . By this, the system allows specifications of an inflow of 80% mud and 20% sand.

On this part of the boundary the fluxes of sand and mud inflow are prescribed as:

$$-\alpha s \frac{\partial h}{\partial n} = f_s \tag{4.14}$$

$$-\beta(1-s)\frac{\partial h}{\partial n} = f_m \tag{4.15}$$

These boundary conditions model an inflow of sediments due to e.g. a river crossing the boundary of the solution domain.

#### **Treatment of the Boundary Condition (BC):**

The boundaries can then be described by two parts.

Most of the boundary has a no-flow condition using a second-order accurate treatment of the Homogeneous Neumann BC:

$$\frac{\partial h}{\partial n} = \frac{\partial s}{\partial n} = 0 \tag{4.16}$$

The standard approach by using one layer of ghost points around the boundary points is applied.

Along domain where the river Kissimmee crosses the boundary, special treatment is needed for the inhomogeneous influx conditions The two conditions, 4.14 and 4.15, can be rewritten into the following equivalent form:

$$\frac{\partial h}{\partial n} = -\frac{f_s}{\alpha} - \frac{f_m}{\beta} \tag{4.17}$$

$$s = \frac{\beta f_s}{\beta f_s + \alpha f_m} \tag{4.18}$$

Here h is an Inhomogeneous Neumann BC and s takes a Dirichlet BC. The derivation of the formulas for the boundary conditions where we have the influx can be seen i Table 4.3.

| Influx Sand                                                                     | Influx Mud                                                                                                       |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| $f_s = -\alpha s \frac{\partial h}{\partial n}$                                 | $f_m = -\beta \left(1 - s\right) \frac{\partial h}{\partial n}$                                                  |

| $\implies \frac{f_s \partial n}{-\alpha \partial h} = s$                        |                                                                                                                  |

| substitute sand's expression for s into the mud eqn.                            | $\implies f_m = -\beta \left(1 - \frac{f_s \partial n}{-\alpha \partial h}\right) \frac{\partial h}{\partial n}$ |

|                                                                                 | $\implies f_m = -\beta \left( \frac{\partial h}{\partial n} + \frac{f_s}{\alpha} \right)$                        |

|                                                                                 | $\implies -\frac{f_m}{\beta} = \frac{\partial h}{\partial n} + \frac{f_s}{\alpha}$                               |

|                                                                                 | $\implies \frac{\partial h}{\partial n} = -\frac{f_s}{\alpha} - \frac{f_m}{\beta}$                               |

| rewrite the expression for sand                                                 |                                                                                                                  |

| $\implies \frac{f_s}{-\alpha \frac{\partial h}{\partial n}} = s$                |                                                                                                                  |

|                                                                                 | substitute mud's expression for $\frac{\partial h}{\partial n}$ into the sand eqn.                               |

| $\implies s = rac{f_s}{-lpha \left( -rac{f_s}{lpha} - rac{f_m}{eta}  ight)}$ |                                                                                                                  |

| $\implies s = rac{f_s}{f_s + rac{lpha f_m}{eta}}$                             |                                                                                                                  |

| $\implies s = rac{\beta f_s}{\beta f_s + \alpha f_m}$                          |                                                                                                                  |

Table 4.3: Derivation of the Formulas for Boundary Conditions at the Influx

#### 4.2.5 Numerical Scheme for Diffusion

Recalling the temporal and the spatial discretization schema with the superscript l for temporal discretization and the subscripts i and j for spatial discretization in respectively x and y direction. These schemas are applied on the derivative of the diffusion equation as seen in equation 4.8 and yields this discretized equation:

The diffusion is then solved with respect to  $h^{l+1}$ , displayed in equation (4.20). This will also be the numerical schema used for the implementation of the diffusion.

$$h_{ij}^{t+1} = \frac{\Delta t}{C_s} \left[ \left[ \frac{\left( \left( (\alpha_{ij}s_{lj}^t + \alpha_{i+1j}s_{l+1j}^t)/2 \right) \cdot \left( h_{i+1j}^t - h_{ij}^t \right) \right) - \left( \left( (\alpha_{i-1}s_{l-1j}^t + \alpha_{ij}s_{lj}^t)/2 \right) \cdot \left( h_{ij}^t - h_{i-1j}^t \right) \right)}{\Delta x^2} \right] + \frac{\Delta t}{C_m} \left[ \frac{\left( \left( (\alpha_{ij}s_{lj}^t + \alpha_{i+1}s_{lj+1}^t)/2 \right) \cdot \left( h_{ij+1}^t - h_{ij}^t \right) \right) - \left( \left( (\alpha_{ij-1}s_{lj-1}^t + \alpha_{ij}s_{lj}^t)/2 \right) \cdot \left( h_{ij-1}^t - h_{ij-1}^t \right) \right)}{\Delta y^2} \right] \right] + \frac{\Delta t}{C_m} \left[ \left[ \frac{\left( \left( (\beta_{ij}(1 - s_{lj}^t) + \beta_{i+1j}(1 - s_{l+1j}^t))/2 \right) \cdot \left( h_{i+1j}^t - h_{ij}^t \right) \right) - \left( \left( (\beta_{i-1j}(1 - s_{l-1j}^t) + \beta_{ij}(1 - s_{lj}^t))/2 \right) \cdot \left( h_{ij}^t - h_{i-1j}^t \right) \right)}{\Delta x^2} \right] + h_{lj}^{t} \right] + h_{lj}^{t} \left[ \frac{\left( \left( (\beta_{ij}(1 - s_{lj}^t) + \beta_{ij+1}(1 - s_{l+1j}^t))/2 \right) \cdot \left( h_{i+1j}^t - h_{ij}^t \right) \right) - \left( \left( (\beta_{i-1j}(1 - s_{l-1j}^t) + \beta_{ij}(1 - s_{lj}^t))/2 \right) \cdot \left( h_{lj}^t - h_{l-1j}^t \right) \right)}{\Delta x^2} \right] + h_{lj}^{t} \right]$$

(4.20)

27

# 4.2.6 Numerical Scheme for Convection

For convection the discretization schema is applied on the derivative of the equation, as displayed in 4.9:

$$A\left(\frac{s^{l+1}-s^{l}}{\Delta t}\right) + s^{l+1}\left(\frac{h^{l+1}-h^{l}}{\Delta t}\right) = \frac{1}{C_{s}}\left[f...\right]$$

$$A\left(s^{l+1}-s^{l}\right) + s^{l+1}\left(h^{l+1}-h^{l}\right) = \frac{\Delta t}{C_{s}}\left[f...\right]$$

$$As^{l+1}-As^{l} + s^{l+1}h^{l+1} - s^{l+1}h^{l} = \frac{\Delta t}{C_{s}}\left[f...\right]$$

$$As^{l+1} + s^{l+1}h^{l+1} - s^{l+1}h^{l} = \frac{\Delta t}{C_{s}}\left[f...\right] + As^{l}$$

$$s^{l+1}\left(A + \left(h^{l+1}-h^{l}\right)\right) = \frac{\Delta t}{C_{s}}\left[f...\right] + As^{l}$$

$$\frac{s^{l+1}\left(A + h^{l+1}-h^{l}\right)}{\left(A + h^{l+1}-h^{l}\right)} = \frac{\frac{\Delta t}{C_{s}}\left[f...\right] + As^{l}}{\left(A + h^{l+1}-h^{l}\right)}$$

$$s^{l+1} = \frac{\frac{\Delta t}{C_{s}}\left[f...\right] + As^{l}}{\left(A + h^{l+1}-h^{l}\right)}$$

When the expression for the function as shown in the section on Spatial Discretization of Convction 4.2.4.2 is filled in between the hard brackets with respect to x and y in solution (4.21), the first line of the equation (4.21) will result in this discretized expression:

$$A\left(\frac{s_{ij}^{l+1} - s_{ij}^{l}}{\Delta t}\right) + s_{ij}^{l+1}\left(\frac{h_{ij}^{l+1} - h_{ij}^{l}}{\Delta t}\right) = \begin{cases} \frac{1}{C_{s}} \left[ \left(\frac{\alpha_{ij}s_{ij}^{l} - \alpha_{i-1j}s_{i-1j}^{l}}{\Delta x}\right) \times \left(\frac{h_{i+1j}^{l+1} - h_{i-1j}^{l+1}}{2\Delta x}\right) \right], & h_{i-1j} > h_{i+1j} \\ \frac{1}{C_{s}} \left[ \left(\frac{\alpha_{i+1j}s_{i+1j}^{l} - \alpha_{ij}s_{ij}^{l}}{\Delta x}\right) \times \left(\frac{h_{i+1j}^{l+1} - h_{i-1j}^{l+1}}{2\Delta x}\right) \right], & h_{i-1j} < h_{i+1j} \end{cases}$$

$$+ \begin{cases} \frac{1}{C_{s}} \left[ \left(\frac{\alpha_{ij}s_{ij}^{l} - \alpha_{ij-1}s_{ij-1}^{l}}{\Delta y}\right) \times \left(\frac{h_{ij+1}^{l+1} - h_{ij-1}^{l+1}}{2\Delta y}\right) \right], & h_{ij-1} > h_{ij+1} \end{cases}$$

$$+ \begin{cases} \frac{1}{C_{s}} \left[ \left(\frac{\alpha_{ij+1}s_{ij+1}^{l} - \alpha_{ij}s_{ij}^{l}}{\Delta y}\right) \times \left(\frac{h_{ij+1}^{l+1} - h_{ij-1}^{l+1}}{2\Delta y}\right) \right], & h_{ij-1} > h_{ij+1} \end{cases}$$

$$(4.22)$$

The last line in equation (4.21) shows this result when it is fully discretized with respect to  $s^{l+1}$ :

$$s_{ij}^{l+1} = \begin{cases} \frac{\Delta t}{C_s} \left[ \left( \frac{\alpha_{ij} s_{ij}^l - \alpha_{i-1j} s_{i-1j}^l}{\Delta x} \right) \times \left( \frac{h_{i+1j}^{l+1} - h_{i-1j}^{l}}{2\Delta x} \right) \right] + A s_{ij}^l \\ \frac{A + h_{ij}^{l+1} - h_{ij}^l}{\left( A + h_{ij}^{l+1} - h_{ij}^l \right)}, \quad h_{i-1j} > h_{i+1j} \\ \frac{\Delta t}{C_s} \left[ \left( \frac{\alpha_{i+1j} s_{i+1j}^l - \alpha_{ij} s_{ij}^l}{\Delta x} \right) \times \left( \frac{h_{i+1j}^{l+1} - h_{i-1j}^{l+1}}{2\Delta x} \right) \right] + A s_{ij}^l \\ \frac{A + h_{ij}^{l+1} - h_{ij}^l}{\left( A + h_{ij}^{l+1} - h_{ij}^l \right)}, \quad h_{i-1j} < h_{i+1j} \end{cases}$$

(4.23)

$$+ \begin{cases} \frac{\Delta t}{C_{s}} \left[ \left( \frac{\alpha_{ij} s_{ij}^{l} - \alpha_{ij-1} s_{ij-1}^{l}}{\Delta y} \right) \times \left( \frac{h_{ij+1}^{l+1} - h_{ij-1}^{l+1}}{2\Delta y} \right) \right] + A s_{ij}^{l}, & h_{ij-1} > h_{ij+1} \\ \frac{\Delta t}{C_{s}} \left[ \left( \frac{\alpha_{ij+1} s_{ij+1}^{l} - \alpha_{ij} s_{ij}^{l}}{\Delta y} \right) \times \left( \frac{h_{ij+1}^{l+1} - h_{ij-1}^{l+1}}{2\Delta y} \right) \right] + A s_{ij}^{l}, & h_{ij-1} < h_{ij+1} \\ \frac{\Delta t}{(A + h_{ij}^{l+1} - h_{ij}^{l})}, & (A + h_{ij}^{l+1} - h_{ij}^{l+1}) \end{cases}$$

# **Chapter 5**

# **High Performance Computing** (**HPC**)

Before describing the implementation of both the serial and the parallel applications, a survey on ideas and concepts regarding High Performance Computing (HPC) will be presented in this chapter. HPC is the use of parallel processing technologies for running applications efficiently. The efficiency can be measured in different ways.

**Clock speed/Clock rate** is the time used by a microprocessor to execute an instruction. All computers contains a clock that regulates the speed. Clock rates are expressed in megahertz (MHz) or gigahertz (GHz).

**Throughput** is a measure of how many units of information a (computer-) system can process in a given time-period. The throughputs are often described as **FLoating-point OPerations per Second (FLOPS)**. This is a benchmark measurement for the speed of microprocessors.

The earliest supercomputers had a throughput measured in

kiloFLOPS (KFLOPS) =  $10^3$  FLOPS and

megaFLOPS (MFLOP) =  $10^6$  FLOPS.

For supercomputers today we are talking about throughput measured in teraFLOPS  $(TFLOPS) = 10^{12}$  FLOPS and

petaFLOPS (PFLOPS) =  $10^{15}$  FLOPS.

Eager scientists are even looking towards exa-scale computing for a throughput on the size of exaFLOPS (EFLOPS) =  $10^{18}$  FLOPS.

The term HPC applies to systems performing above a teraflop  $(10^{12})$  floating point operations per second.

# 5.1 Supercomputing in a Historical Perspective

The basic components used for electronics in radios, televisions, radars, telephones and computers was the vacuum tube (electron tube), a device that was used to control electrical current through a vacuum in a sealed container. The ones with a control grid could also be used as amplifiers. The vacuum tubes was invented in 1907 and are mostly used until the first half of the twentieth century.

In 1947 came the first transistor, a semiconductor device used to amplify and switch electronic signal and electrical power, invented by the American physicists John Bardeen, Walter Brattain, and William Shockley. The transistor revolutionized the field of electronics, and the inventors were rewarded the Nobel Prize in Physics in 1956.

Among the advantages that have allowed the transistors to replace the vacuum tube processors are lower power dissipation and higher energy efficiency.

The first electronic general purpose computer was **Electronic Numerical Integrator and Computer (ENIAC)**. It was Turing-complete (computationally universal) and reprogrammable to solve a large class of numerical problems. The press called it "Giant Brain" when it was announced in 1946. It was primarily designed to calculate artillery firing tables for the US Army.

The **Turing machine** is named after the British pioneering computer scientist, mathematician, cryptanalyst and logician, Alan Mathison Turing (1912-1954). With the development of the Turing machine, a theoretical or hypothetical device, he formalized the concepts of "algorithm" and "computation". An algorithm is a step-by-step set of operations/instructions to be performed, and computation is a calculation or use of computing technology in information processing.

In the 1960's various supercomputers were introduced.

As early as November 1959 the **IBM** 7090 was installed, designed for large-scale scientific and technological applications. This was a transistorized version of the earlier IBM 709, a vacuum tube computer. The processing speed was around 100 KFLOP/s and about six times faster than the 709.

The first **Atlas** supercomputer was commissioned in 1962 and installed at the University of Manchester. The machine used discrete germanium transistors to lower the voltage.

Another supercomputer was introduced by Seymour Cray, and in 1976 the 80 MHz **Cray**-1 system was installed with a single CPU. The 80 MFLOPS Cray-1 was in 1982 succeeded by the 800 MFLOPS Cray X-MP, the first multi-processing computer. This was a shared-memory parallel vector processor with a clock cycle of 9.5 nano seconds (ns) (105 MHz) compared to Cray-1's clock cycle of 12.5 ns. A vector processor, or array processor, is a CPU that has implemented an instruction set able to operate on one-dimensional arrays called vectors, in contrast to a scalar processor that only operates on single data units. In 1984 an improved model of the Cray X-MP came with up to a four-processor system.

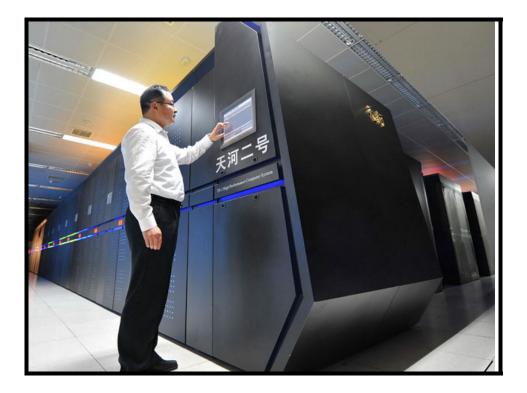

Twice a year the TOP500 list of supercomputers [*Top500List* 2015] is published, and one machine has been on the top of the list the last times the list has come out. China's **Tianhe-2** supercomputer, which translates to "Milky Way 2", has been the fastest in the world since June 2013. It runs at 33.86 petaFLOPS (PFLOPS), or 33.86 quadrillion floating point operations per second. Or in other words; 33.86 thousand million million floating point operations per second.

Figure 5.1: Tianhe-2, Chinese Supercomputer

# **Chapter 6**

# **Parallel Computer Architectures**

# 6.1 Parallel Computing

Workstations today are a hundred times faster than the ones made a decade ago. Yet scientists and engineers still experience that "fast" isn't fast enough. Waiting for hours, days or even weeks for larges computations to finish can be costly. The use of a parallel computers to solve a computational problem is called parallel computing, and is widely used to solve large problems. A parallel computer is a multi-processor computer system where computations on different processors are run in parallel. The use of parallel architectures to solve computational problem often saves a lot of time, but it is important to make the right choices of computer architecture and algorithm design, to achieve the most optimal result.

# 6.1.1 Flynn's Taxonomy -A Scheme for Parallel Architectures

Operations processed in a computer is a set of instructions that operates on a set of data operands. These processes can be executed as a stream of instructions operating on a stream of data. The possibility of multiplicity in the streams of instructions and data lies in the computer architecture.

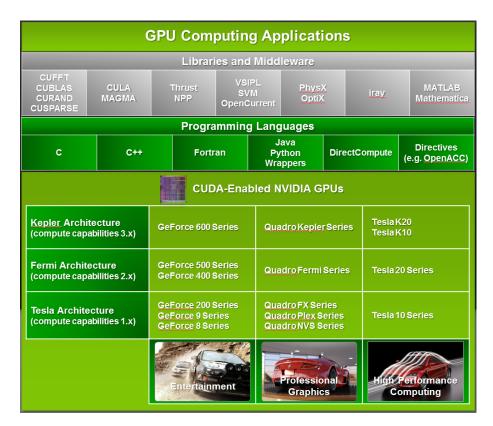

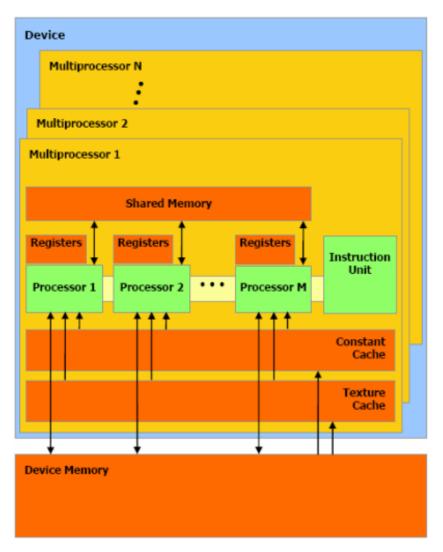

A well-known classifications scheme for parallel computer architectures is Flynn's Taxonomy, proposed by Michael J. Flynn in 1966 [*Quinn* 2003]. In this scheme a computer is categorized on it's ability to exhibit parallelism in the instruction stream and the data stream., see figure 6.1

|               | Single Instruction | Multiple Instructions       |

|---------------|--------------------|-----------------------------|

| Single Data   | SISD               | SIMD                        |

|               | Uniprocessors      | Processor arrays            |

|               |                    | Pipelined vector processors |

| Data          | MISD               | MIMD                        |

| Multiple Data | Systolic arrays    | Multiprocessors             |

| Mul           |                    | Multicomputers              |

Table 6.1: Flynn's Taxonomy for Parallel Computer Architecture

## Single Instruction, Single Data stream (SISD)

This is the architecture of a sequential computer which exploits no parallelism neither in the instruction nor data streams. An example is the **uniprocessor**, a system where all processing tasks share a single CPU.

### Single Instruction, Multiple Data stream (SIMD)

Computers with this architecture employ a single instruction stream but multiple data streams. **Processor arrays** and **pipelined vector processors** are examples in this category, and both technologies employs a single control unit executing one instruction or instruction stream at the time. A processor array has multiple processor elements operating in parallel on multiple data elements in a data stream, and the same instruction is performed on each data element. The vector processor has a single processor element that operates in sequence on the data elements.

# Multiple Instruction, Single Data streams (MISD)

The MISD architecture employs a pipeline of multiple independently executing instructions performed on a single data stream. The **systolic array** exemplifies this kind of computer, forwarding results from one function to the next on a single data element.

### Multiple Instruction, Multiple Data streams (MIMD)

The MIMD class of parallel architectures is for computers consisting of multiple instruction streams performed on multiple data streams. **Multiprocessors** and **multicomputers** fit into this category, and both architectures are based on multiple CPU's where the different CPU's simultaneously execute different instructions streams on multiple data elements. This has possibly been the most familiar form of parallel architectures.

# 6.1.2 Designing a Parallel Algorithm

# 6.1.2.1 The Task/Channel Model for Parallel Architectures)

When designing a parallel algorithm, Ian Fosters [*Quinn* 2003] **task/channel methodology** can be used. The model is intended for MIMD architectures, and not for SIMDs. MIMD architectures are multi-processors and multi-computers witch consists of multiple CPU's with a shared memory. The MIMD architecture typically have fewer processors than the SIMD does.

In the case of constructing the algorithm for the numerical model for sediment transport, the channel/task method will be presented here to enlighten a few topics around choices for designing parallel algorithms.