UNIVERSITY OF OSLO Department of Informatics

Distributed computing with the Cell Broadband Engine

Master thesis

Martin Wam

November, 2010

## Distributed computing with the Cell Broadband Engine

Martin Wam

November, 2010

## Contents

| Abstract vi        |       |            |                                                        | viii |

|--------------------|-------|------------|--------------------------------------------------------|------|

| Acknowledgements x |       |            |                                                        | x    |

| Nomenclature x     |       |            | xii                                                    |      |

| 1                  | Intro | troduction |                                                        |      |

|                    | 1.1   | Backg      | round and motivation                                   | 1    |

|                    | 1.2   | Proble     | em Statement                                           | 4    |

|                    | 1.3   | Main       | Contributions                                          | 4    |

|                    | 1.4   | Outlir     | ne                                                     | 5    |

| 2                  | Back  | cgroun     | d                                                      | 7    |

|                    | 2.1   | Introd     | uction                                                 | 7    |

|                    | 2.2   | Multi-     | core architectures                                     | 8    |

|                    |       | 2.2.1      | Multi-core design approaches                           | 8    |

|                    |       | 2.2.2      | Homogeneous and Heterogeneous Multi-Core Architectures | 10   |

|                    |       | 2.2.3      | Multi-core challenges                                  | 10   |

|                    | 2.3   | The C      | ell Broadband Engine                                   | 13   |

|                    |       | 2.3.1      | Hardware overview                                      | 14   |

|                    |       | 2.3.2      | Overcoming the limitations                             | 17   |

|                    |       | 2.3.3      | Inter-process communication                            | 18   |

|                    |       | 2.3.4      | Bit ordering and bit numbering                         | 20   |

|                    |       | 2.3.5      | PlayStation 3 and Linux                                | 21   |

|                    | 2.4   | Paralle    | el programming and programming models                  | 22   |

|                    |       | 2.4.1      | Terminology                                            | 22   |

|                    |       | 2.4.2      | Amdahl's Law and Gustafson's Law                       | 25   |

|                    |       | 2.4.3      | Parallelism Challenges                                 | 26   |

|   |                   | 2.4.4   | Parallel programming models and strategies | 28 |  |  |

|---|-------------------|---------|--------------------------------------------|----|--|--|

|   | 2.5               | Relate  | d Work                                     | 29 |  |  |

|   |                   | 2.5.1   | The MARS framework                         | 29 |  |  |

|   |                   | 2.5.2   | OpenCL                                     | 33 |  |  |

|   |                   | 2.5.3   | MapReduce                                  | 35 |  |  |

|   | 2.6               | Summ    | ary                                        | 38 |  |  |

| 3 | Des               | ign     |                                            | 41 |  |  |

|   | 3.1               | U       | uction                                     | 41 |  |  |

|   |                   | 3.1.1   |                                            | 42 |  |  |

|   |                   | 3.1.2   |                                            | 43 |  |  |

|   | 3.2               | Desig   |                                            | 44 |  |  |

|   | 3.3               |         |                                            | 45 |  |  |

|   |                   | 3.3.1   |                                            | 45 |  |  |

|   |                   | 3.3.2   | Runtime configuration                      | 45 |  |  |

|   |                   | 3.3.3   |                                            | 46 |  |  |

|   | 3.4               | Cell B  |                                            | 47 |  |  |

|   |                   | 3.4.1   |                                            | 47 |  |  |

|   |                   | 3.4.2   |                                            | 48 |  |  |

|   |                   | 3.4.3   |                                            | 49 |  |  |

|   | 3.5               | Summ    | ary                                        | 51 |  |  |

| 4 | Implementation 53 |         |                                            |    |  |  |

| - | 4.1               | -       |                                            |    |  |  |

|   |                   | 4.1.1   | -                                          | 53 |  |  |

|   |                   | 4.1.2   |                                            | 56 |  |  |

|   |                   |         |                                            | 57 |  |  |

|   |                   | 4.1.4   |                                            | 57 |  |  |

|   | 4.2               | Cell B  |                                            | 58 |  |  |

|   |                   | 4.2.1   |                                            | 58 |  |  |

|   |                   | 4.2.2   | c .                                        | 60 |  |  |

|   |                   | 4.2.3   | Connection Manager                         | 61 |  |  |

|   |                   | 4.2.4   | 0                                          | 62 |  |  |

|   |                   | 4.2.5   |                                            | 63 |  |  |

|   | 4.3               | Summ    |                                            | 63 |  |  |

| 5 | Mot               | ion IPF | EG Video Coding                            | 65 |  |  |

| 0 | 5.1               | -       |                                            | 65 |  |  |

|   |                   | 8       |                                            |    |  |  |

|   |      | 5.1.1                   | Color space conversion             | 5  |  |  |

|---|------|-------------------------|------------------------------------|----|--|--|

|   |      | 5.1.2                   | Downsampling and block splitting 6 | 6  |  |  |

|   |      | 5.1.3                   | Discrete Cosine Transform          | ,7 |  |  |

|   |      | 5.1.4                   | Quantization                       | 8  |  |  |

|   |      | 5.1.5                   | Entropy coding                     | 9  |  |  |

|   | 5.2  | Adapt                   | ion for our framework 7            | 0  |  |  |

|   |      | 5.2.1                   | Implementation                     | 0  |  |  |

|   |      | 5.2.2                   | Evaluation                         | '3 |  |  |

|   | 5.3  | Lessor                  | ns learned                         | '5 |  |  |

|   | 5.4  | Summ                    | ary                                | '6 |  |  |

| 6 | Adv  |                         | 51                                 | 7  |  |  |

|   | 6.1  | Backg                   | round information                  | 7  |  |  |

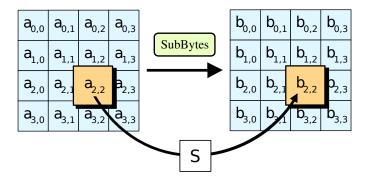

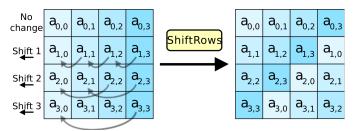

|   |      | 6.1.1                   | AES Cipher overview7               | '8 |  |  |

|   |      | 6.1.2                   | Modes of operation                 | ;1 |  |  |

|   | 6.2  | Softwa                  | are basis                          | 2  |  |  |

|   | 6.3  | Adapt                   | ion for our framework              | 2  |  |  |

|   |      | 6.3.1                   | Implementation                     | 2  |  |  |

|   |      | 6.3.2                   | Evaluation                         | 3  |  |  |

|   | 6.4  | Lessor                  | ns learned                         | 4  |  |  |

|   | 6.5  | Summ                    | ary                                | 6  |  |  |

| 7 | Disc | Discussion 8            |                                    |    |  |  |

|   | 7.1  | Results and performance |                                    |    |  |  |

|   | 7.2  | Applicability           |                                    |    |  |  |

|   | 7.3  | Future                  | possibilities                      | 0  |  |  |

|   |      | 7.3.1                   | Workload communication             | 0  |  |  |

|   |      | 7.3.2                   | Data distribution and compression  | 1  |  |  |

|   |      | 7.3.3                   |                                    | 92 |  |  |

|   | 7.4  | Final t                 | houghts                            | 3  |  |  |

| 8 | Con  | clusion                 | 9                                  | 95 |  |  |

|   | 8.1  | Summ                    | ary                                | 95 |  |  |

|   | 8.2  | Furthe                  | er work                            | 96 |  |  |

|   | 8.3  | Conclu                  | usion                              | 97 |  |  |

## Appendix

### Bibliography

100

# **List of Figures**

| 2.1  | Three different multi-core designs [1]                                 | 9            |

|------|------------------------------------------------------------------------|--------------|

| 2.2  | Distributed caches and cache coherence                                 | 11           |

| 2.3  | Cell Broadband Engine Architecture Overview.                           | 14           |

| 2.4  | Cell BE PPE block diagram.                                             | 15           |

| 2.5  | Cell SPE block diagram.                                                | 16           |

| 2.6  | Big-Endian byte and bit ordering. Figure taken from the Cell Broadband |              |

|      | Engine Programming Handbook [2]                                        | 21           |

| 2.7  | The potential speed-up of parallelization according to Amdahl's Law.   |              |

|      | Illustration is taken from Wikipedia [3]                               | 25           |

| 2.8  | Work distribution models.                                              | 28           |

| 2.9  | A host centric programming model. Figure is taken from the MARS        |              |

|      | documentation. [4]                                                     | 31           |

| 2.10 | An MPU centric programming model. Figure is taken from the MARS        |              |

|      | documentation. [4]                                                     | 31           |

| 2.11 | MARS kernel state diagram. Figure is taken from the MARS documen-      |              |

|      | tation. [4]                                                            | 32           |

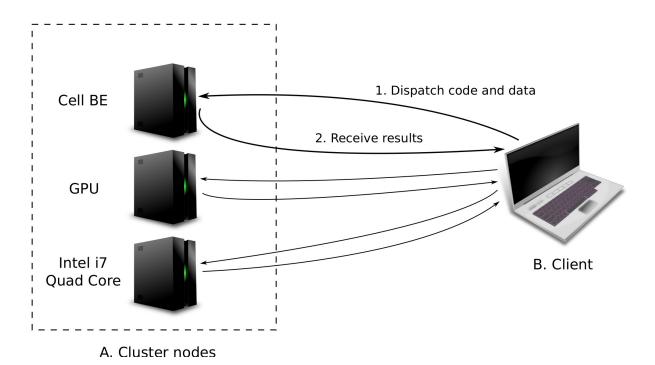

| 3.1  | Distributed offloading scenario.                                       | 42           |

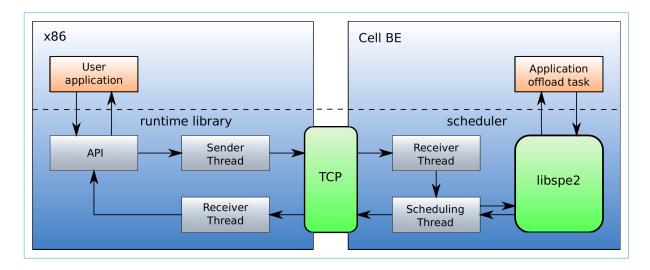

| 3.2  | System flow.                                                           | 44           |

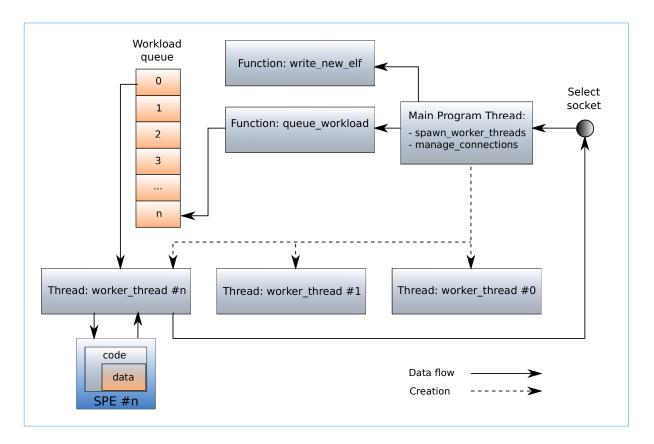

| 3.3  | An overview of the workload scheduler                                  | 48           |

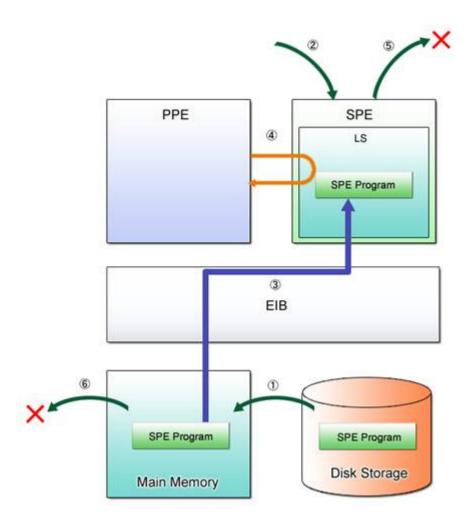

| 4.1  | SPE Program Execution Sequence. Illustration taken from the Cell Pro-  |              |

|      | gramming Primer [5]                                                    | 60           |

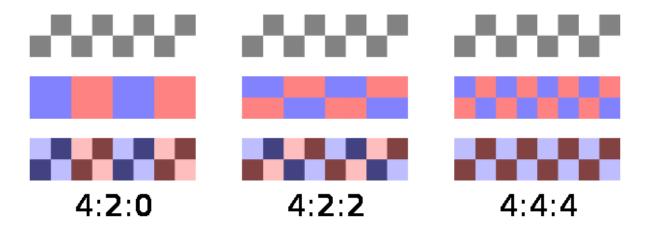

| 5.1  | Common downsampling ratios for JPEG. Modified illustration from Wikipe | edia [6]. 66 |

| 5.2  | Zig-zag pattern. Illustration from Wikipedia [7].                      | 69           |

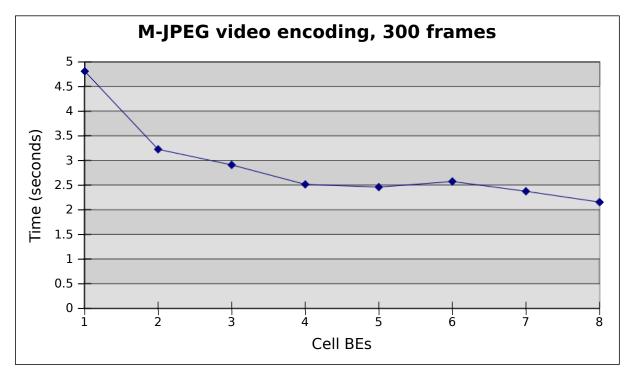

| 5.3  | A benchmark of M-JPEG video encoding using one to eight Cell BEs       | 73           |

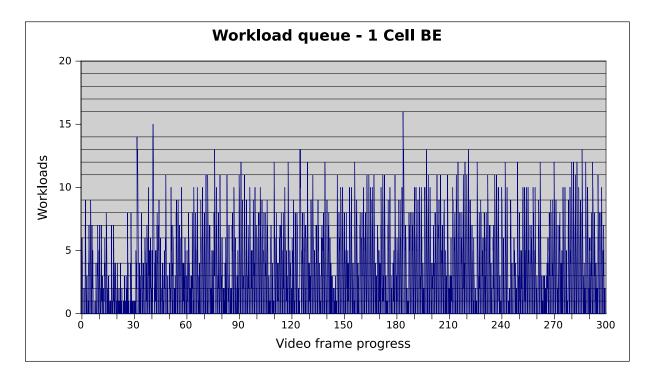

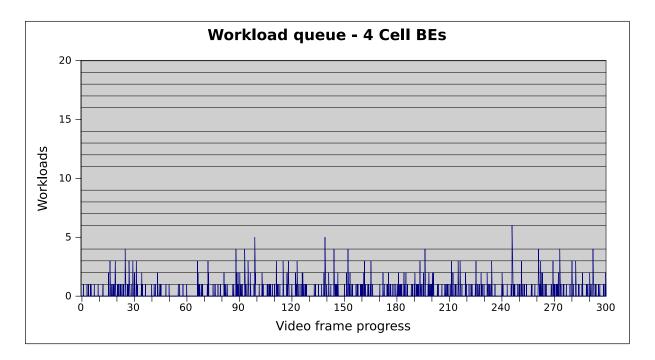

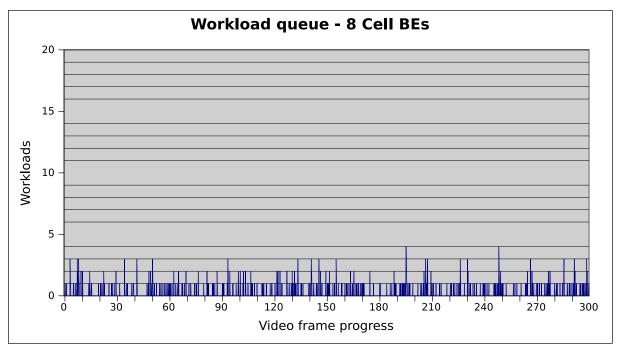

| 5.4  | Scheduler queue during encoding, client offloading to 1 node           | 74           |

| 5.5  | Scheduler queue during encoding, client offloading to 4 Cell BEs       | 75           |

|      |                                                                        |              |

| 5.6 | Scheduler queue during encoding, client offloading to 8 Cell BEs          | 75          |

|-----|---------------------------------------------------------------------------|-------------|

| 6.1 | Substitute Bytes. Illustration from Wikipedia [8]                         | 79          |

| 6.2 | Shift Rows. Illustration from Wikipedia [8]                               | 79          |

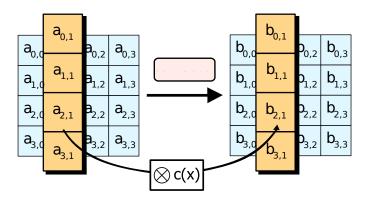

| 6.3 | Mix Columns. Illustration from Wikipedia [8]                              | 80          |

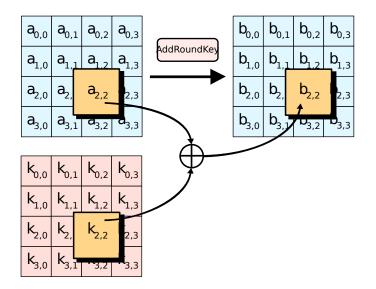

| 6.4 | Add Round Key. Illustration from Wikipedia [8]                            | 80          |

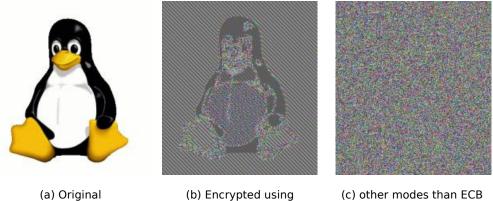

| 6.5 | Comparison of encryption using different modes. Illustration from Wikiped | dia [9]. 81 |

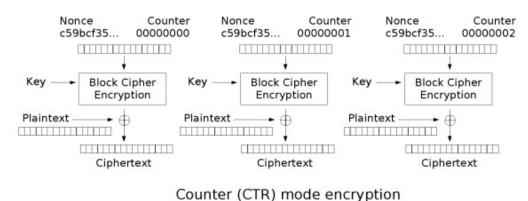

| 6.6 | Counter mode (CTR) block encryption. Illustration from Wikipedia [9]      | 82          |

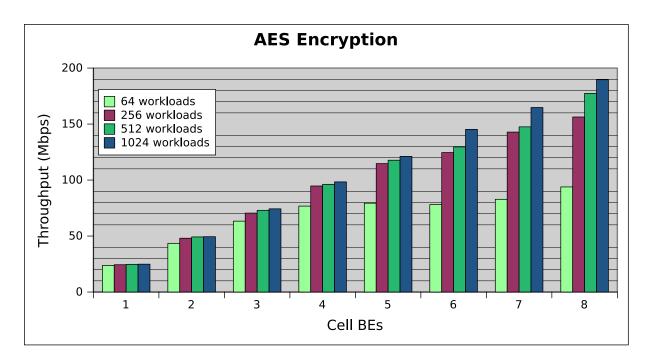

| 6.7 | A benchmark of AES with increasingly added nodes                          | 84          |

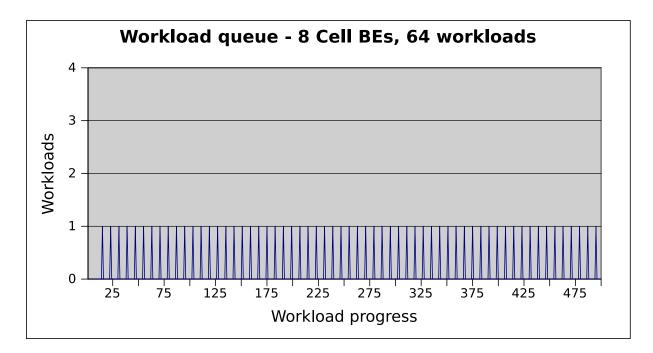

| 6.8 | Scheduler queue during encryption, client offloading to 8 Cell BEs, with  |             |

|     | 64 workloads each pass                                                    | 85          |

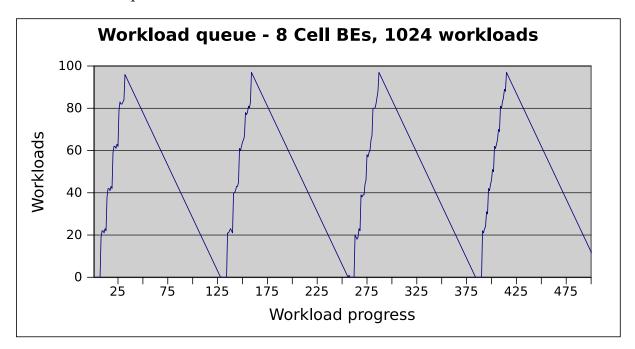

| 6.9 | Scheduler queue during encryption, client offloading to 8 Cell BEs, with  |             |

|     | 1024 workloads each pass                                                  | 85          |

## Abstract

The rapid improvements in the availability of commodity high-performance components has resulted in a proliferation of networked devices, making scalable computing clusters the standard platform for many high-performance and large-scale applications. However, the process of parallelizing applications for such distributed environments is a challenging task, requiring explicit management of concurrency and data locality. While there exists many frameworks and platforms to assist with this process, like Google's MapReduce, Microsoft's Dryad and Azure, Yahoo's Pig Latin programming language, and the Condor framework, they are usually targeted towards off-line batch processing of large quantities of data, contrary to real-time offloading of compute intensive tasks. Moreover, MapReduce, Dryad, and Pig Latin may not be suitable for all application domains, due to their inability to model branching and iterative algorithms.

In this thesis, we present a design for a framework able to accelerate applications by offloading compute intensive tasks to a heterogeneous distributed environment, and provide a prototype implementation for the Cell Broadband Engine. We evaluate the framework performance and scalability, and propose several future enhancements to further increase performance. Our results show that compute intensive applications that allow for high numbers of concurrent jobs fits well to our framework, and shows good scalability.

# Acknowledgements

I would like to thank my supervisors Håvard Espeland, Pål Halvorsen and Carsten Griwodz for their guidance and inspiring attitude. Without their invaluable feedback, this work would not have been possible.

I would also like to thank the guys at the Simula lab for a great work environment, with great conversations and good laughs.

Last but not least, I would like to thank my family and girlfriend, for continued support, encouragement and endless motivation.

Oslo, November 8. 2010 Martin Wam

# Nomenclature

| DMA  | Direct Memory Access                 |

|------|--------------------------------------|

| EA   | Effective Address                    |

| EIB  | Element Interconnect Bus             |

| GPP  | General Purpose Processor            |

| IPC  | Inter-process communication          |

| LS   | Local Store                          |

| LSA  | Local Store Address                  |

| MARS | Multicore Application Runtime System |

| MFC  | Memory Flow Controller               |

| MMIO | Memory Mapped I/O                    |

| MMU  | Memory Management Unit               |

| PPE  | PowerPC Processor Element            |

| PPU  | PowerPC Processor Unit               |

| SIMD | Single-instruction, multiple-data    |

| SPE  | Synergistic Processor Element        |

| SPU  | Synergistic Processor Unit           |

## Chapter 1

## Introduction

### **1.1 Background and motivation**

From the introduction of the first general-purpose electronic computer in 1946, development of processor architectures has ushered in a constant change to satisfy the ever increasing demand for processing power. Intel's co-founder Gordon E. Moore published a paper in 1965, describing a trend where the number of components in integrated circuits had doubled every two years, and would continue to do so for the at least another decade [10]. This trend came to be known as Moore's Law, and has proven to be fairly accurate, as it has continued to hold true for more than half a century.

Due to the physical limitations of the transistor technology, further increases in processor clock frequency is heavily constrained by power consumption and heat generation, entailing the need for manufacturers to make architectural design changes. On a chip produced using AMD's 90mm process, power consumption increases by 60% with every 400 MHz rise in clock speed [11]. To keep fulfilling Moore's Law, manufacturers have shifted the focus from maximizing single-core performance, to increasing the number of processor cores per socket, known as multi-core architectures. However, the single threaded application does not typically benefit from these architectures, and may actually suffer from degraded performance, due to the lowered clock speed of each core. The shift towards new multi-core architectures poses several challenges to the application writer, mainly how the potential processing power can translate into an equal increase in computational performance. In addition to the cumbersome pro-

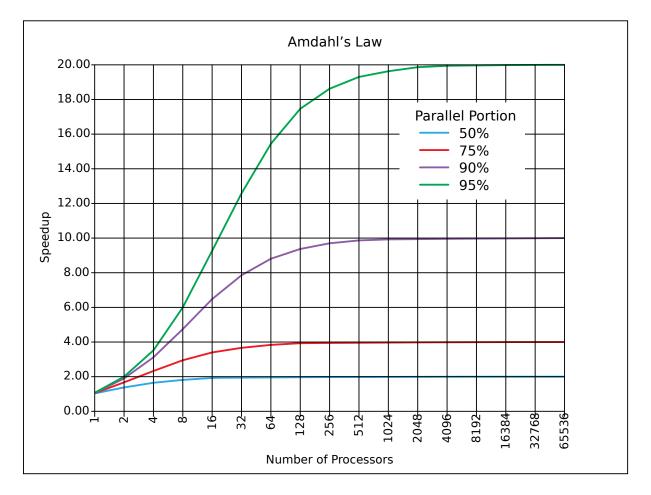

cess of parallelizing an application, there is a limit to the performance gains a parallelized version of an application can achieve. These limitations are defined by Amdahl's Law, which states that a program cannot run faster than the aggregate of its sequential parts.

Furthermore, as the main improvements in performance of general-purpose processors have derived from higher clock frequencies and deeper pipelines, without a commensurate increase in memory speed, new bottlenecks emerge. Increasing the number of cores per socket results in augmented pressure on communication bandwidth, particularly with regard to memory access. In the last couple of decades, memory latency has increased by the several hundredfolds relative to clock speed, causing application performance in many cases to be dictated by latency, rather than in peak compute capability or peak bandwidth. This has motivated manufacturers to make radical design changes to the traditional architectures, introducing new, more specialized, heterogeneous designs.

Heterogeneity is not a new concept, as specialized co-processors have been used to supplement the functions of the main CPU since the early mainframe computers. The floating-point unit (FPU) became common as a co-processor already in the 1980s, to help speed up floating-point arithmetic, which at that point was done in software. Other applications of co-processors include network processors in Network Interface Cards (NICs), used to offload parts of the TCP/IP stack, dedicated Graphics Processing Units (GPUs) for image rendering, and Digital Signal Processors (DSPs) in sound cards. However, the availability of such components for general-purpose programming have until recent years been scarce, due to hardware having limited functionality, and restricted programming APIs. Today, heterogeneous architectures are widespread, designed with general-purpose computation in mind, combining processing elements with different characteristics for great amounts of processing power.

The Cell Broadband Engine [12] is a heterogeneous multi-core architecture, developed as a joint effort by Sony Computer Entertainment, Toshiba, and IBM in 2005. Although the architecture was initially intended for application in game consoles and mediarich consumer-electronics devices, the architecture has been designed to overcome the diminishing returns available from a frequency-oriented design point. A key optimization of the Cell Broadband Engine, is to provide the best combination of parallelism on all levels: The architecture features data level parallelism with both scalar, and single-instruction, multiple-data (SIMD) support. To exploit available memory bandwidth more efficiently, compute-transfer parallelism is provided by using programmable data transfer engines. Thread-level parallelism is supported with a hardware multithreaded PowerPC Processor Element (PPE), and multiple Synergistic Processor Elements (SPEs) on a single chip. In this effort, the Cell Broadband Engine bridges the gap between conventional multi-core architectures, and more specialized, high performance processors.

The rapid improvements in the availability of commodity high-performance components has resulted in a proliferation of networked devices, making scalable computing clusters the standard platform for many high-performance and large-scale applications. The main attractiveness of such systems is that they are built using affordable, low-cost, commodity hardware, fast local area networks (LANs), and standard software components such as Linux/UNIX, consequently leading to low-cost commodity super-computing. Where the demands of computationally bound problems exceed the computing resources available from a single machine, clustered environments allows for these problems to be solved in a timely and reasonable manner, by distributing the problem set amongst several nodes. However, writing code for non-trivial algorithms that dynamically scale to an arbitrary number of nodes is a challenging task, with regard to parallelizing the computation, explicitly handling concurrency and data locality, and non-deterministic behaviour.

To simplify the process of distributed computing, both industrial actors and opensource communities have contributed a significant body of research towards frameworks and programming models. Examples of these include Google's MapReduce [13], Microsoft's Dryad [14] and Azure [15], Yahoo's Pig Latin programming language [16], the Condor [17] system, and environments like PVM [18] and MPI [19]. However, most of these frameworks and models are targeted towards off-line batch processing of large quantities of data, and do not provide a lightweight interface for task offloading. There are also systems that adapt the MapReduce programming model, but target specific architectures only, like multi-core machines [20], GPUs [21], and the Cell Broadband Engine [22]. Moreover, MapReduce, Dryad and Pig Latin share a common drawback in their inability to model branching and iterative algorithms. While the Nornir [23] runtime system solves this latter problem by expressing algorithms in the Kahn process network (KPN) [24] model, it is targeted for shared-memory multi-core machines, and not distributed environments.

### 1.2 Problem Statement

Due to the complexity of parallel processing, with regard to managing concurrency, data locality, and non-deterministic behaviour, frameworks and programming models have emerged from industrial actors and open-source communities, to help simplify the process of parallelization on both standalone machines and in distributed environments. However, most of the frameworks targeted for distributed computing are designed for off-line batch processing and analysis of vast amounts of data, and do not provide a simple interface for offloading compute intensive tasks. We want to investigate how to make an efficient runtime system that allows for a simple offload-model, exploiting the properties of a heterogeneous distributed environment. Among the issues we investigate in this thesis, are the design challenges posed by such a framework, the work distribution strategies required by applications for the integration and adaption to an offload-model, and the potential scalability it may provide.

### 1.3 Main Contributions

In this thesis, we have presented a design and a prototype framework that can be used to accelerate applications, by offloading compute intensive parts of a program to a heterogeneous distributed environment. While we intend for this framework to support a broad range of platforms, we have due to time constraints limited the scope of this thesis to a prototype implementation for the Cell Broadband Engine, and leave the extensions to additional architectures as further work.

With the increasing number of cores in newer processor architectures, and with the proliferation of networked commodity components, application writers should be able to reap the benefits in accordance to Moore's Law, without the need to re-write or re-think the whole application. Therefore, we investigate work distribution strategies for various applications, and evaluate their potential scalability with added hardware. To achieve this, we implement a Motion JPEG video encoder using our framework, then adapt an existing implementation of the Advanced Encryption Standard (AES). These implementations have very different characteristics, which will reflect in both scalability and throughput.

For the Cell Broadband Engine, we have proposed a prototype of a workload scheduler, to be used in conjunction with a runtime library. We evaluate the performance of the servers with regard to workload processing, and propose programming models for the Cell Broadband Engine architecture.

## 1.4 Outline

The rest of this thesis is organized as follows; In chapter 2, we look at the technical details of multi-core architectures, in particular the Cell Broadband Engine, and cover parallelization techniques and parallel programming models. In chapter 3, we discuss the design challenges of such a framework, and propose a prototype design for the Cell Broadband Engine. The design proposed in chapter 3 is then realized in chapter 4, which covers the implementation details. In chapter 5 we evaluate the framework with video encoding, and in chapter 6, we use our framework to implement block cipher encryption. We then discuss the results and lessons learned in chapter 7, and summarize and conclude our thesis, as well as propose further work, in chapter 8.

## Chapter 2

## Background

In this chapter, we introduce the technical aspects of multi-core architectures, in particular the Cell Broadband Engine. Further, we go into the details and challenges of parallel programming, and introduce parallel programming models. We also give insight to current frameworks for distributed computing, and frameworks targeted for heterogeneous architectures.

### 2.1 Introduction

While we are still witnessing Moore's Law by the production of higher density processors, we have reached a plateau on single core performance. As the processor density increases, we get more processing power, along with higher power consumption and heat generation. In traditional architectures, heat generated by each new generation of processors have increased at a greater rate than clock speed. These posing power and thermal constraints have lead to the design of multi-core architectures, integrating two or more processor cores into a single processor socket. Thus, we get increased potential computational performance, but with less power consumption and heat generation. Though, the shift towards multi-core architectures poses several new challenges for both computer architects and programmers.

Providing an increase in computational performance that scales with the number of processor cores, is a challenge both when it comes to the design of the architecture, and its programmability. As processors increase in speed, a key challenge is reducing

memory latency, as well as scaling up memory bandwidth in proportion with the increase in computational performance. Parallelizing and optimizing code for multi-core systems, synchronizing tasks, and the resource management that comes with it, may often be a complex and tedious task. Thus, having reliant tools and frameworks to reduce the programming effort is necessary.

### 2.2 Multi-core architectures

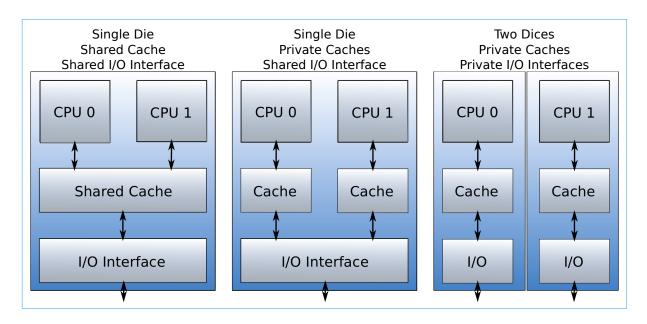

Multi-core architectures places two or more independent processing units (cores) on a single integrated circuit die, or onto multiple dies in a single chip package. Todays multi-core architectures are in many ways much like the older shared memory systems, as they merely migrate the shared memory system onto a single chip. There are several design approaches to these architectures, each with their own trade-offs and benefits, which is discussed later. By changing the level of integration and how resources are shared or partitioned, each design presents a different set of pros and cons. Figure 2.1 shows three different ways of implementing multi-core architectures; Shared cache and I/O interface, private cache with shared I/O interface, and private caches and private I/O interfaces on two dices. Note that cache in these designs represents higher levels of cache (L2 or L3), as L1 cache is too tightly integrated and is considered part of the core. Although there are many ways of implementing multi-core designs, there are two main categories — homogeneous and heterogeneous. These are covered in detail in section 2.2.2.

#### 2.2.1 Multi-core design approaches

The shared cache approach has the advantage of having the lowest communication latency between cores. Data traffic between the cores does not have to go via the I/O interface, thus maximizing bandwidth to other devices, and letting the I/O interface focus on off-chip communication. Further, a shared cache approach lets the cache be dynamically shared between the cores. It only requires a single bus or network drop, making the interconnect network between the sockets simpler. However, while having high performance, it is one of the more complex designs. The cache controller needs to manage sharing policy and dynamic allocation between the cores, which might lead to performance issues if one of the cores is occupying all resources. Also, the cache needs higher bandwidth, as it serves two cores. The Intel Core Duo is an example of a

Figure 2.1: Three different multi-core designs [1].

processor that implements the shared cache design.

The shared I/O interface architecture has the advantage of having a simpler design, but lacks some of the flexibility and performance of a shared cache architecture. Like having a shared cache, communication between the cores does not have to go outside the chip, and the bus controller should be able to handle off- and intra-chip traffic simultaneously. Since the caches are separate, the cache controller may be identical to single core microprocessor units (MPUs), and relatively few modifications are needed to produce shared interface chips. However, since the caches are not shared, there can be no dynamic cache allocation between the cores, which may lead to wasted resources. Montecito is the code-name of a release of Intel's Itanium 2 processor family, which implements the shared interface design.

The shared package approach, often called Dual Chip Module (DCM) or Multi Chip Module (MCM), has the advantage of being less complex, as it does not require modifications to the CPU logic. Each die may also be tested and verified before packaging, granting yields close to that of a single core. The greatest disadvantage with this design, is the communication between the cores, being just as slow as communication between two sockets in a Symmetric Multi-Processor (SMP) approach. The lack of integration greatly increases data traffic across the external interface, and puts a higher load on the bus or interconnect network. Intel's Pentium D, code-named Presler, is an architecture that implements the shared package design [1].

#### 2.2.2 Homogeneous and Heterogeneous Multi-Core Architectures

Homogeneous multi-core architectures are the more common architectures in today's workstation and desktop computers, consisting of one core design repeated consistently; All cores have the same frequency, cache size, functions, memory model, and so on, which makes it easier to produce. Also, since the cores are identical, it allows for a simpler programming model. However, with heterogeneous architectures, each core could have a specialized function. Heterogeneous architectures usually consists of a general purpose processor (GPP), and one or more specialized cores, often with a reduced instruction set, to improve performance on certain tasks or functions. There is an apparent trade-off between the architectures in terms of complexity and customization; Heterogeneous systems could have a centralized core for generic processing and running an operating system, a core for graphics, a core for audio, a heavily mathoriented core, and a core for communication based tasks. Though this is a more complex system, it may have efficiency, power, and thermal benefits that outweighs the complexity. The Cell Broadband Engine is an example of a heterogeneous architecture, and is introduced in detail in section 2.3.

Although the average x86 architecture is not considered as heterogeneous, it does in fact provide heterogeneity on several levels; With NVIDIA's parallel computing architecture CUDA [25], GPUs are becoming increasingly more available to general purpose programming, making virtually all desktop computers heterogeneous systems. In addition to the FPU, Intel has later added extensions to their instruction set architecture, to include technologies like Streaming SIMD Extensions (SSE) [26], and AES New Instructions (AES-NI) [27]. However, without compilers and runtimes to support these technologies, it is still up to the application writers to exploit the potential processing power the system offer.

#### 2.2.3 Multi-core challenges

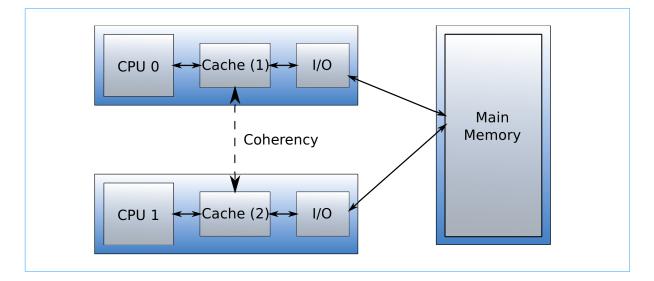

There are several challenges that needs to be considered with a multi-core architecture. Adding an additional core to the architecture does not necessarily mean a hundred procent performance increase. One also needs to consider the overhead associated with interprocessor communication, shared resources and diminishing returns. Distributed caches raises the challenge of cache coherence, and additional cores may also rise problems with power and thermal management.

#### **Cache coherence**

Cache coherence is a challenge with multi-core architectures when having distributed L1 and L2 caches. Since each core has its own set of caches, the current version of data may not always be the one most up-to-date.

Figure 2.2: Distributed caches and cache coherence.

Consider the scenario in figure 2.2, where both processors read a block of memory into its private cache. CPU 0 then writes a specific value to that memory location, making the data in cache one and two inconsistent. When CPU 1 attempts to read the value from its cache it does not have the updated value, unless the cache entry is invalidated and a cache miss occurs. The cache miss then forces the entry in cache two to update. If certain mechanisms like this is not enforced, it results in incorrect data and possibly program crashes.

There are several mechanisms to obtain coherency between caches, each having their benefits and drawbacks. The two most common techniques are directory-based coherence, and snooping. Directory-based coherence places the shared data in a common directory, that maintains the coherence between caches. This directory acts as a filter, as the processor needs to ask for permission to load an entry from primary memory to its cache. When an entry changes, the directory either updates or invalidates the other caches with that entry.

The snooping protocol only works on bus-based systems, as each cache uses the bus to monitor memory access to locations they have cached. When a write operation is observed to a location currently cached, the cache controller invalidates its own copy of the snooped memory location. Although snooping uses more bandwidth, since all cores needs to monitor all requests and responses, it tends to be faster than directories. However, snooping does not scale well, as each added core requires more bandwidth and a larger bus. Directory messages are point to point, uses less bandwidth than snooping, and may therefore be more suitable for systems with a large number of cores.

#### Power and thermal management

Adding an additional core to the chip, in theory, would make the chip consume twice the amount of power, and generate an additional large amount of heat. As mention earlier, the clock frequency of each core is therefore lowered to compensate for the heat generation and power consumption. Many designs also incorporate a power control unit, which is able to shut down unused cores. By powering off cores and using clock gating, which disables portions of a circuit so that its flip-flops do not change state, one is able to reduce the amount of leakage in the chip.

Further, another common power management technique is dynamic voltage scaling, where the voltage to the chip is either increased or decreased, depending on the circumstances. Increasing the voltage is known as overvolting, contrary to undervolting, where voltage is decreased. Undervolting is done when the temperature of the core needs to be reduced, and when conserving power consumption, which is particularly important for laptops and mobile devices. When a performance increase is needed, overvolting is done to apply a higher voltage to the circuit, allowing capacitances to charge and discharge faster. This results in faster operation of the circuit, allowing a higher frequency of operations. Dynamic voltage scaling is in most cases accessible through the BIOS. However, when not accessible through software, hardware modifications are needed.

Dynamic frequency scaling is a technique which is closely related to dynamic voltage

scaling. This power management technique is often used in conjunction with dynamic voltage scaling, since the maximum frequency a chip may run at is related to the operating voltage of the chip. Most modern processors are strongly optimized for low power idle states, making the conjunction a necessity to optimize power and thermal management. Implementations of dynamic frequency and voltage scaling includes Intel's *SpeedStep* [28] series for the mobile processor line, and AMD's *Cool'n'Quiet* [29] and *PowerNow!* [30] processor throttling technology.

Reducing the clock speed and voltage of the processor does indeed reduce heat generation. However, it should be noted that doing this may not reduce power consumption. As the technologies mentioned above can reduce power consumption when the processor is in an idle state, we obviously want the processor to stay idle for as long as possible. This means executing the required tasks as quickly as possible, so the processor can return to idle state faster. Switching to the highest voltage and clock speed, executing the code, then dropping back to idle state, may actually save power consumption.

### 2.3 The Cell Broadband Engine

The Cell Broadband Engine, commonly abbreviated Cell, Cell BE, or CBEA, is a heterogeneous multi-core processor developed by "STI", a joint effort by Sony Computer Entertainment, Toshiba, and IBM, which formed in mid-2000. STI's objective was to develop a processor able to achieve 100 times the processing power of the PlayStation 2 [31]. The STI design center opened in 2001, and the Cell BE was developed over a period of four years. On the 17th of May, Sony Computer Entertainment confirmed that the PlayStation 3 (PS3) would be shipped with the Cell BE, with the possibility of installing third party software [32]. In August 2009, it was announced that the Cell processor in the newer PS3 Slim had moved from 65nm to the 45nm version. However, the Slim-version would unfortunately not have the possibility to install a third party operating system [33]. On April 1, 2010, Sony released firmware update v3.21, rendering all PS3s unable to install other operating systems [34]. Although the upgrade is optional, choosing not to install it disables features like playback of copyright-protected videos over DTCP-IP, and access to the PlayStation Network.

In 2008, IBM announced the release of a revised version of the Cell BE; the PowerXCell 8i. This newer version had improved double-precision floating-point performance on

the SPEs, in addition allowing up to 32GB of slotted DDR2 memory. The PowerXCell 8i is available in IBMs QS22 Blade Servers, and is also used in IBMs Roadrunner supercomputer, which is the first supercomputer able to achieve the high-performance computing goal of one petaflop [35].

#### 2.3.1 Hardware overview

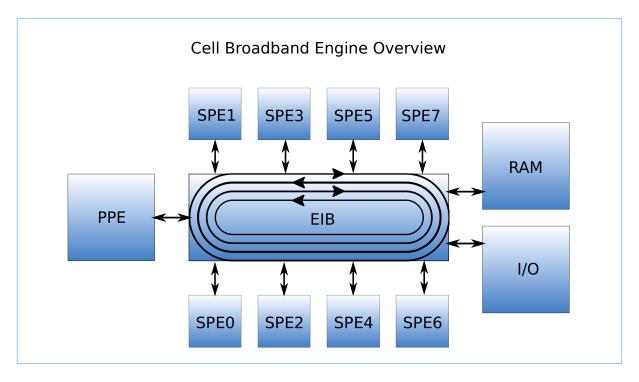

The Cell BE architecture extends the 64-bit PowerPC architecture host processor (PPE) with cooperative synergistic offload processors (SPEs), supporting SIMD-operations for single and double point precision instructions. Connecting the PPE with the SPEs and I/O-elements, there is a specialized high-bandwidth circular data bus called the Element Interconnect Bus (EIB). The PPE and SPEs use fully cache coherent direct memory access (DMA) over the EIB to transfer data between main memory, local store (LS) and other external storage devices. Each of the SPEs have their own DMA engine to fully utilize the potential asynchronous and concurrent processing [31].

Figure 2.3: Cell Broadband Engine Architecture Overview.

The function of the processor elements is specialized into two types; The PPE is optimized for control tasks, and the eight SPEs provide an execution environment optimized for data processing [36]. With a clock speed of 3.2 GHz, the Cell BE has a theoretical peak computational performance of 230.4 GFlops per second (single-precision floating point) [12].

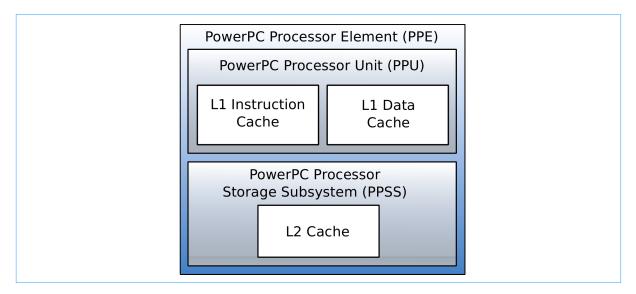

#### **Power Processor Element (PPE)**

The PPE is a dual-issue, dual-threaded, and in-order 64-bit Power-architecture connected to a 512KB L2 cache and 32KB L1 cache. The PPE is the main processor (host) of the Cell BE, and is responsible for running the operating system and control tasks [37]. The implementation of the PPE in the Cell BE includes innovations of Power such as virtualization and support for large page sizes, and provides compatibility with Power which enables the possibility to run conventional operating systems, like Linux. An overview of the PPE is shown in figure 2.4.

Figure 2.4: Cell BE PPE block diagram.

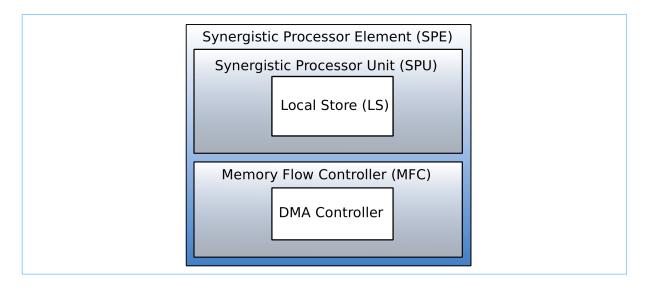

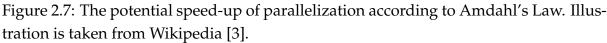

#### Synergistic Processor Element (SPE)

One of the key architectural features of the Cell BE is the SPE. The SPE is a RISC processor with 128-bit SIMD-organization for single and double precision instructions, and is optimized for computation-intensive applications. The SPE is an independent processor, able to run an independent application thread. It is composed of a Synergistic Processor Unit (SPU), with a Memory Flow Controller (MFC) which contains a DMA, MMU and bus interface, enabling it to have full access to coherent shared memory, including memory-mapped I/O-space. It also contains 256KB embedded SRAM called

Local Store (LS), which can be addressed by the PPE through software, and is used for efficient instruction and data access by the SPU. However, LS must not be mistaken for conventional cache, as it is not transparent; It requires explicit DMA transfers to load and store data. An overview of the SPE is shown in figure 2.5.

Figure 2.5: Cell SPE block diagram.

#### **Element Interconnect Bus (EIB)**

The Element Interconnect Bus enables internal communication between the PPE, SPE, main memory and external I/O. The EIB is implemented as a circular ring, comprised of four 16 byte wide unidirectional channels, which counter-rotate in pairs. At maximum concurrency, each channels allows up to three transactions. Each unit connected to the EIB has two 16 byte ports available — one for sending, and one for receiving. These can be accessed simultaneously, and sends and receives every bus cycle. The data rings are illustrated in figure 2.3.

The reason for having the rings run both ways, is to optimize the traffic patterns when units are communicating. The theoretical peak bandwidth for the EIB is 204.8GB/s at 3.2Ghz (128Bx1.6GHz). However, if all the units are trying to either send or fetch data from main memory concurrently, traffic patterns may be limited, resulting in idling on two of the paths. This is also the case for communication between the SPEs, with regard to the relative position between source and destination [38].

#### Memory Flow Controller (MFC)

The Memory Flow Controller is part of each SPE, creating an interface for the SPE to be used by main storage, processor elements, and other system devices, by means of the EIB. It provides the SPE with data transfer and synchronization capabilities, and also offers storage protection on the main-storage side of DMA transfers. Software running on the SPEs communicate with the PPE, main storage, and other SPE devices through channels. Channels are unidirectional message-passing interfaces, supporting 32-bit messages and commands. These commands may be used to initiate DMA transfers, query DMA status, perform MFC synchronization, inter-process communication via mailboxes or signal-notification, and so forth.

#### 2.3.2 Overcoming the limitations

As mentioned is section 2.2.3, multi-core architectures rise many issues and challenges that needs to be overcome for it to be efficient. By optimizing control-plane and dataplane processors individually, the Cell BE overcomes the challenges regarding power, heat and memory management, providing approximately a ten-fold the peak performance of a conventional processor on the same power budget [39].

#### **Power limitations**

To significantly increase the performance of multi-core architectures, power efficiency has to improve at about the same rate as the computational performance. One way of doing this is to differentiate processors on what kind of jobs they are optimized to do, which ensures good utilization efficiency of the available resources.

The Cell BE differentiates its processors this way, by providing a general purpose PPE to run the operating system and other control-intensive tasks, as well as eight specialized synergistic SPEs for computational-heavy applications. The SPEs have a simpler hardware implementation, and do not devote transistors to branch prediction, outof-order execution, register renaming, and extensive pipeline interlocks. Thus, more transistors are used for computation than on a conventional processor core.

#### **Memory limitations**

Processors have increased in speed faster than memory latency has improved, resulting in program performance being dictated by the activity of moving data between main memory and the processor. On symmetric multiprocessor platforms in the multigigahertz range, latency to DRAM memory is approaching 1000 cycles [40]. Hardware cache mechanisms are supposed to relieve the programmer of these tasks, but it has become increasingly more common for programmers and compilers to deal with this explicitly.

To deal with main memory latency, the Cell BE uses a three-level memory structure, with main memory and local storage, in addition to a large register file for each of the eight SPEs. The Cell BE also makes use of asynchronous DMA transfers between main memory and local storage, allowing up to 128 simultaneous data and code transfers. These features allows for the programmer to more efficiently schedule loads and transfers in a highly parallel environment.

#### **Frequency limitations**

To achieve higher operating frequencies, conventional processors require increasingly deeper instruction pipelines, to the point where it is suffering diminishing returns, and even negative returns if power is taken into account.

By specializing the PPE and the SPEs for control- and compute-intensive tasks, respectively, both the PPE and SPEs can be designed for high frequency without excessive overhead. The PPE achieves efficiency by having hardware multi-threading, rather than optimizing for single-thread performance. The SPEs achieve efficiency by having a large register file, and access to DMA transfers, supporting many concurrent memory operations.

#### 2.3.3 Inter-process communication

Since the Cell BE is not a traditional shared-memory multiprocessor, other means are necessary to provide inter-process communication (IPC). The SPEs can execute programs, and directly load and store data from its local store. The system is therefore

provided with three primary communication mechanisms: DMA transfers, mailbox messaging and signal-notification messaging. All three mechanisms are controlled by the SPEs memory flow controller (MFC).

#### **DMA transfers**

The Cell BE's DMA engine is part of the MFC unit, and is responsible for moving data within the Cell BE and external I/O devices. Each SPE has one dedicated DMA engine, with a corresponding control- and memory management unit (MMU) in the MFC. The MMU allows for moving streaming data in and out of LS in parallel with code execution on the SPE, which in turn allows for higher throughput. The DMA control unit consists of two queues - one for PPE-initialized requests, and one for SPE-initialized requests. The SPE uses DMA channels to initiate the DMA transactions, where each individual channel maps to a DMA parameter. These parameters include Local Store Address (LSA) and Effective Address (EA) to initiate transfers between the two storage domains, the size of the data to be transferred, a tag to identify the DMA or group of DMAs, and the MFC DMA command. Regarding alignment, DMA transfers must be 1, 2, 4, 8, or a multiple of 16 bytes, up to a maximum of 16kb, and aligned on a 16 byte boundary.

Most MFC commands have names that imply the direction of the transfer, and is always referenced from the perspective of the SPU that is associated with the MFC command. Thus, *GET* moves data from main memory to LS, and *PUT* moves data from LS to main memory. The other group of MFC commands are synchronization commands, used to control the order in which storage access is performed. The tag associated with the MFC command is a 5-bit tag group ID. SPE programs can use this tag ID to check on the status of a tag group, enable an interrupt when one or more tag groups are complete, or to enforce an execution order of commands within a tag group.

#### Mailbox messaging

Mailboxes on the Cell BE are special purpose registers in the SPEs and PPE, supporting sending and receiving of 32-bit messages. Each SPE has access to three mailbox channels, each of which are connected to the SPU's MFC. Two of the mailboxes are outbound, where one can send interrupts, and are used for sending messages from the SPE to the PPE. These mailboxes are limited to one entry each. The third mailbox is inbound, and can hold up to four entries. The inbound mailbox acts as a FIFO queue, where the oldest message is read first. If a program on the PPE would try to write more than four messages to the queue before the SPE program reads the data, the last message in the queue is always replaced, and the previous message is lost.

It should be noted that mailbox operations from the SPE are blocking operations. An attempt to write to a full outbound mailbox channel stalls the SPE program until the mailbox is read by the PPE. Similarly, a read from an empty inbound mailbox also stalls the SPE. However, this can be avoided using a read-channel-count instruction, checking the message count on the corresponding mailbox before deciding to do a read or write. Stalling does not occur on the PPE. Although mailboxes are intended to communicate messages such as program status and completion flags, they may however also be used for sending other short data, like storage addresses, function parameters or command parameters.

#### Signal-notification messaging

SPE signal-notification channels are connected to the SPEs inbound registers, and may be used to send information such as completion flags or program status from the PPE or other SPEs. Each SPE has two 32-bit signal-notification registers, each of which has a corresponding memory-mapped I/O (MMIO) register that can be written with signalnotification data. The MMIO registers are contained in the SPE's MFC.

Upon reading a signal-notification channel from the SPE, hardware clears the channel atomically. SPE software can use polling or blocking when waiting for a signal, or set up interrupt routines to catch the signals as they appear asynchronously. However, reading from the main-storage's MMIO does not clear its signal-notification register. Each SPU has two signal-notification channels, one to read each of the MMIO registers, where each channel is 32 bits long.

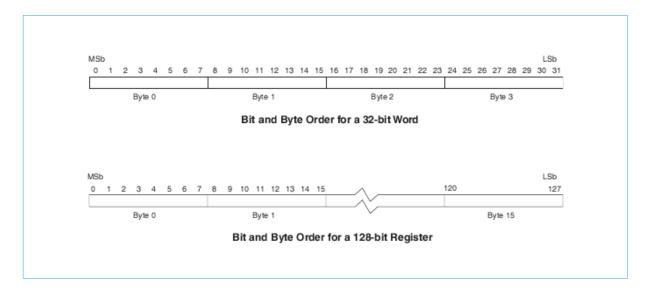

#### 2.3.4 Bit ordering and bit numbering

Storage of data and instructions in the Cell BE uses big-endian ordering, which has the characteristics of storing the most-significant byte at the lowest address, and the least-significant byte stored at the highest address. Bit numbering within a byte goes from the most-significant bit (bit zero) to the least-significant bit (bit n). A summary of the byte-ordering and bit-ordering in memory and the bit-numbering conventions is shown in figure 2.6.

Figure 2.6: Big-Endian byte and bit ordering. Figure taken from the Cell Broadband Engine Programming Handbook [2].

Both the PPE and SPEs, including the MFCs, use big-endian byte-ordering. However, as DMA transfers are simple byte moves without regard to the numeric significance of the byte, byte-ordering becomes irrelevant to the actual movement of a data block. Byte-ordering only becomes relevant when data is loaded and interpreted by a processor element or the MFCs.

## 2.3.5 PlayStation 3 and Linux

The PS3 contains the first commercial application of the Cell BE. The processor is clocked to 3.2GHz with a 512KB L2 cache, and has six accessible SPEs. This is due to the seventh being dedicated to the OS for security aspects, and the eight due to production yields. Access to the RSX GPU is also restricted by a hypervisor implemented by Sony. Since the launch of the PS3, the Cell has had its process reduced from 90nm to 45nm. The latter is shipped with the PS3 Slim edition, which does not support the installation of a third-party operating system.

Even though Linux is not pre-installed on the PS3, Sony has promoted Linux on the

PlayStation since the release of *PS2 Linux* [41]. Linux has been supporting PS3 since kernel 2.6.21, and Sony even worked in cooperation with Terra Soft developing Yellow Dog Linux 5 for the PS3. However, due to the restrictions of access to the RSX GPU by the hypervisor, accelerated graphics is not possible.

IBM has developed a software development kit for Linux, which provides the libraries, tools and resources needed to develop applications on the Cell BE under Linux<sup>1</sup>. The most basic tools in this SDK are *gcc*, *spu-gcc* and *embedspu*. *gcc* is used for building binaries for the PPE, while *spu-gcc* builds binaries for the SPEs. *ppu-embedspu* converts SPE programs into object files that can be linked into a PPE executable. The Cell BE is also supported by the IBM XL C/C++ compiler [42], which is a cross-compiler for x86 platforms only.

# 2.4 Parallel programming and programming models

Traditionally, programs have been written with a single thread of control in mind, as most systems have been limited by a single core. Today, multi-core architectures are becoming increasingly more common, which also increases the demand for understanding parallel programming. This style of programming uses multiple processing elements to simultaneously solve a problem, by breaking the problem up in independent parts and processing them separately. Parallel programming introduces many new challenges, as well as strategies and programming models for solving a given problem.

## 2.4.1 Terminology

**Asynchronous:** In an asynchronous programming model, different processor elements execute different tasks without needing to synchronize with other processor elements or tasks.

**Synchronous:** Coordinated in time among tasks, such as when one task notifies a second task about some state change, which the second task receives when it is polling for such notification.

<sup>&</sup>lt;sup>1</sup>Now part of the non-free IBM SDK for Multicore Acceleration

**Synchronization:** Synchronization enforces constraints on the ordering of events occurring in different processor elements.

**Task:** A unit of execution.

**Thread:** A fundamental unit of execution in many parallel programming systems. One process can contain an arbitrary number of threads, limited by the library used.

**Atomic:** An atomic operation is uninterruptible. In parallel programming, this can mean an operation (or set of instructions) that has been protected by synchronization methods.

**Bandwidth:** The number of bytes per second that can be moved across a network. A program is bandwidth-limited when it generates more data-transfer requests than can be accommodated by the network.

**Busy wait:** Using a timed loop to create a delay. This is often used to wait until some condition is satisfied. Because the device is executing instructions in the loop, no other work can be done until the loop ends.

**Critical section:** A critical section is a piece of code that can only be executed by one task at a time. It typically eliminates in fixed time, and another task only has to wait a fixed time to enter it. Some synchronization mechanism is required at the entry and exit of the critical section to ensure exclusive use. A semaphore is often used for this.

**Deadlock:** A deadlock occurs when two or more tasks or processor elements are stalled, waiting for each other to perform some action such as release a shared resource.

**Latency:** Latency is a time delay between the moment something is initiated, and the moment one of its effects begin. In parallel programming, this often refers to the time between the moment a message is sent and the moment it is received. Programs that generate large numbers of small messages are latency-bound.

**Load balance:** Distributing work among processor elements so that each processor element has roughly the same amount of work.

**Monitor:** A software monitor consists of a set of procedures that allow interaction with a shared resource, a mutual-exclusion lock, the variables associated with the shared resource, and a monitor invariant that defines the conditions needed to avoid race conditions. A monitor procedure takes the lock before doing anything else, and holds it until it either finishes or waits for a condition. If every procedure guarantees that the invariant is true before it releases the lock, then no task can ever find the resource in a state that might lead to a race condition.

**Mutual exclusion:** Mutual exclusion (often abbreviated to *mutex*) algorithms are used in parallel programming to avoid the concurrent use of non-sharable resources by pieces of code called critical sections. When several processor elements share memory, an indivisible test-and-set of a flag is used in a tight loop to wait until the other processor elements clears the flag. This test-and-set ensures that when the code enters the critical region, the flag is set. When the code leaves the critical region, it clears the flag. In a spin lock or busy wait mutex, the wait loop terminates when the test finds that the flag is not set, and the wait continues if the flag is set.

**Race condition:** A race condition occurs when the output exhibits a dependence (typically unexpected) on the relative timing of events. The term originates with the idea of two signals racing each other to influence the output first. The term race condition also refers to an error condition where the output of a program changes as the scheduling of (multiple) processor elements varies.

**Semaphore:** A semaphore is a protected variable (or abstract data type) and constitutes the classic method for restricting access to shared resources (for example shared memory), in a parallel programming environment. There are two operations on a semaphore; V, often called *up*, and P, often called *down*. The V operation increases the value of the semaphore by one, while the P operations decreases the value of the semaphore by one. The V and P operations must be atomic operations.

**Starvation:** Starvation occurs when a task tries to access some resource but is never granted access to that resource.

## 2.4.2 Amdahl's Law and Gustafson's Law

Optimally, one would want the speedup from parallelization to be linear — doubling the number of processing elements should cut the runtime in half. However, achieving this optimal speed-up with a parallel algorithm is very hard to do, and is only plausible when the number of processing elements is low, and most of the program is parallelizable. Speed-up may be near-linear for a small number of processors, until the number of processing elements increases and the speed-up stagnates. This trend is illustrated in figure 2.7.

Amdahl's law [3] is a model for the relationship between the expected speed-up of a parallelized algorithm relative to the serial algorithm, given that the problem size remains the same after parallelization. Any mathematical or engineering problem consists of several parallelizable parts, but also several sequential parts, thus making the potential speed-up limited to the parts parallelizable. This relationship is given by the equation

$$S = \frac{1}{1 - P}$$

where S is the speed-up of the program as a factor of its original sequential runtime, and P is the fraction of the program that is parallelizable. Given that only half of the program's runtime is parallelizable, the maximum achievable speed-up is 2, regardless of the number of processing elements.

Closely related to Amdahl's law is Gustafson's law [43], which addresses the shortcomings of Amdahl's law, primarily that Amdahl did not take into account the availability of computing power as the number of machines increases. Amdahl's law assumes a fixed problem size and that the size of the sequential section is independent of the number of processors, whereas Gustafson's law does not make these assumptions. Gustafson's law can be formulated as

$$S(P) = P - \alpha(P - 1)$$

where P is the number of processors, S is the speed-up, and  $\alpha$  the non-parallelizable part of the program. Gustafson's law implies that, if more processing elements are available, larger problem sizes can be solved in the same time.

#### 2.4.3 Parallelism Challenges

One of the most vital steps to consider when parallelizing a program, is locating and exploiting concurrency. One needs to understand the data flow, data dependencies and functional dependencies of the program to make an efficient parallel implementation, which does not succumb to overhead from data dependencies, synchronization or data-sharing. When looking for concurrency, key elements to examine are function calls, loops and large data structures operated on in chunks. It might be worthwhile to do an analysis of the program, and finding out which parts are the most computation-ally intensive, using profiling tools like Cachegrind, Callgrind and KCachegrind <sup>2</sup>.

Parallelizing a program may lead to a lot of potential overhead, and it is up to the

<sup>&</sup>lt;sup>2</sup>Cachegrind and Callgrind are part of the Valgrind Tool Suite, and may be found at *http://valgrind.org/info/tools.html*. KCachegrind is a graphical profile visualization tool, and may be found at *http://kcachegrind.sourceforge.net*

programmer to make sure the overhead justifies the improvement in performance. After breaking down the program into tasks that can execute in parallel, one needs to consider data dependencies, task size and grouping, overhead from data transfers in terms of latency, bandwidth and amount of data, and synchronization overhead. In situations where a single task may be too small to justify assigning it to a single processing element, it might be beneficial to group tasks, thus performing several sets of operations on data. This approach reduces the amount of synchronization needed between groups, and may also be worthwhile when tasks share data dependencies.

After choosing a parallelization strategy that suits the program, performing profiling and doing hot-spot analysis may give the programmer insight to critical code sections that might be worthwhile to additionally fine-tune. Fine-tuning is often heavily influenced by the architecture the program is targeted for, as different architectures may handle certain operations, branching and memory access differently. Following are some considerations to include when fine-tuning a program for the Cell BE:

**Branching:** The SPU in the Cell BE assumes sequential instruction flow, and a branch instruction has the potential of breaking this assumed flow. Branches predicted correctly executes in one cycle, while mispredicted branches (conditional or unconditional) causes a penalty of 18 to 19 cycles, depending on the address of the branch target [44]. Branch instructions also reduce the compilers ability to schedule instructions, by creating a barrier on instruction reordering. As the SPU has a typical instruction latency of two to seven cycles, mispredicted branches may seriously degrade the program performance. The three most efficient methods of eliminating branch prediction are function inlining, loop unrolling, and branch predication.

**Function inlining and loop unrolling:** Function inlining eliminates the two branches associated with function-call linkage — *branch and set link* (brasl) and *branch indirect* (bi) — for function-call entry and function-call return, respectively. Loop unrolling eliminates branches by reducing the number of iterations, and may be either manually unrolled or automated by the compiler. However, due to the limited space of the SPE's LS, one should be careful with over-excessive use of the latter technique, as it may greatly increase program size.

**Predication:** It is also possible to eliminate branches for control-flow statements, for example *if* and *if-then-else* constructs. By computing the results of both the *then* and *else* clauses, then using *select bits* (selb) to choose the result as a function of the con-

ditional, the *if-then-else* statement can be made branchless. Additional cycles can be saved if the computation of both results is less than a mispredicted branch [44].

# 2.4.4 Parallel programming models and strategies

Parallel programming models exist as an abstraction above hardware and memory architectures, as an idealized view onto which applications can be mapped to express concurrency. As examples, parallel programming models may include shared memory, message passing, threads, data-parallelism, and hybrids of these. Although each programming model is not architecture-specific, certain models may be more suitable for a given architecture due to hardware characteristics.

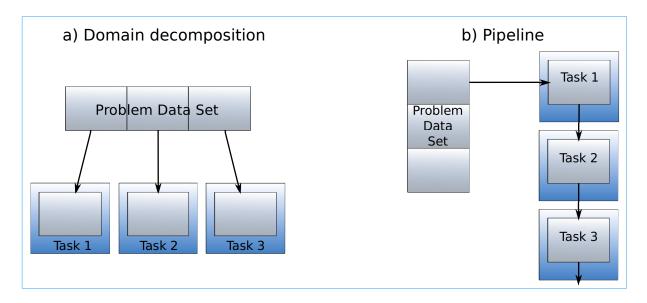

Figure 2.8: Work distribution models.

Work distribution strategies define how concurrency is exploited in an application, and how the program is partioned into independent tasks or grouped into execution threads. Some work distribution models include shared memory, domain decomposition, and pipelining. A shared memory model on the Cell BE usually involves having larger standalone SPE programs, accessing shared memory objects in effective-address space through a locking mechanism. This can be done through an object format called CBE Embedded SPE Object Format (CESOF) [45].

More common is a domain decomposition model, where data is decomposed into sub domains and assigned to a single task, as illustrated in figure 2.8a. This model often

utilizes a shared job queue, where each processor elements must acquire a lock to fetch the next job. For uneven jobs, this model has the advantage of self-balancing the load between the processing elements. Where data needs to undergo several stages of computation, e.g. in video coding, a pipeline model may be more applicable. In this model, each stage is represented as a separate task, and data is transferred between them as stages complete, as illustrated in figure 2.8b. Pipeline models have the advantage of utilizing LS to LS DMA bandwidth; However, it is harder to load-balance.

On the Cell BE, work distribution models are often considered either *PPE-centric* or *SPE-centric*. In PPE-centric models, the PPE is responsible for distributing work amongst the SPEs, as well as the loading and switching of SPE programs. In SPE-centric models, application code is usually distributed amongst the SPEs, and the SPEs are responsible for fetching the tasks from main memory. Although a PPE-centric approach may provide finer control over the SPE programs, the PPE load may become heavily utilized by management and control operations, tying it up from processing other tasks.

# 2.5 Related Work

# 2.5.1 The MARS framework

The Multicore Application Runtime System (MARS) [4] is a framework for the Cell BE that tries to address the performance overhead of cooperative multitasking on the Cell BE's many SPEs. MARS provides an efficient runtime environment for SPE centric application programs, and a set of libraries that provide an API to manage and create programs. MARS takes advantage of a more lightweight context switch, by letting a microkernel run on each of the available SPEs and take part of the scheduling. This also minimizes the runtime load of the host processor (PPE). MARS is developed by Sony, and released under the MIT license.

When programming on a multi-core architecture such as the Cell BE, there are several caveats one should be aware of. First of all, the local store of the SPE is limited (256KB on the PS3). As the application grows more complex, it is also important for the user to make sure the partioned segments of code do not exceed the physical limits of the local store. Second, the number of physical SPEs is limited (6 on the PS3). As the number of workloads grow, and exceeds the number of physical SPEs, the workloads need to be scheduled. The scheduler also needs to take into account the execution order of the programs, since the programs may interact with each other.

In the rest of this section, we use MARS terminology as in the MARS documentation, where *host* is the host processor (PPE), *MPU* for micro-processing unit (SPE), *host storage* for shared memory space (main memory), *MPU storage* for local memory space (local store), *MPU program* for SPE program, and *workload* as a generic unit of work scheduled for execution on the MPU (SPE context).

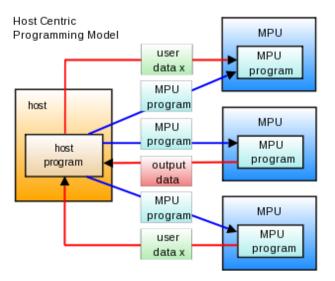

#### The Host- and MPU centric programming model

When using a host centric programming model, the host processor is responsible for organizing and supervising the programs to be run on the MPU. This includes loading and switching programs, as well as sending and receiving necessary data (see figure 2.9). This substantially increases the load on the host processor, and also results in decreased performance of the MPUs, as they often have to wait for instructions and data from the host which causes idle time. There are of course several strategies for optimizing this, however, if the MPUs can directly send and receive data, and load and switch programs, the MPUs might be able to decrease idle time and be used more efficiently.

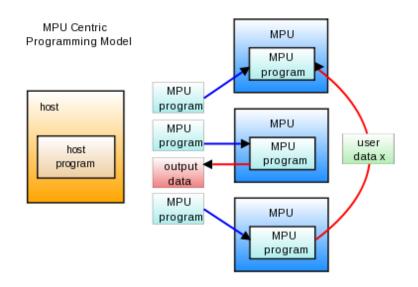

In the MPU centric programming model, the individual MPUs are responsible for loading, executing, and switching MPU programs. They are also responsible for sending and receiving the data between MPUs (see figure 2.10). These operations are done independently of the host program, making the MPUs self managing. The host is however still responsible for some of the setup management necessary to execute the MPU programs. The MARS framework provides the MPU centric model.

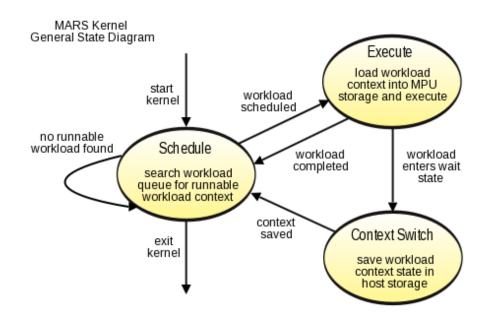

#### The MARS kernel and workloads

The MARS kernel is a small piece of code that gets loaded in to each of the MPU's storage, and stays resident there during execution. The kernel controls program execution, and is responsible for scheduling the workloads. Based on the workload, the kernel loads and executes the necessary MPU program. The scheduler is non-preemptive,

Figure 2.9: A host centric programming model. Figure is taken from the MARS documentation. [4]

Figure 2.10: An MPU centric programming model. Figure is taken from the MARS documentation. [4]

which means each workload runs until it either finishes, or enters a waiting or blocking state. When this occurs, the kernel performs the context switch.

The kernel has three basic states of operation; schedule, load/execute and save/con-

text switch. Once the kernel has been started, it searches the workload queue, located in host storage, for a ready workload. Every time a workload is created, it is put into the workload queue. Since the queue can be accessed by both the host and MPUs, it is protected by atomic operations. If the scheduler finds an available and ready workload, the workload context is loaded into MPU storage and then executed. If the workload enters a waiting/blocking state, the workload context is saved in host storage, and another workload is loaded if ready. See figure 2.11 for an illustration.

Figure 2.11: MARS kernel state diagram. Figure is taken from the MARS documentation. [4]

As mentioned, whenever a new workload is created, it is put into a workload queue. This queue is located inside a MARS context, which must be created at the start of any given program, and destroyed before exit. A MARS context also contains all necessary information and data about the instance initialized. When a context is created, it loads the MARS kernels on to the MPUs, where they reside until the context is destroyed. It is key to only have one MARS context initialized per system, to take advantage of the lightweight context switch MARS offers. More than one MARS context initialized at a time results in dramatic decrease in performance, as the whole context is switched in and out.

## 2.5.2 OpenCL

The Open Computing Language (OpenCL) [46] is a framework developed by the Khronos Group, for building parallel applications portable across multiple heterogeneous platforms, including multi-core machines, GPUs, and the Cell BE. It has a strong heritage from the CUDA [25] environment, but provides a common hardware abstraction layer across multiple architectures. OpenCL consists of a programming language, called OpenCL C, and a set of OpenCL runtime API functions. The OpenCL C language is a subset of C99, with the addition of support for vector types, images, and memory hierarchy qualifiers. While OpenCL has many publicly available implementations, including releases from Apple [47], AMD [48] and NVIDIA [49], the only implementation fully supporting the Cell BE is part of IBM's XL C/C++ compiler [42,50], which is non-free. There exists another project called OpenCL PS3 [51], which aims to make an OpenCL implementation for the PS3, but this project currently only supports a minimal subset of the specification. In this section, we briefly introduce OpenCL as specified in [46].

#### **OpenCL** platform

The OpenCL platforms consists of a host, connected to one more OpenCL devices. These devices are further divided into one or more compute unites (CUs), and a CU consists of one or more processing elements (PEs). An OpenCL application runs on the host, and submits commands to execute computations on the PEs within a OpenCL device. There are three types of commands: kernel execution, memory, and synchronization. Kernels are functions that execute on the PEs, and are further split into two categories: OpenCL kernels, which are written in the OpenCL C programming language, or native kernels, which are accessed through a host function pointer. Both types of kernels are submitted to a device's command-queue in the form of a kernel execution command, and executed on the PEs within that device. Each device may have one or more command-queues, and commands are executed either in-order, or out-of-order, depending on the queue type.

#### **Execution model**

When a kernel is submitted for execution, the host defines an index space where instances of the kernel are executed. Each kernel instance is called a work-item, and is identified by its point in the index space. Each work-item is able to query its own ID, and can perform different tasks and operate on different data, based on the its ID. Work-items are further organized in work-groups, which provide a more coarsegrained decomposition of the index space. Each work-group has a unique ID, and each work-item inside the work-group is assigned a unique local ID for that group, making it possible to identify the work-item by either its global ID, or by a combination of the work-group and local ID. Work-items in a work-group execute concurrently on the PEs of a device.

#### **Programming models**

While the driving programming model of OpenCL is data-parallel, the platform also supports task-parallel programming models, and hybrids of these. The data-parallel programming model defines computation as a sequence of data elements fed into a work-group, where the index space associated with the execution model defines how the data maps to the work-units. In a strictly data-parallel model, the data elements and work-units map with a one-to-one ratio. OpenCL implements a relaxed dataparallel model, where a one-to-one mapping is not required. Moreover, the programmer may explicitly define how work-items are divided into work-groups, or let the OpenCL implementation implicitly handle the division.