**UNIVERSITY OF OSLO Department of Informatics**

## Low Power CMOS Design

Exploring Radiation

Tolerance in a 90 nm

Low Power Commercial

Process

Master thesis

Amir Hasanbegovic

June 2, 2010

## **Abstract**

This thesis aims to examine radiation tolerance of low power digital CMOS circuits in a commercial 90 nm low power triple-well process from TSMC. By combining supply voltage scaling and Radiation-Hardened By Design (RHBD) design techniques, the goal is to achieve low supply voltage, radiation tolerant, circuit behavior.

The target circuit architecture for comparison between different radiation hardening techniques is a Successive Approximation Register (SAR) architecture comprising both combinational and sequential logic. The purpose of the SAR architecture is to emulate a larger system, since larger systems are usually composed of combinational and sequential building blocks. The method used for achieving low power operation is primarily voltage scaling, with the ultimate goal of reaching subthreshold operation, while maintaining radiation tolerant circuit behavior. Radiation hardening is performed on circuit-level by applying RHBD circuit topologies, as well as architectural-level mitigation techniques.

This thesis includes three papers within the field of robust low power CMOS design. Two of the papers cover low power level shifter designs in 90 nm and 65 nm process from ST Microelectronics. The third paper examines memory element design using minority-3 gates and inverters for robust low voltage operation.

Prototyping has been conducted on low power CMOS building blocks including level shifter and memory design, for potential use in future radiation tolerant designs. Prototyping has been conducted on two chips from two different 90 nm processes from ST Microelectronics and TSMC. A test setup for radiation induced errors has been developed. Experimental radiation tests of the SAR architectures were conducted at SAFE, revealing no radiation induced errors.

## **Preface**

This thesis is submitted as part of the degree Master of Science in Microelectronics, to the Department of Informatics, Faculty of Mathematics and Natural Sciences, University of Oslo (UiO). The project was initiated in February 2009, and concluded the following year, June 2010.

The work done throughout my thesis work has been both inspiring and challenging. Among other things, resulting in two published papers, and an invited paper to the MICPRO Elsevier journal. I have been fortunate enough to take part in design, tapeout and prototyping of two chips from two different processes (ST Microelectronics and TSMC). Moreover, working with the "Robust Ultra-Low-Power Circuits for Nano-Scale CMOS Technologies" project through the participation in the DAAD researcher exchange program between Norway and Germany (project number: 193831), has been very educational and inspiring.

I first and formost want to express my gratitude to my supervisor, Snorre Aunet, for all the valuable guidance and the inspiration he has given me throughout this thesis. I also want to thank Tom Arne Danielsen for his assistance with VHDL coding. A special thanks goes to associate professor Torfinn Lindem from the Department of Physics, UiO, and professor Jon Petter Omtvedt from the Department of Chemistry, UiO, for assisting in the radiation testing at SAFE. A lot of gratitude goes to Hans K. Otnes Berge and Olav Stanly Kyrvestad for providing me with helpful information regarding many theoretical and technical aspects encountered in the course of this thesis work. I also want to thank the students at the lab, Mats, Dag and Geir for both relevant and irrelevant discussions during my stay at the Nanoelectronics group.

On a more personal note, I want to thank my family for their support throughout my master thesis work.

## **Contents**

| Ab | stract |                                                             | Ì  |

|----|--------|-------------------------------------------------------------|----|

| Pr | eface  |                                                             | ii |

| 1  | Intro  | oduction                                                    | 1  |

|    | 1.1    | Motivation                                                  | 2  |

|    | 1.2    | Thesis outline                                              | 3  |

| 2  | Low    | Power- and Radiation Tolerant CMOS Design                   | 5  |

|    | 2.1    | Low Power Digital CMOS                                      | 5  |

|    |        | 2.1.1 Subthreshold Operation                                | 5  |

|    | 2.2    | Radiation Environments                                      | 6  |

|    | 2.3    | Radiation Effects In Electronics                            | 7  |

|    |        | 2.3.1 Single Event Transients                               | 8  |

|    |        | 2.3.2 Single Event Upsets                                   | 8  |

|    |        | 2.3.3 Multiple Bit Upset                                    | 8  |

|    |        | 2.3.4 Single Event Latchup                                  | 9  |

|    |        | 2.3.5 Total Ionizing Dose Effects                           | 9  |

|    | 2.4    | Radiation Tolerant CMOS Design                              | 9  |

| 3  | Tran   | sistor -Structures and -Properties in RHBD Applications     | 11 |

|    | 3.1    | Linear CMOS devices                                         | 11 |

|    |        | 3.1.1 Impact of technology scaling on radiation tolerance   | 11 |

|    |        | 3.1.2 Radiation induced leakage                             | 12 |

|    | 3.2    | Alternative CMOS devices                                    | 14 |

| 4  | Circ   | uit- and Architectural Level Hardening of SAR Architectures | 17 |

|    | 4.1    | Circuit level radiation hardening of logic blocks           | 17 |

|    |        | 4.1.1 SET mitigation                                        | 17 |

|    |        | 4.1.2 SEU mitigation                                        | 18 |

|    | 4.2    | Architectural level hardening                               | 19 |

|    |        | 4.2.1 Triple Modular Redundancy                             | 19 |

|    |        | 4.2.2 Dual Modular Redundancy                               | 20 |

|    | 4.3    | SEE Layout Considerations                                   | 21 |

|    | 4.4    | SAR architecture                                            | 21 |

| 5  | Soft   | Error Simulation- and Test Methodology                      | 25 |

|    | 5.1    | Simulation Methodology                                      | 25 |

|    | 5.2    | Template-based Soft Error Characterization                  | 27 |

vi CONTENTS

|   |                                                            | 5.2.1<br>5.2.2<br>5.2.3    | Soft Error Detection using a FPGA                                                                                                                                     | 28<br>29<br>30 |

|---|------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 6 | Resu<br>6.1                                                | lts<br>Papers<br>6.1.1     | Paper I:                                                                                                                                                              | <b>33</b> 33   |

|   |                                                            | 6.1.2                      | Low-Power Subthreshold to Above Threshold Level Shifter in 90 nm Process Paper II:  Memory Elements Based on Minority-3 Gates and Inverters Implemented in 90 nm CMOS |                |

|   |                                                            | 6.1.3                      | in 90 nm CMOS                                                                                                                                                         | 38<br>45       |

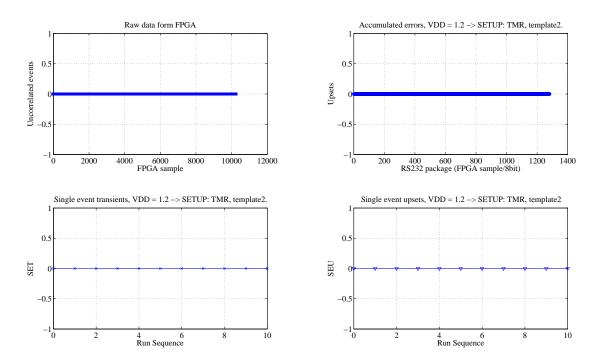

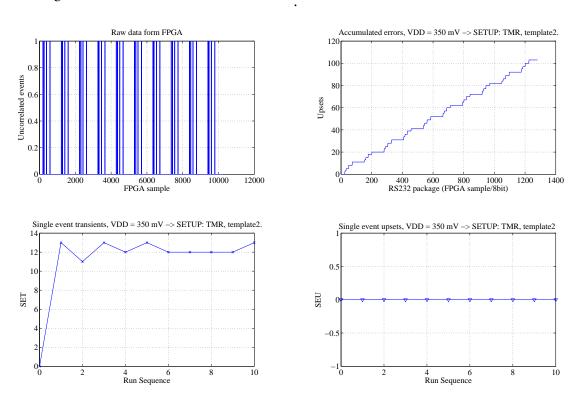

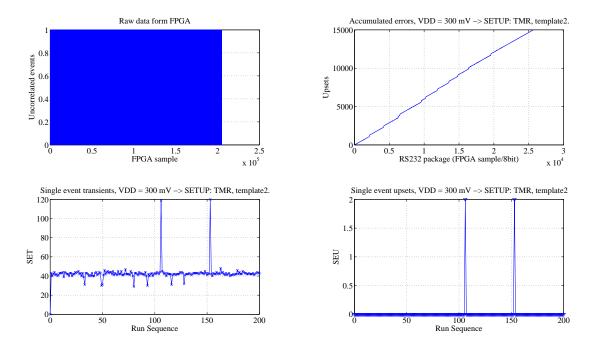

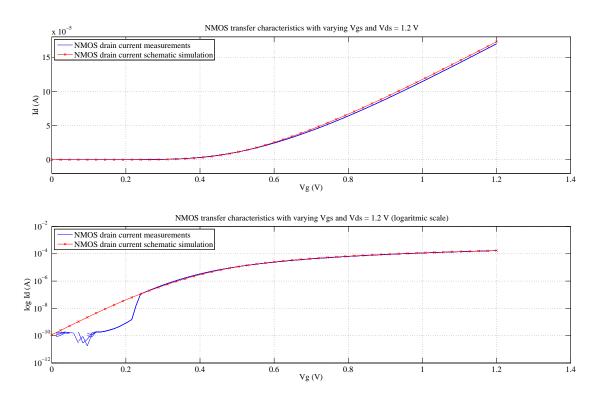

|   | 6.2                                                        | Irradiat<br>6.2.1<br>6.2.2 | ion of SAR architectures                                                                                                                                              | 54<br>54<br>57 |

| 7 | Disc                                                       | ussion                     |                                                                                                                                                                       | 59             |

| 8 | Conc                                                       | clusion                    |                                                                                                                                                                       | 61             |

| A | VHD                                                        | )L code                    | for template-based soft error characterization                                                                                                                        | 69             |

| В | Matl                                                       | ab code                    | for error detection                                                                                                                                                   | 73             |

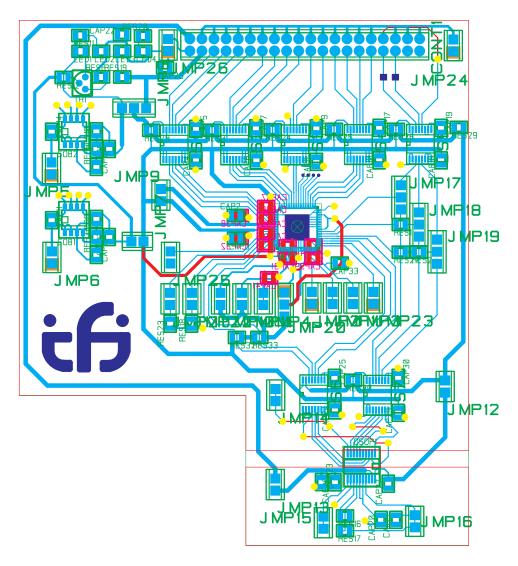

| C | C PCB Layout                                               |                            |                                                                                                                                                                       | 79             |

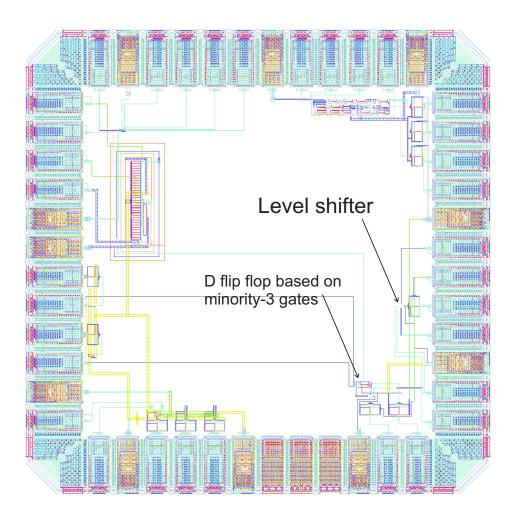

| D | O ST Microelectronics chip (90 nm general purpose process) |                            |                                                                                                                                                                       | 81             |

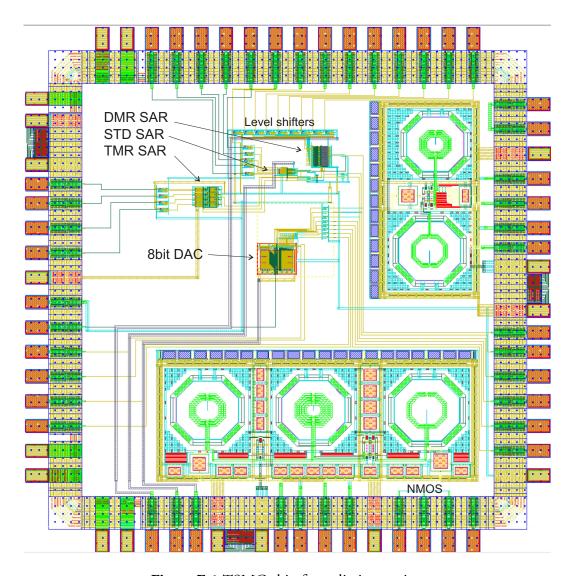

| E | TSMC chip (90 nm low power process)                        |                            |                                                                                                                                                                       | 83             |

## List of Figures

| 1.1                                    | Multiple voltage domains interfaced with level shifters                                                                                                              | 1                                |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2.1<br>2.2<br>2.3                      | Earth's radiation environment                                                                                                                                        | 6<br>7<br>8                      |

| 3.1<br>3.2<br>3.3<br>3.4               | Lateral leakage paths, NMOS intra-device leakage                                                                                                                     | 12<br>13<br>13<br>14             |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | C-element                                                                                                                                                            | 18<br>19<br>20<br>21<br>22<br>22 |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6 | Particle hit induced current                                                                                                                                         | 26<br>26<br>27<br>28<br>29<br>31 |

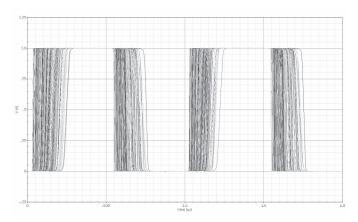

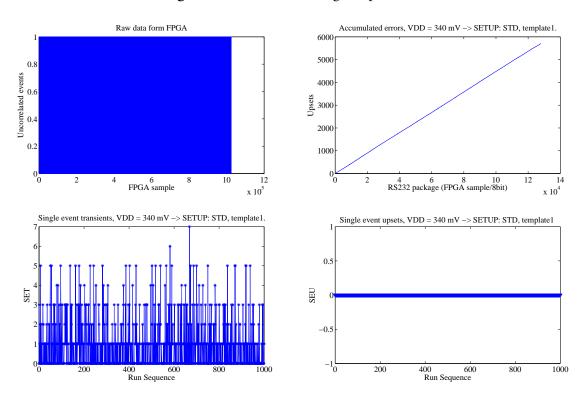

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6 | Preliminary error detection of the TMR SAR architecture with 1.2 V supply voltage Preliminary error detection of the TMR SAR architecture with 350 mV supply voltage | 55<br>56<br>57<br>58             |

| C.1                                    | PCB layout                                                                                                                                                           | 79                               |

| D.1                                    | ST Microelectronics chip with level shifter and a D flip flop based minority-3 gates and inverters                                                                   | 81                               |

| E.1                                    | TSMC chip for radiation testing                                                                                                                                      | 83                               |

viii LIST OF FIGURES

## Chapter 1

## Introduction

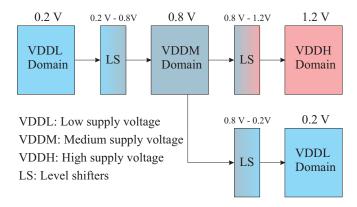

The increasing demand of portability and extended battery life has been a major driving force for optimization between power consumption, performance and reliability. The use of multiple voltage- and clock domains is a good way to optimize device performance and reliability, while maintaining low power consumption [3]. Such implementations dedicate low supply voltage to circuits that operate at low speed in order to save power, while higher supply voltages are dedicated to circuits that have higher speed requirements at the expense of increased power consumption [4]. The use of multiple voltage domains increases circuit complexity, and therefore requires thourough performance and reliability analysis. Level shifters need to be inserted for interfacing of different voltage domains and digital logic blocks need to be designed for their intended supply voltage operation [3,5,6]. The utilization of dynamic voltage scaling enables for futher optimization between performance and power saving by varying the supply voltage based on the speed requirements of the integrated circuit (IC) at any given time. Figure 1.1 shows the principle behind multiple voltage domain utilization.

**Figure 1.1** Multiple voltage domains interfaced with level shifters

Low power IC design is also of interest to the radiation tolerant market. Radiation tolerance of standard circuits is however strongly dependent on the amount of current flowing through each node in the circuit. For this reason, low power- and radiation tolerant circuit implementations are often contradictory in design and are therefore governed by increased complexity and overheads compared to the implementation of equivalent standard circuits. Contemporary technology scaling trends which have contributed to smaller feature sizes, reduction in supply voltage as well as higher density designs have made deep submicron ICs increasingly susceptible to radiation induced errors. Such errors are of main concern to memory design, however standard logic circuits are also becoming more sensitive to radiation induced errors and therefore need to be taken into account

when designing circits for applications requiring high reliability. Parity and error-correcting code (ECC) are usually used in memory designs in order to protect memory from radiation induced errors. Nonetheless, with peripheral combinational and sequential logic exhibiting poor radiation tolerance, the impact of the effectiveness of ECC is thereby limited [7].

Reports have shown that the reliability of Earth based designs has been compromised<sup>1</sup>, sending a clear message to the electronics industry that radiation induced errors are of great concern for further advancement of IC design. Moreover, state of the art realization of automotive and medical devices, such as implantable biomedical devices, must be hardened against radiation induced errors in order to minimize the possibility for human hazards<sup>2</sup>. Comparable Earth based applications have initially the lowest radiation tolerance requirements. The radiation tolerance requirements increase as the application areas get more specific, such as military use and nuclear power plants. For applications such as satallitecommunication, the radiation tolerance requirements may become relatively higher because of the value and cost implications of such projects. System failures that occur in Earth based applications are more accessable for repairs then failures occurring in space applications. Therefore, the radiation tolerance requirements of systems found in space applications are often relatively higher in order to minimize the probability for potential need of repairs.

Current research efforts within the field of radiation tolerant electronics design are focused on meeting these requirements by using commercial process foundries instead of radiation hardened process foundries (which are dedicated for the purpose of radiation tolerance). Design and development of radiation tolerant digital custom cell libraries in commercial processes may contribute to increased efficiency for applications requiring radiation tolerance in terms of power, area, speed and time to market [8]. However, before customized cell libraries can be implemented, a thourough radiation tolerance characterization of the commercial process needs to be conducted. The impact of different types of radiation effects needs to be identified, and techniques for mitigating radiation effects need to be employed. Simulation- and physical verification methodologies are essential in order to be able to predict the radiation tolerance of such cell libraries.

#### 1.1 Motivation

Technology and market trends have altered the way radiation tolerance is achieved in present day electronics design. The design trend is shifting towards radiation hardened by design (RHBD) methodologies and away from radiation hardened by process (RHBP) methodologies. Over the past few decades, the RHBP IC market has been substantially reduced. There are several reasons for this trend, the most significant being the exponential growth of the consumer IC market which has attracted many semiconductor suppliers [9]. Environmental directives such as RoHS and WEEE have indirectly restriced the radiation hardened supplier market because suppliers are more interested in the more lucrative commercial IC market. Moreover, unintentional consequences of the advancements in the commercial semiconductor processing technologies has contributed to increased total dose hardness of commercially produced ICs. The increase in total dose hardness has made commercial processes favorable in many applications where high reliability is required, given that the negative aspects of radiation induced effects are tackled appropriately. Although there are positive sides when it comes to utilizing commercial processes for the purpose of radiation tolerant IC design, there are also negative sides, especially related to the technology scaling trends. The reduction of the supply voltage makes circuits more vulnerable to radiation induced particle hits, which is an effect that needs to be countered using specialized circuit, architectural and layout topologies, i.e. RHBD.

<sup>&</sup>lt;sup>1</sup>Latchup on CISCO routers in 2004 (www.cisco.com)

<sup>&</sup>lt;sup>2</sup>Pacemakers experienced neutron-induced shutdowns (IEEE TNS 96)

1.2 Thesis outline 3

RHBD circuits do impose an area, speed and power consumption overhead compared to the equivalent unhardened circuits in the same process. Nevertheless, due to the fact that radiation hardened process foundries lag 2-3 generation behind commercial process foundries in terms of performance (and availability), the use of commercial process flows are therefore attractive for meeting radiation tolerance requirements at the same time as increasing the performance [10, 9]. The ultimate goal of utilizing commercial IC processes is the instigation of cheaper and faster design and production of radiation tolerant electronics, while maintaining the best possible performance and minimizing RHBD penalties.

#### 1.2 Thesis outline

**Chapter 2** gives a brief introduction to low power- and radiation tolerant CMOS design. A brief introduction to radiation effects in electronics is also provided.

**Chapter 3** presents the most substantial transistor properties in digital RHBD applications.

**Chapter 4** presents circuit- and architectural level SET and SEU mitigation techniques, which are applied to three SAR architectures for SEU characterization.

**Chapter 5** gives an overview the soft error simulation- and test methodology used to evaluate the SEU response of the SAR architectures.

**Chapter 6** presents some of the results obtained during this thesis work. Three papers are included as well as the results from the SEU characterization of SAR architectures.

**Chapter 7** is a discussion of the thesis contributions.

Chapter 8 concludes this thesis work and provides some remarks regarding future work.

Five appendices are also included:

**Appendix A** shows a part of the VHDL code for template-based soft error characterization.

**Appendix B** shows a part of matlab code for error detection.

**Appendix C** shows the PCB layout.

**Appendix D** shows the layout of the ST Microelectronics chip (90 nm general purpose process).

**Appendix E** shows the layout of the TSMC chip (90 nm low power process).

A CD has been enclosed with additional material including full VHDL code for the template-based soft error characterization, necessary matlab code for running the experiment as well as additional measurement results.

## Chapter 2

# Low Power- and Radiation Tolerant CMOS Design

## 2.1 Low Power Digital CMOS

The increasing requirement of portability has been a major driving force for development in low power digital CMOS design the last few decades. Low power IC design incorporates many different design techniques in order to achieve low power consumption while maintaining reasonable speed performace. Such techniques may include utilization of Multi-threshold CMOS (MTC-MOS), low power clocking, multi-supply voltages, dynamic voltage- and frequency scaling and/or standby modes [11]. Although there are many ways of attaining low power consumption, the most direct and dramatic means of reducing power consumption in ICs is by operating circuits in the subthreshold region [12, 13].

## 2.1.1 Subthreshold Operation

Subthreshold operation has become a well established region of operation for digital circuits when ultra low power circuit operation is in demand, and speed is of secondary importance [14]. Subthreshold operation implies that the gate-source voltage,  $V_{gs}$ , and the power supply voltage,  $V_{dd}$ , is below the absolute value of the transistor's threshold voltage,  $|V_T|$  [15]. By reducing the power supply voltage down to the subthreshold region, a large decrease in static and dynamic power consumption can be achieved. However, a decrease in power supply voltage also contributes to circuit reliability issues. Process- and missmatch variations gain an increased impact on circuit behavior due to exponential current dependencies in the subthreshold region. The subthreshold current  $I_{Dsub}$  is given by [15]

$$I_{Dsub} = I_0 e^{\frac{V_{gs} - V_T}{nV_{th}}} \left( 1 - e^{\frac{-V_{ds}}{V_{th}}} \right)$$

(2.1)

where  $I_0$  is the drain current when  $V_{gs} < V_T$

$$I_0 = \mu_0 C_{ox} \frac{W}{L} (n-1) V_{th}^2 \tag{2.2}$$

The exponential current dependencies may lead to large variations in propagation delay, which make it hard to determine the design specification predictability [16]. Such specification predictabilities range from  $I_{ON}/I_{OFF}$  ratio variations to setup- and hold time violations in sequential logic, and are highly dependent on circuit topology choice. Even though subthreshold operation

involves several design challenges, the operating region still remains an attractive method for achieving ultra low power CMOS circuits, given that proper design techniques are employed.

#### 2.2 Radiation Environments

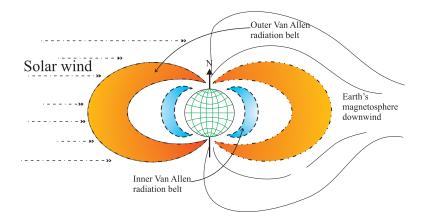

Electronic devices are often exposed to radiation effects, and the most frequently associated radiation environment is the naturally-occurring space radiation environment. Put in simple terms, space electronics are exposed to radiation from the Van Allen belts, solar flares, solar wind and cosmic rays.

Spacecraft and satellites in Earth-orbit encounter large amounts of radiation from the Van Allen radiation belts, which are regions of trapped protons and electrons, see Figure 2.1. The inner Van Allen belt contains mainly protons with energies up to 30 MeV, whereas the outer Van Allen belt contains fast moving electrons and slow moving ions, that are trapped in the magnetosphere, with energies which can exceed 100 MeV. The particle flux in these regions depends highly on the altitude, orbital inclination as well as the solar activity.

**Figure 2.1** Earth's radiation environment

Electronic devices also encounter hazardous radiation environments in the Earths atmosphere. Galactic cosmic rays, which originate from outside the solar system, consist of low flux, highly energetic particles up to the GeV range. These particles produce intense ionization and are very hard to shield against. When cosmic rays interact with atmospheric nuclei, nuclear spallation reactions take place and induce production of high energy neutrons and pions [17]. Figure 2.2 illustrates the terrestrial nuclear cascade shower as a result of incoming cosmic rays.

As in the geospace environment, the particle-flux and energy in the Earths atmosphere depend highly on altitude as well as events in the intergalactic space weather. Therefore, the radiation impact on electronics is higher for avionics applications then for ground based applications [2].

Cosmic rays can also induce soft errors in electronics at sea level [1]. The main radiation sources causing soft errors in electronics at sea level are cosmic ray induced neutrons and pions, and microelectronic packaging induced alpha particles. [1] As neutrons and pions interact with silicon, nuclear reaction takes place and the resulting high energy secondary particles scatter in all directions.

Furthermore, natural radiation environments are not the only radiation environments hazardous for electronics. Man-made radiation environments can also induce errors on electronic devices. Such environments are encountered in, but not limited to, nuclear power plants, medical applications and warefare.

Figure 2.2 Terrestrial radiation environment, adapted from [1]

### 2.3 Radiation Effects In Electronics

Radiation effects in electronics are often categorized into several separate categories of radiation induced effects. Galactic cosmic rays, cosmic solar particles and trapped protons in radiation belts are the main sources of energetic particles causing single event effects (SEE). These single event effect are initially non-destructive events in electronic devices. However, radiation effects can also result in semiconductor degradation (both over time and instantly) by causing radiation damage to local or global parts of the device. Therefore, radiation induced errors in electronics are often categorized in soft and hard errors.

Single event effects have received recognition ever since the 1950s, and their nature has been researched thoroughly ever since then [1]. Soft errors are commonly related to the post impact state of high energy ionizing particles interacting with semiconductor materials at locations close to sensitive circuit nodes of active devices. Figure 2.3 shows the principle behind this phenomenon. When a high energy particle passes through the silicon near a sensitive node, the particle produces a dense radial distribution of electron-hole pairs along its trajectory (Figure 2.3 a). Electrons and holes then drift towards their opposite potential via the electric field in the depletion region, thereby extending and distorting the depletion region, thus giving rise to rapid charge collection via drift (Figure 2.3 b). When the excess carriers along the particle track have been collected, recombined or diffused away from the junction area, the slower diffusion collection takes over until equilibrium is reached (Figure 2.3 c). A current pulse is then generated as a result of the collected charge (2.3 c) and causes a voltage fluctuation at this node [7].

This is only a principal model of a particle strike and the final result depends on a lot of variables such as type of particle, its initial energy, its angle of impact and process parameters.

**Figure 2.3** Principle behind charge collection in a n+/p junction immediately after a particle strike, adapted from [2]

Hard errors on the other hand are errors that cause destructive damage to transistors and other semiconductor materials. Hard errors often occur over time due to cumulative effects, and can therefore be avoided if the potential hard error inducing effects are discovered and corrected in time.

This following subsections briefly describes the most common, both non-destructive and destructive, radiation effects encountered in electronic devices.

## 2.3.1 Single Event Transients

Single Event Transients (SET) are transient voltage fluctuations, induced by charge deposition by a subatomic particle strike. The voltage fluctuations can propagate to storage elements and cause an erroneous latched logic state, resulting in a Single Event Upset (SEU) [18].

Single event transients are of great concern for analog electronics such as comparators [19]. Mitigation techniques primarily involve capacitive hardening and in some cases digital correction techniques.

## 2.3.2 Single Event Upsets

A SEU can be defined as a change in the logic state of a latched logic element from a logic one to a logic zero or vice-versa. SEU occur when high energy particles alter the charge deposition in critical nodes in such a way that it results in a bit error. SEU are defined to be non-destructive events, and therefore the affected logic can be rewritten or reset to regain proper operational behavior [18].

## 2.3.3 Multiple Bit Upset

Multiple bit upsets (MBU) are upsets resulting from a single high velocity charged particle strike, passing through several sensitive nodes in an electronic device, and thereby changing the logic state

in several adjacent latched logic elements. For high velocity particle strikes, the number of bit upsets has been shown to be highly dependent on the impact angle of the particle [20]. MBUs can also occur as a result of proton induced- as well as terrestrial neutron induced nuclear reactions that produce secondary ionizing particles which interact with capacitive nodes in close proximity of the initial strike [21]. However, due to the technology feature size scaling trends, the device sensitivity to MBUs is expected to keep increasing in high density ultra deep-submicron designs [22, 23].

#### 2.3.4 Single Event Latchup

Single event latch-up is a permanent and potentially destructive state of the device under test (DUT) whereby a parasitic thyristor structure is triggered by a high energy particle strike and a low impedance, high current path is established between the power rails. A power cycle is usually sufficient to reestablish normal operation of the device. If for example a latch-up is left uncorrected, the high current path may result in destructive failure, referred to as Single Event Burn-out (SEBO).

#### 2.3.5 Total Ionizing Dose Effects

Total ionizing doze (TID) effects are cumulative damage effects caused by ionizing radiation over time. In semiconductor devices, ionizing radiation contaminates oxide layers by accumulation of trapped positive charge, which degrades transistor performance by causing channel inversion at the oxide/silicon interface. These inverted channels result in current conducting leakage paths and given high enough radiation doses, over a longer period of time, the trapped charge can become sufficiently high to force a transistor to be permanently open/closed. TID effect may also result in displacement damage in electronic devices as a result of proton induced degradation mechanisms [24].

## 2.4 Radiation Tolerant CMOS Design

Throughout this decade, the space industry has been signaling an increased interest in robust ultra low power integrated circuit design for use in future space missions [25, 26, 27]. A special case of this trend has come to be known as "CMOS ULTRA-LOW POWER RADIATION TOLERANT" (CULPRIT) integrated circuits [27]. This concept evolves around scaling of the power supply voltage to reduce power consumption at the same time as scaling the threshold voltage in order to compensate for the performance loss imposed by a decrease in supply voltage.

Traditional circuits used in space applications are designed using radiation hardened processes and may consume relatively large amounts of power. However, with the decline in the RHBP market and with new semiconductor technologies emerging, new mitigation techniques need to be employed in order to successfully suppress the impact of soft errors on modern electronic devices [2].

These recent years, several papers have been published on exploring potential advantages with subthreshold operation in radiation tolerant digital CMOS design [28, 29]. Experimental results have shown that the TID induced leakage current can be reduce by up to 100 times by lowering the supply voltage [28]. With the use of circuit-level soft error mitigation techniques, digital circuits operating in the subthreshold region may become relevant for hazardous radiation environments, and even space applications in the future. In such applications, subthreshold operation may be employed by secondary systems or voltage domains, thereby freeing up power for more crucial components.

<sup>&</sup>lt;sup>1</sup>Iridium Technologies have put radiation hardened subthreshold circuit design as one of their ultimate goals

Traditional design techniques such as voltage scaling and multi supply voltage domain utilization have been proposed for realization of low power, radiation tolerant circuit designs [30]. The proposed idea is based on the use of low-VDD operation for circuits that are less sensitive to radiation induced errors, and high-VDD for circuits that are more sensitive to radiation induced errors.

A challenge with reduced power supply voltages is the reduction of the critical charge,  $Q_{crit}$ , which is the required amount of charge to upset a capacitive node in a circuit [31].  $Q_{crit}$  is a supply voltage- and transistor geometry dependent parameter and will be addressed in Section 5.1 and in Section 4.1.2.

## Chapter 3

## Transistor -Structures and -Properties in RHBD Applications

When designing circuits for radiation tolerant applications, the designer must primarily evaluate the transistor behavior for the targeted radiation environment. For these types of applications, transistor behavior is highly dependent on process choice as well as technology node [32]. The primary concern regarding transistor behavior is described in terms of TID induced leakage. Several approaches have been proposed to counter the effects of TID, and thereby retain stable transistor operation in harsh radiation environments using standard commercial CMOS processes.

#### 3.1 Linear CMOS devices

The standard transistor, also referred to as a linear device, has traditionally been regarded as a poor choice for RHBD applications. The main reason for this is the impact of TID induced leakage which is highly dependent on device isolation process technique and to some extent gate oxide thickness, the first mentioned being implemented using Shallow trench isolation (STI) in newer processes [33, 2]. For gate oxide thickness above 6nm, trapped positive charge in the gate oxide has been a big source of threshold voltage shifts in the transistor [34]. This variation in threshold voltage may potentially drive the transistor out of its intended operation area, and thereby render the transistor unreliable. In the recent years however, this trend has shifted and standard CMOS transistors have become more attractive for use in radiation tolerant integrated circuit design due to the impact of technology scaling.

## 3.1.1 Impact of technology scaling on radiation tolerance

Technology scaling trends in commercial processes have brought about both positive and negative effects in terms of radiation tolerance. The TID induced leakage currents and threshold voltage shifts have been substantially reduced as a consequence of using thinner gate oxides [10]. Contemporary commercial processes exhibit little sensitivity to radiation induced threshold voltage shifts due to the reduced possibility of radiation induced positive charge getting trapped in the thin oxide layers [10]. Furthermore, the utilization of STI instead of Local Oxidation of Silicon (LOCOS) for inter device isolation has contributed to large reductions in TID induced leakage currents. These factors are some of the main reasons RHBD has been made a realistic possibility. Reports have also shown that thin gate oxides are adequate for operating in heavy ion environments, without great risk of gate oxide breakdowns [35].

On the other hand, the impact of technology scaling has also contributed to smaller feature sizes

which in turn result in less nodal capacitances which make devices more prone to SEUs due to less energy may result in a SET. Additionally, as the device sizes shrink, higher density is achieved which thereby enables a single particle hit to upset several devices in close proximity. These properties are further discussed in Section 4.1.2

In contrast to thin gate oxides, isolation oxides are thicker and therefore enable for TID induced positive trapped charge, and thereby need to be taken into account when designing circuits for radiation tolerant applications.

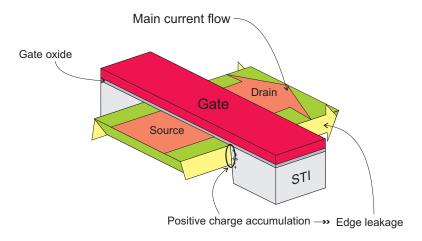

#### 3.1.2 Radiation induced leakage

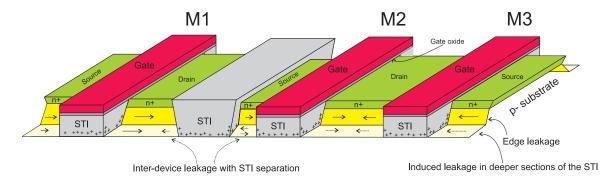

Radiation-induced leakage may be categorized into intra-device leakage and inter-device leakage, since they make up the main sources of leakage currents contaminating the transistor behavior [36]. Intra-device leakage are the leakage currents that form between the drain and source terminals of a transistor, while inter-device leakage are the leakage currents that form between adjacent transistors.

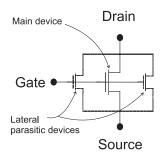

In a standard NMOS, lateral leakage paths can be generated due to buildup of TID induced positive trapped charge in the STI oxide sidewalls, at the SI/SOI2 interface [37, 33]. Figure 3.1 illustrates intra-device leakage current in a standard MOSFET. The positive trapped charge inverts portions of the STI oxide sidewalls, thereby creating an edge leakage path between the source and drain terminals or between adjacent transistors [38]. These leakage paths can be modeled

Figure 3.1 Lateral leakage paths, NMOS intra-device leakage

as lateral parasitic transistors with the same length as the actual transistor length. The transistor model can however only be used as a guidance model, as the lateral leakage paths also depend on p-substrate doping and radiation dose, as well as other physical parameters such as Length of Diffusion (LOD) and Shallow Thrench Isolation Width (STIW) [39]. Figure 3.2 illustrates the transistor-level modeling of lateral leakage in a single MOSFET.

$$W_{main} = n_{finger} \cdot W_{finger} \tag{3.1}$$

$$W_{lateral} = 2 \cdot n_{finger} \cdot W_{lateral, finger} \tag{3.2}$$

$$W_{tot} = W_{main} + W_{lateral} \tag{3.3}$$

As the radiation dose increases, a larger portion of the STI oxide sidewalls near the surface becomes inverted, resulting in higher intra- and inter-device leakage currents. Figure 3.3 illustrates

13

Figure 3.2 Modeling of lateral leakage paths

the effect a large radiation dose can have on both intra- and inter-device leakage. As a result of the increased radiation dose, larger portions of the deeper STI edges become inverted, creating current conducting parasitic channels which further increase the leakage currents. It should be noted that the inversion strength is lower at the deeper levels of the STI oxide sidewall.

Figure 3.3 Lateral leakage paths, NMOS intra- and inter-device leakage

As seen in Figure 3.3, the intra- and inter-device leakage in M2 and M3 is dominated by the lateral leakage paths in and between the transistors when the transistors share active drain/source area. This implies also an increased leakage current vulnerability of transistors utilizing fingered structures, as depicted by equation 3.3 [40]. However, for the case where adjacent transistors do not share drain or source and in addition are separated by STI, then the STI can have a significant impact on reducing the edge leakage. Nevertheless, given high enough radiation dose, parasitic current conducting channels would still form in the deeper portions of the STI, thereby establishing inter-device leakage paths.

For the case of PMOS transistors, experimental results have shown that the TID induced leakage in PMOS transistors is very small compared to NMOS transistors for normal bias conditions [41,36]. The reason is that the trapped positive charge results in negative threshold voltage shift for PMOS transistors, thereby not inducing the previously mentioned leakage paths. This will in turn result to a decrease in drive current for the PMOS.

TID induced leakage and threshold voltage shifts are regarded to be negligible in sub-180 nm commercial processes when transistors are operated at full supply voltage and annealing effects are taken into account [10]. On the other hand, the TID induced leakage may have a significant impact on low supply voltage operation. In order to be able to utilize supply voltage scaling for the purpose of power saving, the TID leakage currents need to be suppressed for the sake of keeping the minimum supply voltage,  $V_{min}$ , as low as possible (subthreshold for example). When operation circuits at low supply voltages, the TID induced leakage my reduce the  $I_{ON}/I_{OFF}$  ratio due to degradation in the subthreshold slope.

### 3.2 Alternative CMOS devices

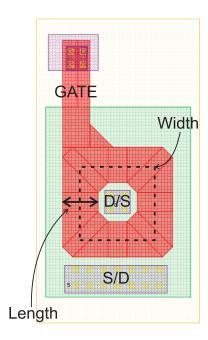

In order to counter the radiation induced leakage along the STI oxide sidewalls that occur in the linear MOSFET structure, the ELT (Enclosed layout transistor) has been a popular transistor device for use in radiation environments in the multi-MeV range [2]. A layout of an ELT is shown in Figure 3.4.

**Figure 3.4** Layout of an ELT

Due to the physical structure of the ELT, the radiation induced leakage is substantially reduced at high TID levels compared to that of the linear transistor. The main reason for the small radiation induced leakage is that the intra-device leakage in the ELT is not affected by the STI sidewalls, since the STI sidewalls do not exist between source and drain terminals in the ELT structure. Furthermore, the utilization of ELT substantially reduces threshold voltage shifts compared to linear transistor devices.

Even though customized transistors such as the ELT offer better total dose hardness at higher radiation dose, they also contribute to complications associated with device geometries and modeling [2]. As it may be appearant from Figure 3.4, the source and drain of the ELT transistor are not symmetrical, and thereby the current conductance of the transistor will vary based on where the drain terminal is assigned. If the drain terminal is assigned to the enclosed part of the transistor, the transistor would have a larger current conduction due to lower drain terminal capacitance then what would have been achieved with having the source terminal in the enclosed part of the transistor. Furthermore, the layout geometry of the ELT imposes a minimum W/L ratio of the transistor since the width is defined by the ring length and the length is defined by the ring width (simplified explanation). For small aspect ratios, a large area consumption is to be expected since the only possible way of achieving very small aspect ratios is by increasing the length parameter. More extensive modeling of the ELT may be found in [42].

In the recent couple of years several papers have proposed new radiation tolerant transistor structures with the aim of reducing the area overhead imposed by the ELT layout topology [43] [44]. However, the device behavior still remains a issue when using commercial CAD tools for simulation without extensive alterations, therefore the most reliable device modeling is still achieved

15

using Technology Computer Aided Design (TCAD) tools<sup>1</sup>. Standard commercial CAD tools are by default not intended for extraction the physical geometries of ELTs, and therefore require manual netlist alterations. Moreover, even with altered extracted netlists, the embedded transistor models may not be sufficient to model the complex behavior of ELT layout topologies.

<sup>&</sup>lt;sup>1</sup>Examples of such tools are; Sentaurus TCAD from Synopsys and NanoTCAD from SFDRC

## Chapter 4

## Circuit- and Architectural Level Hardening of SAR Architectures

This chapter will focus on the selected mitigation techniques performed in order to achieve SEU and SET tolerance in three SAR architectures which employ individual mitigation techniques. The mitigation techniques include circuit-level radiation hardening techniques as well as architecture-level hardening techniques. Due to technology scaling, also layout considerations need to be taken into account when employing SEU and SET mitigation techniques. A SAR architecture is adapted from [45], which consists of both combinational and sequential logic. Since large systems are built up using combinational and sequential logic blocks which operate in conjunction, the SAR architecture can be regarded as a scaled model of a larger system. By analysing the SET and SEU tolerance of the hardened SAR architectures, a better understanding will be provided on how the different mitigation techniques compare.

## 4.1 Circuit level radiation hardening of logic blocks

Circuit level radiation hardening involves the use of circuit topologies capable of withstanding the impact of subatomic particle hits. Several papers have been published on novel mitigation topologies ever since the discovery of particle hit induced errors in electronic devices [46, 50, 49].

Circuit level radiation hardening is primarily aimed at SEU and SET mitigation. Combinational logic is only vulnerable to SETs, sequential logic is however vulnerable to both SETs and SEUs.

## 4.1.1 SET mitigation

There are very few circuit-level SET mitigation techniques that have been proposed in literature. This is mainly due to the fact that every interaction between a subatomic particle hit and a sensitive node in a circuit, will result in a SET given that the particle hit produces enough energy. The magnitude of the impact of the SET on a circuit is closely related to the node capacitance and thereby  $Q_{crit}$ . The effect of a radiation induced strike on any node in a circuit can be illustrated by Eq. 4.1.

$$\triangle q = C \cdot \triangle V \tag{4.1}$$

where  $\triangle q$  is the collected charge due to the radiation strike, C is the effective capacitance of a given node and  $\triangle V$  is the resulting voltage change at that particular node. As feature sizes shrink, the node capacitance decreases with the square of the feature size, resulting in an additional

reduction in  $Q_{crit}$  and additionally an increased impact on node voltage. The increased impact in node voltage is a major contributor to single event transients at low supply voltages. This implies that increasing of  $Q_{crit}$  with design techniques is a good way to start hardening a circuit against radiation induced errors. This approach is often referred to as capacitive hardening [47]. There are several ways of increasing  $Q_{crit}$ , one of them is to increase the node capacitance by increasing the transistor size (i.e drain/source geometries of transistors) or by using circuit topologies that increase node capacitance [48].

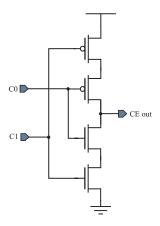

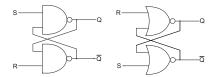

Due to transistor geometries and parasitic components, SETs naturally diminish as they propagate through logic gates. However, the longer SETs propagate, the higher the propability is that they will become latched. Therefore, it is beneficial to suppress the impact of SETs is by filtering them out as fast as possible, thereby prohibiting SET propagation to other logic blocks which might cause SEUs, if latched. Several papers have proposed the use of C-elements for this purpose [49,50]. Figure 4.1 shows the schematic of a C-element.

Figure 4.1 C-element

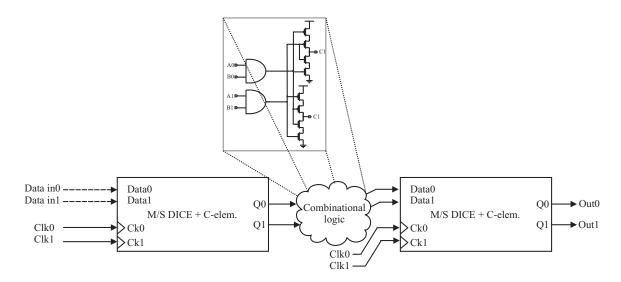

The C-element has two inputs and one output that changes its value only when the two inputs change their values simultaneously (i.e acts as and inverter if there is correspondence between both inputs). Since a SET only results in a short voltage pulse<sup>1</sup>, the C-element is able to suppress the propagation of the SET, given that the SET occurs only on one of the inputs. This implies that two identical logic blocks are needed to drive the C-element inputs, in order to be able to use the C-element as a SET mitigation technique. Such a configuration fits well with dual modular redundancy (DMR) architectures, see Section 4.2.2. Further SET mitigation is discussed in Section 4.2 in terms of architecture level temporal redundancy.

#### 4.1.2 SEU mitigation

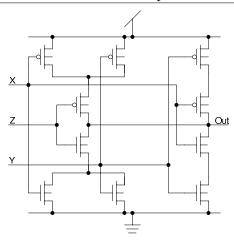

Circuit level SEU mitigation is primarily aimed at sequential logic blocks capable of storage such as latches and flip flops. SEU mitigation involves the use of circuit topologies that prevent a SET to become latched on the output of sequential logic block. In order to realize the SAR architecture, only a D flip flop was needed and is therefore the only storage element that is evaluated in this thesis. A lot of SEU tolerant latch topologies have been proposed over the years [52, 53, 54]. Several of these topologies have been evaluated and compared against eachother using the simulation method described in Section 5.1. The latch that showed the best SEU tolerance with the best tradeoff in

<sup>&</sup>lt;sup>1</sup>Experimental results have shown that the SET pulsewidths can vary from 900 ps to over 3 ns at laser energies from 85 pJ to 179 pJ respectively [51]

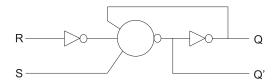

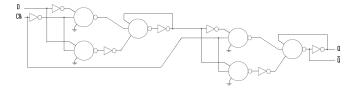

terms of speed-, area- and power consumption, was the dual interlocked cell (DICE) based latch used in [55], which originates from [56]. The DICE latch is shown in Figure 4.2

Figure 4.2 DICE latch with C-elements

This DICE based latch makes use of two locally separated data and clock inputs which, if not corrupted simultaneously, will provide SEU tolerance due to the intrinsic upset tolerance of DICE interlocking configuration. The principle behind a DICE configuration is based on four interlocked nodes where two and two nodes have complementary values at all times (A',C' = B,D). A SET event on any single node in a DICE configuration is not able to trigger the feedback due to the fast recovery time imposed by the interlocked node pairs. However, if a SET occurs on two equal node pairs, the feedback would be triggered and, the state of the latch would flip.

## 4.2 Architectural level hardening

Architectural level SET and SEU mitigation involve the use of spatial redundancy and temporal redundancy techniques. By distributing logic blocks in space, the propability of a SEU occurrences on the output of such architectures is substantially reduced. An error is produced if a particle hits several logic blocks at the same time. Temporal redundancy introduces signal distribution in time. This is an effective way of screening vulnerable inputs, such as clock inputs, from incoming SETs. In order to utilize temporal redundancy, two or more correlated data paths need to be two or more logic blocks. The time distributed data paths make sure that a transient pulse can be expected at only one of the logic block inputs at any given time.

## 4.2.1 Triple Modular Redundancy

A TMR architecture is based on three identical logic blocks which are connected to one or sometimes three majority voters. The output of the majority voter produces a correct value if at least two of the three identical logic blocks contain intended (correct) values. The voter topology may be implemented as a synchronous or asynchronous circuit, and is also vulnerable to soft errors. Therefore it is critical to harden voter circuits in order to prevent SET propagation.

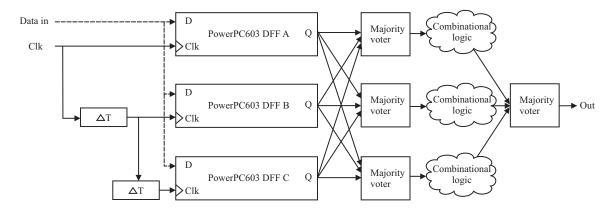

Figure 4.3 shows a TMR architecture, which utilizes both spatial- and temporal redundancy. Several degrees of spatial redundancy can be achieved by using TMR architectures. Standard spatial

Figure 4.3 TMR architecture with temporal sampling

redundancy is achieved by simply stacking the layout cells close to eachother. Higher degree of spatial redundancy can be achieved by interlaving layout cells, however, such an implementation comes at the cost of higher interconnect complexity.

The temporal sampling is in this case applied to the clock input, but can also be applied to the data inputs. Temporal sampling is effective for low/medium frequency operation, however for high performance applications, the delay imposed by the delay elements will amount to a large portion of the overall latency of the circuit. The latency resulting from the delay elements is usually set to be equal to the maximum expected SET duration.

The utilization of the TMR architecture contributes to an area overhead more then three times greater compared to a standard implementation of the same circuit. Furthermore, the power consumption is also increased approximately by the same factor, which makes TMR circuit implementations somewhat undesirable in applications where area- and power consumption are key parameters.

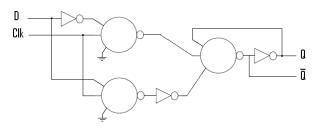

## 4.2.2 Dual Modular Redundancy

The DMR implementation presented in this thesis is based on utilization of two identical, separated data paths Figure 4.4 shows a DMR architecture which makes use of DICE latches and C-elements. The two separated data paths achieve SET tolerance by interconnecting C-element inputs between identical logic elements in the two data paths. The technique has been proposed in [50], but not in the context of dual modular redundancy. The use of interconnected C-elements ensures that SET mitigation at input stages of latches is achieved as long as two interconnected C-elements don't get hit by a particle strike at the same time. Should a SET in one of the data paths propagate to a neighbouring logic block, the SET would thereby be filtered out by the same C-element interlocking configuration, or the fast recovery time imposed by the interlocked node pairs in the DICE latch.

The utilization of C-elements and DICE latches poses a good fit for the DMR architecture in terms that all logic blocks are duplicated and C-elements are added. However the additional C-elements and the additional circuitry required to realize the DICE latch impose a area and power consumption overhead that needs to be taken into account.

For further SET and SEU mitigation in the DMR architecture, temporal sampling can also be applied to C-elements and latch inputs [50, 57].

Figure 4.4 DMR architecture

## 4.3 SEE Layout Considerations

When designing SEE tolerant circuits, it is important to consider the physical implications of a particle hit on or near a sensitive node in the circuit. Therefore layout considerations need to be taken into account in order to achieve the best possible SEE tolerance.

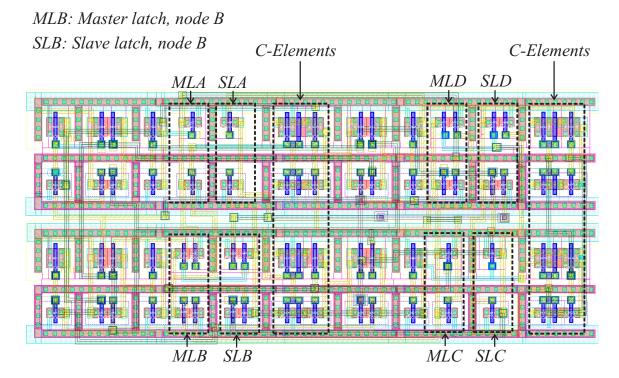

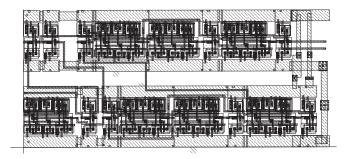

Due to the impact of technology scaling, deep submicron implementations of SEU tolerant topologies are highly affected by the charge sharing between sensitive nodes [58]. Charge sharing implies that the charge generated from a particle hit is shared between transistors in close proximity. The DICE D flip flop is therefore designed with a spatial separation of the sensitive nodes, see Figure 4.5.

As mentioned in Section 2.3, the depleted diffusion areas of a transistor are critical points of impact for a particle hit. By separating the the critical diffusion areas that make up nodes A and C, and nodes B and D in the DICE latch, a higher particle hit tolerance can be achieved. The layout of the master/slave DICE configuration is made up by interleaving the critical nodes of two DICE latches. Master latch, node B (MLB) is placed next to slave latch, node B (SLB). Their other critical noes, MLD and SLD are placed as far away as possible from the B nodes in order to minimize the propability for a single particle hit upsetting several sensitive nodes. This approach contributes to more complex nodal interconnect and more parasitic components, nevertheless, the resulting small decrease in speed is a small price to pay for a large increase in SEU tolerance.

P+ and partial N+ guardbands have been added to increase TID hardness in terms of inter device leakage currents. The guardbands also increase the single event latch-up threshold by suppressing the positive feedback path between PMOS and NMOS transistors. The use of additional guardbands comes at the expense of additionally increased area overhead in addition to the redundancy factor.

## 4.4 SAR architecture

The purpose of implementing the SAR architecture using different SET and SEU mitigation techniques, is to compare the radiation tolerance of each of the mitigation techniques and evaluate the potential penalties in terms of power consumption, speed and area overhead.

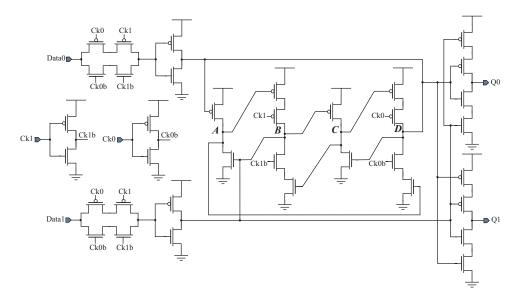

Three different implementations of the SAR architecture have been realized on the TSMC test

Figure 4.5 DICE D flip flop layout

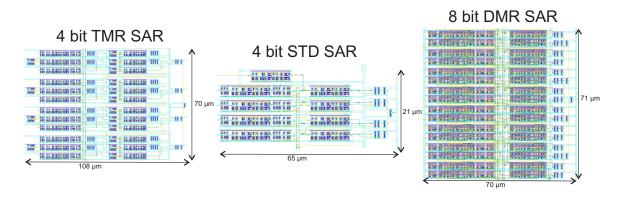

chip. Figure 4.6 shows the layout of the SAR architectures, and Table 4.1 shows the attributes of the implemented SAR architectures. The standard (STD) SAR architecture is designed using standard combinational logic and PowerPC603 D flip flops [59] in a master-slave configuration. The TMR SAR architecture is designed using the procedure presented in Section 4.2.1, and DMR SAR architecture is designed using the procedure presented in Section 4.2.2. The TMR SAR utilizes architectural level SET and SEU mitigation techniques and the DMR SAR utilizes both architectural- and circuit level SET and SEU mitigation techniques.

Synchronization is very important in CMOS design, especially in high speed, low supply voltage operation due to the impact of propagation delays. Therefore, clock trees have been implemented in all of the SAR implementations.

**Figure 4.6** Layout of the thee SAR architectures

By comparing the area overhead imposed by the implementation of the different SET and SEU mitigation techniques, we see that the TMR SAR and DMR SAR are approximately 400% and

4.4 SAR architecture 23

160% larger then the STD SAR respectively. It should be noted that the DMR SAR utilizes a radiation tolerand D flip flop topology, and that the TMR SAR utilizes a standard unhardened D flip flop topology. If the TMR SAR would use ciruit level SET and SEU mitigation techniques, the area overhead imposed by the TMR architecture would be even greater.

**Table 4.1** SAR architecture implementation comparison

|         | D flip flop type | Circuit level hardening | Architectural level hardening |

|---------|------------------|-------------------------|-------------------------------|

| STD SAR | PowerPC603       | none                    | none                          |

| DMR SAR | DICE DFF         | DICE (+ C-elements)     | DMR (+ C-elements)            |

| TMR SAR | PowerPC603       | none                    | TMR (+ temporal sampling)     |

## Chapter 5

## Soft Error Simulation- and Test Methodology

Any electronic device that is intended for, or that risks exposure to any hostile environment, must undergo an extended set of tests in order to be cleared for safe operation in the designated environment. These comprehensive tests often include a vast variety of possible soft- and hard error characterization forms and are often performed under the influence of different radiation sources, depending on the targeted environment of operation and the application for the device. Typical characterization parameters may for example include the radiation induced effects discussed in Chapter 2.3 as well as other application specific parameters, depending on the DUT. However, implementing a complete and reliable hardness assurance flow which includes all these characterization parameters is a very complex and resource demanding procedure [2].

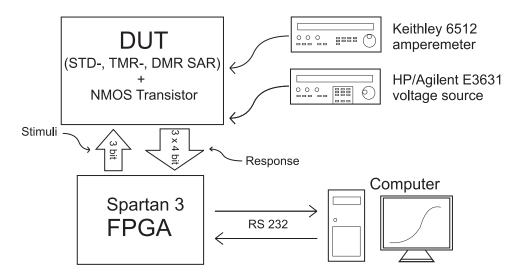

In this thesis, a small portion of a circuit hardness assurance flow is presented and is limited to SEU and SET characterization only. The assurance flow starts at schematic simulation level with SET and SEU evaluation, and ends at a physical measurement level with SEU evaluation only. The procedure utilizes an FPGA development board for interfacing with a PC, and for error detection. The supplementary equipment consists of a power supply and an amperemeter, aiding in the characterization of the DUT by recording current consumption and enabling supply voltage control.

## 5.1 Simulation Methodology

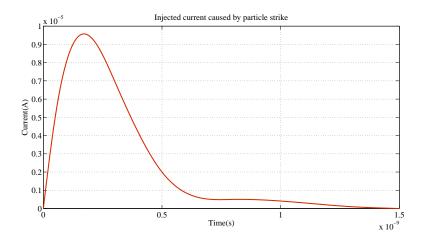

When characterizing CMOS cells for SEU and SET tolerance, a current pulse emulating a particle hit may be used for injection of current into sensitive nodes in the cell. The simulation method used in this thesis is similar to the methods used in recent publications on SEU and SET characterization on the schematic level [60,61]. The use of schematic level simulations for SEE characterization is a cheap and effective way of attaining an approximated prediction of the SEU and SET susceptibility in CMOS circuits by using standard SPICE simulation tools. However, the method does not provide a realistic particle hit scenario as the injected current pulse only affects a single node in the circuit, and parameters such as angle of particle impact and device separation are not included. Figure 5.1 shows the current pulse used for emulating a particle hit.

In this thesis, the nodal injection of the current pulse was performed using Cadence Spectre simulator by importing the data from a MATLAB generated pulse. The pulse injection was used to determine  $Q_{crit}$  of sensitive nodes, which could be determined by evaluating Eq.5.1

Figure 5.1 Particle hit induced current

$$Q_{crit} = \int_0^T I(t)dt \tag{5.1}$$

where T is the time required to drive a node from a logic high to a logic low, or vice-versa.

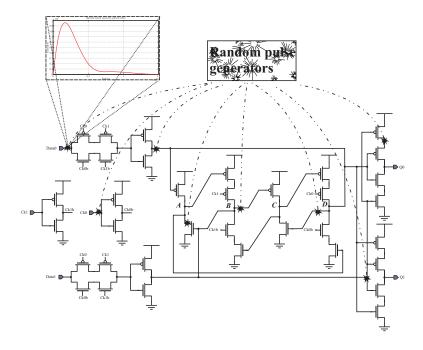

Higher level circuit SEU and SET susceptibility analysis can be achieved by emulating a somewhat more realistic radiation environment. This was achieved by using random pulse generators which inject current pulses with variable amplitudes, on all nodes in the circuits, including inputs. See Figure 5.2. In this thesis the analysis was performed at different supply voltages to evaluate the SEU and SET tolerance of RHBD circuit topologies. The idea behind this approach is to determine if radiation tolerant circuit topologies can make up for the loss in  $Q_{crit}$  as the supply voltage scales down.

Figure 5.2 Simulation method based on random pulse injection

The random pulse injection method was used to determined the soft error rate on the circuitand architecture level [62].

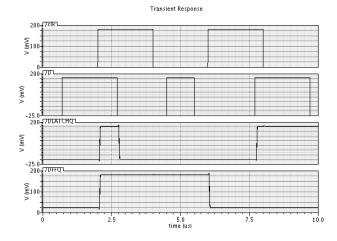

## 5.2 Template-based Soft Error Characterization

The methodology chosen for characterization of soft errors evolves around the comparison of preirradiation data with post-irradiation data. Based on a set of input states, we can predict the expected output from the DUT under normal/ideal operation conditions (pre-radiation). The expected response from the DUT can then be implemented as a template for comparison with the DUT response, when the DUT is being irradiated.

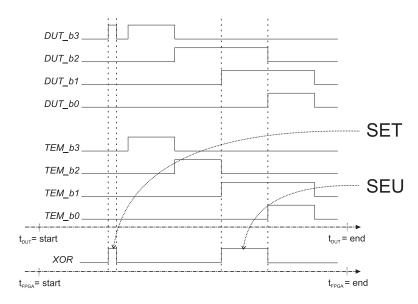

The comparison function is realized using a XOR function, generating '0's for correct response, and '1's for erroneous response. Based on the number of '1's observed, the response, if erroneous, can be characterized as a single event upset or a single event transient. Figure 5.3 shows the principle behind the template-based soft error characterization approach.

**Figure 5.3** Principle behind-template based soft error characterization

Figure 5.3 illustrates a 4 bit DUT response (waves 1,2,3 and 4 from the top) and a 4 bit ideal response template (wave 5, 6, 7 and 8 from the top) which are compared using the XOR function (bottom wave). There are two timelines illustrated, one for the DUT,  $t_{DUT}$ , and one for interface and error detection platform,  $t_{FPGA}$ , which is a FPGA in this case.

The two timelines may or may not be executed simultaneously, depending on the error detection implementation and requirements. For simultaneous execution, four XOR functions are needed for the comparison. In this particular implementation, these to timelines are executed sequentially, thereby only one XOR function is needed. In other words, the DUT timeline is initiated, denoted by  $t_{DUT} = start$ , which signals the DUT to send data to the error detection platform. As soon as all of the data has been sent, indicated by  $t_{DUT} = end$ , the FPGA starts the error detection algorithm indicated by  $t_{FPGA} = start$ . At this point, the comparison between DUT response and template is initiated, sequentially evaluating;  $DUT\_b0 \oplus TEM\_b0$ ,  $DUT\_b1 \oplus TEM\_b1$ ,  $DUT\_b2 \oplus TEM\_b2$  and  $DUT\_b3 \oplus TEM\_b3$ . The sequence completion is indicated by  $t_{FPGA} = end$ , at which point the processed data can be forwarded for further processing.

Figure 5.3 also illustrates a scenario when both a SET and a SEU is detected. A SET is detected during the comparison between  $DUT\_b3$  and  $TEM\_b3$ , and a SEU is detected during the comparison between  $DUT\_b2$  and  $TEM\_b2$ .

## 5.2.1 Soft Error Detection using a FPGA

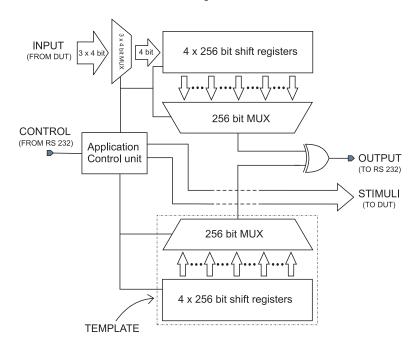

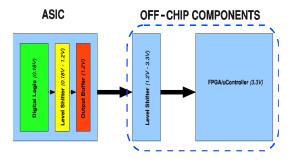

The implementation of the template-based soft error characterization was realized using a FPGA Spartan-3 Starter Board from Digilent. The purpose of the FPGA is to function as a interface between a computer and the DUT by stimulating the DUT and by processing the data received from the irradiated ASIC. Figure 5.4 illustrates a functional diagram of a physical implementation of the template based soft error characterization procedure.

Figure 5.4 Block level diagram of the template based soft error characterization

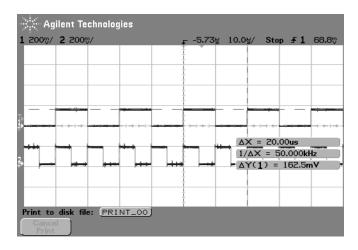

The FPGA is configured to use 8 x 256 shift registers where 4 x 256 shift registers are dedicated to the irradiated received data, and 4 x 256 shift registers are dedicated to the ideal response, ie. the template. The total number of shift registers used for the comparison procedure is 2048 and are realized using the available CLBs on the FPGA. Each shift register on the receiving end is sequentially XORed with their template shift register counterpart. The utilization of a XOR comparison function, enables for detection of any uncorrelated instances between the response and the template. Since the characterization methodology is aimed at characterizing circuit susceptibility at low supply voltages (and therefore low speed), the available processing power on the FPGA allowed for oversampling of the DUT response. The receiving shift registers are oversampled by  $f_s = f \cdot 64$ , ie. 64 times the ASIC output signal frequency. The oversampling approach will therefore provide a certain degree of temporal resolution, and thereby also a certain probability of SET detection. The SET detection is primarily aimed at detecting potential SET occurrences that are results of secondary radiation effects which may interfere with surrounding ICs and equipment. In this particular implementation, the maximum sampling rate is limited by the Spartan 3 maximum clock frequency which is 50 MHz. However, the physical implementation is easily portable to FPGAs capable of sampling at much higher frequencies, such as the Stratix III from Xilinx with the capability to operate at clock frequencies up to 600 MHz. In other words, higher clock frequencies enable higher temporal resolution of the DUT outputs, and thereby higher probability to observe SETs.

A limiting factor regarding this particular approach is the somewhat lack of flexibility. Each template needs to be coded in the FPGA depending on the expected response from the DUT. However, since the FPGA can be reconfigured in a matter of minutes, the existing templates may easily be replaced with new templates, even during radiation testing.

## 5.2.2 PCB Design

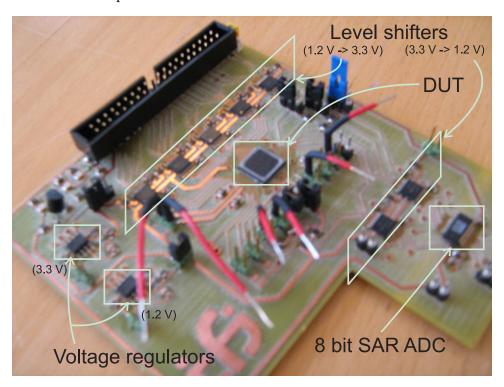

The printed circuit board (PCB) is designed using a two layer FR-4 board. The bottom layer is primarily used as a ground plane for the purpose of ease of routing. The top layer is dedicated to signal- and power routing only. Almost all of the components are placed on the top side, aside from a few decoupling capacitors, which are used for DUT power decoupling and are placed directly below the DUT, on the bottom PCB layer. All ICs have at least one decoupling capacitor in near proximity of the IC package, depending on the requirements. All level shifters are powered by two different supply voltages, and therefore have two decoupling capacitors. The SN740AVC4T774PW level shifters are used both for converting up DUT output voltage signals from 1.2 V to FPGA voltage levels of 3.3 V, and for converting down in the opposite direction. The down-conversion is used for the control signals from the FPGA to the DUT, controlling the SAR architectures. Two level shifters are dedicated to interfacing between an ADS830E 8 bit SAR ADC for the purpose testing of a 8 bit DAC located on the DUT.

Two L6932D1.2 voltage regulators are used for supplying power to the level shifters and the DUT. The voltage regulators are configured in 1.2 V and a 3.3 V configuration, and are powered by two 9 V batteries. A 40-pin connector is placed on the PCB for interfacing with a FPGA development board. Several jumpers have been placed on the PCB for debugging purposes and for different DUT input- and power supply configurations. Figure 5.5 shows the PCB design and indicators to the main components.

**Figure 5.5** The PCB design

The PCB design complexity for this particular experiment is kept relatively low due to the fact that the experiment is run on low speeds. The speed is not limited by the ASIC, but rather by the maximum clock frequency of the FPGA and the oversampling rate, which are given by  $max(f_{FPGA\_clk})$  and X respectively. In order to be able to oversample the output signals of the ASIC, the clock frequency of the FPGA must fulfill the requirement in Eq.5.2

$$f_{FPGA\_clk} = X \cdot f_{ASIC\_output} \tag{5.2}$$

where  $f_{ASIC\_output}$  is the output signal frequency of the ASIC. The maximum signal frequency present on the PCB,  $max(f_{PCB})$ , is thereby given by

$$max(f_{PCB}) = f_{ASIC\_clk} = \frac{max(f_{FPGA\_clk})}{X} \cdot 2$$

(5.3)

since

$$f_{ASIC\ clk} = 2 \cdot f_{ASIC\ output}$$

(5.4)

Given an oversampling rate, X=64, and maximum clock frequency of the FPGA,  $max(f_{FPGA\_clk})=50MHz$ , the highest signal frequency on the PCB would be < 1.5 MHz, which can be categorized as low speed operation. However, it is evident from Eq.5.3 that higher speeds may become relevant if  $max(f_{FPGA\_clk})$  is increased or the oversampling rate, X, is decreased. For such a scenario, more care should be taken when designing the PCB, in order to preserve acceptable signal integrity.

A few measures have been taken in order to prepare the PCB design for radiation testing environment. As a result of high energy particles interacting with materials around the electronic devices, secondary particles may scatter in all directions and thereby have a significant impact other nearby ICs or cables [63]. These secondary particles can induce noise or SEU in sensitive ICs. Therefore, every other wire in the 40-wire ribbon cable is grounded for better crosstalk performance when a long ribbon cable needs to be utilized, and/or when higher speeds are needed. Furthermore, it has been made an effort to keep a distance between the DUT and the surrounding ICs in order to suppress the effect of possible occurrences of secondary particles.

#### 5.2.3 Measurement Setup

The measurement setup used for prototyping and radiation testing is described in this subsection. The setup is used for automated extraction of data from the DUT. Figure 5.6 shows the block diagram of the measurement setup. The setup is based around a host computer that can run the necessary data extractions remotely. A Keithley 6512 Electrometer is configured as an amperemeter for measuring current consumption of the DUT. The amperemeter is used for two purposes; Measuring current consumption of the three SAR architectures, and for measuring the leakage current through the NMOS transistor. Since only one Keithley 6512 is used, only one of these tasks can be performed at any given time. Since, the SAR architectures were to be tested with different supply voltages, the HP/Agilent E3631 voltage source was configured to use two output channels, one for variable power supply for the SAR architectures, and one for gate voltage on the NMOS transistor. The power supply and the amperemeter are connected to a computer using GPIB. The soft error detection algorithm that is implemented on the FPGA development board is controlled by the computer via the RS 232 port. The FPGA development board sends clock, control and reset signals to the DUT and receives the response from specified SAR architectures. The DUT response is evaluated for errors on the FPGA and therafter sent back to the computer via the RS232 port for further processing in Matlab. All cables used for interfacing the DUT PCB are at least 1 meter long in order to minimize any secondary particles hitting the peripheral equipment.

The measurement setup has the capability to plot response data from the DUT continuously in real-time. This ability is preferable in order to be able to observe any irregularities that may occur during the time interval of irradiation testing [64]. Accounting for any irregularities early on during radiation characterisation of a device may help save both time and resources, due to the fact that radiation environments can be highly unpredictable.

According to JEDC89 standards<sup>1</sup>, radiation testing may be performed using static or dynamic

<sup>&</sup>lt;sup>1</sup>http://www4.tsl.uu.se/ bumpen/jedec.pdf

Figure 5.6 Measurement setup

testing of the DUT. Static testing involves writing a predefined sequence to the DUT, followed by irradiation of the device. After the DUT has been irradiated, the radiation sequence is terminated and the DUT response is recorded. For the case of dynamic testing, the DUT is stimulated and the response is recorded during irradiation. The test setup can be modified to perform both dynamic or static testing, however dynamic testing is adequate for testing algorithms such as the SAR architectures. Static testing can be performed in order to observe if bit flips occur in D flip flops, while dynamic testing is preferable in order to test for SET induced SEU while devices are active. Ultimately, both dynamic and static testing should be performed in order to get the best possible SEU characterization of the DUT [65].

# Chapter 6

## Results

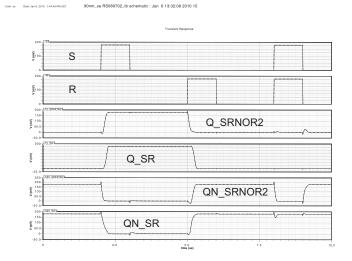

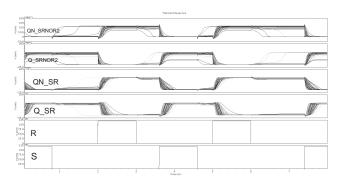

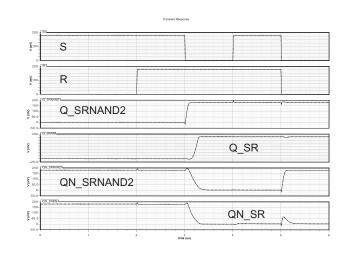

This chapter presents papers related to the field of robust low power CMOS design, as well as results from irradiation testing of the SAR architectures implemented on the TSMC 90 nm chip. The papers are included as potential contributions to future radiation hardened building blocks, and provide individual introductions to their respective topics.

## 6.1 Papers

## 6.1.1 Paper I:

Low-Power Subthreshold to Above Threshold Level Shifter in 90 nm Process

Published at NORCHIP 2009, November 16-17, 2009, Trondheim, Norway

# Low-Power Subthreshold to Above Threshold Level Shifter in 90 nm Process

Amir Hasanbegovic

Department of Informatics

University of Oslo

Email: amirh@ifi.uio.no

Snorre Aunet

Department of Informatics

University of Oslo

Email: sa@ifi.uio.no

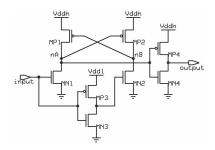

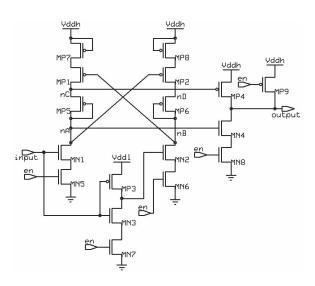

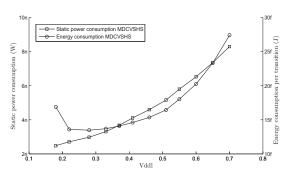

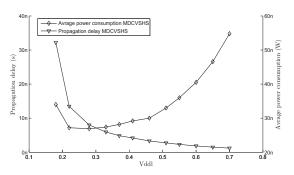

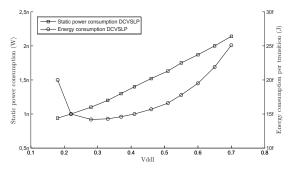

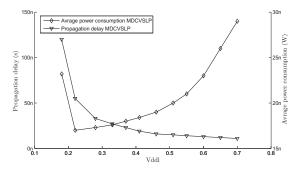

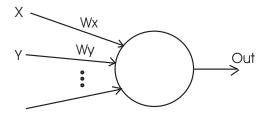

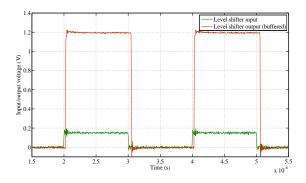

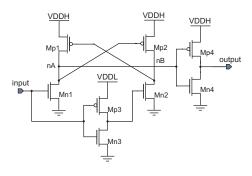

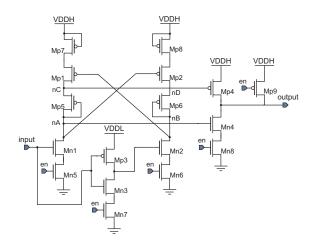

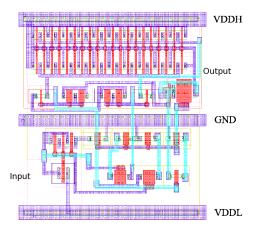

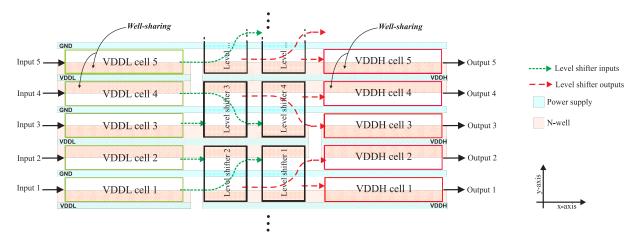

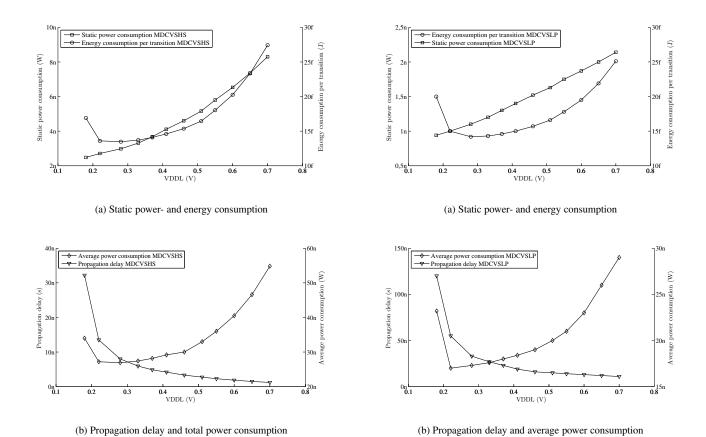

Abstract—The use of multiple voltage domains in an integrated circuit has been widely utilized with the aim of finding a tradeoff between power saving and performance. Level shifters allow for effective interfacing between voltage domains supplied by different voltage levels. In this paper we present a low power level shifters in the 90nm technology node capable of converting subthreshold voltage signals to above threshold voltage signals. The level shifter makes use of MTCMOS design technique which gives more design flexibility, especially in low power systems. Post layout simulations indicate low power consumption and low energy consumption across process-, mismatch- and temperature variations. Minimum input voltage attainable while maintaining robust operation is found to be around 180mV, at maximum frequency of 1MHz. The level shifter employs an enable/disable feature, allowing for power saving when the level shifter is not in use.

#### I. Introduction

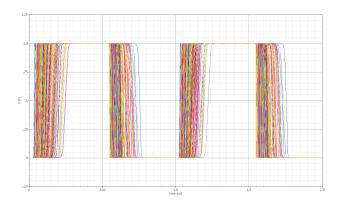

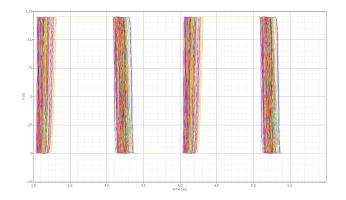

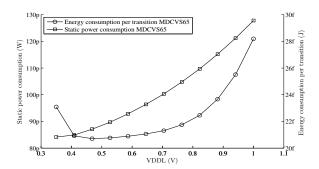

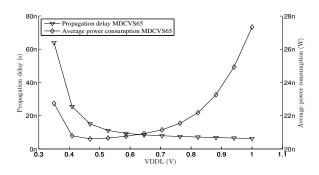

Recently there has been a lot of focus on low power electronics capable of maintaining acceptable performance requirements. One effective way of reducing the power consumption of an integrated circuit (IC) is by reducing its supply voltage. The reduction in supply voltage contributes to dramatic decrease in dynamic and static power consumption, however the utilization of low supply voltage has a negative impact on the speed of the circuit. [1] In order to reduce power consumption while limiting the sacrifice of speed, several voltage domains may be implemented on the same IC. By doing so, less critical sections of the circuit may be supplied by a low supply voltage, Vddl, while critical sections are supplied by higher supply voltages, Vddh. In order to connect the different voltage domains in an effective way, the use of level shifters for interfacing is vital. For the sections of the IC where speed has less importance, the supply voltage may be reduced down to the subthreshold region in order to save as much power as possible. Subthreshold operation has the prospective to contribute with considerable power savings which may benefit modern portable devices.