## Configurable Multiple Value Encoders using Semi Floating-Gate

Dr. Scient thesis

René Jensen

May, 16th 2008

## ACKNOWLEDGMENTS

This thesis has been submitted to the Faculty of Mathematics and Natural Sciences at the University of Oslo as a part of the requirements for a PhD in informatics. The research has been carried out at the Microelectronic Systems Group, Department of Informatics, University of Oslo.

I wish to thank my supervisors Professor Yngvar Berg and Associate Professor Dag T. Wisland for their guidance and encouragement while working on the project. Professor Berg was the one who introduced me to the interesting fields of floating-gate circuits and multiple-valued logic. Both supervisors have given invaluable help in practical as well as in academic terms. Above all though, you have believed in my project and my ability to complete it.

My fellow PhD-students Johannes G. Lomsdalen, Henning Gundersen and Omid Mirmotahari have willingly shared their experiences. Our many long conversations have been valuable and inspiring. I would like to thank all of you for the time we have worked together as colleagues, first at MSc level and later at PhD. It has been a good period of my life both academically and socially.

I would also like to thank the rest of my colleagues in the Department of Informatics who have contributed. In particular Snorre Aunet, Øivind Næss and Mads Høvin.

Finally, I would like to thank everyone else who has helped make this thesis a reality.

Blindern, 16th May 2008

René Jensen

## ABSTRACT

This thesis presents a new multiple-valued encoder with re-configurable radix. The proposed circuits utilize serial cyclic D/A conversion and semi floatinggate (SFG) inverters for compact design and a high functional capacity per device. A re-configurable radix is not supported by existing SFG inverter based multiple-valued encoders which make use of parallel binary weight D/A conversion. The study covers least significant bit-first (LSB), least significant bit-first with alternate bit inversion (LSB ABI) and most significant bit-first (MSB) digital input codes.

The serial cyclic D/A converters with LSB and LSB ABI input codes are implemented in a double-poly 0.35um AMS process. Measured results are provided and analyzed using standard static D/A converter performance measures. Circuits are tested using the practical radices 4, 8 and 16. Experimental results demonstrate that serial cyclic D/A converters using SFG inverters are feasible. Compared to related work on cyclic D/A conversion, the proposed circuits feature both a reduced number of devices and a reduction in the required die area.

Several new techniques are identified for extending the resolution beyond radix 4, 8 and 16 MVL applications. This includes an error correction algorithm called least significant bit-first with alternate bit inversion (LSB ABI), a sample and hold clock scheme and a Dual Data-Rate (DDR) mode of D/A converter operation. The techniques are implemented on a chip and measured results are provided.

The thesis also includes simulation work on several new SFG based circuits. A ternary serial D/A converter, a MSB-first serial D/A converter and a multiple-valued frequency divider which features re-configurable modulus.

## Contents

| A                         | CKN            | NOWLEDGMENT                  | III  |

|---------------------------|----------------|------------------------------|------|

| $\mathbf{A}$              | BST            | RACT                         | IV   |

| $\mathbf{T}_{\mathbf{z}}$ | ABL            | E OF CONTENTS                | VI   |

| $\mathbf{A}$              | CRC            | ONYMS AND ABBREVIATIONS      | XI   |

|                           | Acro           | onyms and abbreviations      | xi   |

|                           | Nota           | ation and nomenclature       | xiii |

| 1                         | INT            | TRODUCTION                   | 1    |

|                           | 1.1            | Objectives                   | 3    |

|                           | 1.2            | Related work                 | 3    |

|                           | 1.3            | Main contributions           | 4    |

|                           | 1.4            | Thesis outline               | 5    |

|                           | 1.5            | Summary of publications      | 6    |

| <b>2</b>                  | SEI            | RIAL D/A CONVERSION          | 9    |

|                           | 2.1            | Introduction                 | 9    |

|                           | 2.2            | LSB-first D/A Conversion     | 10   |

|                           | 2.3            | LSB-first ABI D/A Conversion | 11   |

|                           | 2.4            | MSB-first D/A Conversion     | 13   |

|                           | 2.5            | Summary                      | 14   |

| 3                         | $\mathbf{D}/A$ | A CONVERTER PERFORMANCE      | 15   |

|                           | 3.1            | Introduction                 | 15   |

|               | 3.2  | Ideal D/A Conversion                      | 15 |

|---------------|------|-------------------------------------------|----|

|               | 3.3  | Static D/A Converter performance measures | 16 |

|               | 3.4  | Summary                                   | 20 |

| 4             | SFC  | G SERIAL D/A CONVERSION                   | 21 |

|               | 4.1  | Introduction                              | 21 |

|               | 4.2  | SDR LSB D/A Converter (DAC-1)             | 23 |

|               | 4.3  | SDR LSB ABI D/A Converter (DAC-2)         | 27 |

|               | 4.4  | Improved SDR LSB D/A Converter (DAC-3)    | 31 |

|               | 4.5  | DDR LSB D/A Converter (DAC-4)             | 34 |

|               | 4.6  | MSB D/A Converter (DAC-5)                 | 38 |

|               | 4.7  | Summary                                   | 41 |

| <b>5</b>      | AU   | XILIARY CONVERTER CIRCUITS                | 49 |

|               | 5.1  | Introduction                              | 49 |

|               | 5.2  | SFG S/H Circuits                          | 50 |

|               | 5.3  | N-ary SFG MV FDIV                         | 55 |

|               | 5.4  | Ternary D/A conversion                    | 59 |

|               | 5.5  | Summary                                   | 64 |

| 6             | CO   | NCLUSION                                  | 65 |

|               | 6.1  | Configurable multiple-valued encoders     | 65 |

|               | 6.2  | Optimization techniques                   | 66 |

|               | 6.3  | Concluding remarks                        | 67 |

|               | 6.4  | Further work                              | 67 |

| B             | [BL] | OGRAPHY                                   | 69 |

| LI            | ST   | OF FIGURES                                | 75 |

| $\mathbf{LI}$ | ST   | OF TABLES                                 | 81 |

| 7 | PUBLICATIONS |                                                                                                                       |     |  |  |  |  |  |  |

|---|--------------|-----------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|--|--|

|   | 7.1          | Paper I:<br>Serial Semi Floating Gate MOS D/A Converter With Config-<br>urable Resolution<br>IEEE TENCON 2004         | 85  |  |  |  |  |  |  |

|   | 7.2          | Paper II:<br>Configurable Serial-bit D/A Converter for Multiple Valued<br>Logic<br>IEEE ICSES 2004                    | 91  |  |  |  |  |  |  |

|   | 7.3          | Paper III:<br>Semi Floating-Gate S/H circuits<br>IEEE NORCHIP 2005                                                    | 97  |  |  |  |  |  |  |

|   | 7.4          | Paper IV:<br>Improved Serial SFG MOS D/A Converter with Configurable<br>Resolution<br>IEEE ECS 2005                   | 103 |  |  |  |  |  |  |

|   | 7.5          | Paper V:<br>Dual Data-Rate Cyclic D/A Converter Using Semi Floating-<br>Gate Devices<br>IEEE ISMVL 2007               | 109 |  |  |  |  |  |  |

|   | 7.6          | Paper VI:<br>Configurable MSB-first Serial D/A Converter using Semi Floating<br>Gate Devices<br>IEEE ICSES 2006       |     |  |  |  |  |  |  |

|   | 7.7          | Paper VII:<br>Recharged Comparator and Multiple-Valued<br>N-ary Frequency Divider<br>ULSIWS 2006                      | 123 |  |  |  |  |  |  |

|   | 7.8          | Paper VIII:<br>A Novel Ternary Switching Element Using CMOS Recharge<br>Semi Floating-Gate Devices<br>IEEE ISMVL 2005 | 129 |  |  |  |  |  |  |

### ACRONYMS AND ABBREVIATIONS

- ABI Alternate bit inversion

- A/D Analog-to-digital

- ADC Analog-to-digital converter

- ASIC Application-specific integrated circuits

- ATI Alternate trit inversion

- CFT Clock feedthrough

- CMOS Complementary metal-oxide semiconductor

- DAC Digital-to-analog converter

- D/A Digital-to-analog

- DC Direct current

- DNL Differential non-linearity

- DR Dynamic range

- DDR Dual data-rate

- EDP Energy delay product

- ENOB Effective number of bits resolution

- FDIV Frequency divider

- FG Floating-gate

- FoM Figure of merit

- GPIB General purpose interface bus

- INL Integral non-linearity

- LSB Least significant bit

- LST Least significant trit

- MOS Metal-oxide semiconductor

- MSB Most significant bit

- MST Most significant trit

- MVL Multiple valued logic

- MV Multiple valued

- NMOS N-channel metal oxide semi-conductor

- NOB Number of bits

- OTA Operational transconductance amplifier

- PDP Power delay product

- PMOS P-channel metal-oxide semi-conductor

- PSRR Power supply rejection ratio

- SC Switched capacitor

- SDR Single data-rate

- SFG Semi floating-gate

- S/H Sample-and-hold

| SNDR | Signal-to-noise-and-distortion ratio |

|------|--------------------------------------|

| T/H  | Track-and-hold                       |

| ULSI | Ultra-high large-scale integration   |

| VLSI | Very high large-scale integration    |

| VM   | Voltage mode                         |

### NOTATION AND NOMENCLATURE

Throughout the thesis, the multiple valued output voltages of serial D/A converters are denoted  $Y_n$ . Converters use bit-serial digital input codes. Each code or input word consists of n bit and is denoted B. The *i*-th bit of a code is referred to as  $b_i$ . In this thesis converters perform a bit-wise conversion of the codes, one bit per iteration. The intermediate multiple valued output voltages are denoted  $Y_i$ .

- B Digital input word

- $b_i$  i-th bit of a bit-serial input code

- $D_i$  Deviation

- $f_b$  Bit-rate

- $f_N$  Nyquist frequency,  $f_N = f_{s/2}$

- $f_s$  Sampling or update frequency

- $f_S$  Symbol-rate

- n Number of bits resolution

- R Radix,  $R = 2^n$

- $Y_i$  Intermediate analog output voltage after the *i*-th bit

- $Y_n$  Analog output voltage with n bit resolution

- $\Phi$  Recharge clock/Bit clock

- $\Psi$  Reset clock/Output symbol or multiple value clock

- $V^-$  Lower end of voltage swing

- $V^+$  Upper end of voltage swing

- $V_{LSB}$  Least significant bit voltage/Smallest voltage step

## Chapter 1

## INTRODUCTION

Digital computing has reached widespread use and digital (binary) logic circuits dominate the computer industry. The digital technological revolution is binary. Modern microelectronic fabrication processes and design tools are tailored to meet the demands of digital (binary) circuits.

The concept of how to represent information and information theory has deep roots. Already in 1948 Shannon introduced the idea of information entropy [1]. Intuitively it relates to the uncertainty about an event associated with a probability distribution. According to Shannon, binary signals have a very low entropy and are less efficient than alternate multiple-valued representations. However, a low entropy is often the most robust representation. For instance, digital (binary) VLSI circuits implement binary logic and have the best noise-margins.

In [2], Multiple-Valued Logic (MVL) is proposed as a possible alternative to the digital paradigm. MVL is an alternative with more than two logical values and a higher information entropy. In 1920 Lukasiewicz developed multiple-valued logic of more than two logical truth values. At the same time the American mathematician Emil Post introduced his many valued Post algebra. Post algebra is applicable for optimization of MVL. The MVL research community has its own IEEE organized conference called the "International Symposium of Multiple Valued Logic" (ISMVL). It has been held on an annual basis since 1971. In [3] Etiemble argues strongly that multiplevalued logic is restricted to a small niche. The feasibility of new paradigm MVL depends on the availability of devices constructed for MVL operations [4]. These devices are often associated with a higher functional capacity.

In todays binary world, radix converters have become an immediate concern [5]. Several radix converters are proposed. This includes LUT-cascades [6], arithmetic decompositions [7], iterated function systems [8] and linear coded weights [9]. Radix conversion is described as a complex task. The proposals

are modular but do not necessarily support runtime re-configuration of the radix. The most efficient binary to multiple-valued radix conversion utilizes radices corresponding to an integer number of bit resolution. This also allows implementation using a binary weighted digital to analog converter [10].

Practical radix converter implementations normally assume bit-parallel transmission of digital (binary) input. This means that the number of interconnections and number of bit resolution are fixed. A change in radix therefore requires a redesign of the circuit.

In many applications the cost of interconnection and synchronization makes bit-parallel transmission impractical. Interconnections are a limited resource in modern VLSI, in particular inter-chip connections. A common solution is the use of time multiplexed systems where digital data is communicated serially. In applications where digital input is transmitted serially, a single interconnect can be sufficient. Radix conversion by use of inherently parallel algorithms requires an initial serial to parallel conversion. This solution becomes a problem as it requires considerable chip area. Serial buses are becoming more common. This motivates the development of alternate serial D/A converters. A serial D/A converter is simple and cheap to implement.

Industrial use of floating-gate [11] has long traditions from initial use as EEPROM memories to portable flash memories. Today, FGMOS devices have reached applications [12] beyond memory technology. One example is semi floating-gate (SFG) devices – volatile floating-gate inverters recharged periodically by a recharge clock signal. In this thesis semi floating-gate (SFG) inverters, volatile floating-gate inverters recharged periodically by a recharge clock signal, are utilized for multiple-valued logic purposes. Another example is Field Programmable Gate Arrays (FPGA). Some FPGA implementations exploit floating-gates to create and break connections. Adaptive and reconfigurable circuits are known to reduce the time to market as well as increase the life span of circuits. The importance of configurable floating-gate circuits is emphasized by Aunet *et al.* in [13][14] and by Kelly *et al.* in [15].

This thesis will present the development of configurable serial D/A converters using semi floating-gate (SFG) devices. It introduces flexible/adaptive algorithms with runtime reconfigurable radix. The converters proposed are compact alternatives to traditional radix converters based on parallel binary weight D/A conversion algorithms[16][17][18].

### 1.1 Objectives

The most important aims of this PhD thesis are:

- To develop new and more compact radix converters based on the proposed semi floating-gate based configurable serial D/A converter.

- To bring additional knowledge into the field of volatile floating-gate design and multiple-valued logic by working with problems related to reconfigurable iterative algorithms. In particular the utilization of the semi floatinggate latch and the semi floating-gate inverter devices when using a nonoverlapping two-phase clocking strategy.

- To demonstrate through physical implementations, that semi floating-gate devices can be used in a practical serial D/A conversion application.

- To characterize the linearity of the introduced converters and the associated effective radix using static D/A converter performance measures.

- To improve the effective radix of the SFG serial D/A converter using an error correction scheme referred to as alternate bit inversion (ABI).

- To develop a compact SFG MV frequency divider featuring asymmetrical output clock signal and reconfigurable modulus. The circuit is auxiliary to the D/A converter but applicable as bit-counter and reset signal generator.

- To improve the accuracy and conversion speed of semi floating-gate based memories (SFG Latch) by proposing new and alternate SFG S/H circuits. A physical implementation will demonstrate the concept.

### 1.2 Related work

The work in this thesis is possible thanks to the development of Semi Floating-Gate (SFG) Latches [19] by Mirmotahari *et al.* and SFG inverters [20] introduced by Berg *et al.* SFG inverters are recharged volatile floating-gate inverters exploiting multiple-input multiple-valued floating-gate transistors [21]. Multiple-valued encoders using SFG devices are presented in [17] and [16]. However these converters use a parallel binary weight D/A converter algorithm where binary weights and radix are design parameters. Also relevant for this thesis is clock-controlled neuron-MOS logic gates [22]. Further background on neuron-MOS circuits is given in [23] and [24] by Shibata and Ohmi.

Several modular radix converters for MVL exist. Recent advances in the field include converters using LUT-cascades [6], arithmetic decompositions [7], iterated function systems [8] and linear-coded weights [9][25]. Radix conversion is a complex task and converters tend to be larger circuits. In [26][27] a simple serial D/A converter with configurable radix is introduced. The circuit is passive and utilizes switched-capacitor techniques for reduced circuit complexity.

Advances have been made on active switched-capacitor D/A converters using operational transconductance amplifiers (OTA) and standard serial digital input codes. The simplest converters are cyclic D/A converters, also referred to as algorithmic or iterative. In [28] an active LSB-first serial D/A converter is presented. [29] introduces a different solution with support for MSB-first digital input codes. Several practical cyclic D/A converter implementations have been reported [26, 29, 30, 31, 32, 33, 34, 35]. Further references to algorithmic D/A conversion are also found in [36], [37] or [30].

### **1.3** Main contributions

This thesis presents research on configurable multiple-valued encoders using semi floating-gate devices. The main contributions are:

## New circuits for configurable serial D/A conversion using semi floating-gate devices

The most important part of this thesis is the introduction of several new serial D/A converters using semi floating-gate (SFG) inverters. This includes support of the two main standard bit-serial digital input codes; the least significant bit (LSB) first and the most significant bit (MSB) first. In addition a least significant bit first converter using alternate bit inversion (LSB ABI) is introduced.

## Error cancellation in semi floating-gate based serial D/A conversion by use of LSB ABI codes

Bit-weight errors in serial D/A converters using SFG devices are significantly reduced by introducing a LSB ABI mode of operation. This provides higher accuracy, increased effective radix or improved INL/DNL measures. The negative gain of SFG inverters is exploited for negative feedback in the converter. In each cycle the error of the previous iteration is subtracted due to the negative feedback. The successive generation of binary weights is preserved by introducing alternate bit inversion (ABI) input codes. The effectiveness of the algorithm is demonstrated by simulations in Cadence Spectre and by implementation on a chip. Analog SFG devices have non-linear gain and propagate level-noise. This makes the introduction of an error cancellation scheme in cyclic algorithms particularly important.

## Implementation and analysis of converter linearity in LSB and LSB ABI serial D/A converters using semi floating-gate devices

The proposed SFG serial D/A converters using LSB or LSB ABI digital input codes were selected for implementation in CMOS. The multiple-valued output voltage levels are extracted from the measurements and analyzed in Matlab using standard D/A converter performance measures.

## The use of difference equations to model serial $\mathbf{D}/\mathbf{A}$ converter operation

The serial D/A converter algorithms are mathematically equivalent to the traditional parallel binary weight D/A converter. A set of difference equations modeling the converter operation is derived.

#### Increased speed in semi floating-gate circuits by use of Dual Data-Rate (DDR) operation

The speed of serial D/A conversion using semi floating-gate is significantly improved using DDR mode of operation. It is demonstrated that the maximum bit-rates are doubled using the proposed mode of operation. A traditional SDR SFG performs only one operation per recharge clock cycle. The proposed DDR mode of operation allows latching twice per recharge clock cycle, one on each of the clock edges.

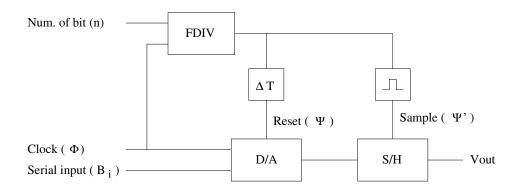

#### A configurable serial D/A converter architecture

A complete architecture for configurable serial D/A conversion is provided. This includes a SFG MV FDIV for generation of the external reset clock signal, a SFG S/H read-out circuit, a modular level restoration circuit for removal of level-noise in multiple-valued input signals and serial D/A converter cores. Practical implementations are provided for all components except the SFG MV FDIV.

### 1.4 Thesis outline

Chapter 2 presents the fundamentals of cyclic D/A conversion. Simple difference equations modeling the operation are derived from the well-known algorithm for parallel binary weighted D/A conversion.

In chapter 3 the fundamentals of D/A conversion and static D/A converter performance measures are presented. This founds the basis of later linear analysis in chapter 4.

D/A converter circuits using SFG devices are proposed in chapter 4. An analysis and discussion of performance in terms of linearity and compact design is given. The main focus is on LSB and LSB ABI digital input codes. Measured results on practical chip implementations are provided for three converter candidates using LSB codes and one LSB ABI based converter

candidate. A comparison with related work on cyclic D/A conversion is given. The fifth D/A converter using MSB-first digital input codes is evaluated using simulation results from Cadence Spectre.

Circuits auxiliary to the D/A converter core are presented in chapter 5. This includes a SFG S/H Read-out circuit, a SFG MV FDIV with configurable radix and a SFG Ternary refresh circuit. Measured results on a chip implementation of the SFG S/H Read-in and Read-out circuits are provided. Additional measured chip results for the ternary switching element (Paper VIII) are provided.

Chapter 6 summarizes this thesis and gives proposals for further work.

Eight publications [38, 39, 40, 41, 42, 43, 44, 45] are selected for presentation in this thesis and are attached in chapter 7 as **[Papers I-VIII]**. All eight publications have been accepted and presented at international conferences with peer review. The articles are published in conference proceedings. These papers have been created and written as part of this Ph.D. thesis.

### 1.5 Summary of publications

In [38] [Paper I] configurable serial D/A conversion using SFG devices is introduced. It is shown how the ideal serial D/A converter model is mathematically equivalent to the well-known parallel binary weight D/A converter algorithm. A practical implementation using SFG devices requires sufficient accuracy in the SFG based adder and memory. A simple serial D/A converter using semi floating-gate devices is implemented on a 0.35um AMS chip. Cadence Spectre is used for tuning of parameters and preliminary simulation results. This paper focuses on the feasibility of configurable serial D/A conversion using SFG devices. The importance of accurate and linear SFG device operation is emphasized. In particular that of the included SFG Latch. The paper presents simulation results demonstrating sufficient accuracy of SFG devices to solve the serial D/A converter difference equation. Additional chip measured results are provided in this thesis in chapter 4.2. The converter supports standard least significant bit (LSB) first digital input codes. The proposed D/A converter is referred to as DAC-1.

Based on the experience from DAC-1, several techniques for increasing the effective radix are introduced. The effective radix or linearity is discussed and studied using standard static D/A converter performance measures.

[39][**Paper II**] introduces a LSB alternate bit inversion (LSB ABI) error cancellation scheme for increased converter accuracy and effective radix. In each cycle the error of the previous iteration is subtracted due to the negative feedback. The successive generation of binary weights is preserved by

introducing alternate bit inversion (ABI) input codes. This allows the effect of symmetrical non-linear gain error in the SFG inverter transfer function to be compensated. The new peak error could be within one LSB for multiplevalued radices 2, 3 and 4. The proposed LSB ABI serial D/A converter is implemented on a chip and simulation results from Cadence Spectre are discussed and analyzed. Additional chip measured results are provided in chapter 4.3 of this thesis. The converter supports LSB ABI digital input codes and is referred to as DAC-2.

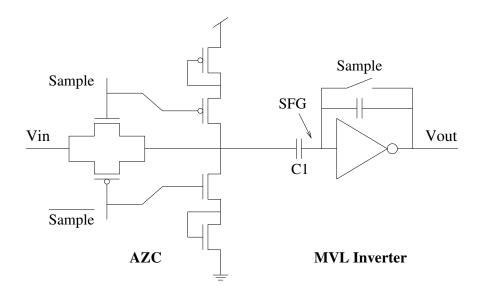

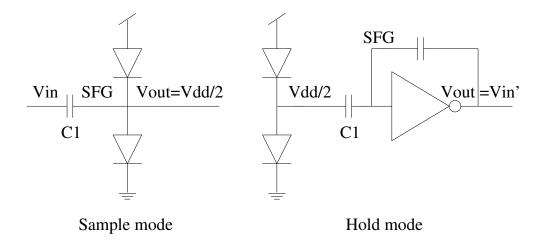

[40] **[Paper III]** addresses problems associated with the existing SFG Latch based memory. Three practical converter applications are discussed; utilization as internal memory, as read-in circuit and as read-out circuit. Improved SFG S/H Read-in and Read-out circuits are introduced. A practical implementation on a chip demonstrates the concept. The linearity of the SFG S/H circuits is discussed and studied.

By integrating the SFG S/H memory proposed in [40][**Paper III**] into DAC-1 proposed in [38][**Paper I**], new converters with both improved linearity and reduced device count are made possible.

In [41] **[Paper IV]** a new configurable serial D/A converter using SFG devices is introduced. This concept exploits SFG S/H circuits for improved linearity and reduced device count. It is referred to as DAC-3. A practical chip implementation is performed and chip measured results are provided.

[42][Paper V] addresses the troubling slow speed associated with all cyclic serial D/A converters. A new mode of operation referred to as Dual Data-Rate (DDR) is introduced. It allows a doubling of the conversion rate by utilizing both clock edges. The new mode of operation exploits SFG S/H circuits for improved linearity and reduced device count. In this paper a new configurable serial D/A converter referred to as DAC-4 is introduced. The converter implements DDR DAC operation. A practical implementation on a chip and chip measured results are provided. The results are discussed and studied in terms of converter linearity.

[43][**Paper VI**] presents a new serial D/A converter with support for standard MSB-first digital input codes. This alternative uses SFG devices and supports runtime reconfiguration of its radix. The converter is referred to as DAC-5.

In [44] **[Paper VII]** an N-ary multiple-valued Frequency Divider (MV FDIV) using SFG devices is introduced. The proposal is applicable as a configurable bit counter in cyclic D/A converters. Simulation results demonstrate usage as reset clock signal generator in a SFG serial D/A converter. The MV FDIV circuit is compared with a digital bit-counter in terms of device count and functionality.

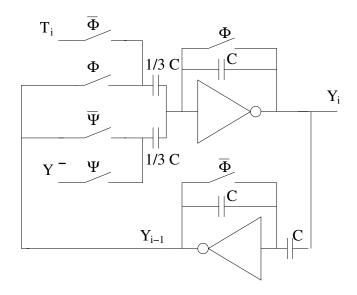

[45] [Paper VIII] proposes a ternary switching element using SFG devices.

A practical implementation on a chip is done and simulation results are discussed. Additional chip measured results are provided in chapter 5.4 of this thesis.

### Chapter 2

# SERIAL D/A CONVERSION

In this chapter mathematical models for discussion of [38, 39, 41, 42, 43] [Papers I, II, IV, V and VI] are presented.

### 2.1 Introduction

In this thesis semi floating-gate devices for binary to multiple-valued conversion are introduced. A focus on compact and configurable SFG MVL devices motivates the use of cyclic D/A conversion algorithms. The proposed LSB-First SFG cyclic D/A converter allows on-chip conversion in a standard CMOS process.

In modern computers the digital (binary) number system is a base two system. The digits of this binary number system are referred to as bit and each position is associated with a binary weight, a power of two. D/A conversion is a multiplication problem in which the product of bits and their weights are added. An illustration is given in table 2.1 where weights (W), binary number (B) and normalized weights  $(W/2^n)$  are included. It is common to denote the leftmost bit with the highest weight as the most significant bit (MSB). The rightmost bit of the lowest weight is the least significant bit (LSB).

| B       | $\  b_n$  |  | $b_i$          | <br>$b_2$        | $b_1$    |

|---------|-----------|--|----------------|------------------|----------|

| W       | $2^{n-1}$ |  | $2^{i-1}$      | <br>$2^{1}$      | $2^{0}$  |

| $W/2^n$ | $2^{-1}$  |  | $2^{-(n+1-i)}$ | <br>$2^{-(n-1)}$ | $2^{-n}$ |

Table 2.1: The binary number system and its binary weights. Calculating the decimal values of a binary number is equal to a multiplication problem.

A good overview of D/A converter architectures which focus on bit-serial and cyclic D/A conversion was given by J.W. Bruce in [46]. A bit-serial D/A converter is characterized by its bit-wise conversion of a digital input. Serial D/A converters are in general constructed with much simpler circuits than their bit-parallel counterparts. However, the speed of the serial D/A converter algorithm decreases linearly with the number of bit resolution. It is therefore associated with moderate speed at low resolutions (2-4 bit) and slow speed at high resolutions (10 or more bit). In a N bit cyclic D/A converter the result of each bit conversion is added to the result of the previous bits converted. After all N bit are clocked in, the accumulated result is at the analog output. It can easily be stored using a sample and hold circuit [47]. Because of their iterative nature the cyclic D/A converters are not only extremely compact, but also support a range of resolutions. D/A conversion is defined as a process of transforming a binary number B into an analog value Y given by

$$Y_n = \sum_{i=1}^n 2^{-i} b_i , \qquad (2.1)$$

where the digital input B is the ordered set of bit  $(b_1, b_2, \ldots, b_n)$ . A cyclic D/A converter solves this process by using a first order difference equation generating the same sum. Traditional and better known bit-parallel binary weighted D/A converters solves it in one big parallel computation. It therefore outperforms bit-serial or cyclic D/A converters in speed, but provides only a fixed resolution. The design is however modular.

Three types of converters are covered. The LSB-First (LSB), LSB-First with Alternate Bit Inversion (LSB ABI) and the MSB-First cyclic D/A converter. These converter algorithms will be referred to as LSB, LSB ABI and MSB type respectively.

### 2.2 LSB-first D/A Conversion

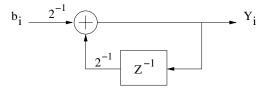

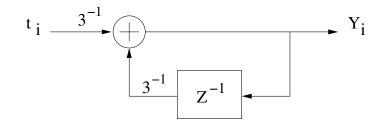

Figure 2.1: Typical signal flow digram of LSB first type cyclic D/A converters.

The LSB-First type cyclic D/A converter operation is modeled by the first

order linear difference equation

$$Y_i = \frac{1}{2} \left( Y_{i-1} + b_i \right) \tag{2.2}$$

with initial condition  $Y_0 = 0$  and n iterations i = 1, ..., n. One iteration for each bit resolution. The input is ordered with the least significant bit (LSB)  $b_1$  first, and the most significant bit (MSB)  $b_n$  last. This gives input codes of the form

$$B = (b_1, b_2, \dots, b_i, \dots, b_n) .$$

(2.3)

After all n bits are clocked into the converter, the corresponding analog value

$$Y_n = \sum_{i=1}^n 2^{-i} b_i \tag{2.4}$$

results at the output. Equation 2.4 shows that a n-bit LSB-first digital code is converted into an analog value  $Y_n$  in the range from 0 to 1. In figure 2.1 a signal flow diagram of the LSB first type cyclic D/A converter is shown.

### 2.3 LSB-first ABI D/A Conversion

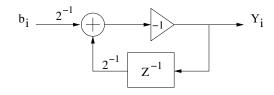

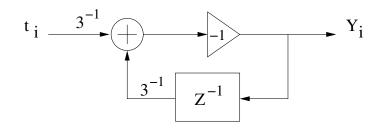

Figure 2.2: Typical signal flow diagram of LSB ABI type cyclic D/A converters.

A LSB-First Alternate Bit Inversion type cyclic D/A converter is a special case of the standard LSB-First type D/A converter. Alternate bit inversion (ABI) of intermediate analog values and digital input codes is utilized. This means that the intermediate analog voltage  $Y_i$  is inverted once per iteration. The inversion process works as a negative feedback subtracting non-linear errors of the previous iteration. A signal flow diagram of the LSB first type cyclic D/A converter is shown in figure 2.2. The algorithm will be referred to as LSB ABI conversion and is modeled by the equation

$$Y_{i} = 1 - \frac{1}{2} \left[ Y_{i-1} + b'_{i} \right]$$

(2.5)

where  $Y_0 = 0$  and n an integer  $n \ge 2$ . The index i takes the values i = 1, ..., n. A LSB ABI converter differs from a LSB converter by utilizing

alternate inversion of the binary input. When converting from a LSB to a LSB ABI code (B'), every second bit is inverted. If the length of the digital input code is an odd number, the inversion starts with the first bit. Otherwise inversion starts at the second bit.

$$B' = (b'_1, b'_2, \dots, b'_n) = (\overline{b_1}, \overline{b_2}, \overline{b_3}, \dots, \overline{b_n}), \quad n = odd$$

$$= (b_1, \overline{b_2}, b_3, \dots, \overline{b_n}), \quad n = even$$

(2.6)

The LSB ABI converter is particularly interesting in a SFG inverter implementation context. A SFG inverter is an analog device which propagates noise. It also has finite gain and parasitic effects which result in an error being added in each iteration. The LSB ABI conversion algorithm has the ability to reduce the effect of SFG inverter computation errors and improve overall linearity. After all n bits are clocked into the converter, the corresponding analog value

$$Y_n = \sum_{i=1}^n 2^{-i} b_i, \qquad n = even$$

=  $2^{-n} + \sum_{i=1}^n 2^{-i} b_i, \quad n = odd$  (2.7)

has been generated. It was mentioned earlier that SFG inverters propagate noise. The devices are inherently analog and not level restoring. In the LSB-First cyclic D/A algorithm each iteration includes a divide-by-two of the previous intermediate result. This reduces the amount of level-noise or level-error propagated by a factor of 1/2 and is often said to assure that the error lies within the least significant bit. Further, it is assumed that the error contributed or generated by SFG inverter computations is symmetrical around  $V_{dd}/2$  and is of opposite signs. By using a LSB ABI algorithm the intermediate result tends to shift between the two regions of operation. The sign of the error contribution shifts with it. An error cancellation effect occurs. All-zero or all-ones codes benefit the most from this technique.

The overall conversion error when using LSB converters and analog SFG inverters can be estimated as

$$E = \sum_{i=1}^{n} 2^{-(i-1)} e_i \tag{2.8}$$

Here,  $e_i$  denotes the error contributed by the *i*-th iteration. A LSB ABI algorithm is proposed, where the error of each iteration is subtracted in the next iteration. This reduces the accumulated error to

$$E = \sum_{i=1}^{n} (-1)^{(n+i+1)} 2^{-(i-1)} e_i$$

(2.9)

#### 2.4 MSB-first D/A Conversion

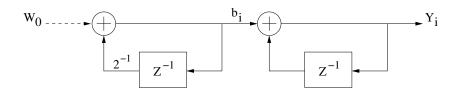

Figure 2.3: Typical signal flow diagram of MSB-First type cyclic D/A converters.

In the MSB-First type cyclic D/A converter each iteration can be expressed as

$$Y_i = Y_{i-1} + 2^{n+1-i}b_{n+1-i} (2.10)$$

where  $Y_0 = 0$  and *n* iterations i = 1, ..., n. The converter reads bit-serial codes

$$B = (b_n, b_{n-1}, \dots, b_{n+1-i}, \dots, b_1) , \qquad (2.11)$$

ordered from MSB to LSB. The converter can easily be implemented using an accumulator and a divide-by-two counter. The accumulator provides memory between each iteration and the counter generates the binary weights. The digital input determines which weights are added to the intermediate result. After all n bits are clocked in, the analog value

$$Y_n = \sum_{i=1}^n 2^{n+1-i} b_{n+1-i} \tag{2.12}$$

is at the output. A weakness of this construction is that the most significant bit is read first in time. It is read and stored from analog memory n-1 times. This is n-1 times more than when using the LSB and LSB ABI algorithms presented earlier. This allows for a much higher error contribution in physical implementation. Although expected to be less accurate than a LSB-first converter, it is included for completeness and comparison. In figure 2.3 a typical signal flow diagram of the MSB-First type cyclic D/A converter is included.

It can be shown that the MSB, LSB and LSB ABI type converters all express the same normalized values. One exception is the LSB ABI type converter configured with an odd number of bit resolution. Its analog output is offset by  $2^{-n}$  as indicated earlier. The converters span

$$Y_{range} = (Y_{max} - Y_{min}) = \frac{2^n - 1}{2^n}$$

(2.13)

portions of the full scale. The cyclic D/A converter algorithms can also be derived from the well-known and popular parallel binary weight D/A converter algorithm in equation 2.14.

$$Y_{n} = \sum_{i=1}^{n} 2^{-i} b_{n+1-i}$$

=  $2^{-1} b_{n} + 2^{-2} b_{n-1} + \dots + 2^{-i} b_{n+1-i} + \dots + 2^{-n} b_{1}$

=  $2^{-n} (2^{n-1} b_{n} + \dots + 2^{i-1} b_{i} + \dots + 2^{0} b_{1})$  (2.14)

An alternative converter algorithm for MSB-first D/A conversion exists. By exploiting a multiply-by-two feedback the conversion process can be made less complex. However multiply-by-two calculations were considered less practical in a SFG context.

#### 2.5 Summary

Fundamental background on configurable serial D/A converter algorithms has been presented. This includes signal flow diagram, difference equations and digital codes for least significant bit (LSB) first, least significant bit first with alternate bit inversion (LSB ABI) and most significant bit (MSB) first conversion.

For further background on serial D/A conversion readers are referred to [46]. The popular D/A converter textbooks include little or no information on cyclic D/A conversion in their surveys on D/A converter architectures [48] [49] [50] [51]. [52] by P. E. Allen covers switched-capacitor circuits and mentions cyclic D/A conversion. The article [53] covers various converter architectures and includes discussion of parameters, limitations and applications for serial cyclic D/A conversion. A brief description is also included in a textbook on CMOS circuits by Jacob Baker [54]. However, [54] covers only cyclic D/A converters using LSB-First bit-serial codes. In [55] professor A. Baschirotto gives a lecture on data converters and interfacing. The talk gives a good introduction to both cyclic MSB-first and LSB-first D/A converters. In [55] cyclic D/A conversion is referred to as serial D/A conversion, a process which generates the analog voltage serially bit by bit. The algorithms are grouped into active multiplication by two, passive multiplication by two and active division by two. Operational transconductance amplifiers are utilized as active component. Cyclic D/A conversion is also referred to as algorithmic D/A conversion. Original work on cyclic D/A converters are presented in [28], [29], [36], [35] and [32].

## Chapter 3

# D/A CONVERTER PERFORMANCE

In this chapter background information on notation and methods for analysis of SFG serial D/A converters is introduced. The material presented forms the basis of later performance characterization for practical implementations in chapter 4.

### 3.1 Introduction

This thesis introduces new D/A converter circuits utilizing compact analog SFG devices. The ideal operation is described using linear first order difference equations. Linear analog SFG based memory and SFG device transfer functions become a main concern. These non-linearities are analyzed using standard static D/A converter performance measures. SFG devices are compact circuits with a high functional capacity per device. However, the devices are analog and provide no form of level correction. Digital (binary) logic suppress level-noise and provide noise margins. A SFG device is inherently analog. In addition to propagating level-noise, the non-linear transfer functions and mismatch errors degrade performance of converters using SFG devices. This makes quantification of static distortion using standard metrics important.

### **3.2** Ideal D/A Conversion

In MVL applications using semi floating gate (SFG) inverters, we are primarily interested in encoding multiple valued signals of radix 4, 8 and 16. This means between two and four bit D/A converter resolution. In tables 3.1, 3.2

and 3.3 examples of LSB, MSB and LSB ABI codes of these resolutions are given as a summary of the three converter types presented.

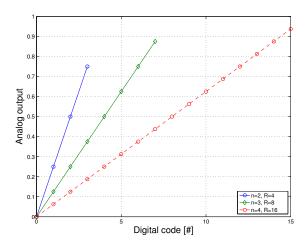

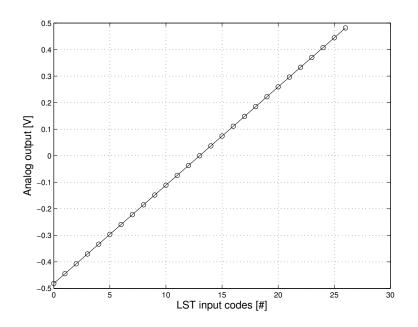

The cyclic D/A converter algorithms are visualized by combining the digital test data from the three tables below and the LSB, LSB ABI and MSB algorithms in equations 2.4, 2.7 and 2.12. The resulting analog values are shown in figure 3.1. Both cyclic D/A algorithms and bit-parallel D/A converter algorithms presented map to the same points. The exception is the LSB ABI type converter with odd number of bit resolution. Its analog value is offset by  $2^{-n}$  when in this configuration. A positive offset of 1/8 when using the three bit codes corresponds to the unused portion of the output range.

| MV  | М     | SB    | L           | SB | LSB ABI |                  |  |

|-----|-------|-------|-------------|----|---------|------------------|--|

| R=4 | $b_2$ | $b_1$ | $b_1$ $b_2$ |    | $b_1$   | $\overline{b_2}$ |  |

| 0   | 0     | 0     | 0           | 0  | 0       | 1                |  |

| 1   | 0     | 1     | 1           | 0  | 1       | 1                |  |

| 2   | 1     | 0     | 0           | 1  | 0       | 0                |  |

| 3   | 1     | 1     | 1           | 1  | 1       | 0                |  |

Table 3.1: LSB, LSB ABI and MSB digital input codes for radix four.

| MV  |       | MSF   | 3     |       | LSB   | 5     | LSB ABI          |       |                  |  |

|-----|-------|-------|-------|-------|-------|-------|------------------|-------|------------------|--|

| R=8 | $b_3$ | $b_2$ | $b_1$ | $b_1$ | $b_2$ | $b_3$ | $\overline{b_1}$ | $b_2$ | $\overline{b_3}$ |  |

| 0   | 0     | 0     | 0     | 0     | 0     | 0     | 1                | 0     | 1                |  |

| 1   | 0     | 0     | 1     | 1     | 0     | 0     | 0                | 0     | 1                |  |

| 2   | 0     | 1     | 0     | 0     | 1     | 0     | 1                | 1     | 1                |  |

| 3   | 0     | 1     | 1     | 1     | 1     | 0     | 0                | 1     | 1                |  |

| 4   | 1     | 0     | 0     | 0     | 0     | 1     | 1                | 0     | 0                |  |

| 5   | 1     | 0     | 1     | 1     | 0     | 1     | 0                | 0     | 0                |  |

| 6   | 1     | 1     | 0     | 0     | 1     | 1     | 1                | 1     | 0                |  |

| 7   | 1     | 1     | 1     | 1     | 1     | 1     | 0                | 1     | 0                |  |

Table 3.2: LSB, LSB ABI and MSB digital input codes for radix eight.

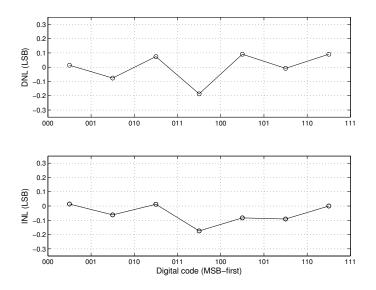

### 3.3 Static D/A Converter performance measures

In this work low frequency MVL encoders are our main interest. INL and DNL are expected to give a good indication of the converter performance. This assumes operation within the limits of the building blocks. In SFG

| MV   |       | М     | SB    |       | LSB   |       |       |       | LSB ABI |                  |       |                  |

|------|-------|-------|-------|-------|-------|-------|-------|-------|---------|------------------|-------|------------------|

| R=16 | $b_4$ | $b_3$ | $b_2$ | $b_1$ | $b_1$ | $b_2$ | $b_3$ | $b_4$ | $b_1$   | $\overline{b_2}$ | $b_3$ | $\overline{b_4}$ |

| 0    | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0       | 1                | 0     | 1                |

| 1    | 0     | 0     | 0     | 1     | 1     | 0     | 0     | 0     | 1       | 1                | 0     | 1                |

| 2    | 0     | 0     | 1     | 0     | 0     | 1     | 0     | 0     | 0       | 0                | 0     | 1                |

| 3    | 0     | 0     | 1     | 1     | 1     | 1     | 0     | 0     | 1       | 0                | 0     | 1                |

| 4    | 0     | 1     | 0     | 0     | 0     | 0     | 1     | 0     | 0       | 1                | 1     | 1                |

| 5    | 0     | 1     | 0     | 1     | 1     | 0     | 1     | 0     | 1       | 1                | 1     | 1                |

| 6    | 0     | 1     | 1     | 0     | 0     | 1     | 1     | 0     | 0       | 0                | 1     | 1                |

| 7    | 0     | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 1       | 0                | 1     | 1                |

| 8    | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0       | 1                | 0     | 0                |

| 9    | 1     | 0     | 0     | 1     | 1     | 0     | 0     | 1     | 1       | 1                | 0     | 0                |

| 10   | 1     | 0     | 1     | 0     | 0     | 1     | 0     | 1     | 0       | 0                | 0     | 0                |

| 11   | 1     | 0     | 1     | 1     | 1     | 1     | 0     | 1     | 1       | 0                | 0     | 0                |

| 12   | 1     | 1     | 0     | 0     | 0     | 0     | 1     | 1     | 0       | 1                | 1     | 0                |

| 13   | 1     | 1     | 0     | 1     | 1     | 0     | 1     | 1     | 1       | 1                | 1     | 0                |

| 14   | 1     | 1     | 1     | 0     | 0     | 1     | 1     | 1     | 0       | 0                | 1     | 0                |

| 15   | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1       | 0                | 1     | 0                |

Table 3.3: LSB, LSB ABI and MSB digital input codes for radix sixteen.

Figure 3.1: Ideal transfer characteristic of a monotonic D/A converter. The three radices of interest, radix four, eight and sixteen, are illustrated.

Inverters[20] the refresh rate is required to be below a certain frequency. Otherwise both leakage and refresh rate will affect performance.

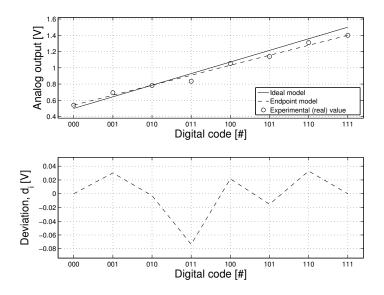

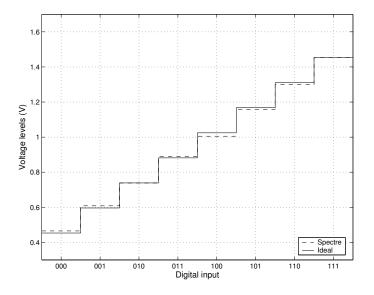

A sweep of all digital input codes X is used as a test, producing the staircase transfer function shown in figure 3.2. The static performance measures are given by the converter deviation between the experimental output voltage levels and the ideal staircase transfer function of uniform steps. The set of ordered digital input codes used are denoted

$$X = (X_0, X_1, \dots, X_{2^n - 1})$$

(3.1)

where  $X_0$  normally is the all-zero code and  $X_{2^n-1}$  is the all-ones code. The codes are ordered ascending by their converter output voltages. In an ideal converter the distance between the output values of two adjacent input codes is 1LSB. The LSB voltage is  $2^{-n}$  of the full scale output swing  $V_{FS}$ .

The experimental output values  $Y_{real}$  and the ideal theoretical values Y deviate by an error

$$d_i = Y_{real}\left(X_i\right) - Y\left(X_i\right) \tag{3.2}$$

A set of standard static measures for characterization of D/A converters exists which can be grouped into linear and non-linear errors. In this thesis the focus is on linear errors such as gain and offset errors, and non-linear measures such as differential non-linearity (DNL) and integral non-linearity (INL) errors.

Figure 3.2: Example of transfer characteristic and deviation measures of a D/A converter using three bit resolution.

The gain is calculated using

$$A = [Y_{real}(X_{2^{n}-1}) - Y_{real}(X_{0})] / [Y(X_{2^{n}-1}) - Y(X_{0})]$$

(3.3)

Offset errors are the difference between experimental and ideal output voltages when using an all-zero input code  $X_0$ . All the digital codes in the transfer characteristic are offset by this value;

$$Y_{offset} = Y_{real} (X_0) - Y (X_0) = d_0$$

(3.4)

The non-linear measures are often calculated after compensating for gain and offset errors. Experimental output values are compared with a straight line Y' going through its end-points  $Y_{real}(X_0)$  and  $Y_{real}(X_{2^n-1})$ .

Differential non-linearity (DNL) is the maximum deviation in the output step sizes from the ideal values of one least significant bit (LSB). It can also be expressed as the change in deviation between to adjacent codes  $X_i$  and  $X_{i-1}$ ;

$$D_i = d_i - d_{i-1} \tag{3.5}$$

An increasing DNL indicates an increasing deviation from the ideal converter characteristics. The ideal DNL is  $D_i = 0$  for all adjacent ordered code transitions. This gives an monotonic increasing transfer characteristic and an uniform distribution of the converter output voltage levels over the output voltage swing,  $V_{FS}$ . A DNL less than  $\pm 1LSB$  indicates a monotonic transfer characteristic.

The integral non-linearity (INL) describes the overall or maximum deviation from a wanted straight line. Before determining the INL it is common to compensate for the gain error and offset which are both linear components. The ideal converter model is adjusted using the end-point values  $Y_{real}(X_0)$ and  $Y_{real}(X_{2^n-1})$  of the experimental result. This form of INL is called endpoint INL. It is defined as

$$I_{i} = \sum_{k=1}^{i} D_{k} = (d_{i} - d_{0}) / V_{LSB}$$

(3.6)

An INL less than 0.5 LSB is analog with a monotonic D/A converter output [49].

In addition the converter resolution is often stated. It is given by the number of bits in the input code, n. It is also common to refer to the number of distinct analog output voltage levels, the radix R, of the converter. In binary weighted converters the radix of the analog output voltage is  $R = 2^n$ . A third option is to give the accuracy in voltage, often relative to the LSB-voltage  $V_{LSB}$ .

### 3.4 Summary

This chapter provides background for analysis of serial D/A converters using SFG devices. The standard non-linear static D/A converter performance measures, integral non-linearity (INL) and differential non-linearity (DNL), are introduced as figures of merit (FoM).

Further information on static D/A converter measures can be found in [48] [49][50][56]. Hoeschele [48] and Razavi [49] define analysis methods and provide popular reference material.

## Chapter 4

# SEMI FLOATING-GATE SERIAL D/A CONVERSION

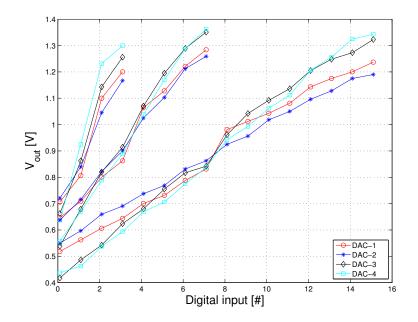

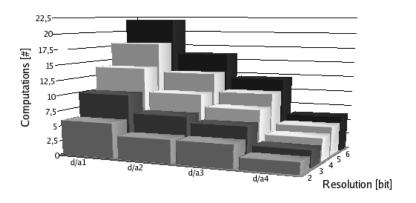

This chapter summarizes the proposed new Semi Floating-Gate (SFG) serial D/A converters published in [38, 39, 41, 42, 43][Papers I, II, IV, V and VI]. The converters are presented and discussed. In addition, previously unpublished measurements of practical chip implementations are included. A total of five new converter implementations using SFG inverters are presented.

The converters are presented in chronological order and referred to as DAC-1,...,DAC-5. The work covers Least Significant Bit-First (LSB), Least Significant Bit-First with Alternate Bit Inversion (LSB-ABI) and Most Significant Bit-First (MSB) type serial D/A conversion. Also, the algorithms can be described by the number of iterations per recharge clock cycle; Single Data-Rate (SDR) when using one iteration per recharge clock cycle and Dual Data-Rate (DDR) when using two. A measure of linearity is found using standard D/A converter measures as described in chapter 3. Finally, a summary of the converter linearity as a function of resolution and converter implementations is provided at the end of this chapter.

### 4.1 Introduction

In this chapter practical implementations of serial D/A converters using semi floating-gate (SFG) devices are presented. The proposed circuits exploit semi floating-gate inverters for a compact and configurable design. In [20] Berg *et al.* introduce the semi floating-gate (SFG) inverter for Multiple-Valued Logic (MVL) purposes. The inverter is a volatile multiple-input Multiple-Valued inverter recharged periodically by a recharge clock signal. Several techniques have been proposed for making this recharge clock surplus. Halvorsrød *et*

al. [57] propose an active floating-gate inverter. The leakage current of reverse powered diodes are utilized to create high impedance conductances between the floating-gate and two bias voltages. Another technique is pseudo floating-gate [58] which makes use of resistors for control of the floating-gate voltage. A different approach is to exploit the recharge switches for increased functional capacity per device. In [19] Mirmotahari *et al.* introduce a SFG Latch structure consisting of only two SFG inverters in series. The technique requires two perfectly matched and non-overlapping complementary clock signals.

Binary to multiple-valued radix converters using SFG devices have traditionally been implemented using bit-parallel D/A converter algorithms. In this thesis, work on new configurable serial D/A converters is presented. A total of five novel SFG based cyclic D/A converters are proposed. The converters out-perform the bit-parallel ones in terms of small die area requirement and ability to adapt through re-configuration. In this thesis, it is assumed that digital data are communicated bit-serially between the surrounding binary world and the multiple valued logic circuit. A cyclic D/A converter then offers a significant reduction in die area compared to bit-parallel D/A based MVL encoders. The latter requires an additional serial to parallel conversion for solving the problem of serial D/A conversion. These serial to parallel converters are typically implemented using a shift-register.

The functionality of the cyclic D/A converters is demonstrated through simulations in Cadence Spectre, chip measurements and study of D/A converter linearity. Two encoder properties are of primary concern; noise margins and monotonicity. Optimal noise margins are synonymous with equal spacing between the output values. This makes it important to characterize the linearity of the converters through simulations.

The construction of SFG based cyclic D/A converters is an interesting and challenging task for several reasons. First of all, a high precision SFG based memory is required. Offset, gain and linearity errors will have a huge impact on the overall performance. Second, the SFG memory will require that a multi-phase clocking strategy is selected. Modern designs tend to minimize the number of clock phases used. In this work two-phase clock signals are chosen as they allow a more compact memory, and thus more compact converters to be built. A problem with this choice is that it requires the clock signals to be perfectly matched, complementary and non-overlapping [19]. A third challenge is the analog nature of SFG inverters. The inverters are inherently level-noise propagating, which can make SFG based cyclic D/A conversion challenging. Its finite gain imposes further deviation from the ideal converter output values.

# 4.2 SDR LSB D/A Converter (DAC-1)

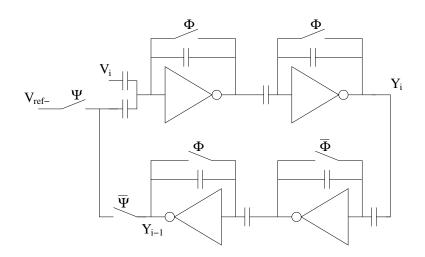

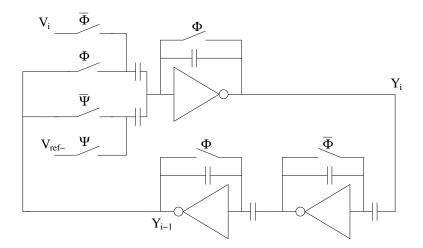

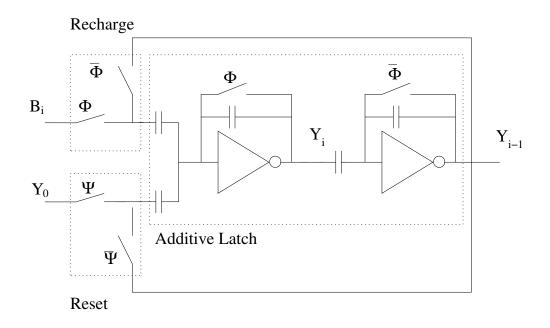

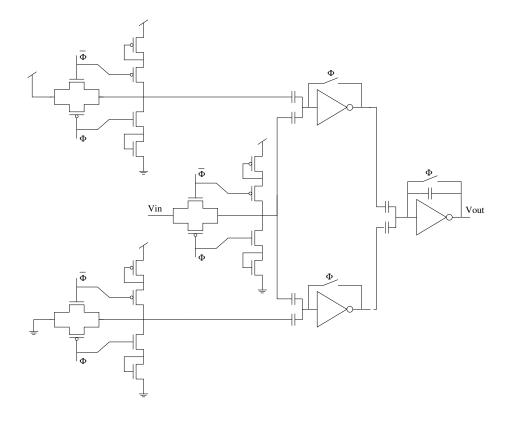

Figure 4.1: Schematic diagram for DAC-1. Digital input voltage  $V_i$ , recharge signal  $\Phi$ , reset signal  $\Psi$  and analog output voltage  $Y_i$  are shown.

The circuit presented in figure 4.1 [38] [Paper I] and described in equation 2.2 will be referred to as DAC-1. It implements LSB-First type D/A conversion. To the knowledge of the author, this converter is the first attempt to implement cyclic D/A conversion using SFG inverters. A two-phase clocking strategy referred to as "recharge and evaluation" is chosen. This requires perfect matching of the two complementary and non-overlapping clock signals  $\Phi$  and  $\overline{\Phi}$ . The circuit consists of two logical components; a two-input SFG Adder and a SFG Latch.

The SFG Latch is the analog memory of the converter. It is required for storing the intermediate result between each iteration. The two one-input inverters with opposite clock signals (latch configuration) form the SFG Latch[19] capable of storing the analog values. A latching clock scheme gives unity gain in each inverter and a delay of half a clock period. The latch provides a one clock period delay as required by the cyclic D/A converter algorithm.

One iteration is computed per cycle using the SFG Adder. The (n-1) first computations therefore involve four SFG inverter computations each. In the *n*-th cycle only two computations take place. This gives a total of 4(n-1) + 2 analog SFG inverter computations. SFG inverters operated in "recharge and evaluation" mode have gain -1. A second one-input inverter is connected in series to compensate for the negative gain. The two inverters form a two-input SFG Adder. In order to solve the difference equation in 2.2, linear operation and binary weights are required. A standard two-input SFG Adder is sufficient. First, the two input capacitors are chosen equally large. Second, in order to assert unity gain, the feedback capacitors and the sum of the input capacitors are matched by layout simulation in Cadence Spectre. The weighted sum then equals the divide-by-two operation found in the LSB-First cyclic D/A algorithm (equation 2.2) of DAC-1. Note, according to simulations the parasitic capacitances are much smaller than the wanted capacitances. This reduces the effect of device variation (mismatch). Gate capacitance is dependent on  $V_{gs}$  and  $V_{ds}$ . In our circuits the effect of these gate-capacitance variations are smaller than in a single *pMOS* or *nMOS* transistor. The *pMOS* and *nMOS* sides will to some extent cancel each other out.

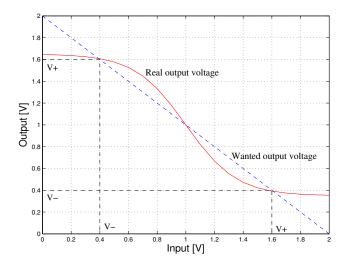

Analog SFG inverters have finite gain and it is necessary to limit their operation to an interval of voltages between  $V^-$  and  $V^+$ . In this study experiments are performed using  $V^- = 0.5V$  and  $V^+ = 1.5V$  due to increased non-linearity close to the rails. This gives a converter with a reduced output voltage swing; from  $V_{dd} = 2V$  to  $(V^+ - V^-)$ . All input signals (except clock signals) are offset by  $V^-$ . The bit-serial digital input  $B_i$  needs to be encoded  $V^-$  when "0" and  $V^+$  when "1".

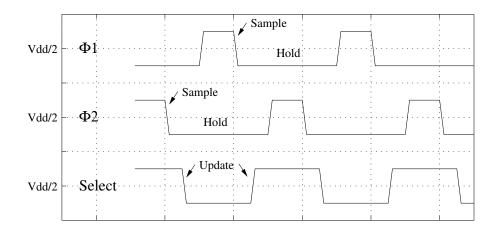

A non-overlapping two phase clock  $\Phi$  and a perfectly matched complementary clock  $\overline{\Phi}$  drive the converter. The two phases  $\Phi = 0$  and  $\Phi = 1$  are referred to as the "evaluation" and "recharge" period respectively. During the "evaluation" period the digital input  $B_i$  is read and one iteration is computed by the SFG Adder. While in this mode the semi floating-gate of the SFG Latch is also recharged. In the "recharge" period the result of previous bits is latched into and stored in the SFG Latch. While in this memory phase, all other nodes are recharged using  $V_{in} = V_{out} = V_{SFG} = V_{dd}/2$ .

The converter is initialized by disconnecting the SFG Latch output voltage from the SFG Adder and replacing it with the all-zero code voltage  $Y_0 = Y^- = 0.5V$ .

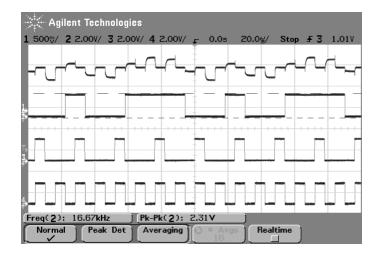

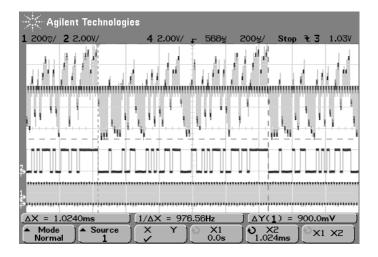

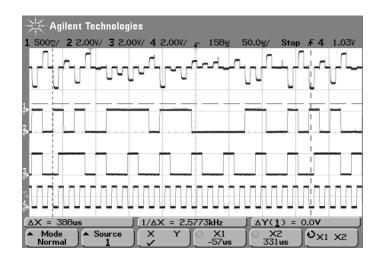

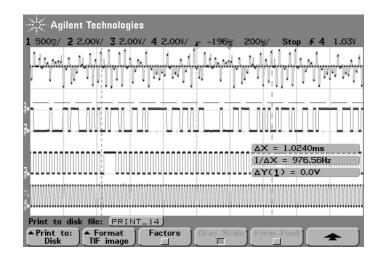

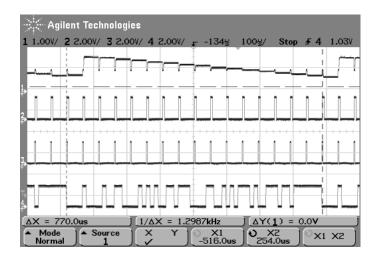

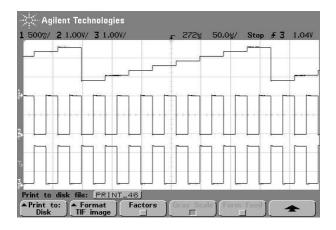

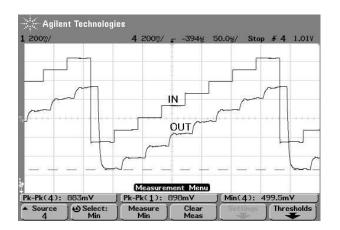

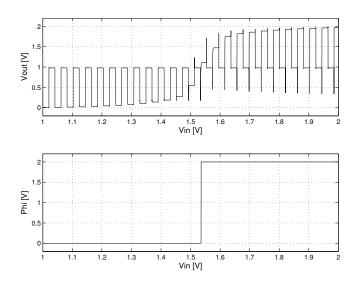

Measured DAC-1 operation is illustrated in figure 4.2, figure 4.3 and figure 4.4. In the first illustration, figure 4.2, there are four traces. The first trace shows a radix four analog output voltage sampled from node  $Y_i$ . Trace two is a train of bit-serial input codes. This code sequence generates a staircase at the output node in trace one. Trace three is the reset clock applied in node  $\Psi$ . The last trace shows the recharge-clock (bit-clock) signal  $\Phi$ . In the second and the third illustration the reset signal  $\Psi$  is omitted. This gives more room for the output voltage as the resolution is increased to three bit in figure 4.3 and four bit in figure 4.4. An additional illustration of the converter operation is shown in figure 4.5. Here, the multiple-valued output voltage levels are circled out.

Figure 4.2: Measured DAC-1 output voltages and timing of clock signals. Configured for radix R=4 using n=2,  $f_{\phi} = 41.7kHz$ ,  $f_{\psi} = 20.83kHz$ . The four traces are; analog output voltage  $Y_i$ , bit-serial input code  $B_i$ , reset clock  $\Psi$  and bit-clock  $\Phi$ .

Figure 4.3: Measured DAC-1 output voltages. Configured for radix R=8 using n=3,  $f_{\phi} = 62.0 kHz$ ,  $f_{\psi} = 20.67 kHz$ . The three traces are; analog output voltage  $Y_i$ , bit-serial input code  $B_i$  and bit-clock  $\Phi$ .

Figure 4.4: Measured DAC-1 output voltages. Configured for radix R=16using n=4,  $f_{\phi} = 62.5 kHz$ ,  $f_{\psi} = 15.63 kHz$ . The three traces are; analog output voltage  $Y_i$ , bit-serial input code  $B_i$  and bit-clock  $\Phi$ .

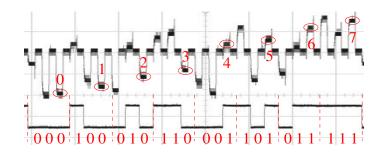

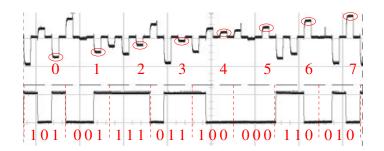

Figure 4.5: Illustration of LSB D/A conversion. Measurements using DAC-1 and three bit resolution are used as illustration data. The multiple-valued output voltage levels are circled out. Labels are included for the voltages representing the multiple-values (0-7) generated by the LSB-First input codes (000-111).

### 4.3 SDR LSB ABI D/A Converter (DAC-2)

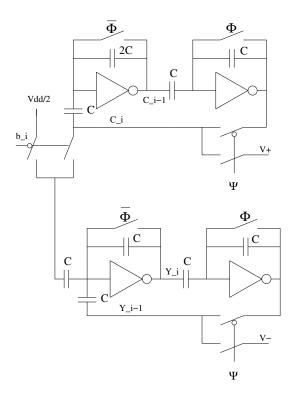

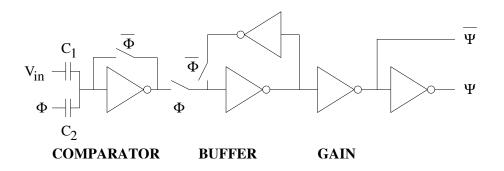

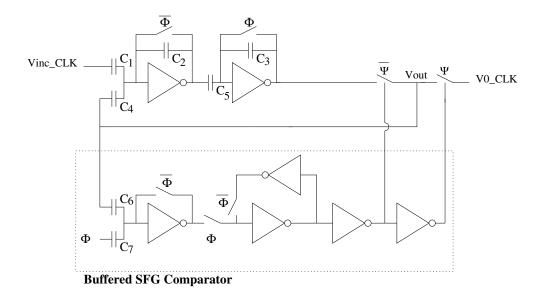

Figure 4.6: Schematic diagram of DAC-2, a SFG inverter implementation of a LSB ABI type D/A converter algorithm. The digital input voltage  $V_i$ , recharge clock signal  $\Phi$ , reset clock signal  $\Psi$  and analog output voltage  $Y_i$  are shown. The auto-zero circuit is built into the design using two switches.

Figure 4.6 shows the SDR LSB ABI D/A Converter from [39][Paper II] called DAC-2. It implements the error correction algorithm referred to as LSB ABI presented in chapter 2.3 (equation 2.7). The proposed circuit is a modified version of DAC-1 [38][Paper I]. External input and output signals of DAC-1 and DAC-2 are mainly the same. Two global input signals, one for digital input codes  $b_i$  and one for the initial all-zero code voltage  $Y_0 = Y^- = 0.5V$ , are needed. The digital input  $b_i$  is recharged using two switches which allows the larger auto-zero circuit (AZC)[59] to be omitted. Removal of the AZC both eliminate a source of error and reduce power consumption. However, this requires the reset signal ( $\Psi$ ) to be modified. The new reset clock signal has half the pulse-width of the original reset clock. There are two feedback wires. The upper wire interleaves the bit-serial input with a recharge voltage ( $V_{dd}/2$ ). The lower wire provides a negative feedback of the intermediate analog output voltage  $Y_i$ .

Two sets of complementary clock signals synchronize the conversion process; bit-clock signals  $\Phi$  and  $\overline{\Phi}$ , and reset clock signals  $\Psi$  and  $\overline{\Psi}$ . Again, both clock signals are required to be sets of perfectly matched, complementary and nonoverlapping waveforms. The binary data are represented by a voltage of 0.5V for zeros and 1.5V for ones. The conversion process for DAC-2 requires three SFG inverter computations the first n-1 cycles, and only one computation the n-th (final) round. A total of 3(n-1) + 1 SFG inverter computations are involved, which is (n-1) less computations than when using the circuit DAC-1. There are mainly two goals for proposing the new circuit, DAC-2. First, the number of analog SFG inverter based computations per cycle is a limited resource. Compared to DAC-1 [38][Paper I], one inverter is omitted in the two-input SFG adder component. This gives a more compact LSB ABI type cyclic D/A converter and reduces the die area of practical implementations. In addition, each SFG inverter operation degrades the multiple-valued signal and propagates level-noise without any form of level correction. By omitting one SFG inverter, the overall converter linearity is improved. In figure 4.7 the SFG inverter transfer function is illustrated.

Figure 4.7: Illustration of how errors are created in the converter. The slashed graph shows wanted output voltage and solid graph shows real output voltage of a SFG Inverter.  $V^- = 0.4V$  and  $V^+ = 1.6$  in this example.

Second, the number of cycles can be extended by introducing the new error correction scheme. The circuit exploits negative inverter gain in the converter loop as negative feedback. This causes errors of previous iterations to be subtracted. By applying the same alternating inversion to digital input codes, only errors are subtracted. LSB ABI digital input codes were presented in more detail in chapter 2.3. Examples of 2, 3 and 4 bit codes are shown in the tables on pages 16 and 17. The codes are more complex than LSB and MSB codes which are standard binary numbers.

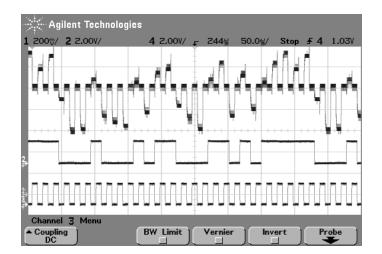

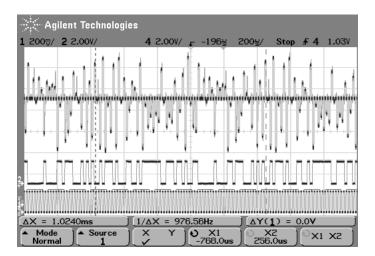

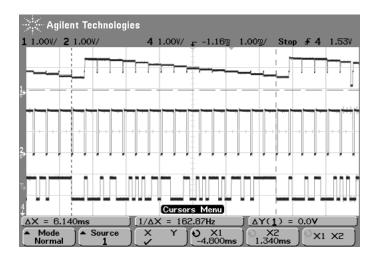

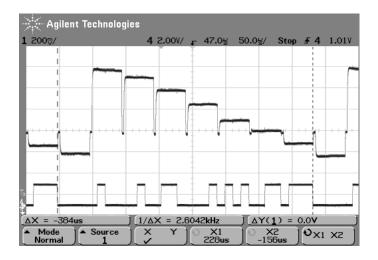

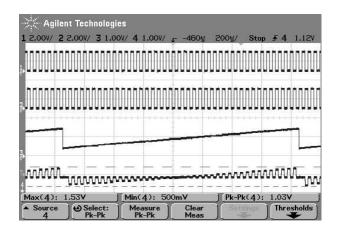

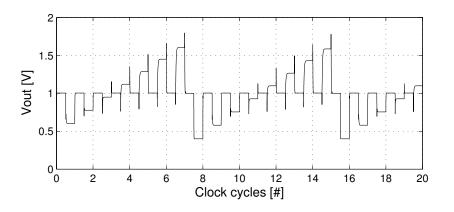

Measured DAC-2 operation is illustrated in figure 4.8, figure 4.9 and figure 4.10. In the first measurement in figure 4.8 there are four traces. The first trace shows a radix eight analog output voltage sampled from node  $Y_i$ . Trace two is a train of bit-serial input codes. This code sequence generates a staircase at the output node in trace one. Trace three shows the reset signal applied in node  $\Psi$ . The last trace shows the recharge clock signal  $\Phi$  (bit-clock). In figures 4.9 and 4.10 the resolution is increased to radix 16 by

Figure 4.8: Measured DAC-2 output voltages. Configured for radix R=8 using n=3,  $f_{\phi} = 61.86 kHz$ ,  $f_{\psi} = 20.62 kHz$ . The four traces are; analog output voltage  $Y_i$ , bit-serial input code  $B_i$ , reset clock  $\Psi$  and bit-clock  $\Phi$ .

applying four bit input codes. An additional illustration of the converter operation is shown in figure 4.11.

Figure 4.9: Measured DAC-2 output voltages. Configured for radix R=16using n=4,  $f_{\phi} = 62.5kHz$ ,  $f_{\psi} = 15.63kHz$ . The three traces are; analog output voltage  $Y_i$ , bit-serial input code  $B_i$  and bit-clock  $\Phi$ .

Figure 4.10: Measured timing of clock signals for DAC-2. Configured for radix R=16 using n=4,  $f_{\phi} = 62.5 kHz$ ,  $f_{\psi} = 15.63 kHz$ . The four traces are; analog output voltage  $Y_i$ , bit-serial input code  $B_i$ , reset clock  $\Psi$  and bit-clock  $\Phi$ .

Figure 4.11: Illustration of LSB ABI D/A conversion. A measurement using DAC-2 and three bit resolution is used as illustration data. The multiple-valued output voltage levels are circled out. Labels are included for the voltages representing the multiple-values (0-7) generated by the LSB-First input codes (000-111).

# 4.4 Improved SDR LSB D/A Converter (DAC-3)

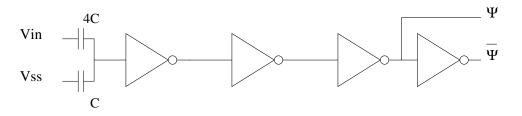

Figure 4.12: Block diagram for latching serial-bit D/A converter with digital input  $B_i$ , recharge signal  $\Phi$ , reset signal  $\Psi$  and analog output voltages  $Y_i$  and  $Y_{i-1}$ .

Figure 4.12 shows a new SDR LSB D/A converter from [41][Paper IV] called DAC-3. Compared to earlier work on DAC-1 in [38][Paper I], DAC-3 features a shorter multiple-valued signal path. This is made possible by use of sample and hold elements [40][Paper III] which have an increased accuracy and a higher functional capacity per device than traditional SFG Latches.

The conversion process is synchronized by the perfectly matched and nonoverlapping complementary clock signals  $\Phi$  and  $\overline{\Phi}$ . Compared to DAC-1 [38] [Paper I] and DAC-2 [39][Paper II], the converter is latching. This means that the "recharge and evaluation" clock scheme is replaced by a "sample and hold" clock scheme [40][Paper III]. In this scheme all input signals are sampled or latched into the converter. As a result the interleaved recharge voltages are shifted by 180 degrees compared to the "recharge and evaluation" clock scheme. The presented implementation makes use of switches for recharging of the input signals  $B_i$  and  $Y_0$ . There are two feedback wires. The upper wire interleaves the bit-serial input with a recharge voltage  $(V_{dd}/2)$ . The lower wire provides a negative feedback of the intermediate analog output voltage  $Y_i$ . In this circuit the critical number of analog SFG inverter based computations per cycle has been further reduced. The conversion process now requires two computations in each of the n-1 first cycles, and one computation for the *n*-th and final iteration. As a result, only 2(n-1) + 1 analog SFG inverter computations are involved. The converter supports one iteration of the SDR LSB D/A conversion algorithm (equation 2.4) per clock cycle.

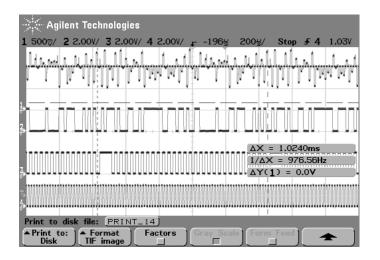

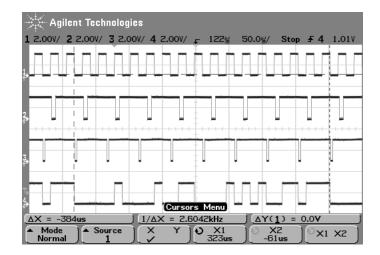

Measured DAC-3 operation is illustrated in figures 4.13 and 4.14. In the first measurement there are four traces. The first trace shows a radix four analog output voltage from node  $Y_i$ . Trace two is a train of bit-serial input codes applied at node  $B_i$ . This code sequence generates a staircase at the output node in trace one. Trace three shows the reset signal applied in node  $\Psi$ . The last trace shows the recharge clock signal  $\Phi$ . In figure 4.14 the three traces are shown. The first trace shows the 16 output voltage levels. The trace is a sampled from node  $Y_i$ . Trace two is the sampling clock signal and the last trace is the bit-serial input codes applied at node  $B_i$ .

Figure 4.13: Measured DAC-3 output voltages. Configured for radix R=4using n=2,  $f_{\Phi} = 82.98 kHz$ ,  $f_{\Psi} = 41.49 kHz$ . The four traces are; analog output voltage  $Y_i$ , bit-serial input code  $B_i$ , reset clock  $\Psi$  and bit-clock  $\Phi$ .

Figure 4.14: Measured DAC-3 output voltages. Configured for radix R=16 using n=4,  $f_{\phi} = 10.4 kHz$ ,  $f_{\psi} = 2.6 kHz$ . The three traces are; analog output voltage  $Y_i$ , sampling signal and bit-serial input code  $B_i$ .

# 4.5 DDR LSB D/A Converter (DAC-4)

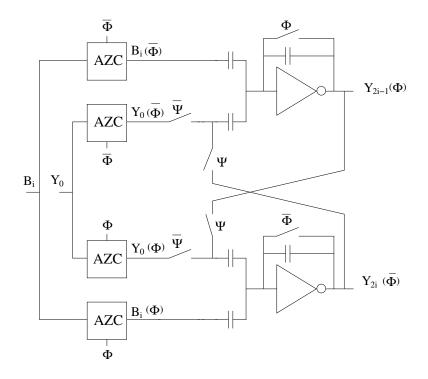

Figure 4.15: Block diagram for DDR LSB serial-bit D/A converter with digital input voltage  $B_i$ , recharge signal  $\Phi$ , reset signal  $\Psi$ , analog output voltage  $Y_{2i-1}$  and analog output voltage  $Y_{2i}$ .

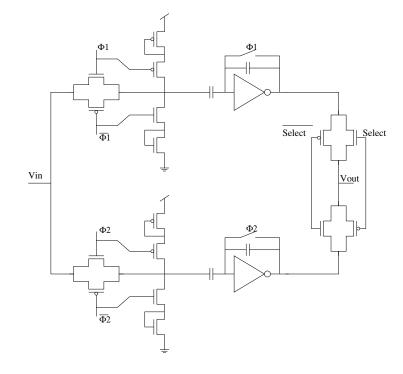

In figure 4.15 [42] **[Paper V]** a new and faster SFG serial D/A converter is presented. The converter supports two iterations per clock cycle compared to merely one in DAC-1 [38] **[Paper I]**, DAC-2 [39] **[Paper II]** and DAC-3 [41] **[Paper IV]**. This change is made possible by combining two SFG S/H elements from [40]**[Paper III]** in a loop.

A new Dual Data-Rate (DDR) clock scheme is introduced in which SFG operations are performed on both recharge clock edges. The remaining time is utilized as settling time and guard intervals. A reduced conversion rate is one of the main problems associated with cyclic D/A conversion [46]. Between each iteration the stored intermediate analog output voltage is delayed only half a clock period between each addition. As a result, by using this new scheme, bit-rates at twice the maximum SFG recharge rate are supported. Because of this property the converter will be referred to as a Dual Data-Rate (DDR) converter. DAC-4 [42][Paper V] is the only converter in this work which supports bit-rates at twice the maximum SFG recharge rate. It is also the only converter presented to process data at a rate beyond the fundamental recharge rate limit. This allows the generation of radix four

signals using merely one recharge clock cycle which correspond to a radix of sixteen after only two recharge clock cycles.

Compared to the extremely compact DAC-3 [41][Paper IV], the size of DAC-4 is only marginally increased. However, four auto-zero circuits (AZC) [59] are utilized for generating input signals with an interleaved recharge voltage. These AZC's contribute noticably to the die area of DAC-4. The two SFG Inverters are in a looped SFG Latch configuration. This means that while resetting one SFG Inverter the other acts as an output buffer.

Again, two bias voltages  $Y^-$  and  $Y^+$  are included, allowing the multiplevalued output voltage levels to be tuned. The initial value  $Y_0$  is set to the smallest output  $Y^-$ , which corresponds to the all-zero code voltage. An initial condition,  $Y_0 = Y^-$ , is set by applying a high reset clock signal  $\Psi$ and low complementary reset clock signal  $\overline{\Psi}$ . The converter is also expected to function with initial voltage  $Y_0$  set to  $V_{dd}/2$ . Note that each iteration is synchronized by the edges of the perfectly matched and complementary clock signals  $\Phi$  and  $\overline{\Phi}$ .

Practical experiments use digital input  $b_i$  encoded as  $Y^- = 0.5V$  when a '0' and  $Y_+ = 1.5V$  when '1'. The input signal  $b_i$  is latched or sampled into the converter as in DAC-3. SFG inverter based latching requires input signals to be interleaved with a recharge voltage of  $V_{dd}/2$ . These voltages are denoted  $b_i(\overline{\Phi}), b_i(\Phi), Y_0(\overline{\Phi})$  and  $Y_0(\Phi)$ . In DAC-4 the recharging is done using AZC's as shown in figure 4.15. The introduction of AZC's is motivated by a reduction in clock signal complexity and their application as input buffers.

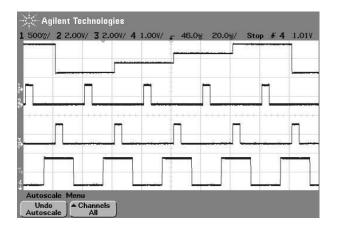

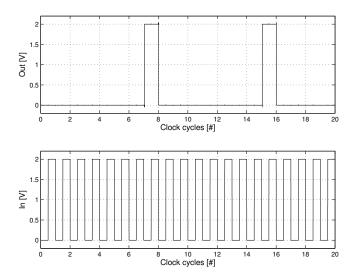

Measured DAC-4 operation is illustrated in figures 4.16 and 4.17. In the first measurement in figure 4.16 there are four traces. The first trace shows a radix 16 analog output voltage sampled from node  $Y_{2i}$ . The next trace shows a read-out clock signal controlling a sample and hold circuit. Trace three shows the reset signal applied in node  $\Psi$ . The last trace shows a train of bit-serial input codes applied at node  $B_i$ . In figure 4.17 only sampled output voltages and bit-serial input codes are traced. In figure 4.18 timing of clock signals is illustrated. Four traces are shown. These are recharge clock from node  $\overline{\Phi}$ , reset clock from node  $\Psi$ , a sample clock and the bit-serial input codes applied at node  $B_i$ .

In DAC-4 [42] [Paper V] the number of analog SFG inverter based processing has been further reduced. Only n SFG inverter computations are required per conversion process. This means an optimal one computation per iteration or per bit resolution.

Figure 4.16: Measured DAC-4 output voltages. Configured for radix R=16using n=4,  $f_{\phi} = 83.14kHz$ ,  $f_{\psi} = 20.78kHz$ . The four traces are; sampled analog output voltage  $Y_{2i}$ , read-out clock signal, reset clock  $\Psi$  and bit-serial input code  $B_i$ .

Figure 4.17: Measured DAC-4 output voltages. Configured for radix R=8using n=3,  $f_{\phi} = 62.5kHz$ ,  $f_{\psi} = 20.83kHz$ . The two traces are sampled analog output voltage  $Y_{2i}$  and bit-serial input code  $B_i$ . The measurement setup was limited to an even number of bit. 3 bit resolution is therefore evaluated using 4 bit codes.

Figure 4.18: Measured timing of clock signals for DAC-4. Configured for radix R=8 using n=3,  $f_{\phi} = 62.5kHz$ ,  $f_{\psi} = 20.83kHz$ . The four traces are; recharge clock (bit-clock)  $\overline{\Phi}$ , reset clock  $\Psi$ , sample clock and bit-serial input code  $B_i$ .

### 4.6 MSB D/A Converter (DAC-5)

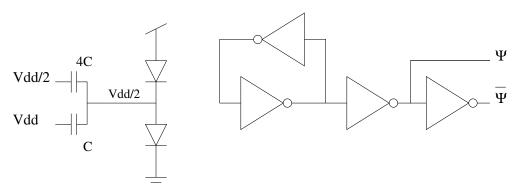

Figure 4.19: Block diagram for MSB-first serial D/A converter using SFG devices.

Figure 4.19 presents a new SFG MSB serial D/A Converter introduced in [43][Paper VI] called DAC-5. The converter supports runtime re-configuration of the output radix and Most Significant Bit-First (MSB) type digital input codes. MSB is the bit-order used by successive-approximation A/D converters. The development of a MSB-First serial D/A converter therefore becomes essential in multiple-valued encoder/decoder applications.

DAC-5 consists of two components, a SFG MV counter and a SFG MV accumulator, both modified versions of DAC-3 [41][Paper IV]. A high functional capacity per device is achieved by use of the SFG sample and hold clock scheme in [40][Paper III]. Note that the use of recharged input signals has been avoided in DAC-5. The presented MSB D/A converter therefore consists of only four SFG inverters.

The converter is clocked and biased using mainly the same input signals as in earlier work. A total of seven input signals are included; a serial MSB-first digital input  $(b_i)$ , two recharge clock signals  $(\Phi \text{ and } \overline{\Phi})$ , two reset clock signals  $(\Psi \text{ and } \overline{\Psi})$ , two bias voltages  $(V^- \text{ and } V^+)$  and an additional voltage reference  $V_{dd}/2$ . Again, note that the input signals are not interleaved with a recharge

Figure 4.20: Sampled output voltages of DAC-5. A stream of MSB-first digital input codes, 000<sub>2</sub>-111<sub>2</sub>, was used as test data.

voltage. The analog output voltage results at terminal  $Y_i$  every n-th cycle and is easily retrieved using the SFG S/H circuit presented in [40][**Paper III**]. The system is reset when  $\Psi$  is high. In this state the SFG MV accumulator is initialized with the all-zero code voltage,  $Y_0 = Y(X_0) = V^-$ , and the SFG MV Counter with the MSB-weight voltage  $W_0 = V^+ = 1.5V$ . These parameters assume a converter output swing between  $V^-$  and  $V^+$ .

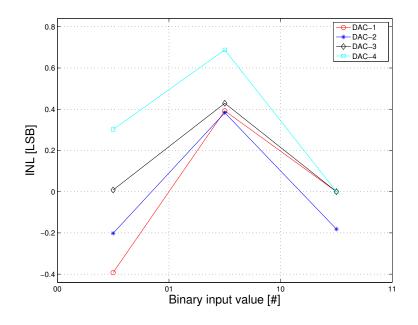

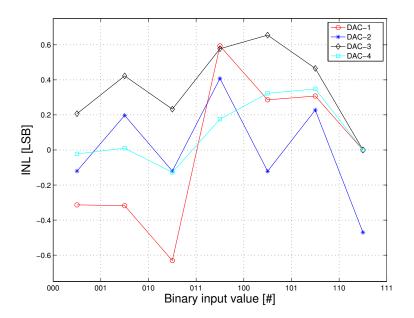

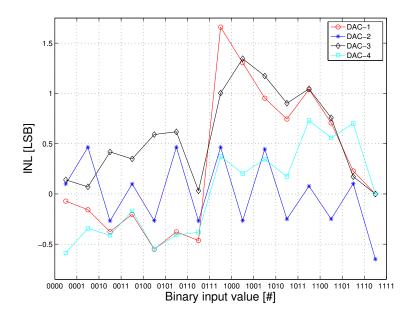

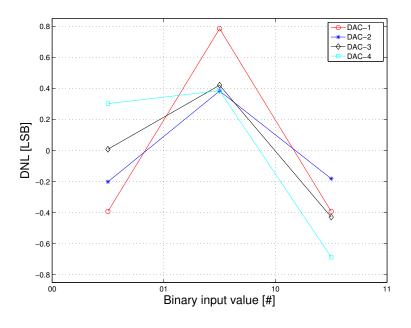

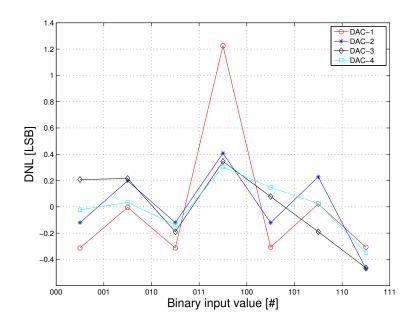

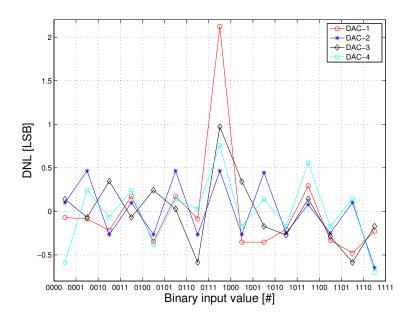

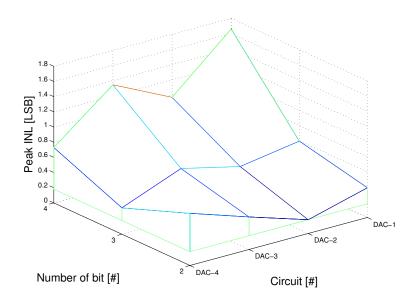

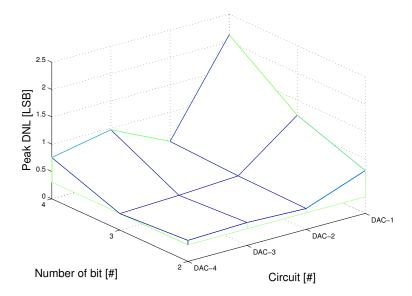

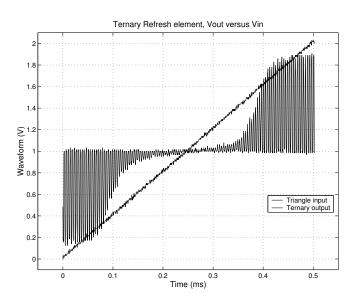

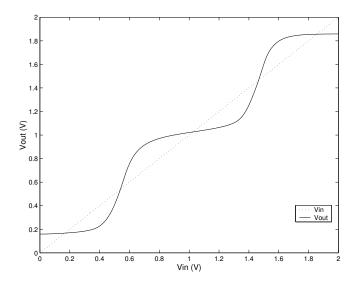

SFG MSB-First serial D/A conversion was described earlier in chapter 2.4 (equation 2.12). Figure 4.19 showed a practical implementation. In the SFG MV counter, binary weights are generated successively in a descending order, starting with the weight of the MSB ( $W_0 = V^+$ ). The voltages representing binary weights are offset by a voltage of  $V_{dd}/2$ . In each cycle a divide-by-two operation takes place. This is implemented using a feedback capacitor which is twice as large as the input capacitor.