UNIVERSITY OF OSLO Department of Informatics

Investigation of parallel programming on heterogeneous multiprocessors

Masteroppgave

Håvard Espeland

# **Contents**

| Pr         | eface |          |                                              | vii |

|------------|-------|----------|----------------------------------------------|-----|

| A          | cknov | wledge   | ments                                        | ix  |

| <b>A</b> l | bbrev | iations  | ;                                            | xi  |

| 1          | Intr  | oductio  | on                                           | 1   |

|            | 1.1   | Backg    | round and motivation                         | 1   |

|            | 1.2   | Proble   | em statement                                 | 3   |

|            | 1.3   | Resea    | rch Contributions                            | 3   |

|            | 1.4   | Outlin   | ne                                           | 3   |

| 2          | Het   | erogen   | eous multi-core architectures                | 5   |

|            | 2.1   | Cell B   | roadband Engine                              | 5   |

|            |       | 2.1.1    | Hardware overview                            | 6   |

|            |       | 2.1.2    | Communication and synchronization            | 7   |

|            |       | 2.1.3    | The Playstation 3 and Linux                  | 8   |

|            |       | 2.1.4    | Performance tuning                           | 9   |

|            |       | 2.1.5    | Parallelization schemes                      | 10  |

|            |       | 2.1.6    | Comparison to x86 symmetric multi processors | 12  |

|            |       | 2.1.7    | Potential and applications                   | 12  |

|            | 2.2   | IXP 24   | 400 Network processor                        | 13  |

|            | 2.3   | Other    | architectures                                | 15  |

|            |       | 2.3.1    | Graphics Processing Units                    | 15  |

|            | 2.4   | Sumn     | nary                                         | 16  |

| 3          | Prot  | ocol tra | anslation on Intel IXP network processor     | 19  |

|            | 3.1   | Backg    | round information                            | 19  |

|            | 3.2   | Imple    | mentation                                    | 21  |

|            |       | 3 2 1    | Network performance                          | 22  |

|   | 3.3         | Lessor  | ns learned                      | 23 |

|---|-------------|---------|---------------------------------|----|

|   | 3.4         | Summ    | ary                             | 24 |

| 4 | n <b>-Q</b> | ueens P | Problem                         | 25 |

|   | 4.1         | Backgı  | round Information               | 26 |

|   | 4.2         | Adapt   | ation for Cell                  | 26 |

|   |             | 4.2.1   | Implementation                  | 26 |

|   |             | 4.2.2   | Evaluation                      | 31 |

|   | 4.3         | Lessor  | ns learned                      | 33 |

|   | 4.4         | Summ    | ary                             | 33 |

| 5 | Adv         | anced I | Encryption Standard             | 35 |

|   | 5.1         | Backgı  | round information               | 35 |

|   |             | 5.1.1   | Cipher overview                 | 35 |

|   |             | 5.1.2   | Modes of Operation              | 38 |

|   | 5.2         | Softwa  | are basis                       | 39 |

|   | 5.3         | Adapt   | ation for Cell                  | 40 |

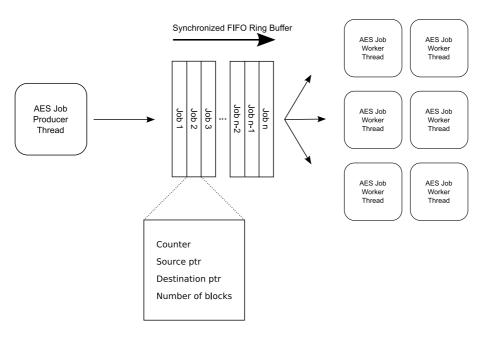

|   |             | 5.3.1   | Job Distribution                | 41 |

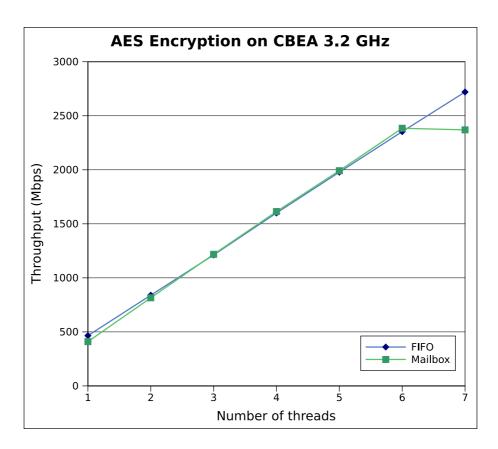

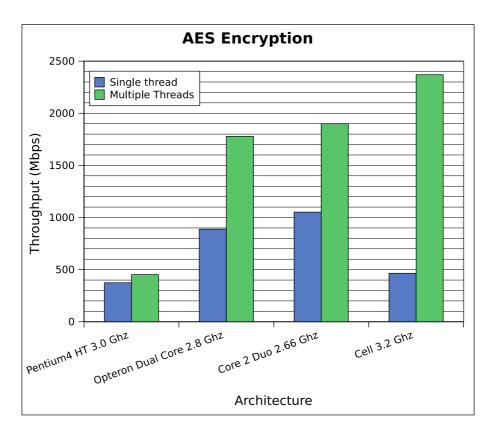

|   |             | 5.3.2   | Evaluation                      | 42 |

|   | 5.4         | Lessor  | ns learned                      | 43 |

|   | 5.5         | Summ    | ary                             | 44 |

| 6 | H.26        | 64/MPE  | G-4 Advanced Video Coding       | 45 |

|   | 6.1         | Backgr  | round information               | 45 |

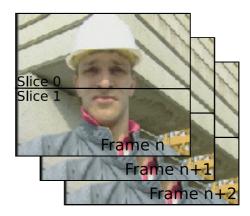

|   |             | 6.1.1   | Frames, Slices, and macroblocks |    |

|   |             | 6.1.2   | Color space                     | 49 |

|   |             | 6.1.3   | Encoding process overview       | 49 |

|   |             | 6.1.4   | Decoding overview               |    |

|   | 6.2         | Softwa  | are basis                       | 54 |

|   |             | 6.2.1   | The x264 video encoder          | 54 |

|   |             | 6.2.2   | Profiling x264                  | 54 |

|   | 6.3         | Adapt   | ation for Cell                  |    |

|   |             | 6.3.1   | Job distribution                |    |

|   |             | 6.3.2   | Half-pixel filtering            | 57 |

|   |             | 6.3.3   | Motion Estimation               |    |

|   |             | 6.3.4   | Evaluation                      |    |

|   | 6.4         | Lessor  | ns learned                      |    |

|   | 6.5         | Summ    | arv                             | 70 |

| 7  | Disc  | cussion                      | 71 |

|----|-------|------------------------------|----|

|    | 7.1   | Performance and potential    | 71 |

|    | 7.2   | Parallelization strategies   | 72 |

|    | 7.3   | Manual labour                | 74 |

|    | 7.4   | Architectural considerations | 75 |

|    | 7.5   | The future                   | 76 |

| 8  | Con   | clusion                      | 77 |

|    | 8.1   | Summary                      | 77 |

|    | 8.2   | Further work                 | 78 |

|    | 8.3   | Conclusion                   | 79 |

| Αŗ | pend  | lix                          | 81 |

| Bi | bliog | raphy                        | 82 |

# **List of Figures**

| 2.1 | The Cell Broadband Engine multiprocessor (public domain image)                | 5  |

|-----|-------------------------------------------------------------------------------|----|

| 2.2 | Main components of the Cell Broadband Engine                                  | 6  |

| 2.3 | A Synergistic Processing Element                                              | 8  |

| 2.4 | An example SIMD multiplication of two 128-bit vectors containing four         |    |

|     | 32-bit integer values. The multiplications are computed in parallel by a      |    |

|     | single instruction                                                            | 8  |

| 2.5 | Common parallelization strategies                                             | 11 |

| 2.6 | ENP-2611 from RadiSys with an IXP2400 Network Processor. The ENP-             |    |

|     | 2611 is a PCI-X card working independently of the host computer. It           |    |

|     | allows DMA transfers to and from the host computer using the PCI bus.         | 13 |

| 2.7 | IXP2400 architecture overview. The figure is from an Intel product brief      |    |

|     | on IXP2400 [1]                                                                | 14 |

| 2.8 | nVIDIA G80 architecture overview from [2]                                     | 16 |

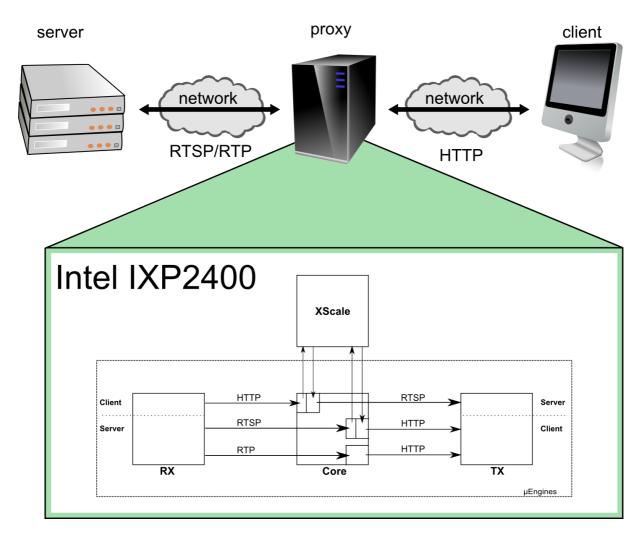

| 3.1 | Network packet flow of the protocol translation proxy                         | 20 |

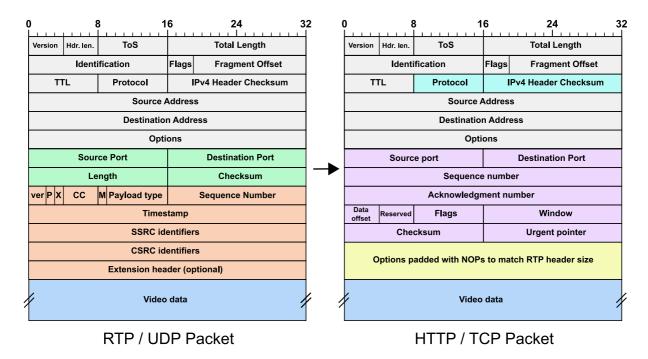

| 3.2 | RTP/UDP to HTTP/TCP Translation                                               | 22 |

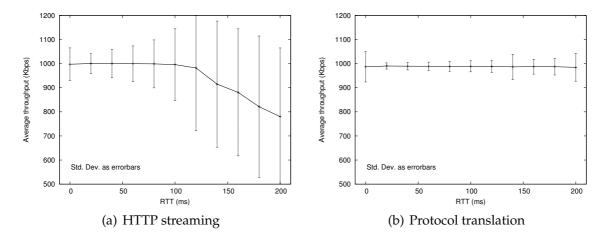

| 3.3 | Achieved bandwidth varying link latency with 1% loss                          | 23 |

| 4.1 | An example solution to the eight queens puzzle. Image from wikipedia [3]      | 25 |

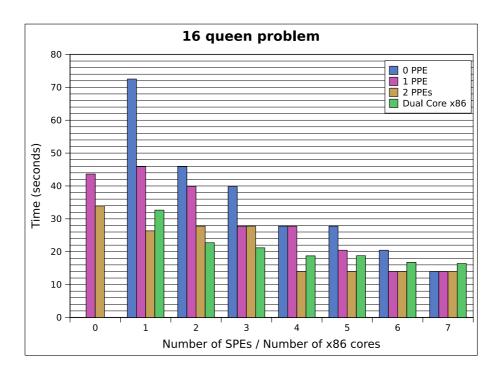

| 4.2 | Benchmark of the n-queens problem using n=16. Lower is better                 | 31 |

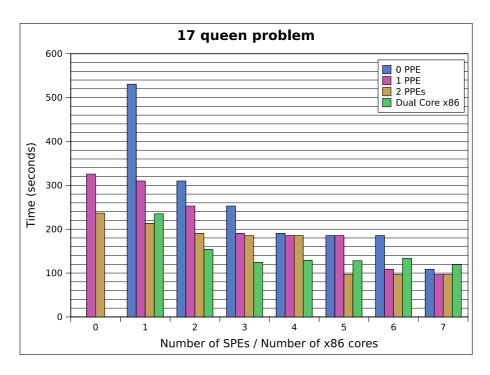

| 4.3 | Benchmark of the n-queens problem using n=17. Lower is better                 | 32 |

| 5.1 | Substitute Bytes. Illustration from Wikipedia [4]                             | 37 |

| 5.2 | Shift Row. Illustration from Wikipedia [4]                                    | 37 |

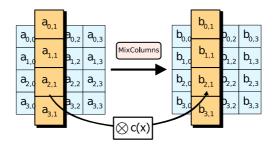

| 5.3 | Mix Column. Illustration from Wikipedia [4]                                   | 37 |

| 5.4 | Add Round Key. Illustration from Wikipedia [4]                                | 38 |

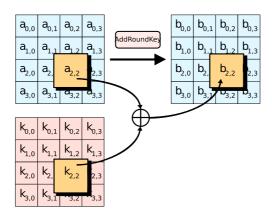

| 5.5 | Block cipher encryption using ECB mode of operation. Tux to the left is       |    |

|     | the original, Tux to the right is encrypted. Illustration from Wikipedia [5]. | 39 |

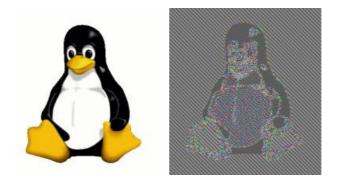

| 5.6 | Counter mode of operation for block encryption. Illustration from Wikipedi    | ia |

|     | [5]                                                                           | 39 |

| 5.7        | AES FIFO job distribution model                                                                                                                                                                                                                                               | 41        |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 5.8        | A benchmark of AES job distribution model on CBEA                                                                                                                                                                                                                             | 43        |

| 5.9        | A benchmark of AES on different architectures                                                                                                                                                                                                                                 | 44        |

| 6.1        | A video using two slices per frame. Each slice contains macroblocks, but are not shown                                                                                                                                                                                        | 47        |

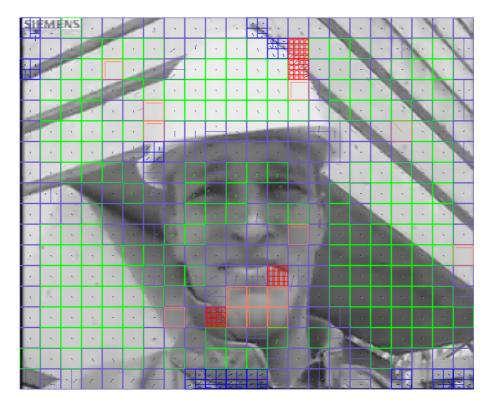

| 6.2        | An image displaying macroblock types for the foreman test sequence using x264 and one slice per frame. Green macroblocks are skipped (unchanged from last frame), red and orange macroblocks are intrapredicted, while the blue macroblocks are inter-predicted depicted with |           |

|            | motion vectors                                                                                                                                                                                                                                                                | 48        |

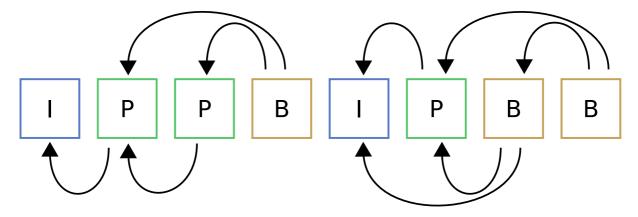

| 6.3        | An example sequence of slices in display order and their dependencies                                                                                                                                                                                                         | 40        |

| <i>(</i> 1 | to earlier ones                                                                                                                                                                                                                                                               | 49        |

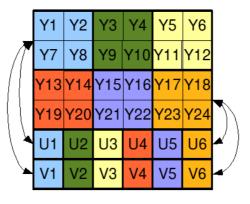

| 6.4        | 4:2:0 YUV packed chroma subsampling. This is similar to H.264's 4:2:0                                                                                                                                                                                                         | 10        |

|            | YCbCr with Cb and Cr represented as U and V. The figure is from Wikipedia article on YUV [6] with modifications                                                                                                                                                               | 1 S<br>50 |

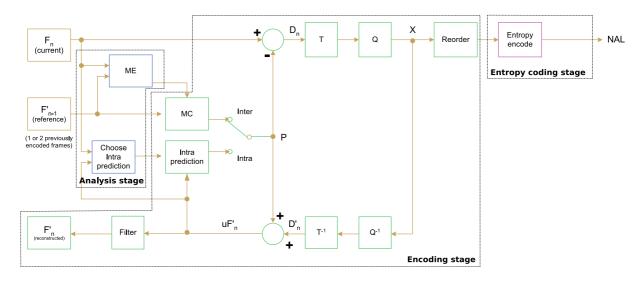

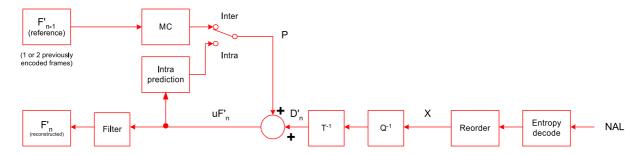

| 6.5        | H.264 encoder overview, borrowed from [7] and slightly modified                                                                                                                                                                                                               | 50        |

| 6.6        | H.264 decoder overview, borrowed from [7]                                                                                                                                                                                                                                     | 53        |

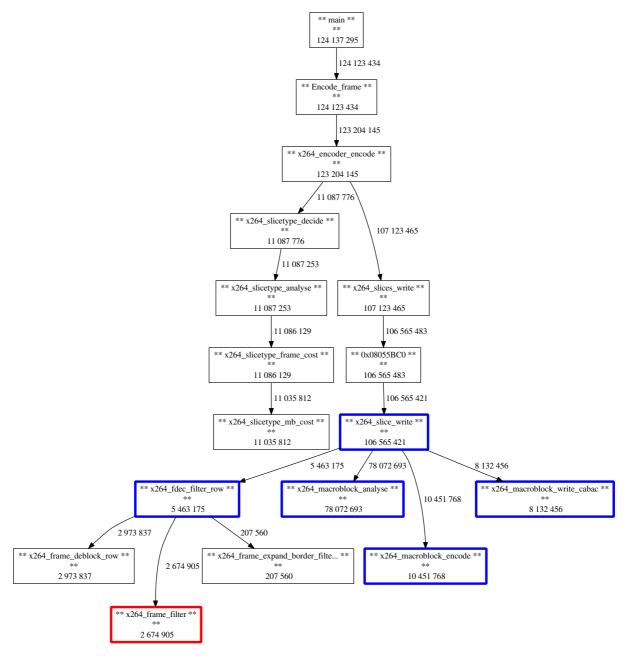

| 6.7        | Profiling graph of x264 main functions during encoding. Numbers are                                                                                                                                                                                                           |           |

|            | absolute cycle estimations                                                                                                                                                                                                                                                    | 56        |

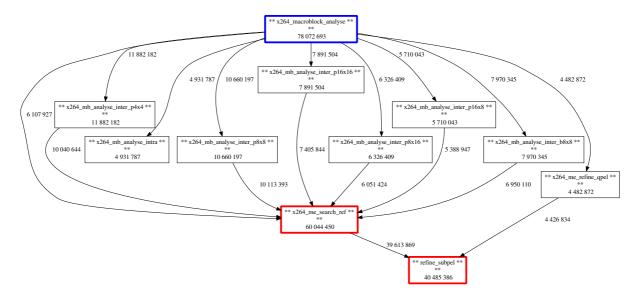

| 6.8        | Profiling graph of x264 analyse stage during encoding. Numbers are                                                                                                                                                                                                            |           |

|            | absolute cycle estimations                                                                                                                                                                                                                                                    | 57        |

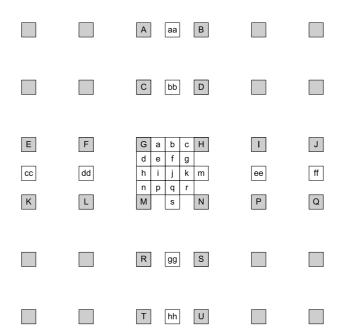

| 6.9        | Half-pixels (b,h,m,s,j) are calculated by interpolation using a 6-tap fil-                                                                                                                                                                                                    |           |

|            | ter. The illustration also shows integer-pixels (upper case), and quarter-                                                                                                                                                                                                    |           |

|            | pixels. Figure from [8]                                                                                                                                                                                                                                                       | 58        |

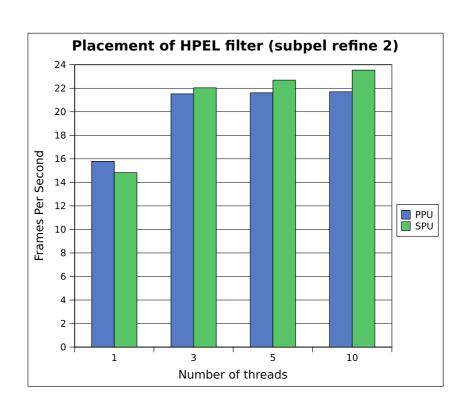

| 6.10       | HPEL filter offloading to SPE using subpixel refine parameter 2                                                                                                                                                                                                               | 63        |

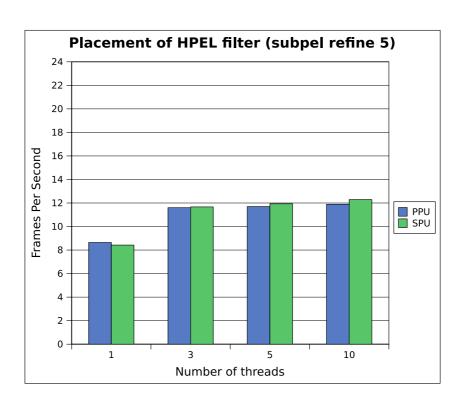

| 6.11       | HPEL filter offloading to SPE using subpixel refine parameter 5                                                                                                                                                                                                               | 64        |

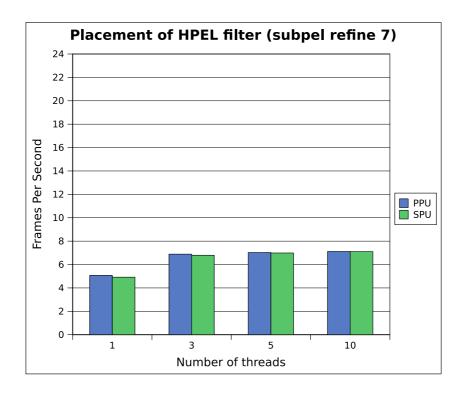

| 6.12       | HPEL filter offloading to SPE using subpixel refine parameter 7                                                                                                                                                                                                               | 64        |

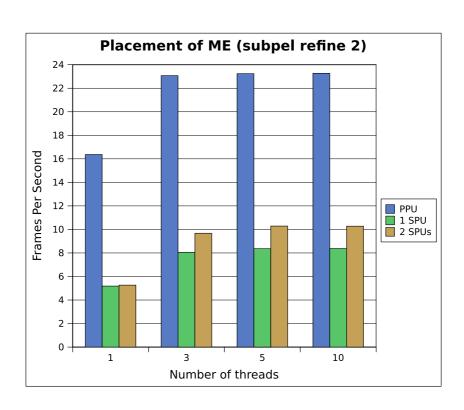

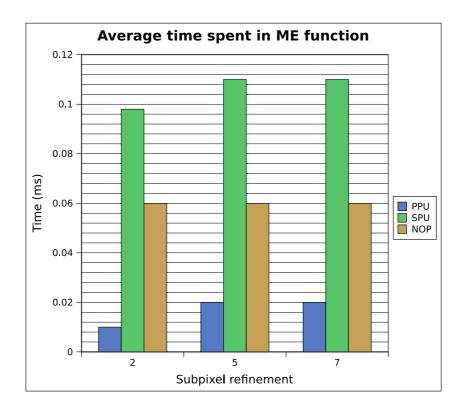

| 6.13       | Motion estimation function offloaded using subpixel refine parameter 2.                                                                                                                                                                                                       | 65        |

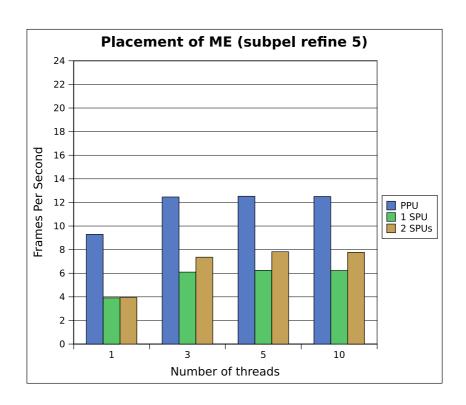

| 6.14       | Motion estimation function offloaded using subpixel refine parameter 5.                                                                                                                                                                                                       | 66        |

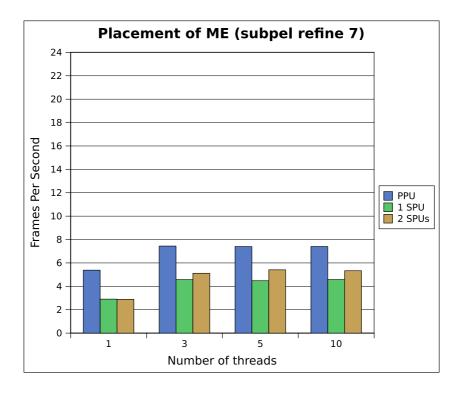

| 6.15       | Motion estimation function offloaded using subpixel refine parameter 7.                                                                                                                                                                                                       | 66        |

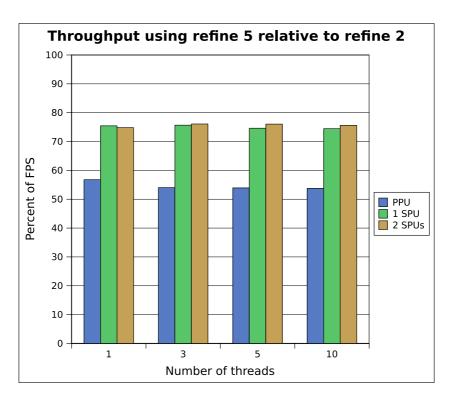

| 6.16       | Relative encoding speed of motion estimation function offloaded using                                                                                                                                                                                                         |           |

|            | subpixel refine parameter 5                                                                                                                                                                                                                                                   | 67        |

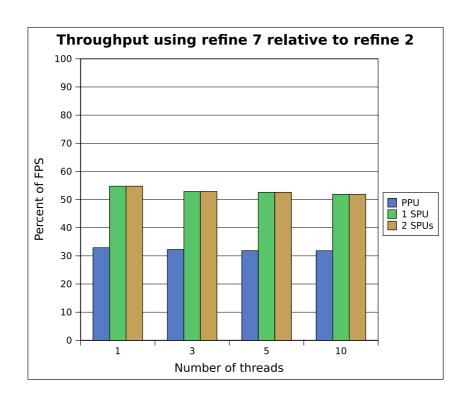

| 6.17       | Relative encoding speed of motion estimation function offloaded using                                                                                                                                                                                                         |           |

|            | subpixel refine parameter 7                                                                                                                                                                                                                                                   | 68        |

| 6.18       | Average time spent in motion estimation search and refine function in-                                                                                                                                                                                                        |           |

|            | cluding job dispatching                                                                                                                                                                                                                                                       | 68        |

## **Preface**

Multi-core processors have become ordinary in modern commodity computers. Computationally intensive applications, like video processing, that previously only ran on specialized hardware, are now common on home computers. However, the demand for more computing power is ever-increasing, and with the introduction of high definition video, more performance is desired. As an alternative to having multiple identical processor cores, heterogeneous multiprocessors have cores with different capabilities. This allows tasks to be processed on simple cores with specialized functionality. The simplicity furthers low power consumption, small die usage, and low price.

Dealing with heterogeneous cores increases the complexity of writing programs for the architecture. The reasons for this includes different capabilities of the cores, and some heterogeneous architectures do not have shared memory. Without shared memory, accessing main memory requires explicit transfers to local memory. In this thesis, we consider two architectures, the STI Cell/B.E. and Intel IXP2400, and evaluate parallelization strategies and performance for real-world problems. Our tests show promising throughput for some applications, and we propose a scheme for offloading computationally intensive parts of an existing application.

# Acknowledgements

I would like to express my gratitude to Håkon Stensland, and Paul Beskow, and my advisors, Carsten Griwodz and Pål Halvorsen. They have all contributed valuable feedback, and without them, this work would not have been possible.

Thanks to the guys at the Simula lab, where I worked during my master studies, for motivation, input, and great conversations.

I will also use this chance to say thank you to my friends and family for always supporting me.

Oslo, July 31. 2008 Håvard Espeland

# **Abbreviations**

AES Advanced Encryption Standard

ASMP Asymmetric Multiprocessing

CBC Cipher Block Chaining Mode of Operation

CBEA Cell Broadband Engine Architecture

CTR Counter Mode of Operation

DCT Discrete Cosine Transform

DES Data Encryption Standard

DMA Direct Memory Access

ECB Electronic Codebook Mode of Operation

EIB Element Interconnect Bus

FIFO First in, First out FPU Floating Point Unit

GPGPU General-Purpose computing on Graphics Processing Units

GPU Graphics Processing Unit

HPC High-performance Computing

HPEL Half pixel

HTTP Hypertext Transfer ProtocolMFC Memory Flow ControllerNAL Network Abstraction Layer

NOP No operation

NPU Network Processing UnitPPE Power Processor ElementPPU Power Processor Unit

PS3 Playstation 3 QPEL Quarter pixel

RTP Real-time Transport Protocol

RTSP Real-time Streaming Protocol

RX Receive

SIMD Single Instruction Multiple Data

SMP Symmetric Multiprocessing

SMT Simultaneous Multithreading

SPE Synergistic Processing Element

SPU Synergistic Processing Unit

TCP Transmission Control Protocol

TFRC TCP Friendly Rate Control

TX Transmit

UDP User Datagram Protocol

# Chapter 1

# Introduction

## 1.1 Background and motivation

Strive for more processing power has been an ever-increasing demand since the introduction of the computer. The number of transistors that are used in a microprocessor has approximately doubled every 24 months, close to what Gordon Moore predicted in 1965, which is now famously known as Moore's Law. For decades, manufacturers have been using multiple processors to meet the demand for increasing computational capabilities. This can be done using a number of computers working together in a cluster configuration, or by using two or more processors in a single system.

Increasing the clock frequency of a CPU is limited by physical properties, and servers with multiple CPUs have been customary. This technique is known as symmetric multiprocessing (SMP), here the operating system treats each core alike. SMP is not a new concept, and was was used at least as early as 1961, when the Burroughs B5000 series mainframe became available with two processors [9]. SMP can be further scaled by clustering processors together near memory, and having multiple clusters. The clusters are able to access all memory directly, but at different latency and bandwidth, depending on how far the cluster operates from the memory. This technique is known as non-uniform memory architecture (NUMA), and allows scaling to many processors in a single system.

In 2001, IBM released the first commercial multi-core processor [10] with two independent cores on a single die. This marked the introduction of multiple CPUs to commodity hardware, and soon after, Intel and AMD also released multi-core CPUs. Multi-core is viewed, from the operating system point of view, as a regular SMP multi processor

system, and applications written using threads can take advantage of them without adaptations.

There are also drawbacks of having multiple CPUs in a SMP configuration, in some architectures the cores share the same bus and memory bandwidth. The shared resources can become exhausted, when the number of cores increase. As a result of this, asymmetric architectures with local storage only available for a limited set of cores have become available. With asymmetric multiprocessing (ASMP), the operating system or application do not treat all cores identically, as done with SMP. This allows some cores to have special functions, limitations, or clock speed. Architectures that have cores with different capabilities, are often called heterogeneous architectures. Kumar et al. [11] performed an evaluation of two processors of the heterogeneous Alpha architecture. They achieved up to 63% better throughput compared to equivalent homogeneous processors occupying the same die area, when performing a set of benchmarks. The smaller die area used by heterogeneous architectures can both lead to reduced power consumption and cost of the processor. It also allows more processing elements to be placed in the die area.

Using co-processors for offloading tasks is an idea used since the beginning of computers. The familiar x86 architecture can use several processors for accelerating tasks, including the MMU for virtual memory, graphics processor for rendering, and network processor for offloading part of the network stack. What has happened in the recent years is the introduction of programmable co-processors which are able to perform general-purpose tasks in commodity hardware. The ability to run programmable shaders revolutionized the graphics processors, which used to have a fixed pipeline in hardware. This also allowed non-graphics related tasks to be executed on the processors. The use of heterogeneous multiprocessors in game consoles also furthers the availability of such architectures.

Heterogeneous multiprocessors are typically configured in such a way that there are a limited number (usually one) of fat cores and many thin cores. The fat cores can be based on existing architectures like PowerPC or ARM, and may run a normal operating system. The fat core's main task is to control a number of thin cores, which are simple, high-performing specialized cores, only capable of doing some tasks fast. Their simplicity makes it possible to have many thin cores on a single die, with a high-speed interconnect, and in some cases access to a shared memory and I/O.

#### 1.2 Problem statement

Because the cores must be treated with regard to the individual core's features and connectivity, programming heterogeneous architectures can be difficult.

The complexity of developing for such architectures varies between platforms, and there is also differences in what types of applications that are suitable, and how to achieve high throughput. We want to investigate how to accelerate programs on two of these architectures, and to evaluate different strategies for parallel execution. Among the issues we investigate in the next chapters are job distribution schemes to accelerate existing projects by offloading CPU-intensive parts from the main processor to processing elements. We also look at strategies for parallelization, and limitations of the heterogeneous architectures.

#### 1.3 Research Contributions

During the master studies, we have published two papers on protocol translation on an Intel IXP network processor [12, 13], released an parallel AES implementation for the STI Cell under the GPL license, and gained valuable insights on how to accelerate computationally intensive applications on heterogeneous architectures. This is, to the best of our knowledge, the first open source AES implementation for CBEA. We have also made progress on the goal of having an open-source H.264 encoder available for Cell, and looked at optimizing the encoder for the architecture without breaking the portability.

#### 1.4 Outline

The rest of this thesis is organized as follows; Chapter 2 introduces the two heterogeneous architectures we use in the evaluations. In chapter 3, we look at our protocol translation proxy, and have a look at the pipelining strategy for processing of network packets on different cores. Chapter 4 looks at a branch-and-bound problem on the Cell architecture, and details how the architecture is programmed. In chapter 5, we investigate parallelization of block cipher encryption on the Cell platform, and in chapter 6, we study video encoding on the Cell platform. Chapter 7 contains the discussion of the results and lessons learned, and the conclusion and further work can be found in

chapter 8.

# Chapter 2

# Heterogeneous multi-core architectures

In this chapter, we look at heterogeneous multiprocessors, and cover details of the architectures. In particular, we look at the two architectures used in the investigations of the next chapters, the Cell Broadband Engine, and the Intel IXP. Also, We highlight features and limitations of the architecture, and some of these will be looked further into during the next chapter's evaluations.

## 2.1 Cell Broadband Engine

The Cell Broadband Engine (CBE) [14] is a heterogeneous multiprocessor developed by Sony, Toshiba, and IBM. It is designed for fields such as high performance computing (HPC), game consoles, and video processing [15].

Figure 2.1: The Cell Broadband Engine multiprocessor (public domain image).

The project was initiated by Sony when they contacted IBM in 2000 and requested a processor with 1000 times the performance of the Playstation 2 Emotion Engine [16] for use in their next generation video game console [17]. As this performance goal turned out to be overly optimistic, the target performance was set to 100 times the Playstation 2 performance, and Toshiba joined as a technology partner. The three companies formed an alliance named STI, and in november 2006, Sony launched the Playstation 3 as the first commercial device embracing the CBE architecture (CBEA). For HPC, IBM and Mercury Computing offer blade servers featuring multiple Cell processors, and Toshiba offers laptops using CBE as an accelerator to offload media processing [18].

#### 2.1.1 Hardware overview

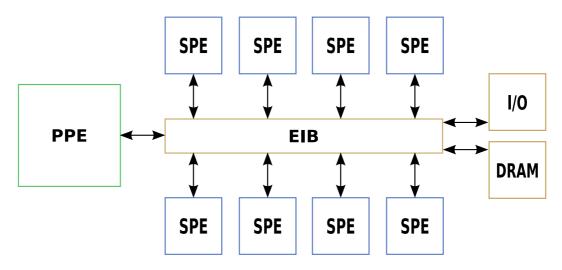

The central components of the CBEA are the Power Processing Element (PPE) and a number of Synergistic Processing Elements (SPE), these are all connected by the Element Interconnect Bus (EIB). The system memory and the Flex IO interface are also connected to the EIB. The Flex IO interface further connects devices such as network interfaces and disk controllers. An overview of the CBEA main components are shown in figure 2.2. The current version of the CBE is clocked up to 3.2 GHz and have 8 SPEs.

Figure 2.2: Main components of the Cell Broadband Engine

The PPE contains a general purpose 64-bit core based on PowerPC 970 (PPU), capable of executing two simultaneous hardware threads, similar to Intel's SMT technology described later. The primary job of the PPE is to control the SPEs, run the operating system, and manage system resources [19]. The PPE supports virtual memory, and features two levels of cache (32 kB level 1 instruction cache, 32 kB level 1 data cache, and 512 kB level 2 unified cache), a branch unit, and a vector (VMX) unit.

The vector unit in the PPE is a standard AltiVec compatible single instruction, multiple data (SIMD) unit. It is capable of processing four independent 32-bit words, eight 16-bit shorts, or sixteen 8-bit bytes, in a total of 128 bits. The unit can work on both integer and floating point values, but not all instructions are available for both types. Using SIMD instructions can improve the throughput in multimedia applications because of the parallel processing on units (see figure 2.4) executed as a single instruction. The SPEs are programmed mainly by SIMD instructions, but they are not AltiVec compatible. The available vector instructions on the PPE and SPEs have different names but are very similar.

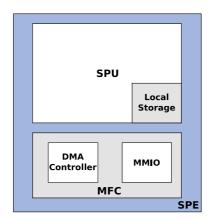

An SPE contains a Synergistic Processing Unit (SPU) <sup>1</sup>, and a Memory Flow Controller (MFC) as illustrated in figure 2.3. The MFC is unable to directly access the system memory, and can only use a small amount of fast local memory, known as the local storage. The local storage is 256 KB large and used for code, data, and stack without segmentation. The Memory Flow Controller passes data back and forth between the system memory and local storage. This is done by Direct Memory Access (DMA) transfers, which can be requested both from SPEs and the PPE. The SPEs have a large 128-entry 128-bit register file and support two simultaneous instructions using two execution pipelines. The instruction set used on SPEs is not PowerPC or PPE compatible, and operates primarily with vector operands.

The SPEs support both single and double precision floating point numbers, although the single precision is not fully IEEE 754 [20] compatible. The range has been extended by removing NaN and Infinity. Rounded numbers are always truncated down towards zero. The reason for this incompatibility is to trade accuracy for speed to better adapt the CBEA for real-time graphics and multimedia processing applications by simplifying the hardware [19].

#### 2.1.2 Communication and synchronization

Programming the CBE often involves synchronization of several parallel tasks. To increase performance, the CBEA includes hardware support for several primitives, including atomic updates, message passing, and signals. The Memory Flow Controller supports atomic operations by DMA, which can be used to implement standard synchronization primitives such as mutexes and semaphores. Message queues for inter-

<sup>&</sup>lt;sup>1</sup>The abbreviations SPE/SPU and PPE/PPU are often interchanged and used ambiguously in literature, and except for in this overview, SPE and PPE will be used, and a strict distinction between element and unit will not be enforced.

Figure 2.3: A Synergistic Processing Element

| o<br>I | 3     | 2 6  | 4 9 | 6 128 |

|--------|-------|------|-----|-------|

|        | 4096  | 730  | 128 | 12    |

| *      | 3     | 3    | 3   | 4     |

| =      | 12288 | 2190 | 384 | 48    |

Figure 2.4: An example SIMD multiplication of two 128-bit vectors containing four 32-bit integer values. The multiplications are computed in parallel by a single instruction.

communication between the PPE and SPEs, and internally among the SPEs, are also available. Similarly, SPEs and the PPE can send signals, which together with messages are received either by polling, or by using an interrupt handler.

#### 2.1.3 The Playstation 3 and Linux

The Playstation 3 uses a Cell multiprocessor clocked at 3.2 GHz, which can run Linux as an alternative to Sony's default operating system used for gaming. The featured processor is somewhat limited, when compared to a fully fledged CBE. One SPE is removed to get better yield in the production process, and one is reserved for a hypervisor, leaving six SPEs available for usage. The system has 256 MB of memory, with about 40 MB reserved by the hypervisor. The hypervisor also blocks access to certain parts of the hardware, including the graphics processing unit (GPU).

Both IBM and Sony are actively participating in improving the CBEA Linux support. Developers can fully utilize both the PPE and SPEs. Both have context switching abilities, including preemptive scheduling (SCHED\_OTHER) for the SPEs. IBM also provides a cycle accurate, full system simulator for the CBEA, which can be used if suitable hardware is not available, and to aid debugging.

The CBE can be programmed using the standard gcc compiler to target both SPEs and the PPE. As an alternative, IBM provides the proprietary compiler XL. Accessing the SPEs from userspace in Linux is abstracted by the spufs [21] virtual file system, which provides the low level interface. Spufs is then used by gdb [22] and the libspe2 [23] runtime library for controlling the SPEs from the processes. The spufs virtual file system exposes the local storge, mailboxes, signals, DMA, execution state, and more to user space. It can be used to read resources and manipulate them directly. Before running a program on a SPE, the bytecode is uploaded to local storage using the libspe2 library, and is started by sending a signal.

#### 2.1.4 Performance tuning

Successfully mapping a larger problem to the CBE can be a significant task. To fully utilize the computational capability of the CBE, the programmer must explicitly control all the resources on the processor. In particular, there is a need for strict data segmentation to fit relevant data in the local storage, and most importantly, avoid stalling the SPEs. Making sure the SPEs always have work pending includes hiding DMA latency, reducing synchronization overhead, eliminating branch misses, and optimizing for cache.

Hiding DMA latency is often accomplished by using multiple buffers, usually double buffering. This allows the SPE to work on a dataset while copying another. Reducing branch misses are especially important on SPEs, because of the lack of dynamic branch prediction. Writing branch free code is possible in many cases, and further speedup can be achieved by unrolling loops and hinting the processor on the likely outcome of branches. A good cache usage can make a big difference as well, i.e., DMAing to or from a non-aligned or non-multiple size of a cache line (128 B), yields a performance penalty.

A few components normally found in other processors are left out of a SPE to save power and cost. This includes above mentioned branch prediction and support for out-of-order execution. Instead, the compiler or the programmer is expected to take care of these issues. A special branch hint instruction is supported to guide the processor and reduce misses. Branch misses on the SPEs are extremely expensive. Correctly predicted branches run in a single cycle, while a mis-predicted branch cost up to 18 or 19 cycles depending on the address of the branch target. Furthermore, since the CBE uses an in-order execution model, shuffling instructions can provide a performance boost by avoiding pipeline stalling. Also, up to two instructions can run in parallel if

they are compatible, and the data they work on is independent.

In an attempt to simplify programming, IBM developed an prototype auto-parallelizing compiler optimized for the CBEA, known as the OctoPiler. This compiler aims at reducing the complexity of using the architecture for novice programmers by automatically optimizing alignment, scalar operations by SIMD, and threads by SPEs. Eichenberger et al. claims in [24] that using IBM's Octopiler compiler increases productivity, and presents promising measurements compared to code not optimized for the CBE. He does not compare performance to hand written optimizations. On the contrary, Greene [25] recommends turning off all compiler optimizations (both on IBM's XL and the gcc compiler) and doing the optimize work manually to generate acceptable SPE code.

Another project for automatic parallelization is the Parallel For project [26], which targets multiple platforms including CBEA. The Parallel For project does automatic parallelization by analyzing dependencies in sequential code, and distribute the work to SPEs. Parallelizable loops are marked in a similar manner as OpenMP, resulting in generated PPE and SPE code. Zumbusch, the author of Parallel For, benchmarked smoothing of a multigrid in [27] using Parallel For compared to various SMP architectures and got decreasing execution time when using multiple SPEs. The SPE results does not scale as well as the SMP benchmarks. He argues that the performance is limited by the local memory size.

#### 2.1.5 Parallelization schemes

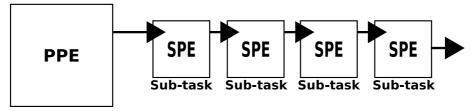

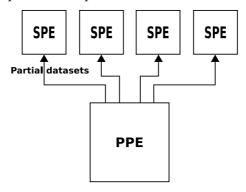

Traditional parallelization concepts, such as pipelining and data partitioning, are applicable on the CBEA (illustrated in figure 2.5), although they require consideration due to the non-shared memory architecture. The complicated part is to efficiently partition the data between parallel tasks, while keeping the amount of synchronization overhead to a minimum.

Several problems require steps to be completed sequentially, and some programs may benefit from a hybrid approach, where the main strategy is pipelining, while some parts of the code may gain an advantage by doing data partitioning on multiple cores. In the case where there are more SPE tasks than available cores, a scheduler is needed.

An SPE task is called an SPE context in Linux, and describes the complete SPE state for a running or suspended SPE task. Several scheduling policies are available in Linux including preemptive scheduling (SCHED\_OTHER) and FIFO scheduling (SCHED\_FIFO).

(a) A pipelining strategy where the data passes through several cores to solve sub-tasks, ending up with a complete solution.

(b) A parallelization strategy where data is partitioned and each partition is processed on a single core.

Figure 2.5: Common parallelization strategies

The current preemptive SPE scheduler runs every 100ms, and hands out time slices rewarding execution time to contexts with high priority. The FIFO scheduler uses a voluntarily model, where the context can be given full SPE control when it has work pending, or otherwise yields, and let another context run. The preemptive policy may not be suitable when overbooking the SPEs, since the scheduler is unaware of when a context has work pending, thereby giving execution time to idle contexts. The FIFO scheduling policy keeps threads running until they yield voluntarily, giving the programmer more explicit control of the scheduling.

Spawning more threads than available cores can make sense for at least two reasons; Several processes may be sharing the same CBE, and the type and amount of work the CBE has to perform on the data may vary. However, a trade-off with running more threads than available processing elements, is a possible performance penalty, because of the context switch and scheduling overhead. Writing programs in such a way can also turn out to be an advantage, since newer models of the CBE family, or alternative platforms, may have more cores available, making the code portable with a small effort.

#### 2.1.6 Comparison to x86 symmetric multi processors

The x86 architecture supports symmetric multiprocessing (SMP), using more than one CPU socket, and recently also multiple CPU cores per socket. Intel also supports simultaneous multithreading (SMT) on some of its processors, this is known as Hyper-Threading. HyperThreading presents two virtual processors for every physical core to the operating system. Processes can be scheduled to both, and the CPU itself will perform context switching between them, allowing otherwise wasted cycles during stalls to be utilized.

The CBEA is different in key factors compared to the Intel x86 architecture. The two major differences are the heterogeneity of the cores, and the non-shared memory architecture with an exclusive local storage on each SPE. Data locality is an important issue on SMP as well, because of cache coherency, but scattered memory usage requires more attention on non-shared memory architectures. The heterogeneity of the cores leads to more complex development, where multiple compilers, and duplication of code is necessary to communicate between different types of cores..

Not all problems scale well on the CBEA compared to the x86 architecture. These are mainly related to the limitations of the hardware, covering scalar problems, branching problems, and problems with low data locality. Since the SPEs are vector processors they do not show their full potential processing scalar data. Good use of background DMA transfers and prefetching can mitigate the penalty of not having shared memory. Although some of these cases may also be troublesome on the x86, the added complexity of non-shared memory and large branch misprediction penalty is avoided.

### 2.1.7 Potential and applications

Williams et al. [28] have investigated the potential of the CBEA for scientific computing and conclude that the potential is tremendous for both single and double precision calculations. The slower double precision, compared to single precision speed is a limitation, but not a show-stopper. In [29], Buttari et al. report on using Playstation 3 nodes for scientific computing and describe several limitations, including limited main memory access speed and size, and the relatively slow gigabit ethernet adapter, compared to the processing speed. They conclude that the attractiveness for scientific computing on the Playstation 3 will depend on the application's characteristics.

In 2005, Sakai et al. [30] gave a keynote speech about performance evaluation of the CBE at Toshiba. They used a MPEG-2 to H.264 transcoder as an example application,

running 2 simultaneous encoders each using 3 SPEs. In addition to the standard CBE optimization techniques, they discovered that bandwidth reservation between the encoders was necessary to avoid over-utilizing the system bus. Unfortunately, very few details are available in slides from the keynote, and apparently no paper was published.

## 2.2 IXP 2400 Network processor

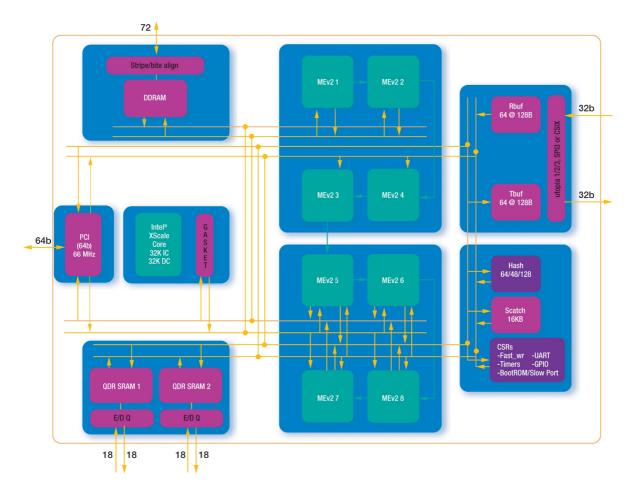

The IXP2400 chipset [31] is a second generation, highly programmable network processor (NPU) and is designed to handle a wide range of access, edge and core network applications. The basic elements include a 600 MHz XScale (ARM compatible) core running Linux or VxWorks, eight 600 MHz special packet processors called microengines ( $\mu$ Engines), several types of memory and different controllers and buses.

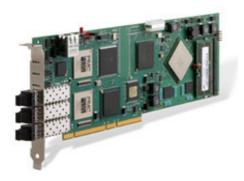

Figure 2.6: ENP-2611 from RadiSys with an IXP2400 Network Processor. The ENP-2611 is a PCI-X card working independently of the host computer. It allows DMA transfers to and from the host computer using the PCI bus.

With respect to the different CPUs, the XScale is typically used for the control plane (slow path), while the  $\mu$ Engines perform general packet processing in the data plane (fast path). The three memory types are used for different purposes, according to access time and bus bandwidth, the 256 MB SDRAM is used for packet store, the 8 MB SRAM for meta-data, tables and stack manipulation, and the 16 kB scratchpad (on-chip) for synchronization and inter-process communication. The physical interfaces are customizable, and can be chosen by the manufacturer of the device on which the IXP chipset is integrated. The number of network ports and the network port type are also customizable.

The major functional blocks of the IXP2400 architecture are shown in figure 2.7. The

Figure 2.7: IXP2400 architecture overview. The figure is from an Intel product brief on IXP2400 [1]

$\mu$ Engines are grouped together in clusters of four, which can communicate by next-neighbour registers internally. In normal configurations, two  $\mu$ Engines are reserved for low-level network receive and transmit functions, leaving six  $\mu$ Engines available for application usage.

The SDK includes a specialized C compiler for the MicroC language, in which the  $\mu$ Engines can be programmed. MicroC is a C-like language allowing rapid development and reuse of code. Synchronization and message passing between the cores can be performed as atomic operations on dedicated hardware channels known as scratch rings. Using a NPU for a network application allows processing on network wire speed, in the case of the IXP2400, up to 2.5 GBps, with very low latency [1]. Such performance can be achieved due to the dedicated architecture for network processing, and software implementation. Packet processing can be done with a limited protocol stack, allowing minimal processing overhead both for extracting information and updating network packets. This makes network processors ideal for high-performance,

low-complexity network operations like statistics collection, deep packet inspection, or packet rewriting.

#### 2.3 Other architectures

#### 2.3.1 Graphics Processing Units

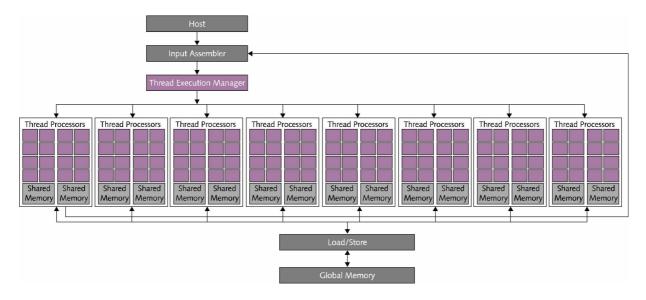

Graphics processing units (GPUs) are available in most commodity PCs, and the last generation are highly programmable. These includes recent graphics cards from AMD and nVIDIA. The GPUs are designed for graphics processing, but can provide a high performance for many computational intensive applications, known as general-purpose computing on graphics processing units (GPGPU). The traditional approach of using GPUs for general purpose applications has been to write vertex and fragment shaders using a specialized graphics API (OpenGL / DirectX). This imposed limitations, and in late 2006, ATI announced the Close-To-Metal [32] framework for GPGPU. Three months later, nVIDIA announced its GPGPU framework, CUDA [33].

The first generation of GPUs supporting CUDA was the G80 series from nVIDIA. The high-end G80 card Geforce 8800 GTX has 128 stream processors (also known as thread processors), organized as illustrated in figure 2.8. The stream processors have single-precision FPUs, and clusters of eight cores share a local memory of 16 kB. Each of the stream processors can handle up to 97 concurrent threads, and developers using the platform are expected to write applications using thousands of threads to get good performance.

Controlling such a large number of threads explicitly would render programming for the platform cumbersome. Instead, the CUDA framework uses a thread manager that dispatches and manages threads based on compiler directives. The programming language used is based on C, but with additional CUDA extensions.

GPUs can provide high throughput for computationally intensive applications that are suitable to the programming model required by the architecture. Schatz et al. [34] demonstrated that using an nVIDIA Geforce 8800 GTX, they could achieve a speedup of 3.79x compared to a similarly priced 3.0 GHz Xeon processor, when doing sequence alignment of DNA. The protein folding project Folding@Home [35] provides GPGPU clients for both nVIDIA and AMD cards. Another computationally intensive task that was successfully accelerated by a GPU is Reed-Solomon coding for use in RAID 6 disk

Figure 2.8: nVIDIA G80 architecture overview from [2]

systems by Curry et al. [36]. Their evaluations show that the GPU can outperform a modern CPU by an order of magnitude for this problem.

## 2.4 Summary

In this chapter we have presented an overview of the heterogeneous multi-core architectures STI Cell Broadband Engine and Intel IXP2400. Such architectures can deliver significant computational capabilities compared to traditional SMP in several fields. Unfortunately, utilizing the performance of these architectures leads to much extra work for the programmer, who has to be aware of how to structure the programs, considering the memory architecture and hardware limitations. Automatic tools for partitioning and memory management do exist, however they do not seem to be sufficient in areas where performance is first priority, like high performance computing or games.

In the next chapters, we consider some of the challenges and potential introduced here, and look at how this relates to programming for these architectures. This will be evaluated by implementations and benchmarks, both by adapting existing programs, and by writing from scratch. In chapter 3, we use a pipline scheme for processing packets on a network processor. In chapter 4, we introduce programming on the CBE, and compare the throughput of a branch-heavy application on SPE and PPE. In chapter 5, we introduce job dispatching of independent datasets, and look at what mechanism works best for distributing jobs, when the PPE is under heavy load. In chapter 6, we use what we

have learned from the previous chapters, when offloading computationally intensive parts of a video encoder to SPEs.

# **Chapter 3**

# Protocol translation on Intel IXP network processor

In this chapter, we introduce a network protocol translating proxy for use in video streaming. The proxy is transparent, implying that both the client and server are unaware of its presence. It can be placed either near the client or the server, depending on the network link quality and the desired effects.

The proxy is implemented on the IXP asymmetric multi-core processor, and details of this proxy and network effects are available in our papers [12] and [13]. Some of the network related details presented in the papers are beyond the scope of this thesis, and we limit ourselves to present only the relevant details here.

This chapter is organized as follows; In section 3.1, we provide the background and motivation for deploying such a proxy. Section 3.2 contains an overview of the implementation of the proxy and some of the results from our network performance evaluations. In section 3.3 we look at what lessons that can be learned from this implementation.

## 3.1 Background information

The discussion about the most suitable protocols for streaming has been going on for years. Initially, streaming services on the Internet used UDP for data transfer, because multimedia applications often have large demands for bandwidth, reliability and jitter than could not be offered by TCP. Today, this approach is prevented by filters in Internet service providers (ISPs), firewalls in access networks and on end-user systems.

Figure 3.1: Network packet flow of the protocol translation proxy.

Some ISPs reject UDP because it is not fair against TCP traffic, and many firewalls reject UDP because it is connectionless and requires too much processing power and memory to ensure security. It has therefore become fairly common to use HTTP-streaming, which delivers streaming media over TCP. The disadvantage is that the end-user can experience playback hiccups and quality reductions because of the probing behavior of TCP, leading to oscillating throughput and slow recovery of the packet rate. A sender that uses UDP would, in contrast to this, be able to maintain a desired constant sending rate. Servers are also expected to scale more easily when sending smooth UDP streams and avoid dealing with TCP-related processing.

To exploit the benefits of both TCP and UDP, we experiment with a proxy that performs a transparent protocol translation. This is similar to the use of proxy caching that ISPs employ to reduce their bandwidth. We aim at live protocol translation in a TCP-friendly manner that achieves a high perceived quality to end-users. Our pro-

totype proxy is implemented on an Intel IXP2400 network processor and enables the server to use UDP at the server side and TCP at the client side as illustrated in figure 3.1. The proxy also supports load-balancing of clients to a cluster of servers.

## 3.2 Implementation

The protocol translation proxy uses the XScale core and one  $\mu$ Engine application block. In addition, we use two  $\mu$ Engines for the receiving (RX) and the sending (TX) blocks. The transport protocol translation operation is shown in figure 3.1. According to the intended use of the different processors, incoming packets are classified by the  $\mu$ Engine based on the header. RTSP and HTTP packets are enqueued for processing on the XScale core (control path) while the handling of RTP packets is performed on the  $\mu$ Engine (fast path). TCP acknowledgements with zero payload size are processed on the  $\mu$ Engine for performance reasons.

The main task of the XScale is to set up and maintain streaming sessions, but after initialization, all video data is processed (translated and forwarded) by the  $\mu$ Engine. The proxy supports only a partial TCP/IP implementation, covering basic features. We do this to save both time and resources on the proxy. In our proxy, the protocol translation is performed by replacing headers (see figure 3.2). The translation reuses the space holding the RTP and UDP headers for the TCP header. It updates only the checksum and protocol number in the IP header before forwarding the packet. To deal with congestion control and fairness, we use TFRC [37], which is a specification for best effort flows that compete for bandwidth. The rate control is performed on a  $\mu$ Engine using fixed point arithmetics, and packets in excess of this rate are dropped.

The parallel approach used is a type of pipelining strategy, where a packet travels from core to core until transmitted. By only doing part of the work on each core, the level of load on the cores is reduced. We did not benchmark the scalability or utilization of the cores in our experiments, because the streaming server used could not handle more than a few connections. The proxy was designed in such a way that extra  $\mu$ Engines could be added in the pipeline for further scalability, if deemed necessary. This can be done by adding forward engines, which use the same channels for communicating with RX, XScale, and TX. The forward engines would work almost independently, by only sharing a common per-stream state in SRAM.

Figure 3.2: RTP/UDP to HTTP/TCP Translation

#### 3.2.1 Network performance

We tested the proxy under different conditions of varying network latency (0-200ms) and drop rate (0-1%) by using a network emulator. These, and even harsher conditions are observed on the Internet [38]. Figure 3.3 shows examples of packet dropping between the server and the proxy. Dropping packets between the proxy and client has similar results. Figure 3.3(a) and 3.3(b) show the respective average throughput for HTTP and protocol translation scenarios under a constant loss rate of 1%. Keeping the link delay constant gives similar results. From the figures, we see that protocol translation achieves an average throughput that is hardly affected by link delays. In contrast, if using TCP end-to-end, the performance drops with an increasing loss rate and link delay, and the bandwidth oscillates heavily.

Using a network processor for implementing this proxy enables forwarding packets in the range of microseconds whereas typical existing systems require several milliseconds. The low overhead is caused by the minimal processing of network packets that does not have to traverse a network stack nor being copied to userspace when forwarding. The  $\mu$ Engines accesses the incoming packets directly, by only updating the changed packet headers. The XScale is used for session management, and only a few packets in every stream are processed on it. Since more  $\mu$ Engines are available, it is possible to use multiple forwarding cores, working in parallel. Benchmarks of scalability and core utilization were not within the scope of the papers, and are left as

Figure 3.3: Achieved bandwidth varying link latency with 1% loss

further work.

### 3.3 Lessons learned

The hardware-near approach on the IXP using no protocol stack delivers high throughput and low latency. Similar performance and transparency using a regular network card in a host PC, without overriding the network stack by writing applications as kernel modules seems unlikely. There is also an issue of overhead, since the host PC is not designed for low latency network applications, however, writing such programs on a network processor provides some interesting challenges.

The XScale processor runs both an operating system and a full protocol stack. This stack should not be used for the dataplane in high performance networking applications, as this would eliminate the advantage over a standard network card. Instead, it can be used for debugging and monitoring subsystems.

Network proxies like ours that manipulates packets, need a protocol implementation running on the  $\mu$ Engines. There are open source TCP/IP stacks available (e.g. uIP [39]) that are written for general embedded systems, but to reduce the processing overhead to a minimum, we implemented our own for this proxy. This gave us great flexibility in manipulating TCP behaviour, including the retransmission and congestion control mechanisms.

The pipeline strategy chosen allowed almost all packets to stay on the fast path. The only packets sent to the XScale by the control path were the session setup packets, initializing a session state in shared memory. The pipeline strategy uses, allows all packet

processing to be done without synchronization primitives, even though multiple cores work on the same data in shared memory. The receive and transmit core never access the session states, since they only understand raw network frames. The XScale control processor, is the only core creating and deleting sessions, and after the initial session setup, it does not access session state until deletion. After this, all packets of this session stay on the fast path, and the session is handeled by only one forwarding engine. The use of a lock-free pipeline furthers throughput, since no time is spent waiting for acquiring locks.

The protocol state in shared memory of the IXP allows easy addition of more forwarding engines working in parallel. Distributing the incoming packets to the forwarding engines can be done in a simple round-robin schemes (which would require synchronization), or by more sophisticated schemes like adaptive load sharing [40]. The latter scheme assigns connections to forwarding engines based on the load of each engine, in such a way that packets from a connection in most cases are processed on the same  $\mu$ Engine. This is an advantage, otherwise packets from the same session processed in parallel would have to wait for the  $\mu$ Engine to acquire a lock on the session state.

# 3.4 Summary

In this chapter we have looked at the implementation of a protocol translating proxy running on a network processor. The proxy allows smooth video streaming on unreliable network scenarios, and uses three  $\mu$ Engines and the XScale processor on an Intel IXP network processor card. The use of multiple cores in a pipelining scheme and the hardware-near architecture of the network processor allow low latency and high throughput.

# Chapter 4

# *n*-Queens Problem

In this chapter, we use the Cell Broadband Engine to generate solutions to the n-queens problem using a branch-and-bound algorithm. The chapter briefly looks at the necessary steps of using libspe2 to start SPE threads. We also investigate how fast the algorithm runs on the PPE compared to an SPE. The lack of dynamic branch prediction on SPEs should impact the throughput of this algorithm. The results are also compared with an implementation running on x86.

Figure 4.1: An example solution to the eight queens puzzle. Image from wikipedia [3]

This chapter is organized as follows; In section 4.1, we introduce the n-queens problem. Section 4.2 outlines the algorithm used, and we look at the details of running an SPE thread on the CBEA. In section 4.2.2, we present benchmarks of the implementation, and evaluates the results. In section 4.3, we look at the lessons learned.

# 4.1 Background Information

The n-queens problem is a generalization of the famous eight queens chess puzzle, where the player must place n hostile queens on an n x n chess board without any of the queens being able to take out another queen in one move. An example of a valid solution for an  $8 \times 8$  board is shown in figure 4.1. The 8 queens problem has 92 distinct solutions, with most of them being symmetries, leaving a total of 12 unique solutions.

# 4.2 Adaptation for Cell

### 4.2.1 Implementation

Our implementation finds all unique solutions to the problem by using what is known as Wirth's algorithm [41]. The algorithm is of the class branch-and-bound, and permutates the board to all legal solutions. This is done by having three bit vectors representing horizontal, vertical and diagonal placement of queens. Combined, these three vectors represent the current state of the board, and placing a queen is a matter of setting the appropriate bits in the vectors representing the now illegal positions for a new queen. To check if a position is valid, a bitwise AND of the vectors gives a new vector of legal positions. To speed up execution, several constraints are introduced to avoid using time searching for known symmetries. The most obvious constraint is to only place the first queen in the upper half of the board, more constraints are honoured, but are not relevant for this overview.

The parallel approach is very simple; Each processing element gets a set of start positions in the first row, and is asked to find all unique solutions given placement of the first queen. This is not optimal, since it only scales to a number of cores limited by  $\lceil n/2 \rceil$ . It also means that the amount of work given to each core may be uneven, depending on the number of cores and the size of n. A better approach would be to split the problem space evenly by providing start positions for more queens.

Listings 4.1 to 4.5 show how an SPE job is dispatched on the PPE, and listing 4.6 displays the control set of operations running on the SPEs. The listings are from the *n*-queens implementation, but are modified to ease readability.

In listing 4.1 the data structures are set up. spu\_params is shared to the SPEs, hence the 16 byte alignment. The binary of the compiled SPE code is loaded on line 7. The desired number of SPE contexts are created, and loaded binary is associated with the

contexts. The running PPE thread is given a FIFO scheduling policy, meaning that they are not preemptively scheduled out until voluntarily yielded.

```

pthread_t sputhread[num_threads];

struct thread_arg arg[num_spus];

struct queen_params spu_params[num_threads] __attribute((aligned

(16)));

createflags = 0;

unsigned int

5

spe_program_handle_t* program = spe_image_open("spu_queen");

for (i=0; i < num\_spus; ++i) {

arg[i].queen_args = &spu_params[i];

10

arg[i].spe = spe_context_create(createflags, 0);

11

spe_program_load(arg[i].spe, program);

12

}

13

14

sched_setscheduler(getpid(), SCHED_FIFO, 0);

15

```

Listing 4.1: Parameter setup

The next step is job distribution in listing 4.2. The distribution is very coarse, as explained earlier, with the start positions spread among the threads.

```

int remain = N.HALVED;

int startpos = 0;

for (i=0; i < num_threads; ++i) {

spu_params[i].startpos = startpos;

spu_params[i].num = remain / (num_threads - i);

spu_params[i].N = N;

remain -= spu_params[i].num;

startpos += spu_params[i].num;

}</pre>

```

```

/* Get the rest */

spu_params[num_threads - 1].num += remain;

```

Listing 4.2: Job distribution

In listing 4.3, the threads are given FIFO scheduling policy to avoid them being scheduled out when using more SPE contexts than the available SPEs. Instead, a blocked SPE context will wait until another SPE finishes before starting. Each SPE context needs a thread to run in, and we use regular pthreads for this. The thread runs as long as the SPE context exists, and the code to start it is listed in 4.4. After started, the threads will wait until they receive a signal to synchronize the work.

```

pthread_attr_t attr;

pthread_attr_init(&attr);

pthread_attr_setschedpolicy(&attr, SCHED_FIFO);

for (i=0; i<num_threads; ++i) {</pre>

ret = pthread_create(&sputhread[i], &attr, run_queen_spe, &

arg[i]);

if (ret) {

perror("pthread_create");

exit(1);

11

}

}

13

/* Send start signal */

15

for (i=0; i < num\_spus; ++i)

16

spe_signal_write(arg[i].spe, SPE_SIG_NOTIFY_REG_1, 2);

17

```

Listing 4.3: Thread creation and start signalling

```

void *run_queen_spe(void *thread_arg)

int ret;

struct thread_arg *arg = (struct thread_arg*) thread_arg;

```

```

unsigned int entry = SPE_DEFAULT_ENTRY;

spe_stop_info_t stop_info;

ret = spe_context_run(arg->spe, &entry, 0, arg->queen_args, 0, & stop_info);

if (ret < 0)

perror("spe_context_run");

return ret;

}

</pre>

```

Listing 4.4: Starting an SPE

When a SPE finishes the work, a message is sent by a mailbox to the PPE. The PPE waits until it receives a message from all SPE contexts as listed in 4.5. This method of receiving mailbox messages is poll-based. Another approach is to create an event thread, and enable interrupts to be raised when a message is received.

```

int work_left = num_spus;

unsigned int val;

while(work_left) {

usleep (50000);

for (i=0; i < num\_spus; ++i) {

if (spe_out_mbox_status(arg[i].spe)) {

spe_out_mbox_read(arg[i].spe, &val, 1);

fprintf(stderr, "Spe_%d:_Received_mbox_%d\n", i, val)

-work_left;

10

}

11

}

12

}

13

```

Listing 4.5: Shutdown sequence

In listing 4.6, the SPEs start by waiting for a signal. When received, they DMA the parameters pointed to by the argp variable sent to main. All DMA operations are asyn-

chronous, and are identified by a tag. spu\_mfcstat on line 17 waits for the operations tagged to complete. When the parameters are received, the SPEs calculate the number of unique solutions given the start positions. When done, the result is DMAed back to main memory. After this operation is complete, the SPE use the mailbox to notify the PPE of its completion.

The SPE code is compiled using a version of gcc targeting the SPU instruction set, known as spu-gcc. The resulting binary can be embedded in the executable in a dedicated section, or as in this example, be loaded as a separate file at runtime.

```

int main (unsigned long long spe, unsigned long long argp, unsigned

long long envp)

{

int tag = 1;

struct queen_params params;

do {

/* wait until start */

} while(!spu_readchcnt(SPU_RdSigNotify1));

spu_readch(SPU_RdSigNotify1);

10

11

/* Get meta */

12

spu_mfcdma64(&params, mfc_ea2h(argp), mfc_ea2l(argp),

sizeof(struct queen_params), tag, MFC_GET_CMD);

spu_writech(MFC_WrTagMask, 1 << tag);</pre>

spu_mfcstat(MFC_TAG_UPDATE_ALL);

17

unsigned int startpos = params.startpos;

19

20

N = params.N;

21

N_{-}MIN_{-}1 = N - 1;

22

N.HALVED = (N >> 1) + (N & 1);

23

24

unsigned int num_solutions = 0;

25

26

int i;

27

for (i=0; i<params.num; ++i)

28

```

```

num_solutions += partial_findqueen(startpos + i);

29

}

30

31

spu_mfcdma64(&num_solutions, mfc_ea2h(argp), mfc_ea2l(argp),

32

4, tag, MFC_PUT_CMD);

33

34

spu_writech(MFC_WrTagMask, 1 << tag);</pre>

35

spu_mfcstat(MFC_TAG_UPDATE_ALL);

36

37

unsigned int mb_value = 1;

38

spu_writech(SPU_WrOutMbox, mb_value);

39

40

return 0;

41

42

```

Listing 4.6: The main function on the SPEs

#### 4.2.2 Evaluation

Figure 4.2: Benchmark of the n-queens problem using n=16. Lower is better.

The n-queens implementation was benchmarked on a PS3, and a dual core AMD Athlon X2 4200+ using various configurations of threads and SPEs. The results from

Figure 4.3: Benchmark of the n-queens problem using n=17. Lower is better.

n=16 and n=17 are shown in figure 4.2 and 4.3. The first, and most important observation from the graphs is the time spent solving the problem using a single SPE and a single PPE. For the 16-queens problem, calculating the solution using only a PPE thread take 43.6 seconds, while doing the same with a single SPE requires 72.5 seconds. Since our implementation does not use any dynamic job distribution, dispatch overhead is low. The large difference in performance is likely related to the lack of dynamic branch prediction, as this solution is based upon a branch-and-bound algorithm. On the x86, we benchmarked up to three threads, and compared that with the PS3 results. A single thread on x86 ran faster than on the PPE, and about twice as fast as an SPE thread.

The scalability on CBEA suffers a bit from the coarse split of work where each thread only gets a start position, and the number of rows to inspect. This leads to the jagged reduction of time with regard to the number of processing elements. In the case where the number of starting positions is non-dividable by the number of cores, one or more cores will get extra work compared to the others, and since we only split on the first start position, the other threads will idle until finished. This can be seen in the graphs by looking at the 2 PPE series, where in 4.2, we only take full advantage of 4 SPEs, and 5 SPEs in 4.3. For n=18 (not graphed), the number of starting positions is identical to n=17, and for n=19 all six SPEs should by utilized. As an effort to mitigate the effect of non-even distribution, we also tried over-booking the SPEs by using an 7th SPE. It

is scheduled using Linux' SCHED\_FIFO, meaning that it will only get execution time when one other SPE thread finishes. In 4.2 this provided the same execution time using only SPEs compared to dual processing on PPE and SPE. When increasing the number of starting positions (n=17, n=18), using only SPEs was not as fast as the combined approach. The scalability of the implementation is almost linear with regard to the number of SPEs used as long as there are enough starting positions available to evenly distribute among the processing elements.

### 4.3 Lessons learned

The algorithm used in this implementation required very little memory, with only three vectors to represent a state, and it fits into local storage with ease. The algorithm requires no synchronization or shared state, and is therefore well suited for architectures with many cores. With regards to SIMD usage for this problem, we have not considered if this is possible, and this is left as further work.

By evaluating the time spent for finding the number of solutions to the n-queens problem on SPE, PPE, and x86, we have an indication of the performance for branch heavy programs. For this type of application, an SPE provides a lower throughput than the PPE. However, the power of multiple SPEs is much higher than the PPE. We have also shown that even though this type of problem is not optimal for the CBEA, the combined throughput of the SPEs and PPE on the Playstation 3 are still faster than a dual core Opteron when running our implementation.

# 4.4 Summary

We have briefly looked at the *n*-queens problem, and outlined an branch-and-bound algorithm to solve it. The algorithm to calculate the number of unique solutions to the problem was implemented on the CBEA and x86. We have also benchmarked how an SPE thread is started, and how to distribute initial parameters to them. The implementation was then benchmarked on CBEA and x86. The *n*-queens problem is very simple, and the parallel strategy presented is not optimal, however, the benchmarks gives an indication of how the SPEs perform compared to the PPE and other platforms when branching is of importance.

# **Chapter 5**

# **Advanced Encryption Standard**

In this chapter, we parallelize the block cipher encryption algorithm AES. We split the work into job units, and focus on the job dispatching task of parallel programming. We benchmarked the scalability of throughput, when using different models for job dispatching.

Since the AES algorithm itself is not the subject of our investigation, we base our work on an existing single-threaded implementation of AES for x86, and do not explain details of the algorithm. To adapt the implementation for parallel processing, we designed a job dispatching framework suitable for PPE, SPE, and x86 usage. The scalability of job distribution is later evaluated.

The chapter is organized as follows; In section 5.1, we give an overview of the AES algorithm and modes of operation. Section 5.2 introduce the implementation we base our work on, and our adaptation of this is detailed in section 5.3. The lessons learned from this work can be found in section 5.4.

# 5.1 Background information

## 5.1.1 Cipher overview

The Advanced Encryption Standard (AES) [42] is a block cipher developed by the Belgian cryptographers Joan Daemen and Vincent Rijmen. It was submitted to the AES standardization process under the name Rijndael.

The standardization process started on January 2nd, 1997 when The National Institute

of Standards and Technology (NIST) announced that a successor to the Data Encryption Standard (DES) was needed. This was because DES only had a small 56-bit key, which was becoming increasingly vulnerable to brute force attacks. 3DES solved the issue with small key-size by using three DES encryptions in sequence (with 2 or three different 56-bit keys), however DES was originally designed for hardware implementations, and not software. This made it unsuitable for software implementations on resource limited platforms, like embedded systems and mobile devices.

Similar to DES, AES was going to be an publicly disclosed encryption algorithm. In the nine months after the announcement, fifteen different designs were submitted. After the submission, all the candidates were analysed by cryptographers on the matter of security and performance. NIST held two conferences where the algorithms were discussed, and in august 1999, the fifteen algorithms were narrowed down to five finalists. A final round of reviews followed, and Rijndael was announced as the winner by NIST on October 2, 2000 and was standardized as AES in may 2002.

AES uses a fixed block size of 128-bit, and key sizes of 128, 192 and 256-bit. Because of the fixed block size, AES operates with a 4x4 array of bytes. Based on the size of the key, 10, 12, or 14 rounds with the basic steps below are performed:

- 1. Substitute Bytes

- 2. Shift Rows

- 3. Mix Columns

- 4. Add Round Key

The first step is KeyExpansion. This is a process also referred to as Rijndael key schedule, where the encryption key is expanded into a unique key for every round called a round key. In the *initial round*, only the *AddRoundKey* operation is applied. In the next rounds, the algorithm does the *SubBytes*, *ShiftRows*, *MixColums* and *AddRoundKey* operations. The *final Round* does not apply the *MixColums* operation.

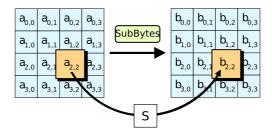

#### **Substitute Bytes**

The first step in a round is the substitute bytes transformation step (Figure 5.1). Here, each byte in the array is updated using an 8-bit substitution box, also referred to as a Rijndael S-Box. This step is done to provide non-linearity in the cipher, and is important to prevent cryptographic attacks based on simple algebraic properties.

Figure 5.1: Substitute Bytes. Illustration from Wikipedia [4].

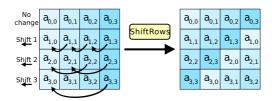

#### **Shift Rows**

The shift row transformation (Figure 5.2) called ShiftRow operates on the row of state (first row). Each byte on the second row is shifted one to the left. Similarly the third and forth rows are moved two and three places.

Figure 5.2: Shift Row. Illustration from Wikipedia [4].

#### Mix Column