# A Thesis Submitted for the Degree of PhD at the University of Warwick

## **Permanent WRAP URL:**

http://wrap.warwick.ac.uk/136163

# **Copyright and reuse:**

This thesis is made available online and is protected by original copyright.

Please scroll down to view the document itself.

Please refer to the repository record for this item for information to help you to cite it.

Our policy information is available from the repository home page.

For more information, please contact the WRAP Team at: wrap@warwick.ac.uk

# A Conformance Test Framework for the DeviceNet Fieldbus

by Soo Beng KHOH

A thesis submitted for the award of degree of

# **Doctor of Philosophy**

International Manufacturing Centre

Department of Engineering

University of Warwick

October 1996

#### Abstract

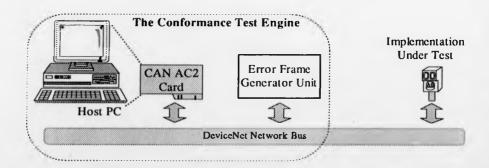

The DeviceNet fieldbus technology is introduced and discussed. DeviceNet is an open standard fieldbus which uses the proven Controller Area Network technology. As an open standard fieldbus, the device conformance is extremely important to ensure smooth operation. The error management in DeviceNet protocol is highlighted and an error injection technique is devised to test the implementation under test for the correct error-recovery conformance. The designed Error Frame Generator prototype allows the error management and recovery of DeviceNet implementations to be conformance tested. The Error Frame Generator can also be used in other Controller Area Network based protocols.

In addition, an automated Conformance Test Engine framework has been defined for realising the conformance testing of DeviceNet implementations. Automated conformance test is used to achieve consistent and reliable test results, apart from the benefits in time and personnel savings. This involves the investigations and feasibility studies in adapting the ISO 9646 conformance test standards for use in DeviceNet fieldbus.

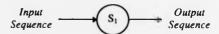

The Unique Input/Output sequences method is used for the generation of DeviceNet conformance tests. The Unique Input/Output method does not require a fully specified protocol specification and gives shorter test sequences, since only specific state information is needed. As conformance testing addresses only the protocol verification, it is foreseen that formal method validation of the DeviceNet protocol must be performed at some stage to validate the DeviceNet specification.

# Acknowledgement

The author would like to thank his academic supervisors Dr. Ken Young and Mr. Richard McLaughlin of Warwick Manufacturing Group for their assistance, guidance, and the informative and stimulating discussions during the course of research. The author would also like to acknowledge the University of Warwick with whose grant this PhD research was carried out.

Secondly, Mr. Shawn Adams of Allen Bradley must be thanked for allowing me the opportunity to work at Allen Bradley, USA as a visiting researcher. Appreciation is also due to Mr. Ed Polce and Mr. Doug Stanton for their help on DeviceNet Conformance; Mr. Pat Maloney, Mr. Ron Holl, Mr. Dave Callaghan, Mr. Tom Kocjan and Mr. Dan Noonen on DeviceNet protocol comprehension; Mr. Dave Comeau on Visual C++ Software Design; Mr. James Gross on Systems Tests and many more who work at Allen-Bradley, Landerhaven site, USA. Thanks are due to Mr. Les Warrington and Mr. Adrian Vinsome for their help and guidance on Object- Oriented methodology and Visual C++/C++ development, Mr. Trevor Martin of Hitex UK who supplied the Hitop embedded software development environment and Phytec embedded controllers. Special thanks are also due to all the research fellows and technicians at International Manufacturing Centre and Advanced Technology Centre for their assistance and friendships.

Lastly, my deepest heartfelt thanks to many friends, who are too numerous to be individually named, and my family for their patience and support during the production of this thesis.

Soo Beng KHOH October, 1996

# **Declaration**

This thesis forms the original work by the author and has not been published or used in any other award submission. All published works have been acknowledged with references.

# Disclaimer

The trademarks and companies mentioned in this thesis do not imply recommendation or endorsement by the author, nor that the products are necessarily the best available for the purpose. All trademarks remain the properties of the corresponding companies.

In loving memory of my beloved mother...

# Contents

| Chapter 1 - Introduction1-1                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 Evolution of Digital Control Systems1-1                                                                                                                                                                                                                                      |

| 1.2 Complexity of Control Systems1-3                                                                                                                                                                                                                                             |

| 1.3 Fieldbus Technology1-5                                                                                                                                                                                                                                                       |

| 1.4 Fieldbus Standards1-6                                                                                                                                                                                                                                                        |

| 1.5 Conformance to Fieldbus Standard1-8                                                                                                                                                                                                                                          |

| 1.6 1.6 Research Objectives1-9                                                                                                                                                                                                                                                   |

| Chapter 2 - Fieldbus Control Systems2-1                                                                                                                                                                                                                                          |

| 2.1 The Automated Manufacturing Hierarchy       2-1         2.1.1 Information Layer       2-5         2.1.2 Control Layer       2-6         2.1.3 Device Layer       2-6                                                                                                         |

| 2.1.4 Planning Horizon       2-7         2.2 Overview of Fieldbus       2-8         2.2.1 Historical Background       2-10         2.2.2 Open Standard Fieldbus       2-17         2.2.3 Intelligent instruments       2-17         2.2.4 Intrinsically Safe Fieldbus       2-14 |

| 2.2.5 ISO OSI 7-layer model       2-14         2.3 Discrete Control System       2-16         2.3.1 Time-Triggered       2-16         2.3.2 Event-Triggered       2-16         2.3.3 Time Consistency       2-17         2.3.4 Space Consistency       2-17                      |

| 2.4 Conformance to the Open Standard Fieldbus2-18                                                                                                                                                                                                                                |

| 2.5 Future of Fieldbus2-19                                                                                                                                                                                                                                                       |

| Chapter 3 - The DeviceNet Fieldbus3-1                                                                                                                                                                                                                                            |

| 3.1 Overview of CAN       3-1         3.1.1 The ISO 11898 Standard       3-2         3.1.2 CAN Industrial Applications       3-3         3.1.3 Higher Layer Protocols using CAN       3-3                                                                                        |

| 3.2 DeviceNet - A Higher Layer Protocol                                                                                                                                                                                                                                          |

| 3.2.2 The DeviceNet Layered Architecture 3.2.3 Medium Access Unit (MAU) | 3-6                          |

|-------------------------------------------------------------------------|------------------------------|

| 3.3 DeviceNet Messaging Scheme                                          | 3-11                         |

| 3.4 Application Layer Optimised for Control                             | 4)3-16<br>3-17<br>3-18       |

| 3.5 DeviceNet Network Error Management                                  | 3-21<br>3-23<br>3-25<br>3-26 |

| 3.6 DeviceNet Abstract Object Model                                     | 3-29<br>3-29                 |

| 3.8 Conformance to DeviceNet                                            |                              |

| 3.9 DeviceNet Hardware Conformance Test                                 | 3-32<br>3-35<br>3-35<br>3-35 |

| 3.10 DeviceNet Software Conformance Test                                | 3-39                         |

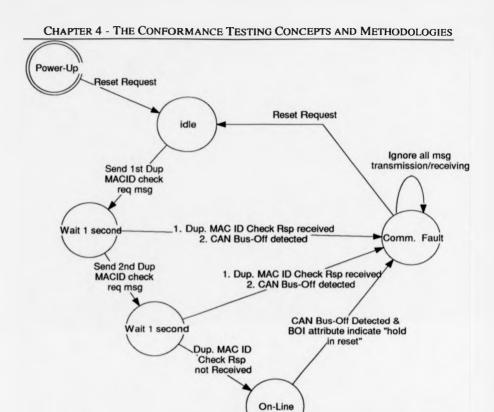

| Chapter 4 - The Conformance Testing Concepts at Methodologies           |                              |

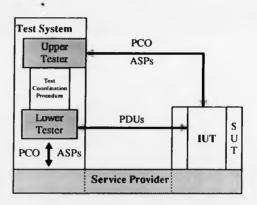

| 4.1 The Black Box Testing Approach                                      | 4-2                          |

| 4.2 Formal Tool for Protocol Representation                             | 4-3                          |

| 4.3 Requirements of Conformance Testing                                 |                              |

| 4.4 Types of Conformance Testing                                        | 4-9                          |

| 4.4.                                        | 3 Behaviour Testing                                                                                                                   |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 4.5 The Con<br>4.5.<br>4.5.<br>4.5.<br>4.5. | formance Test Generation Methodologies                                                                                                |

| 4.6 The Con                                 | ppliance Testing of OSI protocols4-16                                                                                                 |

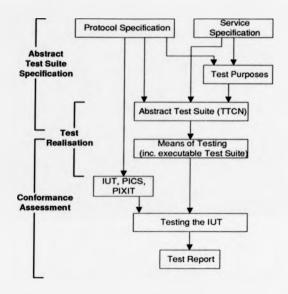

| 4.7 Abstract                                | Test Suite Specification4-19                                                                                                          |

| 4.8 Conform                                 | ance Test Realisation4-22                                                                                                             |

| 4.9 Conform                                 | ance Assessment Process4-23                                                                                                           |

| 4.10<br>4.10                                | 1 Frames Definition                                                                                                                   |

| 4.11                                        | nformance Test Architecture for DeviceNet4-25 .1 Conformance Special Interest Group in ODVA4-28 .2 Independent DeviceNet Test Lab4-28 |

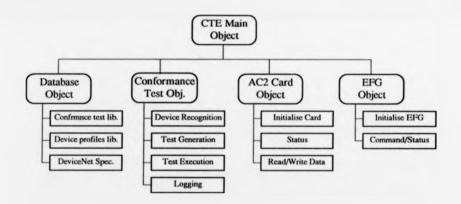

| •                                           | he DeviceNet Conformance Test Engine                                                                                                  |

|                                             |                                                                                                                                       |

| •                                           | ons                                                                                                                                   |

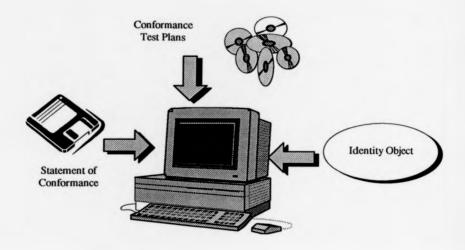

|                                             | ng the Conformance Testing process5-2                                                                                                 |

| 5.3.<br>5.3.<br>5.3.                        | ria considered in CTE design                                                                                                          |

| 5.4 CTE Har                                 | dware5-4                                                                                                                              |

| 5.5.                                        | ware                                                                                                                                  |

| 5.6.2<br>5.6.2<br>5.6.3<br>5.6.4            | Based CTE Software Design                                                                                                             |

| 5.6.6 Maintainability.                         | 5-12 |

|------------------------------------------------|------|

| 5.7 Disadvantages of the Windows platform      | 5-12 |

| 5.7.1 Memory Use                               |      |

| 5.7.2 Timers                                   | 5-12 |

| 5.7.3 Development Tool Wizard                  | 5-13 |

| 5.8 In-house testing with a Standard PC set-up |      |

| 5.9 The Operation of CTE                       | 5-14 |

| Chapter 6 - The Error Frame Generator Design   | 6-1  |

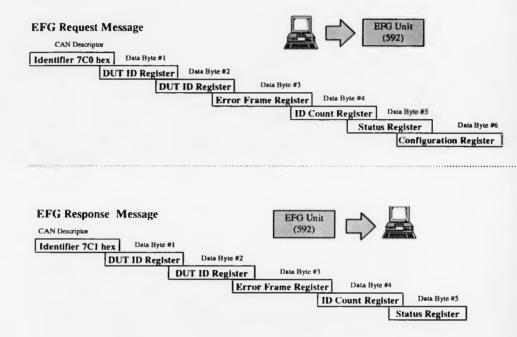

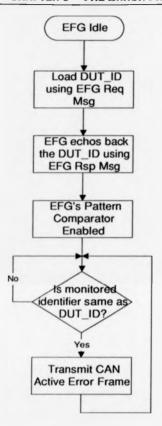

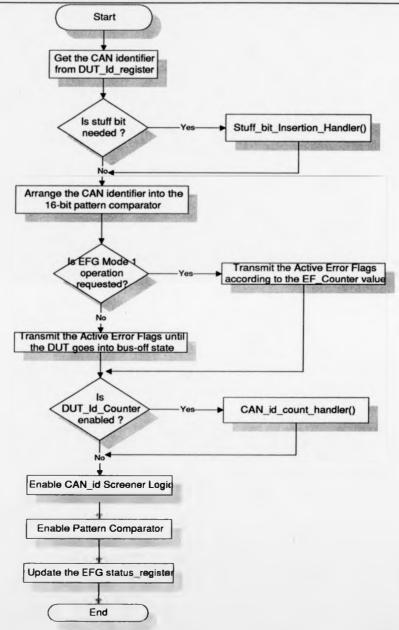

| 6.1 The EFG Prototype Design                   | 6-1  |

| 6.2 The EFG Operation explained                | 6-2  |

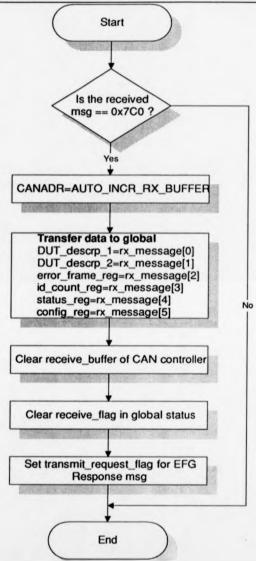

| 6.2.1 EFG Request Message                      |      |

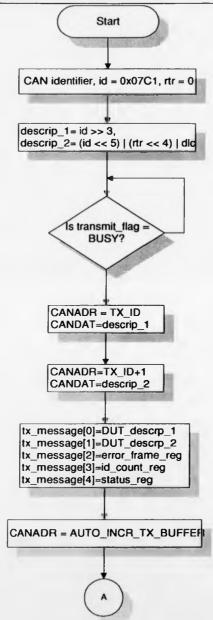

| 6.2.2 EFG Response Message                     |      |

| 6.2.3 DUT_ID Register                          |      |

| 6.2.4 Error Frame Register                     | 6-5  |

| 6.2.5 ID_Count                                 | 6-6  |

| 6.2.6 Status Register                          |      |

| 6.2.7 Configuration Register                   |      |

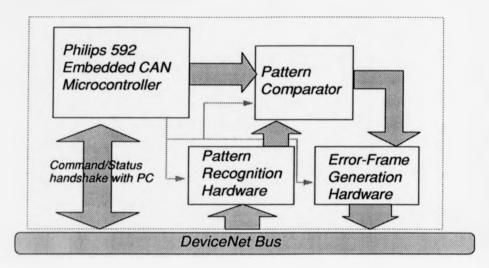

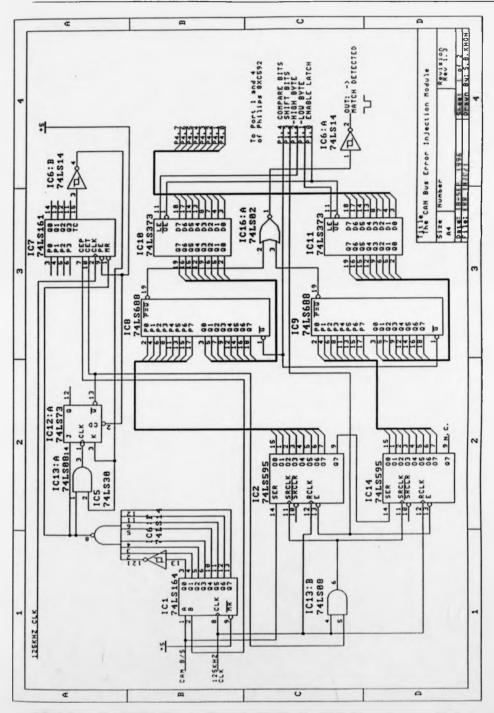

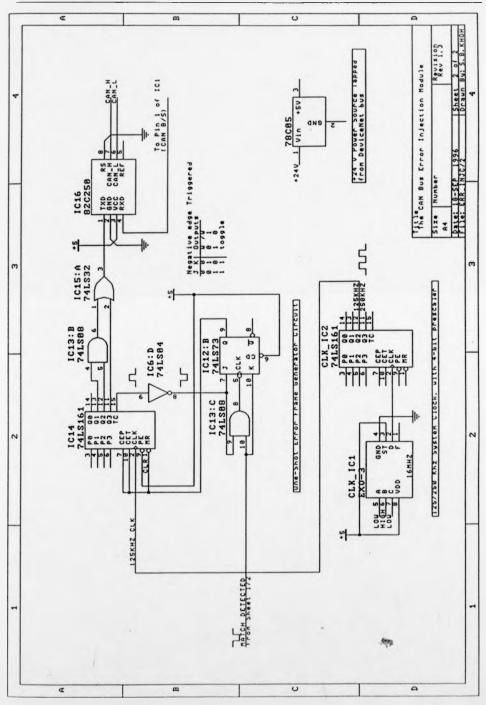

| 6.3 The EFG Hardware                           | 6-8  |

| 6.3.1 Pattern Recognition Hardware             |      |

| 6.3.2 Pattern Comparator                       |      |

| 6.3.3 Error Frame Generation Logic             | 6-11 |

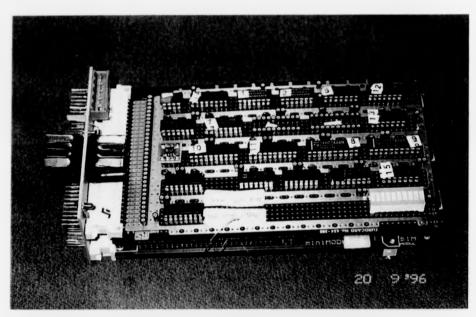

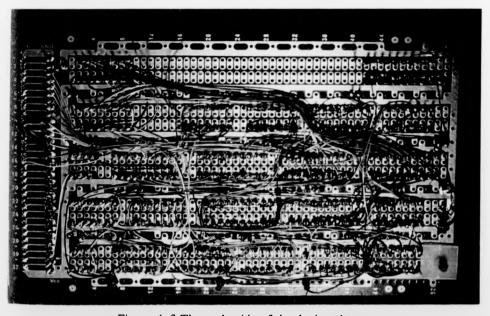

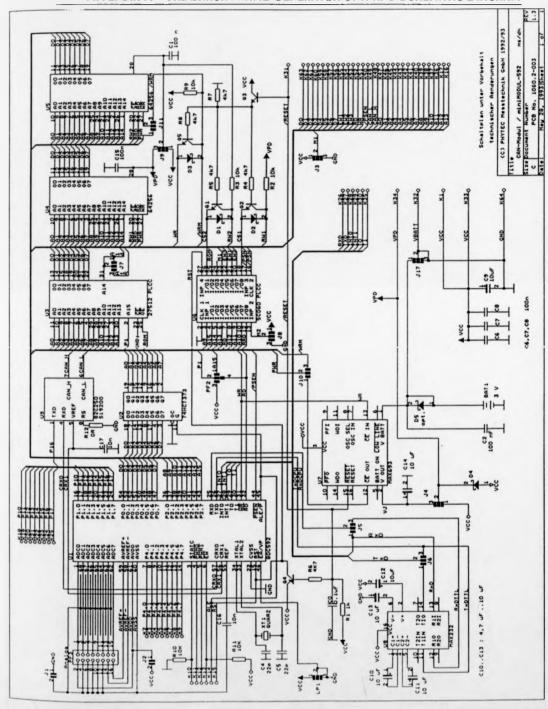

| 6.4 EFG Hardware Design                        | 6-13 |

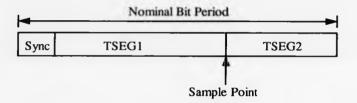

| 6.4.1 Clock Synchronisation                    | 6-13 |

| 6.4.2 Hardware based CAN Message Screeners     | 6-13 |

| 6.4.3 EFG Response Time                        |      |

| 6.4.4 CTE Baud Rate Setting                    | 6-17 |

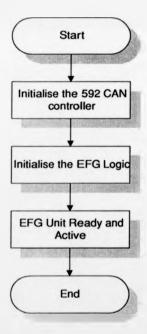

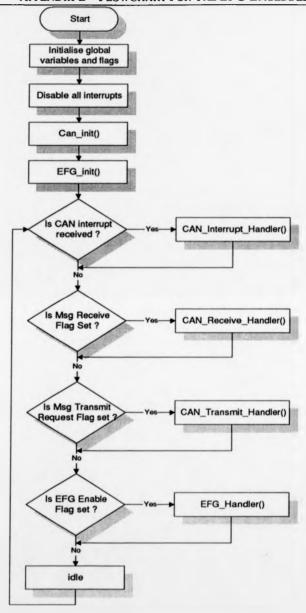

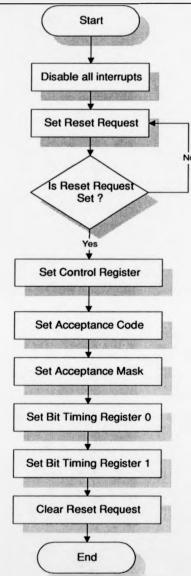

| 6.5 EFG Software Design                        | 6-17 |

| 6.6 The EFG Unit Verification Process          | 6-18 |

| 6.7 EFG Unit Constraints                       | 6-22 |

| 6.7.1 EFG Request/Response Message priority    | 6-23 |

|                                                |      |

| Chapter 7 - Discussions                        | /-1  |

| 7.1 CAN Bit Timing Parameters Verification     | 7-1  |

| 7.2 Local Control for EFG Unit                 | 7-2  |

| 7.3 Global Error Generator                     | 7-2  |

| 7.4 Test Preamble/Post-amble Optimisation      | 7-2  |

| 7.5 Uniform Resource Interpreter               | 7-3  |

| 7.6 Future Systems                             | 7-4  |

| 7.6.1 Interoperability Test                            | 7-4          |

|--------------------------------------------------------|--------------|

| 7.6.2 The Protocol Watch-dog                           | 7-6          |

| 7.6.3 DeviceNet Fieldbus Emulator                      |              |

| 7.6.4 DeviceNet Protocol Controller                    |              |

| 7.6.5 Formal Methods for Protocol Specifica            |              |

| Modelling                                              |              |

| 7.6.6 Notation and Methodology Compilers               |              |

| 7.6.7 Knowledge-Based Fault Diagnostic Mo              |              |

| 7.6.8 Peer-to-peer and Highly Distributed Co           |              |

| Chapter 8 - Conclusions                                | 8-1          |

| References                                             | R-1          |

| Bibliography                                           | R-1          |

| Appendix A - The Error Frame Generator Unit an Diagram | nd Schematic |

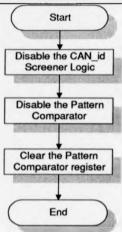

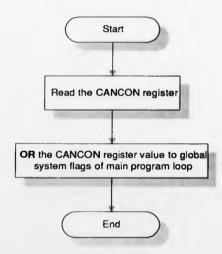

| Appendix B - Flowchart for the EFG Embedded S          | Software     |

| Appendix C - Invalid DeviceNet Message Test D          | efinition    |

# **List of Figures**

| Figure 2-1                                                                    | The automated manufacturing hierarchy of McLean et al2-2      |

|-------------------------------------------------------------------------------|---------------------------------------------------------------|

| Figure 2-2                                                                    | 2 The automated manufacturing pyramid and its communication   |

|                                                                               | network hierarchy2-3                                          |

| Figure 2-3                                                                    | Conventional point-to-point PLC based control system2-9       |

| Figure 2-4                                                                    | Distributed control using fieldbus network2-9                 |

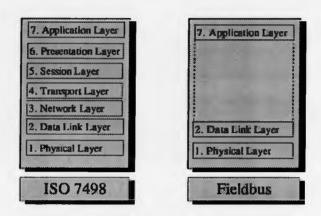

| Figure 2-5                                                                    | The ISO 7 layer model and reduced stack fieldbus model2-1     |

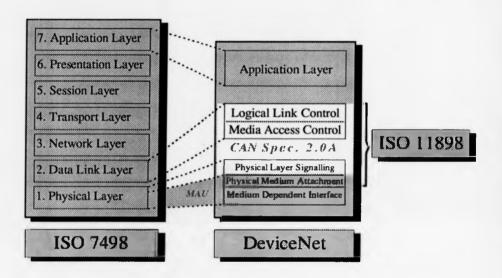

| Figure 3-1                                                                    | DeviceNet and its reference to the OSI 7 layer model3-7       |

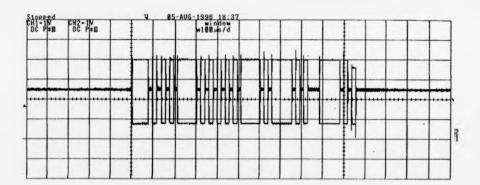

| Figure 3-2                                                                    | An Example of the ISO 11898 high speed physical signalling3-9 |

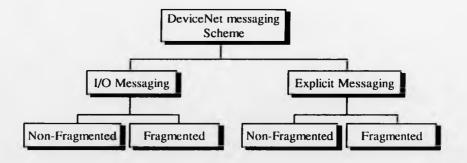

| Figure 3-3                                                                    | The summary of DeviceNet Messages3-1                          |

| Figure 3-4                                                                    | Open Explicit Messaging Connection Request/Response           |

|                                                                               | Message [62]                                                  |

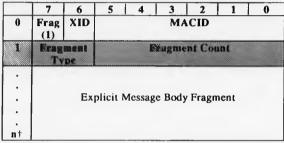

| Figure 3-5                                                                    | The Fragmentation Protocol Message Format [62]3-1             |

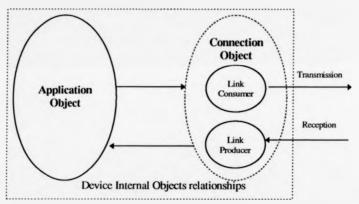

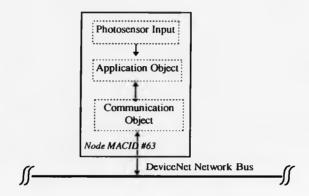

| Figure 3-6                                                                    | The interface between Application Object and Connection       |

|                                                                               |                                                               |

|                                                                               | Object3-1                                                     |

| Figure 3-7                                                                    | Object                                                        |

|                                                                               |                                                               |

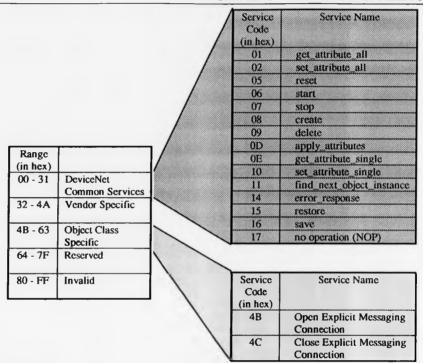

| Figure 3-8                                                                    | The DeviceNet Network services3-2                             |

| Figure 3-8 Figure 3-9                                                         | The DeviceNet Network services                                |

| Figure 3-8 Figure 3-9 Figure 3-10                                             | The DeviceNet Network services                                |

| Figure 3-8 Figure 3-9 Figure 3-10 Figure 4-1                                  | The DeviceNet Network services                                |

| Figure 3-8 Figure 3-9 Figure 3-10 Figure 4-1 Figure 4-2                       | The DeviceNet Network services                                |

| Figure 3-8 Figure 3-9 Figure 3-10 Figure 4-1 Figure 4-2                       | The DeviceNet Network services                                |

| Figure 3-8 Figure 3-10 Figure 4-1 Figure 4-2 Figure 4-3                       | The DeviceNet Network services                                |

| Figure 3-8 Figure 3-10 Figure 4-1 Figure 4-2 Figure 4-3 Figure 4-4            | The DeviceNet Network services                                |

| Figure 3-8 Figure 3-10 Figure 4-1 Figure 4-2 Figure 4-3 Figure 4-4 Figure 4-5 | The DeviceNet Network services                                |

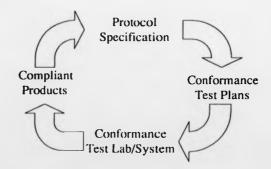

| Figure 4-7 The Conformance Test Life Cycle4-26                            |

|---------------------------------------------------------------------------|

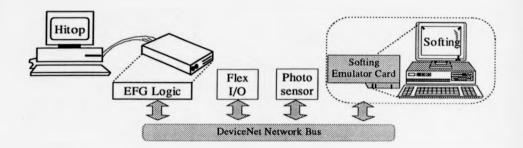

| Figure 5-1 The Conformance Test Engine Framework5-1                       |

| Figure 5-2 The object decomposition of CTE software5-9                    |

| Figure 5-3 The CTE internal interactions5-15                              |

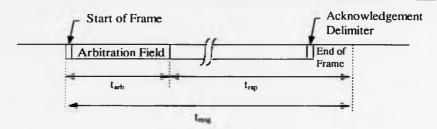

| Figure 6-1 The EFG Request and Response Messages6-3                       |

| Figure 6-2 The operation of the EFG Request/Response Messages6-4          |

| Figure 6-3 The block diagram of the Error Frame Generator Module          |

| Hardware 6-8                                                              |

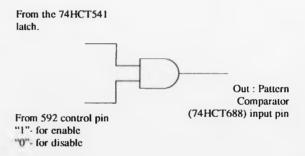

| Figure 6-4 A simple data flow control using AND gate6-10                  |

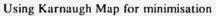

| Figure 6-5 The Karnaugh Map for Active Error Flag Minimisation6-12        |

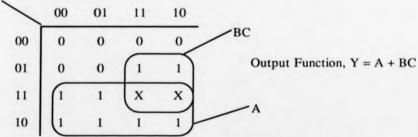

| Figure 6-6 A CAN message frame with reference to the bit                  |

| period clock, t <sub>bit</sub> 6-14                                       |

| Figure 6-7 The definition of EFG response time6-15                        |

| Figure 6-8 The EFG Verification Test Set-up6-19                           |

| Figure 6-9 The error injection sequence6-22                               |

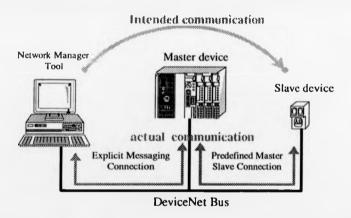

| Figure 7-1 The communication between the network manager tool and a slave |

| device owned by a master 7-5                                              |

# **List of Tables**

| Table 2-1 The summary characteristics of different level computer              |     |

|--------------------------------------------------------------------------------|-----|

| networks in a manufacturing organisation2                                      | -7  |

| Table 3-1 The DeviceNet Baud Rate and Bus length3-                             | -5  |

| Table 3-2 The DeviceNet Message Groups []3                                     | -10 |

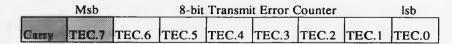

| Table 3-3 The Transmit Error Counter (TEC)/Receive Error Counter               |     |

| (REC) values with respect to their corresponding states3-                      | -24 |

| Table 3-4 The DeviceNet BOI value and its corresponding meaning3-              | -27 |

| Table 3-5 The BTR0 and BTR1 values used in DeviceNet3-                         | -34 |

| Table 3-6 A summary of available CAN chips and their compatibility to          |     |

| DeviceNet3-                                                                    | -37 |

| Table 6-1 The DUT_ID Register6-                                                | -5  |

| Table 6-2 The Error Frame Register6-                                           | -5  |

| Table 6-3 ID_Count Register6-                                                  | -6  |

| Table 6-4 The Status Register and its functional description6-                 | -7  |

| Table 6-5 The Configuration Register and its functional description6-          | -7  |

| Table 6-6 The bit word for pattern comparator6-                                | -9  |

| Table 6-7 The Truth Table for Active Error Flag6-                              | -12 |

| Table 6-8 The relationships between band rate and the bit period, $t_{bit}$ 6- | -16 |

| Table 6-9 A summary observation results of the experiment6-                    | -20 |

# Glossary

CAL CAN Application Layer

CAN Controller Area Network

CID Connection Identifier

CIM Computer Integrated Manufacturing

CSMA/CD+NDBA Carrier-Sense Multiple Access/Collision Detection +

Non-Destructive Bitwise Arbitration

CTE Conformance Test Engine

DDE Dynamic Data Exchange

DLL Dynamic Link Library

DUT Device Under Test

ECU Electronic Control Unit

EFG Error Frame Generator

EMC Electromagnetic Compatibility

EPR Expected Packet Rate

FDT Formal Description Technique

FSM Finite State Machine

IEC International Electrotechnical Committee

ISA Instrument Society of America

ISO International Organisation for Standardisation

IUT Implementation Under Test

LLC Logical Link Control

MAC Medium Access Control

MACID Media Access Control Identifier

MAU Media Access Unit

MDI Medium Dependent Interface

ODVA Open DeviceNet Vendors Association

OLE Object Linking and Embedding

OOA Object Oriented Analysis

OOD Object Oriented Design

OOP Object Oriented Programming

PDU Protocol Data Unit

PICS Protocol Implementation Conformance Statement

PIXIT Protocol Implementation eXtra Information for Testing

PLS Physical Layer Signalling

PMA Physical Medium Attachment

SDS Smart Distributed System

SLIO Serial Linked Input/Output

SOC Statement of Compliance

SOF Start-of-Frame

TTCN The Tree and Tabular Combined Notation

UCMM Unconnected Message Manager

UIO Unique Input/Output Sequence Method

# CHAPTER 1 - INTRODUCTION

With the reduction of product life-cycle from years to months, today's manufacturing systems must not only be efficient enough to produce high volume and quality products at minimal possible costs, they must also have sufficient flexibility for fast product change. The advent of higher power-to-cost ratio silicon has enabled microprocessors to be used extensively in the control and instrumentation of the manufacturing world. As such, computer-controlled systems are ideal for producing quality products competitively.

# 1.1 Evolution of Digital Control Systems

Digital computers were first introduced to improve the efficiency of measurement and control systems two decades ago. Initially these were standalone custom-designed control systems which were very bulky, expensive and unreliable. In 1968, a group of engineers from General Motors, USA conceived an idea to provide a flexible and cost effective solution to replace the hard-wired relay-logic in industrial control [1, 2]. They called their invention the Programmable Logic Controller (PLC). Since then the PLC has become the dominant control technology in the manufacturing and process industry.

The advancement in the semiconductor industry has had a dramatic impact on PLC technology. Intel introduced the first 8-bit 8008 microprocessor in 1972, development followed by the more powerful 8080 two

By S.B. Khoh Page 1-1

years later [3]. To date, the growth of the semiconductor industry has been correctly predicted by Moore's Law<sup>1</sup>. In 1977, Allen-Bradley of the USA introduced the first industry standard PLC based on the newly introduced Intel 8080 microprocessor [2]. It was not until the 1980s that PLCs were used extensively in control and instrumentation in the manufacturing industry.

The advantage of using the PLC is that the sequence of operations or controls can be altered easily by programming the PLC using customised software called ladder-logic. The PLC (which consists of microprocessors) reads values from the sensors, evaluates and executes commands by sending new states to the actuators. Its modular design allows easy upgrade and expansion of the control system when the need arises. When there is a fault in a module, it can be easily replaced by another plug-in module, thus increasing the maintainability of the system, as well as production up-time.

This flexibility has enabled control system vendors to mass produce the PLC to be used in virtually all control applications. End-users can then alter the software to cater for their specific requirements. Control system vendors like Allen-Bradley, Festo, GEC, Hitachi, Omron, Mitsubishi, Selectron to name a few, have since shared the market for PLCs. This has brought PLCs within the budget of many potential users in the manufacturing industries, with higher performance systems introduced every year. For example, the PLC3 controller introduced by Allen Bradley in 1980 was 1,000 times more powerful than the company's first PLC [1].

By S B. Khoh

<sup>&</sup>lt;sup>1</sup> Gordon Moore is the co-founder of Intel and a chip designer. He observed that a new chip will be developed every 18 months and contain twice as much processing power as its predecessor. Combining the two observations, he predicted that chip processing power will increase exponentially and this became known as Moore's Law.

## 1.2 Complexity of Control Systems

As the activity of process control becomes more complex, more sensors and actuators are needed to perform the control sequences. More devices mean more wiring. In addition, the strive towards higher product quality in the competitive global market of the 90s has imposed new requirements on the manufacturing systems. The use of quality assurance technique such as the statistical process control (SPC) [4] requires manufacturing processes to be monitored closely. Furthermore, all instruments involved in the manufacturing processes must be in tip-top working condition to maximise production uptime. To achieve this, extensive preventive failure analysis and maintenance program is exercised to monitor and maintain the instrument's health. This resulted in the influx of the wiring harness as monitor lines are needed to obtain the health and status feedback from the devices. To meet the ever increasing demand of complex process control, the following observations are made.

#### Flexibility

The conventional point-to-point system was designed for transfer line facility in mass production environment, i.e. large batch size manufacturing. Most of the process/assembly stations were not expected to be reconfigured frequently as it is a very tedious and time-consuming job to set up and manage the wire spaghetti. Any addition of new device will involve the routing of new wires through the already complex cable conduit that is difficult to access. In other words, the time penalty for set-up and commissioning of these control system has become noticeable.

#### Reliability

The reliability of the conventional point-to-point wiring is questionable. An average size PLC may consist of 8 I/O racks with 32 I/Os per rack. This means that there are about 200 wires that need to be labelled and managed properly. To get the wiring right first time is a challenging experience. The large number of wires may also lead to a decreased in system reliability, i.e. more wires, more chances of things going wrong. In addition, the use of junction boxes and connectors for wire management will contribute to the poor reliability of the system.

#### Noise and Cross-talk interference

Cross-talk interference is another problem in wire-packed control systems. It is a situation where neighbouring wires induce electromagnetic noise to each other and caused stray signals and distortions. Therefore, additional care must be taken when routing the analogue-to-digital converter's signal wire to ensure that the accuracy of the analogue value is not affected. The use of shielded cable may be required in extremely noisy environments.

#### Maintainability

The objective of a production system is to convert the raw materials into finished products. Machine breakdown or production downtime is a costly affair. Hence, the reliability and maintainability of the production system is of utmost importance. The speed with which a fault can be located and rectified, or prevented, plays a vital role. However, if a wire were to have bad electrical contact in the 200 wires conduit, identifying the fault may be a painstaking and time consuming job.

Ideally, the new generation of manufacturing control systems must be modular, easily reconfigurable, highly reliable and maintainable, fault tolerant and, most importantly, cost effective. They must be flexible in adapting themselves to fast product change. A solution is to inter-connect all the sensors and actuators with a single digital bus for realising the automation and controls. The multiplexing of these sensors and actuators signals via a single bus is achieved using the emerging fieldbus technology, i.e. a technology derived from the computer local area networks (LANs).

## 1.3 Fieldbus Technology

Fieldbus is defined as an all digital, high performance, multi-drop communication network for connecting process instrumentation to controllers [5]. In its simplest form, fieldbus is just a communication media which benefits the users with simple 'plug-and-play' installation, reduced wiring, improved diagnostic-ability, reconfiguration flexibility and ease of maintenance. Fieldbus is a computer network optimised for controls and instrumentation. Therefore, it features small data packets with deterministic bus arbitration scheme for guaranteed network response time.

Fieldbus system brings substantial costs savings. An Italian power utility predicts a 4% reduction in overall investment costs after allowing for 10-20% increase in new device costs [6]. In Du Pont's fieldbus installation, wiring cost savings of up to 20% were reported for its Brevard site facility in Asheville, North Carolina, USA [7]. The installation at BP Research and Engineering facility, Sunbury-on-Thames, UK, has also demonstrated savings in cost and installed cables, as well as enhanced process control system performance in an industrial situation [8].

The application of fieldbus is not restricted to process control and manufacturing industry. For example, Profibus (i.e. another instance of fieldbus) is used in the Warsaw underground, Poland for reporting the status of the subway equipment and data exchange between computers at the dispatch and control centre, and the Kabaty end station [9]. This is believed to be the first fieldbus installation in safety-critical railway signalling application [10]. Other areas of fieldbus application include building automation and marine application.

#### 1.4 Fieldbus Standards

Fieldbus can be divided into open standard and proprietary. Proprietary fieldbus standard is developed and marketed by a single vendor with limited product range. Market trend has indicated that the proprietary fieldbusses are no longer welcome by the industry. The flexibility of sourcing devices from different vendors and plugging together to form a single field control and instrument system (i.e. an open fieldbus standard) has far greater benefits than relying on a single source. Many proprietary fieldbusses have since joined forces to reduce the many proprietary standards by forming the consortia for an open standard.

The Instrument Society of America (ISA) has collaborated with the International Electrotechnical Committee (IEC) to form the ISA/IEC SP-50 working committee in an attempt to define an international standard for the fieldbus. One of the objectives of the SP-50 working committee was to define an international fieldbus standard so as to eliminate the many *standards* available today.

In the meantime, two vendor-driven consortia fieldbusses, i.e. WorldFip<sup>2</sup> and Interoperable Systems Project<sup>3</sup> (ISP) had collaborated in October 1994 to produce the Fieldbus Foundation (FF) fieldbus standard. The Fieldbus Foundation has inherited many of the SP-50 specification which include the SP-50 physical layer (IEC 1158-2 standard) for intrinsically safe operation. Fieldbus Foundation (FF) hopes that when an international fieldbus standard is created, FF can be fully compatible with the SP-50 fieldbus standard and become the de-facto industry standard.

Within Europe, CENELEC<sup>4</sup> has approved WorldFip [11], Profibus [12] and P-Net [13] as the European fieldbus norm, EN 50170 [14, 15]. This may mean that Europe and America may well go in different directions, leaving us with no international fieldbus standard.

While the ISA/IEC SP-50 has neared its end of the international fieldbus standard specification, there have been another development of a much simpler, lower level fieldbus subset. This simple I/O function fieldbus is sometimes referred to as the sensor bus. Among them are Actuator Sensor Interface (ASI), Controller Area Network (CAN) [16] based networks, e.g. CAL [17], CANOpen [18], CAN Kingdom [19], DeviceNet [20] and Smart Distributed Systems (SDS) [21, 22, 23], Lonworks [24, 25] and Profibus-DP [26, 27]. The successful de-facto standard in this sector will depend on the cost-effectiveness, product availability, consortia of vendors, as well as the technical advantages.

<sup>&</sup>lt;sup>2</sup> WorldFip is backed by Allen-Bradley, Honeywell and others.

<sup>&</sup>lt;sup>1</sup> Interoperable Systems Project (ISP) is supported by Fisher-Rosemount, Siemens, Jonson Yokogawa etc.

<sup>&</sup>lt;sup>4</sup> CENELEC - The European Committee for Electrotechnical Standardisation

#### 1.5 Conformance to Fieldbus Standard

In an open fieldbus scenario, all the field instruments must conform to the rules laid out by the standard specification. Failure to adhere to the fieldbus standard protocol will bring catastrophic failure not only to the responsible culprit, but the entire fieldbus network or system. This will affect the end-users' confidence on the particular fieldbus standard. Conformance testing an open fieldbus implementation is the vital step to ensure that all the field device developers have uniform interpretation of the specification, and that their products conform to the protocol standard.

"A conformance testing is used to verify that the external behaviour of a given implementation of a protocol is equivalent to its formal specification" [28].

DeviceNet is an open standard fieldbus which uses the proven CAN technology. Since it is an open standard, the conformance testing is a must to ensure the smooth operation and success of this fieldbus standard. DeviceNet is owned by the Open DeviceNet Vendors' Association (ODVA), and consists of a consortium of more than 130 companies which include Allen-Bradley, Banner, Omron, Peperl & Fuch, Schrader-Bellows and SMC. ODVA has formed many Special Interest Group (SIG) to manage and govern the technical related issues of DeviceNet. Among the many ODVA SIGs, the Conformance SIG is of particular interest due to its responsibility on the conformance testing of DeviceNet implementation.

A significant number of conformance test suites have been developed by the Conformance SIG. Until now, the conformance test suites of DeviceNet still do not include the tests for error recovery and management. The error

By S.B. Khoh

Page 1-9

recovery sequences and state machines are defined in the protocol specification for product developers to follow. For example, when a fault is detected the device must indicate the detected fault by flashing its LEDs in a predefined fashion and move into a predefined "safe state". In addition, the device's internal object's attribute must register the detected fault. So far, the test for correct error recovery and management has been hampered by the lack of a suitable method of injecting errors.

Given the importance in conformance testing of the implementation of correct error recovery and handling, perhaps a special hardware can be researched and designed to carry out the job. This protocol emulator must be able to inject errors in a controlled manner. In other words, it must only induce error on the implementation under test so that the effect can be observed by another node, i.e. the test system.

## 1.6 Research Objectives

The primary objective of this thesis is to study, investigate and devise an appropriate compliance test tool for injecting error onto the bus. This allows the testing of DeviceNet open standard fieldbus implementations for correct error recovery.

The research started with the investigation of alternative uses of the Controller Area Network (CAN) technology in non-automotive sectors. It was envisaged that the CAN technology can be feasibly applied in the controls and instrumentation industry. The background study and investigation on the current controls and instrumentation trends were carried out. This led to the development of DeviceNet, i.e. a CAN derivative fieldbus. Progressively a

By S.B. Khoh

knowledge gap had been identified in the area of conformance testing, in particular on the error injection for implementation fault testing.

The possibility of realising an automated approach for conformance testing had to be explored to achieve consistent and high-quality test results. Thus an error injection mechanism has been designed and included in the automated compliance test framework for realising the error testing.

The secondary objective includes the study and recommendation of the suitable object-oriented concept and design methodology for use in the prototype development. An interoperability test system for DeviceNet must also be investigated to test DeviceNet as a complete controls and instrumentation system, rather than as individually complied nodes.

# CHAPTER 2

By S.B. Khoh

# FIELDBUS CONTROL SYSTEMS

Fieldbus is a new technology of controls and instrumentation which uses the computer networks technology. These fieldbusses must be able to interface with the existing computer networks within a manufacturing organisation. A hierarchy of computer networks has been established, each responsible for the corresponding level needs. For instance, the computer networks at the lowest hierarchy normally consist of hard real-time controls, with short and bursty data packets for deterministic network response. On the other hand, higher level networks such as those used in the Management Information System (MIS) will place great emphasis on the data carrying capacity rather than deterministic network response time. Combining these various levels of computer networks, data from the shop floor can be fed directly into higher level systems to achieve the computer integrated manufacturing (CIM) systems within the organisation.

# 2.1 The Automated Manufacturing Hierarchy

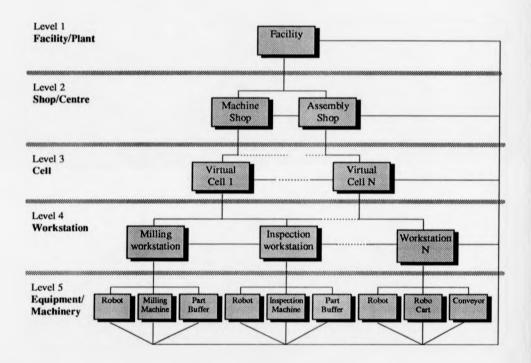

In the paper published by C. McLean et al [29], the authors have proposed the five levels of control hierarchy based on analysis of a non-automated batch manufacturing system. The five levels were facility, shop, cell, work station and equipment. Computer Aided Manufacturing (CAM) was believed to be introduced sometime later as there is no evidence of it when McLean et al. published their findings in 1983. The automated manufacturing

Page 2-1

control hierarchy realised in the National Bureau of Standards' Automated Manufacturing Research Facility (currently known as the National Institute of Standards and Technology, NIST), which was planned to be operational in 1986 [29] is shown in Figure 2-1.

Figure 2-1 The automated manufacturing hierarchy of McLean et al.

Also known as the control pyramid [30], the hierarchy has to act as the foundation whenever automated manufacturing issues are discussed. So, the introduction of CIM has further caused the need to interconnect every machines or islands of machines in the manufacturing environment in order to facilitate better information flows within the CIM envelope. This has

By S.B. Khoh

encouraged the development and utilisation of various communication networks between different hierarchies and within the same hierarchy.

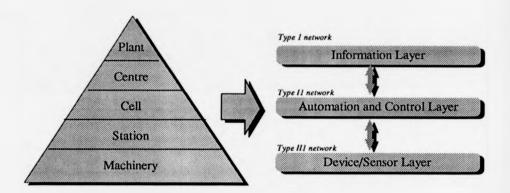

According to the work done by Valenzano et al [31], the communication infrastructure to support CIM is composed of 3 types of communication networks as shown in Figure 2.2. The communication network within this context is referring to computer networks such as Local Area Network (LAN).

Figure 2-2 The automated manufacturing pyramid and its communication network hierarchy

At the higher level of the hierarchy, large data flow is required, with less emphasis on the real-time response. However, the situation is totally reversed at the bottom of the hierarchy where fewer data are exchanged rapidly with strict real-time constraints. These two extreme applications on both ends of the pyramid place greatly differing demands on networks requirements, and no single network technology today can be optimised for the full range of operations.

The currently recognised solution to the differing requirements is to use different levels of communication networks to cover these needs. This involves the use of many communication gateways to convert the different data formats from one level to another so that the data can be consumed by other communication networks.

However, there is a drastic change in the type-II and type-III networks. Years ago, these networks mainly consisted of vendor specific or proprietary solution. The majority of the communication networks were not part of the control system design, nor use LAN type communication. They were simply some extensions to be bolted on the controllers for communication to take place, e.g. RS-232, IEEE-488 communication standards. Emphasis was placed on the better design of the control system rather than integrating the communication protocol into the control systems. Because they were not computer networks, the OSI 7 layer model cannot be used to model the communication interface. Hence, communication between these devices were not elegantly carried out.

Today, many of these communication media such as RS-485, have been replaced with the open standards computer networks, most of which are based their design on the ISO/OSI 7 layer model for openness. The adoption of computer network allows the communication interface to be designed into the control and instrumentation systems, rather than the conventional 'bolted-on' approach. The availability of more powerful and advanced semiconductor technology, i.e. more powerful and cost effective processors, has enabled more complex and sophisticated communication to be implemented.

By S.B. Khoh

Suddenly, the communication requirements in the factory shop floor have opened another new market niche, i.e. communication networks. Digital busses were used to interconnect the machines and islands of automation together, These industrial communication networks are known as fieldbus. Elegantly designed gateways were introduced by the fieldbus vendors to transfer the data from one layer to another.

#### 2.1.1 Information Layer

At the top of the hierarchy, information exchange through the network is in large blocks (in the region of several kilo bytes to megabytes). This level is incompatible with real-time critical applications due to the inverse relationship between real-time control and data packet size. Table 2.1 shows a comparison between various level of industrial computer networks in-terms of the network size, data volume and response time. Networks at the information level will therefore tend to have more data carrying capability but less real-time performance.

At this level, networks will be used for transferring data between departments in the CIM environment (Figure 2.2) within a company (Intranet), or even globally (Internet) using Ethernet with TCP/IP protocol. The packet size for Ethernet based networks varies between 64 bytes to 1,518 bytes at 10 to 50 Mbits/s typical. The applications that run at this level do not have any strict real-time constraints and any additional delays can be tolerated by the system. A typical application may be transferring Statistical Process Control (SPC) data from automation cells to the Management Information System

By S.B. Khoh Page 2-5

(MIS) database of the factory for quality assurance purposes. Other applications include email, file transfer, database query and update, etc.

#### 2.1.2 Control Layer

One level down from the information layer is the control layer. At the control level, smaller quantities of data (as compared to information level) are being transferred between different cell controllers at high speed for exercising real-time control. Each data packet may be in the region of a hundred bytes. Most of the computer networks used in this layer are found on the shop floor to connect field instruments together. Hence, the term fieldbus is coined to refer to any computer network which is used for real-time control. For example, Profibus and Fip are currently the two top contender at this level.

#### 2.1.3 Device Layer

Communication networks in the Device Layer are very similar to the control layer. Here, the communication network needs to satisfy hard real-time constraints as compared to the control layer. Since the communications are among devices such as sensors, actuators and the PLC, data flows are usually in terms of bits or in a few bytes. The network traffic mainly involves the cyclic exchanges of sensor values and actuator commands in a short and bursty fashion. The Protocol Data Unit (PDU) must be short in order to minmise the network latency time. In addition, the network must be capable of delivering high network efficiency in this frequent, periodic, small sized data application.

Network efficiency refers to the ratio between the amount of useful user data ferried across the network and the number of bits needed to perform the ferrying operation [32].

Since the network links mainly the sensors and actuators to the PLC, it is also known as Sensor Bus. Example of sensor bus include Actuator Sensor Interface (ASI), CANopen, DeviceNet and Smart Distributed System (SDS). Another reason for having a Sensor Bus is the economic factor, i.e. the cost of putting the network interface on a low-cost device must be minimal.

Table 2-1 The summary characteristics of different level computer networks in a manufacturing organisation

|                   | Network size | Data volume | Response time |

|-------------------|--------------|-------------|---------------|

| Information Layer | Large        | Large       | Slow          |

| Control Layer     | Moderate     | Moderate    | Moderate      |

| Device Layer      | Small        | Small       | Fast          |

#### 2.1.4 Planning Horizon

With the use of more powerful hardware solely for communication, the planning horizon on each level will undoubtedly increase. Planning horizon is the amount of time any control system is allocated to handle its tasks [29]. The system does not need to know about any activities outside its planning horizons. Hence, the planning horizon acts as an information hiding mechanism so that the complex system can be decomposed and executed separately by less powerful sub-systems. The boundary of control in each subsystem is defined by its immediate higher level in the hierarchy.

The planning horizon of the 3 layer model may still remain the same, but be implemented differently. Instead of using the physical hardware to decompose the planning horizon, the planning horizon can be done in some clever software routine. In other words, instead of using 3 separate sets of PLCs to form a control hierarchy, the system can be implemented in a multiprocessors PLC with 3 different independent sets of software routine (3 channels of software), each invisible to the other. The object-oriented technology in software design, which features the data abstraction and encapsulation, can be used in this instance to hide away unnecessary information, thus simplifying the control system design.

#### 2.2 Overview of Fieldbus

By S.B. Khoh

The process control industry has been waiting for a technology which is capable of reducing the wiring harness, providing reconfiguration flexibility, reliability and, most importantly, cost effectiveness. These requirements have made fieldbus systems the key focal point for the development of better and more efficient digital control systems for the 21st. century.

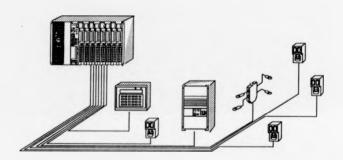

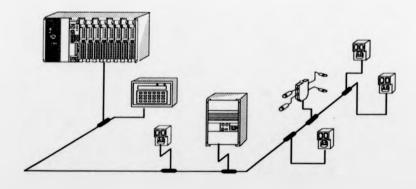

With the application of fieldbus, the control systems in Figure 2-3 can now be replaced with a single wire serial data bus that interconnects all the sensors and actuators before linking back to the central controller. Figure 2-4 depicts a typical fieldbus control system. The availability of an on-board microcontroller allows the simple switch to have some 'intelligence'. This allows it to perform other functions such as self-diagnosis, self-calibration, error warning etc. In addition, extra parameters can be realised without the

Page 2-8

use of additional wire. The appearance of intelligent/smart sensors and actuators and control networks has marked a new era of control technology in factory automation. Figure 2-3 and Figure 2-4 show the comparison between the conventional point-to-point control system and the more simplified fieldbus control.

Figure 2-3 Conventional point-to-point PLC based control system

Figure 2-4 Distributed control using fieldbus network

#### 2.2.1 Historical Background

The original idea of having a Fieldbus was simply to replace the ageing 4-20mA transmission signal designed some 25 years ago with a digital communication media. In the past, communication between smart field instruments was done mainly by proprietary digital busses and custom designed gateways. Most vendors developed proprietary digital busses for their own markets. This does not create a problem as the user company has large engineering resources to support the many gateways and signal converters. General Motors for instance, spend more than half of their automation budget on the implementation of custom interfaces between intelligent instruments. At the end of the 1980s, there were so many proprietary digital busses around that engineering staff of the user company could no longer cope with the specific proprietary solutions. In addition, many companies were involved in "rightsizing" exercises and laid-off many "redundant" employees. The industry has since realised that in order to utilise these smart instruments successfully, a new generation of communication standard is required. This is the same train of thought that GM had when it embarked on the Manufacturing Automation Protocol (MAP) and Technical and Office Protocol (TOP) project to minimise the interfacing problems.

In the simplest form, fieldbus networks replace complex wiring which benefits the users in terms of system installation cost, shorter commissioning time and improved diagnostics-ability. Fieldbusses interface with higher level computer networks through gateways to allow a continuous flow of data from

By S.B. Khoh

the shop floor to higher hierarchy. This allows higher level systems access to data on lower levels, thus providing better integration within the organisation, i.e. a step closer to computer integrated manufacturing (CIM).

However, fieldbus is more than a digital communication network [33]. It is an open Field Control System (FCS) of the 21st. century which will change the scene in distributed control and field instrumentation. Although it took the industry almost a decade to realise the full potential and complexity of Fieldbus, this highly distributed process system will be an important issue in Automation Industry.

The availability of new generation high performance single-chip microcomputers or microcontrollers has started to change the scene of process control. For example, microcontrollers now have the capability and power to process complex PID control algorithms locally, instead of routing the raw data back to the central processors for processing. Fuelled by the smaller footprint of surface mounted technology and higher performance to cost ratio silicon, more advanced control routines can be feasibly and economically implemented on the field device itself. This has indirectly moved the control tasks from the central control unit to the field resident microcontrollers, hence the birth of distributed control systems. These microprocessor based instrumentation systems are collectively referred to as smart instruments. If implemented properly, these smart instruments will execute the control sequence in parallel. In 1989, Oxford University, Foxboro GB Ltd and ICI

launched the Sensor Validation (SEVAC) project to develop smart sensors for fieldbus application [34].

## 2.2.2 Open Standard Fieldbus

In general Fieldbus networks can be divided into two categories, i.e. proprietary and open standard architecture. Proprietary fieldbus is developed and marketed by a single vendor with a range of products to offer. Since it's proprietary, the vendor has full authority and responsibility to optimise the performance and rectify the fault of its fieldbus system. This will either give an outstanding performance or otherwise. Being controlled by a single source means easier technical support access when things go wrong. For instance, one call to the vendor may solve the problem. However, when the system consists of several vendor's products, it may take a while for the vendors to work out whose device is at fault in an open architecture scenario.

On the other hand, open standard Fieldbus, which consists of numerous automation vendors, offers better product range and varieties. These different vendors' devices must be able to co-exist on the same network, thus interoperability and interchangeability is of paramount importance. For example, DeviceNet is an open standard fieldbus which consist of more than 130 vendors such as ABB Robotics, Allen Bradley, Hewlett-Packard, Hitachi, Omron, and Mitsubishi. More vendors means better product choice. In theory, the open standard fieldbus offers the users the 'pick and mix' solution. However, when things go wrong, it may be difficult to nail down which vendor's device is responsible for the fault. To prevent this problem from

By S.B. Khoh

surfacing, all devices must undergo strict interoperability and conformance exercise before delivery to the end-users. Nevertheless, open standard tends to survive longer than a proprietary solution and become the de-facto standard.

The most important criteria in selecting a fieldbus network are not technical but political [35]. However, this does not mean that the technical constraints are unimportant. The technical constraints should always reflect the real user needs, which include the organisational and management constraints. For example, although fieldbus A is better than fieldbus B technically, fieldbus B may be chosen as the solution based on management grounds that it is more cost effective and readily available. In addition, there is no global solution as to which fieldbus to use. A successful implementation in one organisation may result in total disaster in another organisation. This is why there are so many proprietary and open fieldbus standards available to date.

There are a few general guidelines to consider when choosing the right network for the right level of operation. These include the network size, real-time capability and data volume requirements. Table 2.1 (Page 2-7) summarises the characteristics of each level's network in the hierarchy.

#### 2.2.3 Intelligent instruments

The use of fieldbus has contributed to the development of intelligent instrument for industrial automation. In order for the fieldbus communication to take place, the field devices are now furnished with microprocessors and digital interfaces. With an onboard microprocessor, the instrument can now

perform some 'thinking' process, hence the birth of intelligent devices. An intelligent device is more aware of its environment and surroundings through its sensors and clever software algorithm. The availability of low cost but more powerful silicon has also helped to make the dream of intelligent devices a reality. The development has enabled some of the intelligence or features previously resident in automation computers to be installed in these intelligent field devices.

## 2.2.4 Intrinsically Safe Fieldbus

The intrinsically safe version of fieldbus allows fieldbus technology to be used in the chemical and petro-chemical industries. This involves the use of special electronic line drivers to prevent ignition arising from electrical short-circuits or temperature rises. Essentially, they are the same as the non-intrinsically safe devices, except that special interface protection allows them to be used in hazardous conditions. A point must be made that intrinsically safe fieldbus is never certified for safety critical applications such as nuclear plant.

## 2.2.5 ISO/OSI 7-layer model[88]

As mentioned before, fieldbus is a low level industrial computer network optimised for real-time control. At the simplest form, it serves as a common communication medium which links the sensors, actuators and instruments in the manufacturing process control using a single cable bus. This scenario of networking sensors and actuators using fieldbus is analogous to networking computers in offices for information and resource sharing through a single wire bus. The difference is that conventional TCP/IP systems that use the Ethernet signalling as the backbone are optimised for file transfers. Data packet size of 1,500 bytes is typical. In addition to this, Ethernet signalling is non-

By S.B. Khoh

deterministic and deteriorates exponentially when transmission bandwidth overshoots 33%. These higher level communication networks are not suitable for real-time control purpose. Since fieldbus is a form of computer network, it can be referenced using the ISO 7498 OSI model as shown in Figure 2.5.

Figure 2-5 The ISO 7 layer model and reduced stack fieldbus model

As all fieldbusses use base-band transmission technique, they do not need to implement the full 7 layers of the OSI. Furthermore, more layers mean more time overheads involved, which is not desired in the real-time control entity. Therefore, all fieldbus protocols use the reduced stack 7 layer OSI model (i.e. the 3 layer model) for fast network response time as shown in Figure 2.5.

By S.B. Khoh

## 2.3 Discrete Control System

Fieldbus control system is discrete in nature where the system monitors the process under control at a discrete distant of time. The time distant maybe 500µs, 6ms, 30ms etc. depending on the criticality of the real-time system. In general, the discrete control system utilising fieldbus technology falls into two categories, i.e. event-triggered or time-triggered control systems.

## 2.3.1 Time-Triggered

Time-triggered system, also known as sampled-data system, involves the sampling of data and execution of control sequence at predefined time interval. This approach allows synchronisation and simultaneity in carrying out the control sequence. The fundamental mechanism in realising this method of control, i.e. time-triggered system, is through the use of polling. All the device's data on the fieldbus are polled and their states are updated at a discrete time interval. The advantage of this approach is that the network bus traffic is predefined. The bus loading for a time-triggered fieldbus is almost constant, regardless of devices' activities.

#### 2.3.2 Event-Triggered

On the other hand, event-triggered system only acts when there is a change of state within the device occurring. For example, if a switch is not triggered, there will not be any message on the bus. The notion of this event-triggered system allows lower bus loading when there is not much activity going on, except for the 'heart-beat' messages. However, when everything starts to happen at once, there is a risk of overloading the transmission bandwidth, or delaying of time-critical messages if not designed properly.

Fieldbus utilising the event-triggered approach normally has special priority allotted for the safety critical and time critical data. For example, when an alarm condition is encountered, a special high priority message may be used to ensure that the safety and time critical alarm message do get through irrespective of the network traffic condition. Nevertheless, there will always be some network traffic for the "heart-beat" message<sup>2</sup> when the system is idle. In real-life fieldbus implementation, a mixture of the event-triggered and time-triggered approach is used.

## 2.3.3 Time Consistency

Time consistency means that the set of values available on a given control device is identical to the samples of the states of the next lower devices at the same sampling instant [36]. For example, the DeviceNet scanner will issue the bit-strobe command to sample the data from all the devices (i.e. lower devices) on its scan list. If the system fulfils the time consistency criterion, then all the data values on the lower devices, e.g. photosensor input, flex input/output, pneumatics on/off states will be the same as those data values sampled by the scanner at the same sampling instant.

## 2.3.4 Space Consistency

Space consistency means that the value of the sampled data will be the same and identical throughout the network regardless of where the controller is situated, i.e. data consistency throughout the network [36]. The global acknowledgement of Controller Area Network (CAN) protocol, where all the

By S.B. Khoh

<sup>&</sup>lt;sup>2</sup> "Heart-Beat" message is the message to tell the consumer of the data (client) that the producer of the data (server) is still alive. This will enable the proper countermeasure to be taken by the control system should the server become faulty and fail to provide the required parameters.

nodes receive, verify and acknowledge the same data fulfils the spatial consistency of fieldbus implementation. In other words, space consistency ensures that different copies of the data transmitted will be identical at the same sampling instant.

## 2.4 Conformance to the Open Standard Fieldbus

Conformance is very important in a multi-vendor, multi-product open standard scenario. The effect of not conforming to the open standard can lead to the loss of user confidence on the standard. For example, when IBM opened the PC architecture to the vendors, only those 100% compatible PCs survived the strong competition. Those vendors with 95% compatibility systems eventually lost their share of the market. The lesson learnt from the personal computer industry can be applied to the open standard fieldbus industry in general.

What happens if we have a 95% conformed device for an open standard fieldbus? At some point during its operation, the device will disrupt the network due to the incompatibility problem. This compatibility issue has resulted in the extensive use of the term interoperability. The interoperability of devices becomes the acid test for an open standard fieldbus. Every open standard fieldbus is trying to get the devices to work harmoniously on the same network, even if they come from different vendors.

Interoperability and interchangeability are the buzzwords C. Ajluni [37] used to describe the open standard fieldbus devices. It is also the intention of this thesis to look into the interoperability and interchangeability aspects of an

open standard fieldbus, i.e. DeviceNet. This leads to the proposed design and development of a conformance test engine for the conformance testing of DeviceNet devices. The interoperability testing is discussed in Section 4.5.5.

## 2.5 Future of Fieldbus

The use of fieldbus is almost certain to increase in factory automation as well as building automation. Fieldbus will do to the control and instrumentation industry what the networked PCs did to the office automation. To date, however, there is no one fieldbus that caters for all of the manufacturing world's needs. The scenario always consists of various fieldbus standards working in concert to achieve this new era in production control. For example, Profibus, WorldFIP, Lonworks, CAN based network (e.g. DeviceNet, SDS) and others have different roles to play in the scene. Conversely, each company's choice of fieldbus is unlikely to be based on the technical aspects. Already different suppliers of automation control system hardware are pushing different fieldbusses, with the result that, even though the fieldbus may not be proprietary, the choice of fieldbus and supplier are not independent decisions.

One of the major reasons why fieldbuses have not been used more widely is the lack of availability of automation products with the communication capability. This will ease over the next year or two, but the fieldbus that is most likely to be widely adopted will be the one which has the widest range of compatible products in the market first and a large installed nodes.

In another development, the European Comission has initiated the Pre-Normative Requirements for Intelligent Actuation and Measurement (PRIAM) project to study the implication of intelligence in field devices [38]. PRIAM (an ESPRIT project) has also developed many prototype tools to assist effective application of the fieldbus technology in Europe. In order to review and enhance the findings of PRIAM project, the European Intelligent Actuation and Measurement Group (EIAMUG) was formed in 1994. The goal of EIAMUG is to shift the evolution of plant automation from current emphasis on control towards an integrated structure of control, maintenance and technical management function, or Control, Maintenance and technical Management (CMM) in short [39].

# CHAPTER 3 THE DEVICENET FIELDBUS

DeviceNet is one of the low level open standard fieldbusses suitable for real-time control in industrial applications. It uses the proven Controller Area Network (CAN) technology as a backbone. CAN's high performance error detection mechanism and good electromagnetic immunity make DeviceNet feasible to be used safely in the noisy factory environment. The high volume of CAN silicon used in production cars make DeviceNet implementations cost effective in simple, low cost field devices.

## 3.1 Overview of CAN

CAN was originally designed as in-vehicle network by Bosch, Germany in 1986 for distributed real-time control [40]. Work on designing CAN protocol began in 1981 when the engineers at Bosch were faced with the task of establishing real-time communication between three electronic control units (ECUs), i.e. engine management unit, anti-lock brakes and automatic transmission control. Conventional universal asynchronous receiver/transceiver (UART) interface for point-to-point communication (one-to-one relationship) has immediately became unusable for multi-microcontrollers communication (many-to-many relationships). In addition, the use of electronics in vehicle is increasing each year. These electronics systems are getting more complex and sophisticated which resulted in the increase size of the wiring harness. Today's

Mondeo for example, uses a total of 1.5km of wiring [41]. It was apparent that CAN protocol needed to be developed not only to replace the conventional UART interface, but also to reduce the wiring harness so as to increase the manufacturability of modern vehicles.

The term Controller Area Network (CAN) was coined by Professor Lawrence of Fachhochschule Wolfenbüttel in Germany as the design neared its completion. After the protocol launch in 1986, the first CAN silicon was available from Intel in summer 1987. The first production car using the CAN technology was rolled out from production in 1991. CAN was used to interlink the 5 electronic control units (ECUs) of this luxury car, Mercedes S Class at a baud rate of 500 kbit/s [40].

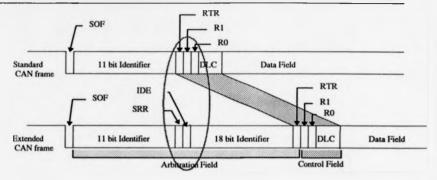

#### 3.1.1 The ISO 11898 Standard

By 1993, CAN became the ISO 11898 [42] and ISO 11519-2 [43] standards for information exchange and real-time control in road vehicles. It has been widely used on many production cars including BMW [44], Jaguar [45] and Mercedes for high speed information exchange and real-time control between Electronic Control Units (ECUs) such as the engine management unit and Anti-lock braking System (ABS). Other innovative CAN automotive applications include the Mercedes-Benz's Electronic Stability Program (ESP - where driving on a frozen lake without losing control is possible) and Lucas's intelligent brake developed under PROgraMme for a European Traffic with Highest Efficiency and Unprecedented Safety (PROMETHEUS) project, as well as Arnold Schwarzenegger's High Mobility Modular Wheeled Vehicle (HUMMER) [41].

## 3.1.2 CAN Industrial Applications

Today, CAN technology is not only being used extensively in the automotive sectors, it can also be found in many industrial applications. Until 1995, over 10 million CAN chips were sold, of which the automotive industry only accounted for 3 million, while the other 6 million chips were used in non-automotive applications [46]. This reflected the popularity and wide acceptance of the technology in industry [47, 48, 58]. The use of Carrier-Sense Multiple Access/Collision Detection + Non-Destructive Bitwise Arbitration (CSMA/CD + NDBA) technique for guaranteed network latency time and a bit rate of up to 1Mbit/s makes CAN an ideal control network in a wide variety of real-time applications [49, 50]. Its high immunity against electromagnetic noise enable it to work in harsh electromagnetic environments [51, 52].

In addition, the high quantity of CAN chips available from Intel, Philips, Motorola, National Semiconductor, NEC and Siemens for automotive applications, helps lower the CAN implementation costs. The cost effectiveness of CAN technology allows network interface to be implemented directly onto low cost devices such as the proximity switches and photosensors in the automation field. With its many technical advantages, it is evident that the cost effective CAN technology can be used in industrial automation, with many other applications that are yet to be discovered [43, 53].

#### 3.1.3 Higher Layer Protocols using CAN

In order to adapt the CAN technology efficiently in the automation world, new application layer protocols and standards need to be defined to realise a truly open networking standard. Many higher layer protocols based on CAN technology have been developed in recent years for industrial

applications. Among them are CANOpen (CAN Application Layer profiles) [17, 18], CAN Kingdom [19], DeviceNet [53] and Smart Distributed System (SDS) [22, 23] open standard fieldbusses. There are also numerous proprietary CAN industrial implementations which include the marine navigational equipment (NAVICO), Philips medical equipment [54], aerospace electronics [55, 56], lift controls, building automation and access control [57].

## 3.2 DeviceNet - A Higher Layer Protocol

DeviceNet protocol was designed by Allen Bradley, USA for industrial automation. Since its launch in Spring 1994, DeviceNet has joined the many open standard fieldbusses available today for real-time control and communication in the process control automation. A year later, DeviceNet had become the property of the Open DeviceNet Vendors Association (ODVA). ODVA consists of a consortium of companies who developed DeviceNet products.

Even though CAN network can support numerous bus rates, DeviceNet standard chooses to support only 3 operating baud rates, i.e. 125 kbit/s, 250 kbit/s and 500kbit/s. According to a conducted survey [58], more than 66% of fieldbus applications require a bus length of less than 100 metres, and only 3% of the fieldbus applications require a length of more than 1000 metres. This statistic makes DeviceNet, which supports a maximum bus length of 500 metres (refer Table 3-1), an ideal candidate for networking sensors and actuators in automation islands.

Table 3-1 The DeviceNet Baud Rate and Bus length

| Baud Rate   | Bus Length (Metres) |

|-------------|---------------------|

| 500 kbit/s  | 100                 |

| 250 kbit/s  | 250                 |

| 125 kbit/s† | 500                 |

<sup>†</sup> All DeviceNet devices are default to operate at 125kbit/s.

## 3.2.1 The Network Topology

DeviceNet network uses linear bus network topology with 121Ω terminators (1% metal film, ¼ Watt resistor) at both ends of the trunk line. The bus network topology allows easy node connection and detachment from the trunk, without affecting other communicating nodes. The network can also be configured with various branches on the drop lines [59], thereby enhancing the flexibility of the network configuration. Each DeviceNet cable consists of 5 wires for CAN High and CAN Low signals, Power (+24V), Ground and Shielding. The power bus allows a maximum of 8 amperes of current to be drawn from any point of the thick trunk cable. This allows simple devices such as photosensors and proximity switches to be powered directly from the DeviceNet network. There are restrictions which govern the power consumption and cumulative drop length defined in the DeviceNet specification.

A DeviceNet network is capable of supporting 64 physical nodes, with up to 6 meters of drops via the tee-junction at the trunk line. The long drop cables offer the flexibility to route DeviceNet devices at difficult corners. Every DeviceNet device must have a unique Media Access Control Identifier (MACID) such that no two nodes will transmit the same data packet. The valid