# COORDINATED MANAGEMENT OF THE PROCESSOR AND MEMORY FOR OPTIMIZING ENERGY EFFICIENCY

A Dissertation

Presented to

The Academic Faculty

By

Karthik Rao

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology

August 2018

# COORDINATED MANAGEMENT OF THE PROCESSOR AND MEMORY FOR OPTIMIZING ENERGY EFFICIENCY

#### Approved by:

Dr. Sudhakar Yalamanchili, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Yorai Wardi, Co-Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Magnus Egerstedt School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Saibal Mukhopadhyay School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Santosh Pande School of Computer Science Georgia Institute of Technology

Dr. Joseph Greathouse Senior Member of Technical Staff *Advanced Micro Devices Inc.*

Date Approved: May 14, 2018

# कर्मण्येवाधिकारस्ते मा फलेषु कदाचन । मा कर्मफलहेतुर्भूमी ते सङ्गोऽस्त्वकर्मणि ॥ २-४७

You have the right to work only but never to its fruits.

Let not the fruits of action be your motive, nor let your attachment be to inaction.

Bhagavad Gita Chapter 2 Verse 47.

#### **ACKNOWLEDGEMENTS**

## गुरुर्ब्रहमा गुरुर्विष्णुर्गुरुर्देवो महेश्वरः । गुरुः साक्षात् परब्रहमा तस्मै श्री गुरवे नमः ॥

The Guru is Brahma (creator); the Guru is Vishnu (protector); the Guru is Maheshwara (destroyer). The Guru is verily the Supreme Brahman. I offer my salutations to that Guru, the remover of my darkness and my ignorance.

To my advisers, my *Gurus*, Dr. Sudhakar Yalamanchili and Dr. Yorai Wardi, I offer my sincere salutations. They have been the guiding lights in my journey through graduate school. The technical discussions were truly enriching and have expanded my perspective not just in my own area of research but on research in general as well. They have taught me to appreciate the art of identifying subtle insights and also the rigor involved in presenting ideas in a crisp and articulate manner. Looking back at my first meeting with both of them five years ago, when I was quite unsure about working in computer architecture, I can now say safely that I am a better engineer and hopefully a better researcher because of their guidance. Their general life advice and subtle course corrections have steered my ship to where it is now. I will never forget the non-technical discussions with Dr. Wardi that spanned a plethora of topics. Remembering Dr. Wardi's words, "You are not out of my orbit yet!", I eagerly look forward to continuing this relationship with both my advisers.

I would also like to thank my committee Dr. Magnus Egerstedt, Dr. Saibal Mukhopadhyay, Dr. Santosh Pande and Dr. Joseph Greathouse for providing their valuable suggestions and comments that have improved the quality of this thesis. I must thank Dr. Egerstedt in particular for introducing me to my advisers. Special thanks to Dr. Joseph Greathouse for believing in my abilities and bringing me to AMD Research.

My graduate studies have been generously supported by multiple sources and I would like to thank them profusely viz. NSF, Huawei and AMD. The internship at Huawei Technologies, that essentially decided my thesis topic, was made possible by my mentor Jun

Wang and manager Handong Ye. The constant encouragement given by Jun, Zongfang Lin and other colleagues at Huawei made me productive and insightful discussions lead to my very first patent applications.

During the six years at Georgia Tech, I had the privilege of interacting and sharing lab space with members from the CASL and GRITS Labs. I am very grateful to William Song, Minhaj Hasan, Eric Anger, Jin Wang, Xinwei Chen, Chad Kersey, Tine Blaise, Hugh Xiao, Matt Hale, Thiagarajan Ramachandran, Maria Santos, Tina Setter, Swamit Tannu, Gururaj Saileshwar and many others. The course homeworks, research collaborations and many discussions over coffees have helped me stay afloat. I look forward to maintaining the same level of communication in the future as well.

A heartfelt thank you to all my teachers who helped shape my career, especially K. Subrahmanya Bhat, Mrs. Shahin Masood, Dr. Kumara Shama, Dr. U.Sripathi, Dr. M.S.Bhat, Chirag Jain, Dr. Kadagattur Srinidhi, Dr. Ed Coyle and many others. I would be remiss if I do not thank Sundar, Garima and Dhawal, who believed in me right from our undergraduate days at Manipal. To Megha Sandesh, Ayush Sharma and many other friends at Georgia Tech, thank you for all the philosophical exchanges. Words are insufficient to express my gratitude to "Dhani" Shishir Kolathaya, who held me up during tough times. I am indebted to him. To my partners in crime, my roommates at one time or the other, my brothers, Kaivalya Bakshi and Srinivas Hanasoge. Our "conferences" on every little topic under the sun, shall never be forgotten. The joys, sorrows, frustrations and successes we shared will undoubtedly make for a good laugh later on.

My parents Jyoti Umesh and Govindarao Umesh, my sister Deepa, my grandmother Puttalakshmi and my foster parents in the US, Mr. Bhaskar and Dr. Jayanthi Srinivasiah have been my pillars of moral support since the very beginning. Without their encouraging words during tough times, I do not think I would have made it thus far. My father, a professor himself, deserves a special mention especially since he helped me edit this thesis. I aspired to be like him since my childhood and I hope I have made him proud.

### TABLE OF CONTENTS

| Acknow    | rledgments                                                         | V   |

|-----------|--------------------------------------------------------------------|-----|

| List of T | Tables                                                             | xii |

| List of I | Figures                                                            | xiv |

| Chapter   | r 1: Introduction                                                  | 1   |

| 1.1       | Thesis Statement                                                   | 3   |

| 1.2       | Thesis Organization                                                | 8   |

| Chapter   | r 2: Problem Formulation and Related Work                          | 11  |

| 2.1       | The Memory Wall                                                    | 11  |

| 2.2       | Power, Energy and Thermal Management of Processors and Memory      | 13  |

|           | 2.2.1 Dynamic Voltage and Frequency Scaling (DVFS)                 | 13  |

|           | 2.2.2 CPU Idling                                                   | 17  |

|           | 2.2.3 Microarchitecture Optimizations                              | 18  |

|           | 2.2.4 OS, Compiler Optimizations                                   | 18  |

| 2.3       | Coordinated Management of Processor and Memory                     | 19  |

| 2.4       | Summary                                                            | 20  |

| Chantei   | r 3. Parformance Power and Energy Characterization: Mobile Devices | 22  |

| 3.1    | Overvi  | iew                                                 | 22 |

|--------|---------|-----------------------------------------------------|----|

| 3.2    | Metho   | odology                                             | 24 |

|        | 3.2.1   | Experimental Testbed                                | 25 |

|        | 3.2.2   | Hardware and Software Testing Options               | 27 |

|        | 3.2.3   | Other Factors                                       | 29 |

| 3.3    | Result  | s                                                   | 30 |

|        | 3.3.1   | Compiler Optimizations and Thread Level Parallelism | 30 |

|        | 3.3.2   | CPU Governors                                       | 33 |

|        | 3.3.3   | Memory Bandwidth Governors                          | 35 |

|        | 3.3.4   | GPU Governors                                       | 38 |

|        | 3.3.5   | Cross Effects                                       | 39 |

| 3.4    | Summ    | ary                                                 | 45 |

| Chapte | r 4: Co | ordinated Control: Mobile Devices                   | 47 |

| 4.1    | Overvi  | iew                                                 | 47 |

| 4.2    | Motiva  | ation                                               | 50 |

| 4.3    | Contro  | oller Design                                        | 52 |

|        | 4.3.1   | Offline Profiling                                   | 52 |

|        | 4.3.2   | Online Controller                                   | 55 |

|        | 4.3.3   | Implementation Challenges                           | 59 |

|        | 4.3.4   | Applications                                        | 60 |

| 4.4    | Evalua  | ation                                               | 61 |

|        | 4.4.1   | Results and Analysis                                | 62 |

|         | 4.4.2 Application Scope                                                              | 70  |

|---------|--------------------------------------------------------------------------------------|-----|

|         | 4.4.3 Effect of Different Background Loads                                           | 71  |

|         | 4.4.4 Comparison with CPU-only DVFS                                                  | 73  |

| 4.5     | Summary                                                                              | 74  |

| Chapter | 5: Coordinated Control: Generalization to Multi-Core Multi-Memory-Controller Systems | 76  |

| 5.1     | Overview                                                                             | 77  |

| 5.2     | Memory Controller Configurations                                                     | 78  |

| 5.3     | Performance and Power Model for a Single-Core Single-Memory-Controller System        | 79  |

| 5.4     | Optimization Problem: Single-Core Single-Memory-Controller                           | 82  |

| 5.5     | Solution Strategy                                                                    | 83  |

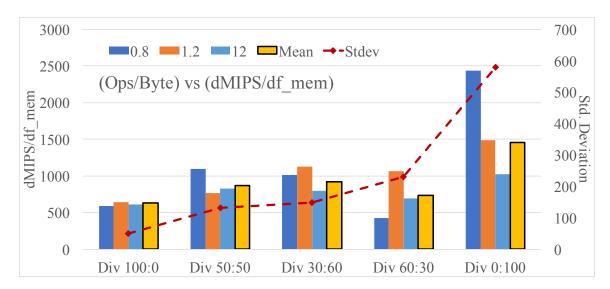

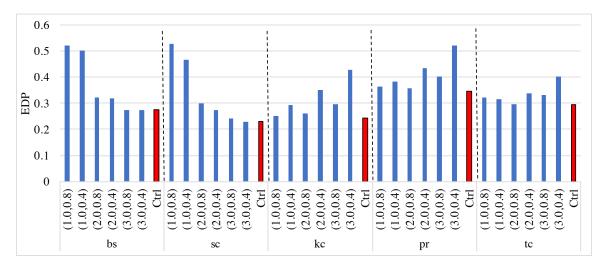

| 5.6     | Results                                                                              | 84  |

| 5.7     | Microbenchmark Characterization: Two-Cores Two-Memory Controllers                    | 86  |

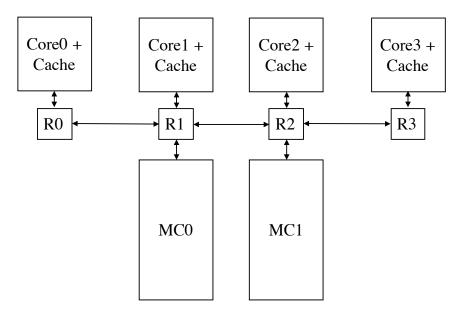

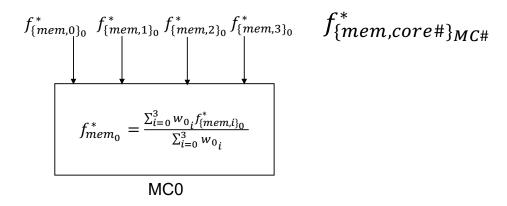

| 5.8     | Optimization Problem: Four-Cores Two-Memory-Controllers                              | 90  |

| 5.9     | Solution Strategy                                                                    | 91  |

| 5.10    | Results                                                                              | 92  |

| 5.11    | Discussion                                                                           | 93  |

| 5.12    | Summary                                                                              | 94  |

| Chapter | 6: Thermal Management: 2D Architectures                                              | 96  |

| 6.1     | Overview                                                                             | 97  |

| 6.2     | Regulation Technique                                                                 | 100 |

| 63      | Temperature Control in Multi-Core Processors                                         | 10/ |

| 6.4    | Result  | s                                                                           |

|--------|---------|-----------------------------------------------------------------------------|

| 6.5    | Summ    | ary                                                                         |

| Chapte | r 7: Ch | aracterization of a 3D Processor-Memory Architecture 117                    |

| 7.1    | Overv   | iew                                                                         |

| 7.2    | Charac  | cterization                                                                 |

|        | 7.2.1   | Experimental Framework                                                      |

|        | 7.2.2   | Nomenclature                                                                |

|        | 7.2.3   | Thermal Coupling Analysis                                                   |

| 7.3    | Summ    | ary                                                                         |

| Chapte |         | ordinated Management in 3D Architectures: Performance, Engy and Temperature |

| 8.1    | Overv   | iew                                                                         |

| 8.2    | TRINI   | TY                                                                          |

|        | 8.2.1   | System Models                                                               |

|        | 8.2.2   | Solution Strategy                                                           |

| 8.3    | Result  | s                                                                           |

|        | 8.3.1   | Benchmarks                                                                  |

|        | 8.3.2   | Analyzing TRINITY Performance                                               |

|        | 8.3.3   | Impact on Lifetime Reliability                                              |

|        | 8.3.4   | Effect of TRINITY Parameter Variations                                      |

| 8.4    | Summ    | ary                                                                         |

| Chante | r 9• Co | nclusions and Future Work                                                   |

| Re | eferen | ices               |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 174 |

|----|--------|--------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

|    | 9.2    | Future Work        | • |   | • |   |   |   | • | • | • |   |   | • | • | • |   |   |   |   | • |   | • | • |   | • | • |   |   |   |   | • | 157 |

|    | 9.1    | Thesis Conclusions | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 154 |

### LIST OF TABLES

| 3.1 | List of benchmarks suites                                                                                                                                                                          | 26       |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.2 | Table listing different options tested. ✓indicates the tested option for the benchmark group. *Except 3DMark                                                                                       | 27       |

| 3.3 | 3DMark score for different GPU governors on N6. CPU governor fixed to interactive                                                                                                                  | 38       |

| 3.4 | Performance difference when changing CPU governor from interactive to powersave, with fixed BW governor. All numbers compared against intCPU-defBW on N6                                           | 40       |

| 3.5 | Performance difference when changing BW governor from default to powers as or performance, with fixed CPU governor. Numbers compared against intCPU-defBW and powsavCPU-defBW, respectively, on N6 | ve<br>41 |

| 3.6 | Power difference when changing CPU governor from interactive to powersave, with fixed BW governor. All numbers compared against intCPU-defBW on N6                                                 | 41       |

| 3.7 | Power difference caused by changing BW governor from default to powersave or performance, with fixed CPU governors. Numbers compared against intCPU-defBW and pwrsavCPU-defBW, respectively, on N6 | €<br>41  |

| 3.8 | Performance, Power and Energy difference of different CPU and idle configurations as compared to default <i>intCPU-idleON</i> on <i>N5X</i>                                                        | 14       |

| 3.9 | Summary of tests and findings                                                                                                                                                                      | 46       |

| 4.1 | Sample table with performance and power data profiled offline for Angry-Birds application                                                                                                          | 54       |

| 4.2 | List of CPU frequencies and memory bandwidths on Nexus 6 5                                                                                                                                         | 59       |

| 4.3 | Summary of performance difference and energy savings obtained by the controller                                                                                |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.4 | Summary of performance difference and energy savings obtained for the tested applications under Baseline Load (BL), No Load (NL), Heavier Load (HL) conditions |

| 4.5 | Summary of performance difference and energy savings obtained by the CPU-only DVFS controller                                                                  |

| 5.1 | DDR3 Timing parameters for different speed grades                                                                                                              |

| 5.2 | Performance model parameters                                                                                                                                   |

| 7.1 | Simulation framework parameters. Technology node is 16nm                                                                                                       |

| 8.1 | Table demonstrating variable application heat capacities and room for improving balance between performance, temperature and energy                            |

| 8 2 | Parameters estimated offline 141                                                                                                                               |

### LIST OF FIGURES

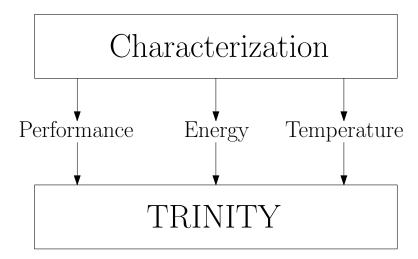

| 1.1 | Thesis Overview: Characterization of <i>three</i> parameters leading to <i>TRINITY</i> , a control theory based solution for <i>3D</i> stacked architectures                                                | 6  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

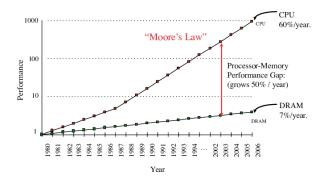

| 2.1 | Memory Wall Problem [41]                                                                                                                                                                                    | 12 |

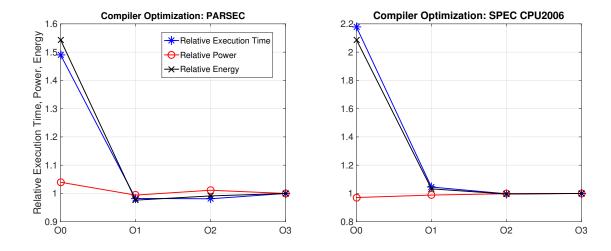

| 3.1 | Effect of compiler optimization on performance, power, and energy on <i>N6</i> . Normalized w.r.t 03                                                                                                        | 31 |

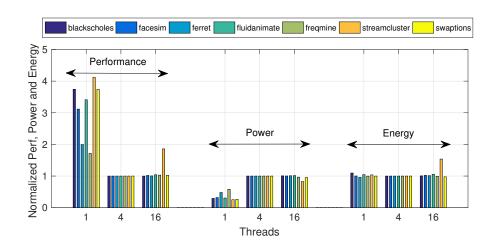

| 3.2 | PARSEC Threads: Performance, Power and Energy on <i>N6</i> . Normalized w.r.t 4 threads                                                                                                                     | 32 |

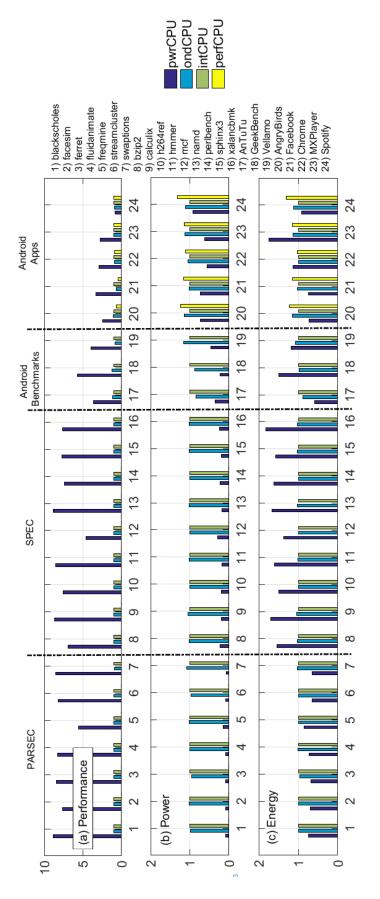

| 3.3 | CPU Governors: (a) Performance (b) Power and (c) Energy on N6. Normalized w.r.t interactive governor.                                                                                                       | 34 |

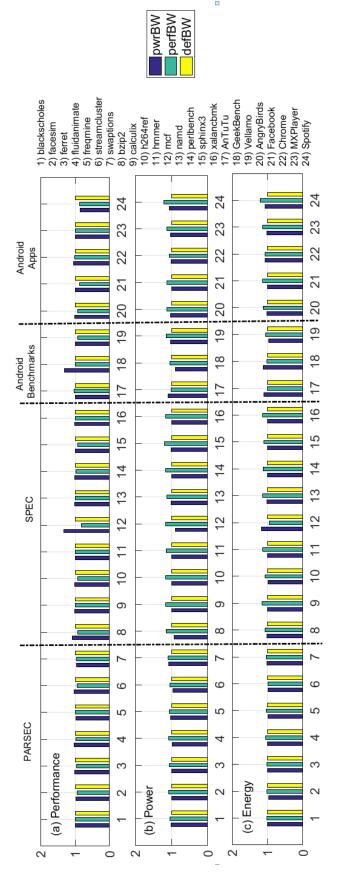

| 3.4 | Memory BW Governors: (a) Performance (b) Power and (c) Energy on N6.  Normalized w.r.t cpubw_hwmon BW governor                                                                                              | 37 |

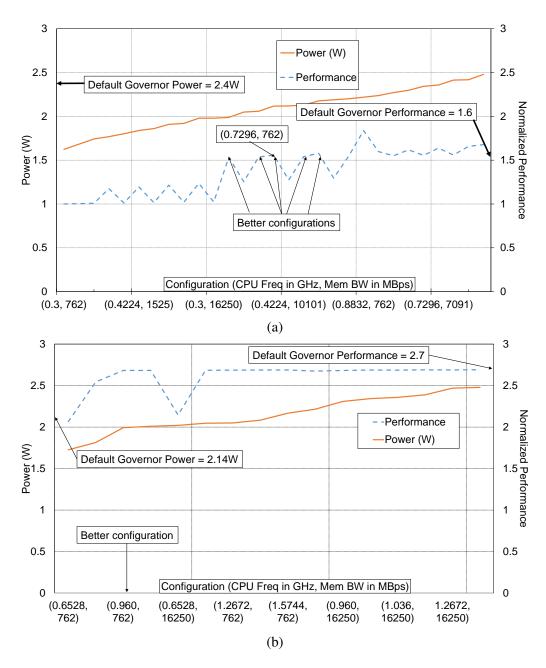

| 3.5 | (a)AngryBirds and (b)MXPlayer: Performance and Power trends on <i>N6</i> for different CPU frequencies and mem BW combinations. Performance normalized to configuration (0.3GHz, 762MBps)                   | 43 |

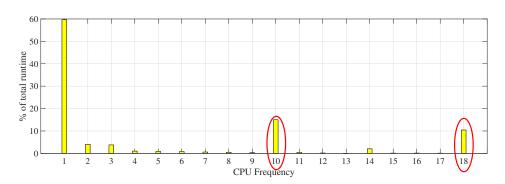

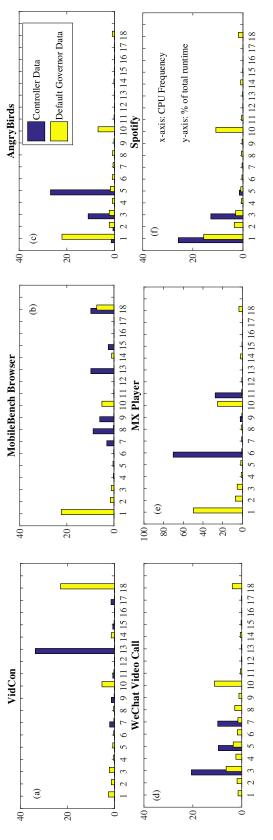

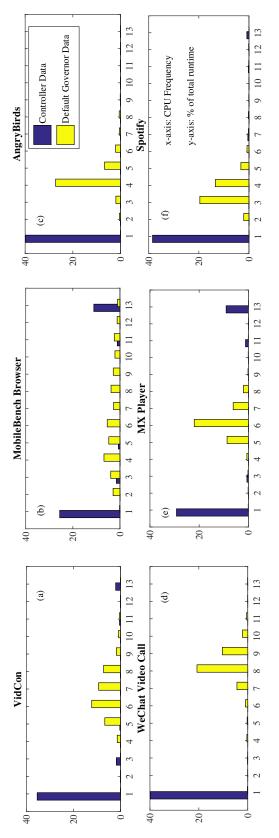

| 4.1 | Histogram of CPU frequencies for eBook application. The numerals indicated on the x-axis stand for the choice of 18 discrete frequencies (in the range $0.3-2.65 \mathrm{GHz}$ ). See Table 4.2 for details | 51 |

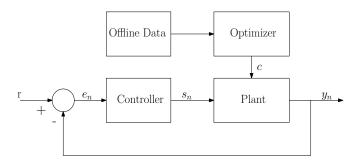

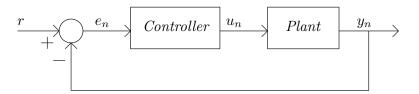

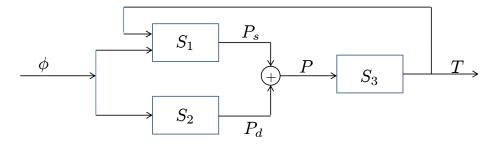

| 4.2 | Block diagram of feedback controller                                                                                                                                                                        | 55 |

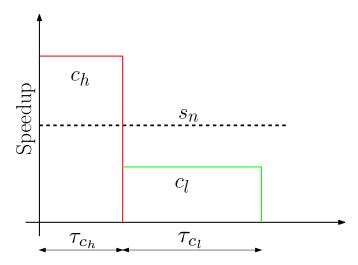

| 4.3 | Pictorial representation of the energy optimization                                                                                                                                                         | 59 |

| 4.4 | Histogram of CPU frequencies: controller vs. default                                                                                                                                                        | 63 |

| 4.5 | Histogram of memory bandwidths: controller vs. default                                                                                                                                                      | 64 |

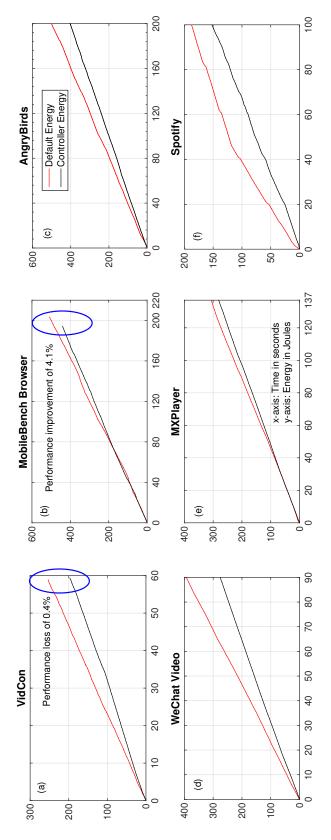

| 4.6  | Energy Consumption: controller vs. default                                            | 55 |

|------|---------------------------------------------------------------------------------------|----|

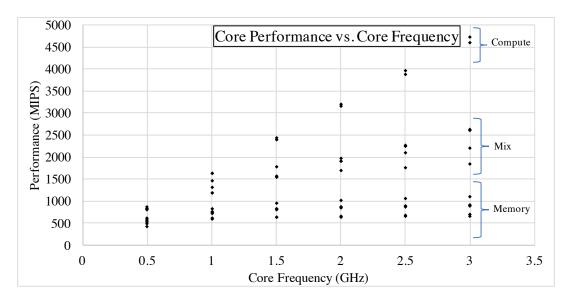

| 5.1  | Performance model for a single-core single-memory-controller system 8                 | 30 |

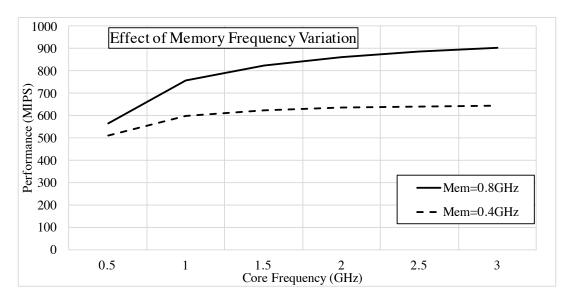

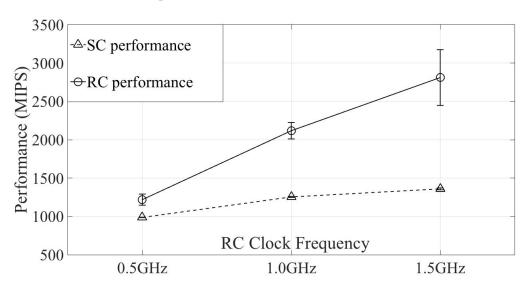

| 5.2  | Performance of a memory bound workload for different memory controller frequencies    | 31 |

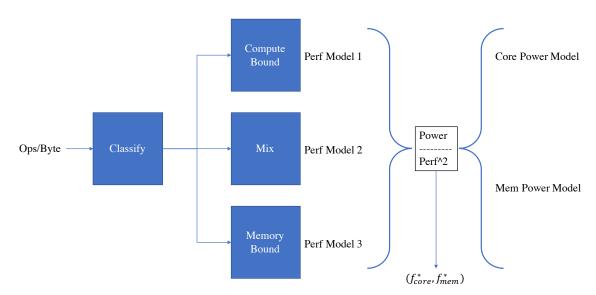

| 5.3  | Solution strategy for optimizing EDP in a Single-Core Single-Memory-Controller system | 33 |

| 5.4  | EDP Comparison: Single-Core Single-Memory-Controller                                  | 35 |

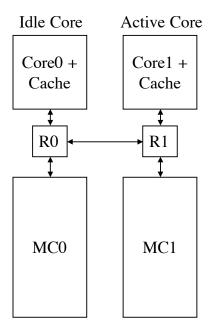

| 5.5  | Two-core two-memory-controller system for microbenchmark characterization             | 36 |

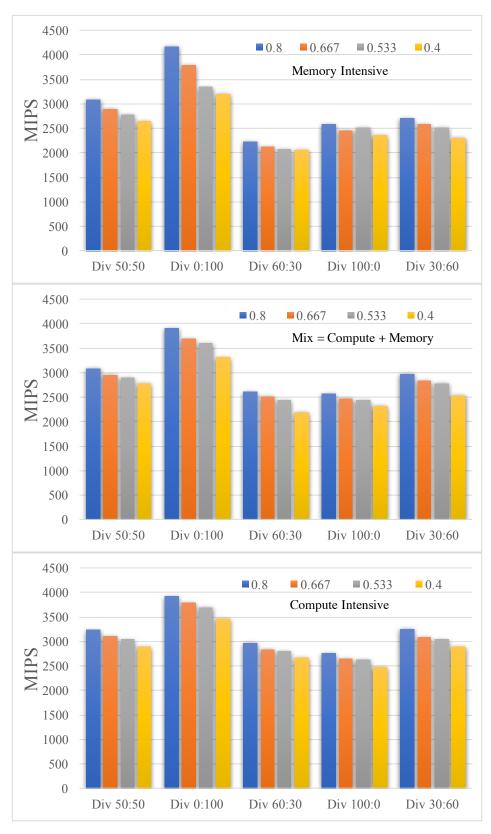

| 5.6  | Performance of a microbenchmark for different ops/Byte and memory addressing patterns | 38 |

| 5.7  | Performance sensitivity graph                                                         | 39 |

| 5.8  | Four-core two-memory-controller system                                                | 90 |

| 5.9  | Memory controller arbitration algorithm                                               | )1 |

| 5.10 | EDP Comparison: Four-Cores Two-Memory-Controller                                      | )2 |

| 6.1  | Control System Block Diagram                                                          | )0 |

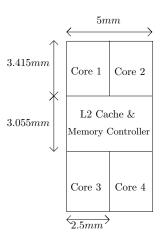

| 6.2  | System Model                                                                          | )5 |

| 6.3  | Floor Plan of the 4 Core Processor                                                    | )9 |

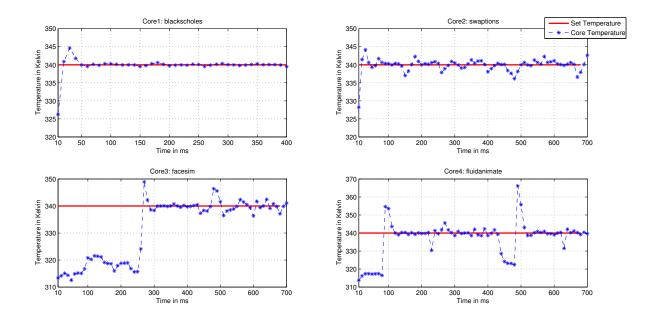

| 6.4  | Tracking results with Continuous Frequencies                                          | 12 |

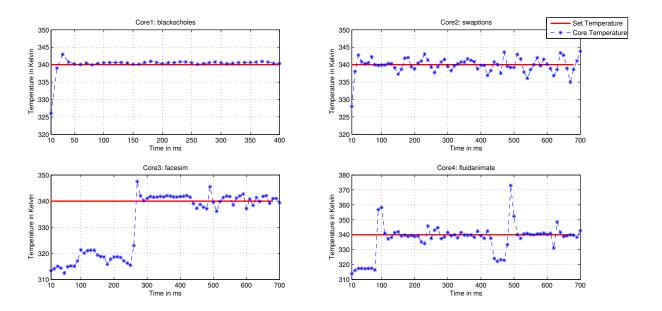

| 6.5  | Tracking results with Discrete Frequencies                                            | 12 |

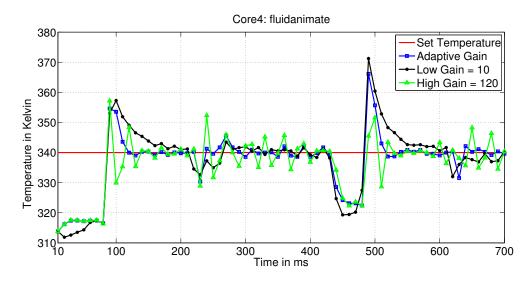

| 6.6  | Tracking results with fixed gains and variable gains                                  | 15 |

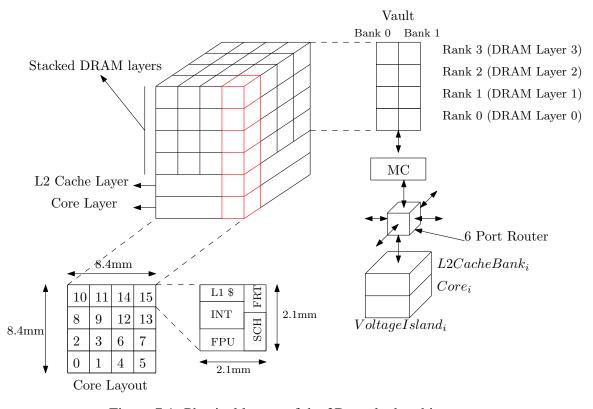

| 7.1  | Physical layout of the 3D stacked architecture                                        | 23 |

| 7.2  | Functional description of the 3D stack                                                | 24 |

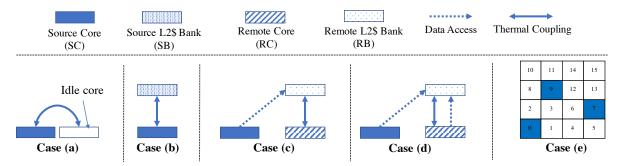

| 7.3 | Microbenchmark characterization nomenclature                                                                                                                                                              | 124 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

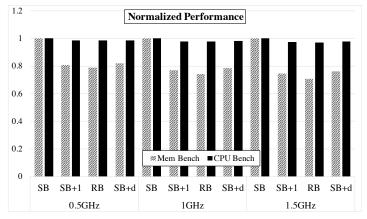

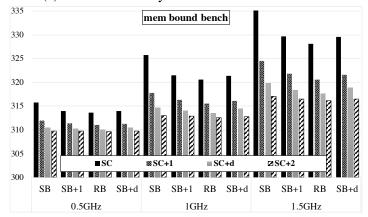

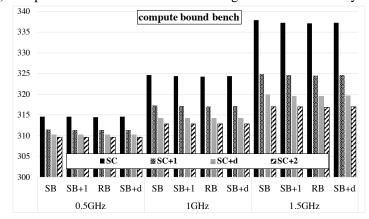

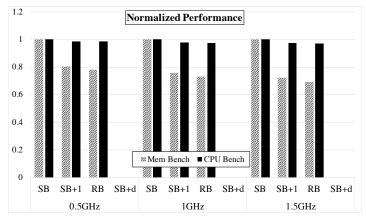

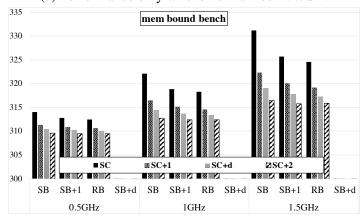

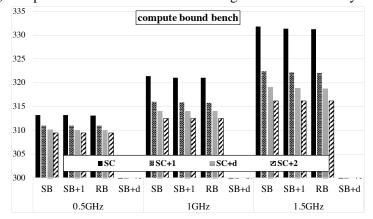

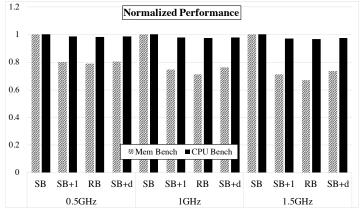

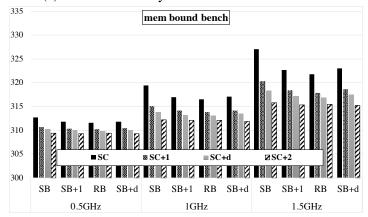

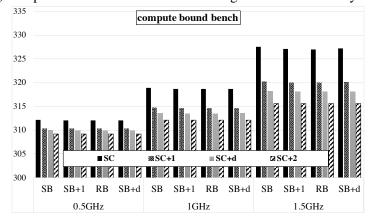

| 7.4 | Performance and temperature variation when running mem bound and compute bound benchmarks on a source core accessing source and remote cache banks at different core frequencies                          | 126 |

| 7.5 | Performance and temperature variation when running mem bound and compute bound benchmarks on a source core accessing source and remote cache banks at different core frequencies. SC is Core <sub>2</sub> | 127 |

| 7.6 | Performance and temperature variation when running mem bound and compute bound benchmarks on a source core accessing source and remote cache banks at different core frequencies. SC in Core <sub>3</sub> | 128 |

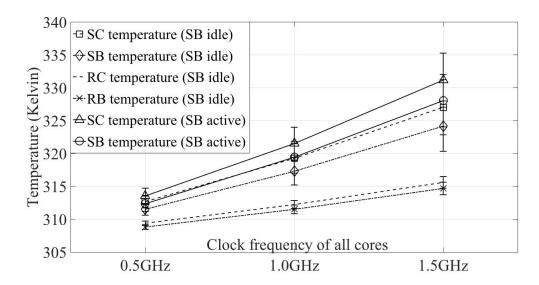

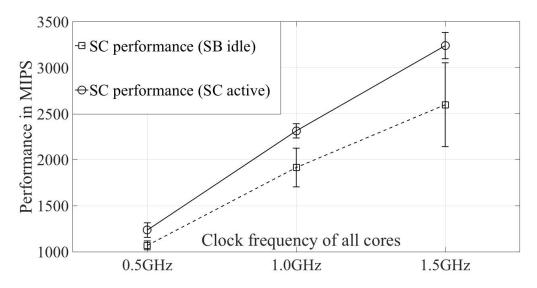

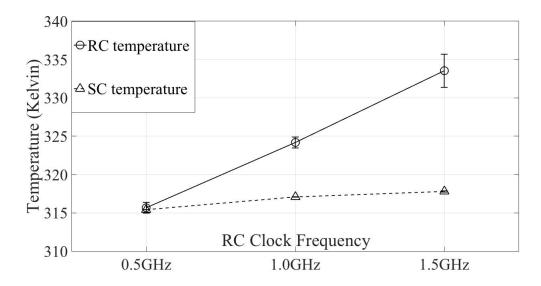

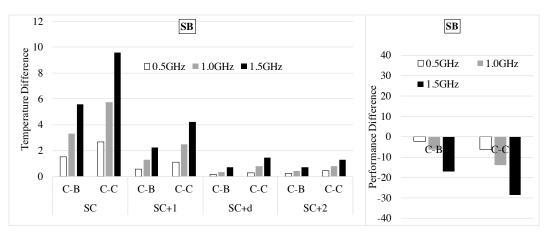

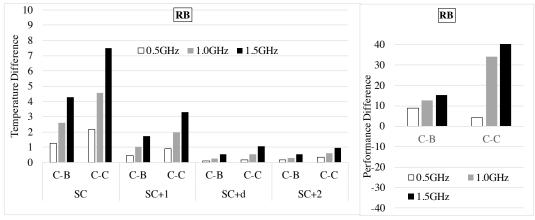

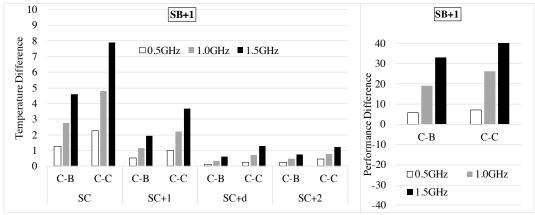

| 7.7 | Thermal coupling Cases (b) and (c). The error bars are variances in temperature due to different ops/byte and physical locations of the source core.                                                      | 130 |

| 7.8 | Thermal coupling Case (d). The error bars are variances in temperature due to different ops/byte and physical locations of the source core                                                                | 131 |

| 7.9 | Influence of package boundaries on thermal coupling and performance                                                                                                                                       | 133 |

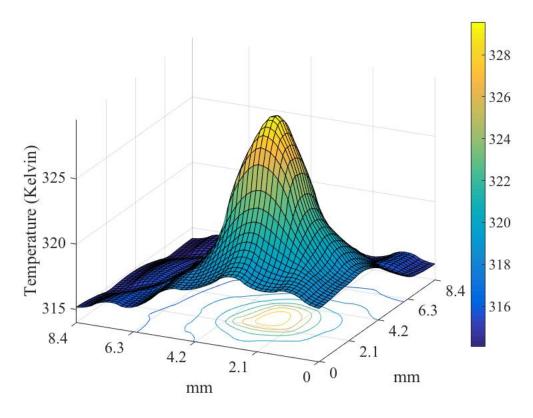

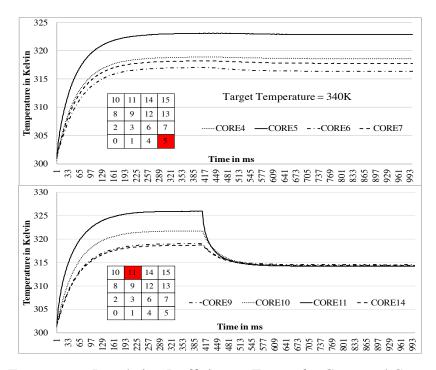

| 8.1 | Heat map of the core layer showing reduction in thermal headroom for neighboring cores                                                                                                                    | 137 |

| 8.2 | Temperature Regulation Inefficiency: Except for $Core_5$ and $Core_{11}$ , rest of the cores are idle. At $400ms$ mark $Core_{11}$ becomes idle as well                                                   | 139 |

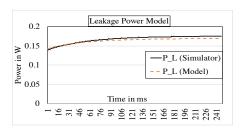

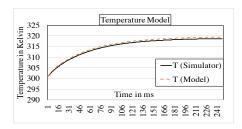

| 8.3 | Leakage power and temperature model                                                                                                                                                                       | 143 |

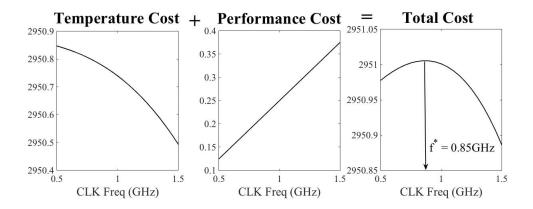

| 8.4 | Behavior of the optimization cost                                                                                                                                                                         | 145 |

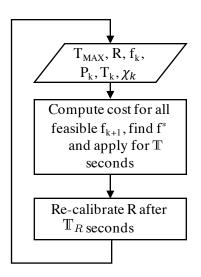

| 8.5 | TRINITY Algorithm                                                                                                                                                                                         | 146 |

| 8.6 | Pseudo code for re-calibrating $R$                                                                                                                                                                        | 147 |

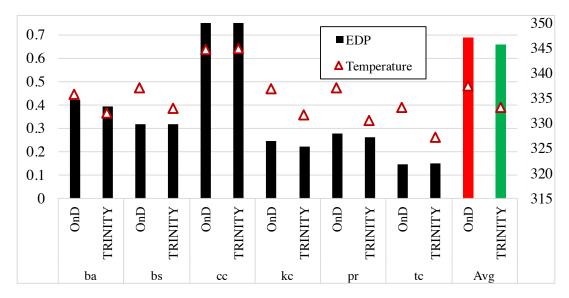

| 8.7 | Controller performance compared against the ondemand heuristic. Controller Parameters: $T=1 \mathrm{ms}$ and $T_R=1 \mathrm{ms}$ . Left y-axis and right y-axis units are EDP and Kelvin, respectively    | 149 |

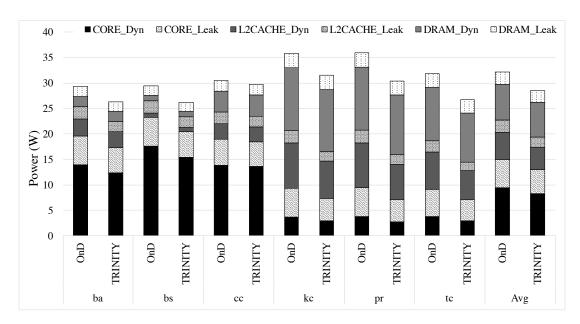

| 8.8 | Average power consumption by TRINITY compared against the ondemand heuristic. Controller Parameters: $T=1 \mathrm{ms}$ and $T_R=1 \mathrm{ms}$                                                            | 150 |

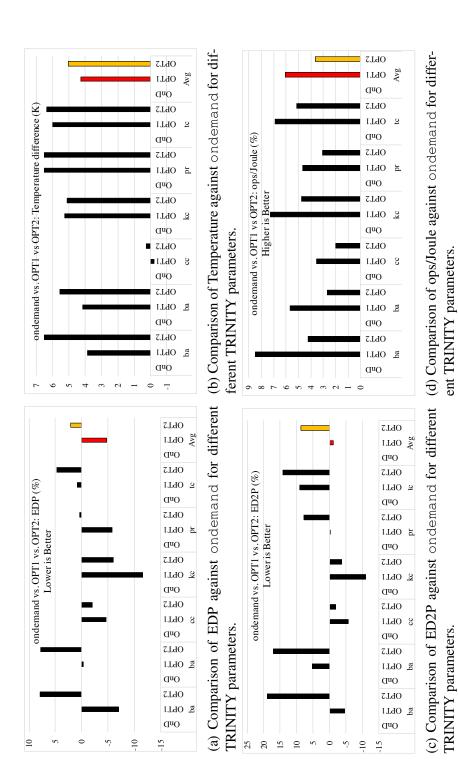

| 8.9 | TRINITY Parameter Variation                                                                                                                                                                               | 152 |

#### **SUMMARY**

Energy efficiency is a key design goal for future computing systems. With diverse components interacting with each other on the System-on-Chip (SoC), dynamically managing performance, energy and temperature is a challenge in 2D architectures and more so in a 3D stacked environment. Temperature has emerged as the parameter of primary concern. Heuristics based schemes have been employed so far to address these issues. Looking ahead into the future, complex multiphysics interactions between performance, energy and temperature reveal the limitations of such approaches. Therefore in this thesis, first, a comprehensive characterization of existing methods is carried out to identify causes for their inefficiency. Managing different components in an independent and isolated fashion using heuristics is seen to be the primary drawback. Following this, techniques based on feedback control theory to optimize the energy efficiency of the processor and memory in a coordinated fashion are developed. They are evaluated on a real physical system and a cycle-level simulator demonstrating significant improvements over prior schemes. The two main messages of this thesis are, (i) coordination between multiple components is paramount for next generation computing systems and (ii) temperature ought to be treated as a resource like compute or memory cycles.

#### **CHAPTER 1**

#### INTRODUCTION

The ever-increasing demand for better computational performance has driven several innovations at the hardware, software and microarchitectural levels. In tune with Moore's law, the microprocessor has undergone an exponential growth in performance since its advent in 1971. Simultaneously, supply voltage scaling governed by the tenets of Dennard scaling has enabled this increase in performance by keeping power consumption under a reasonable envelope. However, the bandwidth, latency and energy consumption of off-chip memories have not kept pace with their processor counterparts. The energy consumed by a DRAM access is more than twice that of a double precision floating point operation [1, 2]. The US Department of Energy estimates that 70% of the total power of a 100,000 node exascale system will be consumed by the DRAM accesses alone (See [3] and references therein). In the age of Cloud Computing, Big Data processing and the Internet of Things, applications require moving large amounts of data to and from off-chip memories. The performance of a computing system is, therefore, not a function of the processor alone. The memory system is more often than not, the bottleneck in deciding the overall performance while consuming a significant portion of the input power.

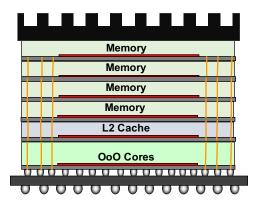

Addressing the so-called "Memory Wall", 3D packaging of silicon dice, enabled by advances such as Through-Silicon Via (TSV) technology [4], has led to the integration of memory and logic into a single package. Their footprint is small and they promise significant reductions in data movement latency and energy. Further, the 3D package provides an order of magnitude increase in memory bandwidth. For example, commercial standards like DDR3-1333 [5], DDR4-2667 [6], HBM2 [7] and HMC2 [8] realize 10.66 GB/s, 21.34 GB/s, 256 GB/s and 320 GB/s, respectively. To effectively exploit the high bandwidth provided by 3D die-stacked DRAM, multiple efforts have explored moving compute

logic inside the package as part of the die-stack, revisiting the early efforts at architecting Processing-In-Memory (PIM) designs [9, 10, 11, 12, 13, 14, 15].

Alongside high performance server computers, the world of mobile System-on-Chips (SoC) is also rapidly expanding. It is predicted that by 2020 there will be over 20 billion mobile-connected devices [16]. The mobile CPU itself has improved 10× in performance between 2009 and 2015 [17]. Furthermore, it has evolved from a single core (2009) to multiple homogeneous cores (2011) to multiple heterogeneous cores (2013). With mobile applications becoming more memory intensive, the effects of the "memory wall" are being observed on mobile SoCs as well. Complementing the mobile CPU, newer low power mobile memories such as LPDDR [18] and Wide I/O [19] have been introduced. The mobile SoCs of today are more diverse and capable with advanced GPUs, DSPs, audio/video decoders, WiFi, 3G and 4G LTE modules etc. Despite this, the two pillars defining performance of such systems continue to be the mobile CPU and the memory.

As transistor sizes get smaller, effects due to leakage currents and subthreshold voltages, which are not accounted for in Dennard scaling rules, start to to play a dominant role. Since the breakdown of Dennard scaling in 2006, microprocessor performance scaling has demanded a more detailed understanding of the multi-physics interactions between performance, energy and temperature of the computing environment. While 3D stacking of memory and logic die delivers an order of magnitude improvement in available memory bandwidth, the price paid, however, is tighter thermal constraints. Due to thermal shielding, the logic die temperatures can reach unsustainable levels, thereby placing an upper limit on clock frequencies (and hence performance). Furthermore, large localized temperature variations across different layers of DRAM and logic die can lead to detrimental effects on the performance and reliability. It is therefore natural to ask the following questions: How should one go about managing such computing environments? Is it beneficial to expect a 'balance' between achievable performance and the physics of the device?

Attempting to answer these questions inevitably leads to a related, yet important, issue:

the choice of the optimization metric. *Power efficiency* and *energy efficiency* are two commonly used metrics. Power efficiency is measured as the ratio of Watts of power dissipated for a given number of operations executed, whereas energy efficiency is measured as the ratio of Joules of energy consumed for a given number of operations executed. In most of the research efforts in the past, the third parameter, temperature, is included in the problem definition only as a constraint to be observed. Minimizing power or energy consumed subject to performance constraints, a problem definition which falls in the same categories, have also been considered. The choice of the metric is strongly influenced by the platform i.e. mobile SoC or server class processor, primarily because the end-user demands vary widely. While a mobile phone user requires consistent performance and a long battery life, a server processor typically demands the best performance.

Researchers have proposed and implemented innovative techniques to manage processor and memory system power at various levels of the hardware and the software stack. For the processor, hardware-level power management methods such as clock gating, aggressive CPU idling and Dynamic Voltage and Frequency Scaling (DVFS) help in reigning in excess power consumption. Similarly on the software end, optimized application code, per-module governors implementing DVFS and software enabled low-power modes help to save power. Power management of memory systems involve dynamic frequency scaling, dynamic bandwidth throttling and multiple power-down states. Since the 3D stacked memory is a relatively new technology, limited studies on dynamic power and thermal management have been reported (see [20, 21, 22]). However, as discussed in CHAPTER 2, there is a need for detailed investigations to achieve higher efficiency levels.

#### 1.1 Thesis Statement

While the power/energy/thermal management methods proposed so far work well in general, more often than not, these methods implement their respective policies for distinct elements in an independent and isolated manner. A few studies ([23, 24, 25]) have shown that

independent power/performance control strategies can lead to conflicting policies causing performance and/or power losses. Addressing this problem, researchers have investigated the coordinated control of different hardware subsystems on servers [23], System-on-Chips (SoC) [26, 27, 28], heterogeneous architectures [24] and embedded systems ([29] and references therein). Looking ahead into the future, computing platforms such as servers are expected to process exabytes of data using (a) heterogeneous cores, (b) specialized and dedicated hardware (accelerators) and (c) high-bandwidth low-latency memories. Similarly, mobile devices powered by increasingly heterogeneous SoCs are expected to be highly energy efficient while providing the best end-user experience. Techniques proposed until now either, (a) optimize only power consumption, (b) are not amenable to expanding the scope of the solution or (c) are based on heuristics. Heuristics based solutions have been the state-of-the-art and state-of-the-practice primarily because of their simplicity and practical implementation constraints. However, the tight physical and functional coupling between the major components (processor and memory) require much better power, energy, performance and thermal management strategies that go past the achievable boundaries set by heuristics. These challenges lead to the main theme of this thesis: *Interactions* between (a) thermal behaviors (b) compute and memory microarchitecture and (c) application workloads necessitate the management of performance, energy and temperature in a coordinated fashion. Control theory inspired approaches to coordinate the power management of the processor and memory can dynamically trade-off performance, energy and temperature, both leading to better energy efficiency.

In order to go beyond heuristics based approaches, this thesis makes a case for exploiting the rich set of tools available from fields such as mathematical optimization and control theory. Feedback controllers have been employed to regulate power, throughput and temperature of the processor [30, 31, 32, 33]. There have also been research efforts that sought to optimize power, performance-per-watt, performance-per-joule etc. using more complex tools such as Model Predictive Control (MPC) [34, 35, 36]. The approach presented in

this thesis is along the lines of the aforementioned works. However, the results reported here emphasize the need to coordinate power management between the processor and the memory by exploiting control theoretic tools. The notion of coordination between controllers used in this thesis is as follows. Suppose there are two controllers A and B, one for the processor (A) and another for the memory (B). Coordination between the two controllers A and B, monitoring a system output means that the decision taken by controller A for the current control cycle depends on the decision taken by B in the previous cycle and vice versa. Controllers implementing DVFS on the processor and memory have implications on the performance, energy and temperature of the entire computing system. It is demonstrated that control decisions made for the processor and memory in an uncoordinated fashion leads to energy inefficiency. This aspect is elucidated in the subsequent chapters.

A recurring theme throughout this thesis is the pursuit of simple, effective and robust feedback controllers that can be implemented on a real physical system with minimal overheads. The quest for achieving the aforementioned 'balance' is what drives this thesis towards unravelling key observations leading to simple and effective solutions. The vehicles of exploration in this thesis are the following two computing platforms: (1) A mobile SoC processor and (2) a server-class processor. The exploration *algorithm* is divided into three steps: (1) Characterization (2) Insight identification and (3) Solution development.

Figure 1.1 pictorially describes the exploration *algorithm*. The end goal is the design of TRINITY, a control theory based technique that dynamically balances the three parameters of interest: performance, energy and temperature.

**Characterization:** The first contribution of this thesis is the characterization of various power/energy management methods implemented in different hardware and software levels of the SoC stack, using a smartphone as an example of a mobile device. Finding the right balance between performance and energy consumption in an SoC, when application complexity varies widely, has generally been influenced by heuristics, end user demands

Figure 1.1: Thesis Overview: Characterization of *three* parameters leading to *TRINITY*, a control theory based solution for *3D* stacked architectures.

etc. Understanding the behavior of the SoC and its components under a variety of operating conditions helps in identifying areas of energy inefficiency. The impact on power, performance and energy by varying a multitude of design parameters and governors are analyzed individually. The investigation of interactions *between* individual governors reveals that governors implementing their policies in an isolated manner are energy inefficient, thus laying the groundwork for coordinated control of the processor and memory.

A second set of characterization experiments are conducted on a 3D stacked processor-memory architecture. A comprehensive characterization of the multi-physics interaction between (a) thermal behaviors (b) compute and memory microarchitecture and (c) application workloads is presented. Insights from this exploration reveal the need to manage performance, energy and temperature in a coordinated fashion. Furthermore, the concept of "effective heat capacity", the heat generated beyond which no further gains in performance are observed with increases in voltage and frequency in the compute logic, is established as a useful metric. This characterization study also opens up multiple directions for further research.

**Optimization:** In light of the insights generated from the SoC characterization, this thesis demonstrates a software controller designed to maintain application performance while

minimizing energy consumption on a Nexus 6 smartphone [37]. The controller is based on the work presented in [38] and exploits (a) techniques from feedback control theory and mathematical optimization and (b) the in-depth understanding of the SoC components and its governors. It chooses a combination of CPU frequency and memory bandwidth *simultaneously*, thus making it an *energy-efficient coordinated control* scheme. The novelty of this work is that it, (1) successfully demonstrates a coordinated controller, (2) is generic enough to incorporate other SoC components into the ambit of the problem and (3) indicates the viability of application-specific controllers on SoC platforms.

Since the dependence on application-specific offline data limits the extent and effectiveness of such a controller, an improvement/extension is explored as well. Simple analytic

models for the performance and power of the processor and memory are developed which

are subsequently used by the feedback controller at run-time to optimize energy efficiency.

Using the parameter (ops/byte) measured at run-time, the controller classifies the application as compute bound or memory bound or a mix of the two and selects the processor

and memory frequencies that minimize the energy-delay-product. A similar approach is

explored for a multi-core multi-memory-controller system.

Neither of the works described in the previous two paragraphs consider temperature in the problem formulation. This thesis explores Dynamic Thermal Management (DTM) on Chip MultiProcessors (CMP)s using feedback controllers. An adjustable gain integral controller is demonstrated in [39] to regulate the temperature of each core in a CMP to a fixed value by performing per-core DVFS. The controller is tested on a cycle-level simulator running PARSEC and Splash2 benchmarks. An important insight gained from this work is the connection between workload characteristics and thermal behavior of the core. Specifically, the wastage of energy in the form of heat is clearly observed during memory intensive phases of the workload. The concept of "effective heat capacity" is strongly motivated by this phenomenon.

The final part of this thesis tackles this very issue in a 3D stacked processor-memory

architecture where its effects are exacerbated. As opposed to prior works which consider temperature as a constraint to be met, this thesis advocates using temperature as a *resource* just like compute or memory cycles. The characterization experiments provide ground rules for the design of a real-time, numerical optimization based, application agnostic controller, TRINITY, for intelligently managing performance, energy *and* temperature. TRINITY achieves up to 11% improvement in energy-delay-product (EDP) over heuristic schemes. On an average, TRINITY reduces temperature by 4 Kelvin for similar EDP. An analysis of device reliability shows an increase by up to 26% on account of reduced temperature. In summary, the contributions of this thesis are as follows:

- Performance characterization of current power management strategies in SoCs demonstrating the scope for coordinated power management.

- A control-theoretic solution to the coordinated management of the core and the memory to minimize energy consumption for a target performance level.

- Extending the coordinated control framework to multi-core multi-memory-controller systems to improve energy efficiency.

- A distributed feedback controller to regulate core temperatures in a 2D multi-core processor.

- A comprehensive characterization of a 3D stacked processor-memory architecture.

- A distributed coordinated control framework for performance, energy and thermal management in a 3D stacked processor-memory architecture.

#### 1.2 Thesis Organization

Apart from CHAPTER 1, this thesis comprises of the following 9 chapters:

CHAPTER 2 begins with a brief discussion of the evolution of microarchitecture from planar 2D to 2.5D to 3D stacked architectures. The issues associated with each architectural

design and the limitations of the solutions adopted emerge out of a detailed literature survey. The state-of-the-art power, energy and thermal management techniques in the domain of SoCs and traditional server-class processors are described in detail. Their associated shortcomings are highlighted which forms the basis of this thesis. It concludes with a list of challenges that are addressed in the subsequent chapters.

CHAPTER 3 presents characterization of performance, power and energy consumption in an SoC using a commercially available mobile phone as a platform for exploration. It describes in detail, the interaction between a multitude of software and hardware optimizations on a wide range of target applications. It also highlights the need to coordinate the power management between the processor and memory. This, and more insights are summarized in the end forming the basis for the next chapter.

In CHAPTER 4, a feedback controller is developed which minimizes energy consumption while maintaining a performance target. Experimental results obtained from a mobile phone are discussed in detail. The results confirm the need for coordinating processor and memory clock frequencies to trade-off energy and performance. The chapter concludes with a summary of results and shortcomings of the presented approach.

CHAPTER 5 extends the feedback controller framework presented in CHAPTER 4. This chapter proposes an application agnostic energy optimization approach for a more generic architecture. Starting from a single-core single-memory controller model, the concept is extended to explore a multi-core multi-memory-controller system. The chapter concludes with a discussion of the results and also prospects for future implementation on a real system.

CHAPTER 6 focuses on the role of temperature, the third key parameter in this thesis. Using a cycle-level simulator coupled with power and thermal calculations, a distributed feedback controller designed to regulate temperature in a 2D multi-core processor environment is described. Experimental results are presented and key observations regarding the potential inefficiency of such an approach in thermally constrained 3D stacked processor-

memory architectures are also mentioned.

CHAPTER 7 analyzes the interaction between performance, processor-memory interactions and thermal coupling in a 3D stacked architecture. Insights from the previous chapter motivate the development of the concept of "effective heat capacity". This chapter lists key insights which open up many possibilities for future research.

CHAPTER 8 presents details of a feedback controller (TRINITY) which manages performance, energy and temperature of a 3D stacked processor-memory architecture. The power, performance and temperature models used in the controller are described in detail. An in-depth analysis of experimental results shows the benefits of TRINITY over existing state-of-the-art techniques.

Finally, CHAPTER 9 summarizes the main contributions of this thesis and discusses potential future research directions.

Collectively, through the different contributions presented in this thesis, the following aspects are substantiated: (1) The need to manage the processor and memory in a coordinated fashion for current and future architectures, (2) The benefits of control theoretic approaches over heuristics, and (3) The importance of managing temperature as a resource similar to compute or memory cycles. Furthermore, this thesis identifies a set of future research directions pointing towards to innovative inter-disciplinary solutions.

#### **CHAPTER 2**

#### PROBLEM FORMULATION AND RELATED WORK

This chapter begins by describing the "Memory Wall" problem and provides an overview of related research efforts that address this problem from architectural, software and hardware perspectives. A second important aspect, discussed in detail is the dynamic management of performance, power, energy and temperature of processors and memory. Finally, this chapter concludes with a list of open problems that stress the need to optimize energy efficiency for compute and memory in a coordinated fashion.

#### 2.1 The Memory Wall

The rate of increase in microprocessor speed and memory speed have been following an exponential curve. However, the exponent for the microprocessor has been larger than that for the DRAM (See Figure 2.1). The *memory wall* is described as a situation where the rate of increase of processor speed as compared with that of the DRAM will eventually lead to processor speed improvements being masked by the DRAM. Quoting an example from [40], consider the following equation:

$$t_{avg} = p \times t_c + (1 - p) \times t_m \tag{2.1}$$

where p is the probability of a cache hit,  $t_c$  is the cache access time,  $t_m$  is the DRAM access time and  $t_{avg}$  is the average time to access the memory. The above equation implies the following: Suppose 20% of the instructions reference the DRAM, if  $t_{avg}$  exceeds  $5t_c$ , the performance of the processor is entirely determined by  $t_m$ . Consequently, the queuing delays grow ( $t_{avg}$  continues to increase) and the processor performance hits a wall i.e. the memory wall.

Figure 2.1: Memory Wall Problem [41]

Researchers have addressed this issue at multiple levels. The details can be found in the technical report [42] and references therein. Some of the efforts aimed at improving the DRAM are access latency reduction, increasing bandwidth, latency hiding via aggressive prefetching, non-blocking caches etc. Improving cache performance however, is not a very obvious method to handle the memory wall because the DRAM access speed will continue to be the critical bottleneck. Nevertheless, reducing the number of requests between the last level cache and the DRAM can potentially improve system performance. Optimizing cache size and cache associativity for reducing cache misses, memory compression etc. are a few techniques listed here among several others. Simultaneous Multi Threading (SMT) and Chip Multi Processors (CMP) try to hide the DRAM latency by executing available work on a thread while the other thread waits for the memory request. SMT can keep a single processor busy whereas a CMP can have better overall system throughput even though some cores remain idle.

The US Department of Energy predicts that for an exascale system with 100,000 nodes, the memory size, bandwidth and hierarchy are some of the important challenges [43]. The steep performance demands ( $\geq 1$  ExaFlop/s) are expected to be met subject to a cap on the maximum power consumed ( $\leq 20$ MW). As mentioned in CHAPTER 1, the DRAM is projected to consume 70% of this total power. To address this issue, device manufacturers proposed a solution: 3D and 2.5D die stacking of compute logic and memory [44]. Accordingly, 3D die stacked memories such as HBM [45] from JEDEC and HMC [46]

from Micron were introduced which offered an order of magnitude better bandwidth than traditional DDR technologies. These hardware and architectural innovations are primarily aimed at meeting the performance target. Dynamically managing the power consumed by the processor and the memory under a variety of workloads has been an active research topic for the past two decades.

#### 2.2 Power, Energy and Thermal Management of Processors and Memory

Power and energy management strategies have been extensively explored ever since the advent of the very first series of computers. In the last decade, with the proliferation of cloud technologies, thermal management too is receiving a great deal of attention. A number of technological innovations have been proposed that span the entire hardware-software stack: from the logical circuit to complex applications. Many have become industry standards.

#### 2.2.1 Dynamic Voltage and Frequency Scaling (DVFS)

At the circuit level, DVFS is a widely used technique which has been implemented with multiple design objectives. The basic principle of DVFS emerges from the dynamic power equation  $P \propto V^2 \cdot f$ , where V is the supply voltage and f is the clock frequency. Reducing voltage leads to quadratic power savings whereas lowering the frequency reduces the power linearly. Modern processors and even peripheral devices such as RAM, GPU etc., support DVFS. Linux provides OS-level support for CPU-DVFS through a subsystem known as cpufreq [47] and devfreq enables DVFS for other peripheral devices. The DVFS policies are called governors. In [48], different cpufreq governors provided by Linux are tested for a variety of applications. The power, performance and energy numbers are compared for each of the CPU governors. On mobile systems running the Android OS as well, DVFS policies for the CPU and other subsystems are inherited from the Linux kernel designed for servers. The two main objectives are: (1) energy/power saving and (2) meeting task deadlines. DVFS has benefits in reducing power and energy but it does so at the cost

of performance. In reference [49], the authors investigate the effects of DVFS on power, energy and performance on a Pentium III and a PowerPC system. DVFS algorithms implemented on processors available in the market today are described in references [50, 51, 52, 53, 54]. The effects of DVFS are also evaluated on three generations of AMD processors in [55], wherein the authors claim that DVFS will have diminishing returns for future processors and memories. Nevertheless, reaffirming the efficacy of DVFS based techniques, the more recent survey article [56], reviews among other approaches, recent research works which perform DVFS to reduce power consumption on embedded processors.

Optimization based approaches aim to minimize (i) system wide energy consumption under performance bounds [57], (ii) energy-delay<sup>2</sup> [58], (iii) power-per-watt [59], (iv) power budgets with temperature constraints [60]. More exotic schemes use game theory for maximizing performance under power budgets [61], machine learning to efficiently share system resources for performance maximization [62], balance resource utilization and fairness in a CMP using market based strategies [63, 64] and [65] finds a Pareto optimal per-core configuration by integrating multiple power management techniques. On mobile systems, power/energy consumption is a top priority. Accordingly, a model-based DVFS governor for Android systems is presented in [66]. At first, offline profiling is performed on a set of benchmarks and for each benchmark the critical speed (CS), i.e., the energy-optimal CPU frequency is obtained along with the corresponding memory access rate (MAR), which in turn is obtained from the hardware performance monitoring unit. Statistical methods are then used to derive a model for CS with regard to MAR. This model is called the MAR-based CS Equation, or MAR-CSE. A DVFS governor is created that uses MAR-CSE to select the optimal CPU frequency based on the run-time MAR values. This approach is application-agnostic in the sense that it is independent of the running application. Furthermore, it is designed to optimize energy without considering performance. Another work in the same domain is the POET system [38]. It minimizes energy consumption of an application while attempting to meet its performance requirement. The system

requires two inputs before it starts: a performance target, and performance and power data for different system configurations. At run-time, it repeatedly measures the actual performance, and uses feedback control and linear programming to select energy-optimal configurations that meet the performance target. POET consists of a C library and a run-time system, and is designed for traditional embedded systems with soft real-time constraints. Because of the diversity of such systems, one of the key design goals of POET is portability. The problem it tries to solve is to create an application and platform-independent resource allocation framework. The advantage of [38] over [66] is the inclusion of performance constraint within the ambit of the problem. CHAPTER 4 is based on [38] for this very reason.

As opposed to optimization, researchers have implemented simpler PID based techniques for power budgeting via DVFS [67, 68, 69]. Power regulation [32, 70] and instruction throughput regulation [71] using adaptive gain integral controllers has also been explored on traditional desktop/server class processors. Benefits of using adaptive gain feedback controllers versus fixed gain controllers are: (i) robustness to modeling errors and (ii) rapid convergence. Fixed gains can lead to sluggish response or worse, oscillations. While most approaches tend to be application-agnostic DVFS methods, the authors in [72] present a DVFS algorithm for a specific application: video decoding. Application specific techniques can outperform their agnostic counterparts but at the added cost of switching between multiple policies depending on the application type.

Modern manufacturing technologies, while allowing for faster processing, have the unavoidable effect of increase in static power dissipation as well. Researchers have proposed Dynamic Thermal Management (DTM) strategies for the CPU and chip packages based on (i) power gating, (ii) reducing instruction fetch rate, (iii) thread migration, (iv) DVFS and (v) external cooling. What began as heuristic approaches eventually gave way to more formal control-theoretic solutions. References [31, 30] use PI and PID controls to slow down the rate of the instruction-fetch unit whenever the temperature exceeds a given up-

per bound. Stressing the importance of managing temperature effectively, the work in [73] points out that minimizing thermal impact extends the sustainability of desired Quality-of-Service levels on mobile devices.

In contrast to power gating, DVFS allows for reducing the temperature by simply reducing the dynamic power dissipated. Reference [74] applies DVFS for temperature control when the temperature hits an upper bound. Capitalizing on the drawbacks of threshold based control, researchers have proposed more advanced and rigorous formulations for DTM using techniques from the domain of optimal control and numerical optimization [35, 34, 36, 75]. These works however, assume linear and time-invariant plant-models for their respective control systems; [34, 75] updates the model on-line while [35, 36] do not. DTM under soft and hard real-time constraints has been investigated in [76] and [77], respectively.

Power and thermal management are not limited to the CPU alone. The survey paper [78] classifies and describes several DRAM power and thermal management techniques. Recently, researchers have started to focus on the DTM of 3D stacked memories as well. Due to the 3D architecture, higher power densities lead to larger thermal gradients, localized heating and heat shielding. The state-of-the-art for the DTM of 3D stacked memories is evolving along the lines of CPU-DTM strategies. The approaches vary from architectural level changes [79] to applying numerical optimization to maximize instruction throughput under strict power and thermal constraints [80]. Some other approaches involve data compression at the memory controller [21], two level prefetching with throttling off-chip memory links [20], dynamic page allocation [81], DVFS [82], thread migration [83] and data block reallocation with heterogeneous memory architectures [84].

3D stacking of memories has been explored academically [12] and also by the industry [7, 19, 46] for performance improvements. Memory intensive applications can benefit greatly due to availability of increased bandwidth as predicted by [85]. PIM architectures are being proposed to further increase performance by offloading memory-intensive code

to the logic die of the 3D memory. Some researchers have characterized the performance of 3D processor-memory systems [79, 86, 87] under a variety of benchmark applications. Reference [79] goes onto propose a new 3D memory architecture specifically suited for SoCs and compares it against 2D memory systems, whereas [87] explores the possibility of controlling CPU and 3D memories simultaneously. The authors in [3] explore the viability of using the execution unit of a General Purpose GPU (GPGPU) as the in-memory processing element. An important observation they make is that exascale computing workload may benefit from PIM; PIM itself does not require exascale workloads in order to be useful. In their experiments, they observe a tremendous reduction in energy-delay-product (85%) at marginal performance improvements (7%). However, they design their experiments such that power and thermal emergencies are not triggered. [88] proposes moving the hottest datapaths closer to the heat sink (thermal herding) for better heat dissipation. More recently, the use of thermal TSVs to extract heat from the different layers has been proposed [22], wherein the authors propose boosting the performance of applications by exploiting the improved cooling efficiency.

#### 2.2.2 CPU Idling

To further optimize power consumption, when certain components in the processor or the SoC are not being used, it is a common strategy to either power down (clock gating) or enter different levels of sleep modes. Linux calls it *cpuidle* and different processor manufacturers provide drivers which implement idling policies. Reference [48] explores (i) the benefits of the stock *cpuidle* manager and (ii) the effect of *cpuidle* on compiler optimizations and CPU governors. They find that idling helps in saving up to 19% energy when combined with other mechanisms such as CPU DVFS. CPU idling has been inherited by Android systems with msm\_idle as the default driver on Qualcomm chipsets. CHAPTER 3 discusses the interaction between CPU DVFS and CPU idling.

### 2.2.3 Microarchitecture Optimizations

Moving up the hardware stack, at the architecture and microarchitecture levels, there has been a clear shift of design goals from being performance-centric to power-aware. Many designs at these levels target power efficiency of major hardware components such as memory [89], cache [90], etc. Other methods include clustered DVFS [91], heterogeneous computing that incorporates CPUs and accelerators such as DSPs and GPUs [92], asymmetric cores such as the big.LITTLE architecture from ARM [93] and many more. For the work presented in this thesis, a specific microarchitecture is assumed. The control techniques presented in the subsequent chapters are agnostic to the changes in the microarchitecture.

#### 2.2.4 OS, Compiler Optimizations

Commensurate software improvements have complemented hardware optimizations. An important problem at the OS level that has been extensively studied is power-aware thread/task scheduling, not only in a single core [94] but also across cores [95]. [96, 97] schedule threads (computations) from hot cores to cooler cores in an effort to maintain a balanced thermal field. More recently, Linaro [98] announced an Energy Aware Scheduler which aims to improve power management on ARM processors (homogeneous and heterogeneous like big.LITTLE). They schedule tasks intelligently on to cores so as to minimize energy consumption. Above the OS level, compiler optimizations however have focused on performance improvement [99]. Improved performance generally leads to better energy efficiency due to shorter execution times as noted in [100]. Furthermore, power-aware compiler optimizations have also been studied [101]. To truly understand the ramifications, [102] explores the design space of the embedded gcc compiler to identify the optimization options that offer maximum reduction in energy. The authors of reference [48] compare the power, performance and energy trends of different optimization levels of the qcc compiler on a server system. Multithreaded programs can exploit inherent parallelisms in applications and [103] compares energy efficiency of two parallelism technologies: parallelization

and vectorization. At the programming language level, various aspects for writing energy-efficient programs including programming framework, language extensions and so on have seen some research activities [104, 105].

Except for [87, 62, 64], rest of the works listed in this section either implement independent strategies for the CPU and memory or control only CPU parameters such as clock frequency, L1 cache banks, Re-Order Buffer size etc. CPU-only methods do not consider memory boundedness of applications whereas, memory-only schemes are concerned with meeting bandwidth or latency requirements. Some DTM schemes consider static power dissipation as a constant and do not take into account heating from neighboring components. Software optimizations at the application layer focus on performance and ignore power/energy effects in the lower layers of the hardware stack.

#### 2.3 Coordinated Management of Processor and Memory

The idea of controlling multiple components simultaneously has been explored extensively for embedded systems. In [23] the authors point out that independent control policies may run into conflicts with each other leading to oscillations, thereby significantly reducing the effectiveness in achieving energy savings. They demonstrate "CoScale" on a server that performs coordinated control of CPU and memory, where the goal is to minimize energy consumption while staying within a user defined performance degradation bound. Using performance and power models and also aided by hardware counters, CoScale uses a gradient-descent-like algorithm to select the optimal configuration. For a mobile device platform, [26] evaluates energy-performance trade-offs when implementing DVFS on the CPU and the memory bandwidth. They run SPEC CPU2006 benchmarks on a gem5 simulator and conclude that capturing the complex interplay between the CPU and memory subsystems is essential and that coordinated strategies can deliver higher energy efficiencies. On an Android phone, [27] demonstrates a coordinated control of the CPU and GPU for saving power. Based on power and performance models generated offline, they design

an algorithm to keep the performance within a predefined range while consuming the least amount of power. They achieve up to 58% power savings by performing CPU-GPU DVFS simultaneously. The authors in [106, 107] demonstrate heuristic schemes to balance performance and power between the CPU and GPU on AMD's Accelerated Processing Units. In [24], the authors propose "Harmonia", which balances computation and memory power on a high performance GPGPU. This is a heuristic based algorithm and is designed for server workloads, which generally tend to be memory intensive. MemScale [108] proposes applying DVFS to the memory controller and memory channels in order to reduce energy consumption while staying within performance loss bounds. Finally, the authors in [109] present a hardware control system implemented on an FPGA for GPUs that manages, (1) number of streaming multiprocessors (SM), (2) number of warps/wavefronts, (3) frequency of the SM and, (4) the DRAM frequency.

## 2.4 Summary

This chapter discussed previous research efforts related to the dynamic management of power, temperature, energy and performance of a computing system. Most prior research has focused on processor management. As the memory power consumption started becoming comparable to their processor counterparts, multiple techniques were developed to increase the efficiency of the memory subsystem. However, state-of-the-art processor and memory power management techniques were, and continue to be, independent of each other. Coordinated control of multiple components has started receiving interest only recently. However, the techniques developed thus far are either platform centric or application-specific. Furthermore, almost all approaches are based on heuristics. Control theoretic schemes are slowly gaining steam. Additionally, since the industry is moving towards 3D stacking of silicon die, there is a need to fundamentally understand the multi-physics interactions between performance, energy and temperature. Heuristics based methods fail to satisfy all the necessary requirements. This thesis substantiates the lacuna

in heuristics-based approaches and develops control theory based solutions to manage processors and memories in a coordinated fashion.

#### **CHAPTER 3**

# PERFORMANCE, POWER AND ENERGY CHARACTERIZATION: MOBILE DEVICES

Energy-efficient high performance mobile computing is receiving increasing attention in recent years. Mobile device manufacturers are continuously striving to provide the best user experience at the lowest energy consumption. Multiple, yet independent research efforts, have focused on individual layers of the hardware-software stack (operating systems, compilers, microarchitecture etc.). While providing better performance individually, energy/power saving mechanisms may sometimes not lead to complementary benefits when employed in tandem. A global understanding of interactions between these techniques can help in developing strategies at different layers that supplement each other. In this chapter, a collection of energy management schemes are evaluated on a Nexus 6 and a Nexus 5X phone at both the hardware and software levels. Their effects on the following three parameters: 1) Average performance 2) Average power and 3) Total energy, are compared. The goal is to help designers better understand interactions of these methods for more innovative solutions.

## 3.1 Overview

The performance of smartphones has been constantly improving. However, high performance comes at the cost of high power consumption and faster battery discharge, which can negatively impact user satisfaction. To tackle this issue, numerous studies, on both the hardware and software sides, have been conducted in an effort to make smart devices more power/energy efficient. However, research efforts in this direction have more or less investigated each issue independently. There is rarely a common platform, in either hardware or software, and there is a lack of comparative studies which consider effects of a new

technique on existing technologies. The problem of multiple platforms is exacerbated by the continuously changing landscape in the smartphone industry. Furthermore, there are variations in the reported results; while some report average power, others report average energy. Comparing two methods which have the same goal yet very different experimental platforms is a futile exercise.

To better understand the benefits of a particular power/energy management method, one must carefully analyze the cross effects between different layers of the stack. A newly developed method tested in isolation, might offer high power savings but deliver little gain when working on a full system with other kinds of mechanisms. This type of survey has been performed on a server [48], where the authors put the system under a series of rigorous tests to determine which mechanisms work well while some schemes fail. Drawing inspiration from their work, the work presented in this chapter performs extensive testing of a collection of energy/power management techniques on a smartphone and compares the effects on (1) Average Performance (2) Average Power and (3) Total Energy. The goal is to help a hardware/software designer understand the nature of interactions between different layers of the stack so that they can develop even better energy/power management strategies.

A set of widely used optimization techniques is tested, some designed explicitly for energy efficiency while others created mainly to improve performance but with side effects on energy consumption. Specifically, these include compiler optimizations, multithreading, CPU idle states, dynamic voltage and frequency scaling (DVFS) on CPU and GPU, and memory bandwidth scaling. In particular, two scenarios are evaluated that each involve two optimization techniques to understand their interactions: (1) CPU DVFS and memory bandwidth scaling and (2) CPU DVFS and CPU idle states. The experiments are performed on two Android devices: a Nexus 6 and a Nexus 5X, and the test programs include 5 popular Android apps such as AngryBirds, and 4 prominent Android benchmarking applications such as AnTuTu. For further insights and to highlight differences from servers, single and

multi-threaded benchmarks from SPEC CPU2006, PARSEC, respectively, are also tested. In total, the test suite includes 367 test cases.

Some of the important findings of this work are listed below:

- 1. The default DVFS governors can be optimized for better energy efficiency.

- (a) CPU governors must include energy consumption and not just performance or power in their design.

- (b) A DVFS mechanism which can adapt to the behavior of individual apps can possibly provide higher energy efficiency with the same performance.

- (c) CPU and memory bandwidth governors working in collaboration can lead to better energy savings.

- 2. Smartphone vendors may want to consider customizing certain aspects of power management.

- (a) The *performance* CPU and GPU governor consumes excessive power and results in severe thermal throttling. Vendors should carefully decide if it should be avoided.

- (b) CPU idling, at least on the Nexus 5X, does not seem to have much effect on the power and energy consumption for real-world Android apps.

- 3. Developers may want to note that increasing the number of threads for a program while improving performance does not save energy, contrary to the trend on a server.

## 3.2 Methodology

This section describes the experimental platform, the software benchmarks and the different power/energy management techniques tested. It also explains the rationale for the benchmarks and options chosen along with the base configurations against which the results from different options are compared.

# 3.2.1 Experimental Testbed

The experiments are performed on the Motorola Nexus 6 and LG Nexus 5X hereafter referred to as N6 and N5X respectively. The N6 runs on a Qualcomm Snapdragon 805 chipset which has a quad-core Krait 450 CPU and Adreno 420 GPU with 3GB of RAM. In all the experiments conducted, the N6 has Android 6.0 Marshmallow operating system with a Linux kernel v3.10. N5X comes with a Qualcomm Snapdragon 808 SoC comprising of a quad-core ARM Cortex-A53 and a dual-core ARM Cortex-A57, Adreno 418 GPU and 2GB of RAM. The N5X runs Android 6.0 Marshmallow operating system with a Linux kernel v3.10. Section 3.3 describes experiments on the following: CPU governor, memory bandwidth governor, GPU governor, CPU idle, threads and parallelization and compiler optimization. The userdebug build on N6 and N5X is required to enable changes to the cpufreq, devfreq and cpuidle modules in the Linux kernel. The Monsoon Power Monitor [110] is used which measures power consumption of the whole phone i.e. power values are inclusive of the CPU and other modules as well. Power samples are collected every 2ms and to communicate with the phone, Android Debugging Bridge [111] (adb) runs on a host machine. Since the default setting on the phone is to start charging when connected to a computer via USB, USB charging is turned OFF to avoid bias in the power measurements.

Table 3.1 lists all the 25 benchmark applications tested in this work. They are into 4 groups: (G1) Android benchmarks (G2) Android apps (G3) PARSEC and (G4) SPEC CPU2006. Each benchmark in the experimental survey is chosen with a specific intent and the intention is to touch as many features of the SoC as possible.

First of all, a few commonly used Android benchmark applications are chosen which test the performance of the entire SoC. The set includes AnTuTu v6 [112], Geekbench3 v3.4.1 [113], Vellamo v3.2 [114], and 3DMark [115]. AnTuTu performs tests on CPU, GPU, RAM and I/O. GeekBench tests the CPU and RAM. Vellamo offers web browser, single core and multicore benchmarks. Only the browser feature of this benchmark app is tested in order to prevent repetitions of single and multicore benchmarks. Finally, 3DMark

Table 3.1: List of benchmarks suites.

| Ве | enchmark suite | Applications/Tests                                    |  |  |

|----|----------------|-------------------------------------------------------|--|--|

|    | AnTuTu         | CPU, GPU, I/O, UX,                                    |  |  |

| G1 | Geekbench3     | Single and multi-core CPU benchmarks, STREAM mem-     |  |  |

| O1 |                | ory benchmarks                                        |  |  |

|    | Vellamo        | HTML5 browser benchmarks                              |  |  |

|    | 3DMark         | Sling Shot using OpenGL ES 3.1 (Physics and Graphics  |  |  |

|    |                | tests)                                                |  |  |

| G2 | Android Apps   | Facebook, AngryBirds, Chrome Browser, MX Player, Spo- |  |  |

|    |                | tify                                                  |  |  |

| G3 | PARSEC 3.0     | blackscholes, facesim ,ferret,                        |  |  |