## THERMAL PERFORMANCE ENHANCEMENT OF PACKAGING SUBSTRATES WITH INTEGRATED VAPOR CHAMBER

A Dissertation Presented to The Academic Faculty

by

Sangbeom Cho

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Mechanical Engineering

Georgia Institute of Technology May 2018

## **COPYRIGHT © 2018 BY SANGBEOM CHO**

### THERMAL PERFORMANCE ENHANCEMENT OF PACKAGING SUBSTRATES WITH INTEGRATED VAPOR CHAMBER

Approved by:

Dr. Yogendra K. Joshi, Co-Chairman School of Mechanical Engineering *Georgia Institute of Technology*

Dr. Rao R. Tummala, Co-Chairman School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Suresh K. Sitaraman School of Mechanical Engineering *Georgia Institute of Technology*  Dr. Samuel Graham Jr. School of Mechanical Engineering *Georgia Institute of Technology*

Dr. Venkatesh Sundaram School of Electrical and Computer Engineering *Georgia Institute of Technology*

Date Approved: March 23, 2018

То

My Loving Family

#### ACKNOWLEDGEMENTS

First and foremost, I would like to express my sincere gratitude to my advisors, Prof. Yogendra Joshi for guiding me through my work, and Prof. Rao Tummala for giving me an opportunity to work at the Georgia Tech 3D systems packaging research center (GT-PRC). My discussion with them has been always inspiring, which have greatly helped shape my dissertation. Next, I would like to thank Dr. Venky Sundaram for his constant support during my stay at GT-PRC.

I also would like to thank my PhD reading committee, Prof. Suresh Sitaraman for all the valuable discussions and feedback, and Prof. Samuel Graham not only for his valuable advice but also for allowing me to use his lab for my research.

This work could not have been completed without the help of many students, mentors, visiting engineers and staffs in GT-PRC. I'd like to thank Dr. Vanessa Smet, Dr. Fuhan Liu, and Dr. Raj Pulugurtha for all the valuable technical discussions, guidance and help regarding my research. I'd like to thank Karen May, Patricia Allen, and Brian Mcglade for their administrative support, and Jason Bishop and Chris White for their support on resolving technical issues I had with cleanroom equipment. Working with visiting engineers has been a great learning experience, and I'd like to give special thanks to: Yoichiro Sato (Asahi Glass, Japan), Yuya Suzuki, Makoto Kobayashi (Namics, Japan), Toshitake Seki and Yutaka Takagi (NTK, Japan), Akira Mieno (Atotech, Japan), Ryuta Furuya (Ushio, Japan), Tomonori Ogawa (AGC Electronics, Japan), Hiroyuki Matsuura (NGK, Japan). My discussion with PRC students were always helpful. I'd like to give special thanks to Vijay Sukumaran, Nathan Huang, Hao Lu, and Jialing Tong, who shared their time to help me find solutions to technical issues.

Special thanks to Min Seok Ha from Prof. Samuel Graham's group for sharing his nanoparticle coating recipe and solutions, Georges Pavlidis from Prof. Samuel Graham's group for his help with thermoreflectance microscopy, Sang-in Park from Prof. David Rosen's group for teaching me how to use meshing tools which was useful for my study.

I'd like to acknowledge my lab mates in METTL for their friendship and supports: Steven Isaacs, Andrew McNamara, Rhajat Ghosh, Aravind Sathyanarayana, Banafsheh Barabadi, Thomas Sherer, Zhimin Wan, Seungho Mok, Xuefei Han, Daniel Lee, Jiaxing Liang, Sumit De, Daniel Lorenzini, Yuanchen Hu, Justin Broughton, Jayati Athavale, and Pouya Asrar.

My stay in Georgia Tech as a graduate student has been a joyful experience thanks to my friends. Special thanks to ME (Mechanical Engineering) students in GTKSA (Georgia Tech Korean Student Association).

.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTS iv                             |                                                |  |  |  |

|-------------------------------------------------|------------------------------------------------|--|--|--|

| LIST OF TABLES                                  | viii                                           |  |  |  |

| LIST OF FIGURES                                 | Х                                              |  |  |  |

| SUMMARY                                         | XV                                             |  |  |  |

| CHAPTER 1. INTRODUCTION                         | 1                                              |  |  |  |

| 1.1 Glass Interposer Technology 2               |                                                |  |  |  |

| 1.2 Fundamental Challenges in Glass inte        | erposers 3                                     |  |  |  |

| <b>1.3</b> Two-phase Cooling Technologies for 2 | Electronics 5                                  |  |  |  |

| 1.4 Research Tasks                              | 8                                              |  |  |  |

| <b>1.5</b> Overview of Chapters                 | 10                                             |  |  |  |

| CHAPTER 2. THERMAL MODELING O                   | F GLASS INTERPOSER 12                          |  |  |  |

| 2.1 Compact Thermal Modeling of Electr          | 2.1 Compact Thermal Modeling of Electronics 12 |  |  |  |

| 2.2 Compact Thermal Modeling of Glass           | Interposer 13                                  |  |  |  |

| 2.2.1 Compact thermal modeling of microb        | bump/TPV/bump 14                               |  |  |  |

| 2.2.2 Compact modelling of copper traces        | 16                                             |  |  |  |

| 2.2.3 Thermal conductivity measurement o        | f glass interposer components 18               |  |  |  |

| 2.2.4 Effective thermal conductivity measu      | rement of copper TPVs 22                       |  |  |  |

| CHAPTER 3. THERMAL PERFORMAN                    | CE OF GLASS INTERPOSER 32                      |  |  |  |

| <b>3.1</b> The Effect of Copper Structures on G | Hass and Silicon Interposers32                 |  |  |  |

| 3.1.1 The effect of copper TPVs with groun      | nd plane 32                                    |  |  |  |

| 3.1.2 The effect of copper traces               | 40                                             |  |  |  |

| <b>3.2</b> Effect of Vapor Chamber Integrated   | Packaging Substrate (PCB)42                    |  |  |  |

| CHAPTER 4. VAPOR CHAMBER EMBE                   | EDDED PACKAGING SUBSTRATE 49                   |  |  |  |

| 4.1 Prior Art                                   | 49                                             |  |  |  |

| 4.2 Integration of Vapor Chamber with H         | PCB 50                                         |  |  |  |

| 4.3 Micropillar Wick Structure                  | 52                                             |  |  |  |

| 4.3.1 Hydraulic Performance Test of Micro       | opillar Wick Structure54                       |  |  |  |

| 4.3.2 Micropillar Wick Design for Vapor C       |                                                |  |  |  |

| 4.4 Mechanical Design and Machining of          |                                                |  |  |  |

| 4.5 Device Sealing                              | 80                                             |  |  |  |

| 4.5.1 Device sealing with soldering             | 80                                             |  |  |  |

| 4.5.2                                               | Preparation of evaporator side for soldering               | 82  |  |

|-----------------------------------------------------|------------------------------------------------------------|-----|--|

| 4.5.3 Preparation of condenser side for soldering 8 |                                                            |     |  |

| 4.5.4                                               | -                                                          |     |  |

| 4.5.5                                               | • •                                                        |     |  |

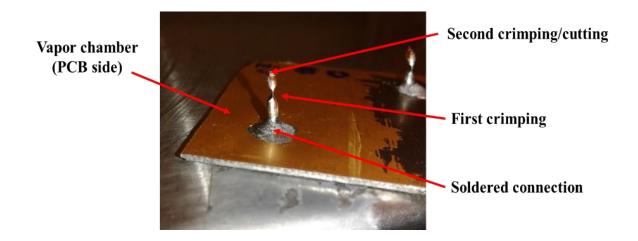

| 4.5.6                                               | 4.5.6 Charging and evacuation tube sealing                 |     |  |

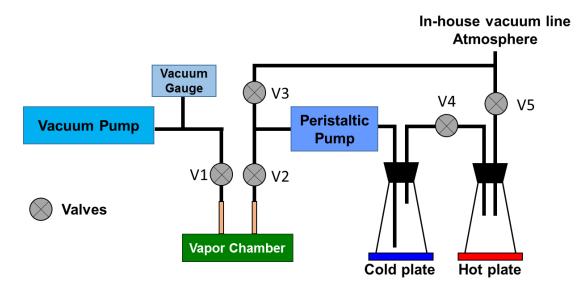

| 4.6 I                                               | Device charging/evacuation station                         | 90  |  |

| СНАРТ                                               | <b>TER 5. THERMAL PERFORMANCE OF VAPOR CHAMBER</b>         |     |  |

| EMBEI                                               | DED PCB                                                    | 95  |  |

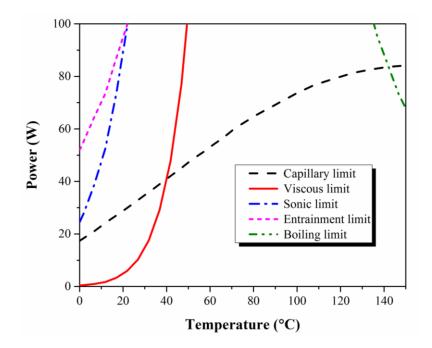

| 5.1 I                                               | Heat Transport Limitations of Prototype Vapor Chamber      | 95  |  |

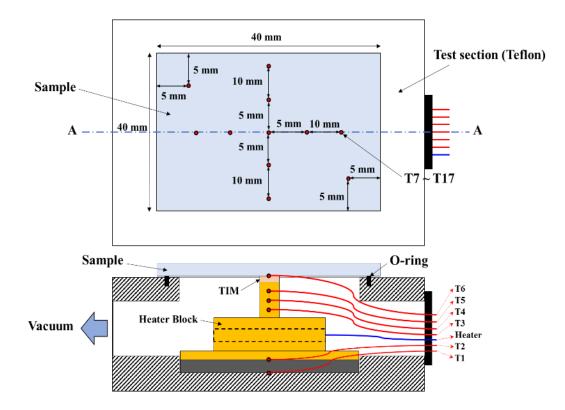

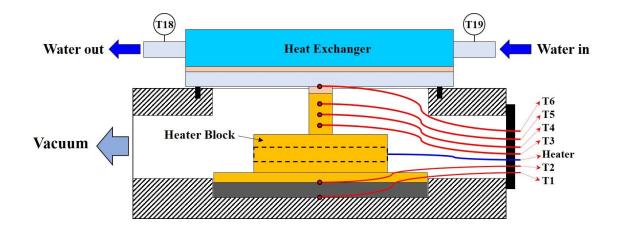

| 5.2                                                 | <b>Fest Setup for Thermal Performance Test</b>             | 99  |  |

| 5.3 I                                               | Performance Test                                           | 102 |  |

| СНАРТ                                               | <b>TER 6. MODELING OF VAPOR CHAMBER INTEGRATED PCB</b>     | 114 |  |

| 6.1 I                                               | Prior Works on Modeling of Heat Pipes/Vapor Chambers       | 114 |  |

| 6.2 (                                               | Governing Equations                                        | 115 |  |

| 6.3 (                                               | Code Validation                                            | 117 |  |

| 6.3.1                                               | 2D model                                                   | 117 |  |

| 6.3.2                                               | 3D Model                                                   | 119 |  |

| 6.4 3                                               | <b>3D Numerical Model of Vapor Chamber Embedded PCB</b>    | 120 |  |

| СНАРТ                                               | <b>TER 7. CONCLUSIONS AND RECOMMENDATIONS</b>              | 125 |  |

| 7.1 I                                               | Key Contributions                                          | 127 |  |

| 7.2 I                                               | Recommendations for Future Works                           | 128 |  |

| 7.2.1                                               | The effect of nanoparticle coating                         | 128 |  |

| 7.2.2                                               | Condenser design for vapor chamber performance improvement | 128 |  |

| 7.2.3                                               | Liquid chamber                                             | 129 |  |

| REFER                                               | ENCES                                                      | 130 |  |

# LIST OF TABLES

| Table 1.1 Comparison of different material candidates for interposer substrate                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2.1 Geometric dimensions of chip, interposer and printed circuit board (PCB) 14                                                                                                                                                |

| Table 2.2 Measured thermal conductivity of samples    22                                                                                                                                                                             |

| Table 2.3 TPV geometry and dimensions                                                                                                                                                                                                |

| Table 2.4 The comparison of the measured out-of-plane effective thermal conductivitiesof the glass samples with simulation.29                                                                                                        |

| Table 2.5 The percentage error between calculated effective out-of-plane thermalconductivity from models and measurements for sample 2 and 3                                                                                         |

| Table 3.1 Geometric dimensions of interposer components                                                                                                                                                                              |

| Table 3.2 Material properties and calculated effective thermal conductivities of interconnects and TPVs       35                                                                                                                     |

| Table 3.3 Pitch/count and normalized $\Theta_{jb}$ of microbumps, TPVs, and bumps for 3 cases.<br>Each thermal resistance is normalized by the resistance value from case 1                                                          |

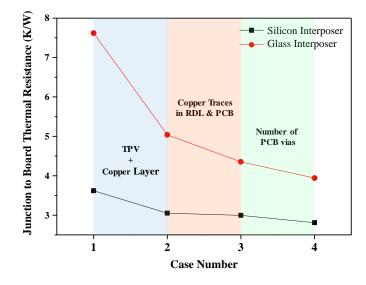

| Table 3.4 TPV, RDL, and PCB conditions for 4 different cases    42                                                                                                                                                                   |

| Table 3.5 Calculated effective thermal conductivity based on thermal resistance                                                                                                                                                      |

| Table 4.1 Summary of prior researches on integration of two-phase cooling technology 50                                                                                                                                              |

| Table 4.2 Summary of correlation between dimensionless permeability ( $K^*$ ) and porosity<br>( $\varepsilon$ )                                                                                                                      |

| Table 4.3 Wick sample porosity, pitch size, and permeability calculated from a numerical model developed with flat meniscus shape. Results from other models are presented in % error with respect to flat meniscus modeling results |

| Table 4.4 Effective capillary radius and capillary performance parameters of samples(Results in parentheses are calculated using correlation from [42] with 55° contact angle)                                                       |

| Table 4.5 Comparison of the capillary performance parameter of the wicks acquired with and without considering hydrostatic pressure effect                                                                                           |

| Table 4.6 Mass of the water container measured before and after the discharging withdifferent discharge volume settings. The difference of mass measured before and after thedischarging is also presented |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 5.1 Pump setting versus measured mass flow rate                                                                                                                                                      |

| Table 5.2 Geometric conditions of two vapor chambers with different pillar arrangement conditions.       106                                                                                               |

| Table 5.3 Geometric conditions of two vapor chambers with different pillar arrangement conditions.       109                                                                                               |

| Table 5.4 Geometric conditions of vapor chamber used for long-term performance 112                                                                                                                         |

| Table 6.1 Detailed thermal properties of vapor chamber components    120                                                                                                                                   |

# LIST OF FIGURES

| Figure 1.1 The schematic of 2.5D interposer structure. Numbers in brackets are minimum and maximum sizes of the features in each component                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2 Heat flow within interposer through copper structures                                                                                                                                                                      |

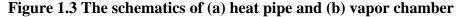

| Figure 1.3 The schematics of (a) heat pipe and (b) vapor chamber7                                                                                                                                                                     |

| Figure 2.1 Schematic view of ball grid array (BGA) package with junction, case, and ambient nodes [14]                                                                                                                                |

| Figure 2.2 Compact modeling scheme used for TPV modeling. Upper part of TPV array is connected to microbumps, and lower part is connected to bumps                                                                                    |

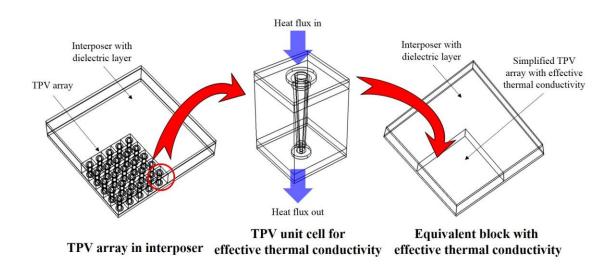

| Figure 2.3 Glass interposer substrate with single chip (left image from http://www.shinko.co.jp/english/product/buildup/dll.html), top view of example metal layers' layout, and cross-sectional view of TPV and metal layers (right) |

| Figure 2.4 Determination of total thermal resistance to obtain in-plane effective thermal conductivity for compact modeling of metal layer                                                                                            |

| Figure 2.5 Setup for out-of-plane thermal conductivity measurement                                                                                                                                                                    |

| Figure 2.6 a) Top view of test fixture and b) cross-sectional view of section A-A 20                                                                                                                                                  |

| Figure 2.7 Temperature map from IR microscope measurement                                                                                                                                                                             |

| Figure 2.8 Process flow for glass TPV sample fabrication                                                                                                                                                                              |

| Figure 2.9 Schematic of test setup to measure effective thermal conductivity of glass samples with copper TPVs                                                                                                                        |

| Figure 2.10 Thermal resistance network of sample stack-up on heater                                                                                                                                                                   |

| Figure 2.11 Surface temperature profile of (a) Sample 1, (b) Sample 2, (c) Sample 3, and (d) Sample 4 measured with Infrared microscopy. (D: diameters of vias, P: pitches of vias, and N: numbers of vias)                           |

| Figure 2.12 Cross-sectional view (left) and top view (right) of Sample 3                                                                                                                                                              |

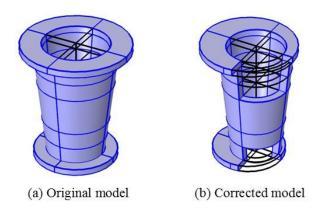

| Figure 2.13 Copper plating condition of vias in (a) original model, and (b) corrected model                                                                                                                                           |

| Figure 3.1 Schematic drawing of 2.5D interposer and geometric dimensions of microbumps, TPVs, and bumps used for modeling                                                                                                             |

| Figure 3.2 Geometric dimension of TPV in silicon interposer                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

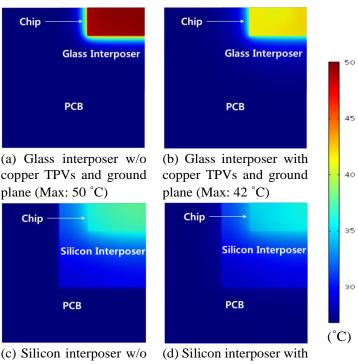

| Figure 3.3 Surface temperature profile of glass interposer ((a) and (b)), and silicon interposer ((c) and (d)) with different via and layer condition                                                                                        |

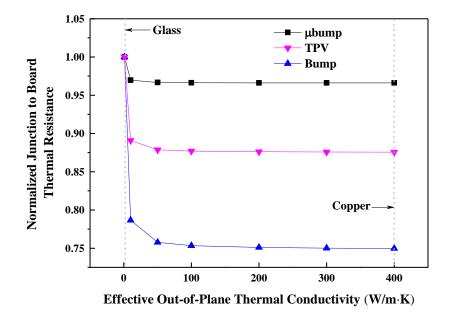

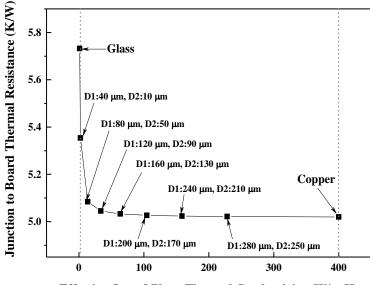

| Figure 3.4 Normalized junction to board thermal resistance with different effective out-<br>of-plane thermal conductivities of 3 components (microbumps, TPVs, and bumps). Each<br>component's resistance is normalized by its maximum value |

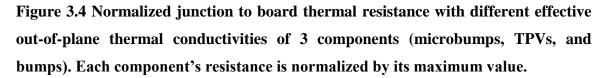

| Figure 3.5 Junction to board thermal resistances of glass interposer with different D1 (laser entrance diameter) and D2 (laser exit diameter)                                                                                                |

| Figure 3.6 The schematic of 2.5D interposer (top) and layouts of four metal layers (bottom) used for simulation                                                                                                                              |

| Figure 3.7 Junction to board thermal resistance of 4 different cases. The factors that affect the thermal resistance are indicated on the plot                                                                                               |

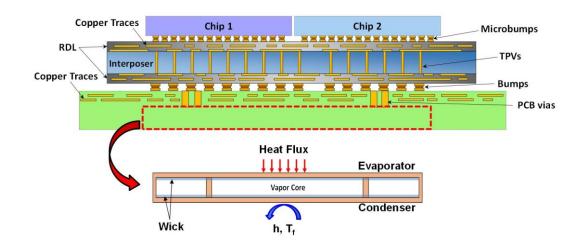

| Figure 3.8 Interposer with vapor chamber integrated PCB                                                                                                                                                                                      |

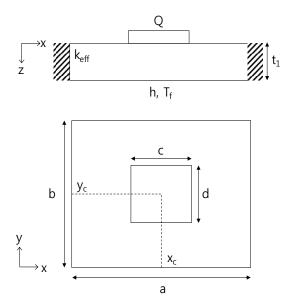

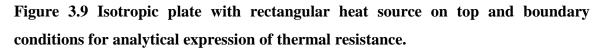

| Figure 3.9 Isotropic plate with rectangular heat source on top and boundary conditions for analytical expression of thermal resistance                                                                                                       |

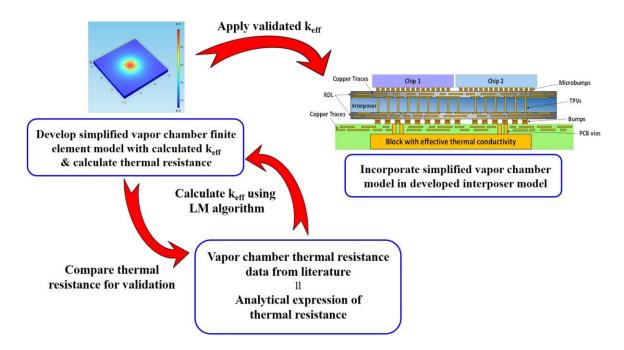

| Figure 3.10 Thermal performance simulation steps for interposer with vapor chamber integrated PCB                                                                                                                                            |

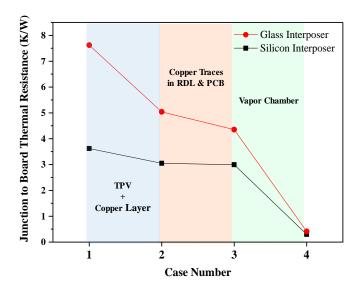

| Figure 3.11 Junction to board thermal resistance of 4 different cases. The factors that affect the change of thermal resistance are indicated on the plot                                                                                    |

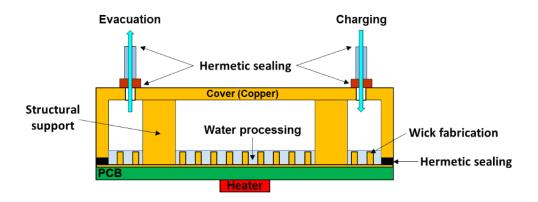

| Figure 4.1 Schematic cross-sectional view of vapor chamber integrated PCB and subtasks for fabrication of prototype                                                                                                                          |

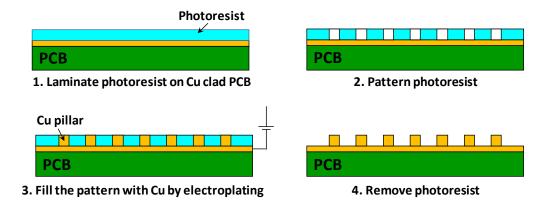

| Figure 4.2 Process flow for fabricating micropillars on copper clad PCB                                                                                                                                                                      |

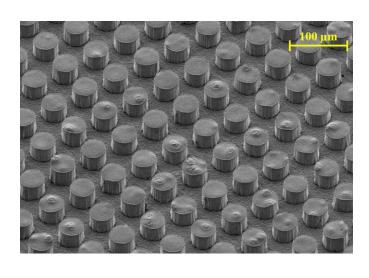

| Figure 4.3 (a) SEM image of fabricated micropillar arrays in square arrangement. 3D optical profiler image of fabricated micropillar arrays in (b) square arrangement, (c) hexagonal arrangement, and (d) rectangular arrangement            |

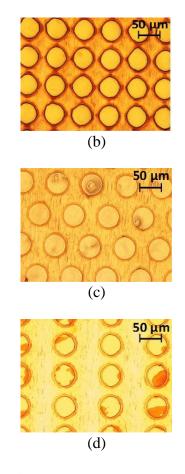

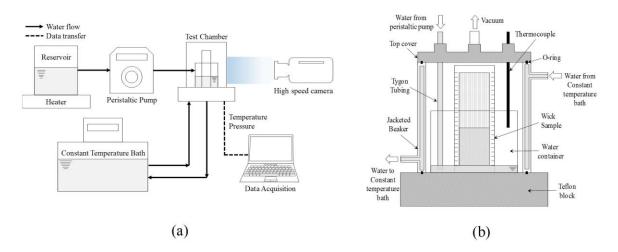

| Figure 4.4 Schematic of capillary rate-of-rise test setup (a) test system and (b) detail view of test chamber                                                                                                                                |

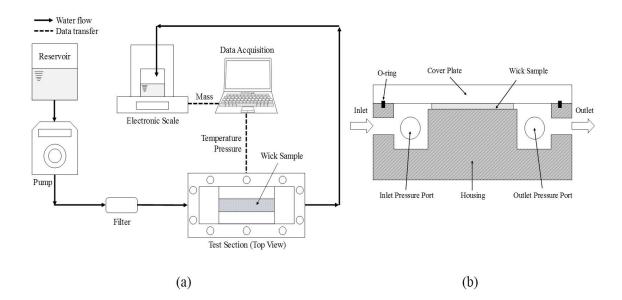

| Figure 4.5 Schematic of permeability measurement (a) test setup and (b) cross-sectional view of test section                                                                                                                                 |

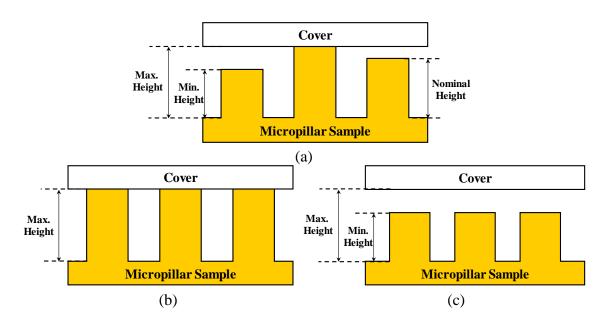

| Figure 4.6 The schematic of wick samples with (a) non-uniform pillar height, (b) maximum measured height, and (c) minimum measured height under polycarbonate cover during permeability test                                                 |

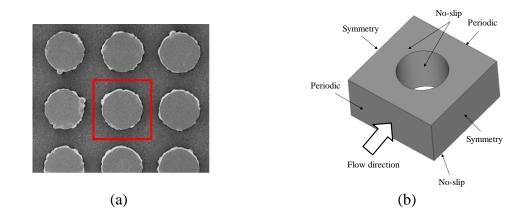

| Figure 4.7 (a) SEM image of pillar array (top view) and computation domain (red box) used for numerical model. (b) Boundary conditions for computation domain                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

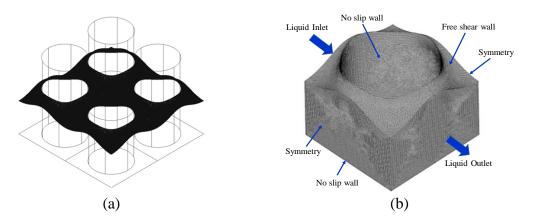

| Figure 4.8 (a) Liquid meniscus shape within micropillar array and (b) unit cell and boundary conditions used to estimate permeability of micropillar structure in square arrangement                                                                                                             |

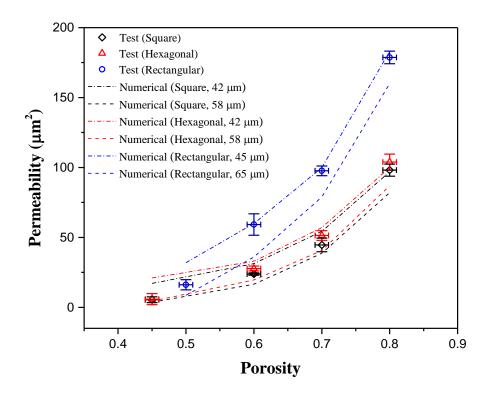

| Figure 4.9 Comparison of permeability test results with numerical modeling results for micro post arrays in different arrangement and porosity                                                                                                                                                   |

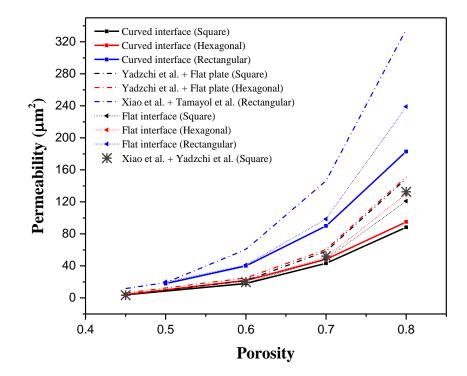

| Figure 4.10 Comparison of permeability results from different numerical and analytical models                                                                                                                                                                                                    |

| Figure 4.11 Recorded video frames of capillary rise at different time steps (Hexagonal arrangement, Porosity=0.8)                                                                                                                                                                                |

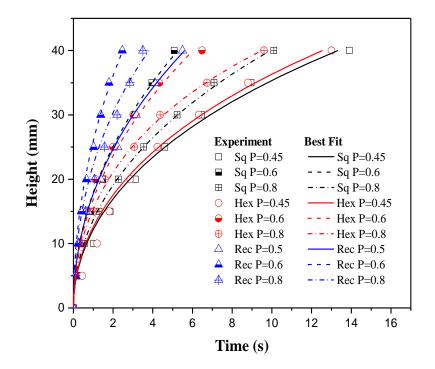

| Figure 4.12 The height of the capillary rise versus time data of samples with different pillar arrangements and different porosity acquired from rate-of-rise test                                                                                                                               |

| Figure 4.13 Square of liquid front height versus time data of micropost arrays in hexagonal arrangement with 0.8 porosity                                                                                                                                                                        |

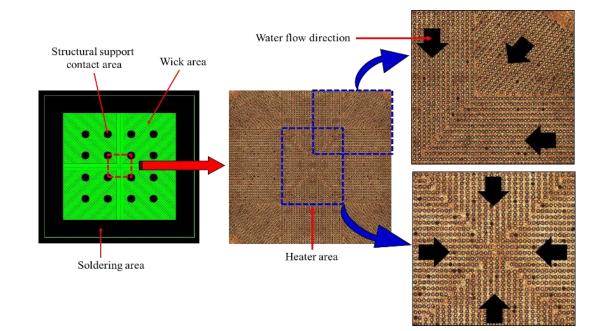

| Figure 4.14 Evaporator side wick structure (micropillar array in rectangular arrangement, porosity=0.6) mask layout (left), microscopic image of fabricated sample's center area (center), and zoomed view of the center and upper right area (right)                                            |

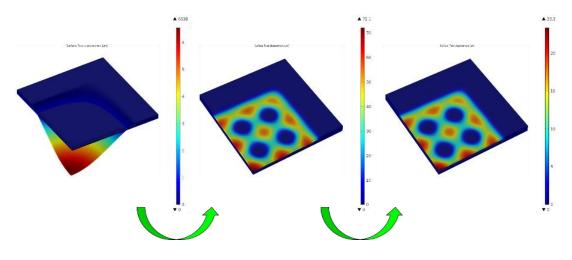

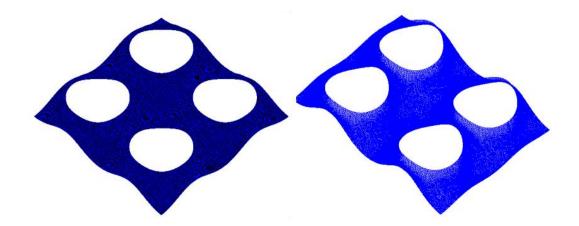

| Figure 4.15 Condenser side design of vapor chamber. Displacement ( $\mu$ m) contour plot of the vapor chamber before (left, Max: 6538 $\mu$ m) and after (middle, Max: 72 $\mu$ m) the placement of structural support, and after the adjustment of the pillar position (right, Max: 23 $\mu$ m) |

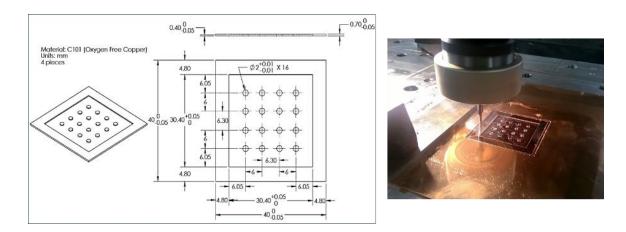

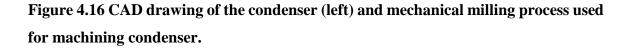

| Figure 4.16 CAD drawing of the condenser (left) and mechanical milling process used for machining condenser                                                                                                                                                                                      |

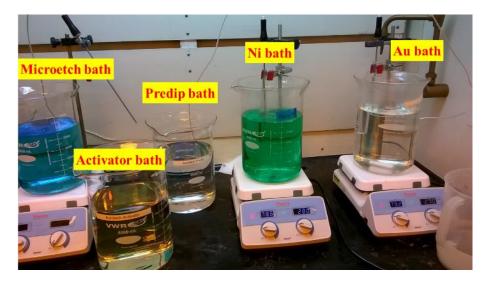

| Figure 4.17 Setup for surface finish (ENIG) process                                                                                                                                                                                                                                              |

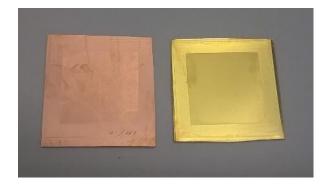

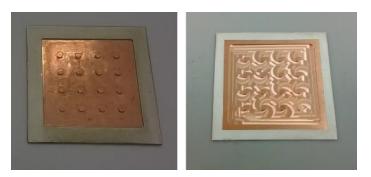

| Figure 4.18 PCB wick samples before ENIG (left) and after ENIG (right)                                                                                                                                                                                                                           |

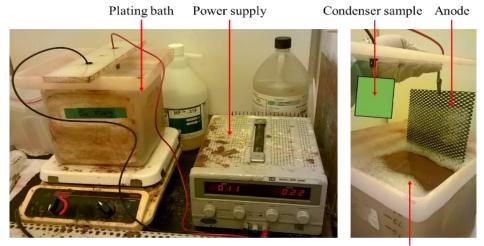

| Figure 4.19 Setup for SnAg solder electroplating                                                                                                                                                                                                                                                 |

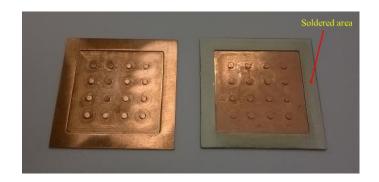

| Figure 4.20 Copper plate before (left) and after solder plating                                                                                                                                                                                                                                  |

| Figure 4.21 Reflow oven used for PCB/Copper plate soldering                                                                                                                                                                                                                                      |

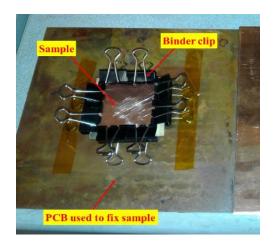

| Figure 4.22 PCB/copper plate prepared for soldering                                                                                                                                                                                                                                              |

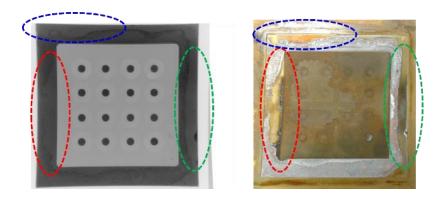

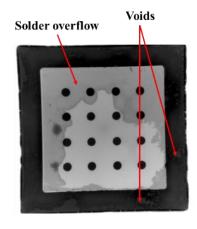

| Figure 4.23 X-ray image (left) of soldered sample and photo image (right) of PCB side of the sample                                                                                                                                                                                              |

| Figure 4.24 X-ray image of soldered sample with high pressure                                                                                                                                                                                                                                                                                                                                                            | 88 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.25 Copper cover with plated solder before (left) and after (right) masking half of the periphery area                                                                                                                                                                                                                                                                                                           |    |

| Figure 4.26 X-ray image of soldered sample with reduced solder                                                                                                                                                                                                                                                                                                                                                           | 89 |

| Figure 4.27 Sealing of charging/evacuation tubes                                                                                                                                                                                                                                                                                                                                                                         | 90 |

| Figure 4.28 Schematic of filling station with peristaltic pump9                                                                                                                                                                                                                                                                                                                                                          | 92 |

| Figure 5.1 Various heat transfer limitations of prototype vapor chamber                                                                                                                                                                                                                                                                                                                                                  | 98 |

| Figure 5.2 Schematic of the test section (Top and cross-sectional view)                                                                                                                                                                                                                                                                                                                                                  | 99 |

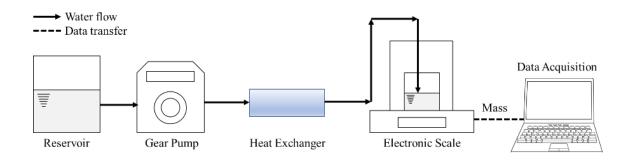

| Figure 5.3 Test setup for vapor chamber thermal performance with water heat exchange 10                                                                                                                                                                                                                                                                                                                                  |    |

| Figure 5.4 Setup for gear pump calibration                                                                                                                                                                                                                                                                                                                                                                               | 02 |

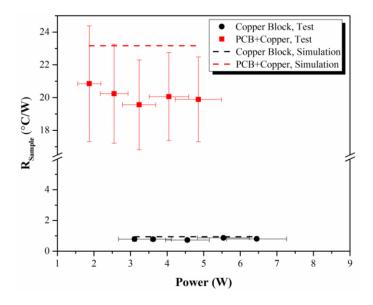

| Figure 5.5 Copper block and PCB sample thermal resistance test results vs. simulation results                                                                                                                                                                                                                                                                                                                            | 05 |

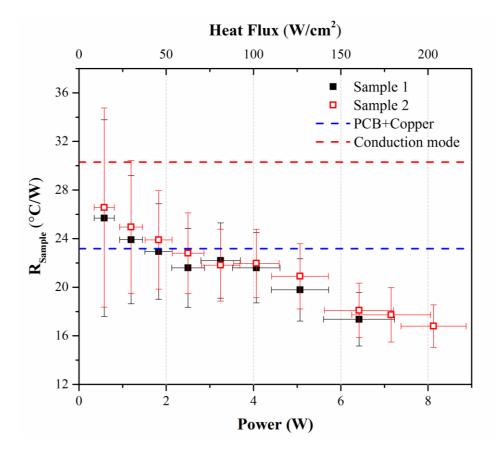

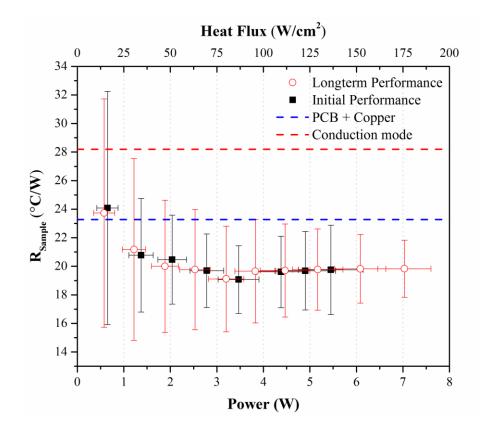

| Figure 5.6 Thermal resistance of two vapor chambers (total thickness: ~1250 $\mu$ m) with similar geometric conditions (Table 5.2) at different heating power/heat flux conditions. Thermal resistance of copper plated PCB (thickness:1250 $\mu$ m) and conduction thermal resistance of charged vapor chamber obtained from numerical modeling are presented for comparison.                                           | or |

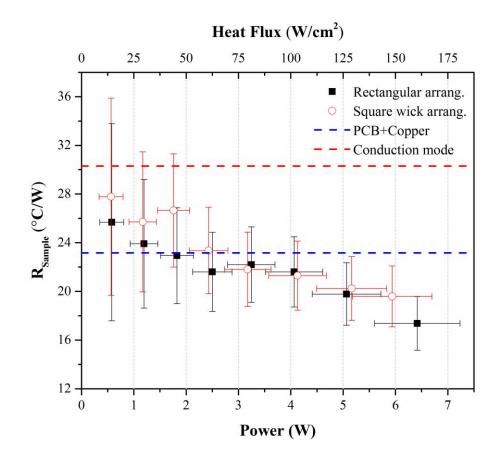

| Figure 5.7 Thermal resistance of vapor chambers (total thickness: ~1250 $\mu$ m) with micropillar wick structure in square and rectangular arrangement measured at different heating power/heat flux conditions. Thermal resistance of copper plated PCB with the same thickness (1250 $\mu$ m) and conduction thermal resistance of charged vapor chamber obtained from numerical modeling are presented for comparison |    |

| Figure 5.8 Meniscus shape of water within square-packed pillar array (left) and rectangular-packed pillar array (right) obtained from Surface Evolver                                                                                                                                                                                                                                                                    | 11 |

| Figure 5.9 Thermal resistance of vapor chamber (total thickness: $\sim 800 \ \mu m$ ) measured within $\sim 24$ hours, and $\sim 2,160$ hours (3 months) after the completion of charging. Therm resistance of copper plated PCB (thickness: $800 \ \mu m$ ) obtained from numerical modeling is presented for comparison.                                                                                               | 5  |

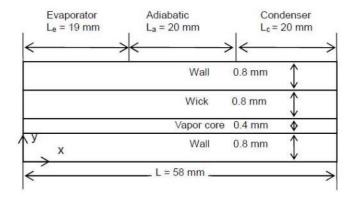

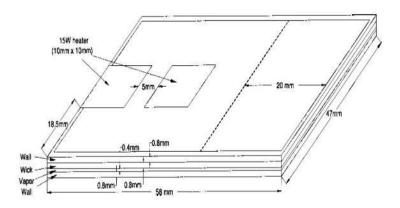

| Figure 6.1 Computational domain of 2D model used for code validation. Image adapted from [84].                                                                                                                                                                                                                                                                                                                           |    |

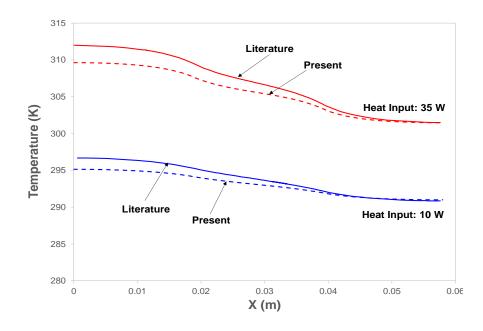

| Figure 6.2 Axial wall temperature distribution in the heat pipe at different times (10 seconds and 30 seconds) for two input powers. The results from developed numerical model (FLUENT) is compared with the results from [88] |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.3 Computational domain of the flat heat pipe used for 3D model code validation.<br>Image adapted from [89]                                                                                                             |

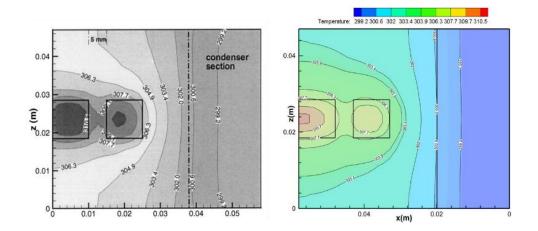

| Figure 6.4 Temperature contours of heat pipe (top surface) for heat inputs of 15 W - 15 W. The result on the left is from [89], and the result on the right is from the code numerical model developed for current study        |

| Figure 6.5 3D computation domain of prototype vapor chamber                                                                                                                                                                     |

| Figure 6.6 Steady-state velocity contour and vector of vapor in vapor core                                                                                                                                                      |

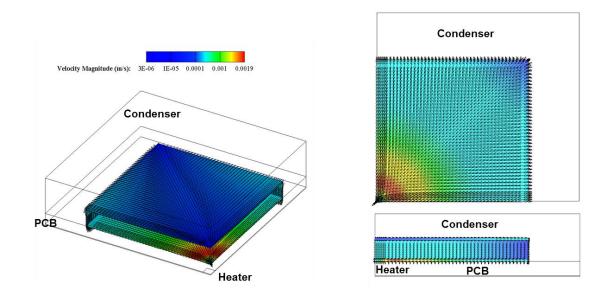

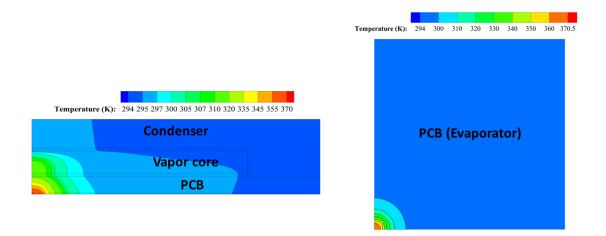

| Figure 6.7 Steady-state liquid (Water) flow velocity contour and vector in wick structure.                                                                                                                                      |

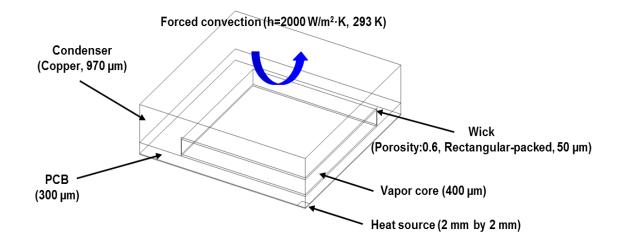

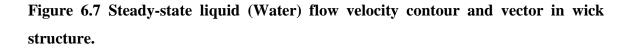

| Figure 6.8 Steady-state temperature profile (K) at the mid plane (left) and evaporator (right) of the vapor chamber with 5 W heat input                                                                                         |

#### SUMMARY

As demands on performance for mobile electronics continue to increase, traditional microsystems packaging technology is facing limits in number of input/outputs (I/Os) and thermal challenges. Glass interposers offer many advantages over silicon, as well as previous packaging technology for mobile electronics, including ultra-high electrical resistivity, low loss, and lower cost at processed interposer levels. However, glass has a relatively low thermal conductivity (~1 W/m·K), compared to silicon (~150 W/m·K), which may cause thermal related problems.

The main objective of this thesis is to overcome the limitation associated with low thermal conductivity of glass, by incorporating copper structures and additional cooling technology that can spread heat efficiently. This study focuses on characterizing the effect of copper structures on the thermal performance of glass interposers, and demonstrating ultra-thin (< 1 mm) cooling device, which makes the performance of glass substrate comparable with silicon.

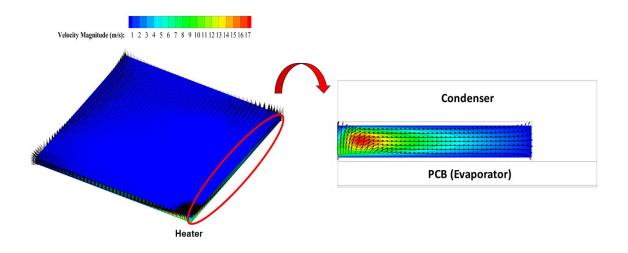

The first part of this research investigates the effects of copper structures, such as copper through-package-vias (TPVs), and copper traces in redistribution layer (RDL), on the thermal performance of glass interposers through numerical and experimental approaches. Numerical parametric study on 2.5D interposers shows that as more copper structures are incorporated in glass interposers, the performance of silicon and glass interposers becomes closer, showing 31% difference in thermal resistance, compared to 53% difference without any copper structures in both interposers. The numerical modeling study on glass interposers with 145 µm-thick glass substrate suggests that if the out-of-plane effective thermal conductivity of glass becomes higher than 50 W/m·K, thermal resistance of other components becomes more dominant, which results in negligible enhancement of thermal performance with further increase in out-of-plane effective thermal conductivity. In the second part of this study, a thermal model of glass interposer mounted on the vapor chamber integrated PCB is developed using multi-scale modeling. The comparison of

thermal performance between silicon and glass interposers through simulation study shows that integration of vapor chamber with PCB makes thermal performance of both interposers almost identical, overcoming the limitation posed by low thermal conductivity of glass. The third part of this thesis focuses on design, fabrication, and performance evaluation of the prototype vapor chamber embedded PCB. Copper micropillar wick structure is fabricated on PCB with electroplating process, and its wettability is enhanced by silica nanoparticle coating. Design of the wick for the vapor chamber is determined based on capillary performance and permeability test results. The thermal performance of the device is found better than copper plated PCB with the same thickness. Finally, a numerical model of vapor chamber is developed, and the results from the model compared with test results.

#### CHAPTER 1. INTRODUCTION

Mobile electronics are packing more features than ever before, and require higher bandwidth (10-30 GB/s) and larger memory capacity, with the same or lower power consumption. Additionally, the form factors of such devices continue to shrink, especially in thickness. In order to address these demands at a reasonable manufacturing cost, breakthroughs in packaging technologies are needed. Three-dimensional (3D) integrated circuit (IC) structures where multiple chips or dies are stacked have been considered to be an efficient solution to accomplish these goals, achieving the highest possible bandwidth enabled by the shortest interconnection length. However, there remains a number of technical challenges such as electrical interference between disparate functional blocks (RF, digital, analog, and sensors), design complexity, high cost, and thermal issue caused by high power density.

Two and a half dimensional (2.5D) Interposer packaging technology offers a way to achieve the benefits of chip-scale connected configurations without having the issues posed by 3D IC integration, and considered as a good alternative for stacked integration technology. Interposer is a packaging platform with high density of electrical connections, and it is used to fan out the electrical connections to a wider pitch, and also to route the signals between different components placed on the same interposer. Because of the high wiring density, interposers can support large number of inputs/outputs (I/Os) required by the advanced IC technology nodes.

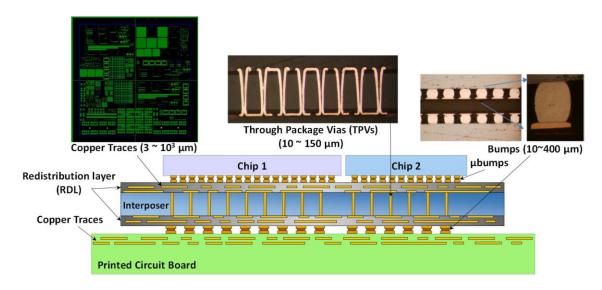

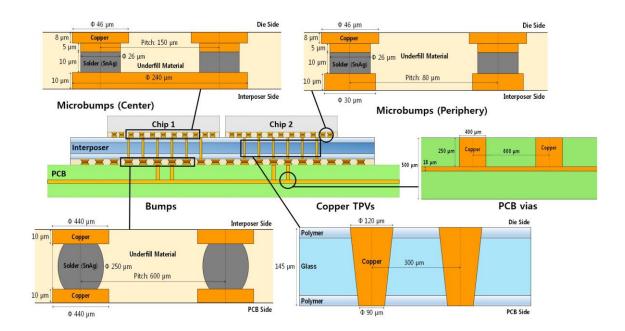

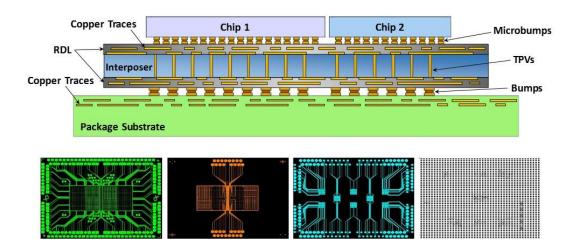

Figure 1.1 shows the schematic of a 2.5D interposer structure, where two dies are interconnected through copper traces in the redistribution layer (RDL) on the interposer

substrate, while both dies are connected to PCB through the copper plated through package vias (TPVs).

Figure 1.1 The schematic of 2.5D interposer structure. Numbers in brackets are minimum and maximum sizes of the features in each component.

#### 1.1 Glass Interposer Technology

Silicon and glass are two major candidates for an interposer substrate. Silicon interposer has been developed to overcome the limitations of organic substrates due to many advantages, including high I/O density, high manufacturability and reliability, and high thermal conductivity. Recently, 2.5D silicon interposers have been developed by Xilinx for packaging their FPGA modules, which enables them to pack twice more logic capacity compared to any other announced 28-nm FPGAs [1]. However, the size of silicon is limited to 300 mm wafer sizes, leading to high fabrication cost per interposer. Also, its high electrical losses due to its higher electrical conductivity limit its performance. To address these issues, glass interposers are being developed [2]. Glass has the advantage of panel-based processing, which results in lower cost per interposer. Moreover, glass has

high electrical resistivity, resulting in lower insertion loss and cross-talk compared to silicon. Combined with the advantages of ultra-high electrical resistivity and low electrical losses, glass becomes an excellent interposer candidate due to its benefits in thickness, especially for mobile applications [3]. Table 1 compares electrical properties, process complexity, and cost associated with glass, silicon, and organic interposers.

| Characteristics Required Properties |                                                     | Materials |         |         |

|-------------------------------------|-----------------------------------------------------|-----------|---------|---------|

|                                     |                                                     | Glass     | Silicon | Organic |

| Electrical                          | High Resistivity                                    | Good      | Poor    | Good    |

| Mechanical                          | High Strength<br>High Elastic Modulus               | Fair      | Fair    | Poor    |

| Chemical                            | High Resistance to Process<br>Chemicals             | Good      | Fair    | Poor    |

| Processability                      | Low Cost Via Formation<br>and Metallization         | Poor      | Fair    | Fair    |

| Cost                                | Low Cost                                            | Good      | Poor    | Poor    |

| Thermal                             | High Thermal Conductivity<br>CTE Match with Silicon | Fair      | Good    | Poor    |

Table 1.1 Comparison of different material candidates for interposer substrate

#### 1.2 Fundamental Challenges in Glass interposers

Despite several advantages over other materials, glass has two fundamental limitations: its brittleness and thermal conductivity (1 W/m·K) 100 times lower than that of silicon (150 W/m·K). These limitations can cause various challenges including the following:

- 1) Formation of defect-free TPV holes at small pitch

- 2) Assembly of interposer with ICs or organic package substrate

- 3) Thermo-mechanical reliability of TPVs

4) Thermal management of ICs on glass substrate

Recent studies have focused on addressing some of the challenges related to formation of defect-free TPV holes at small pitch [2], assembly of interposer with ICs or organic package substrate [4], and thermos-mechanical reliability of TPVs [5].

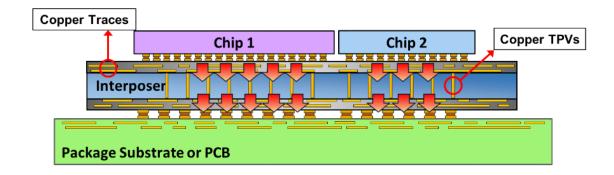

#### Figure 1.2 Heat flow within interposer through copper structures

This thesis focuses on addressing fundamental challenges associated with low thermal conductivity of glass, namely thermal management of ICs on glass substrate, by incorporating copper structures (TPVs and copper traces) to provide a thermal path within the package as illustrated in Figure 1.2, and integrating package substrate with thin twophase heat spreaders which can spread the heat more efficiently than copper. The design rules governing the feasibility of such structures can be established by thermal characteristic studies through modeling and test.

The idea of using metal structures for thermal management was first adopted in the design of interconnects between the chip and printed circuit boards (PCBs). Lee et al. developed analytical closed form expressions for the thermal resistance network of metal vias between multichip modules (MCMs), which showed good agreement with experimental data [6]. Li et al. studied relationship between the thermal resistance and the via design parameters. The study shows that adding metal vias can improve the thermal

performance across the PCB by over 10 times [7]. Recent studies with thermal vias were focused on the development of algorithms for an efficient placement of thermal vias in 3D ICs, minimizing the perturbations on routing. Golpen et al. developed an algorithm to determine the optimized number of thermal vias in 3D ICs for various thermal objectives, including minimizing maximum temperature and thermal gradients [8]. Lee et al. presented a co-optimization study for interconnects in 3D ICs, considering signal, power, and thermal aspects [9].

A number of studies have investigated the thermal characteristics of interposers through simulation [10],[11] Also, a few experimental thermal characterizations of interposer structures have been reported [12],[13]. Heinig et al. [14] presented thermal analysis and optimization results for various 2.5D and 3D integrated processor configurations. These results indicated that maximum total power of the processor on 25 mm×16 mm interposer can be increased up to 10 W when there is convective heat removal on bottom side with an effective heat transfer coefficient of 50 W/m<sup>2</sup>·K.

#### **1.3** Two-phase Cooling Technologies for Electronics

Heat generation from semiconductor devices in the past was easily managed using air cooling. However, as chip heat flux increase above 100 W/cm<sup>2</sup>, air cooled solutions become large, and acoustic noise becomes a challenge. Two phase heat transport systems have been demonstrated as an attractive advanced cooling technology for an increasing number of high power applications. Two phase heat transport systems utilize latent heat of working fluid, which usually is one or two orders larger than the sensible heat. This results in higher heat removal per unit mass of fluid than conventional air cooling technology, and gives an advantage of lower system mass and size. Another advantage of two phase cooling

systems is their temperature stability. Phase change of the liquid occurs at nearly fixed temperature, allowing such systems to operate over narrower operating temperature ranges.

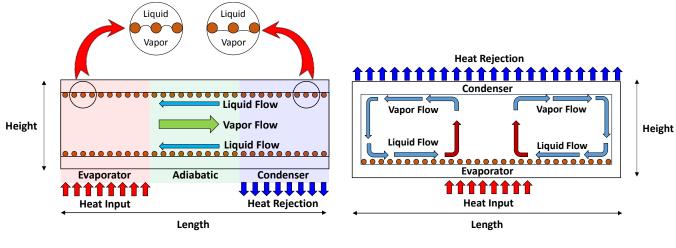

The most well-known two-phase cooling device used in current consumer electronic products is the heat pipe. It is a closed pipe filled with vapor and liquid of a working fluid. The heat pipe is divided into three parts: the evaporator, adiabatic section, and condenser. Heat is externally applied at the evaporator section and is conducted through walls and the capillary wick structure to the working fluid. The working fluid vaporizes within the wick structure in the evaporator, and the resulting vapor pressure drives the vapor through the adiabatic section to the condenser, where vapor condenses, releasing the latent heat of vaporization. The meniscus of liquid-vapor interface at evaporator section is highly curved, while in the condenser section it is almost flat. The difference of menisci radius of curvature between evaporator and condenser sections causes a capillary pressure gradient along the heat pipe wick, which drives the condensate to the evaporator. This capillary driven liquid pumping continues as long as there is a sufficient capillary pressure to drive condensate back to the evaporator. Typical heat pipe has circular cylindrical shape container, but rectangular, conical, corrugated flexible heat pipe geometries have been developed and studied [15].

As indicated in Figure 1.2, the vapor chamber is a capillary-driven flat heat pipe with a very small length to height ratio compared to conventional heat pipe (CHP) geometry [16]. Vapor chambers are sometimes preferred over CHP for electronics cooling, since heat flow within vapor chamber is two or three-dimensional, which can spread and dissipate the concentrated heat over much larger area than CHP. Vapor chamber usually has wick structure only on evaporator side when the condenser is above the evaporator, as the condensed liquid on upper wall will drip back to the evaporator section. Wick structure on the evaporator side supplies liquid to localized hot spot or heat source to prevent dryout.

The thermal resistance of the vapor chamber is often dominated by the wick structure. Thin evaporator wicks with high effective thermal conductivity are desired to reduce the thermal resistance at evaporator. However, such thin wick structures suffer from low critical heat fluxes due to their large liquid hydraulic resistance. To overcome this difficulty, material with high thermal conductivity, such as carbon nanotubes (CNTs) have been tested as wick structures [17].

The ultra-thin (< 1 mm) and light vapor chambers are an appealing solution for use in cooling glass interposer package to fit in a limited space, especially for its mobile application. Moreover, passive heat spreading technologies are also preferred over active cooling systems to minimize power consumption. However, their performance needs to be high enough to dissipate high heat fluxes from small hot spots, which in turn requires careful design of their wick structures and condensers.

#### 1.4 Research Tasks

The primary objectives of this thesis are 1) characterize the effect of copper structures on thermal performance of glass interposer and 2) develop and characterize ultrathin (< 1 mm) packaging substrates integrated with vapor chamber for cooling glass interposer package. These objectives are accomplished through the completion of following tasks:

# *Task 1. Develop an experimentally validated compact thermal model of glass interposer for thermal characterization study*

In order to estimate the thermal performance of glass interposer, it is important to develop an experimentally validated thermal model. Research task 1 focuses on investigating out-of-plane and in-plane effective thermal conductivity of glass substrate enhanced by copper structures such as TPVs and copper traces. To develop a numerical model of interposer package with complicated copper structures, compact thermal modeling scheme is used. The results from the model is validated against test results, and the effect of different copper structures on thermal performance of glass interposer is studied through subsequent numerical modeling.

Task 2. Predict the effect of vapor chamber integrated package substrate on thermal performance of glass interposer

A numerical model of glass interposer mounted on the package substrate, combined with vapor chamber is developed to predict its performance, and the result is compared with the result with silicon interposer. The thermal performance of vapor chamber is estimated by using an effective thermal conductivity calculated from the published thermal resistance data, in conjunction with the analytical expression of thermal resistance for a given geometry of the vapor chamber.

Task 3. Develop a vapor chamber integrated package substrate and characterize its performance

A prototype of vapor chamber integrated package substrate is designed, fabricated and tested to demonstrate its performance. The prototype is made of printed circuit board (PCB) with the thickness of 220/330  $\mu$ m, and oxygen-free copper sheet with 570/950  $\mu$ m thickness. Cylindrical micropillar structures with different pillar arrangements (square, hexagonal, and rectangular) and porosities (0.45/0.5, 0.6, 0.7, and 0.8) are fabricated on PCB using electrochemical process, and their hydraulic performance is characterized using capillary rate-of-rise test and forced liquid flow test. Pillar arrangement that shows the best performance is chosen as a wick structure for the prototype vapor chamber.

Hermetic sealing is an important requirement for two-phase cooling devices as both the leakage of working fluid and inflow of gases deteriorate their performances. In this thesis, the hermetic sealing is achieved by soldering copper sheet which has its periphery area plated with eutectic SnAg alloy (Sn-3.5Ag) and PCB with its copper surface finished with electroless nickel immersion gold (ENIG) process. Due to its small volume, the amount of the working fluid charged in the ultra-thin vapor chamber is much smaller (tens of microliters) than that of working fluid in conventional heat pipes/vapor chambers. In this thesis, a peristaltic pump is used to control the volume of charging fluid with microliter-scale accuracy.

#### **1.5** Overview of Chapters

This dissertation is organized into seven chapters. Each chapter begins with the review of relevant literature and theoretical background, followed by fabrication processes/characterization/data analysis, or details of the numerical models/result analysis.

Chapter 1 introduces 2.5D interposer packaging technology, glass interposers, the need for this research, and the research tasks to complete the objectives. Chapter 2 introduces challenges in modeling 2.5D interposers associated with multi-scale size of the components, and explains how each component is modeled using compact modeling scheme. This chapter also compares the modeling approach with test result using glass TPV samples having different via pitches, and diameters. Chapter 3 performs parametric studies with numerical model developed by using compact modeling scheme introduced in Chapter 2 to investigate the effect of different copper structures (TPVs and copper traces) on the thermal performance of glass interposers. The effect of PCB integrated with vapor chamber is also studied, and compared with thermal performance of interposers on the ordinary PCB. Chapter 4 explains the fabrication process of the package substrate integrated with vapor chamber. Details on fabrication steps and any test performed in each step are provided in this chapter, including wick structure fabrication and hydraulic performance testing, and device charging and sealing. Chapter 5 explains the test setups

for measuring thermal performance of vapor chamber. The test results of vapor chambers with different total thickness are presented and discussed. Chapter 6 explains the modeling process of vapor chamber. The code developed for vapor chamber is validated against the literature. 3D numerical model of vapor chamber integrated PCB is then developed and the results are compared with the test. Finally, Chapter 7 summarizes the key findings, research contributions, and potential extension of the research presented in the dissertation.

#### CHAPTER 2. THERMAL MODELING OF GLASS INTERPOSER

#### 2.1 Compact Thermal Modeling of Electronics

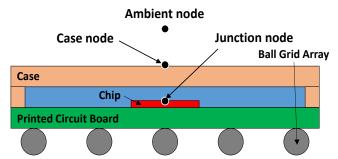

The goal of compact thermal modeling is to predict sufficiently accurate thermal responses of electronic components without constructing highly geometrically detailed models. Two approaches are often used for compact modeling of electronic systems. The first represents the packaging of electronic systems as single or two thermal resistors by using analogy between heat flow and electrical current flow. For commonly used packaging configurations as shown in Figure 2.1, the junction-to-ambient thermal resistance (R<sub>JA</sub>) can be used as a thermal characterization parameter. R<sub>JA</sub> consisting of an internal resistance (R<sub>JC</sub>), and an external resistance (R<sub>CA</sub>). R<sub>JC</sub> characterizes the thermal path between die and case, and R<sub>CA</sub> is associated with the heat transfer between case and the coolant around the case [18]. Although the resistor model is simple and the most intuitive compact model approach, the choice of a reference temperature value becomes ambiguous when describing 3D stacked packages, and non-uniform temperature profile around chip area also poses difficulty in applying resistor concept to the model. The second approach also utilizes thermal resistor model, but reduces it to an effective thermal conductivity. Calculated effective thermal conductivity replaces the thermal properties of the materials. The advantage of this approach is that complicated geometries such as solder ball arrays can be simplified into a single block with effective thermal conductivity, which gives advantages of computational efficiency over detailed model by reducing requirements for mesh size and quality. It also captures temperature profile from nonuniform heat generation better than first approach. However, the second approach averages

out the peak temperature on the localized hot spot, which might lead to an inaccurate prediction of junction temperature. Despite this disadvantage, this approach is often used for a system level analysis to compare thermal performances of different thermal management technologies.

Figure 2.1 Schematic view of ball grid array (BGA) package with junction, case, and ambient nodes [14]

#### 2.2 Compact Thermal Modeling of Glass Interposer

As shown in Figure 1.1, interposers consist of microbumps, interposer substrate, TPVs, and bumps. Bumps are used for forming electrical connections with small bump pitches (~500  $\mu$ m), and microbumps are miniaturized bumps with pitches less than 50  $\mu$ m, designed to provide high wiring density in chips. Top and bottom surfaces of the interposer substrate are laminated with dielectric layers, which work as buildup layers for wiring, referred to as redistribution layers (RDLs). Complicated copper traces are buried in the RDLs and connected to enable communication between different chips mounted on the interposer. There are through package vias (TPVs) in the interposer substrate, which pass completely through the substrate for vertical electrical connection between chips and package substrate. The TPVs are either partially or fully filled with copper. Figure 1.1 and Table 2.1 compare the various length scales of different components in interposer. When including all the fine details of interposers in the model results in need of extensive

computational time and resources to solve the simulation. As such, a compact or reduced order modeling methodology is needed. Over-simplification of the geometric features, however, can produce large errors in predicting temperature profile of the system.

|                             | Size (Width(mm) x Length(mm) x Height (mm)) |

|-----------------------------|---------------------------------------------|

| Chip                        | 10 x 10 x 0.5                               |

| Interposer                  | 25 x 25 x 0.2                               |

| Printed Circuit Board (PCB) | 50 x 50 x 1.2                               |

Table 2.1 Geometric dimensions of chip, interposer and printed circuit board (PCB)

Several numerical simulations have been carried out to study the temperature distribution within 2.5D and 3D ICs with through silicon vias (TSVs) by using the second approach. Ma et al. proposed a simplified thermal model for TSVs in interposer by using effective thermal properties [19]. The accuracy and the application limits of the developed compact model were presented, along with the volume ratio of copper and the silicon. Lau et al. studied the thermal performance of 3D IC integration system-in-package (SiP) with TSVs through modeling [20]. The study presented the effect of various parameters, including TSV filler material, diameter, pitch, and aspect ratios, on the thermal resistance of the interposers. While a number of works have been reported on the thermal characterization of silicon-based 2.5D and 3D integration technologies, thermal studies on glass based integration technologies are currently lacking.

#### 2.2.1 Compact thermal modeling of microbump/TPV/bump

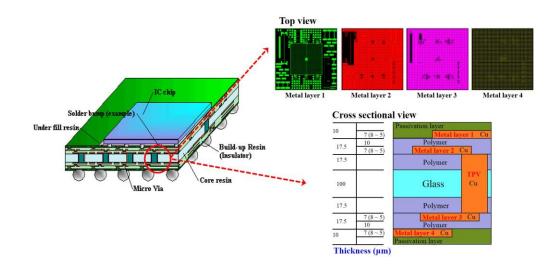

Microbump/TPV/bump arrays are modeled by simplifying the geometry into an equivalent block with effective thermal conductivity. Figure 2.2 summarizes the compact modeling procedure used for TPV array. To begin with, a unit cell of TPV is chosen, and

thermal boundary conditions to calculate effective thermal conductivity are applied to this cell.

# Figure 2.2 Compact modeling scheme used for TPV modeling. Upper part of TPV array is connected to microbumps, and lower part is connected to bumps.

Out-of-plane (z direction) effective thermal conductivity is calculated by imposing uniform heat flux condition at top and negative heat flux at bottom surface, while surrounding surfaces are set as adiabatic. The average temperatures of the top and bottom surfaces are obtained and consequently the equivalent thermal conductivity is calculated using

$$k_{eff} = Q'' \frac{\Delta x}{\Delta T} \tag{1}$$

Where Q'' is the heat flux,  $\Delta x$  the thickness of the sample, and  $\Delta T$  the temperature difference across it. In-plane (x-y direction) effective thermal conductivity is calculated by applying the same boundary conditions to two side walls, while the other boundaries are kept as adiabatic. This approach averages local hot spot temperature, which may underestimate the peak temperature. However, using average die temperature is still a valid approach to evaluate and compare thermal characteristics of electronics packaging while a

uniform heat generation is assumed. The approach was validated under uniform heat generation boundary condition by comparing the simplified model with detailed model, which showed only ~1% difference between maximum temperatures predicted by the two models. More detailed validation of the approach under various geometric conditions is provided in the literature [19].

#### 2.2.2 Compact modelling of copper traces

Figure 2.3 Glass interposer substrate with single chip (left image from http://www.shinko.co.jp/english/product/buildup/dll.html), top view of example metal layers' layout, and cross-sectional view of TPV and metal layers (right).

In a redistribution layer (RDL), copper traces are patterned in a sophisticated way to enable I/O layout, and they fan out from the chips to a looser pitch footprint. Such redistribution requires thin film polymers such as dielectric layers, and metallization to enlarge the pitch of the chip I/Os to match that of another array configuration with larger pitch. Figure 2.3 shows a top view of the four example metal layers with different patterns, and a cross-sectional view of TPV and copper traces patterned in a glass interposer substrate with single IC chip.

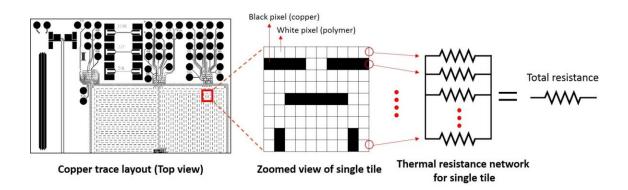

Figure 2.4 Determination of total thermal resistance to obtain in-plane effective thermal conductivity for compact modeling of metal layer.

Figure 2.4 explains how in-plane effective thermal conductivity is calculated for metal layer with copper traces when the layers are assumed to be orthotropic. First, the CAD drawing of a metal layer is converted to a binary image, which contains the size and location information of the copper traces and the polymer. A black pixel in the Figure 2.4 represents copper, and the white pixel represents polymer. Then, the layout is divided into small tiles and each tile's total thermal resistance is obtained by using thermal resistance network analysis. Out-of-plane thermal conductivity of metal layer is calculated with the assumption that black and white pixels are thermally parallel. Pixel resolution of the image is considered acceptable when the difference between calculated effective thermal conductivity from current image and the highest resolution image that CAD program could export is less than 5 %. Generally, 25 times reduction of pixels from maximum resolution results in ~4% difference between the results.

Equation (2) and (3) are used to calculate in-plane (row: x-direction, column: ydirection) and out-of-plane (z-direction) effective thermal conductivity, respectively.

$$R_{row/column} = \frac{(Number of white pixels) \times (Pixel size)}{k_{polymer}A_{row/column}} + \frac{(Number of black pixels) \times (Pixel size)}{k_{copper}A_{row/column}}$$

$$R_{total} = \frac{1}{\sum (1/R_{row/column})}$$

$$k_{in-plane} = \frac{L_{total}}{A_{total}} \sum (1/R_{row/column})$$

$$R_{total} = \frac{1}{1/R_{copper} + 1/R_{polymer}}$$

$$k_{out-of-plane} = \frac{A_{copper}}{A_{total}} \times k_{copper} + \frac{A_{polymer}}{A_{total}} \times k_{polymer}$$

$$(3)$$

The tile with complicated copper traces is then converted into a simple block with calculated effective thermal conductivities along x, y, and z direction. More details and the validation of this approach are presented in [21].

#### 2.2.3 Thermal conductivity measurement of glass interposer components

Prior to develop a numerical model of glass interposer package, out-of-plane thermal conductivity of polymer is experimentally determined by using IR microscopy. The Quantum Focus Instruments (QFI) Infrascope II infrared (IR) microscope is used for the measurements. The IR imaging is performed using the IR microscope's 15X objective lens, which has a spatial resolution of 2.8  $\mu$ m and a pixel size of 1.6  $\mu$ m. The temperature resolution is approximately 0.1 °C.

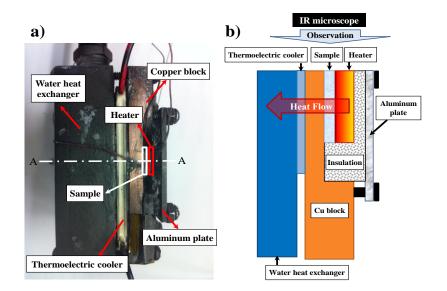

Figure 2.5 Setup for out-of-plane thermal conductivity measurement

Figure 2.5 shows the experimental setup for thermal conductivity measurement. For the measurement, separate test fixture (Figure 2.6) is machined to observe the temperature gradient along the edges of the samples with 1 cm by 1 cm size. Sample is first placed in the test fixture which is equipped with ceramic heater (Barry Industries) and thermoelectric cooler. Then the test fixture is mounted on the IR microscope stage. A water-cooled heat sink is used to remove the heat from the thermoelectric cooler. An Agilent 34970A Data Acquisition/Switching unit reads the thermocouples which are strategically placed to confirm the temperature reading from IR microscope. The cooling water, which flows through the water heat exchanger to cool down the test fixture temperature, is pumped through the system using RM6 Lauda constant temperature bath. The heater power is supplied through an Agilent System 6644A DC Power Supply. A Hewlett Packard E3632A DC Power Supply controlled the thermoelectric cooler.

Figure 2.6 a) Top view of test fixture and b) cross-sectional view of section A-A.

Figure 2.6 a) shows a top view of the sample fixture and b) shows a cross sectional view taken along the line A-A in a). A ceramic heater which corresponds to the sample size is used to heat up one side of the sample. The other side of the sample is cooled down by the thermoelectric cooler, attached to a copper block.

Two 1 cm by 1 cm polymer and glass samples are prepared, and placed between a copper block and a heater so that one edge of the sample is exposed for measurements. Unexposed edges are insulated to ensure unidirectional heat conduction. Thermal grease is applied at the heater/sample and sample/copper block interfaces to reduce temperature drops at the interfaces. An aluminum plate is used to firmly fix the sample within the fixture. Once the sample is mounted, its exposed part is coated with carbon spray to keep its emissivity high enough to reduce the experimental uncertainty.

The sample and copper block are heated by a thermoelectric unit until they reach a steady state temperature. Radiance is measured to generate reference emissivity map of the sample and is used to determine temperature distribution along the thickness of the sample. Following the reference emissivity mapping, the heater is turned on to heat one side of the sample, and the thermoelectric cooler to cool the other side and copper block. The power supplied to the heater is used for heat flux calculation and the thermocouple measurements are used to ensure that the system has reached the steady state. The IR microscope measures temperature distribution of the sample based on the radiance and emissivity map previously recorded.

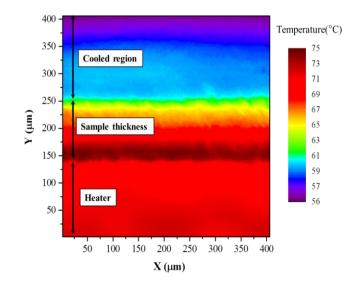

Figure 2.7 Temperature map from IR microscope measurement.

Figure 2.7 shows the temperature distribution measured at the edge of the polymer sample and its surroundings. The temperature change shows almost linear behavior across the sample thickness, between 150  $\mu$ m and 250  $\mu$ m region, which corresponds to the sample thickness of 100  $\mu$ m. The temperature readings of the pixels locating at the same Y axis are averaged for thermal conductivity calculations. The heat flux *Q*" generated by heater is calculated by

$$Q'' = \frac{VI}{A} = \frac{I^2 R}{A} \tag{4}$$

where I is the current supplied to the heater, R its resistance, V the voltage readout from the power supply, and A the cross-sectional area of the sample. Thermal conductivity, k, can be determined by Equation (1).

Thermal conductivity of each sample is measured for four different heat fluxes. The uncertainty of the thermal conductivity is determined by Equation (5).

$$U_{k} = \left\{ \left( \frac{\partial k}{\partial (Q/A)} U_{Q/A} \right)^{2} + \left( \frac{\partial k}{\partial (\Delta x)} U_{\Delta x} \right)^{2} + \left( \frac{\partial k}{\partial (\Delta T)} U_{\Delta T} \right)^{2} \right\}^{\frac{1}{2}}$$

(5)

17

where U is uncertainty. Table 2.2 shows the measured thermal conductivity values of samples and their comparison with manufacturer's value. Comparison results show that the measured thermal conductivities are in reasonable agreement with suppliers' data, showing 4% and 15% difference for each different sample. More details about thermal conductivity measurement technique using IR microscope can be found from [22].

Table 2.2 Measured thermal conductivity of samples

|           | Measured Value | Reported Value  |

|-----------|----------------|-----------------|

|           | (W/m·K)        | $(W/m \cdot K)$ |

| Polymer 1 | 1.05±0.02      | N/A             |

| Polymer 2 | 0.52±0.01      | 0.50            |

| Glass     | 1.15±0.04      | 1.00            |

### 2.2.4 Effective thermal conductivity measurement of copper TPVs

To validate compact thermal modeling scheme used for TPVs, the effective thermal conductivity of glass sample with copper TPVs is measured and compared with the result from numerical model.

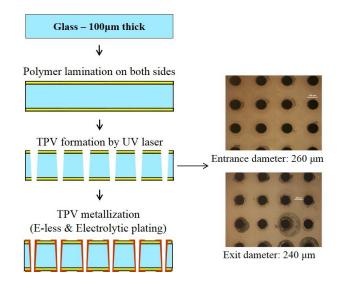

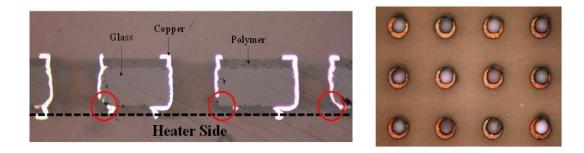

Figure 2.8 Process flow for glass TPV sample fabrication.

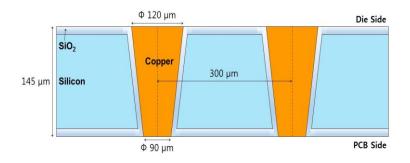

TPV via arrays with different diameters and pitches are fabricated on a 114 mm  $\times$  114 mm  $\times$  100 µm borosilicate glass panel. Prior to via drilling, both surfaces of the panel are cleaned with acetone and isopropyl alcohol (IPA). Then both sides are laminated with 22.5 µm-thick dielectric polymer layers. A hot press machine is used during the lamination process with optimized temperature and time settings. The laminated polymer layer serves as a buildup layer for wiring, and also as a buffer layer which reduces the impact of laser on glass during the ablation process. The laminated glass sample is then subjected to ultraviolet (UV) laser ablation for via formation. The UV laser drilling results in tapered via profiles.

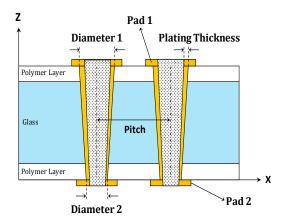

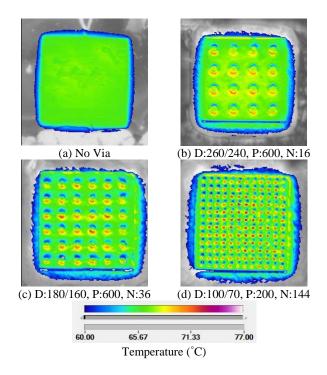

Figure 2.8 summarizes the process flow used for the test sample fabrication. It also shows the optical images of glass samples' via entrance and exit formed by UV laser ablation. To achieve good metal adhesion to the glass panel, the surface of polymer is roughened through micro etch processes. A 1  $\mu$ m copper seed layer is formed on the roughened surface through electroless copper deposition, followed by electrolytic copper plating processes which results in final copper layer thickness of 10  $\mu$ m. After having via side walls plated, via pads are patterned by using photolithography. Via pad diameter is designed to be 40  $\mu$ m larger than each via diameter. Table 2.3 summarizes the via dimensions of fabricated via arrays including entrance and exit via diameters, pitches, plating thickness, pad size, and the number of vias. After patterning the via pads, the panel is diced into 10 pieces of 2.54 mm × 2.54 mm size glass samples with TPV arrays having different via parameters.

Table 2.3 TPV geometry and dimensions

| Diameters (1 & 2) | Pad (1 & 2) | Pitch  | # of vias |  |

|-------------------|-------------|--------|-----------|--|

| 1:100 µm,         | 1: 140 µm,  | 200    | 144       |  |

| 2: 70 µm          | 2: 110 µm   | 200 µm | 144       |  |

| 1: 180 µm,        | 1: 220 µm,  | 400 um | 36        |  |

| 2: 160 µm         | 2: 200 µm   | 400 µm | 50        |  |

| 1: 260 µm,        | 1: 300 µm,  | 600 um | 16        |  |

| 2: 240 µm         | 2: 280 µm   | 600 µm | 16        |  |

To measure thermal conductivity of via samples, a heater assembly is fabricated, which consists of a heater and a PCB. The size of the heater is  $2.54 \text{ mm} \times 2.54 \text{ mm}$ , which corresponds to the sample size with 100 µm thickness. The heater is comprised of two resistors, each able to dissipate a maximum power of 6 W and is wire bonded to the PCB for power supply connection. Two diodes placed at the center and the edge of the heater are utilized for surface temperature measurements. The heat generating surface of the

heater is exposed to ambient, and its other sides are surrounded by epoxy with wire bonds. The epoxy protects the heater and wirebonds from mechanical and electrical impact and also minimizes heat loss from the surfaces of heater. After the epoxy is cured, the heater diodes are calibrated by putting the assembly in a large oven. A via patterned glass sample of the size of 2.54 mm  $\times$  2.54 mm is attached to the heater by using thermal adhesive pad. After the sample is attached to the heater, the assembly is covered with an insulation material to reduce heat losses through convection and radiation to the ambient.

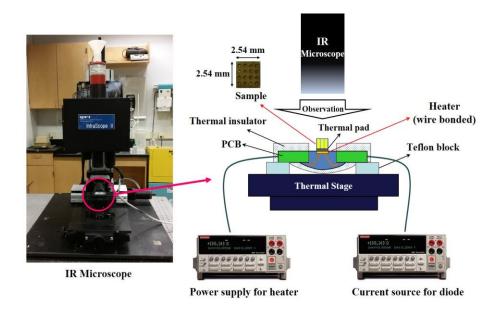

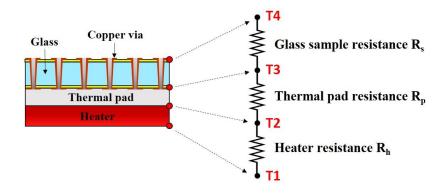

Figure 2.9 Schematic of test setup to measure effective thermal conductivity of glass samples with copper TPVs

Figure 2.9 shows the schematic of test setup used to measure the effective thermal conductivity of glass samples with copper TPVs. A QFI IR microscope is used to measure surface temperature of the sample. The heater assembly is mounted and tightly fixed on the thermal stage of IR microscope by using Teflon blocks. Two source meters are

connected to the heater assembly to supply power to the heater, and to provide constant current source (1 mA) to diodes.

Six additional thermocouples are attached to the PCB and the epoxy area to estimate the amount of heat dissipated through conduction. Prior to the measurements, the surface of the sample is coated with a black carbon spray to reduce the uncertainty in the measurement.

Heat loss through epoxy is estimated by using thermal resistance analysis, including spreading resistance and calculated to be ~ 14% of total power input of the heater. Heat loss through convection  $Q_c$  is estimated by using Equation (6) and its heat transfer coefficient  $h_c$  is calculated using Equation (7) for small devices in natural convection [23].

$$Q_c = h_c A \Delta T \tag{6}$$

$$h_c = 0.83 f \left(\Delta T / L_{ch}\right)^n \tag{7}$$